# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**User's Manual**

# How to Use Low Latency DRAM

Document No. M19202EJ1V0UM00 (1st Edition) Date Published July 2008 NS

© NEC Electronics Corporation 2008

Printed in Japan

[MEMO]

#### **1** VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between V<sub>IL</sub> (MAX) and V<sub>IH</sub> (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between V<sub>IL</sub> (MAX) and V<sub>IH</sub> (MIN).

#### (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### **③** PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must have hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### **④** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

#### 5 POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

#### **(6)** INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

QDR RAMs and Quad Data Rate RAMs comprise a new series of products developed by Cypress Semiconductor, Renesas, IDT, NEC Electronics, and Samsung.

- The information in this document is current as of July, 2008. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

# INTRODUCTION

- Target Readers

This manual is intended for users who design application systems which use low latency DRAM.

- Purpose

The purpose of this manual is to help users understand the basic functions of low latency

DRAM, and how to use them.

For the detailed values of each product, see the corresponding data sheets.

- How to Read This Manual It is assumed that the readers of this manual have general knowledge of electrical engineering, logic circuits, and memory products. For details of the functions of each product, see the corresponding data sheets. Note that the operation examples described in this user's manual are presented for reference and that the described data are not guaranteed values but values to be used for reference.

ConventionsData significance:Higher digits on the left and lower digits on the rightxxx# (sharp symbol appended to a pin or signal name) :

|          | Active low representation                       |  |  |

|----------|-------------------------------------------------|--|--|

| Note:    | Footnote for item marked with Note in the text. |  |  |

| Caution: | Information requiring particular attention      |  |  |

| Remark:  | Supplementary information                       |  |  |

**Configuration** This manual is configured of the following contents.

CHAPTER 1 OVERVIEW CHAPTER 2 COMMANDS CHAPTER 3 REFRESH OPERATIONS CHAPTER 4 POWER APPLICATION CHAPTER 5 PLL CIRCUIT CHAPTER 6 OUTPUT IMPEDANCE MATCHING CHAPTER 7 TERMINAL RESISTORS CHAPTER 8 ON DIE TERMINATION (ODT)

# CONTENTS

| CHAPTER 1 OVERVIEW                                                       | 11 |

|--------------------------------------------------------------------------|----|

| 1.1 Features                                                             |    |

| 1.2 CIO and SIO Product Characteristics                                  | 12 |

| 1.3 Bank Operation                                                       | 13 |

| 1.4 Data Transfer Rate (Band Width) Comparison                           | 16 |

| 1.5 Explanation of pin functions                                         | 17 |

| 1.6 Output Data and Output Data Clock                                    | 21 |

| 1.6.1 READ latency (tr∟)                                                 | 21 |

| 1.6.2 Output data and output data clock timing                           | 22 |

| 1.7 HSTL interface and VREF                                              | 23 |

| CHAPTER 2 COMMANDS                                                       |    |

| 2.1 Command Operation                                                    | 24 |

| 2.2 DESEL/NOP Command                                                    | 25 |

| 2.3 MRS Command                                                          | 25 |

| 2.3.1 How to set MRS command                                             | 25 |

| 2.3.2 Configuration setting                                              | 28 |

| 2.3.3 Burst length (BL) setting                                          |    |

| 2.3.4 Non-multiplexed address mode and multiplexed address mode settings | 31 |

| 2.3.5 PLL setting                                                        |    |

| 2.3.6 Output impedance mode setting                                      |    |

| 2.3.7 ODT (On Die Termination) function setting                          | 34 |

| 2.4 READ and WRITE Commands                                              | 35 |

| 2.5 AREF                                                                 | 54 |

| CHAPTER 3 REFRESH OPERATIONS                                             | 55 |

| 3.1 Refresh Operations                                                   | 55 |

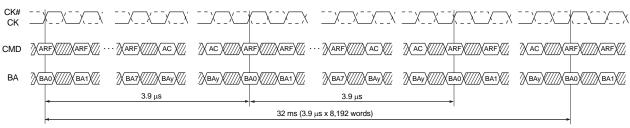

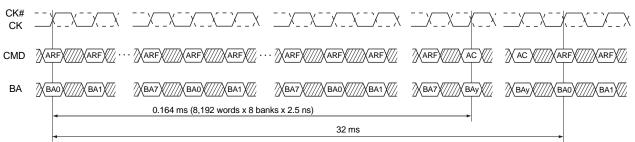

| 3.1.1 Distributed refresh operation                                      |    |

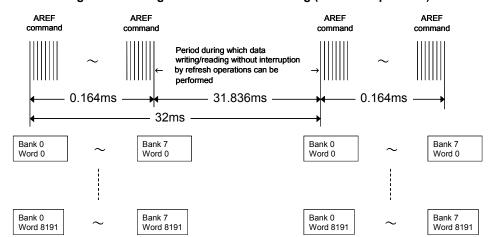

| 3.1.2 Burst refresh operation                                            | 57 |

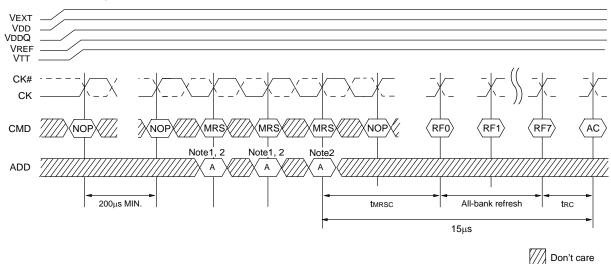

| CHAPTER 4 POWER APPLICATION                                              |    |

| 4.1 Non-Multiplexed Address Mode                                         |    |

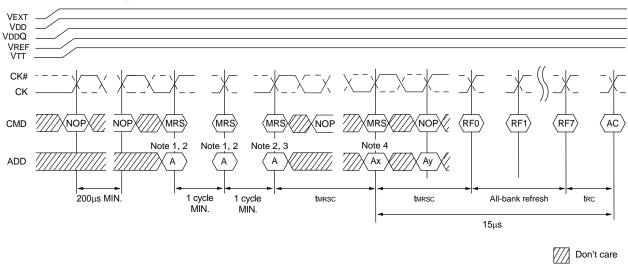

| 4.2 Multiplexed Address Mode                                             | 60 |

| CHAPTER 5 PLL CIRCUIT                                                    | 62 |

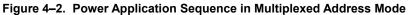

| 5.1 Mounting PLL Circuit                                                 | 62 |

| 5.1.1 Advantages of PLL circuit                                          |    |

| 5.1.2 Disabling PLL circuit                                              |    |

| 5.1.3 Clock stop                                                         |    |

| 5.1.4 Operation frequency change                                         | 63 |

| CHAPTER 6 OUTPUT IMPEDANCE MATCHING                                      |    |

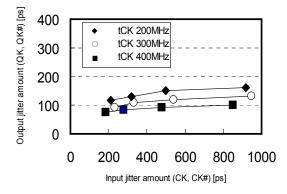

| 6.1 Output Impedance Adjustment                                          | 64 |

| CHAPTER 7 TERMINAL RESISTORS                                             |    |

| 7.1 Effects of Terminal Resistor                                         | 66 |

| CHAPTER 8 ON DIE TERMINATION (ODT) | 68 |

|------------------------------------|----|

| 8.1 ODT Function Setting           |    |

| 8.2 ODT-On Timing of Each Pin      |    |

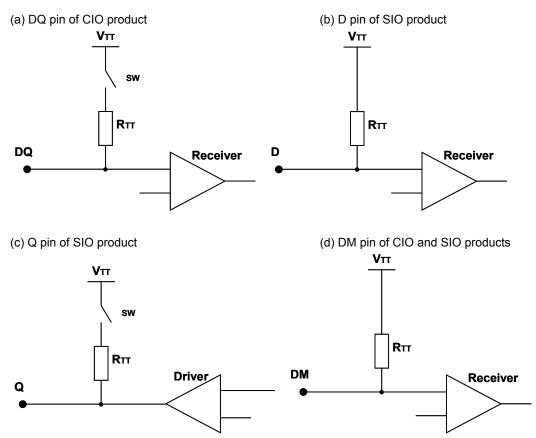

| 8.3 ODT Structure                  |    |

| 8.4 ODT DC Parameters              |    |

|                                    | •  |

# LIST OF FIGURES (1/2)

| Figu | re No. Title P                                                                                            | age   |

|------|-----------------------------------------------------------------------------------------------------------|-------|

| 1–1  | CIO Product Timing Chart (Non-Multiplexed Address Mode, BL = 2, Configuration 1)                          | 12    |

|      | SIO Product Timing Chart (Non-Multiplexed Address Mode, BL = 2, Configuration 1)                          |       |

|      | CIO Product Timing Chart (Non-Multiplexed Address Mode, BL = 2, Configuration 1)                          |       |

| 1–4  | SIO Product Timing Chart (Non-Multiplexed Address Mode, BL = 2, Configuration 1)                          | 14    |

| 1–5  | CIO Product Timing Chart Including Refresh Operation (Non-Multiplexed Address Mode, BL = 2, Configuration | on 1) |

|      |                                                                                                           | 15    |

| 1–6  | SIO Product Timing Chart Including Refresh Operation (Non-Multiplexed Address Mode, BL = 2, Configuration | on 1) |

|      |                                                                                                           | 15    |

| 1–7  | Band Width Efficiency READ and WRITE Command Input Ratio Dependence                                       | 16    |

| 1–8  | READ Timing Chart (Non-Multiplexed Address Mode, BL = 2, Configurations 1, 2, 3)                          | 22    |

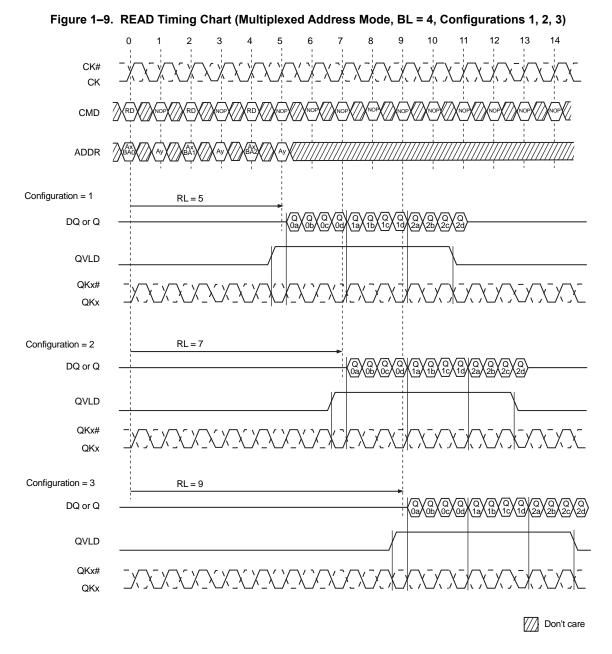

| 1–9  | READ Timing Chart (Multiplexed Address Mode, BL = 4, Configurations 1, 2, 3)                              | 23    |

|      |                                                                                                           |       |

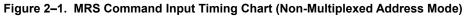

| 2–1  | MRS Command Input Timing Chart (Non-Multiplexed Address Mode)                                             | 25    |

| 2–2  | Pin Input States During MRS Command Input (Non-Multiplexed Address Mode)                                  | 26    |

| 2–3  | MRS Setting Timing Chart (Multiplexed Address Mode)                                                       | 27    |

| 2–4  | How to Input to Pins During MRS Command Input (Multiplexed Address Mode)                                  | 27    |

| 2–5  | CIO Product Timing Chart (Non-Multiplexed Address Mode, BL = 2, Configuration 1)                          | 35    |

| 2–6  | SIO Product Timing Chart (Non-Multiplexed Address Mode, BL = 2, Configuration 1)                          | 35    |

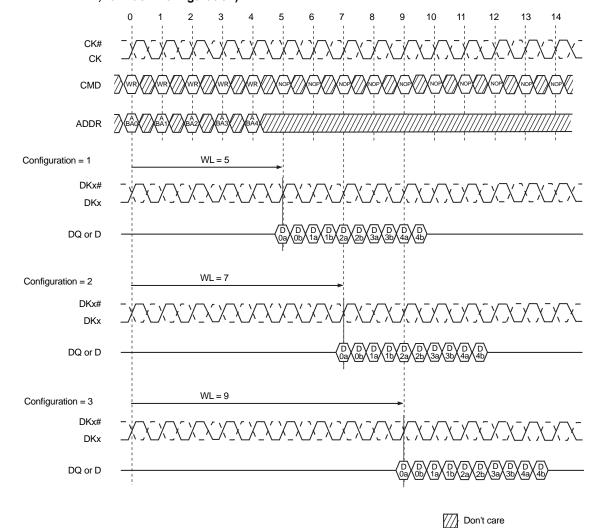

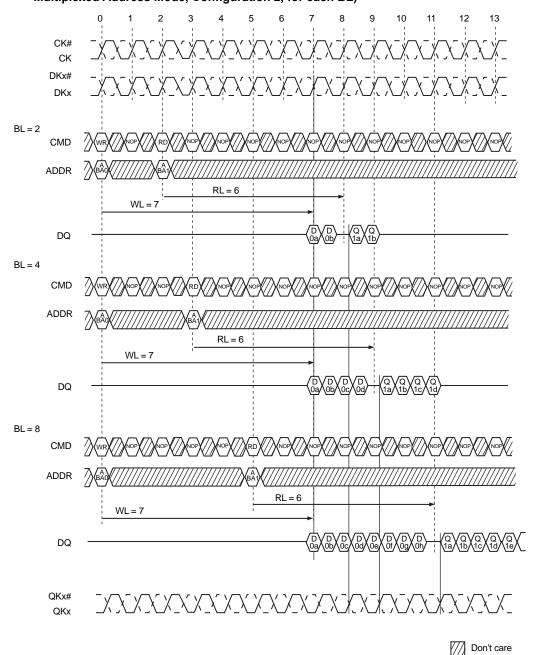

| 2–7  | Timing Charts of Successive READ Commands (CIO Products, Non-Multiplexed Address Mode, BL = 2, for        |       |

|      | Each Configuration)                                                                                       | 36    |

| 2–8  | Timing Charts of Successive WRITE Commands (CIO Products, Non-Multiplexed Address Mode, BL = 2, for       |       |

|      | Each Configuration)                                                                                       | 37    |

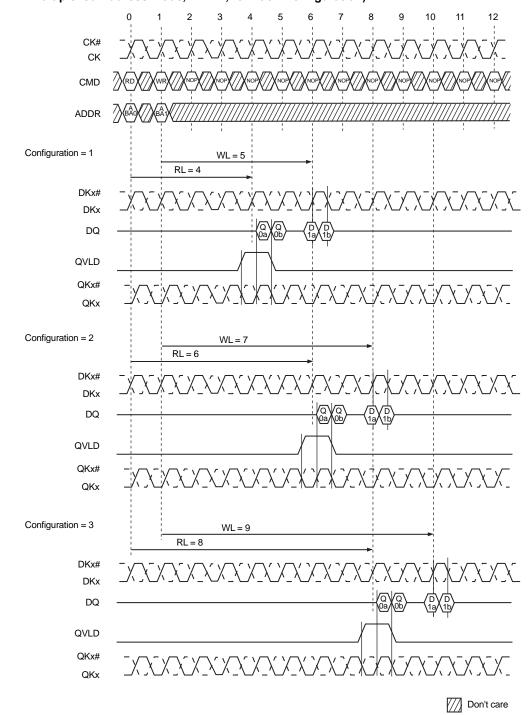

| 2–9  | Timing Charts When READ Commands Are Switched to WRITE Commands (CIO Products, Non-Multiplexed            | I     |

|      | Address Mode, BL = 2, for Each Configuration)                                                             | 38    |

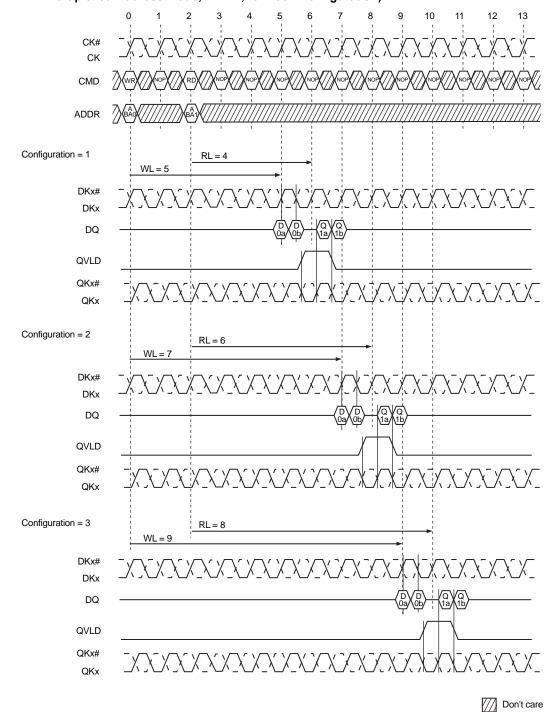

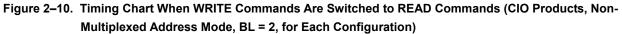

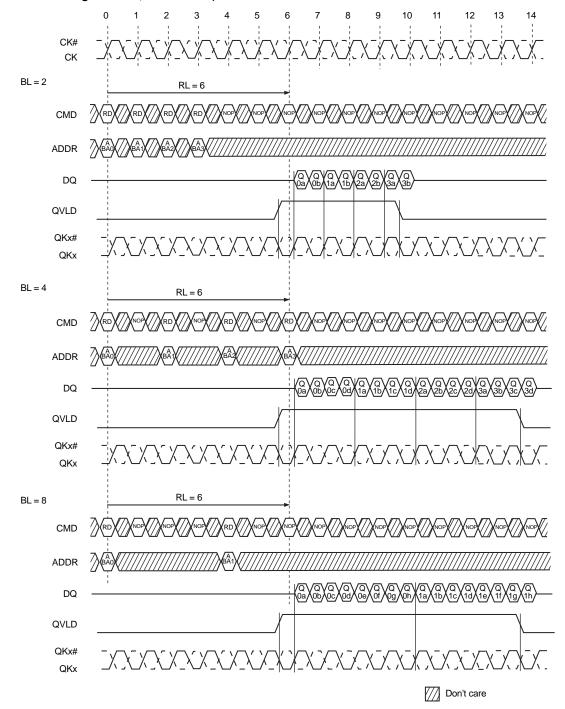

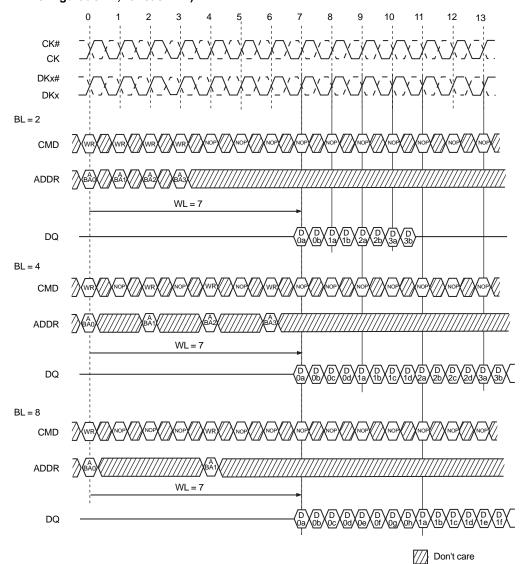

| 2–10 | Timing Chart When WRITE Commands Are Switched to READ Commands (CIO Products, Non-Multiplexed             |       |

|      | Address Mode, BL = 2, for Each Configuration)                                                             | 39    |

| 2–11 | Timing Charts of Successive READ Commands (CIO Products, Non-Multiplexed Address Mode, Configuration      | ion   |

|      | 2, for each BL)                                                                                           | 40    |

| 2–12 | Timing Charts of Successive WRITE Commands (CIO Products, Non-Multiplexed Address Mode, Configura         | ition |

|      | 2, for each BL)                                                                                           | 41    |

| 2–13 | Timing Charts When READ Commands Are Switched to WRITE Commands (CIO Products, Non-Multiplexe             |       |

|      | Address Mode, Configuration 2, for each BL)                                                               |       |

| 2–14 | Timing Charts When WRITE Commands Are Switched to READ Commands (CIO Products, Non-Multiplexe             | d     |

|      | Address Mode, Configuration 2, for each BL)                                                               |       |

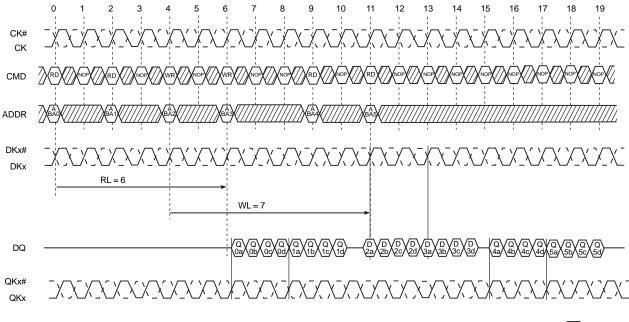

| 2–15 | Timing Chart of CIO Products in Non-Multiplexed Address Mode (BL = 4, Configuration 1)                    |       |

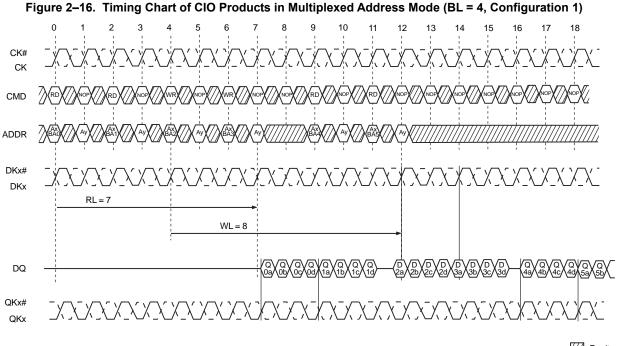

| 2–16 | Timing Chart of CIO Products in Multiplexed Address Mode (BL = 4, Configuration 1)                        |       |

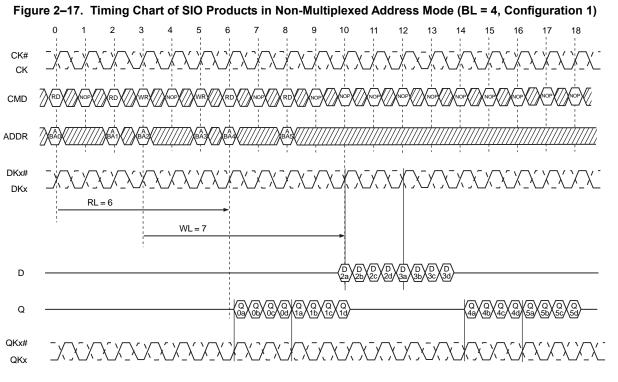

| 2–17 | Timing Chart of SIO Products in Non-Multiplexed Address Mode (BL = 4, Configuration 1)                    |       |

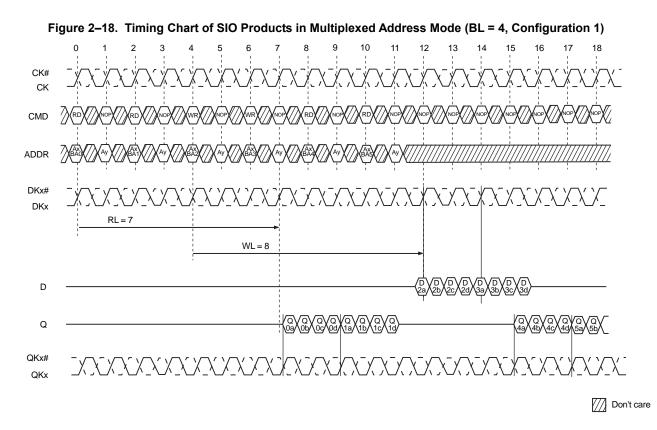

| 2–18 | Timing Chart of SIO Products in Multiplexed Address Mode (BL = 4, Configuration 1)                        |       |

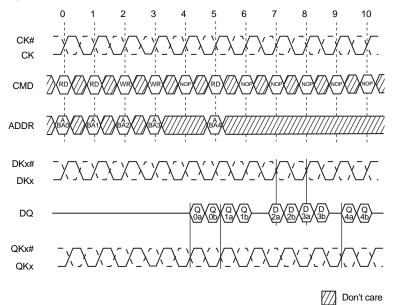

| 2–19 | Timing Chart (CIO Products, Non-Multiplexed Address Mode, BL = 2, Configuration = 1)                      |       |

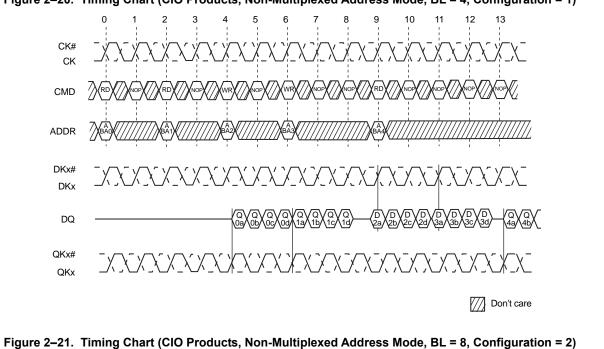

| 2–20 | Timing Chart (CIO Products, Non-Multiplexed Address Mode, BL = 4, Configuration = 1)                      |       |

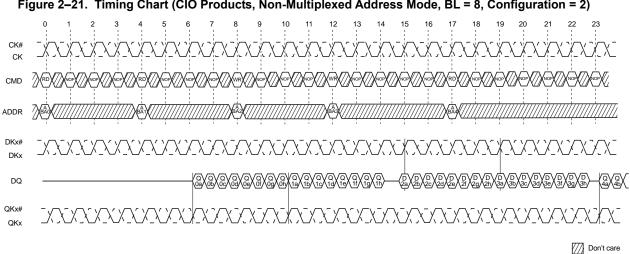

| 2–21 | Timing Chart (CIO Products, Non-Multiplexed Address Mode, BL = 8, Configuration = 2)                      |       |

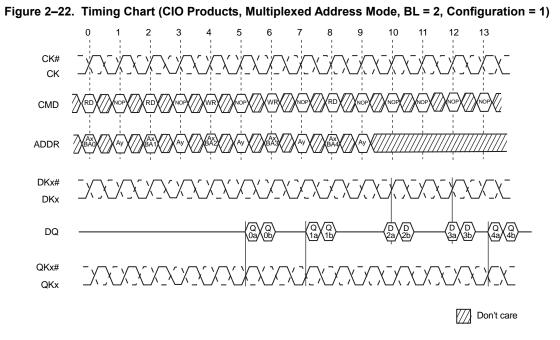

| 2–22 | Timing Chart (CIO Products, Multiplexed Address Mode, BL = 2, Configuration = 1)                          |       |

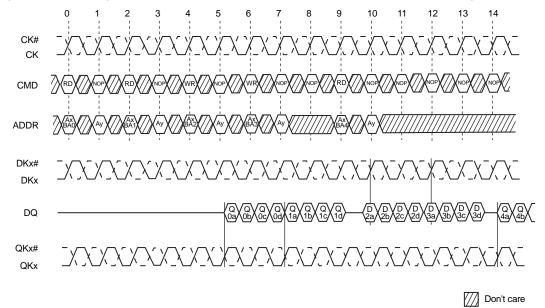

| 2–23 | Timing Chart (CIO Products, Multiplexed Address Mode, BL = 4, Configuration = 1)                          |       |

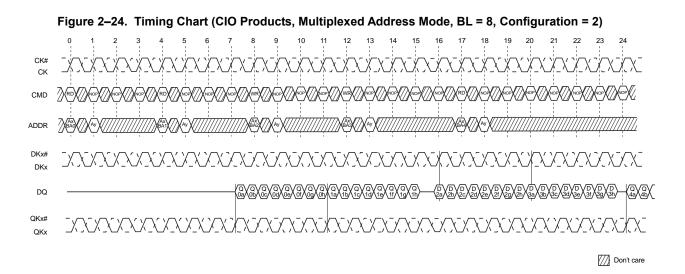

| 2–24 | Timing Chart (CIO Products, Multiplexed Address Mode, BL = 8, Configuration = 2)                          |       |

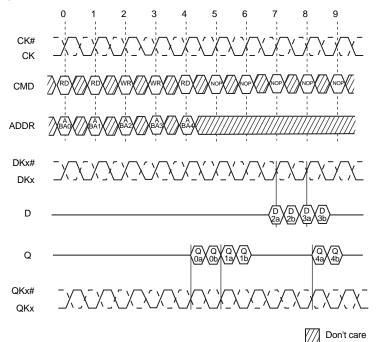

| 2–25 | Timing Chart (SIO Products, Non-Multiplexed Address Mode, BL = 2, Configuration = 1)                      |       |

| 2–26 | Timing Chart (SIO Products, Non-Multiplexed Address Mode, BL = 4, Configuration = 1)                      |       |

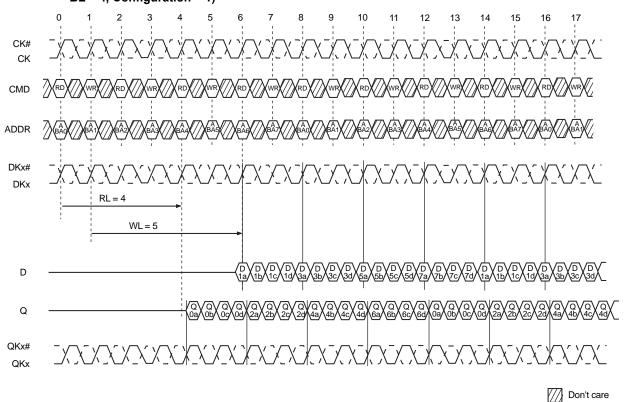

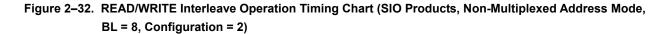

| 2–27 | Timing Chart (SIO Products, Non-Multiplexed Address Mode, BL = 8, Configuration = 2)                      | 50    |

# LIST OF FIGURES (2/2)

| Figu | ire No. Title                                                                                     | Page |

|------|---------------------------------------------------------------------------------------------------|------|

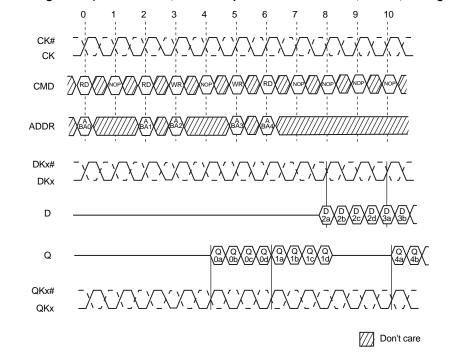

| 2–28 | Timing Chart (SIO Products, Multiplexed Address Mode, BL = 2, Configuration = 1)                  | 51   |

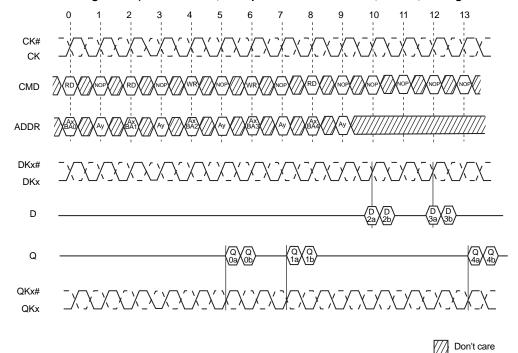

| 2–29 | Timing Chart (SIO Products, Multiplexed Address Mode, BL = 4, Configuration = 1)                  | 51   |

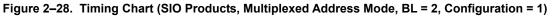

| 2–30 | Timing Chart (SIO Products, Multiplexed Address Mode, BL = 8, Configuration = 2)                  | 52   |

| 2–31 | READ/WRITE Interleave Operation Timing Chart (SIO Products, Non-Multiplexed Address Mode, BL = 4, |      |

|      | Configuration = 1)                                                                                | 52   |

| 2–32 | READ/WRITE Interleave Operation Timing Chart (SIO Products, Non-Multiplexed Address Mode, BL = 8, |      |

|      | Configuration = 2)                                                                                | 53   |

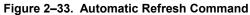

| 2–33 | Automatic Refresh Command                                                                         | 54   |

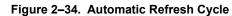

| 2–34 | Automatic Refresh Cycle                                                                           | 54   |

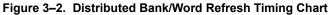

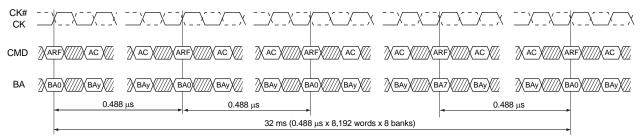

| 3–1  | Image of Distributed Bank/Word Refresh Timing                                                     | 55   |

| 3–2  | Distributed Bank/Word Refresh Timing Chart                                                        |      |

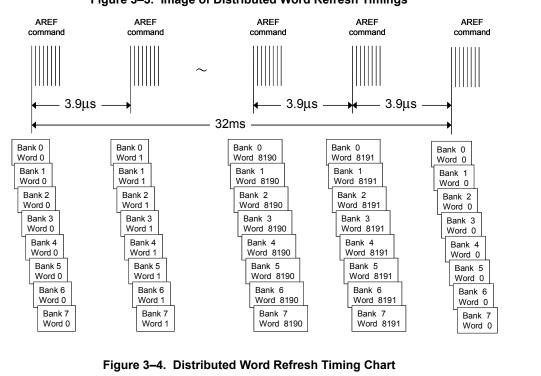

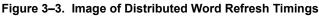

| 3–3  | Image of Distributed Word Refresh Timings                                                         | 56   |

| 3–4  | Distributed Word Refresh Timing Chart                                                             | 56   |

| 3–5  | Image of Burst Refresh Timing (400 MHz Operation)                                                 | 57   |

| 3–6  | Burst Refresh Timing Chart (400 MHz Operation)                                                    | 57   |

| 4–1  | Power Application Sequence in Non-Multiplexed Address Mode                                        | 59   |

| 4–2  | Power Application Sequence in Multiplexed Address Mode                                            | 61   |

| 5–1  | Dependence of Output Jitter Amount on Input Jitter Amount for PLL Circuit                         | 62   |

| 6–1  | Output Impedance Setting Example                                                                  | 65   |

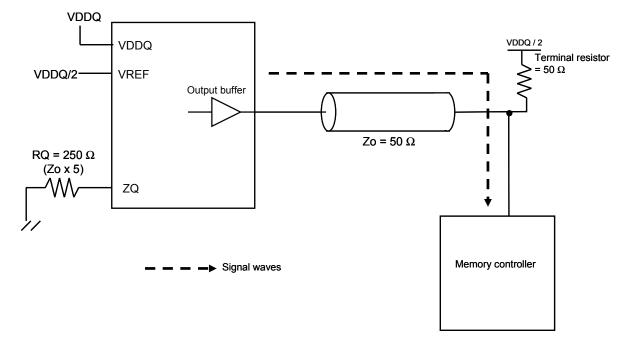

| 7–1  | Image of Signal Wave Transmission When Transmission Line Has Been Terminated                      | 66   |

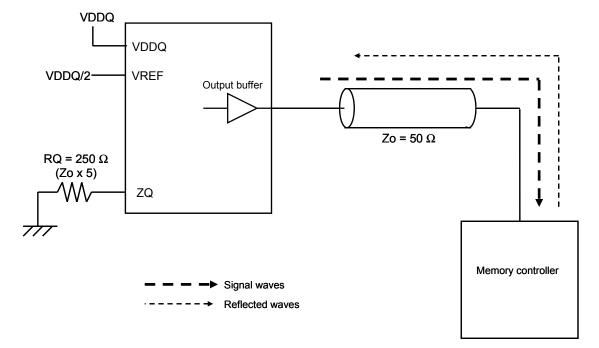

| 7–2  | Image of Signal Wave Transmission When Transmission Line Has Not Been Terminated                  | 67   |

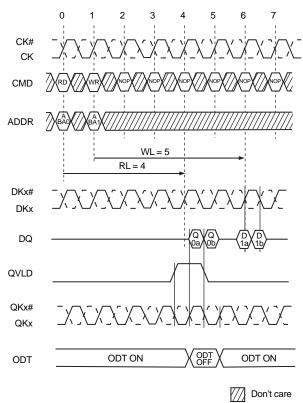

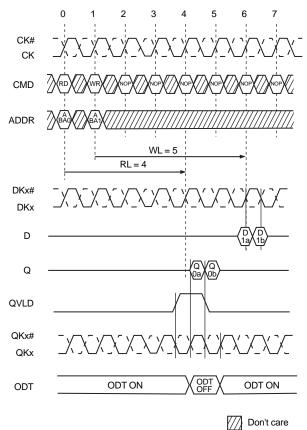

| 8–1  | CIO Product Timing Chart When ODT Is Used (Non-Multiplexed Address Mode, BL = 2, Configuration 1) | 69   |

| 8–2  | SIO Product Timing Chart When ODT Is Used (Non-Multiplexed Address Mode, BL = 2, Configuration 1) | 69   |

| 8–3  | Equivalent Circuits of ODT                                                                        | 70   |

# LIST OF TABLES

| Tab  | le No. Title                                                                           | Page |

|------|----------------------------------------------------------------------------------------|------|

| 1–1  | 288 Mb Low Latency DRAM Product Classification                                         | 11   |

| 1–2  | Selectable Product Functions                                                           | 11   |

| 1–3  | Bank Correspondence                                                                    | 13   |

| 1–4  | Pins Common to CIO and SIO Products (1/3)                                              | 17   |

| 1–5  | Pins Unique to CIO Products                                                            | 20   |

| 1–6  | Pins Unique to SIO Products                                                            | 20   |

| 1–7  | tRL Configuration in Non-Multiplexed Address Mode (Common to CIO and SIO Products)     | 21   |

| 1–8  | tRL Configuration in Multiplexed Address Mode (Common to CIO and SIO Products)         | 21   |

| 2–1  | Command Types and Descriptions                                                         | 24   |

| 2–2  | Determined Commands                                                                    | 24   |

| 2–3  | Number of Addresses Used                                                               | 24   |

| 2–4  | Address Pin Allocation with Respect to Function Setting (Non-Multiplexed Address Mode) | 26   |

| 2–5  | Address Pin Allocation of MRS Setting (Multiplexed Address Mode)                       | 27   |

| 2–6  | Configuration Setting Contents (Non-Multiplexed Address Mode)                          |      |

| 2–7  | Configuration Settings (Non-Multiplexed Address Mode)                                  |      |

| 2–8  | Configuration Setting Contents (Multiplexed Address Mode)                              |      |

| 2–9  | Configuration Settings (Multiplexed Address Mode)                                      | 29   |

| 2–10 |                                                                                        |      |

| 2–11 | BL Settings (Multiplexed Address Mode)                                                 | 30   |

| 2–12 | 2 Address Multiplex Function Setting (Non-Multiplexed Address Mode)                    | 31   |

| 2–13 | Address Multiplex Function Setting (Multiplexed Address Mode)                          |      |

| 2–14 | PLL Setting (Non-Multiplexed Address Mode)                                             | 32   |

| 2–15 | 5 PLL Setting (Multiplexed Address Mode)                                               | 32   |

| 2–16 | ······································                                                 |      |

| 2–17 | Output Impedance Mode Setting (Multiplexed Address Mode)                               |      |

| 2–18 | 3 ODT Function Setting (Non-Multiplexed Address Mode)                                  |      |

| 2–19 |                                                                                        |      |

| 2–20 | ) Timing Charts of READ and WRITE Operations                                           | 46   |

| 5–1  | Mode Register Codes                                                                    | 62   |

| 5–2  | Minimum Operation Frequency                                                            | 63   |

| 6–1  | Mode Register Codes                                                                    | 64   |

| 8–1  | Mode Register Codes                                                                    | 68   |

| 8–2  | Mode Register Codes                                                                    | 68   |

| 8–3  | ODT DC Specifications                                                                  | 70   |

# **CHAPTER 1 OVERVIEW**

NEC Electronics develops QDR<sup>™</sup> SRAMs, DDR SRAMs, and low latency DRAM as memories for network devices. QDR SRAMs and DDR SRAMs are suitable for network devices which require high-speed random access performance, and low latency DRAM is suitable for network devices which require memory capacity and random access performance. Furthermore, the application of low latency DRAM is increasing not only for network devices, but also for digital home appliances. This manual describes how to use low latency DRAM.

#### 1.1 Features

Low latency DRAM is memory which is suited to be used as buffer memories of highly functional network switches, network routers, and digital home appliances. The random access performance is improved by configuring the memory cell array in eight banks.

Low latency DRAM is classified into four major product groups according to the I/O configuration and I/O voltage, as shown in Table 1-1. The part numbers of products differ for I/O voltages of 1.5 V and 1.8 V, so select the I/O voltage product to be used accordingly.

| Part Number        | I/O Configuration | I/O Voltage | Absolute Maximum<br>I/O Voltage Rating |

|--------------------|-------------------|-------------|----------------------------------------|

| μPD482882xxFF-EFxx | Common (CIO)      | 1.5 V       | 1.975 V                                |

| μPD482881xxFF-EFxx | Separated (SIO)   | 1.5 V       | 1.975 V                                |

| μPD482882xxFF-Exx  | Common (CIO)      | 1.8 V       | 2.1 V                                  |

| μPD482881xxFF-Exx  | Separated (SIO)   | 1.8 V       | 2.1 V                                  |

Table 1–1. 288 Mb Low Latency DRAM Product Classification

With low latency DRAM, the product functions shown in Table 1-2 can be set according to the application. See **2.3 MRS Command** for setting descriptions and setting methods, because some functional combinations are restricted.

| Selectable Product Functions            |

|-----------------------------------------|

| Configuration                           |

| • Random cycle time (t <sub>RC</sub> )  |

| • READ latency (t <sub>RL</sub> )       |

| <ul> <li>WRITE latency (twL)</li> </ul> |

| Burst length                            |

| Address multiplex function              |

| PLL function                            |

| Output impedance mode function          |

| ODT function <sup>Note</sup>            |

Note ODT: On Die Termination

### 1.2 CIO and SIO Product Characteristics

CIO (Common I/O) and SIO (Separate I/O) products have different pin counts and command input timings.

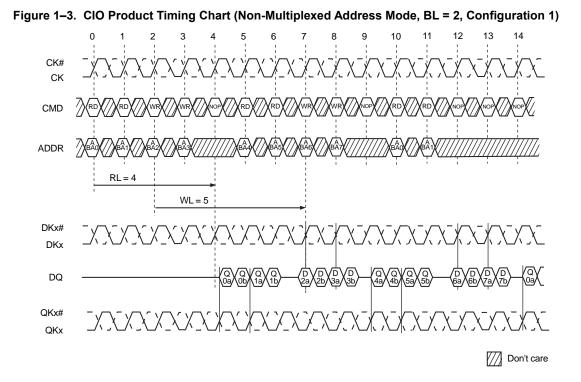

With CIO products, data ports are shared for input and output. The number of I/O pins used can therefore be halved in contrast to SIO products. With CIO products, insertion of NOP cycles, however, is required when switching from WRITE command input to READ command input, as shown in Figure 1-1.

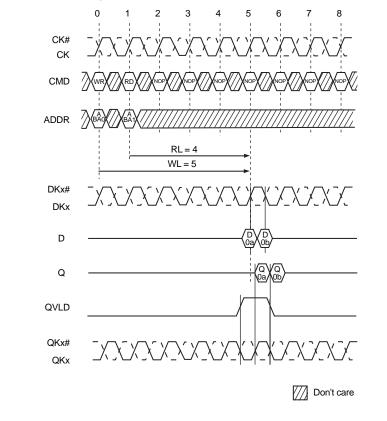

With SIO products, data ports are separately provided for input and output. The data transfer rate (band width) can therefore be improved in contrast to CIO products. Furthermore, unlike with CIO products, insertion of NOP cycles when switching from WRITE command input to READ command input is not required, as shown in Figure 1-2.

Figure 1–1. CIO Product Timing Chart (Non-Multiplexed Address Mode, BL = 2, Configuration 1)

Don't care

Figure 1–2. SIO Product Timing Chart (Non-Multiplexed Address Mode, BL = 2, Configuration 1)

#### 1.3 Bank Operation

The memory cell array is configured in eight banks, each of which can be controlled separately. By freely selecting the bank, banks can be operated normally, even if a refresh operation is performed on another bank.

The selection of banks can be set according to the bank address [BA2:0] input level. Table 1-3 shows the correspondence between the selected addresses of each bank.

| Selected Bank | BA2 | BA1 | BA0 |

|---------------|-----|-----|-----|

| Bank 0        | 0   | 0   | 0   |

| Bank 1        | 0   | 0   | 1   |

| Bank 2        | 0   | 1   | 0   |

| Bank 3        | 0   | 1   | 1   |

| Bank 4        | 1   | 0   | 0   |

| Bank 5        | 1   | 0   | 1   |

| Bank 6        | 1   | 1   | 0   |

| Bank 7        | 1   | 1   | 1   |

Table 1–3. Bank Correspondence

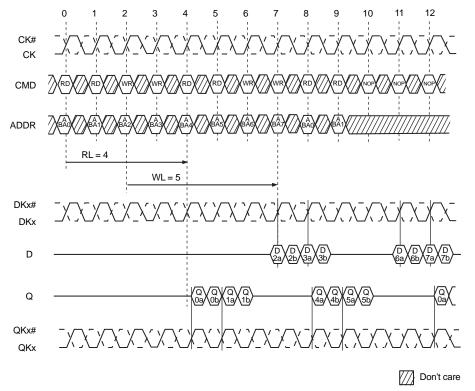

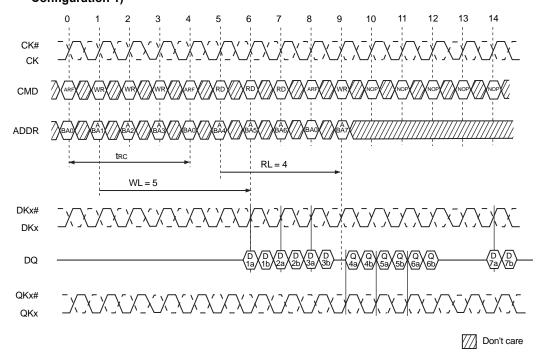

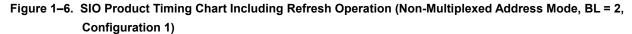

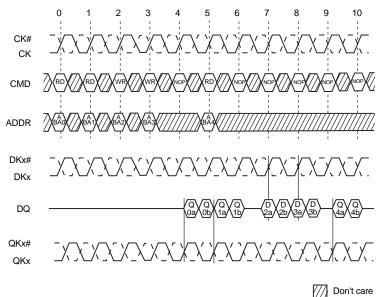

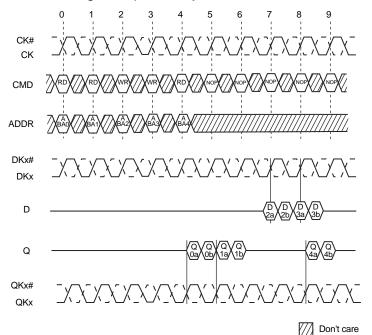

Figures 1-3, 1-4, 1-5, and 1-6 show examples of the representative timing charts of bank operations.

Figure 1–4. SIO Product Timing Chart (Non-Multiplexed Address Mode, BL = 2, Configuration 1)

Figure 1–5. CIO Product Timing Chart Including Refresh Operation (Non-Multiplexed Address Mode, BL = 2, Configuration 1)

#### 1.4 Data Transfer Rate (Band Width) Comparison

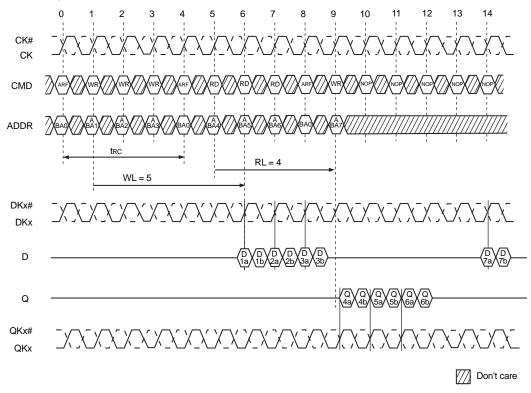

A data transfer rate (band width) represents the data transfer performance at a data port (D pin, Q pin, or DQ pin). The band width varies, depending on the product (CIO or SIO product), bit configuration ( $\times$ 9,  $\times$ 18, or  $\times$ 36), burst length (BL = 2, 4, or 8), operation frequency, and operation ratio between READ and WRITE operations. Figure 1-7 shows the relationship between the READ and WRITE command input ratio and the band width efficiency for each product and burst length. Comparisons are made assuming the same operation frequencies and bit configurations.

# **1.5 Explanation of pin functions**

This section explains the product pin functions. Table 1-4 describes pins that are common to CIO and SIO products, Table 1-5 describes pins unique to CIO products, and Table 1-6 describes pins unique to SIO products.

| Pin       | Туре   | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CK#   | Input  | Input clock<br>This is a clock signal input pin which becomes the standard for the input timing of command<br>and address signals. Command and address signals must be input in synchronization with<br>the rising edge of CK. The inputs of CK and CK# are differential clock inputs. Input CK and<br>CK#, being at a phase difference of 180 degrees against each other.                                                                                                                                                                                                                                                                                                                                                                                        |

| CS#       | Input  | Chip selection<br>This pin is used to control command input. When CS# = LOW at the rising edge of CK at a<br>CK/CK# cross point, command input becomes valid. When CS# = HIGH, command input<br>becomes invalid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| WE#       | Input  | WRITE command input<br>This pin is used to control WRITE and READ command input. When WE# = LOW, CS# =<br>LOW, and REF# = HIGH at the rising edge of CK at a CK/CK# cross point, a WRITE<br>command results. A READ command results when WE# = HIGH, CS# = LOW, and REF# =<br>HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| REF#      | Input  | Refresh command input<br>This pin is used to control refresh command input. When REF# = LOW, CS# = LOW, and<br>WE# = HIGH at the rising edge of CK at a CK/CK# cross point, an automatic refresh<br>command results.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A[xx:0]   | Input  | Address input<br>These are address signal input pins. Input write and read addresses at the rising edge of<br>CK at a CK/CK# cross point.<br>The address input pins are used to set the mode register. See <b>2.3 MRS Command</b> for<br>details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BA[2:0]   | Input  | Bank address input<br>These pins are used to select the banks which perform "READ" and "WRITE". This product<br>has eight banks. Input the addresses of the banks which will perform "WRITE" and "READ"<br>at the rising edge of CK at a CK/CK# cross point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| QKx, QKx# | Output | <ul> <li>Output data clock</li> <li>These are the output pins of the clock signals output by the IC. QKx and QKx# are clock signals for referencing output data signals and are output at the same timing as output data signals. QKx and QKx# are constantly output at a phase difference of 180 degrees against each other.</li> <li>x9 product: QK0 and QK0# are output from output data Q0 (DQ0) at the same timing as Q8 (DQ8).</li> <li>x18 product: QK0 and QK0#, and Q8 (DQ8), QK1, and QK1# are output from Q0 (DQ0) and Q9 (DQ9), respectively, at the same timing as Q17 (DQ17).</li> <li>x36 product: QK0 and QK0#, and Q17 (DQ17), QK1, and QK1# are output from Q0 (DQ0) and Q18 (DQ18), respectively, at the same timing as Q35 (DQ35).</li> </ul> |

| Table 1–4. | Pins Common to | CIO and SIO | Products | (1/3) |

|------------|----------------|-------------|----------|-------|

|------------|----------------|-------------|----------|-------|

| Pin       | Туре         | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DKx, DKx# | Input        | Input data clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           |              | These are the clock signal input pins which become the standard for the data input timing.<br>The data to be written must be input in synchronization with the cross point of DKx/DKx#.<br>The inputs of DKx and DKx# are differential clock inputs. Input DKx and DKx#, being at a<br>phase difference of 180 degrees against each other.<br>x9 and x18 products: Input data Dxx (DQxx) is captured at the same timing as DK and DK#.<br>x36 products: D0 (DQ0) to D17 (DQ17), and D18 (DQ18) to D35 (DQ35) are captured at the        |

|           |              | same timing as DK0 and DK0#, and DK1 and DK1#, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DM        | Input        | Data mask input<br>This pin is used to control the operation that writing is not executed for any data when<br>writing the data. DM is captured in synchronization with the rising edges of DKx and DKx#.<br>Data is not written if DM = HIGH is set while data is being input. Data is written while DM =<br>LOW.                                                                                                                                                                                                                      |

| QVLD      | Output       | Valid-data output period<br>This is an output signal pin that indicates the period during which valid data is output. The<br>QVLD signal is switched at the same timing as QKx and QKx#. QVLD goes to HIGH half a<br>cycle before valid data is output. QVLD goes to LOW half a cycle before output of valid<br>data is completed.                                                                                                                                                                                                      |

| ZQ        | Input/Output | Output impedance matching input<br>This pin is used to adjust the output impedance. Connect RQ, with a resistance five times<br>the output impedance value to be set, between the ZQ pin and Vss. The output impedance<br>values of the data output pins (Q, DQ), output data clocks (QKx, QKx#), and valid-data<br>output period signal (QVLD) are automatically adjusted to $0.2 \times RQ$ in the IC.<br>Minimum impedance mode is set when ZQ = Vss, and maximum impedance mode is set<br>when ZQ = VbbQ. Do not connect ZQ to Vbb. |

| TMS       | Input        | IEEE1149.1 test input<br>This pin is used to select the JTAG test mode when using the JTAG function. Input a<br>command to be input to the TAP controller. Input TMS according to the rising edge of TCK.<br>This pin may be left open when not using the JTAG function.                                                                                                                                                                                                                                                                |

| TDI       | Input        | IEEE1149.1 test input<br>This pin is used to input JTAG test data when using the JTAG function. It is used to input<br>serial data to be input to the JTAG instruction register and data register. Input TDI<br>according to the rising edge of TCK. This pin may be left open when not using the JTAG<br>function.                                                                                                                                                                                                                     |

| тск       | Input        | IEEE1149.1 clock input<br>This is the clock input pin for the JTAG test when using the JTAG function. The input<br>signals of the TMS and TDI pins are captured at the rising edge of TCK and data output to<br>the TDO pin is started at the falling edge of TCK. Be sure to connect the pin to $V_{\rm SS}$ when<br>not using the JTAG function.                                                                                                                                                                                      |

| TDO       | Output       | IEEE1149.1 test output<br>This pin is used to output JTAG test data when using the JTAG function. This pin must be<br>left open when not using the JTAG function.                                                                                                                                                                                                                                                                                                                                                                       |

# Table 1–4. Pins Common to CIO and SIO Products (2/3)

| Pin  | Туре   | Pin Function                                                                             |  |

|------|--------|------------------------------------------------------------------------------------------|--|

| VREF | Input  | Input reference voltage                                                                  |  |

|      |        | This is a voltage application pin used to reference the input.                           |  |

| VEXT | Supply | Power supply voltage                                                                     |  |

|      |        | This pin is used to apply the power supply voltage to the product.                       |  |

| Vdd  | Supply | Power supply voltage                                                                     |  |

|      |        | This pin is used to apply the power supply voltage to the product.                       |  |

| VddQ | Supply | Power supply voltage                                                                     |  |

|      |        | This pin is used to apply the power supply voltage to I/O buffers.                       |  |

| Vss  | Supply | Ground                                                                                   |  |

|      |        | This pin is used to ground Vss.                                                          |  |

| VssQ | Supply | DQ ground                                                                                |  |

|      |        | This is an I/O buffer ground pin.                                                        |  |

| Vtt  | Supply | Power supply voltage                                                                     |  |

|      |        | This is a power supply voltage application pin that applies the terminal potential.      |  |

| DNU  |        | Unused pin                                                                               |  |

|      |        | This is an I/O pin that is not to be used. Connect it to Vss.                            |  |

| NF   |        | No function                                                                              |  |

|      |        | This is an input pin that is not to be used. Connect it to $V_{\mbox{\scriptsize SS}}$ . |  |

# Table 1–4. Pins Common to CIO and SIO Products (3/3)

| Pin      | Туре         | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DQ[xx:0] | Input/Output | Data I/O<br>These pins are alternatively used for data input and output.<br>READ operation: Output the data to be read to the DQxx to DQ0 pins. Input a READ<br>command and output the first data at the rising edge of QKx after the set RL (READ<br>latency). Data is output for as much as the burst length at successive rising edges of QKx<br>and QKx#.<br>WRITE operation: Input the data to be written to the DQxx to DQ0 pins. Input a WRITE<br>command and input the data at the rising edge of DKx after the set WL (WRITE latency).<br>Data is captured for as much as the burst length at successive rising edges of DKx and<br>DKx#. |  |  |

# Table 1–5. Pins Unique to CIO Products

# Table 1–6. Pins Unique to SIO Products

| Pin     | Туре   | Pin Function                                                                                                                                                                                                                                                                                                            |

|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[17:0] | Input  | Data input<br>These are data input pins. Input the data to be written to the D17 to D0 pins.<br>Input a WRITE command and input the data at the rising edge of DK after the set WL<br>(WRITE latency). Data is captured for as much as the burst length at successive rising<br>edges of DK and DK#.                    |

| Q[17:0] | Output | Data output<br>These are data output pins. Output the data to be read to the Q17 to Q0 pins.<br>Input a READ command and output the first data at the rising edge of QK0/QK1 after the<br>set RL (READ latency). Data is output for as much as the burst length at successive rising<br>edges of QK0/QK1 and QK0#/QK1#. |

## 1.6 Output Data and Output Data Clock

Low latency DRAM output data signals are Q and DQ, valid-data output period signal QVLD, and output data clocks QKx and QKx#. Q, DQ, and QVLD are output at the same timing as the rising edge of QKx or QK#.

#### 1.6.1 READ latency (tRL)

A READ latency ( $t_{RL}$ ) is the period from when a READ command is input until data is output and is specified by the number of clock cycles. With low latency DRAM, the  $t_{RL}$  to be used can be set by setting the configuration when setting the mode register. The  $t_{RL}$  that can be set, however, varies according to the operation frequency and the address multiplex function setting. Table 1-7 shows the  $t_{RL}$  configuration in non-multiplexed address mode and Table 1-8 shows the  $t_{RL}$  configuration in multiplexed address mode. See **2.3 MRS Command** for how to set the configuration.

|                     | D      | Configuration |    | l la it |        |

|---------------------|--------|---------------|----|---------|--------|

| Operation Frequency | BL     | 1             | 2  | 3       | Unit   |

| 400 MHz             | BL = 2 |               |    |         | cycles |

|                     | BL = 4 | NA            | NA | 8       |        |

|                     | BL = 8 |               |    |         |        |

| 300 MHz             | BL = 2 |               |    |         |        |

|                     | BL = 4 | NA            | 6  | 8       |        |

|                     | BL = 8 |               |    |         |        |

| 200 MHz             | BL = 2 |               |    |         |        |

|                     | BL = 4 | 4             | 6  | 8       |        |

|                     | BL = 8 | NA            |    |         |        |

Table 1–7. trL Configuration in Non-Multiplexed Address Mode (Common to CIO and SIO Products)

**Remark** NA (Not Available) : No setting is available.

#### Table 1–8. tRL Configuration in Multiplexed Address Mode (Common to CIO and SIO Products)

|                     | D      |    |    | Configuration |        |  |

|---------------------|--------|----|----|---------------|--------|--|

| Operation Frequency | BL     | 1  | 2  | 3             | Unit   |  |

| 400 MHz             | BL = 2 |    |    |               | cycles |  |

|                     | BL = 4 | NA | NA | 9             |        |  |

|                     | BL = 8 |    |    |               |        |  |

| 300 MHz             | BL = 2 |    |    |               |        |  |

|                     | BL = 4 | NA | 7  | 9             |        |  |

|                     | BL = 8 |    |    |               |        |  |

| 200 MHz             | BL = 2 | _  |    |               |        |  |

|                     | BL = 4 | 5  | 7  | 9             |        |  |

|                     | BL = 8 | NA |    |               |        |  |

Remark NA (Not Available) : No setting is available.

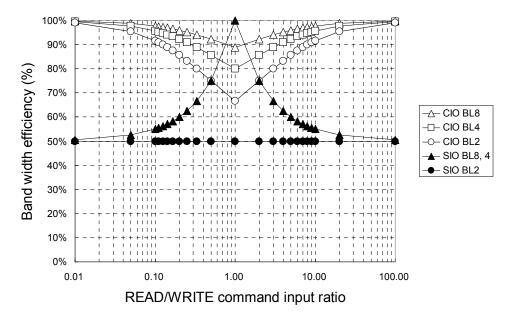

#### 1.6.2 Output data and output data clock timing

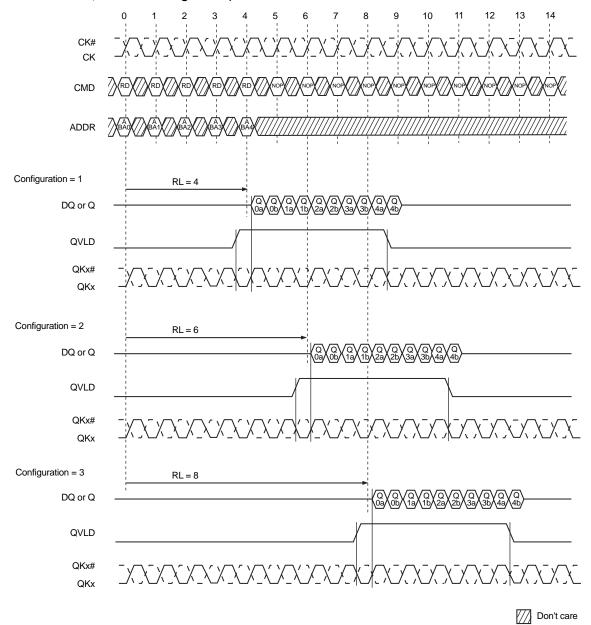

Figures 1-8 and 1-9 show representative timing charts of Q, DQ, QVLD, QKx, and QKx# output by low latency DRAM.

Figure 1–8. READ Timing Chart (Non-Multiplexed Address Mode, BL = 2, Configurations 1, 2, 3)

Don't care

## 1.7 HSTL interface and VREF

Low latency DRAM uses an HSTL (high-speed transceiver logic) interface as the I/O interface. An HSTL interface distinguishes between HIGH and LOW, based on the differential potential for the reference voltage (VREF). A VREF power supply must therefore be supplied to the HSTL interface and, normally, the HSTL interface should be used around  $V_{REF} = V_{DD}Q/2$ .

When the VREF voltage fluctuates during an operation, the input level of an input signal cannot be identified correctly, and malfunctioning may result; therefore, supply a stable voltage to VREF.

# **CHAPTER 2 COMMANDS**

#### 2.1 Command Operation

Low latency DRAM is provided with five commands, which are determined by the input of CS#, WE#, REF#, Ax, or BAx.

Table 2-1 shows the types and descriptions of the commands. Table 2-2 shows the input level of each pin when a command is determined. Input each signal in synchronization with the rising edge of CK at a CK/CK# cross point. Table 2-3 shows the differences in the number of addresses used according to the burst length and bit configuration

| Code        | Command Name                       | Command Description                                                                      |

|-------------|------------------------------------|------------------------------------------------------------------------------------------|

| DESEL / NOP | No operation command (NOP command) | This command sets a device to no-operation and to a non-selected state.                  |

| MRS         | Mode register set command          | This command sets the value of the mode register, which determines the product function. |

| READ        | READ command                       | This command is used to read data.                                                       |

| WRITE       | WRITE command                      | This command is used to write data.                                                      |

| AREF        | Automatic refresh command          | This command is used to perform a refresh operation to retain memory cell data.          |

Table 2–1. Command Types and Descriptions

| Table 2–2. D | etermined | Commands |

|--------------|-----------|----------|

|--------------|-----------|----------|

| Code        | CS# | WE# | REF# | Ax                      | BAx                 | Note |

|-------------|-----|-----|------|-------------------------|---------------------|------|

| DESEL / NOP | Н   | Х   | Х    | Х                       | Х                   |      |

| MRS         | L   | L   | L    | OPCODE <sup>Note1</sup> | Х                   | 3    |

| READ        | L   | Н   | Н    | А                       | BA                  | 4    |

| WRITE       | L   | L   | Н    | А                       | BA                  | 4    |

| AREF        | L   | Н   | L    | Х                       | BA <sup>Note2</sup> |      |

Notes 1. The address (A) input during MRS setting is used to select the MRS setting contents.

2. The bank address (BA) input during AREF is used to set the bank that performs a refresh operation.

3. Only address pins A0 to A17 are used for MRS.

4. See Table 2-3 for the number of addresses used.

Table 2–3. Number of Addresses Used

| Durationation |         | SIO Product |         |         |

|---------------|---------|-------------|---------|---------|

| Burst Length  | x36     | x18         | x9      | x18     |

| BL = 2        | A[18:0] | A[19:0]     | A[20:0] | A[19:0] |

| BL = 4        | A[17:0] | A[18:0]     | A[19:0] | A[18:0] |

| BL = 8        | NA      | A[17:0]     | A[18:0] | A[17:0] |

## 2.2 DESEL/NOP Command

The internal state of a device will be set to non-selectable by inputting a no operation command at the rise timing of CK. Unnecessary commands can be prevented from being input to the device internal state during an idle period by using this command.

## 2.3 MRS Command

This command is used to set the value of the mode register, which determines the product function of a device. The following six functions can be set by selecting the register value.

- Configuration

- Burst length

- Address multiplex function

- PLL function

- Output impedance mode function

- ODT function

#### 2.3.1 How to set MRS command

How to the set the MRS command differs depending on whether the address multiplex function is in non-multiplexed address mode or multiplexed address mode.

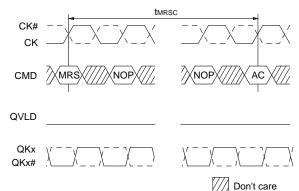

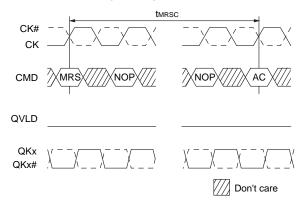

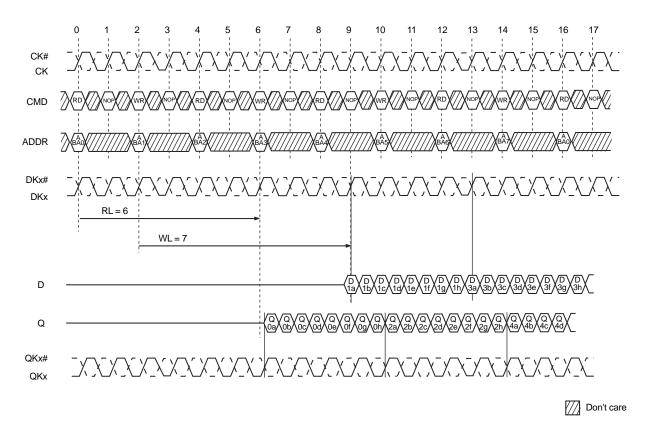

#### (1) How to set MRS command in non-multiplexed address mode

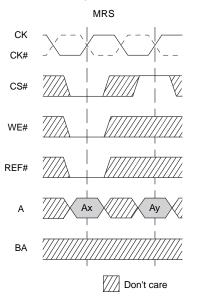

Input CS# = LOW, WE# = LOW, and REF# = LOW at the rising edge of CK at a CK/CK# cross point. At the same time, input the expected value, which set the function to be used, to address pins A0 to A17. The period from inputting the MRS command until the function settings are completed is specified by  $t_{MRSC}$ . Figure 2-1 shows the MRS command input timing chart, Figure 2-2 shows the pin input states during MRS command input, and Table 2-4 shows the address pin allocation.

Figure 2–2. Pin Input States During MRS Command Input (Non-Multiplexed Address Mode)

Table 2–4. Address Pin Allocation with Respect to Function Setting (Non-Multiplexed Address Mode)

| Address Pin | MRS Allocation                         | Remark           |

|-------------|----------------------------------------|------------------|

| A0, A1, A2  | Configuration setting                  |                  |

| A3, A4      | Burst length setting                   |                  |

| A5          | Address multiplex function setting     |                  |

| A6          | Unused                                 |                  |

| A7          | PLL function setting                   |                  |

| A8          | Output impedance mode function setting |                  |

| A9          | ODT function setting                   |                  |

| A [xx:10 ]  | For future function expansion          | All fixed to LOW |

#### (2) How to set MRS in multiplexed address mode

Input CS# = LOW, WE# = LOW, and REF# = LOW at the rising edge of CK at a CK/CK# cross point. Input the expected value, which set the function to be used, to address pins A0, A3 to A5, A8 to A10, A13, A14, A17, and A18, in two separate cycles. The period from inputting the MRS command until the function settings are completed is specified by  $t_{MRSC}$ . Figure 2-3 shows the MRS command input timing chart, Figure 2-4 shows the pin input states during MRS command input, and Table 2-5 shows the address pin allocation.

Figure 2–3. MRS Setting Timing Chart (Multiplexed Address Mode)

Figure 2–4. How to Input to Pins During MRS Command Input (Multiplexed Address Mode)

Table 2–5. Address Pin Allocation of MRS Setting (Multiplexed Address Mode)

| Addre  | ess Pin |                                        |                  |

|--------|---------|----------------------------------------|------------------|

| Ax     | Ay      | MRS Allocation                         | Remark           |

| A0     | A3, A4  | Configuration setting                  |                  |

| A3, A4 | -       | Burst length setting                   |                  |

| A5     | -       | Address multiplex function setting     |                  |

| -      | A8      | Unused                                 |                  |

| -      | A9      | PLL function setting                   |                  |

| A8     | -       | Output impedance mode function setting |                  |

| A9     | -       | ODT function setting                   |                  |

| A[x:   | x:10]   | For future function expansion          | All fixed to LOW |

#### 2.3.2 Configuration setting

Low latency DRAM has three predetermined combinations (configurations) of random cycle time t<sub>RC</sub>, READ latency t<sub>RL</sub>, and WRITE latency t<sub>WL</sub>. t<sub>RC</sub>, t<sub>RL</sub>, and t<sub>WL</sub> vary between non-multiplexed address mode and multiplexed address mode. The configuration settings in non-multiplexed address mode and multiplexed address mode are described below.

#### (1) Configuration settings in non-multiplexed address mode

The configuration is set according to the expected values of address pins A0, A1, and A2. Input to the address pins is performed according to the MRS command input timing. Table 2-6 shows the configuration setting contents and Table 2-7 shows the address pin expected values related to the configuration settings.

| <b>F</b>  | Symbol          |                   | 1.114 |      |        |

|-----------|-----------------|-------------------|-------|------|--------|

| Frequency |                 | 1 <sup>Note</sup> | 2     | 3    | Unit   |

|           | trc             | 4                 | 6     | 8    | cycles |

|           | t <sub>RL</sub> | 4                 | 6     | 8    |        |

|           | tw∟             | 5                 | 7     | 9    |        |

| 400 MHz   | <b>t</b> RC     | NA                | NA    | 20.0 | ns     |

|           | t <sub>RL</sub> | NA                | NA    | 20.0 |        |

|           | tw∟             | NA                | NA    | 22.5 |        |

| 300 MHz   | trc             | NA                | 20.0  | 26.7 |        |

|           | t <sub>RL</sub> | NA                | 20.0  | 26.7 |        |

|           | tw∟             | NA                | 23.3  | 30.0 |        |

| 200 MHz   | trc             | 20.0              | 30.0  | 40.0 |        |

|           | t <sub>RL</sub> | 20.0              | 30.0  | 40.0 |        |

|           | tw∟             | 25.0              | 35.0  | 45.0 |        |

Table 2–6. Configuration Setting Contents (Non-Multiplexed Address Mode)

**Note** Configuration 1 cannot be set when BL = 8.

Remark NA (Not Available) : No setting is available.

Table 2–7. Configuration Settings (Non-Multiplexed Address Mode)

| A2 | A1 | A0 | Configuration               |

|----|----|----|-----------------------------|

| 0  | 0  | 0  | 1 <sup>Note</sup> (default) |

| 0  | 0  | 1  | 1 <sup>Note</sup>           |

| 0  | 1  | 0  | 2                           |

| 0  | 1  | 1  | 3                           |

| 1  | 0  | 0  | For future expansion        |

| 1  | 0  | 1  | For future expansion        |

| 1  | 1  | 0  | For future expansion        |

| 1  | 1  | 1  | For future expansion        |

**Note** Configuration 1 cannot be set when BL = 8.

#### (2) Configuration settings in multiplexed address mode setting

The configuration is set according to the expected values of address pins A0, A3, and A4. Input to the address pins is performed separately in two successive cycles following the MRS command input timing. Table 2-8 shows the configuration setting contents and Table 2-9 shows the address pin expected values related to the configuration settings.

| <b>F</b>  | Or mark at      |                   | Configuratior | 1    | 11     |

|-----------|-----------------|-------------------|---------------|------|--------|

| Frequency | Symbol          | 1 <sup>Note</sup> | 2             | 3    | Unit   |

|           | <b>t</b> RC     | 4                 | 6             | 8    | cycles |

|           | <b>t</b> RL     | 5                 | 7             | 9    |        |

|           | tw∟             | 6                 | 8             | 10   |        |

| 400 MHz   | <b>t</b> RC     | NA                | NA            | 20.0 | ns     |

|           | <b>t</b> RL     | NA                | NA            | 22.5 |        |

|           | tw∟             | NA                | NA            | 25.0 |        |

| 300 MHz   | <b>t</b> RC     | NA                | 20.0          | 26.7 |        |

|           | <b>t</b> RL     | NA                | 23.3          | 30.0 |        |

|           | tw∟             | NA                | 26.7          | 33.3 |        |

| 200 MHz   | <b>t</b> RC     | 20.0              | 30.0          | 40.0 |        |

|           | t <sub>RL</sub> | 25.0              | 35.0          | 45.0 |        |

|           | tw∟             | 30.0              | 40.0          | 50.0 |        |

Table 2–8. Configuration Setting Contents (Multiplexed Address Mode)

**Note** Configuration 1 cannot be set when BL = 8.

Remark NA (Not Available) : No setting is available.

| A4y | A3y | A0x | Configuration               |

|-----|-----|-----|-----------------------------|

| 0   | 0   | 0   | 1 <sup>Note</sup> (default) |

| 0   | 0   | 1   | 1 Note                      |

| 0   | 1   | 0   | 2                           |

| 0   | 1   | 1   | 3                           |

| 1   | 0   | 0   | For future expansion        |

| 1   | 0   | 1   | For future expansion        |

| 1   | 1   | 0   | For future expansion        |

| 1   | 1   | 1   | For future expansion        |

Table 2–9. Configuration Settings (Multiplexed Address Mode)

**Note** Configuration 1 cannot be set when BL = 8.

#### 2.3.3 Burst length (BL) setting

The burst length of low latency DRAM can be set to BL = 2, 4, or 8. BL = 8, however, cannot be set for CIO x36 products. The BL settings for non-multiplexed address mode and multiplexed address mode differ and are therefore separately described below.

#### (1) BL setting in non-multiplexed address mode

The burst length is set according to the expected values of address pins A3 and A4. Table 2-10 shows the address pin inputs of the BL settings. Input to A3 and A4 when inputting the MRS command.

| A4 | A3 | BL                |

|----|----|-------------------|

| 0  | 0  | 2 (default)       |

| 0  | 1  | 4                 |

| 1  | 0  | 8 <sup>Note</sup> |

| 1  | 1  | Invalid           |

Table 2–10. BL Settings (Non-Multiplexed Address Mode)

Note BL = 8 cannot be set for CIO x36 products.

#### (2) BL setting in multiplexed address mode

The burst length is set according to the expected values of address pins A3 and A4. Table 2-11 shows the address pin inputs of the BL settings. Input to A3x and A4x when inputting the MRS command.

| A4x | A3x | BL                |

|-----|-----|-------------------|

| 0   | 0   | 2 (default)       |

| 0   | 1   | 4                 |

| 1   | 0   | 8 <sup>Note</sup> |

| 1   | 1   | Invalid           |

#### Table 2–11. BL Settings (Multiplexed Address Mode)

**Note** BL = 8 cannot be set for CIO x36 products.

#### 2.3.4 Non-multiplexed address mode and multiplexed address mode settings

With low latency DRAM, non-multiplexed address mode, in which all address inputs are captured in one cycle in a batch, or multiplexed address mode, in which address inputs as X-address inputs and Y-address inputs are captured in two separate cycles, can be set.

#### (1) Address multiplex function setting in non-multiplexed address mode

Non-multiplexed address mode or multiplexed address mode is set according to the expected value of address pin A5. Table 2-12 shows the address pin input in non-multiplexed address mode. Input to A5 when inputting the MRS command.

#### Table 2–12. Address Multiplex Function Setting (Non-Multiplexed Address Mode)

| A5 | Address Multiplex Function             |  |

|----|----------------------------------------|--|