**Preliminary User's Manual**

# **ERTEC 200**

## Enhanced Real-Time Ethernet Controller 32-Bit RISC CPU Core

Hardware

µPD800261F1-523-HN2

Document No. A17988EE1V1UM00 Date Published August 2007

© NEC Electronics Corporation 2007 Printed in Germany

#### NOTES FOR CMOS DEVICES —

#### (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN).

#### (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to V<sub>DD</sub> or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### **③ PRECAUTION AGAINST ESD**

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### **④** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

#### (5) INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

All other product, brand, or trade names used in this publication are the trademarks or registered trademarks of their respective trademark owners.

Product specifications are subject to change without notice. To ensure that you have the latest product data, please contact your local NEC Electronics sales office.

- The information in this document is current as of August, 2007. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property

rights of third parties by or arising from the use of NEC Electronics products listed in this document or any

other liability arising from the use of such products. No license, express, implied or otherwise, is granted under

any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.11-1

For further information, please contact:

NEC Electronics Corporation

1753, Shimonumabe, Nakahara-ku, Kawasaki, Kanagawa 211-8668, Japan Tel: 044-435-5111 http://www.necel.com/

#### [America]

NEC Electronics America, Inc.

2880 Scott Blvd. Santa Clara, CA 95050-2554, U.S.A. Tel: 408-588-6000 800-366-9782 http://www.am.necel.com/

#### [Europe]

#### NEC Electronics (Europe) GmbH

Arcadiastrasse 10 40472 Düsseldorf, Germany Tel: 0211-65030 http://www.eu.necel.com/

#### Hanover Office

Podbielskistrasse 166 B 30177 Hannover Tel: 0 511 33 40 2-0

Munich Office Werner-Eckert-Strasse 9 81829 München Tel: 0 89 92 10 03-0

Stuttgart Office Industriestrasse 3 70565 Stuttgart Tel: 0 711 99 01 0-0

United Kingdom Branch Cygnus House, Sunrise Parkway Linford Wood, Milton Keynes MK14 6NP, U.K. Tel: 01908-691-133

Succursale Française 9, rue Paul Dautier, B.P.52 78142 Velizy-Villacoublay Cédex France Tel: 01-3067-5800

Sucursal en España Juan Esplandiu, 15 28007 Madrid, Spain Tel: 091-504-2787

**Tyskland Filial** Täby Centrum Entrance S (7th floor)

18322 Täby, Sweden Tel: 08 638 72 00 **Filiale Italiana** Via Fabio Filzi, 25/A

Via Fabio Fiizi, 25/A 20124 Milano, Italy Tel: 02-667541

#### Branch The Netherlands

Steijgerweg 6 5616 HS Eindhoven The Netherlands Tel: 040 265 40 10

#### [Asia & Oceania]

NEC Electronics (China) Co., Ltd 7th Floor, Quantum Plaza, No. 27 ZhiChunLu Haidian District, Beijing 100083, P.R.China Tel: 010-8235-1155 http://www.cn.necel.com/

Shanghai Branch

Room 2509-2510, Bank of China Tower, 200 Yincheng Road Central, Pudong New Area, Shanghai, P.R.China P.C:200120 Tel:021-5888-5400 http://www.cn.necel.com/

#### Shenzhen Branch

Unit 01, 39/F, Excellence Times Square Building, No. 4068 Yi Tian Road, Futian District, Shenzhen, P.R.China P.C:518048 Tel:0755-8282-9800 http://www.cn.necel.com/

#### NEC Electronics Hong Kong Ltd.

Unit 1601-1613, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: 2886-9318 http://www.hk.necel.com/

#### NEC Electronics Taiwan Ltd.

7F, No. 363 Fu Shing North Road Taipei, Taiwan, R. O. C. Tel: 02-8175-9600 http://www.tw.necel.com/

#### NEC Electronics Singapore Pte. Ltd.

238A Thomson Road, #12-08 Novena Square, Singapore 307684 Tel: 6253-8311 http://www.sg.necel.com/

#### NEC Electronics Korea Ltd.

11F., Samik Lavied'or Bldg., 720-2, Yeoksam-Dong, Kangnam-Ku, Seoul, 135-080, Korea Tel: 02-558-3737 http://www.kr.necel.com/

G0705

## Preface

| Readers      | This manual is intended ERTEC 200. | for users who want to understand the functions of the                                                                                                             |

|--------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose      | This manual presents th            | e hardware manual of ERTEC 200.                                                                                                                                   |

| Organization | This user's manual desc            | ribes the following sections:                                                                                                                                     |

|              | Pin function                       |                                                                                                                                                                   |

|              | CPU function                       |                                                                                                                                                                   |

|              | Internal peripheral fu             | unction                                                                                                                                                           |

|              | Test function                      |                                                                                                                                                                   |

| Legend       | Symbols and notation a             | re used as follows:                                                                                                                                               |

|              | Weight in data notation            | : Left is high-order column, right is low order column                                                                                                            |

|              | Active low notation                | N (capital letter N before or after signal name)                                                                                                                  |

|              | Memory map address:                | : High order at high stage and low order at low stage                                                                                                             |

|              | Note                               | : Explanation of (Note) in the text                                                                                                                               |

|              | Caution                            | : Item deserving extra attention                                                                                                                                  |

|              | Remark                             | : Supplementary explanation to the text                                                                                                                           |

|              | Numeric notation                   | : Binary xxx <sub>b</sub><br>Decimal xxxx<br>Hexadecimal xxxxH or 0x xxxx                                                                                         |

|              | Prefixes representing po           | wers of 2 (address space, memory capacity)<br>k (kilo): $2^{10} = 1024$<br>M (mega): $2^{20} = 1024^2 = 1.048.576$<br>G (giga): $2^{30} = 1024^3 = 1.073.741.824$ |

|              | Data Type:                         | Word 32 bits<br>Halfword 16 bits<br>Byte 8 bits                                                                                                                   |

#### **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

| Document Name                                                                          | Document No.             |

|----------------------------------------------------------------------------------------|--------------------------|

| ERTEC 200 Preliminary Data Sheet                                                       | A17989EE1V1DS00          |

| ERTEC 200 Preliminary User's Manual - Boot Mode Description                            | TPS-HE-A-1066            |

| CB-12 Family L/M Type Block Library                                                    | A15353EJ4V0BL00          |

| CB-12 Family L/M Type Product Data                                                     | A14937EJ3V0DM00          |

| ARM946E-S Technical Reference Manual                                                   | DDI0201C <sup>Note</sup> |

| ARM9E-S (Rev. 1) Technical Reference Manual                                            | DDI0165B <sup>Note</sup> |

| ARM AMBA Specification Rev. 2.0                                                        | IHI0011A <sup>Note</sup> |

| ARM PrimeCell <sup>TM</sup> UART (PL010) Technical Reference Manual                    | DDI0139B <sup>Note</sup> |

| ARM PrimeCell <sup>TM</sup> Synchronous Serial Port (PL021) Technical Reference Manual | DDI0171B <sup>Note</sup> |

| ARM Embedded Trace Macrocell Architecture Specification                                | IHI0014J <sup>Note</sup> |

| ARM Multi ICE System Design Considerations Application Note 72                         | DAI0072A <sup>Note</sup> |

Note: These documents are available from ARM Limited (www.arm.com).

## **Table of Contents**

| Chapter 1  | Introduction                                                  |    |

|------------|---------------------------------------------------------------|----|

| 1.1        | General                                                       |    |

| 1.2        | Device Features                                               |    |

| 1.3        | Ordering Information                                          |    |

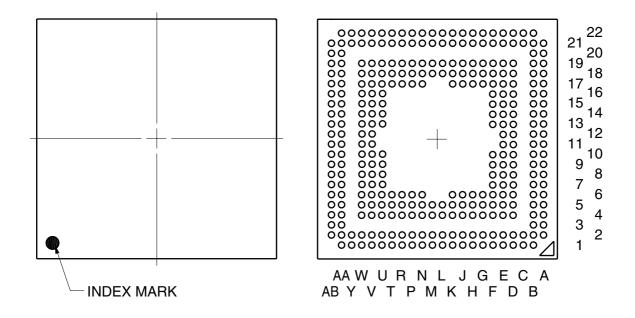

| 1.4        | Pin Configuration                                             |    |

| 1.5        | Pin Identification                                            |    |

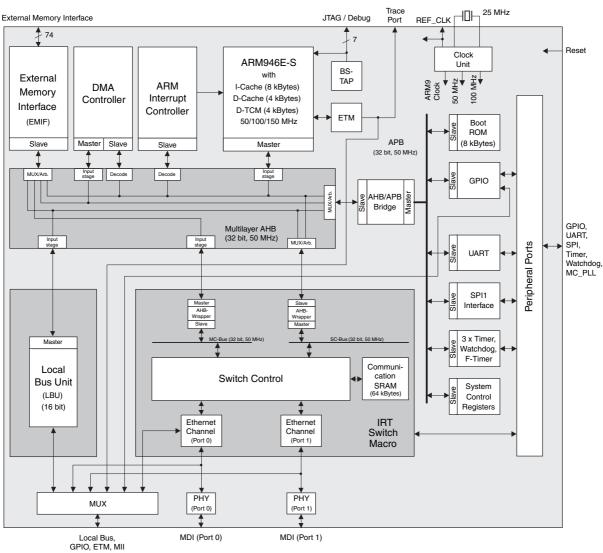

| 1.6        | Configuration of Functional Blocks                            |    |

|            | .6.1 Block Diagram of ERTEC 200                               |    |

| 1          | .6.2 On-chip Units                                            | 30 |

| •          |                                                               |    |

| 2.         | Pin Functions                                                 |    |

| 2.1        | List of Pin Functions                                         |    |

| 2.2        | Pin Characteristics                                           |    |

| 2.3        | Pin Status and Drive Characteristics                          | 45 |

| Chapter 3  | CPU Function                                                  | 10 |

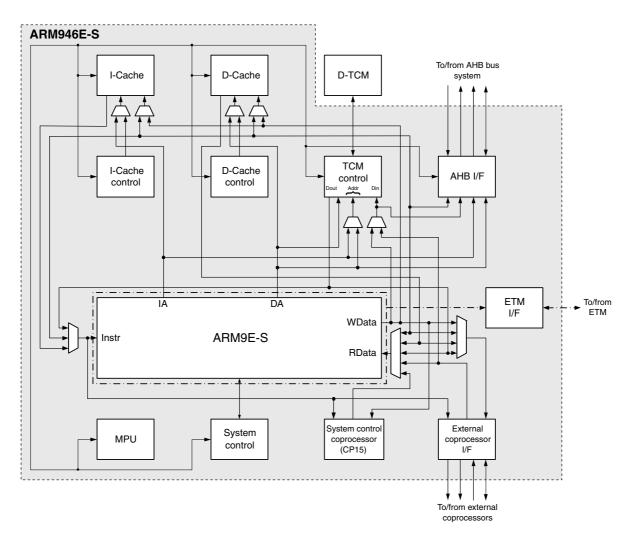

| 3.1        | Structure of The ARM946E-S Processor System                   |    |

| 3.1        | Cache Structure of ARM946E-S                                  |    |

| 3.2<br>3.3 | Tightly Coupled Memories                                      |    |

| 3.3<br>3.4 | Memory Protection Unit (MPU)                                  |    |

| 3.4<br>3.5 | Bus Interface of ARM946E-S.                                   |    |

|            |                                                               |    |

| 3.6<br>3.7 | ARM946E-S Embedded Trace Macrocell (ETM9) ARM946E-S Registers |    |

| 3.7        |                                                               | 55 |

| Chapter 4  | ERTEC 200 Bus System                                          | 55 |

| 4.1        | Multilayer AHB Bus                                            |    |

| 4.2        | APB I/O Bus                                                   |    |

| 7.2        |                                                               | 50 |

| Chapter 5  | ERTEC 200 Memory Map                                          | 57 |

| 5.1        | Memory Partitioning of ERTEC 200                              |    |

| 5.2        | Detailed Memory Map Description                               | 58 |

| 5.3        | Memory Map Example                                            | 60 |

| _          |                                                               |    |

| Chapter 6  | External Memory Interface (EMIF)                              |    |

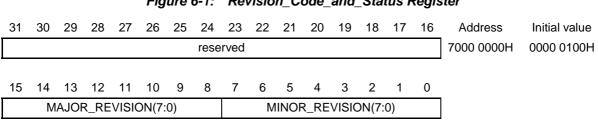

| 6.1        | Address Assignment of EMIF Registers                          |    |

| 6.2        | Detailed EMIF Register Description                            |    |

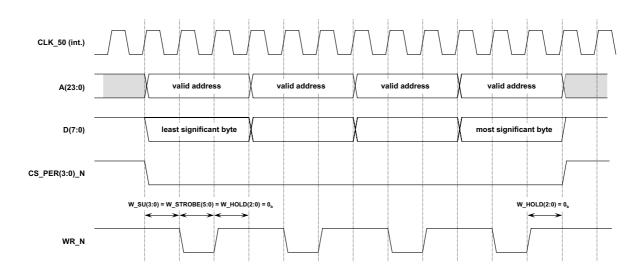

| 6.3        | Asynchronous Access Timing Examples                           |    |

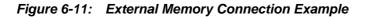

| 6.4        | External Memory Connection Example                            |    |

| 6.5        | Hints for Setting the EMIF Registers                          | 77 |

| 01         |                                                               | 70 |

| Chapter 7  | DMA Controller                                                |    |

| 7.1        | Address Assignment of DMA Controller Registers                |    |

| 7.2        | Detailed DMA Controller Register Description                  | 81 |

| Chapter 8  | Interrupt Controller                                          | 87 |

| 8.1        | Prioritization of Interrupts                                  |    |

| 8.2        | Trigger Modes                                                 |    |

| 8.3        | Masking the Interrupt Inputs                                  |    |

| 8.4        | Software Interrupts for IRQ                                   |    |

| 8.5        | Nested Interrupt Structure                                    |    |

| 8.6        | EOI End-Of-Interrupt                                          |    |

| 8.0<br>8.7 | IRQ Interrupts as FIQ Interrupt Sources                       |    |

| 8.8        | Interrupt Control Register Summary                            |    |

| 8.9        | Detailed ICU Register Description                             |    |

| 0.5        |                                                               | 50 |

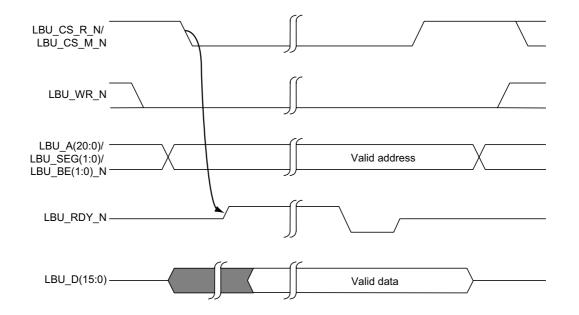

| Chapter 9                                                                                                                                                                                         | Local Bus Unit (LBU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 109                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.1                                                                                                                                                                                               | Page Size Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 111                                                                                                                                                                  |

| 9.2                                                                                                                                                                                               | Page Offset Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 112                                                                                                                                                                  |

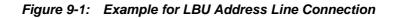

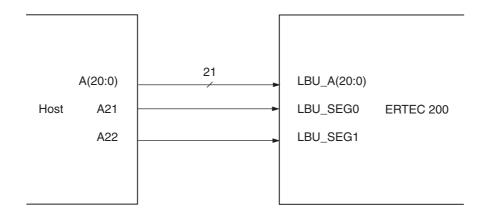

| 9.3                                                                                                                                                                                               | Local Bus Unit Address Mapping Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 113                                                                                                                                                                  |

| 9.4                                                                                                                                                                                               | Page Control Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

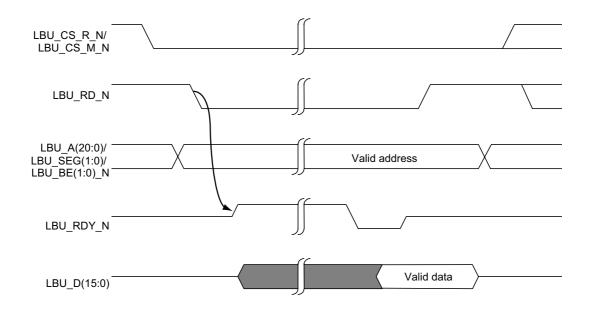

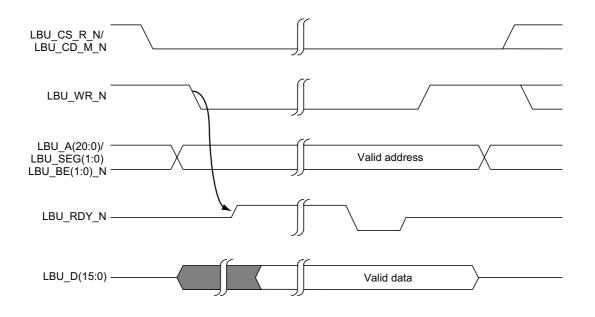

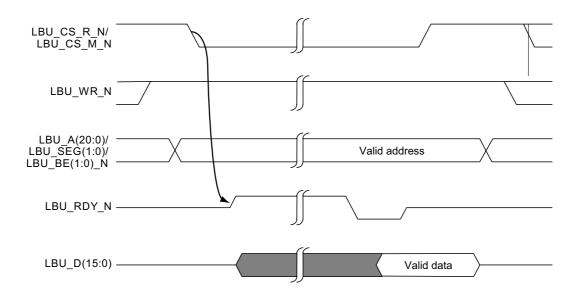

| 9.5                                                                                                                                                                                               | Host Accesses to ERTEC 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 116                                                                                                                                                                  |

| 9.6                                                                                                                                                                                               | Host Interrupt Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                      |

| 9.7                                                                                                                                                                                               | Address Assignment of LBU Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 119                                                                                                                                                                  |

| 9.8                                                                                                                                                                                               | Detailed LBU Register Description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 120                                                                                                                                                                  |

|                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

| Chapter 10                                                                                                                                                                                        | 0 Boot ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                      |

| 10.1                                                                                                                                                                                              | Booting from External ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

| 10.2                                                                                                                                                                                              | Booting via SPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

| 10.3                                                                                                                                                                                              | Booting via UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

| 10.4                                                                                                                                                                                              | Booting via LBU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

| 10.5                                                                                                                                                                                              | Memory Swapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 124                                                                                                                                                                  |

|                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

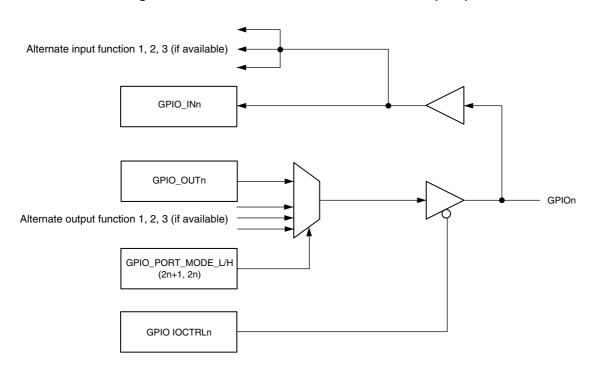

| Chapter 11                                                                                                                                                                                        | 1 General Purpose I/O (GPIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

| 11.1                                                                                                                                                                                              | Address Assignment of GPIO Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

| 11.2                                                                                                                                                                                              | Detailed GPIO Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 128                                                                                                                                                                  |

|                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

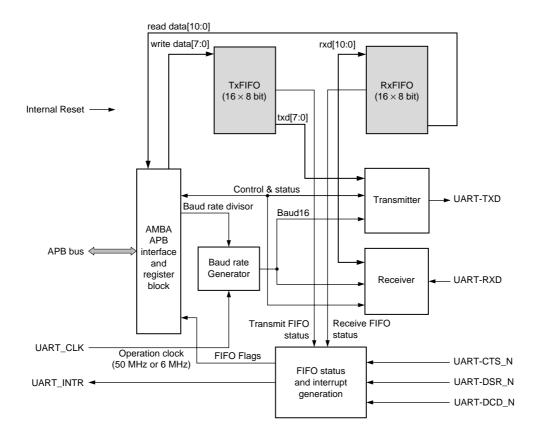

| Chapter 12                                                                                                                                                                                        | 2 Asynchronous Serial Interface UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

| 12.1                                                                                                                                                                                              | Address Assignment of UART Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

| 12.2                                                                                                                                                                                              | Detailed UART Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                      |

| 12.3                                                                                                                                                                                              | GPIO Register Initialization for UART Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 150                                                                                                                                                                  |

|                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

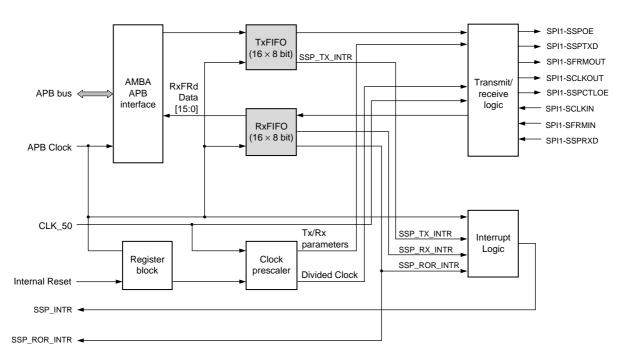

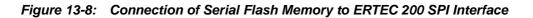

| -                                                                                                                                                                                                 | 3 Synchronous Serial Interface SPI1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |

| 13.1                                                                                                                                                                                              | Address Assignment of SPI1 Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

| 40.0                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

| 13.2                                                                                                                                                                                              | Detailed SPI1 Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                      |

| 13.2<br>13.3                                                                                                                                                                                      | Detailed SPI1 Register Description           [GPIO Register Initialization for SPI1 Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

| 13.3                                                                                                                                                                                              | [GPIO Register Initialization for SPI1 Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 160                                                                                                                                                                  |

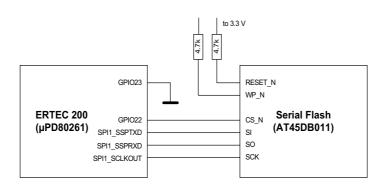

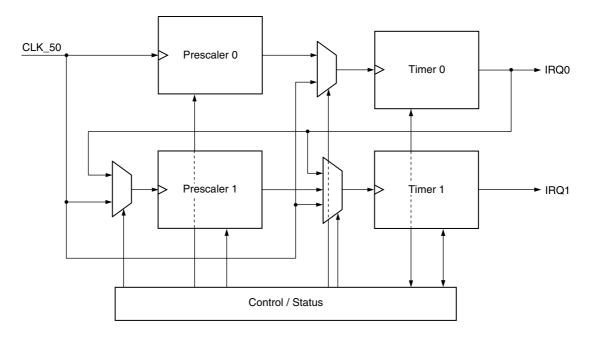

| 13.3<br>Chapter 14                                                                                                                                                                                | [GPIO Register Initialization for SPI1 Usage         4 ERTEC 200 Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 160<br>161                                                                                                                                                           |

| 13.3<br>Chapter 14<br>14.1                                                                                                                                                                        | [GPIO Register Initialization for SPI1 Usage         4 ERTEC 200 Timers         Timer 0 and Timer 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 160<br>161<br>161                                                                                                                                                    |

| 13.3<br>Chapter 14<br>14.1                                                                                                                                                                        | [GPIO Register Initialization for SPI1 Usage         4 ERTEC 200 Timers         Timer 0 and Timer 1         14.1.1       Operation mode of Timer 0 and Timer 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>160</b><br><b>161</b><br><b>161</b><br>162                                                                                                                        |

| 13.3<br>Chapter 14<br>14.1<br>1<br>1                                                                                                                                                              | [GPIO Register Initialization for SPI1 Usage         4 ERTEC 200 Timers         Timer 0 and Timer 1         14.1.1       Operation mode of Timer 0 and Timer 1         14.1.2       Timer interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 160<br>161<br>161<br>162<br>162                                                                                                                                      |