# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**Preliminary Design Manual**

# **CB-9 Family VX/VM Type**

# 0.35 $\mu$ m CMOS Cell-Based IC (CBIC)

NB85E, NB85ET

Document No. A14335EJ3V1DM00 (3rd edition) Date Published January 2002 NS CP(N)

© NEC Corporation 1999 Printed in Japan [MEMO]

#### **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

**OPENCAD** is a trademark of NEC Corporation.

Design Compiler is a registered trademark of Synopsys, Inc. in Japan.

Verilog-XL is a trademark of Cadence Design Systems, Inc..

The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

- The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production.

- Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

- NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property

rights of third parties by or arising from use of a device described herein or any other liability arising from use

of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other

intellectual property rights of NEC Corporation or others.

- Descriptions of circuits, software, and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these circuits,

software, and information in the design of the customer's equipment shall be done under the full responsibility

of the customer. NEC Corporation assumes no responsibility for any losses incurred by the customer or third

parties arising from the use of these circuits, software, and information.

- While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

- NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### NEC Electronics Inc. (U.S.) Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### **NEC Electronics (Europe) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 01 Fax: 0211-65 03 327

• Branch The Netherlands Eindhoven, The Netherlands Tel: 040-244 58 45 Fax: 040-244 45 80

• Branch Sweden Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388 NEC Electronics (France) S.A. Vélizy-Villacoublay, France Tel: 01-3067-58-00 Fax: 01-3067-58-99

NEC Electronics (France) S.A. Representación en España Madrid, Spain Tel: 091-504-27-87 Fax: 091-504-28-60

NEC Electronics Italiana S.R.L. Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

**NEC Electronics (UK) Ltd.** Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290 NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd. Novena Square, Singapore Tel: 253-8311 Fax: 250-3583

NEC Electronics Taiwan Ltd. Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### NEC do Brasil S.A.

Electron Devices Division Guarulhos-SP, Brasil Tel: 11-6462-6810 Fax: 11-6462-6829

J01.12

# Major Revisions in This Edition (1/2)

| Pages                       | Pages Description                                                                                                               |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| Throughout                  | Deletion of descriptions on NPB peripheral macro                                                                                |  |

| p.19                        | Modification of Figure 2-1 Clock Controller Connection Example (Placing Oscillator Inside ASIC and Attaching Resonator Outside) |  |

| p.25                        | Addition of Figure 3-1 NB85E ROM Area Setting (1) When one compiled ROM of 32 bits $\times$ 8 Kwords is connected               |  |

| p.25                        | Addition of Note in Figure 3-2 ROM Access Timing                                                                                |  |

| p.26                        | Addition of 3.2.1 When connecting one ROM                                                                                       |  |

| p.26                        | Addition of Figure 3-3 Example of Connecting One Compiled ROM (32 Bits x 8 Kwords) to VFB                                       |  |

| pp.27 to 31                 | Addition of 3.2.2 When connecting multiple ROMs                                                                                 |  |

| p.28                        | Modification of Figure 3-4 Example of Connecting Two Compiled ROMs (32 Bits × 4 Kwords) to VFB                                  |  |

| p.33                        | Modification of Figure 3-9 RAM Access Timing                                                                                    |  |

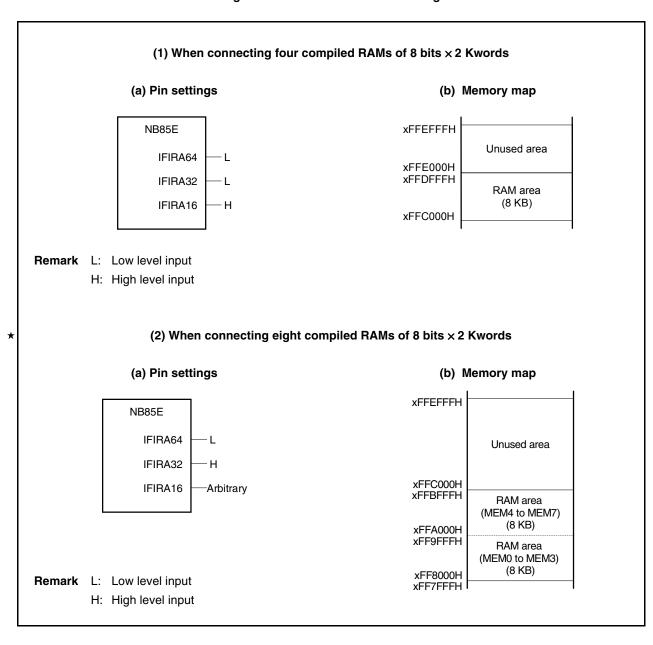

| p.34                        | Addition of Figure 3-10 NB85E RAM Area Setting (2) When connecting eight compiled RAMs of 8 bits × 2 Kwords                     |  |

| p.35                        | Modification of Figure 3-11 Example of Connecting Compiled Memory to VDB (Connecting Four<br>Compiled Memories)                 |  |

| p.36                        | Modification of Figure 3-12 Example of Connecting Compiled Memory to VDB (Connecting Eig<br>Compiled Memories)                  |  |

| pp.37 to 39                 | Addition of 3.3.1 Operation when eight RAMs are connected                                                                       |  |

| p.41                        | Modification of Figure 4-1 Example of Connecting User Logic to VSB                                                              |  |

| p.42                        | Modification of 4.1.1 Overview of VSB operation                                                                                 |  |

| p.44                        | Modification of Figure 4-4 VSB Timing (Address Hold)                                                                            |  |

| p.51                        | Modification of 4.2 Connection of Compiled Memory                                                                               |  |

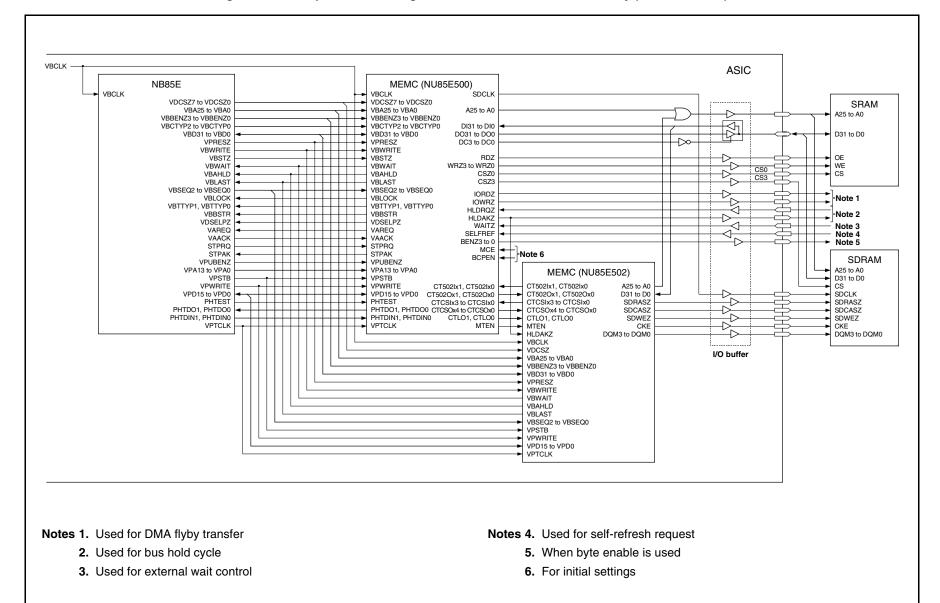

| p.56                        | Modification of description in CHAPTER 5 CONNECTION OF MEMORY CONTROLLER (MEMC)                                                 |  |

| p.57                        | Modification of Figure 5-1 Example of Connecting NB85E, MEMC, and External Memory (SRAM, SDRAM)                                 |  |

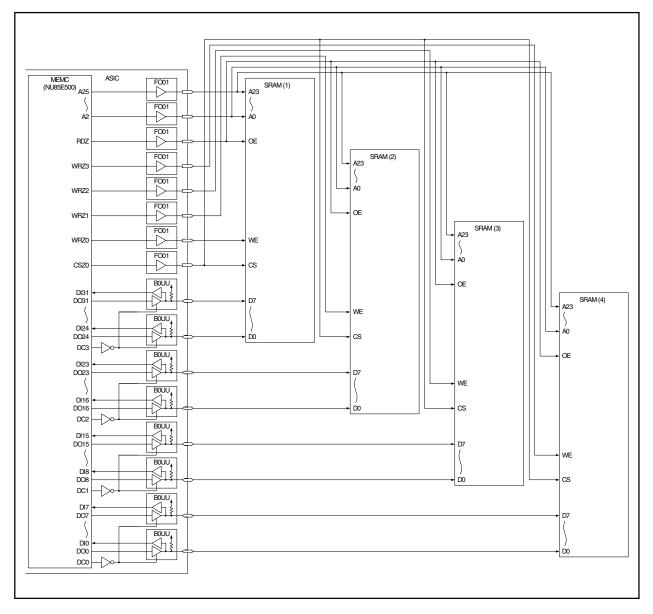

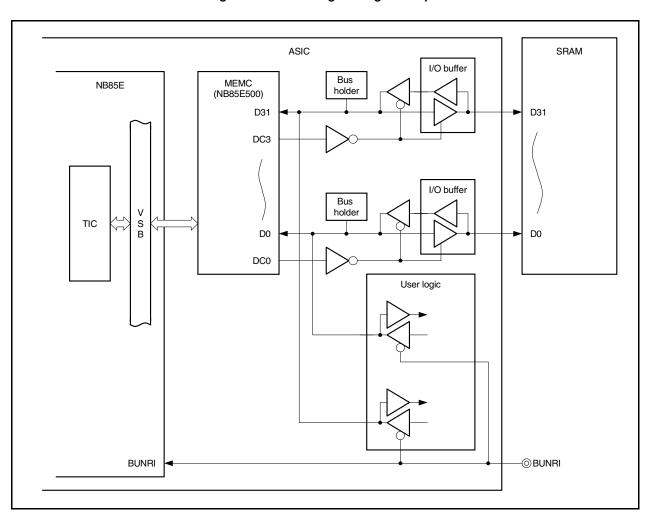

| p.58                        | Modification of Figure 5-2 Example of Connection to SRAM                                                                        |  |

| pp.50 to 53 in 2nd edition  | Deletion of 5.1 (2) Register example and (3) Operation timing example                                                           |  |

| pp.55, 56 in 2nd<br>edition | Deletion of 5.2 (2) Register example and (3) Operation timing example                                                           |  |

| p.60                        | Modification of 5.3 Connection to SDRAM                                                                                         |  |

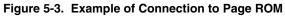

| p.61                        | Modification of Figure 5-4 Example of Connection to SDRAM                                                                       |  |

| pp.59 to 65 in 2nd edition  | Deletion of 5.3 (2) Register example and (3) Operation timing example                                                           |  |

| p.63                        | Modification of peripheral I/O area in 6.2 (1) Register mapping                                                                 |  |

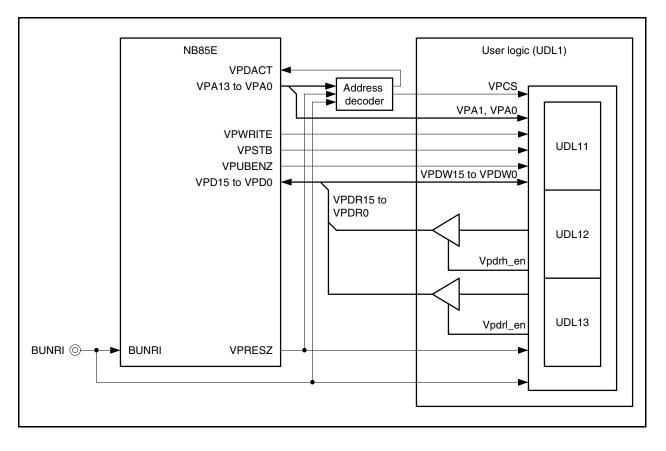

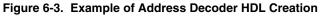

| p.64                        | Modification of Figure 6-3 Example of Address Decoder HDL Creation                                                              |  |

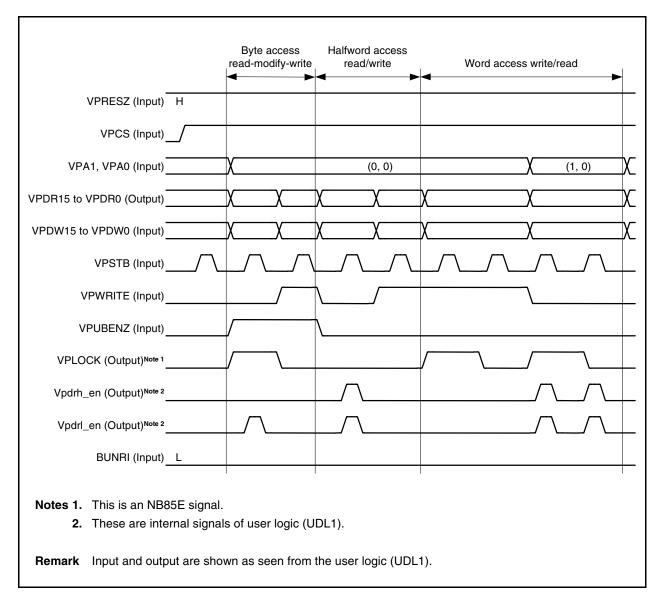

| p.65                        | Modification of Figure 6-4 Example of User Logic HDL Creation                                                                   |  |

# Major Revisions in This Edition (2/2)

| Pages         | Description                                                                                            |  |

|---------------|--------------------------------------------------------------------------------------------------------|--|

| p.67          | Modification of Figure 6-6 Example of HDL Creation for User Logic with Retry Function                  |  |

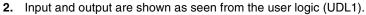

| p.69          | Modification of Figure 7-1 Example of Connecting Instruction Cache (NB85E213) to NB85E                 |  |

| p.71          | Addition of 7.1.1 (7) Initial program settings                                                         |  |

| p.71          | Addition of 7.1.1 (8) Setting BHC register of NB85E                                                    |  |

| p.71          | Addition of 7.1.1 (9) Test bus auto wiring tool support                                                |  |

| p.72          | Addition of 7.1.1 (10) Tag clear procedure                                                             |  |

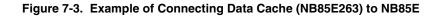

| p.73          | Modification of Figure 7-3 Example of Connecting Data Cache (NB85E263) to NB85E                        |  |

| p.74          | Addition of 7.2.1 (5) Test bus auto wiring tool support                                                |  |

| p.74          | Addition of 7.2.1 (6) Other                                                                            |  |

| p.75          | Addition of 7.2.1 (7) Operation during debugging                                                       |  |

| p.79          | Modification of Figure 8-4 Circuit Example for In-Circuit Emulator Connection (NB85E + RCU (NB85E901)) |  |

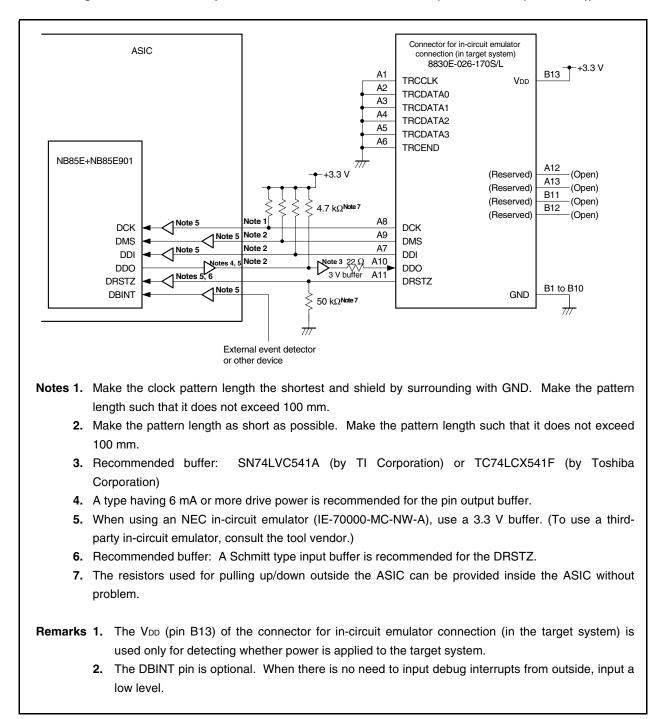

| p.80          | Modification of Figure 8-5 Circuit Example for In-Circuit Emulator Connection (NB85ET)                 |  |

| p.81          | Addition of 8.2.4 Design of timing with N-wire type in-circuit emulator                                |  |

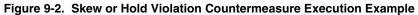

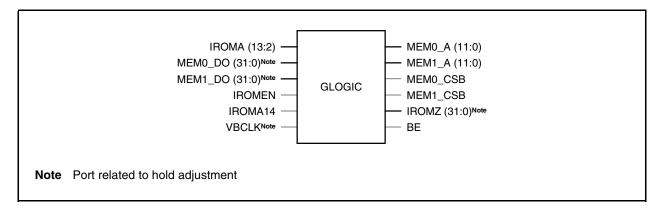

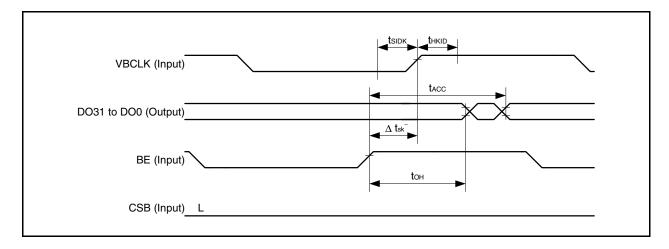

| p.86          | Modification of Figure 9-2 Skew or Hold Violation Countermeasure Execution Example                     |  |

| p.90          | Modification of 9.5 (2) Product specifications                                                         |  |

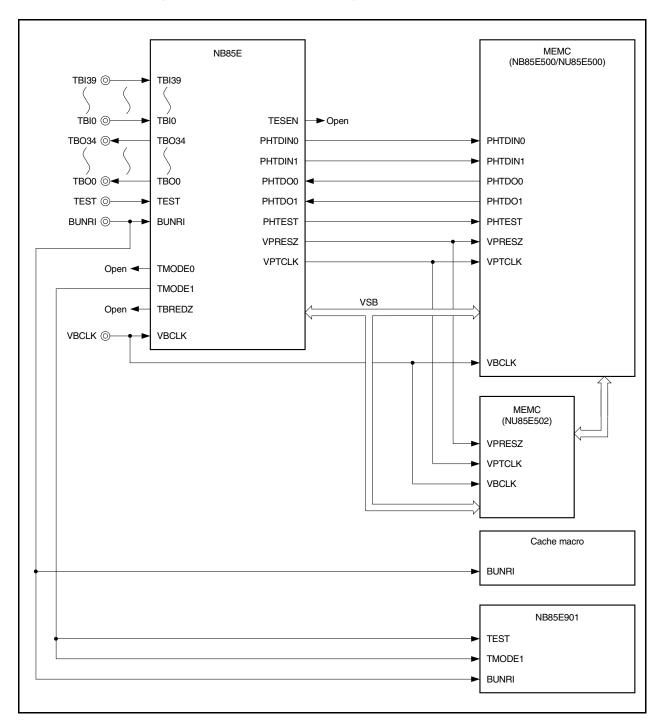

| p.92          | Modification of Figure 10-1 Example of Connecting Peripheral Macro to NB85E                            |  |

| p.94          | Modification of 10.2.1 (1) (b) Input pin processing                                                    |  |

| p.94          | Modification of 10.2.1 (1) (c) Output pin processing                                                   |  |

| p.95          | Modification of 10.2.1 (2) Pins for test mode                                                          |  |

| p.95          | Modification of 10.2.1 (3) Cautions when using NB85E901 (RCU)                                          |  |

| p.95          | Modification of 10.2.1 (4) Cautions when using NB85ET                                                  |  |

| pp.98 and 99  | Addition of 10.3 Test Bus Auto Wiring                                                                  |  |

| pp.100 to 105 | Addition of 10.4 Test Bus PINF File Creation/Editing Methods                                           |  |

| p.106         | Addition of description in CHAPTER 11 (1) Creation of test patterns for checking connections           |  |

| p.112         | Addition of APPENDIX REVISION HISTORY                                                                  |  |

The mark  $\star$  shows major revised points.

#### PREFACE

Target Readers

This manual is intended for users who design ASICs using NEC Corporation's "CB-9

Family VX/VM Type" high-speed, high-integration CMOS CBIC.

Purpose

The purpose of this manual is to give users an understanding of design methods and various restrictions and cautions specific to designing ASICs that have on-chip NB85E or NB85ET 32-bit microprocessor cores.

Be sure to observe the points (general information, cautions, and restrictions) described in this design manual. Failure to do so may lower the quality or performance of the ASIC or lead to malfunctions. Note, however, that these points do not necessarily guarantee a circuit, and necessary functions may not be satisfied as a result of placement and routing. Therefore, be sure to perform development after verifying operation.

**Organization** This manual is roughly organized into the following sections.

- Connection of clock controller

- Cache connection

- Connection of ROM/RAM to VFB/VDB

- Connection to VSB

- Cautions

- Connection of memory controller

- Connection to NPB

- Test circuit design

- Total chip simulation

Connection to in-circuit emulator (IE)

How to Use This Manual Note in this manual apply to both the NB85E and NB85ET, but the NB85E is used as the representative microprocessor core (CPU core) unless specifically stated otherwise. When using the NB85ET, read and modify the CPU core name and some of the pin names according to the following table (pin functions are the same in both products).

| Item     | Using NB85E <sup>№№ 1</sup><br>(Names used in this manual) | Using NB85ET<br>(Names must be changed to the following) |

|----------|------------------------------------------------------------|----------------------------------------------------------|

| CPU core | NB85E                                                      | NB85ET                                                   |

| Pin name | ne DCRESZ <sup>NOLE 2</sup> RESETZ                         |                                                          |

|          | DCSTOPZ                                                    | STOPZ                                                    |

|          | DCNMI2 to DCNMI0                                           | NMI2 to NMI0                                             |

- Notes 1. Includes systems in which the NB85E901 (run control unit (RCU)) is connected.

- **2.** There is a pin of the same name but with a different function in the NB85ET. Be careful when reading and changing names.

Before using this manual, be sure to read the separate "CB-9 Family VX/VM Type Design Manual (A12745E)".

| Conventions       | Data significance:<br>Active low representation:<br>Note:<br>Caution:<br>Remark:<br>Numerical representation:                                                                                    | Higher digits on the left and lower digits of<br>xxxZ (Z after pin or signal name)<br>or xxxB (B after pin or signal name)<br>Footnote for item marked with Note in the<br>Information requiring particular attention<br>Supplementary information<br>Binary xxxx or xxxxB<br>Decimal xxxx<br>Hexadecimal xxxxH                            | -                                       |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|                   | Prefix indicating the power                                                                                                                                                                      | Interacted contrait XXXXII         of 2 (address space, memory capacity):         K (kilo) $2^{10} = 1024$ M (mega) $2^{20} = 1024^2$ G (giga) $2^{30} = 1024^3$                                                                                                                                                                           |                                         |

| Related Documents | ted Documents The related documents indicated in this publication may include prelined However, preliminary versions are not marked as such.                                                     |                                                                                                                                                                                                                                                                                                                                            | reliminary versions.                    |

|                   | • CB-9 Family VX/VM Type     • NEC SYSTEM LSI DESIC     • NEC SYSTEM LSI DESIC     • NEC SYSTEM LSI DESIC     • NB85E Hardware User's     • NB85ET Hardware User's     • Memory Controller NB85E | e Core Library<br>U Core, Memory Controller Design Manua<br>Memory Macro (Compiled Type)<br>Design Manua<br>GN OPENCAD <sup>™</sup> V5.4<br>OPC_VSHELL User's Manua<br>GN OPENCAD V5.4<br>Verilog-XL <sup>™</sup> Interface User's Manual<br>GN OPENCAD V5.4<br>Design Compiler <sup>™</sup> Interface User's Manual<br>Manual<br>s Manual | I (A12982E)<br>I (A15050E)<br>(A15052E) |

|                   | • IE-V850E-MC, IE-V850E-                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                            | (U14487E)<br>(U14482E)                  |

The related documents listed above are subject to change without notice. Be sure to use the latest version of each document for designing.

### CONTENTS

| CHAPTE | ER 1 OVERVIEW                                                         | 16 |

|--------|-----------------------------------------------------------------------|----|

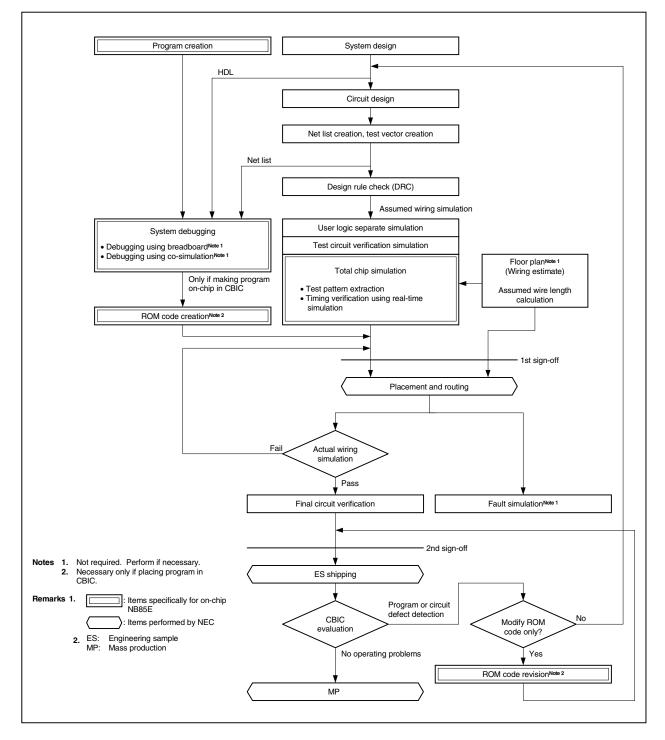

| 1.1    | Design Flow for CBIC with On-Chip NB85E                               | 16 |

| 1.2    | Items Specifically for On-Chip NB85E                                  | 17 |

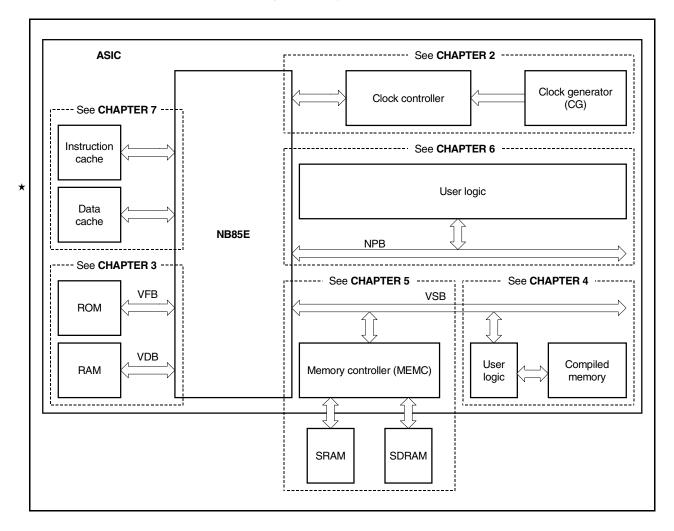

| 1.3    | System Example                                                        | 18 |

| CHAPTE | ER 2 CONNECTION OF CLOCK CONTROLLER                                   | 19 |

| СНАРТ  | ER 3 CONNECTION OF ROM/RAM TO VFB/VDB                                 | 23 |

| 3.1    | Overview                                                              | 23 |

| 3.2    | Connection of Compiled Memory to VFB                                  | 24 |

| *      | 3.2.1 When connecting one ROM                                         | 26 |

| *      | 3.2.2 When connecting multiple ROMs                                   | 27 |

| 3.3    | Connection of Compiled Memory to VDB                                  | 32 |

| *      | 3.3.1 Operation when eight RAMs are connected                         | 37 |

| СНАРТ  | ER 4 CONNECTION TO VSB                                                | 40 |

| 4.1    | Connection of User Logic                                              | 40 |

|        | 4.1.1 Overview of VSB operation                                       | 42 |

|        | 4.1.2 Circuit example                                                 | 45 |

| 4.2    | Connection of Compiled Memory                                         | 51 |

| СНАРТЕ | ER 5 CONNECTION OF MEMORY CONTROLLER (MEMC)                           | 56 |

| 5.1    | Connection to SRAM                                                    |    |

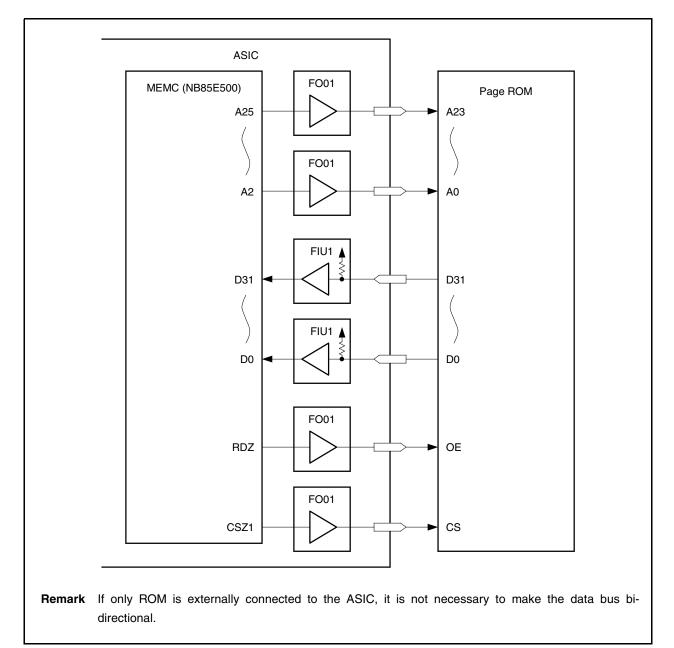

| 5.2    | Connection to Page ROM                                                | 59 |

| 5.3    | Connection to SDRAM                                                   | 60 |

| СНАРТЕ | ER 6 CONNECTION TO NPB                                                | 62 |

| 6.1    | Overview of NPB                                                       | 62 |

| 6.2    | Connection of User Logic                                              |    |

| СНАРТЕ | ER 7 CACHE CONNECTION                                                 |    |

| 7.1    | Connection of Instruction Cache                                       | 69 |

|        | 7.1.1 Cautions when using instruction cache                           |    |

| 7.2    |                                                                       |    |

|        | 7.2.1 Cautions when using data cache                                  |    |

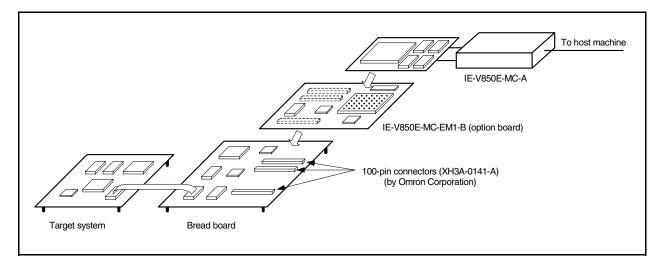

| СНАРТЕ | ER 8 CONNECTION TO IN-CIRCUIT EMULATOR (IE)                           |    |

| 8.1    | Using In-Circuit Emulator for NB85E (IE-V850E-MC-A)                   |    |

| 8.2    | Using N-Wire Type In-Circuit Emulator (IE-70000-MC-NW-A)              |    |

|        | 8.2.1 Connector for in-circuit emulator connection (in target system) |    |

|        | 8.2.2 Circuit example when RCU (NB85E901) is connected to NB85E       |    |

|        | 8.2.3 Circuit example when NB85ET is connected                        |    |

| *      | 8.2.4 Design of timing with N-wire type in-circuit emulator           | 81 |

|   | CHAPTE | R 9 CAUTIONS                                               | 82  |

|---|--------|------------------------------------------------------------|-----|

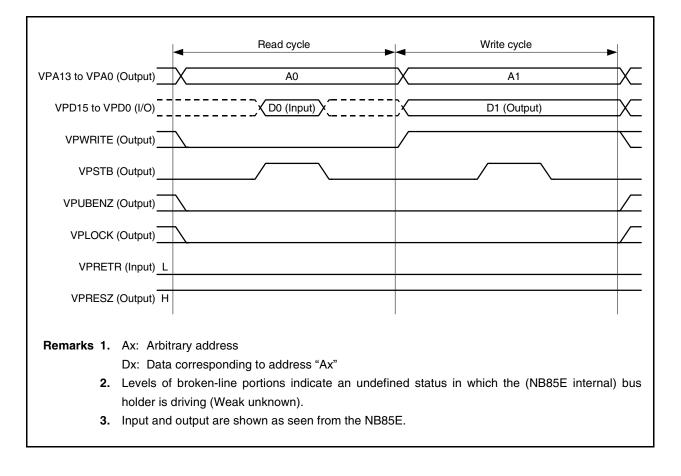

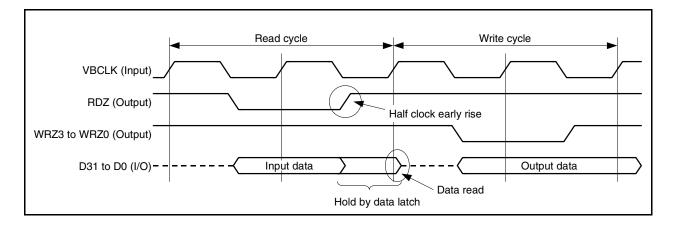

|   | 9.1    | Bus Contention When Moving from Read Cycle to Write Cycle  |     |

|   |        | (Using MEMC (NB85E500))                                    | 82  |

|   | 9.2    | Cautions on Verilog Simulation                             | 83  |

|   | 9.3    | Cautions on BUNRI-Testing Chip                             | 84  |

|   | 9.4    | Timing Adjustment                                          | 85  |

|   |        | 9.4.1 Adjustment of clock skew or data line hold violation |     |

|   |        | 9.4.2 Resolution of hold violation using design compiler   |     |

|   |        | 9.4.3 Clock skew adjustment                                |     |

|   | 9.5    | Device File                                                | 90  |

|   | CHAPTE | R 10 TEST CIRCUIT DESIGN                                   | 91  |

|   | 10.1   | Peripheral Macro Connection Example in Test Mode           | 92  |

|   |        | 2 Processing Pins in Test Mode                             |     |

|   |        | 10.2.1 Processing NB85E and NB85ET pins                    |     |

|   |        | 10.2.2 Processing MEMC pins                                |     |

| * | 10.3   | 3 Test Bus Auto Wiring                                     | 98  |

|   |        | 10.3.1 Test bus auto wiring method                         |     |

|   |        | 10.3.2 Verification of test bus by dummy model             |     |

| * | 10.4   | Test Bus PINF File Creation/Editing Methods                | 100 |

|   |        | 10.4.1 PINF file creation example                          |     |

|   | CHAPTE | R 11 TOTAL CHIP SIMULATION                                 | 106 |

|   | 11.1   | Creation of Test Patterns for Checking Connections         |     |

|   |        | 2 Verifying Timing Between Macros                          |     |

|   | CHAPTE | R 12 ROM CODE CREATION                                     | 111 |

| * | APPEND | NX REVISION HISTORY                                        | 112 |

# LIST OF FIGURES (1/3)

| Figure | e No. Title                                                                                             | Page |

|--------|---------------------------------------------------------------------------------------------------------|------|

| 1-1    | System Example                                                                                          | 18   |

| 2-1    | Clock Controller Connection Example<br>(Placing Oscillator Inside ASIC and Attaching Resonator Outside) | 19   |

| 2-2    | Clock Controller Timing Chart                                                                           |      |

| 2-3    | Example of Clock Controller HDL Creation                                                                | 21   |

| 2-4    | Clock Controller Connection Example (Using PLL Macro)                                                   | 22   |

| 3-1    | NB85E ROM Area Setting                                                                                  | 25   |

| 3-2    | ROM Access Timing                                                                                       | 25   |

| 3-3    | Example of Connecting One Compiled ROM (32 Bits $\times8$ Kwords) to VFB                                |      |

| 3-4    | Example of Connecting Two Compiled ROMs (32 Bits $\times$ 4 Kwords) to VFB                              |      |

| 3-5    | ROM Read Timing (For Same MEM Area)                                                                     |      |

| 3-6    | ROM Read Timing (When MEM Area Has Changed)                                                             | 30   |

| 3-7    | CSB, OEB Generation Block                                                                               |      |

| 3-8    | CSB and OEB Timings                                                                                     |      |

| 3-9    | RAM Access Timing                                                                                       |      |

| 3-10   | NB85E RAM Area Setting                                                                                  |      |

| 3-11   | Example of Connecting Compiled Memories to VDB (Four Memories)                                          | 35   |

| 3-12   | Example of Connecting Compiled Memories to VDB (Eight Memories)                                         | 36   |

| 3-13   | RAM Read Timing (Read from Same RAM Area)                                                               |      |

| 3-14   | RAM Read Timing (When RAM Area Has Changed)                                                             |      |

| 3-15   | RAM Write Timing                                                                                        | 39   |

| 4-1    | Example of Connecting User Logic to VSB                                                                 | 41   |

| 4-2    | VSB Timing (No Wait)                                                                                    | 42   |

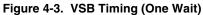

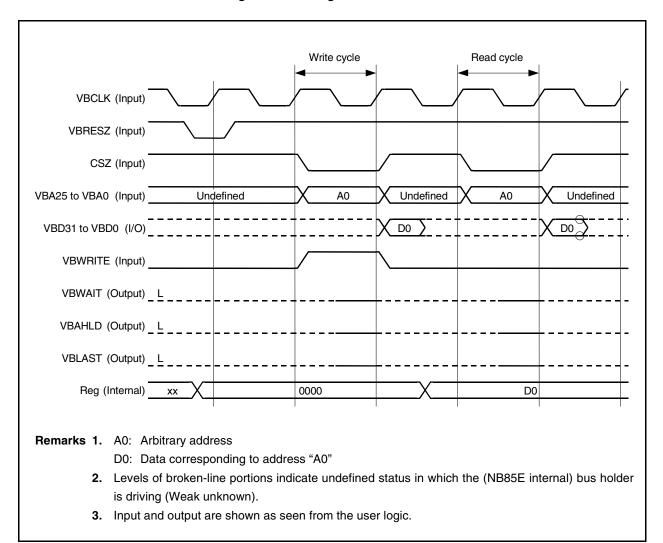

| 4-3    | VSB Timing (One Wait)                                                                                   | 43   |

| 4-4    | VSB Timing (Address Hold)                                                                               | 44   |

| 4-5    | HDL Creation Example for User Logic Operating with No Wait                                              | 45   |

| 4-6    | Timing Chart for No Wait                                                                                | 46   |

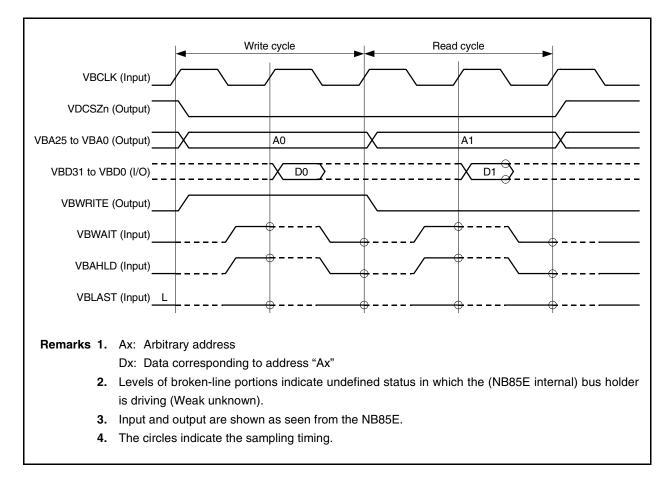

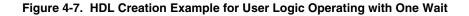

| 4-7    | HDL Creation Example for User Logic Operating with One Wait                                             | 47   |

| 4-8    | Timing Chart for One Wait Insertion                                                                     | 48   |

| 4-9    | Example of HDL Creation for User Logic in Which Address Hold Function Is Used                           | 49   |

# LIST OF FIGURES (2/3)

| Figure No. Title |                                                                                          | Page |

|------------------|------------------------------------------------------------------------------------------|------|

|                  |                                                                                          |      |

| 4-10             | Timing Chart for Address Hold                                                            | 50   |

| 4-11             | Example of Connecting Compiled Memory                                                    | 52   |

| 4-12             | Timing Chart for Compiled Memory Access                                                  | 53   |

| 4-13             | Example of HDL Creation for Compiled Memory Access Controller                            | 54   |

| 5-1              | Example of Connecting NB85E, MEMC, and External Memory (SRAM, SDRAM)                     | 57   |

| 5-2              | Example of Connection to SRAM                                                            | 58   |

| 5-3              | Example of Connection to Page ROM                                                        | 59   |

| 5-4              | Example of Connection to SDRAM                                                           | 61   |

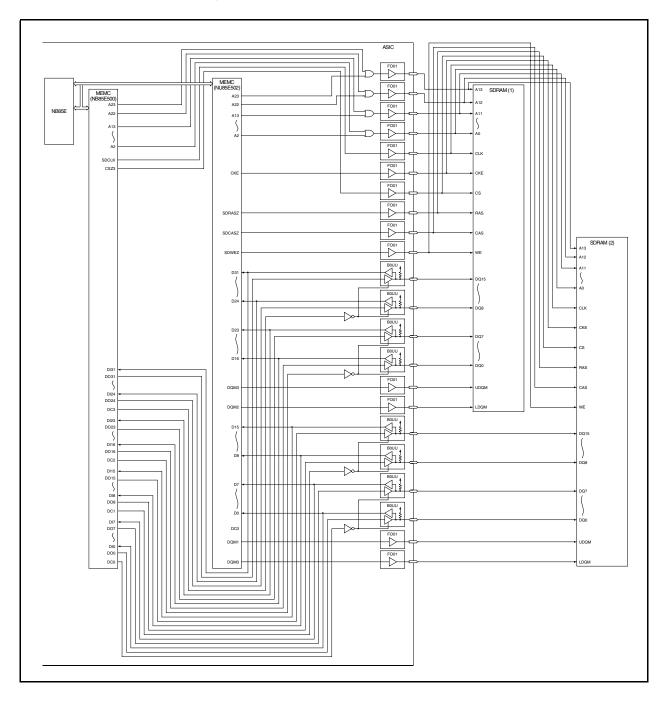

| 6-1              | NPB Operation Timing Chart                                                               | 62   |

| 6-2              | Example of Connecting User Logic                                                         | 64   |

| 6-3              | Example of Address Decoder HDL Creation                                                  | 64   |

| 6-4              | Example of User Logic HDL Creation                                                       | 65   |

| 6-5              | User Logic Operation Timing Chart                                                        | 66   |

| 6-6              | Example of HDL Creation for User Logic with Retry Function                               | 67   |

| 6-7              | Operation Timing Chart of User Logic with Retry Function                                 | 68   |

| 7-1              | Example of Connecting Instruction Cache (NB85E213) to NB85E                              | 69   |

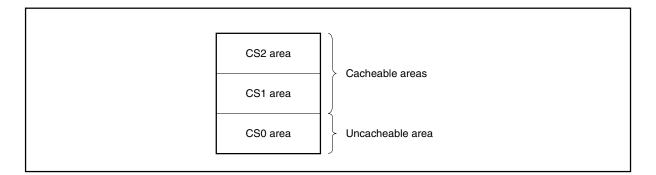

| 7-2              | Cache Area Setting Example                                                               | 71   |

| 7-3              | Example of Connecting Data Cache (NB85E263) to NB85E                                     | 73   |

| 8-1              | Connection of In-Circuit Emulator for NB85E (IE-V850E-MC-A)                              | 76   |

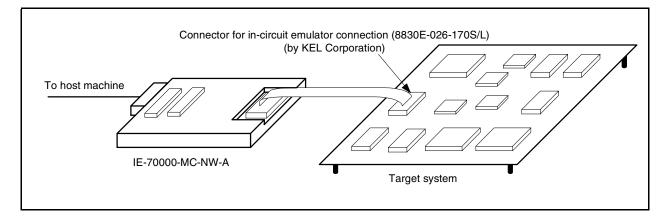

| 8-2              | Connection of N-Wire Type In-Circuit Emulator                                            | 77   |

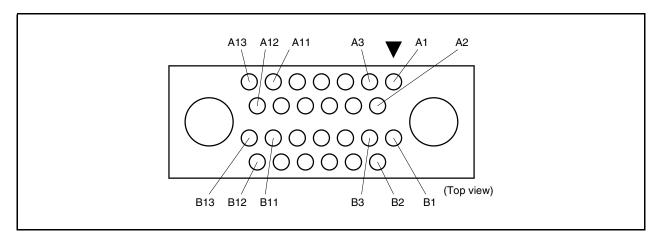

| 8-3              | Pin Placement Diagram of Connector for In-Circuit Emulator Connection (in Target System) | 77   |

| 8-4              | Circuit Example for In-Circuit Emulator Connection (NB85E + RCU (NB85E901))              | 79   |

| 8-5              | Circuit Example for In-Circuit Emulator Connection (NB85ET)                              | 80   |

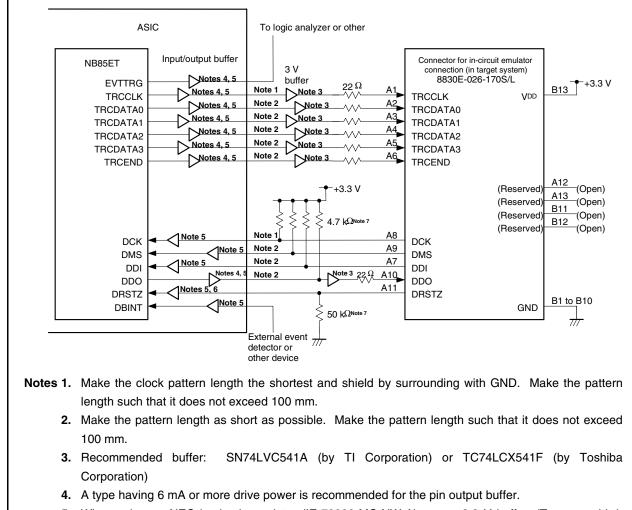

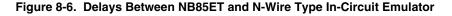

| 8-6              | Delays Between NB85ET and N-Wire Type In-Circuit Emulator                                | 81   |

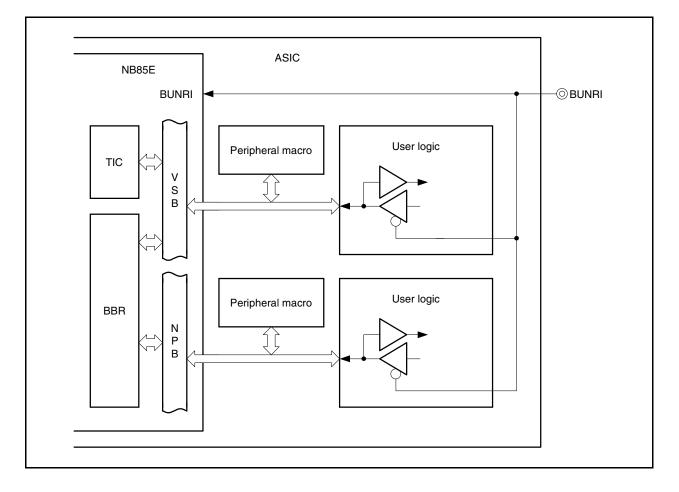

| 9-1              | User Logic Design Example                                                                | 84   |

| 9-2              | Skew or Hold Violation Countermeasure Execution Example                                  | 86   |

| 10-1             | Example of Connecting Peripheral Macro to NB85E                                          | 92   |

# LIST OF FIGURES (3/3)

| Figure | No. Title                                                                             | Page |

|--------|---------------------------------------------------------------------------------------|------|

|        |                                                                                       |      |

| 10-2   | User Logic Design Example                                                             | 94   |

| 10-3   | User Logic Design Example                                                             | 96   |

| 10-4   | PINF File Creation Example (NB85E + NU85E500 + NU85E502 + NB85E901 + NB85E212)        | 101  |

| 10-5   | PINF File Creation Example (NB85ET + NU85E500 + NU85E502 + NB85E212)                  | 104  |

|        |                                                                                       |      |

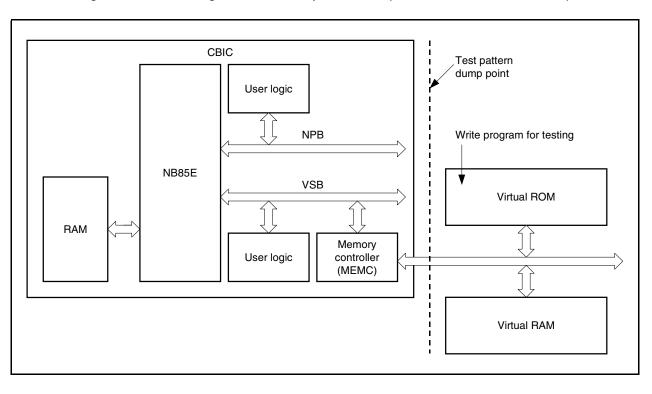

| 11-1   | Block Diagram for Total Chip Simulation (When There Is No ROM in VFB)                 | 107  |

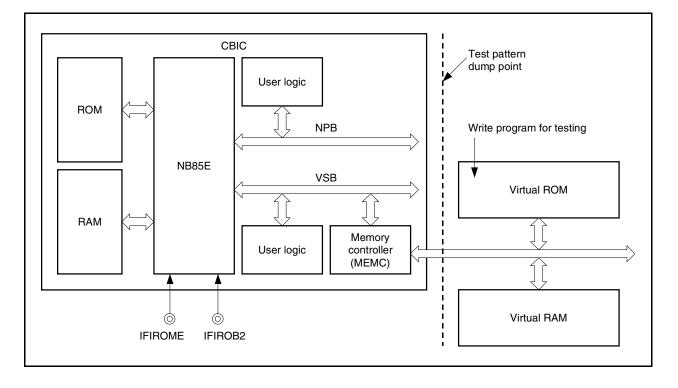

| 11-2   | Block Diagram for Total Chip Simulation                                               |      |

|        | (When There Is ROM in VFB and Creating Test Pattern by Connecting Virtual ROM to VSB) | 108  |

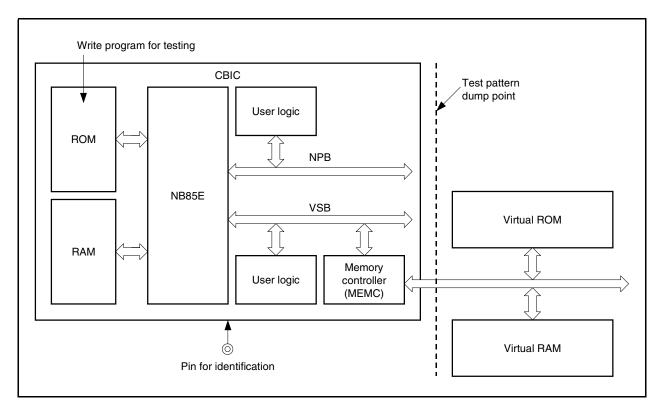

| 11-3   | Block Diagram for Total Chip Simulation                                               |      |

|        | (When There Is ROM in VFB and Writing Program for Testing in That ROM)                | 109  |

# LIST OF TABLES

| Table | No. Title                                                                        | Page |

|-------|----------------------------------------------------------------------------------|------|

| 4-1   | User Logic Interface Signals                                                     | 40   |

| 6-1   | Example of User Logic Address Assignment                                         | 63   |

| 8-1   | Pin Functions of Connector for In-Circuit Emulator Connection (in Target System) | 78   |

# 1.1 Design Flow for CBIC with On-Chip NB85E

#### 1.2 Items Specifically for On-Chip NB85E

#### (1) Total chip simulation

Total chip simulation is simulation that checks the connections between macros by operating the NB85E. See **CHAPTER 11 TOTAL CHIP SIMULATION** for the simulation method and cautions.

#### (2) System debugging

System debugging debugs the entire target system, including the CBIC under development.

#### (a) Debugging using breadboard

#### <1> Debugging using in-circuit emulator for NB85E (IE-V850E-MC-A)

Debug the target system by creating a breadboard using a general-purpose LSI, FPGA, and G/A. See **8.1 Using In-Circuit Emulator for NB85E (IE-V850E-MC-A)** regarding connecting to the IE-V850E-MC-A.

#### <2> Debugging using N-Wire type in-circuit emulator (IE-70000-MC-NW-A)

Since the NB85ET has a debug control unit (DCU) that supports an on-chip debug function, realtime debugging using an ES is possible by connecting to the IE-70000-MC-NW-A via a dedicated debug interface based on JTAG.

Similar debugging can be performed in the case of an NB85E if an NB85E901 (run control unit (RCU)) is connected.

| Debug           | NB85ET | NB85E + NB85E901 |

|-----------------|--------|------------------|

| Break           |        | $\checkmark$     |

| Event detection |        | _                |

| Trace           |        | _                |

See 8.2 Using N-Wire Type In-Circuit Emulator (IE-70000-MC-NW-A) regarding connecting to the in-circuit emulator.

#### (b) Debugging using co-simulation

Debug the target system using co-simulation.

Normally, integrated debugging of hardware and software using an in-circuit emulator is not possible before ES completion. However, co-simulation makes possible target-less debugging of both hardware and software at the system design stage before ES completion. Contact NEC for details.

#### (3) ROM code creation and revision

Sign-off to NEC must be performed using a specific format. See **CHAPTER 12 ROM CODE CREATION** regarding the format.

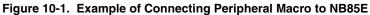

#### 1.3 System Example

In this manual, the ASIC shown below is used as an example and explained by focussing on the method of connecting each peripheral macro to the NB85E.

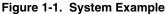

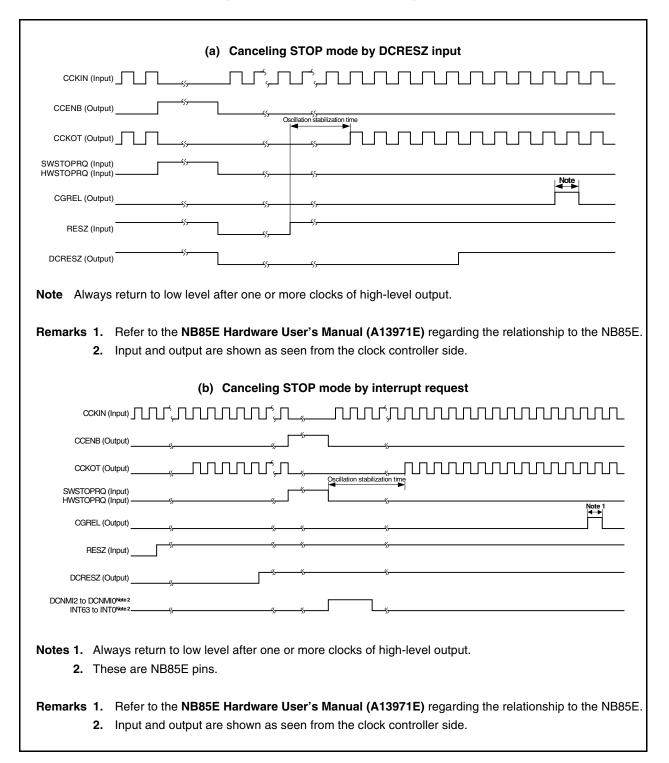

#### CHAPTER 2 CONNECTION OF CLOCK CONTROLLER

When using the NB85E software or hardware STOP mode, connect a clock controller between the oscillator (or external input clock) and NB85E or between the oscillator (or external input clock) and an other circuit related to VBCLK so that sufficient oscillation stabilization time can be guaranteed, allowing a stable clock to be supplied to the NB85E.

# Figure 2-1. Clock Controller Connection Example (Placing Oscillator Inside ASIC and Attaching Resonator Outside)

The oscillator oscillates when a low level is output from the CCENB pin of the clock controller. Oscillation stabilization time is counted by the counter register (CNTR) inside the clock controller. The standard value of CNTR is determined using the following relational expression.

CNTR >> Oscillation stabilization time [s] × Clock frequency [Hz]

\*

**Example** Using an oscillator for which the output clock frequency is 20 MHz and the oscillation stabilization time is 1 ms:

$CNTR >> 1 \times 10^{-3} \times 20 \times 10^{6} = 20000 (4E20H)$

Caution If the STPAK pin of the NB85E is unused, input a high level to the STPAK pin. If a high level is not input, the HWSTOPRQ signal and SWSTOPRQ signal do not become active and STOP mode cannot be entered.

Figure 2-2 shows the timing chart of each signal of the clock controller in Figure 2-1 and Figure 2-3 shows an HDL creation example.

Figure 2-2. Clock Controller Timing Chart

In the example in Figure 2-3, the reset input of the NB85E (DCRESZ) is also controlled. This is in order to reliably supply a stable clock during a reset period. The DCRESZ signal rises after the oscillation stabilization time has been secured following the rise of the RESZ signal (system reset).

```

module CLKCTL(

CCKOT, SWSTOPRQ, HWSTOPRQ, CGREL,

CCKIN, CCENB, DCRESZ, RESZ

);

// Output to VBCLK pin of NB85E

output

CCKOT ;

SWSTOPRQ ; // Input from SWSTOPRQ pin of NB85E

input

HWSTOPRQ ; // Input from HWSTOPRQ pin of NB85E

input

// Output to CGREL pin of NB85E

output

CGREL ;

CCKIN;

// Input from CLKOUT pin of oscillator (or PLL)

input

// Output to ENB pin of oscillator (or PLL)

output

CCENB ;

DCRESZ :

// Output to DCRESZ pin of NB85E

output

RESZ ;

// System reset input

input

reg [7:0] CNTR ;

// Oscillation stabilization time counter. The bit width is adjusted in accordance with the oscillation stabilization time.

CKOTEN ;

// Clock output enable

reg

reg

DCRESZ;

// NB85E reset

STOPRQZ = ~ (SWSTOPRQ | HWSTOPRQ);

wire

CGREL = ( CNTR == 8'hFE ) ;

// CGREL output timing setting

wire

CCKOT = CKOTEN & CCKIN ;

wire

CCENB = ~STOPRQZ ;

wire

// synopsys async_set_reset "DCRESZ"

always @( negedge CCKIN or negedge STOPRQZ or negedge RESZ ) begin

if (~RESZ) begin

CNTR

<= 8'h00 :

CKOTEN

<= 1'b0 ;

DCRESZ

<= 1'b0 ;

end

else begin

if( ~STOPRQZ ) begin

CNTR

<= 8'h00 ;

CKOTEN

<= 1'b0 ;

end

else begin

if ( CNTR == 8'hF0 ) CKOTEN

<= 1'b1 ;

// Clock output timing setting. The oscillation stabilization time is F0H.

if ( CNTR == 8'hF5 ) DCRESZ

<= 1'b1 ;

// DCRESZ output timing setting

if ( CNTR != 8'hFF ) CNTR

<= CNTR + 1 ; // Internal counter stop timing setting

end

end

end

endmodule

```

| Figure 2-3. | Example of | <b>Clock Controller</b> | <b>HDL Creation</b> |

|-------------|------------|-------------------------|---------------------|

|-------------|------------|-------------------------|---------------------|

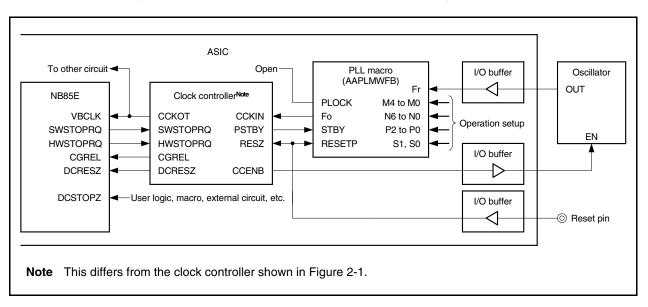

When using a PLL macro, the configuration is as shown in Figure 2-4.

Figure 2-4. Clock Controller Connection Example (Using PLL Macro)

The PLL macro and clock controller in Figure 2-4 are described below.

#### (1) PLL macro

"AAPLMWFB" is taken as an example (contact NEC for details about macros). The input clock corresponds to 5 MHz to 160 MHz, and the output clock to 50 MHz to 250 MHz.

In Figure 2-4, if each of pins M4 to M0, N6 to N0, and P2 to P0, which set counter values, and each of pins S1 and S0, which set VCO range setting switching, is set as follows, when a 16.384 MHz clock is input to the Fr pin, a 49.152 MHz (50% duty) signal is obtained from the Fo pin.

- M4 to M0: L, L, L, L, H

- N6 to N0: L, L, L, L, L, H, H

- P2 to P0: L, L, H

- S1, S0: L, L

Remark L: Low-level input H: High-level input

#### (2) Clock controller

A control pin (PSTBY) must be added for setting the PLL to standby mode when the controller shown in Figure 2-1 is in STOP mode.

In addition, if both the PLL (twPLL) and the OSC (twosc) are made to oscillate, the oscillation stabilization time must take into account the time interval twPLL+twosc.

# CHAPTER 3 CONNECTION OF ROM/RAM TO VFB/VDB

### 3.1 Overview

The NB85E provides a V850E fetch bus (VFB) that makes direct connection of ROM possible and a V850E data bus (VDB) that makes direct connection of RAM possible.

The VFB is a bus optimized for fetching instructions, and the VDB is a bus optimized for accessing data.

Since these buses are independent of the VSB, instructions can be fetched, or data accessed, even if the VSB is occupied by another macro.

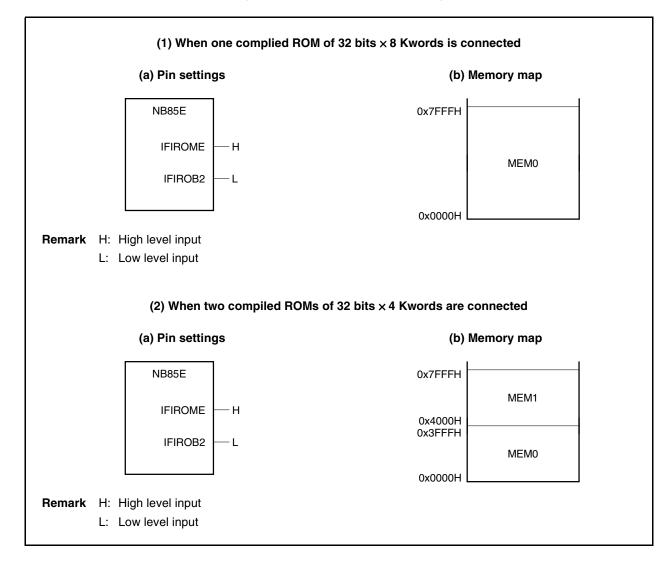

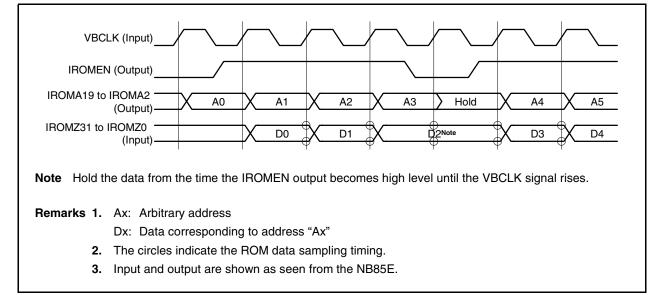

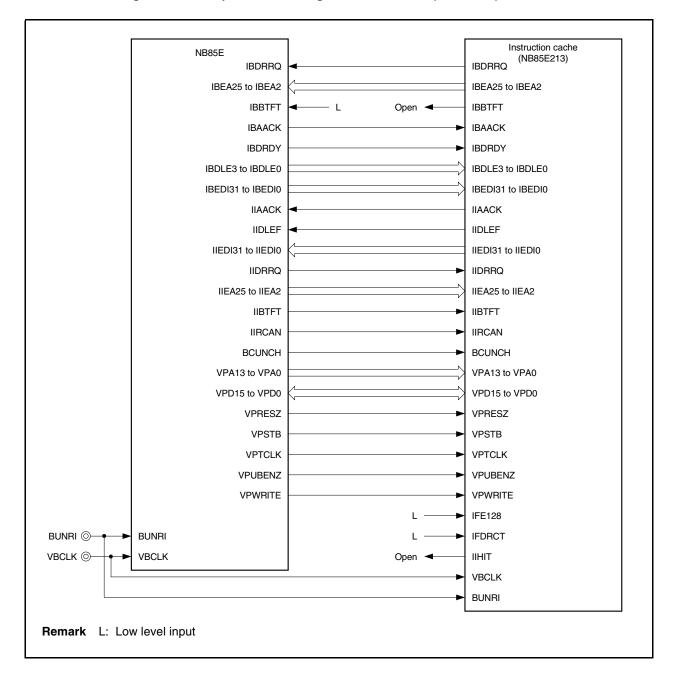

#### 3.2 Connection of Compiled Memory to VFB

The VFB is a bus for fixed 32-bit access instruction fetches that is optimized for data access and by which one clock access is possible.

When a high level is input to the IFIROME pin, an instruction fetch from a ROM connected to the VFB is possible. The compiled ROM that can be used by the CB-9 Family VX/VM Type is fast synchronous ROM.

When connecting compiled ROM to the VFB, it is necessary to compute the relationship of the ROM access time and cycle time to the CPU clock frequency and check that the timing fits adequately (see **9.4 Timing Adjustment**).

Figure 3-1 shows the NB85E ROM area setting, Figure 3-2 shows the ROM access timing, Figure 3-3 shows an example in which one compiled ROM of 32 bits  $\times$  8 Kwords for the CB-9 Family VX Type is connected, and Figure 3-4 shows an example in which two compiled ROMs of 32 bits  $\times$  4 Kwords for the CB-9 Family VX Type are connected.

- Remarks 1. For details about compiled memory, refer to the CB-9 Family VX/VM Type Memory Macro (Compiled Type) Design Manual (A12982E).

- 2. For the creation method of compiled memory, refer to NEC SYSTEM LSI DESIGN OPENCAD V5.4 OPC\_VSHELL User's Manual (A15050E).

- When using compiled memory, test wiring is needed in order to use the ASIC standard test procedure. Refer to the CB-9 Family VX/VM Type Design Manual (A12745E) regarding the test procedure.

\*

25

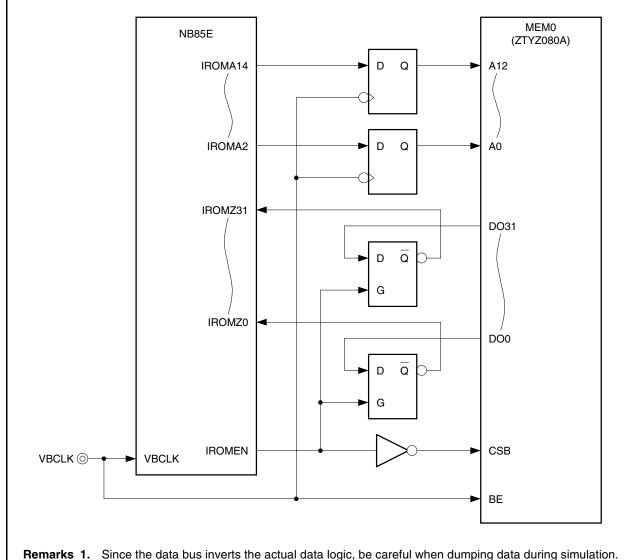

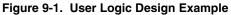

#### ★ 3.2.1 When connecting one ROM

\*

Figure 3-3 shows an example of connecting one compiled ROM of 32 bits  $\times$  8 Kwords for the CB-9 Family VX Type.

The operation of the VFB of the NB85E is of the pipeline type, whereby an address and the data that corresponds to that address is shifted by only 1 cycle. Here, to facilitate securing of the address setup/hold time, a flip-flop is inserted between the IROMA14 to IROMA2 pins of the NB85E and the A12 to A0 pins of the compiled ROM. Also, since data is held while the IROMEN is low level, a level latch is inserted between the DO31 to DO0 pins of the compiled ROM and the IROMZ31 to IROMZ0 pins of the NB85E.

The compiled ROM addresses are allocated to 0x00000H to 0x07FFFH.

#### Figure 3-3. Example of Connecting One Compiled ROM (32 Bits × 8 Kwords) to VFB

Since the data bus inverts the actual data logic, be careful when dumping data during simulation.

The figure shows the normal pin wiring method. Wire test pins in accordance with the ASIC test procedure (for details, refer to the CB-9 Family VX/VM Type Design Manual (A12745E)).

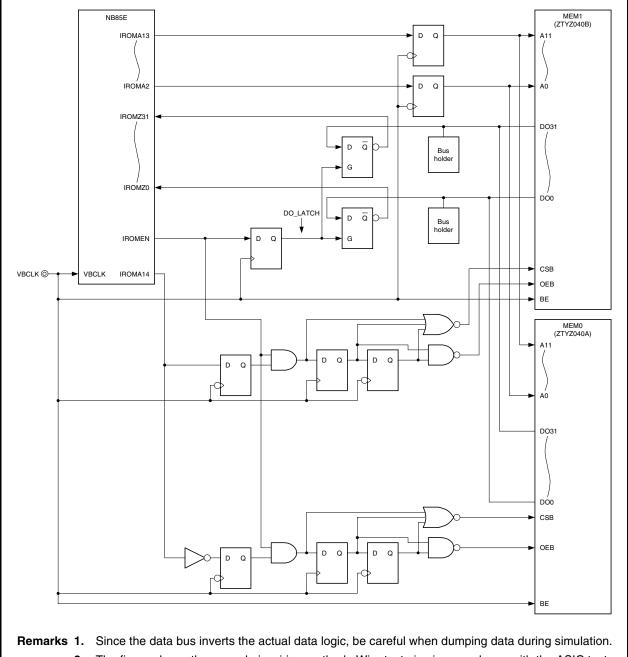

#### 3.2.2 When connecting multiple ROMs

Figure 3-4 shows an example of connecting two compiled ROMs of 32 bits  $\times$  4 Kwords for the CB-9 Family VX Type. For the ROM area memory map, refer to Figure 3-1 (2) When two compiled ROMs of 32 bits  $\times$  4 Kwords are connected.

When multiple ROMs (for example MEM0 and MEM1) are connected, normal read may be prevented because the CSB changes to inactive level prior to the completion of data read from ROM during continuous fetching for the area spanning MEM0 and MEM1 or during branching between MEM0 and MEM1.

To prevent this, in the connection example shown in Figure 3-4, a circuit that adjusts the CSB change timing during area changes is inserted between the IROMEN pin of the NB85E and the CSB pin of the compiled ROM. This circuit also functions as an address decoder between MEM0 and MEM1.

The compiled ROM addresses are allocated to 0x0000H to 0x3FFFH for MEM0 and 0x4000H to 0x7FFFH for MEM1.

Figure 3-4. Example of Connecting Two Compiled ROMs (32 Bits × 4 Kwords) to VFB

Since the data bus inverts the actual data logic, be careful when dumping data during simulation.

The figure shows the normal pin wiring method. Wire test pins in accordance with the ASIC test procedure (for details, refer to the CB-9 Family VX/VM Type Design Manual (A12745E)).

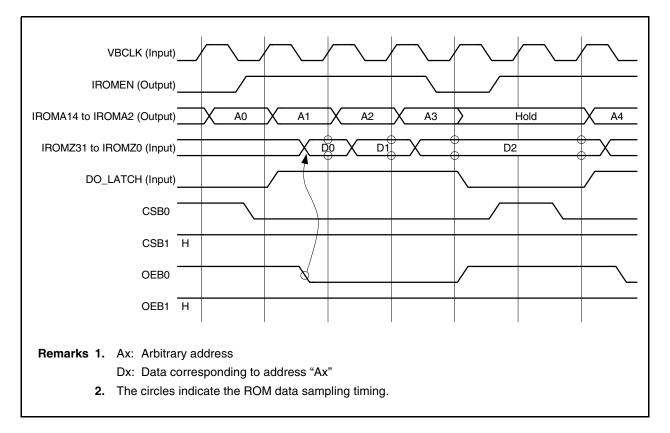

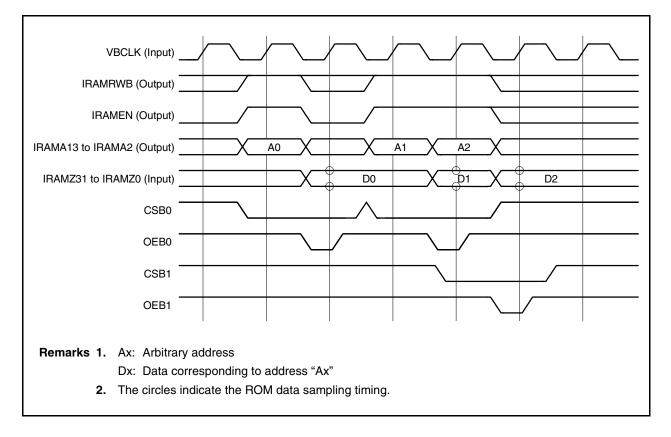

#### (1) ROM read from the same MEM area

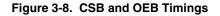

When the result of decoding addresses is MEM0 area (in Figure 3-4, IROMA14 is low level), CSB0 becomes active as soon as IROMEN becomes active. The address on the MEM0 side is latched at the rising edge of the next clock after CSB0 becomes active, OEB0 becomes active at the next falling edge, and the valid data is input to IROMZ31 to IROMZ0.

At the next rising edge after IROMEN becomes inactive, at the same time as OEB0 becomes inactive, IROMZ31 to IROMZ0 hold the value at that time. This is because the values are held without performing ROM read while IROMEN is inactive, through level latching between D0 and IROMZ31 to IROMZ0. At the next falling edge of the clock after OEB0 becomes inactive, CSB0 becomes inactive. Figure 3-5 shows the timing when the MEM0 area is accessed continually.

#### Figure 3-5. ROM Read Timing (For Same MEM Area)

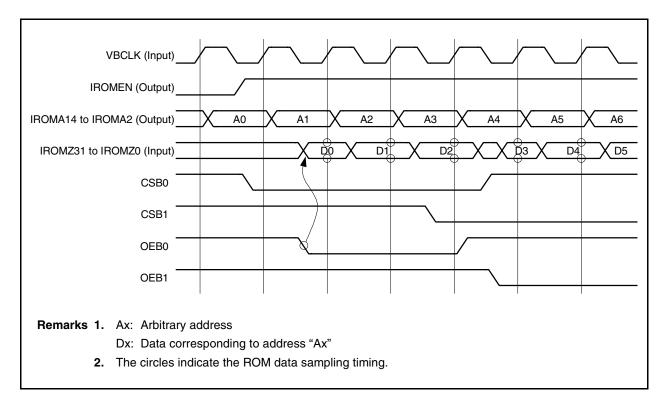

#### (2) ROM read when MEM area has changed

Figure 3-6 shows the CSB0, CSB1, OEB0, and OEB1 timings during continuous access to A0 to A2 (MEM0 area) and A3 to A6 (MEM1 area).

Even if IROMA14 to IROMA2 become A3 and the ROM address changes from the MEM0 area to the MEM1 area, since the data (D2) read timing for A2 is one clock later, at the rising edge of VCLK, OEB0 is extended by 1 clock, and CSB0 by 1.5 clocks. CSB1 is made active at the falling edge of A3 for preparation to read D3. To avoid data conflict between MEM0 and MEM1, OEB1 becomes active 0.5 clocks after OEB0 becomes inactive.

Figure 3-6. ROM Read Timing (When MEM Area Has Changed)

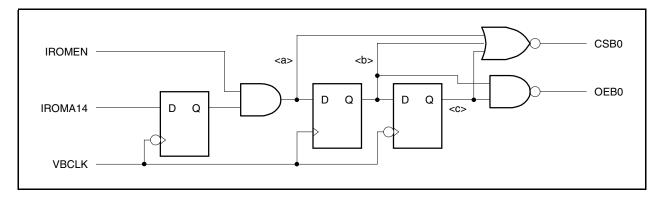

Figure 3-7 shows the CSB0, OEB0 generation block, and Figure 3-8 shows the CSB0 and OEB0 timings. (<a> to <c> in Figure 3-7 correspond to <a> to <c> on the MEM0 side in Figure 3-8.)

#### 3.3 Connection of Compiled Memory to VDB

The VDB is a bus that is optimized for data access and can perform access in as fast as one clock.

Access is possible using 8-bit, 16-bit, or 32-bit units.

When connecting compiled RAM to the VDB, it is necessary to compute the relationship of the compiled RAM access time and cycle time to the CPU clock frequency and check that the timing fits adequately (see **9.4 Timing Adjustment**).

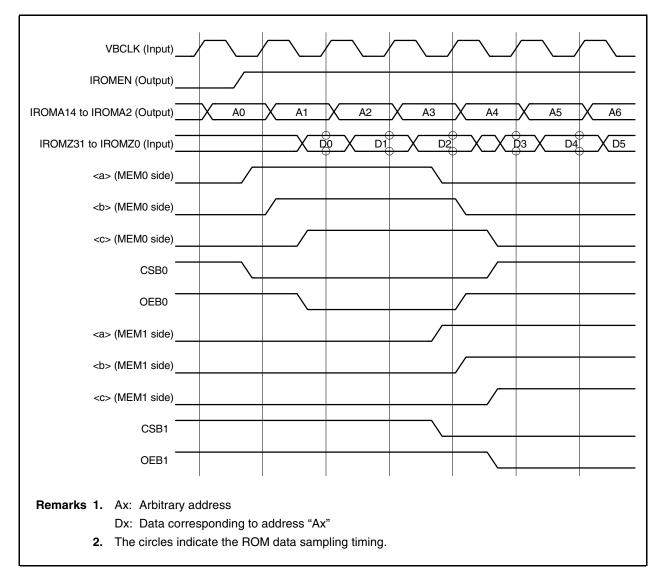

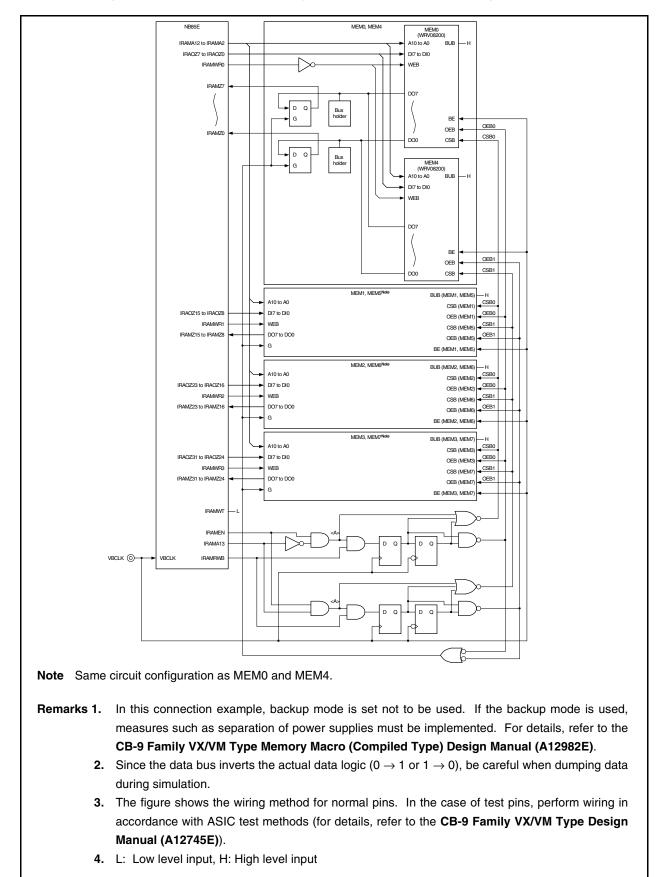

Figure 3-9 shows the RAM access timing, Figure 3-10 shows the NB85E RAM area setting, Figure 3-11 shows an example in which four compiled RAMs of 8 bits  $\times$  2 Kwords for the CB-9 Family VX Type are connected, and Figure 3-12 shows an example in which eight compiled RAMs of 8 bits  $\times$  2 Kwords are connected.

- Remarks 1. For details about compiled memory, refer to the CB-9 Family VX/VM Type Memory Macro (Compiled Type) Design Manual (A12982E).

- 2. For the creation method of compiled memory, refer to NEC SYSTEM LSI DESIGN OPENCAD V5.4 OPC\_VSHELL User's Manual (A15050E).

- 3. When using compiled memory, test wiring is needed in order to use the ASIC standard test procedure. Refer to the CB-9 Family VX/VM Type Design Manual (A12745E) regarding the test procedure.

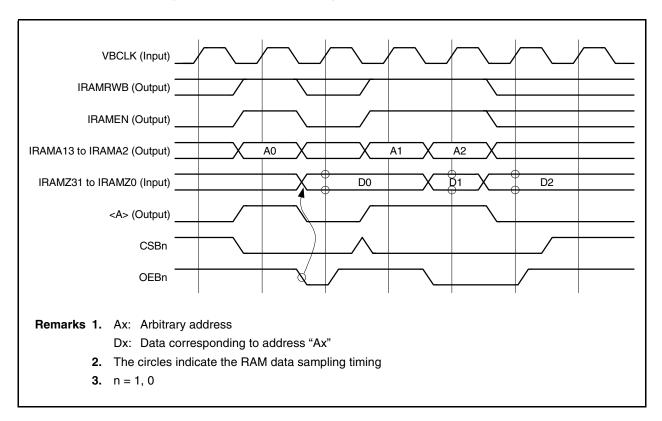

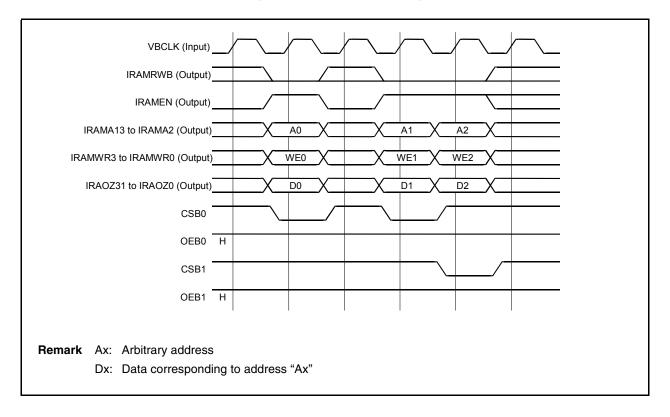

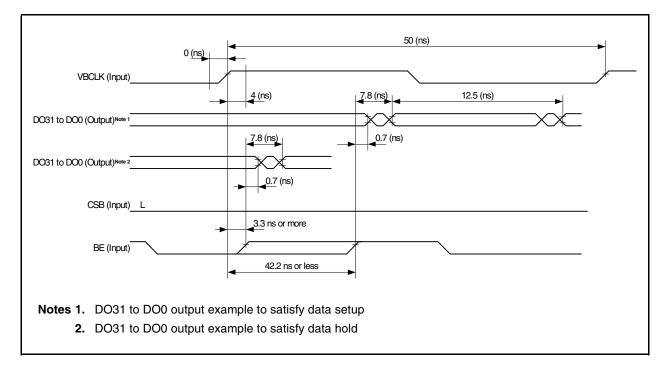

Figure 3-9. RAM Access Timing

\*

Figure 3-10. NB85E RAM Area Setting

Preliminary Design Manual A14335EJ3V0DM

#### 3.3.1 Operation when eight RAMs are connected

### (1) Read from same RAM area

Figure 3-13 shows the timing when the RAM area of either MEM0 to MEM3 or MEM4 MEM7 is read. To support read access in the VDB pipeline method, OEB is generated with the result of decoding IRAMA13 delayed by 1 clock. To prevent data conflicts, CSB is generated by ORing the address decoding result and OEB.

As soon as the result of inputting and decoding IRAMEN and IRAMA13 (refer to  $\langle A \rangle$  in Figure 3-12) becomes active, CSBn becomes active. RAM starts being read at the next rising edge of the clock, but output is not performed because OEBn is inactive at that time. OEBn becomes active at the next falling edge of the clock, and valid data is input to IRAMZ31 to IRAMZ0 (n = 1, 0).

At the next rising edge after the decoded result becomes inactive, at the same time that OEBn becomes inactive, IRAMZ31 to IRAMZ0 hold the value at that time. This is because they hold the value without reading RAM while OEBn is inactive. At the next falling edge of the clock after OEBn becomes inactive, CSBn becomes inactive.

Since the pipeline method is not used during write access, the result of decoding IRAMA13 is transferred as is to CSB.

Figure 3-13. RAM Read Timing (Read from Same RAM Area)

### (2) Read when RAM area has changed

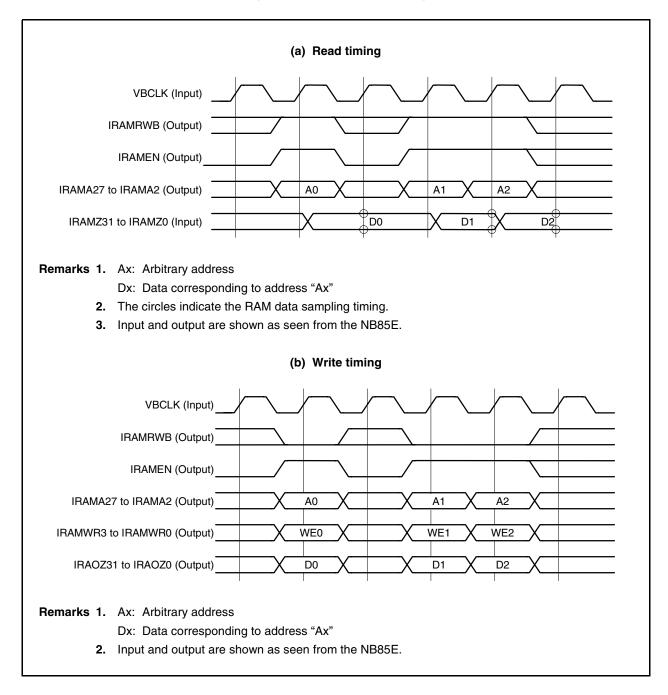

Figure 3-14 shows the CSB0, OEB0, CSB1, and OEB1 timings during continuous read access to A0 and A1 (MEM0 to MEM3 area) and A2 (MEM4 to MEM7 area).

Even if IRAMA13 to IRAMA2 change from A1 to A2, and the RAM address changes from the MEM0 to MEM3 area to the MEM4 to MEM7 area, the timing for reading the data (D1) corresponding to A1 is the rising edge of the clock 0.5 clocks later, so OEB0 and CSB0 for the MEM0 to MME3 area are extended 0.5 clocks and 1 clock, respectively. Since CSB1 reads D2, it becomes active when IRAMA13 to IRAMA2 become A2. In order to prevent data conflict, OEB1 becomes active 0.5 clocks after OEB0 becomes inactive.

Figure 3-15 shows the CSB0 and CSB1 timings during continuous write access to A0 and A1 (MEM0 to MEM3 area) and A2 (MEM4 to MEM7 area).

In the case of write access, since pipeline processing is not required, CSB is generated based on IRAMEN and the address decoding result.

### **CHAPTER 4 CONNECTION TO VSB**

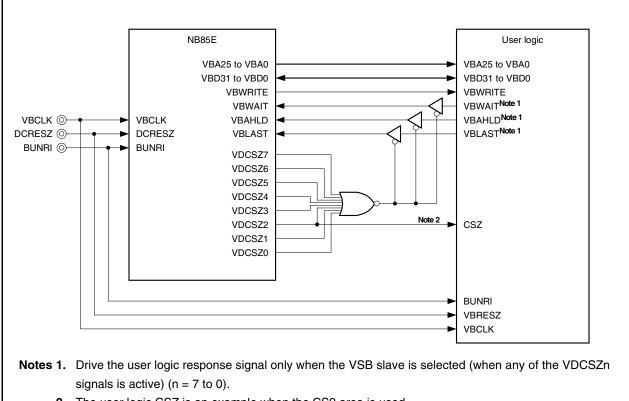

### 4.1 Connection of User Logic

This section describes how to connect user logic to the VSB.

Three kinds of read/write 32-bit registers are taken as examples of user logic. These registers operate using no wait, one wait, and address hold.

Each register can be written in word units only and undefined values are written in bits that are written by byte or halfword instructions. Moreover, all bits are cleared (0) on reset input.

Signals that user logic uses in the interface to the outside are as follows.

| Signal Name   | I/O    | Function                                                                                  |

|---------------|--------|-------------------------------------------------------------------------------------------|

| VBCLK         | Input  | System clock                                                                              |

| VBRESZ        | Input  | System reset                                                                              |

| CSZ           | Input  | Select signal (one of VDCSZ7 to VDCSZ0)                                                   |

| VBA25 to VBA0 | Input  | Address input                                                                             |

| VBD31 to VBD0 | I/O    | Data input/output                                                                         |

| VBWRITE       | Input  | Write status                                                                              |

| VBWAIT        | Output | Wait response output                                                                      |

| VBAHLD        | Output | Address hold response output                                                              |

| VBLAST        | Output | Last response output                                                                      |

| BUNRI         | Input  | Normal/test mode selection input (used to make output high impedance status when testing) |

### Table 4-1. User Logic Interface Signals

### Figure 4-1. Example of Connecting User Logic to VSB

2. The user logic CSZ is an example when the CS2 area is used.

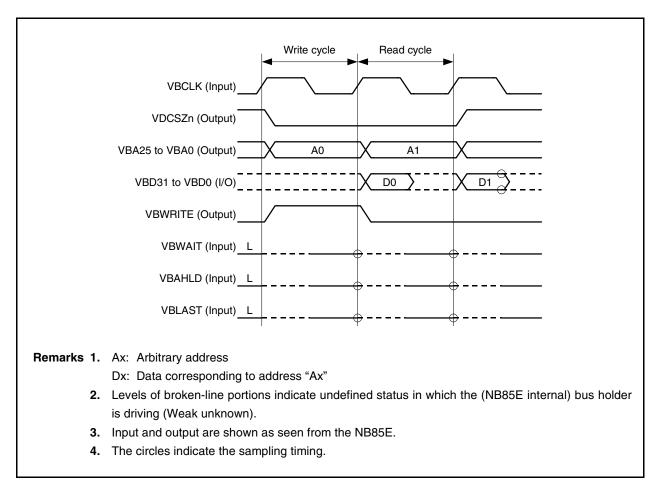

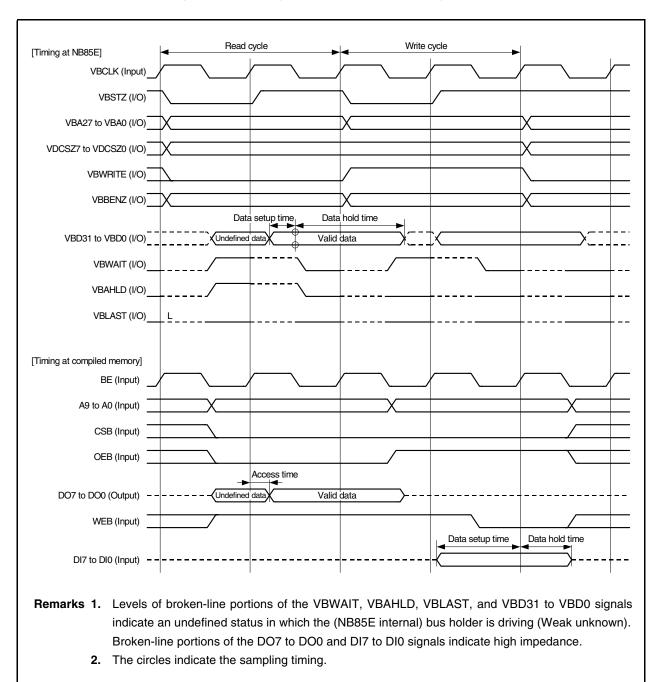

### 4.1.1 Overview of VSB operation

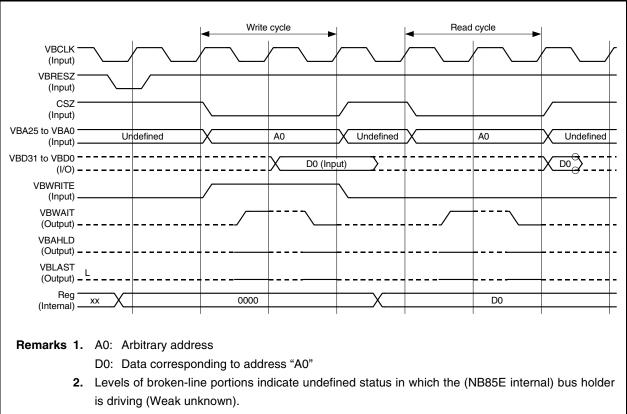

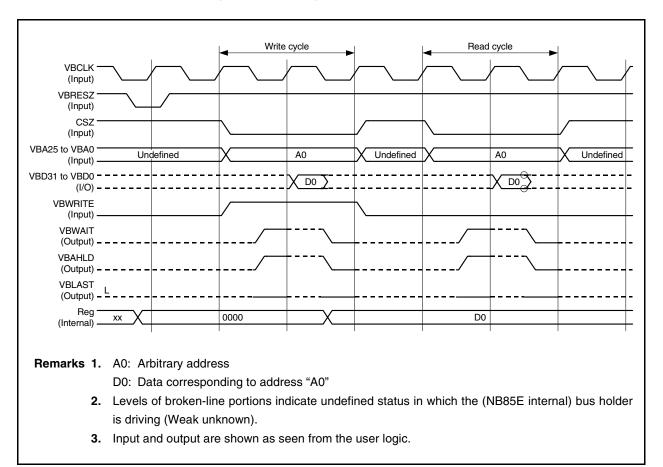

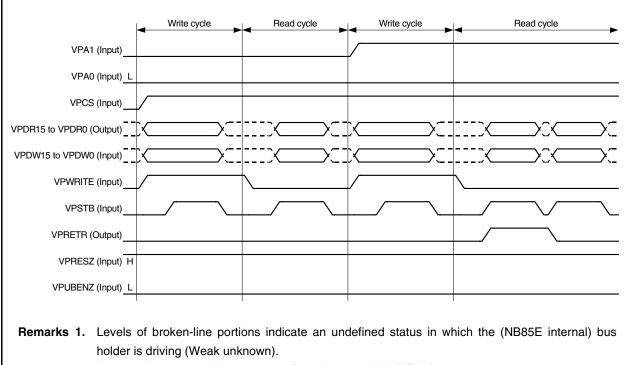

★ The basic VSB timing is 1-clock access, as shown in Figure 4-2. Also, the USB is a pipeline type bus that shifts data corresponding to addresses by one clock.

Timing adjustment is performed by inserting a wait cycle or address hold cycle as needed by manipulating the VBWAIT signal or VBAHLD signal.

### (1) For no wait (basic timing)

Output an address during one clock to perform a read or write during the next half clock.

The data bus (VBD31 to VBD0) drives only while the clock (VBCLK) is high level. While the clock is low level, it has undefined status in which the NB85E internal bus holder is driving (Weak unknown).

The VBWAIT, VBAHLD, and VBLAST signals drive only while the clock is low level. While the clock is high level, it has undefined status in which the NB85E internal bus holder is driving (Weak unknown).

Figure 4-2. VSB Timing (No Wait)

### (2) For one wait

Output an address in two clock periods to perform a read or write in the next half clock. By inserting a wait, a low-speed circuit can be connected.

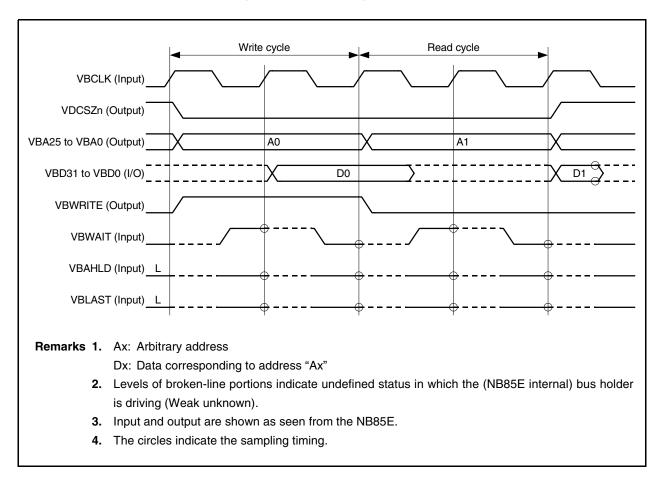

### (3) For address hold

\*

Similar to the case for one wait, two clock periods are used for one data transfer. The time interval from address output until data input or output is the same as for basic timing, but since the address is held until the end of the read cycle or write cycle, designing the interface circuit is easy.

### Figure 4-4. VSB Timing (Address Hold)

### 4.1.2 Circuit example

#### (1) For no wait

An example of connecting user logic that operates using no wait is shown below. In this example, reading or writing is performed at high speed, but when the VBCLK frequency is high, guaranteeing the data setup time or hold time is difficult.

```

module UDL_NOWAIT( VBCLK, VBRESZ, CSZ, VBA, VBD, VBWRITE, VBWAIT, VBAHLD, VBLAST, BUNRI );

input

VBCLK ;

input

VBRESZ ;

CSZ;

input

VBA ;

input [25:0]

VBD;

input [31:0]

VBWRITE ;

input

output

VBWAIT ;

output

VBAHLD;

output

VBLAST ;

BUNRI;

input

// nowait

reg [31:0]

reg1;

sel_reg_rd;

reg

reg

sel_reg_wr;

sel = (CSZ==1'b0 && VBA[7:2]==6'b0000_00) ? 1'b1 : 1'b0 ;

wire

// wait control

VBWAIT = (~VBCLK & sel) ? 1'b0 : 1'bZ ;

assign

VBAHLD = (~VBCLK & sel) ? 1'b0 : 1'bZ ;

assign

assign

VBLAST = (~VBCLK & sel) ? 1'b0 : 1'bZ ;

// read

VBD = ( sel_reg_rd & VBCLK & ~BUNRI ) ? reg1 : 32'hZZZZZZZ ;

assign

always @(VBCLK)

begin

if( VBCLK == 1'b0 )

begin

sel_reg_rd <= sel & ~VBWRITE ;</pre>

end

end

// write

always @( negedge VBCLK or negedge VBRESZ )

begin

if( ~VBRESZ)

reg1 <= 32'h00000000;

else

begin

if( sel_reg_wr )

reg1 <= VBD ;

sel_reg_wr <= sel & VBWRITE ;</pre>

end

end

endmodule

```

Figure 4-6. Timing Chart for No Wait

### (2) For insertion of one wait

An example of connecting user logic that operates using one wait is shown below. In this example, delaying the data read or write timing 1 clock makes it possible to have extra access time.

To increase the number of wait insertions, use a VBSTZ signal after extending it using a configuration like that of a shift register.

```

module UDL_1WAIT( VBCLK, VBRESZ, CSZ, VBA, VBD, VBSTZ, VBWRITE, VBWAIT, VBAHLD, VBLAST, BUNRI );

input

VBCLK ;

VBRESZ;

input

CSZ;

input

input [25:0]

VBA ;

VBD;

input [31:0]

VBSTZ;

input

input

VBWRITE ;

output

VBWAIT ;

output

VBAHLD;

output

VBLAST ;

input

BUNRI;

reg [31:0]

reg2;

reg

sel_reg_rd ;

sel_reg_wr;

reg

wire

sel = (CSZ==1'b0 && VBA[7:2]==6'b0000_01) ? 1'b1 : 1'b0 ;

// wait control

wa = ~VBSTZ ; // 1wait

wire

VBWAIT = (~VBCLK & sel) ? wa : 1'bZ ;

assign

assign

VBAHLD = (~VBCLK & sel) ? 1'b0 : 1'bZ ;

assign

VBLAST = (~VBCLK & sel) ? 1'b0 : 1'bZ ;

// read

VBD = ( sel_reg_rd & VBCLK & ~BUNRI) ? reg2 : 32'hZZZZZZZ ;

assign

always @(VBCLK)

begin

if( VBCLK == 1'b0 )

begin

sel_reg_rd <= sel & ~VBWRITE ;</pre>

end

end

// write

always @( negedge VBCLK or negedge VBRESZ )

begin

if(~VBRESZ)

reg2 <= 32'h0000000;

else

begin

if( sel_reg_wr )

reg2 <= VBD ;

sel_reg_wr <= sel & VBWRITE & ~wa;

end

end

endmodule

```

### Figure 4-8. Timing Chart for One Wait Insertion

3. Input and output are shown as seen from the user logic.

### (3) For address hold

An example of connecting user logic in which the address hold function is used is shown below. In this example, the address does not change in a data read or write cycle. Therefore, address latch is not necessary and the circuit can be simplified.

This also can be combined with wait insertion to connect long-access-time I/O.

#### Figure 4-9. Example of HDL Creation for User Logic in Which Address Hold Function Is Used

```

module UDL_AHLD( VBCLK, VBRESZ, CSZ, VBA, VBD, VBSTZ, VBWRITE, VBWAIT, VBAHLD, VBLAST, BUNRI ) ;

input

VBCLK ;

VBRESZ;

input

CSZ;

input

input [25:0]

VBA ;

VBD;

input [31:0]

VBSTZ;

input

input

VBWRITE ;

output

VBWAIT ;

output

VBAHLD;

output

VBLAST ;

input

BUNRI;

reg [31:0]

reg3;

wire

sel = (CSZ==1'b0 && VBA[7:2]==6'b0000_10) ? 1'b1 : 1'b0 ;

// wait control

wire

wa = ~VBSTZ ; // 1wait

VBWAIT = (~VBCLK & sel) ? wa : 1'bZ ;

assign

assign

VBAHLD = (~VBCLK & sel) ? wa : 1'bZ ;

VBLAST = (~VBCLK & sel) ? 1'b0 : 1'bZ ;

assign

// read

rea

VBSTZ_1E

always @(posedge VBCLK)

VBSTZ_1E = VBSTZ;

wire

sel_reg_rd = (sel & ~VBWRITE);

assign

VBD = ( sel_reg_rd & VBCLK & ~VBSTZ_1E & BUNRI ) ? reg3 : 32'hZZZZZZZ ;

// write

sel_reg_wr = (sel & VBWRITE & ~wa);

wire

always @( negedge VBCLK or negedge VBRESZ )

begin

if( ~VBRESZ )

reg3 <= 32'h00000000;

else

begin

if( sel_reg_wr )

reg3 <= VBD ;

end

end

endmodule

```

Figure 4-10. Timing Chart for Address Hold

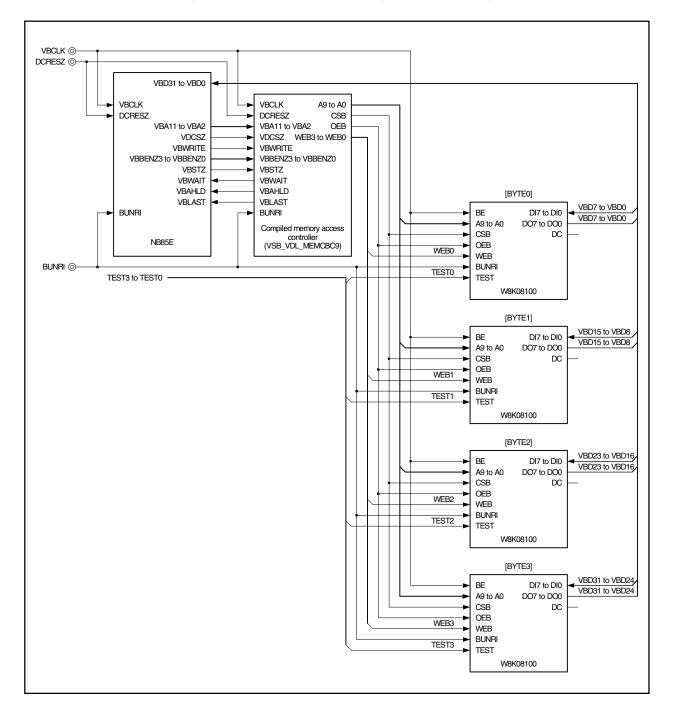

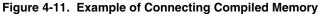

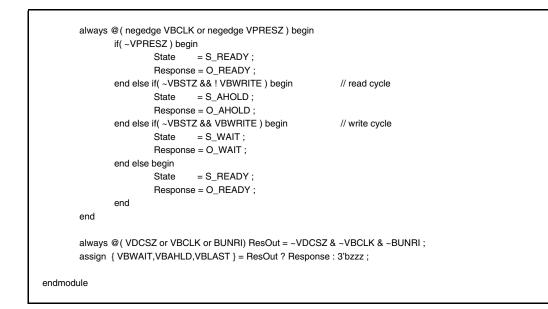

## 4.2 Connection of Compiled Memory

This section describes how to connect high-density synchronous 1-port RAM to the VSB without using a memory controller (MEMC).

Figure 4-11 shows a connection example, Figure 4-12 shows a timing chart, and Figure 4-13 shows an example of the creation of the HDL for the compiled memory access controller (VSB\_VDL\_MEMCBC9).

The following high-density synchronous 1-port RAM is used in this connection example.

- Macro block name: W8K08100

- Memory capacity (total): 4 KB (1024 words  $\times$  8 bits  $\times$  4<sup>Note</sup>)

- Operating frequency: 66 MHz

- **Note** The bit width of a high-density synchronous 1-port RAM can be selected from 1 to 32 bits in 1-bit units. The VSB data bus width is 32 bits, but it must be possible to access RAM in 8-bit units. Therefore, connect four RAMs with a bit width of 8 bits to configure a 32-bit width.

- For a normal access, the VSB performs a "pipeline method" bus operation, which shifts the data to an arbitrary address by one cycle. In the connection example in Figure 4-11, compiled memory access control is simplified by controlling the VBWAIT, VBAHLD, and VBLAST signals and responding to the NB85E in address hold status when reading and in wait status when writing.

Moreover, CB-9 Family VX/VM Type synchronous RAM has the following timing restrictions.

- Address change that uses the same timing as a clock input signal (BE) rise is prohibited

- CSB signal change when the clock input signal (BE) is high level is prohibited

To observe these restrictions, measures like the following are taken in the connection example in Figure 4-11.

- The clock (VBCLK) is input to the NB85E at the clock input pin (BE)

- An address that changes at the rise of VBCLK and CSB (VDCSZ) are used by latching at the fall of VBCLK

- OEB is used by latching so that it has the same timing as CSB

- For WEB, VBBENZ signal, which is the byte enable signal from the NB85E, is used under the conditions CSB = 0 and OEB = 1

Figure 4-12. Timing Chart for Compiled Memory Access

| VRWA                                             |                                                                                                                                                   | D,VBLAST,BUNF                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                        | B,VBBENZ,WEB,VBSTZ                                                    | , |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---|--|

| VDVVA                                            | II,VDANL                                                                                                                                          | D, VBLAST, BUINF                                                                                                                                                                                                                                                                                                                                                                                                     | ור <i>)</i> ,                                                                                                                                                                                                                                                                          |                                                                       |   |  |

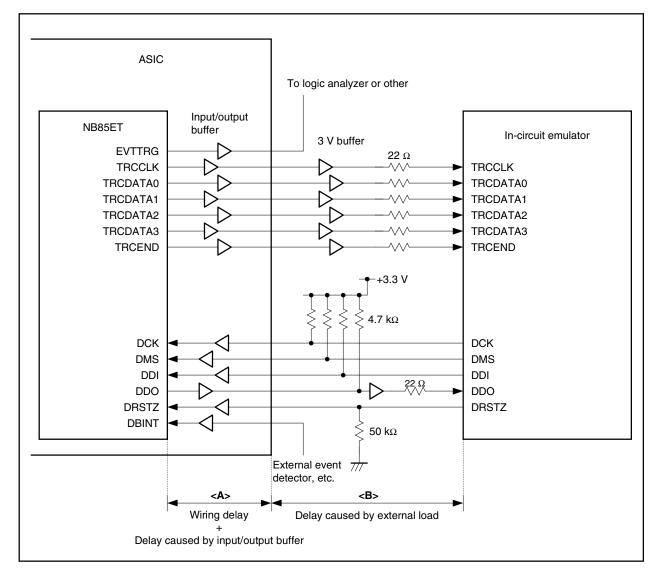

| input                                            |                                                                                                                                                   | VPRESZ;                                                                                                                                                                                                                                                                                                                                                                                                              | // Reset                                                                                                                                                                                                                                                                               |                                                                       |   |  |