# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

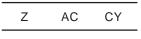

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **USER'S MANUAL**

# 78K/II SERIES

# **8-BIT SINGLE-CHIP MICROCOMPUTER**

**INSTRUCTIONS**

μPD78214 SUB-SERIES μPD78218A SUB-SERIES μPD78224 SUB-SERIES μPD78234 SUB-SERIES μPD78244 SUB-SERIES

> Document No. U10228EJ6V0UM00 (6th edition) (Previous No. IEU-1311) Date Published December 1995 P Printed in Japan

В

С

- **78K/II SERIES FEATURES**

- 78K/II SERIES PRODUCTS

- MEMORY SPACE

- REGISTERS

- INTERRUPT FUNCTIONS

- ADDRESSING

- INSTRUCTION SET

- INSTRUCTION DESCRIPTIONS

- DEVELOPMENT TOOLS

- BUILT-IN SOFTWARE

- INDEX OF INSTRUCTIONS (MNEMONICS CLASSIFIED BY FUNCTION)

- INDEX OF INSTRUCTIONS (MNEMONICS IN ALPHABETICAL ORDER)

- **REVISION HISTORY**

#### **Cautions on CMOS Devices**

#### (1) Countermeasures against static electricity for all MOSs

Caution When handling MOS devices, take care so that they are not electrostatically charged. Strong static electricity may cause dielectric breakdown in gates. When transporting or storing MOS devices, use conductive trays, magazine cases, shock absorbers, or metal cases that NEC uses for packaging and shipping. Be sure to ground MOS devices during assembling. Do not allow MOS devices to stand on plastic plates or do not touch pins.

Also handle boards on which MOS devices are mounted in the same way.

#### (2) CMOS-specific handling of unused input pins

#### Caution Hold CMOS devices at a fixed input level.

Unlike bipolar or NMOS devices, if a CMOS device is operated with no input, an intermediatelevel input may be caused by noise. This allows current to flow in the CMOS device, resulting in a malfunction. Use a pull-up or pull-down resistor to hold a fixed input level. Since unused pins may function as output pins at unexpected times, each unused pin should be separately connected to the V<sub>DD</sub> or GND pin through a resistor.

If handling of unused pins is documented, follow the instructions in the document.

#### (3) Statuses of all MOS devices at initialization

#### Caution The initial status of a MOS device is unpredictable when power is turned on.

Since characteristics of a MOS device are determined by the amount of ions implanted in molecules, the initial status cannot be determined in the manufacture process. NEC has no responsibility for the output statuses of pins, input and output settings, and the contents of registers at power on. However, NEC assures operation after reset and items for mode setting if they are defined.

When you turn on a device having a reset function, be sure to reset the device first.

MS-DOS and Windows are trademarks of Microsoft Corporation. IBM DOS, PC/AT, and PC DOS are trademarks of IBM Corporation. SPARCstation is a trademark of SPARC International, Inc. SunOS is a trademark of Sun Microsystems Corporation. HP9000 series 700 and HP-UX are trademarks of Hewlett-Packard Company. TRON is an abbreviation of The Realtime Operating system Nucleus. ITRON is an abbreviation of Industrial TRON. The export of these products from Japan is regulated by the Japanese government. The export of some or all of these products may be prohibited without governmental license. To export or re-export some or all of these products from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customer must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices in "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact NEC Sales Representative in advance.

Anti-radioactive design is not implemented in this product.

# **Major Changes**

| Page           | Description                                                                                                                                                                                                  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| p.3, 9, 18     | A disaster/crime prevention unit has been added as a special product in applications of the $\mu$ PD78214 sub-series, $\mu$ PD78218A sub-series, and $\mu$ PD78234 sub-series.                               |

| p.170 to p.177 | (Z, AC, and CY flags also do not change) has been added to the sentence, "If the second operand (cnt) is 0, no processing is performed." in [Description] of ROR, ROL, RORC, ROLC, SHR, SHL, SHRW, and SHLW. |

| p.223          | <ul> <li>Chapter 9</li> <li>Description related to the 3.5-inch 2HC has been added to IBM PC/AT.</li> <li>The HP9000 series 300 has been changed to the HP9000 series 700.</li> </ul>                        |

| p.237          | <ul> <li>The screen debugger of IBM PC/AT and the 5.25-inch 2HC of the device file have been<br/>already developed.</li> </ul>                                                                               |

| p.239          | • (4) OS for the IBM PC has been added.                                                                                                                                                                      |

| p.248          | <ul> <li>The Fuzzy inference debugger (FD78K/II) has been already developed.</li> </ul>                                                                                                                      |

| p.253          | Appendix C has been added.                                                                                                                                                                                   |

The mark \* shows major revised points.

# PREFACE

| Intended readership | This manual is intended for engineers who wish to gain an understanding of the functions of the 78K/II series <sup>Note</sup> and design application systems using a device in this series.                                                                                                                                                                                                                                                         |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | Note         78K/II series products:           μPD78214 sub-series         : μPD78212,78213,78214,78P214,78212(A),<br>78213(A), 78214(A), 78P214(A)           μPD78218A sub-series:         μPD78217A, 78218A, 78P218A, 78P218A, 78218A(A)           μPD78224 sub-series         : μPD78220, 78224, 78P224           μPD78234 sub-series         : μPD78233, 78234, 78237, 78238, 78P238           78234(A), 78238(A)         : μPD78244 sub-series |

| Purpose             | The purpose of this manual is to give users an understanding of the various instruction functions of the 78K/II series products.                                                                                                                                                                                                                                                                                                                    |

| Organization        | <ul> <li>This manual is broadly organized as follows:</li> <li>78K/II series features</li> <li>78K/II series products</li> <li>CPU functions</li> <li>Instruction set</li> <li>Description of instructions</li> <li>Development tools</li> <li>Built-in Software</li> </ul>                                                                                                                                                                         |

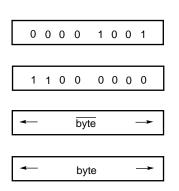

Using the manual When reading this manual, a general knowledge of electrical and logic circuits and microcomputers is necessary. • To check details of the function of an instruction when the mnemonic is known: -> Use the instruction indexes in Appendix A and B. • To check an instruction when the function is generally known but the mnemonic is not known: -> Find the mnemonic from Chapter 7, then check the function of the instruction in Chapter 8. • To get an overview of the function's of the 78K/II series instructions: -> Read the manual in accordance with the table of contents. • To learn about the hardware functions of the 78K/II series: -> Refer to the relevant separate User's Manual. µPD78214 Sub-Series User's Manual (IEM-1236) • μPD78218A Sub-Series User's Manual (IEU-1313) • μPD78224 Sub-Series User's Manual (IEM-1215) • μPD78234 Sub-Series Use's Manual (IEU-1290) • μPD78244 Sub-Series User's Manual (IEU-1316) To learn about the electrical specifications of the 78K/II series: -> Refer to the relevant separate Data Sheet. • To learn about application examples of the various functions of the 78K/II series products: -> Refer to the relevant separate Application Note. Legend Weighting in data notation: High-order digit on the left, low-order digit on the right Active-low notation : xxx (line over pin/signal name) : Explanation of text marked "Note" Note Caution : Information to be noted carefully Remarks : Supplementary information Numeric notations : Binary : xxxxB or xxxx Decimal : xxxx

Hexadecimal: xxxxH

#### **Related documentation**

# • Documents for entire 78K/II series

| Document             | Document number                            |          |

|----------------------|--------------------------------------------|----------|

| User's Manual, Inst  | This manual                                |          |

| SBI User's Manual    | EEU-1303                                   |          |

| Application Note     | Basic                                      | IEA-1220 |

|                      | Application                                | IEA-1282 |

|                      | Floating-Point Arthmetic Operation Program | IEA-1273 |

| Selection Guide      | IF-1160                                    |          |

| Instruction Applicat | _                                          |          |

| Instruction Set      | _                                          |          |

| Development Tools    | Selection Guide                            | EF-1114  |

# • Individual documents

# • µPD78214 sub-series

| Product name<br>Document        | μPD78212 | μPD78213 | μPD78214 | μPD78P214 |

|---------------------------------|----------|----------|----------|-----------|

| Brochure                        |          | -        | _        |           |

| Data Sheet                      |          | IC-2526  |          | IC-2481   |

| User's Manual, Hardware         |          | IEM-     | 1236     |           |

| Mode Register Application Table |          | _        | _        |           |

| Product name<br>Document        | μPD78212(A) | μPD78213(A) | μPD78214(A) | μPD78P214(A) |  |

|---------------------------------|-------------|-------------|-------------|--------------|--|

| Brochure                        |             | -           | _           |              |  |

| Data Sheet                      |             | IC-2831     | IC-3095     |              |  |

| User's Manual, Hardware         | IEU-1236    |             |             |              |  |

| Mode Register Application Table |             | _           | _           |              |  |

### • µPD78218A sub-series

| Product name<br>Document                       | μPD78217A | μPD78218A | μPD78P218A | μPD78P218A(A) |

|------------------------------------------------|-----------|-----------|------------|---------------|

| Brochure                                       |           | _         | -          |               |

| Data Sheet                                     | IC-2748   |           | IC-2722    | IC-3188       |

| User's Manual, Hardware                        |           | IEU-1     | 1313       |               |

| Special Function Register<br>Application Table |           | _         | -          |               |

# • $\mu$ PD78224 sub-series

| Product name<br>Document                       | μPD78220 | μPD78224 | μPD78P224 |

|------------------------------------------------|----------|----------|-----------|

| Brochure                                       |          | _        |           |

| Data Sheet                                     | IC-2     | 374      | IC-2475   |

| User's Manual, Hardware                        |          | IEU-1215 |           |

| Special Function Register<br>Application Table |          | _        |           |

# • $\mu$ PD78234A sub-series

| Product name<br>Document                       | μPD78233 | μPD78234 | μPD78237 | μPD78238 | μPD78P238 | μPD78234(A) | μPD78238(A) |

|------------------------------------------------|----------|----------|----------|----------|-----------|-------------|-------------|

| Brochure                                       |          |          |          | _        |           |             |             |

| Data Sheet                                     |          | IC-2     | 2476     |          | IC-2607   | IC-2        | 984         |

| User's Manual, Hardware                        | IEU-1290 |          |          |          |           |             |             |

| Special Function Register<br>Application Table |          |          |          | _        |           |             |             |

# • µPD78244 sub-series

| Product name<br>Document                       | μPD78243 | μPD78244 |

|------------------------------------------------|----------|----------|

| Brochure                                       | _        | _        |

| Data Sheet                                     | IC-2     | 774      |

| User's Manual, Hardware                        | IEU-     | 1316     |

| Special Function Register<br>Application Table | _        | _        |

# CONTENTS

| CHAPTER 1 | 78K/ | II SERI | ES FEATURES                            | 1  |

|-----------|------|---------|----------------------------------------|----|

|           | 1.1  | 78K/II  | SERIES PRODUCT EXPANSION DIAGRAM       | 2  |

|           | 1.2  | OUTLI   | NE OF µPD78214 SUB-SERIES PRODUCTS     | 3  |

|           |      | 1.2.1   | Features                               | 3  |

|           |      | 1.2.2   | Applications                           | 3  |

|           |      | 1.2.3   | Ordering Information and Quality Grade | 4  |

|           |      | 1.2.4   | Function Outline                       | 6  |

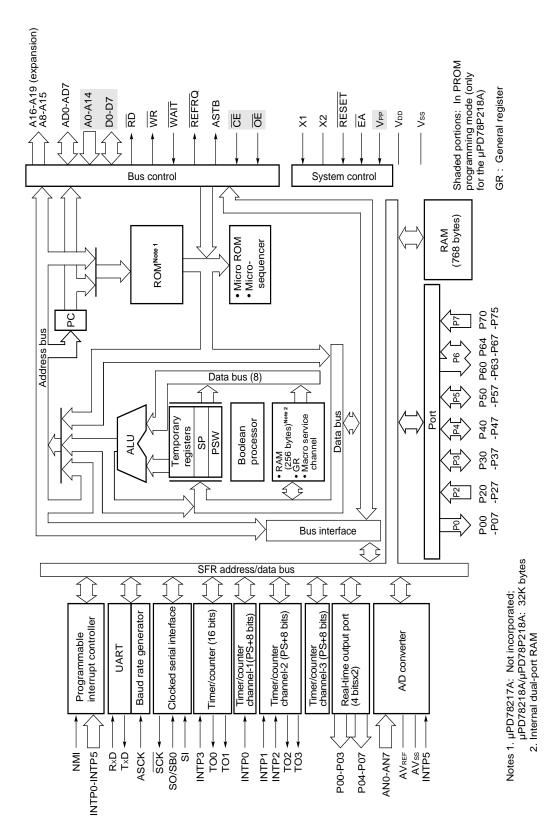

|           |      | 1.2.5   | Block Diagram                          | 8  |

|           | 1.3  | OUTLI   | NE OF µPD78218A SUB-SERIES PRODUCTS    | 9  |

|           |      | 1.3.1   | Features                               | 9  |

|           |      | 1.3.2   | Applications                           | 9  |

|           |      | 1.3.3   | Ordering Information and Quality Grade | 10 |

|           |      | 1.3.4   | Function Outline                       | 11 |

|           |      | 1.3.5   | Block Diagram                          | 13 |

|           | 1.4  | OUTLI   | NE OF µPD78224 SUB-SERIES PRODUCTS     | 14 |

|           |      | 1.4.1   | Features                               | 14 |

|           |      | 1.4.2   | Applications                           | 14 |

|           |      | 1.4.3   | Ordering Information and Quality Grade | 15 |

|           |      | 1.4.4   | Function Outline                       | 16 |

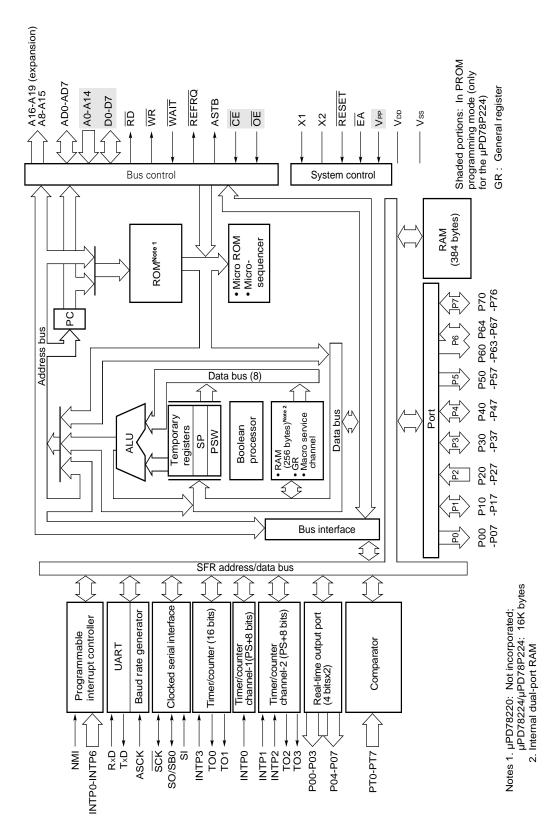

|           |      | 1.4.5   | Block Diagram                          | 17 |

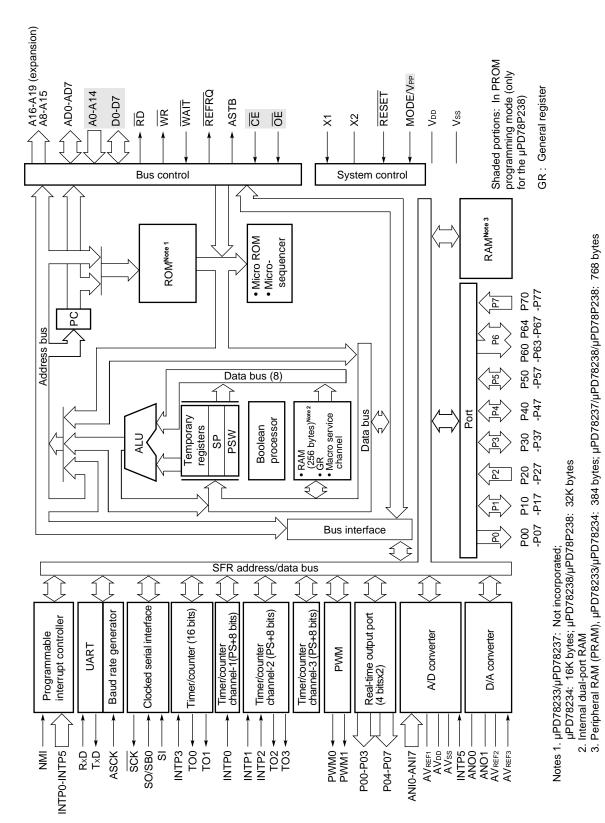

|           | 1.5  | OUTLI   | NE OF µPD78234 SUB-SERIES PRODUCTS     | 18 |

|           |      | 1.5.1   | Features                               | 18 |

|           |      | 1.5.2   | Applications                           | 18 |

|           |      | 1.5.3   | Ordering Information and Quality Grade | 19 |

|           |      | 1.5.4   | Function Outline                       | 21 |

|           |      | 1.5.5   | Block Diagram                          | 23 |

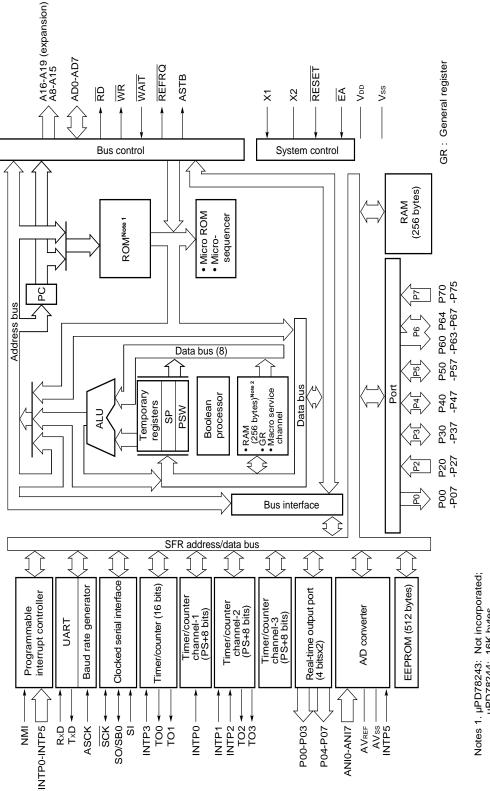

|           | 1.6  | OUTLI   | NE OF µPD78244 SUB-SERIES PRODUCTS     | 24 |

|           |      | 1.6.1   | Features                               | 24 |

|           |      | 1.6.2   | Applications                           | 24 |

|           |      | 1.6.3   | Ordering Information and Quality Grade | 25 |

|           |      | 1.6.4   | Function Outline                       | 26 |

|           |      | 1.6.5   | Block Diagram                          | 28 |

| CHAPTER 2 | 78K/ | II SERI | ES PRODUCTS                            | 29 |

| CHAPTER 3 | MEN  | IORY SPACE                                          | . 37 |

|-----------|------|-----------------------------------------------------|------|

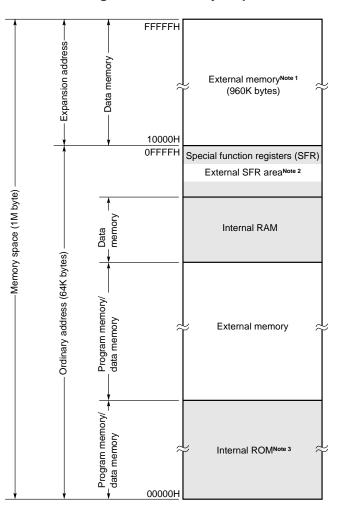

|           | 3.1  | MEMORY SPACE                                        | . 37 |

|           |      | 3.1.1 µPD78214 Sub-Series Memory Space              | . 38 |

|           |      | 3.1.2 µPD78218A Sub-Series Memory Space             | . 38 |

|           |      | 3.1.3 µPD78224 Sub-Series Memory Space              | . 39 |

|           |      | 3.1.4 µPD78234 Sub-Series Memory Space              | . 39 |

|           |      | 3.1.5 µPD78244 Sub-Series Memory Space              | . 40 |

|           | 3.2  | INTERNAL PROGRAM MEMORY AREA (INTERNAL ROM)         | 41   |

|           | 3.3  | VECTOR TABLE AREA                                   | . 42 |

|           | 3.4  | CALLT INSTRUCTION TABLE AREA                        | . 43 |

|           | 3.5  | CALLF INSTRUCTION ENTRY TABLE                       | . 43 |

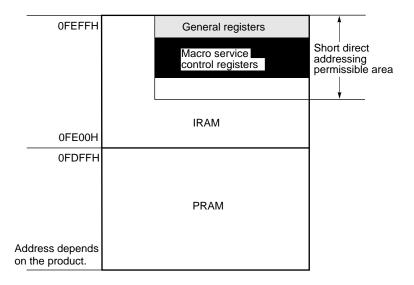

|           | 3.6  | INTERNAL RAM AREA                                   | . 44 |

|           | 3.7  | EEPROM AREA (µPD78244 SUB-SERIES ONLY)              | . 46 |

|           | 3.8  | SPECIAL FUNCTION REGISTER (SFR) AREA                | . 46 |

|           | 3.9  | EXTERNAL SFR AREA (EXCEPT $\mu$ PD78224 SUB-SERIES) | 46   |

|           | 3.10 | EXTERNAL MEMORY SPACE                               | . 47 |

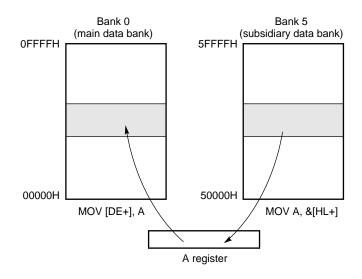

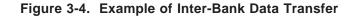

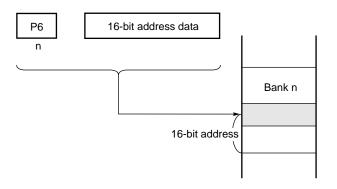

|           | 3.11 | EXTERNAL EXPANSION DATA MEMORY SPACE                | . 48 |

| CHAPTER 4 | REG  | ISTERS                                              | . 51 |

|           | 4.1  | CONTROL REGISTERS                                   | . 51 |

|           |      | 4.1.1 Program Counter (PC)                          | . 51 |

|           |      | 4.1.2 Program Status Word (PSW)                     | . 51 |

|           |      | 4.1.3 Stack Pointer (SP)                            | . 53 |

|           | 4.2  | GENERAL REGISTERS                                   | . 54 |

|           |      | 4.2.1 Configuration                                 | . 54 |

|           |      | 4.2.2 Functions                                     | . 56 |

|           | 4.3  | SPECIAL FUNCTION REGISTERS (SFR)                    | . 57 |

| CHAPTER 5 | INTE | ERRUPT FUNCTIONS                                    | . 59 |

|           | 5.1  | INTERRUPT REQUESTS                                  | . 60 |

|           |      | 5.1.1 Software Interrupt Requests                   | . 60 |

|           |      | 5.1.2 Nonmaskable Interrupt Requests                | . 60 |

|           |      | 5.1.3 Maskable Interrupt Requests                   | . 60 |

|           | 5.2  | MACRO SERVICE FUNCTION                              | . 61 |

| CHAPTER 6 | ADD  | RESSING                                             | . 63 |

|           | 6.1  | INSTRUCTION ADDRESS ADDRESSING                      | . 63 |

|           |      | 6.1.1 Relative Addressing                           | . 63 |

|           |      | 6.1.2 Immediate Addressing                          |      |

|           |      | 6.1.3 Table Indirect Addressing                     | . 65 |

|           |                             | 6.1.4  | Register Addressing                                  | 65  |  |  |

|-----------|-----------------------------|--------|------------------------------------------------------|-----|--|--|

|           | 6.2                         | OPER   | AND ADDRESS ADDRESSING                               | 66  |  |  |

|           |                             | 6.2.1  | Implied Addressing                                   | 66  |  |  |

|           |                             | 6.2.2  | Register Addressing                                  | 67  |  |  |

|           |                             | 6.2.3  | Immediate Addressing                                 | 69  |  |  |

|           |                             | 6.2.4  | Short Direct Addressing                              | 70  |  |  |

|           |                             | 6.2.5  | Special Function Register (SFR) Addressing           | 72  |  |  |

|           |                             | 6.2.6  | Stack Addressing                                     | 73  |  |  |

|           | 6.3                         | 1M-BY  | TE EXPANSION SPACE ADDRESSING                        | 74  |  |  |

|           |                             | 6.3.1  | Direct Addressing                                    | 74  |  |  |

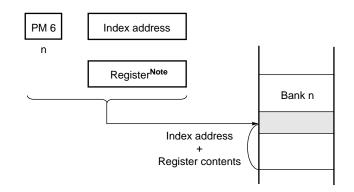

|           |                             | 6.3.2  | Register Indirect Addressing                         | 77  |  |  |

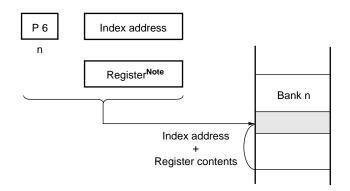

|           |                             | 6.3.3  | Based Addressing                                     | 80  |  |  |

|           |                             | 6.3.4  | Indexed Addressing                                   | 83  |  |  |

| CHAPTER 7 | INST                        | RUCTI  | ON SET                                               | 87  |  |  |

|           | 7.1                         | OPER   | ATIONS                                               | 87  |  |  |

|           |                             | 7.1.1  | Operand Representation Format and Description Method | 87  |  |  |

|           |                             | 7.1.2  | Operation Field                                      |     |  |  |

|           |                             | 7.1.3  | Flag Field                                           | 89  |  |  |

|           |                             | 7.1.4  | List of Basic Instruction Operations                 | 90  |  |  |

|           |                             | 7.1.5  | Instruction Lists for Each Addressing Type           | 102 |  |  |

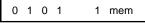

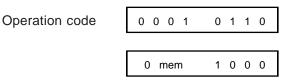

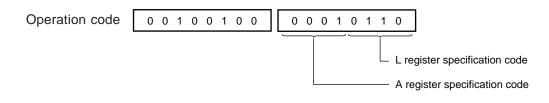

|           | 7.2                         | OPER   | ATION CODES                                          | 106 |  |  |

|           |                             | 7.2.1  | Operation Code Symbols                               | 106 |  |  |

|           |                             | 7.2.2  | Operation Code When mem, &mem, mem1 or &mem1 Is      |     |  |  |

|           |                             |        | Specified as Operand                                 | 108 |  |  |

|           |                             | 7.2.3  | List of Operation Codes                              | 109 |  |  |

|           | 7.3                         | INSTR  | UCTION CLOCK CYCLES                                  | 123 |  |  |

|           |                             | 7.3.1  | Clock Cycles Column                                  | 123 |  |  |

|           |                             | 7.3.2  | List of Clock Cycles                                 | 124 |  |  |

| CHAPTER 8 | INSTRUCTION DESCRIPTIONS 14 |        |                                                      |     |  |  |

|           | 8.1                         | 8-BIT  | DATA TRANSFER INSTRUCTIONS                           | 143 |  |  |

|           | 8.2                         | 16-BIT | DATA TRANSFER INSTRUCTIONS                           | 146 |  |  |

|           | 8.3                         | 8-BIT  | OPERATION INSTRUCTIONS                               | 148 |  |  |

|           | 8.4                         | 16-BIT | OPERATION INSTRUCTIONS                               | 157 |  |  |

|           | 8.5                         | MULT   | IPLICATION/DIVISION INSTRUCTIONS                     | 161 |  |  |

|           | 8.6                         | INCRE  | EMENT/DECREMENT INSTRUCTIONS                         | 164 |  |  |

|           | 8.7                         | SHIFT  | ROTATE INSTRUCTIONS                                  | 169 |  |  |

|           | 8.8                         | BCD A  | ADJUSTMENT INSTRUCTIONS                              | 180 |  |  |

|           | 8.9                         | BIT M  | ANIPULATION INSTRUCTIONS                             | 183 |  |  |

|            | 8.10 | 8.10 CALL/RETURN INSTRUCTIONS |                                                         |     |  |  |  |

|------------|------|-------------------------------|---------------------------------------------------------|-----|--|--|--|

|            | 8.11 | STACK                         | ( MANIPULATION INSTRUCTIONS                             | 199 |  |  |  |

|            | 8.12 | UNCO                          | NDITIONAL BRANCH INSTRUCTIONS                           | 205 |  |  |  |

|            | 8.13 | COND                          | ITIONAL BRANCH INSTRUCTIONS                             | 207 |  |  |  |

|            | 8.14 | CPU C                         | ONTROL INSTRUCTIONS                                     | 216 |  |  |  |

| CHAPTER 9  | DEV  | ELOPM                         | ENT TOOLS                                               | 223 |  |  |  |

|            | 9.1  | DEVEL                         | OPMENT TOOLS                                            | 223 |  |  |  |

|            | 9.2  | OUTLI                         | NE OF TOOLS                                             | 230 |  |  |  |

|            |      | 9.2.1                         | Hardware                                                | 230 |  |  |  |

|            |      | 9.2.2                         | Software                                                | 234 |  |  |  |

|            | 9.3  | UPGR/                         | ADING OTHER IN-CIRCUIT EMULATORS TO 78K/II SERIES LEVEL | 240 |  |  |  |

|            |      | 9.3.1                         | Upgrading to IE-78240-R-A Level                         | 240 |  |  |  |

|            |      | 9.3.2                         | Upgrading to IE-78240-R Level                           | 241 |  |  |  |

|            |      | 9.3.3                         | Upgrading to IE-78240-R-A Level                         | 242 |  |  |  |

|            |      | 9.3.4                         | Upgrading to IE-78230-R Level                           | 243 |  |  |  |

|            |      | 9.3.5                         | Upgrading to IE-78220-R Level                           | 244 |  |  |  |

|            |      | 9.3.6                         | Upgrading to IE-78210-R Level                           | 245 |  |  |  |

| CHAPTER 10 | BUIL | .T-IN SC                      | DFTWARE                                                 | 247 |  |  |  |

|            | 10.1 | REAL-                         | TIME OS                                                 | 247 |  |  |  |

|            | 10.2 | FUZZY                         | INFERENCE DEVELOPMENT SUPPORT SYSTEM                    | 248 |  |  |  |

| APPENDIX A | INDE | X OF IN                       | NSTRUCTIONS (MNEMONICS CLASSIFIED BY FUNCTION)          | 249 |  |  |  |

| APPENDIX B | INDE | X OF IN                       | NSTRUCTIONS (MNEMONICS IN ALPHABETICAL ORDER)           | 251 |  |  |  |

| APPENDIX C | REV  | ISION H                       | IISTORY                                                 | 253 |  |  |  |

\*

# LIST OF FIGURES

| Figure No. | Title                                    | Page |

|------------|------------------------------------------|------|

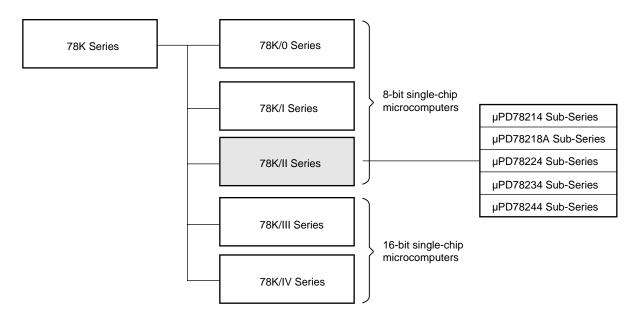

| 1-1        | 78K Series and 78K/II Series Composition | . 1  |

| 3-1        | Memory Map                               | 37   |

| 3-2        | Internal RAM Mapping                     | 45   |

| 3-3        | Example of Inter-Bank Data Transfer      | 49   |

| 3-4        | Example of Inter-Bank Data Transfer      | 50   |

| 4-1        | Program Counter Configuration            | 51   |

| 4-2        | Program Status Word Configuration        | 51   |

| 4-3        | Stack Pointer Configuration              | 53   |

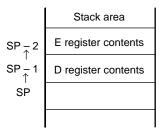

| 4-4        | Data Saved to Stack Area                 | 53   |

| 4-5        | Data Restored from Stack Area            | 53   |

| 4-6        | General Register Configuration           | 54   |

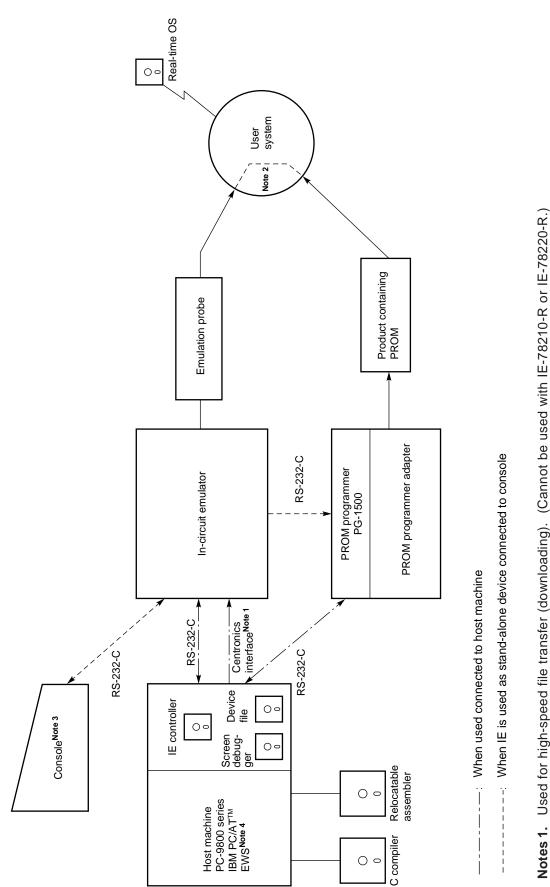

| 9-1        | Development Tool Configuration           | 224  |

# LIST OF TABLES

| Table No. | Title                                                              | Page |

|-----------|--------------------------------------------------------------------|------|

| 3-1       | Vector Table                                                       | 42   |

| 3-2       | Internal RAM Area in 78K/II Series Products                        | 44   |

| 3-3       | External Memory Space in 78K/II Series Products                    | 47   |

| 4-1       | Register Bank Selection                                            | 52   |

| 4-2       | Correspondence Between Function Names and Absolute Names           | 57   |

| 5-1       | Interrupt Request Servicing Modes                                  | 59   |

| 7-1       | 8-Bit Instructions for Each Addressing Type                        | 102  |

| 7-2       | 16-Bit Instructions for Each Addressing Type                       | 103  |

| 7-3       | Bit Manipulation Instructions for Each Addressing Type             | 104  |

| 7-4       | Call Instructions and Branch Instructions for Each Addressing Type | 105  |

| 7-5       | Operation Codes for mem, &mem                                      | 108  |

| 7-6       | Table of Instruction Execution Cycles                              | 136  |

| 9-1       | Development Tools (for Screen Debugger)                            | 226  |

| 9-2       | Development Tools (for In-Circuit Emulator Control Program)        | 228  |

# **CHAPTER 1 78K/II SERIES FEATURES**

The 78K series consists of the 5 series shown in Figure 1-1.

The 78K/II series is one of these 5 series, and comprises general-purpose type products with an on-chip 8-bits CPU.

These products have an instruction system and high-performance interrupt controller suited to control applications, and also incorporate a high-performance CPU provided with a 1M-byte data memory space.

The 78K/II series further comprises 5 sub-series (the  $\mu$ PD78214 sub-series,  $\mu$ PD78218A sub-series,  $\mu$ PD78224 sub-series,  $\mu$ PD78234 sub-series, and  $\mu$ PD78244 sub-series), allowing the most suitable sub-series to be selected for the particular application.

Each sub-series has the same CPU, with differences in the peripheral hardware only; consequently the entire instruction set is shared by all sub-series. The only difference between products within the same sub-series, moreover, is the size of memory.

\*

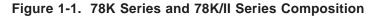

## 1.1 78K/II SERIES PRODUCT EXPANSION DIAGRAM

# 1.2 OUTLINE OF μPD78214 SUB-SERIES PRODUCTS (μPD78212, 78213, 78214, 78P214, 78212(A), 78213(A), 78214(A), 78P214(A))

#### 1.2.1 Features

- Instruction cycle : 333 ns (μPD78212, 78214, 78P214) 500 ns (μPD78213)

- On-chip memory

- ROM

| Mask ROM | : 16K bytes (μPD78214)      |

|----------|-----------------------------|

|          | 8K bytes (μPD78212)         |

|          | Not incorporated (µPD78213) |

| PROM     | : 16K bytes (μPD78P214)     |

| • RAM    | : 512 bytes                 |

- 384 bytes (µPD78212 only)

- I/O pins : 54 36 (μPD78213 only)

- On-chip 8-bit A/D converter (8 analog inputs)

- Timer/counters

- 16 bits x 1

- 8 bits x 3

- Serial interface

Independent on-chip UART and CSI

- μPD78212(A), 78213(A), 78214(A), 78P214(A):

"Special" quality grade products of μPD78212, 78213, 78214, 78P214

### 1.2.2 Applications

- Standard products : OA equipment including printers, typewriters, PPCs, facsimile, etc., electronic musical instruments, inverters, cameras, etc.

- Special products : Automotive electronic equipment, combustion control, disaster/crime prevention unit

# 1.2.3 Ordering Information and Quality Grade

# (1) Ordering information

| Ordering code         | Package                                         | On-chip ROM   |

|-----------------------|-------------------------------------------------|---------------|

| μPD78212CW-xxx        | 64-pin plastic shrink DIP (750 mil)             | Mask ROM      |

| μPD78212GC-xxx-AB8    | 64-pin plastic QFP (14 x 14 mm body)            | Mask ROM      |

| μPD78212GJ-xxx-5BJ    | 74-pin plastic QFP (20 x 20 mm body)            | Mask ROM      |

| μPD78213CW            | 64-pin plastic shrink DIP (750 mil)             | None          |

| μPD78213GC-AB8        | 64-pin plastic QFP (14 x 14 mm body)            | None          |

| μPD78213GJ            | 74-pin plastic QFP (20 x 20 mm body)            | None          |

| μPD78213GQ-36         | 64-pin plastic QUIP                             | None          |

| μPD78213L             | 68-pin plastic QFJ (🗆 950 mil)                  | None          |

| μPD78214CW-xxx        | 64-pin plastic shrink DIP (750 mil)             | Mask ROM      |

| μPD78214GC-xxx-AB8    | 64-pin plastic QFP (14 x 14 mm body)            | Mask ROM      |

| μPD78214GJ-xxx-5BJ    | 74-pin plastic QFP (20 x 20 mm body)            | Mask ROM      |

| μPD78214GQ-xxx-36     | 64-pin plastic QUIP                             | Mask ROM      |

| μPD78214L-xxx         | 68-pin plastic QFJ (🗆 950 mil)                  | Mask ROM      |

| μPD78P214CW           | 64-pin plastic shrink DIP (750 mil)             | One-time PROM |

| μPD78P214GC-AB8       | 64-pin plastic QFP (14 x 14 mm body)            | One-time PROM |

| μPD78P214GJ           | 74-pin plastic QFP (20 x 20 mm body)            | One-time PROM |

| μPD78P214GQ-36        | 64-pin plastic QUIP                             | One-time PROM |

| μPD78P214L            | 68-pin plastic QFJ (🗆 950 mil)                  | One-time PROM |

| μPD78P214DW           | 64-pin ceramic shrink DIP with window (750 mil) | EPROM         |

| μPD78212CW(A)-xxx     | 64-pin plastic shrink DIP (750 mil)             | Mask ROM      |

| μPD78212GC(A)-xxx-AB8 | 64-pin plastic QFP (14 x 14 mm body)            | Mask ROM      |

| μPD78213CW(A)         | 64-pin plastic shrink DIP (750 mil)             | None          |

| μPD78213GQ(A)-36      | 64-pin plastic QUIP                             | None          |

| μPD78214CW(A)-xxx     | 64-pin plastic shrink DIP (750 mil)             | Mask ROM      |

| μPD78214GC(A)-xxx-AB8 | 64-pin plastic QFP (14 x 14 mm body)            | Mask ROM      |

| μPD78214GJ(A)-xxx-5BJ | 74-pin plastic QFP (20 x 20 mm body)            | Mask ROM      |

| μPD78214GQ(A)-xxx-36  | 64-pin plastic QUIP                             | Mask ROM      |

| μPD78214L(A)-xxx      | 68-pin plastic QFJ (🗆 950 mil)                  | Mask ROM      |

| μPD78P214CW(A)        | 64-pin plastic shrink DIP (750 mil)             | One-time PROM |

| μPD78P214GC(A)-AB8    | 64-pin plastic QFP (14 x 14 mm body)            | One-time PROM |

**Remark** xxx is the ROM code number.

### (2) Quality grade

| Ordering code         | Package                                         | Quality grade |

|-----------------------|-------------------------------------------------|---------------|

| μPD78212CW-xxx        | 64-pin plastic shrink DIP (750 mil)             | Standard      |

| μPD78212GC-xxx-AB8    | 64-pin plastic QFP (14 x 14 mm body)            | Standard      |

| μPD78212GJ-xxx-5BJ    | 74-pin plastic QFP (20 x 20 mm body)            | Standard      |

| μPD78213CW            | 64-pin plastic shrink DIP (750 mil)             | Standard      |

| μPD78213GC-AB8        | 64-pin plastic QFP (14 x 14 mm body)            | Standard      |

| μPD78213GJ            | 74-pin plastic QFP (20 x 20 mm body)            | Standard      |

| μPD78213GQ-36         | 64-pin plastic QUIP                             | Standard      |

| μPD78213L             | 68-pin plastic QFJ (□ 950 mil)                  | Standard      |

| μPD78214CW-xxx        | 64-pin plastic shrink DIP (750 mil)             | Standard      |

| μPD78214GC-xxx-AB8    | 64-pin plastic QFP (14 x 14 mm body)            | Standard      |

| μPD78214GJ-xxx-5BJ    | 74-pin plastic QFP (20 x 20 mm body)            | Standard      |

| μPD78214GQ-xxx-36     | 64-pin plastic QUIP                             | Standard      |

| μPD78214L-xxx         | 68-pin plastic QFJ (🗆 950 mil)                  | Standard      |

| μPD78P214CW           | 64-pin plastic shrink DIP (750 mil)             | Standard      |

| μPD78P214GC-AB8       | 64-pin plastic QFP (14 x 14 mm body)            | Standard      |

| μPD78P214GJ           | 74-pin plastic QFP (20 x 20 mm body)            | Standard      |

| μPD78P214GQ-36        | 64-pin plastic QUIP                             | Standard      |

| μPD78P214L            | 68-pin plastic QFJ (□ 950 mil)                  | Standard      |

| μPD78P214DW           | 64-pin ceramic shrink DIP with window (750 mil) | Standard      |

| μPD78212CW(A)-xxx     | 64-pin plastic shrink DIP (750 mil)             | Special       |

| μPD78212GC(A)-xxx-AB8 | 64-pin plastic QFP (14 x 14 mm body)            | Special       |

| μPD78213CW(A)         | 64-pin plastic shrink DIP (750 mil)             | Special       |

| μPD78213GQ(A)-36      | 64-pin plastic QUIP                             | Special       |

| μPD78214CW(A)-xxx     | 64-pin plastic shrink DIP (750 mil)             | Special       |

| μPD78214GC(A)-xxx-AB8 | 64-pin plastic QFP (14 x 14 mm body)            | Special       |

| μPD78214GJ(A)-xxx-5BJ | 74-pin plastic QFP (20 x 20 mm body)            | Special       |

| μPD78214GQ(A)-xxx-36  | 64-pin plastic QUIP                             | Special       |

| μPD78214L(A)-xxx      | 68-pin plastic QFJ (□ 950 mil)                  | Special       |

| μPD78P214CW(A)        | 64-pin plastic shrink DIP (750 mil)             | Special       |

| μPD78P214GC(A)-AB8    | 64-pin plastic QFP (14 x 14 mm body)            | Special       |

|                       |                                                 |               |

**Remark** xxx is the ROM code number.

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

### 1.2.4 Function Outline

|                              |                          | Proc      | luct name              | μPD78212                             | μPD78214                                                 | μPD78P214                                                          | μPD78213                                                           |  |

|------------------------------|--------------------------|-----------|------------------------|--------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--|

| Item                         |                          |           |                        | 4                                    |                                                          | •                                                                  |                                                                    |  |

| Number of ba                 |                          |           |                        |                                      |                                                          | 65                                                                 |                                                                    |  |

| Minimum inst<br>(at 12 MHz o |                          | ition tim | e                      |                                      | 333 ns 5                                                 |                                                                    |                                                                    |  |

| On-chip memory capacity ROM  |                          |           | 8K bytes<br>(Mask ROM) | 16K bytes<br>(Mask ROM               |                                                          | ROM-less                                                           |                                                                    |  |

| RAM                          |                          |           | 384 bytes              |                                      | 512 byte                                                 |                                                                    |                                                                    |  |

| Memory spac                  | e                        |           |                        | Program: 64K                         | bytes, data:                                             | 1M byte                                                            |                                                                    |  |

| I/O pins                     |                          | Input     |                        |                                      |                                                          | 14                                                                 |                                                                    |  |

|                              |                          | Outpu     | t                      |                                      |                                                          | 12                                                                 |                                                                    |  |

|                              |                          | Input/    | output                 |                                      | 28                                                       |                                                                    | 10                                                                 |  |

|                              |                          | Total     |                        |                                      | 54                                                       |                                                                    | 36                                                                 |  |

| Additional                   | Pins with p              | ull-up re | sistor                 |                                      | 34                                                       |                                                                    | 16                                                                 |  |

| function<br>pins <b>Note</b> | LED direct drive outputs |           |                        | 16 —                                 |                                                          |                                                                    | —                                                                  |  |

| pine                         | Transistor of            | direct dr | ive outputs            | 8                                    |                                                          |                                                                    |                                                                    |  |

| ROM-less mo                  | de setting               |           |                        |                                      |                                                          |                                                                    | ROM-less<br>product                                                |  |

| Real-time out                | put ports                |           |                        | 4 bits x 2 or 8 bits x 1             |                                                          |                                                                    |                                                                    |  |

| General regis                | ters                     |           |                        | 8 bits x 8 x 4 banks (memory mapped) |                                                          |                                                                    |                                                                    |  |

| Timer/counte                 | "S                       |           |                        | 16-bit timer/co                      | Capt                                                     | er register x 1<br>ure register x 1<br>pare register x 2           | Pulse output<br>capability<br>( Toggle output<br>PWM/PPG<br>output |  |

|                              |                          |           |                        | 8-bit timer/cou                      | Capt<br>regis                                            | er register x 1<br>ure/compare<br>ster x 1<br>pare register x 1    | Pulse output<br>capability<br>(Real-time<br>output:<br>4 bits x 2  |  |

|                              |                          |           | 8-bit timer/cou        | Capt                                 | er register x 1<br>ure register x 1<br>pare register x 2 | Pulse output<br>capability<br>( Toggle output<br>PWM/PPG<br>output |                                                                    |  |

|                              |                          |           |                        | 8-bit timer/cou                      |                                                          | er register x 1<br>pare register x 1                               |                                                                    |  |

| Serial interface             |                          |           | UART                   |                                      | 1 channel (incor<br>dedicated baud i                     |                                                                    |                                                                    |  |

|                              |                          |           |                        | CSI (3-wire se                       | rial I/O, SBI) :                                         | 1 channel                                                          |                                                                    |  |

(Continued)

Note Additional function pins are included in the I/O pins.

| Product name<br>Item | μPD78212                                                                                                                                            | μPD78214                                              | μPD78P214                             | μPD78213 |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------|----------|--|

| A/D converter        | 8-bit resolution                                                                                                                                    | x 8 channels                                          |                                       |          |  |

| Interrupts           | 19 sources (7 external, 12 internal) + BRK instruction<br>2-level priority (programmable)<br>2 servicing modes (vectored interrupts, macro service) |                                                       |                                       |          |  |

| Instruction set      | 16-bit operation<br>Multiply/divide (8 bits x 8 bits, 16 bits/8 bits)<br>Bit manipulation<br>BCD adjustment, etc.                                   |                                                       |                                       |          |  |

| Package              | 64-pin plastic C<br>68-pin plastic C<br>64-pin plastic C<br>74-pin plastic C                                                                        | QFP (14 x 14 mm<br>QFP (20 x 20 mm<br>shrink DIP with | D78212)<br>(except μPD7821<br>n body) |          |  |

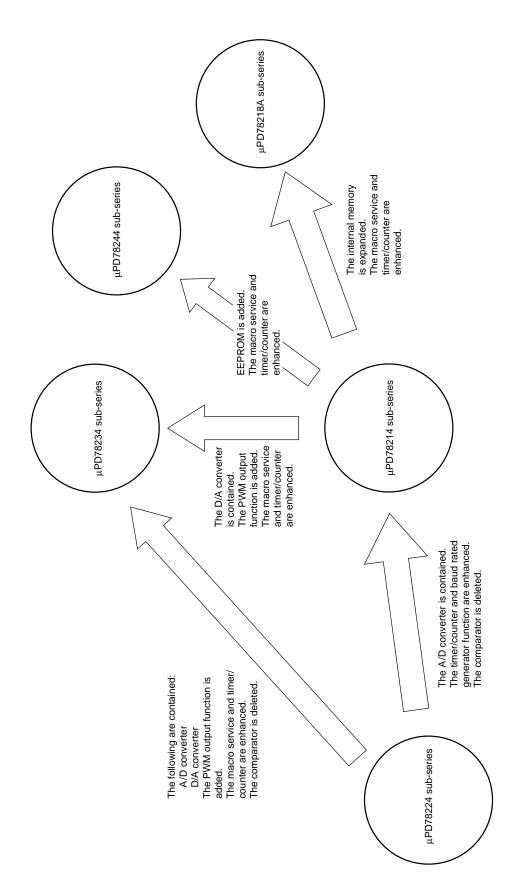

#### 1.2.5 Block Diagram

#### 1.3 OUTLINE OF μPD78218A SUB-SERIES PRODUCTS (μPD78217A, 78218A, 78P218A, 78218A(A))

#### 1.3.1 Features

- Instruction cycle : 333 ns (μPD78218A, 78P218A) 500 ns (µPD78217A)

- On-chip memory

- ROM Mask ROM : 32K bytes (µPD78218A) Not incorporated (µPD78217A) PROM : 32K bytes (µPD78P218A) RAM : 1024 bytes

- Upward compatible with μPD78214 series Enhanced macro service & timer/counters, increased on-chip memory size

- I/O pins : 54 36 (µPD78217A only)

- On-chip 8-bit A/D converter (8 analog inputs)

- Timer/counters

- 16 bits x 1

- 8 bits x 3

- Serial interface Independent on-chip UART and CSI

- μPD78218A(A) : "Special" quality grade product of μPD78218A.

#### 1.3.2 Applications

- Standard products: OA equipment including printers, typewriters, PPCs, facsimile, etc., electronic musical instruments, inverters, cameras, etc.

- Special products : Automotive electrical equipment, combustion control, disaster/crime prevention unit

\*

## 1.3.3 Ordering Information and Quality Grade

#### (1) Ordering information

| Ordering code          | Package                                         | On-chip ROM   |

|------------------------|-------------------------------------------------|---------------|

| μPD78217ACW            | 64-pin plastic shrink DIP (750 mil)             | None          |

| μPD78217AGC-AB8        | 64-pin plastic QFP (14 x 14 mm body)            | None          |

| μPD78218ACW-xxx        | 64-pin plastic shrink DIP (750 mil)             | Mask ROM      |

| μPD78218AGC-xxx-AB8    | 64-pin plastic QFP (14 x 14 mm body)            | Mask ROM      |

| μPD78P218ACW           | 64-pin plastic shrink DIP (750 mil)             | One-time PROM |

| μPD78P218AGC-AB8       | 64-pin plastic QFP (14 x 14 mm body)            | One-time PROM |

| μPD78P218ADW           | 64-pin ceramic shrink DIP with window (750 mil) | EPROM         |

| μPD78218ACW(A)-xxx     | 64-pin plastic shrink DIP (750 mil)             | Mask ROM      |

| μPD78218AGC(A)-xxx-AB8 | 64-pin plastic QFP (14 x 14 mm body)            | Mask ROM      |

**Remark** xxx is the ROM code number.

#### (2) Quality grade

| Ordering code          | Package                                         | Quality grade |

|------------------------|-------------------------------------------------|---------------|

| μPD78217ACW            | 64-pin plastic shrink DIP (750 mil)             | Standard      |

| μPD78217AGC-AB8        | 64-pin plastic QFP (14 x 14 mm body)            | Standard      |

|                        |                                                 |               |

| μPD78218ACW-xxx        | 64-pin plastic shrink DIP (750 mil)             | Standard      |

| μPD78218AGC-xxx-AB8    | 64-pin plastic QFP (14 x 14 mm body)            | Standard      |

|                        |                                                 |               |

| μPD78P218ACW           | 64-pin plastic shrink DIP (750 mil)             | Standard      |

| μPD78P218AGC-AB8       | 64-pin plastic QFP (14 x 14 mm body)            | Standard      |

| μPD78P218ADW           | 64-pin ceramic shrink DIP with window (750 mil) | Standard      |

|                        |                                                 |               |

| μPD78218ACW(A)-xxx     | 64-pin plastic shrink DIP (750 mil)             | Special       |

| µPD78218AGC(A)-xxx-AB8 | 64-pin plastic QFP (14 x 14 mm body)            | Special       |

**Remark** xxx is the ROM code number.

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

# 1.3.4 Function Outline

|                                                          |                 | Pro     | duct name  | μPD78218A                            | μPD78P218A                                                                                                                                                            | μPD78217A                           |  |  |

|----------------------------------------------------------|-----------------|---------|------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|

| Item                                                     |                 |         |            | μι Β/ο2 Ιολ                          |                                                                                                                                                                       | μιστοΣτητ                           |  |  |

| Number of basic instructions (mnemonics)                 |                 |         | emonics)   |                                      | 65                                                                                                                                                                    |                                     |  |  |

| Minimum instruction execution time (at 12 MHz operation) |                 |         |            | 333                                  | 3 ns                                                                                                                                                                  | 500 ns                              |  |  |

| On-chip memory capacity ROM                              |                 |         | ROM        | 32K bytes<br>(Mask ROM)              | 32K bytes (PROM)                                                                                                                                                      | ROM-less                            |  |  |

|                                                          |                 |         | RAM        |                                      | 1024 byte                                                                                                                                                             |                                     |  |  |

| Memory space                                             | ce              |         |            | Program: 64K byte                    | es, data: 1M byte                                                                                                                                                     |                                     |  |  |

| I/O pins                                                 |                 | Inpu    | t          |                                      | 14                                                                                                                                                                    |                                     |  |  |

|                                                          |                 | Outp    | out        |                                      | 12                                                                                                                                                                    |                                     |  |  |

|                                                          |                 | Inpu    | t/output   | 2                                    | 8                                                                                                                                                                     | 10                                  |  |  |

|                                                          |                 | Tota    | I          | 5                                    | 4                                                                                                                                                                     | 36                                  |  |  |

| Additional                                               | Pins with pull- | -up re  | sistor     | 3                                    | 4                                                                                                                                                                     | 16                                  |  |  |

| function<br>pins <b>Note</b>                             | LED direct dri  | ve ou   | tputs      | 1                                    | —                                                                                                                                                                     |                                     |  |  |

|                                                          | Transistor dire | ect dri | ve outputs | 8                                    |                                                                                                                                                                       |                                     |  |  |

| ROM-less m                                               | ode setting     |         |            | EA pin = low level   ROM-less pro    |                                                                                                                                                                       |                                     |  |  |

| Real-time ou                                             | tput ports      |         |            | 4 bits x 2 or 8 bits x 1             |                                                                                                                                                                       |                                     |  |  |

| General regi                                             | sters           |         |            | 8 bits x 8 x 4 banks (memory mapped) |                                                                                                                                                                       |                                     |  |  |

| Timer/counte                                             | ers             |         |            | 16-bit timer/counter                 | S Timer register x 1<br>Capture register x<br>Compare register                                                                                                        | c1 capability                       |  |  |

|                                                          |                 |         |            | 8-bit timer/counter                  | Timer register x 1<br>Capture/compare<br>register x 1<br>Compare register x 1<br>Compare register x 1Pulse output<br>capability<br>Real-time<br>output:<br>4 bits x 2 |                                     |  |  |

|                                                          |                 |         |            | 8-bit timer/counter :                | 2 Timer register x 1<br>Capture register x<br>Compare register                                                                                                        | (1 capability                       |  |  |

|                                                          |                 |         |            | 8-bit timer/counter                  | 3 Timer register x 1<br>Compare register                                                                                                                              |                                     |  |  |

| Serial interface                                         |                 |         |            | UART                                 | baud rate ge                                                                                                                                                          | ncorporating dedicated<br>enerator) |  |  |

|                                                          |                 |         |            | CSI (3-wire serial I/                | O, SBI): 1 channel                                                                                                                                                    |                                     |  |  |

(Continued)

**Note** Additional function pins are included in the I/O pins.

| Product nam     | μPD78218A                                                                                                                                          | μPD78P218A                                                                                                                                          | μPD78217A |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|

| A/D converter   | 8-bit resolution x 8                                                                                                                               | 8-bit resolution x 8 channels                                                                                                                       |           |  |  |  |

| Interrupts      | 2-level priority (pro                                                                                                                              | 19 sources (7 external, 12 internal) + BRK instruction<br>2-level priority (programmable)<br>2 servicing modes (vectored interrupts, macro service) |           |  |  |  |

| Instruction set | Bit manipulation                                                                                                                                   | Multiply/divide (8 bits x 8 bits, 16 bits/8 bits)                                                                                                   |           |  |  |  |

| Package         | 64-pin plastic shrink DIP (750 mil)<br>64-pin plastic QFP (14 x 14 mm body)<br>64-pin ceramic shrink DIP with window (750 mil):<br>μPD78P218A only |                                                                                                                                                     |           |  |  |  |

#### 1.3.5 Block Diagram

# 1.4 OUTLINE OF μPD78224 SUB-SERIES PRODUCTS (μPD78220, 78224, 78P224)

#### 1.4.1 Features

- Instruction cycle : 333 ns (μPD78224, 78P224) 500 ns (μPD78220)

- On-chip memory

- ROM

- Mask ROM : 16K bytes (μPD78224) Not incorporated (μPD78220) PROM : 16K bytes (μPD78P224)

- RAM : 640 bytes

- I/O pins : 71

53 (μPD78220 only)

- Comparator : 4-bit resolution x 8

- Timer/counters

- 16 bits x 1

- 8 bits x 2

- Serial interface Independent on-chip UART and CSI

#### 1.4.2 Applications

Areas handling a large amount of data such as kanji character generators, typewriters, hand-held word processors, ECRs, etc.

# 1.4.3 Ordering Information and Quality Grade

#### (1) Ordering information

| Ordering code      | Package                              | On-chip ROM   |

|--------------------|--------------------------------------|---------------|

| μPD78220GJ-5BG     | 94-pin plastic QFP (20 x 20mm body)  | None          |

| μPD78220L          | 84-pin plastic QFJ (🗆 1150 mil)      | None          |

|                    |                                      |               |

| μPD78224GJ-xxx-5BG | 94-pin plastic QFJ (20 x 20 mm body) | Mask ROM      |

| μPD78224L-xxx      | 84-pin plastic QFJ (🗆 1150 mil)      | Mask ROM      |

|                    |                                      |               |

| μPD78P224GJ-5BG    | 94-pin plastic QFP (20 x 20 mm body) | One-time PROM |

| μPD78P224L         | 84-pin plastic QFJ (🗆 1150 mil)      | One-time PROM |

Remark xxx is the ROM code number.

#### (2) Quality grade

| Ordering code      | Package                              | Quality grade |

|--------------------|--------------------------------------|---------------|

| μPD78220GJ-5BG     | 94-pin plastic QFP (20 x 20 mm body) | Standard      |

| μPD78220L          | 84-pin plastic QFJ (🗆 1150 mil)      | Standard      |

|                    |                                      |               |

| μPD78224GJ-xxx-5BG | 94-pin plastic QFP (20 x 20 mm body) | Standard      |

| μPD78224L-xxx      | 84-pin plastic QFJ (□ 1150 mil)      | Standard      |

|                    |                                      |               |

| μPD78P224GJ-5BG    | 94-pin plastic QFP (20 x 20 mm body) | Standard      |

| μPD78P224L         | 84-pin plastic QFJ (🗆 1150 mil)      | Standard      |

**Remark** xxx is the ROM code number.

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

### 1.4.4 Function Outline

|                                                             | Pro    | duct name                                                                                                                                          |                                                                           |                                                                                                      |                                  |

|-------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------|

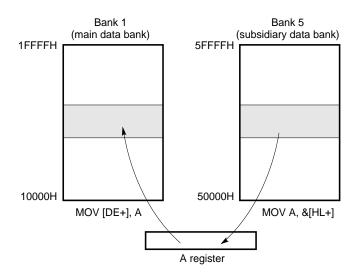

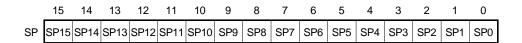

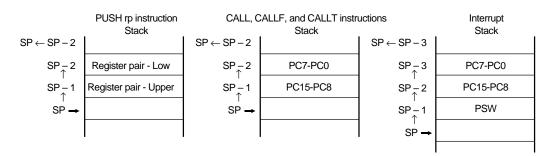

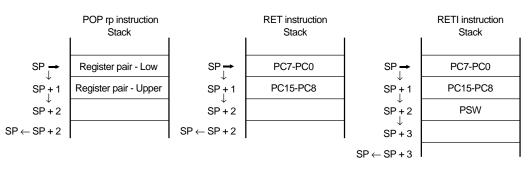

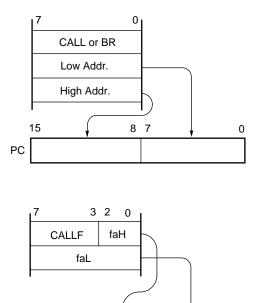

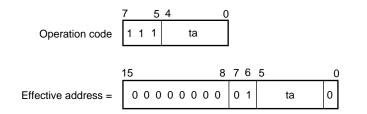

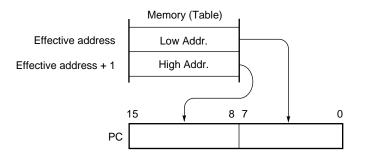

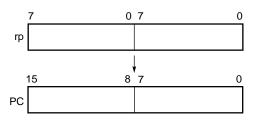

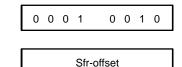

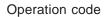

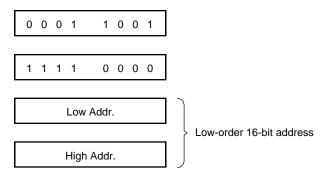

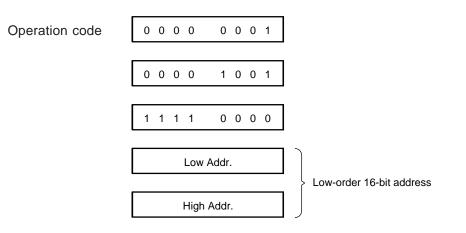

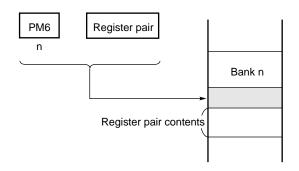

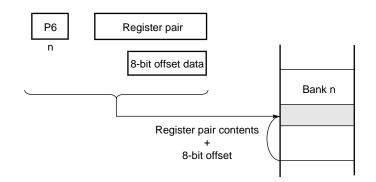

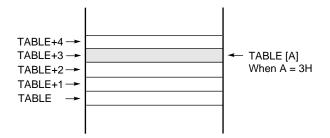

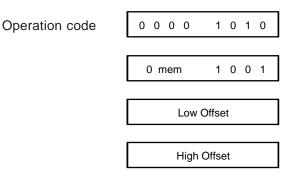

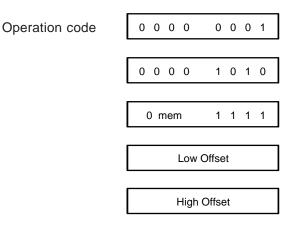

| Item                                                        |        |                                                                                                                                                    | μPD78224                                                                  | μPD78P224                                                                                            | μPD78220                         |