### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

### DATA SHEET

## RENESAS

## MOS INTEGRATED CIRCUIT Phase-out/Discontinued µPD9971

### SOUND GENERATOR LSI FOR RINGER MELODIES FOR MOBILE PHONES THAT ARE EQUIPPED WITH 3D POSITIONING SURROUND FUNCTIONS

### DESCRIPTION

The  $\mu$ PD9971 is a sound generator LSI for ringer melodies for mobile phones that are equipped with 3D positioning surround functions.

### FEATURES

- PCM sound generation method provides realistic sound reproduction

- Contains 32 kHz sampling Wavetable, it include 128 GM tone and 47 drum set and 32 effect tone.

- A richer tone is achieved by using 2 Wave a tone.

- The wave and the parameter can be downloaded, and the sound-making not limited to a fixed tone is possible.

- Can play up to four melodies because of four MIDI<sup>™</sup> ports that are embedded in the sound generator core.

- The port for a real-time control of MIDI that assumes karaoke and the JAVA® application program is installed.

- Contains a digital parametric equalizer for equalizing speakers.

- The function for a low output of the level to always enable the reproduction in the vicinity of the maximum volume is built into.

- Various sound effects (pitch pipe bend, vibrato, Delay, reverberation, chorus, Doppra, and compressor) can be achieved.

- Supports MOBILE-XMF.

- Contains real-time-processing 3D positioning surround functions

- The effect of the sound that the sound source moves three-dimensionally by the digital signal processing can be achieved.

- The stereophonic effect with the extension can be obtained by the digital signal processing.

- The programmable solid sound parameter is installed, and the best setting is possible in the case and the speaker arrangement etc. of the cellular phone.

- When the headphone is used, the stereophonic effect can be obtained.

- Includes a high-performance D/A converter with 16-bit resolution

- Supports five sampling frequency (fs) modes: 8 kHz, 16 kHz, 32 kHz, 44.1 kHz, and 48 kHz

- Provides an audio serial I/O interface (16 bits).

- The serial data input frequency is variable from 32 fs to 64 fs (during slave mode).

- Supported formats are right-justified, left-justified, and IIS

- Provides an external serial input/output interface for the sound generator

- Provides stereo line output for audio

- Supports 8-bit parallel interface or 3 or 4-wire serial interface (SPI).

- Output control functions for vibration and LED.

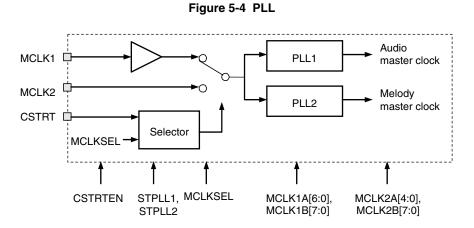

- Built-in PLL, so various types of input clocks can be supported.

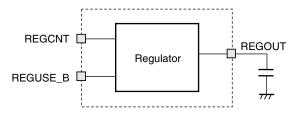

- Contains a regulator for digital power supply (DVDD).

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

• Power supply voltages

| I/O power supply (EVDD):                      | 1.7 to 3.3 V                                          |

|-----------------------------------------------|-------------------------------------------------------|

| Power supply for PLL (PLLVDD):                | 2.7 to 3.3 V                                          |

| Analog power supply (AVDD):                   | 2.7 to 3.3 V                                          |

| Power supply for regulators (REGVDD):         | 2.7 to 3.3 V                                          |

| Digital power supply (DVDD):                  | Internal regulators (External voltage can be applied) |

| Operating ambient temperatures: -20 to +85 °C | C                                                     |

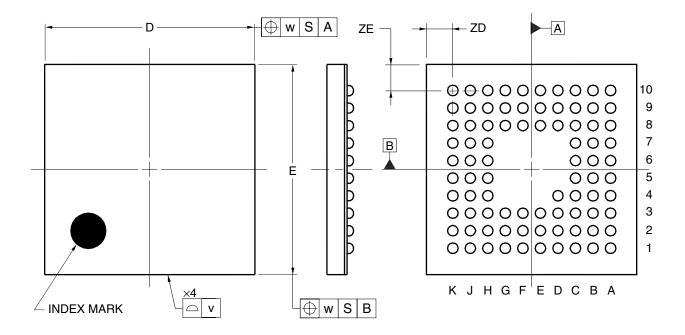

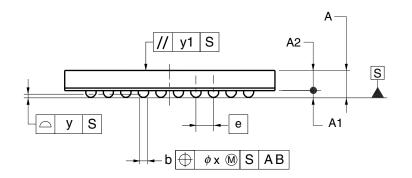

• 85-pin tape FBGA package (Body size: 6 × 6 mm, Ball pitch: 0.5 mm)

### **ORDERING INFORMATION**

| Part number     | Package                           |

|-----------------|-----------------------------------|

| μPD9971F9-BA3-A | 85-pin tape FBGA ( $6 \times 6$ ) |

Remark A lead-free product.

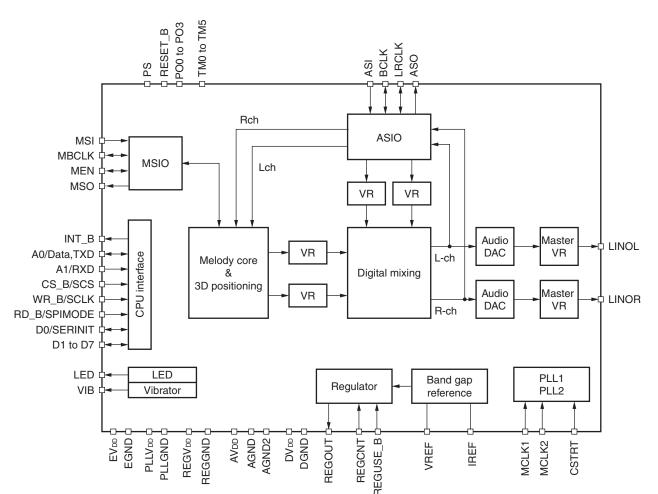

### **BLOCK DIAGRAM**

NEC

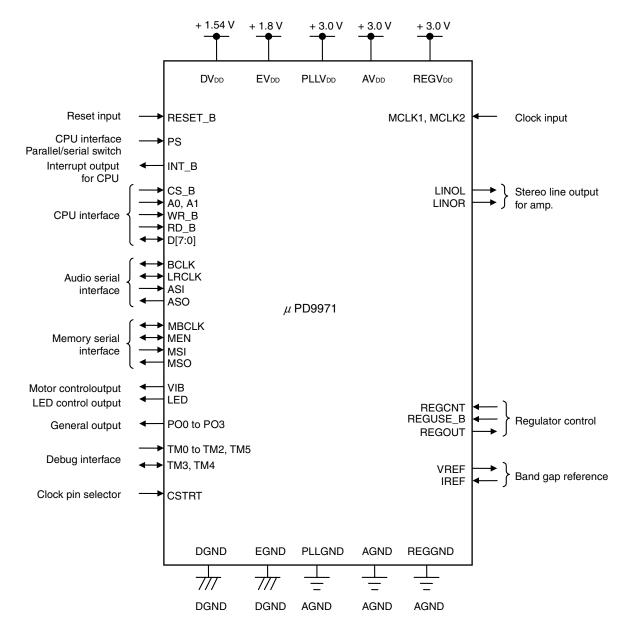

(Top View)

### **PIN CONFIGURATION**

• 85-pin tape FBGA ( $6 \times 6$ ) μPD9971F9-BA3-A

| (Bottom View)                        | _                                               | (Top View) |

|--------------------------------------|-------------------------------------------------|------------|

| 000000000000000000000000000000000000 | 10<br>9<br>8<br>7<br>6<br>5<br>4<br>3<br>2<br>1 | $\bigcirc$ |

| K J H G F E D C B A                  | <b>_</b>                                        | /          |

|                                      | Ĺ                                               |            |

| Pin<br>No. | Pin Name            | Pin<br>No. | Pin Name    | Pin<br>No. | Pin Name     | Pin<br>No. | Pin Name             |

|------------|---------------------|------------|-------------|------------|--------------|------------|----------------------|

| 1A         | Shorted with 1K pin | 3C         | MSO         | 6B         | PS           | 9B         | N.C                  |

| 1B         | N.C                 | 3D         | N.C         | 6C         | TM5          | 9C         | EVDD                 |

| 1C         | LINOL               | 3E         | N.C         | 6H         | PO1          | 9D         | VIB                  |

| 1D         | AGND                | 3F         | MCLK2       | 6J         | CS_B/SCS     | 9E         | RESET_B              |

| 1E         | AVDD                | 3G         | REGGND      | 6K         | A0/Data, TXD | 9F         | D7                   |

| 1F         | LINOR               | ЗH         | REGVDD      | 7A         | ASI          | 9G         | D5                   |

| 1G         | AGND2               | ЗJ         | REGOUT      | 7B         | ASO          | 9H         | D3                   |

| 1H         | PLLGND              | ЗК         | REGCNT      | 7C         | DVDD         | 9J         | N.C                  |

| 1J         | REGVDD              | 4A         | MSI         | 7H         | DVDD         | 9K         | N.C                  |

| 1K         | Shorted with 1A pin | 4B         | TM4         | 7J         | RD_B/SPIMODE | 10A        | Shorted with 10K pin |

| 2A         | N.C                 | 4C         | DVDD        | 7K         | WR_B/SCLK    | 10B        | N.C                  |

| 2B         | N.C                 | 4D         | N.C (index) | 8A         | LRCLK        | 10C        | LED                  |

| 2C         | ТМО                 | 4H         | REGUSE_B    | 8B         | BCLK         | 10D        | DVDD                 |

| 2D         | IREF                | 4J         | PO3         | 8C         | CSTRT        | 10E        | INT_B                |

| 2E         | VREF                | 4K         | PO2         | 8D         | N.C          | 10F        | D6                   |

| 2F         | TM1                 | 5A         | MEN         | 8E         | N.C          | 10G        | D4                   |

| 2G         | PLLVDD              | 5B         | MBCLK       | 8F         | DVDD         | 10H        | D2                   |

| 2H         | MCLK1               | 5C         | DGND        | 8G         | EGND         | 10J        | N.C                  |

| 2J         | N.C                 | 5H         | PO0         | 8H         | EVDD         | 10K        | Shorted with 10A pin |

| 2K         | REGOUT              | 5J         | A1/RXD      | 8J         | D1           |            |                      |

| ЗA         | ТМЗ                 | 5K         | DGND        | 8K         | D0/SERINIT   |            |                      |

| 3B         | TM2                 | 6A         | EGND        | 9A         | N.C          | 7          |                      |

Remark N.C: Reserved for future use. Leave this pin open.

### **PIN NAME**

| A0, A1:   | Address                                 | MSO:         | Data Output for Melody Core          |

|-----------|-----------------------------------------|--------------|--------------------------------------|

| AGND:     | Ground for Analog Block                 | N.C.:        | No Connection                        |

| AGND2:    | Ground for Analog Block                 | N.C.(index): | No Connection                        |

| ASI:      | Audio Serial Data Input                 | PLLGND:      | Ground for PLL                       |

| ASO:      | Audio Serial Data Output                | PLLVDD:      | Power Supply for PLL                 |

| AVDD:     | Power Supply for Analog Block           | PO0 to PO3:  | Peripheral Output                    |

| BCLK:     | Bit Clock Input/Output                  | PS:          | Parallel/Serial Interface Select     |

| CS_B:     | Chip Select                             | RD_B:        | Read                                 |

| CSTRT:    | Clock Select Signal Input from External | REGCNT:      | Regulator Control                    |

| D0 to D7: | Data Bus                                | REGGND:      | Ground for Regulator                 |

| Data:     | Data                                    | REGOUT:      | Regulator Output                     |

| DGND:     | Ground for Digital Block                | REGUSE_B:    | Regulator Block Enable Signal Input  |

| DVDD:     | Power Supply for Digital Block          | REGVDD:      | Power Supply for Regulator           |

| EGND:     | Ground for I/O Pins                     | RESET_B:     | Reset                                |

| EVDD:     | Power Supply for I/O Pins               | RXD:         | Serial Data Input                    |

| INT_B:    | Interruption                            | SCLK:        | Clock for Serial I/F                 |

| IREF:     | Current Reference for Analog Block      | SCS:         | Chip Select Input for Serial I/F     |

| LED:      | LED Control Output                      | SERINIT:     | Initialization Signal for Serial I/F |

| LINOL:    | Line Out (L-ch)                         | SPIMODE:     | SPI Mode Select                      |

| LINOR:    | Line Out (R-ch)                         | TM0 to TM2:  | Test Mode Input                      |

| LRCLK:    | Left Right Clock Input/Output           | TM3, TM4:    | Test Mode I/O                        |

| MBCLK:    | Bit Clock for Melody Core               | TM5:         | Test Mode Input                      |

| MCLK1:    | Clock Input                             | TXD:         | Serial Data Output                   |

| MCLK2:    | Clock Input                             | VIB:         | Vibration Control Output             |

| MEN:      | Frame Clock for Melody Core             | VREF:        | Voltage Reference for Analog Block   |

| MSI:      | Data Input for Melody Core              | WR_B:        | Write                                |

### CONTENTS

| 1. FUNCTIONS                                                                                                  | 9  |

|---------------------------------------------------------------------------------------------------------------|----|

| 1.1 General Descriptions of Functions                                                                         |    |

| 1.2 General Descriptions of Circuits                                                                          |    |

|                                                                                                               |    |

| 2. PINS FUNCTIONS                                                                                             | 10 |

| 2.1 Pin Configuration                                                                                         | 10 |

| 2.2 Recommended External Circuit                                                                              | 11 |

| 2.3 Descriptions of Pin Functions                                                                             | 12 |

| 2.4 Connection of Unused Pins                                                                                 | 17 |

| 2.5 Pin Statuses                                                                                              | 18 |

|                                                                                                               |    |

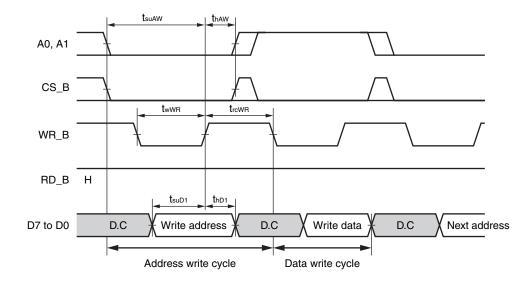

| 3. CPU INTERFACE                                                                                              |    |

| 3.1 Parallel Host CPU Interface                                                                               | 21 |

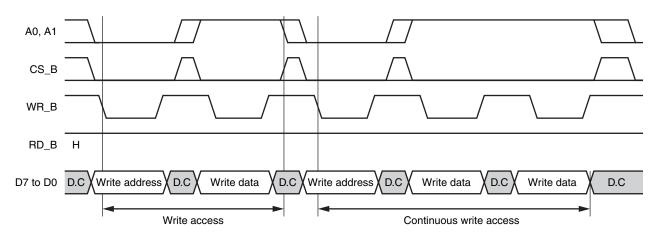

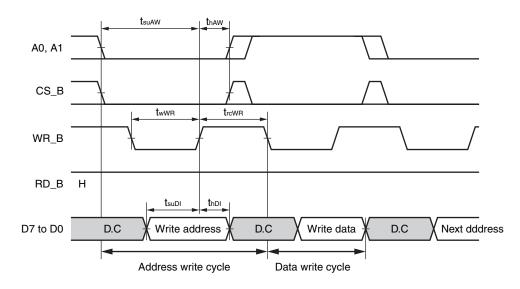

| 3.1.1 Write access                                                                                            | 21 |

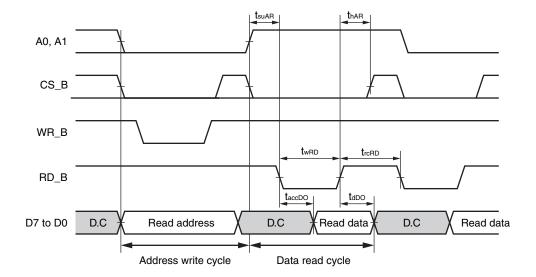

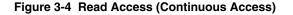

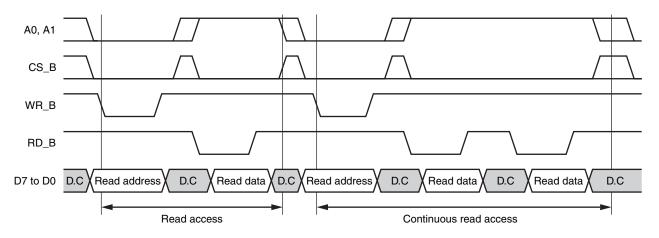

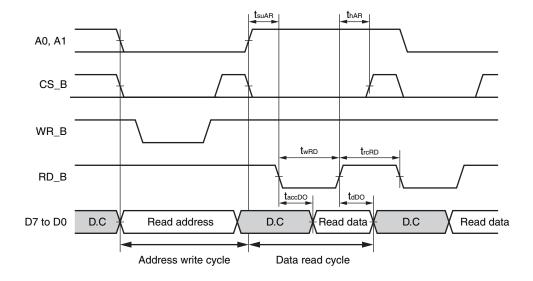

| 3.1.2 Read access                                                                                             | 23 |

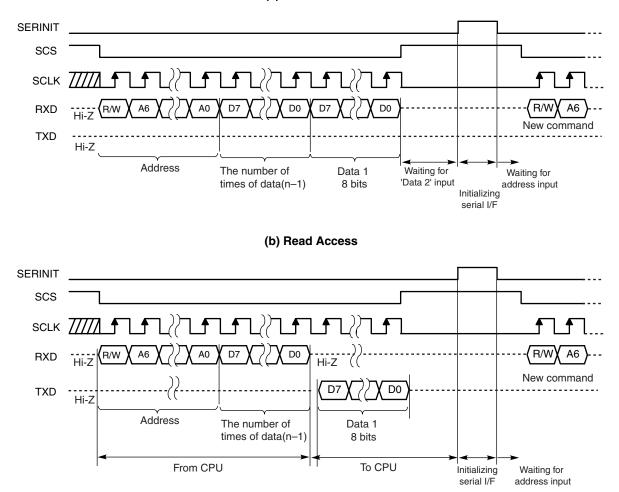

| 3.2 Serial Host Interface                                                                                     | 24 |

| 3.2.1 Pin functions                                                                                           | 24 |

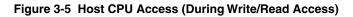

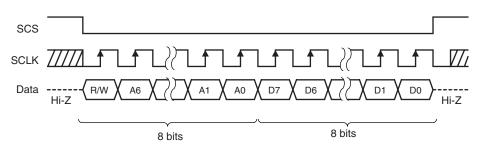

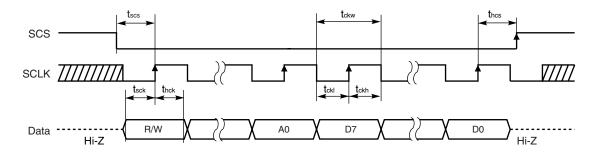

| 3.2.2 Serial formats                                                                                          | 25 |

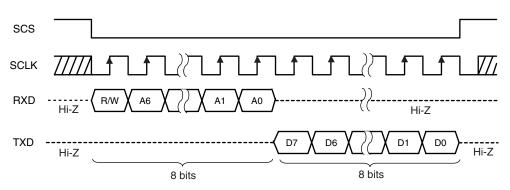

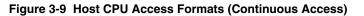

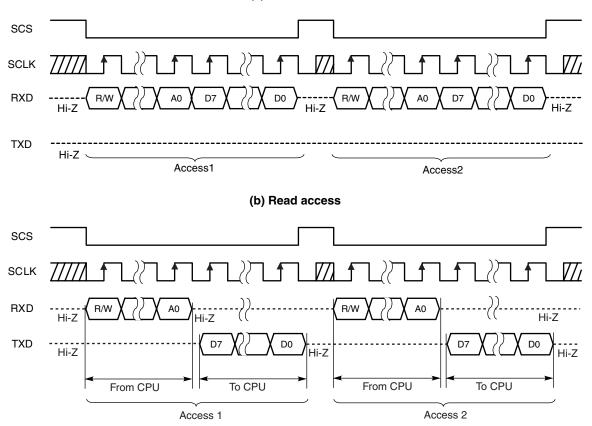

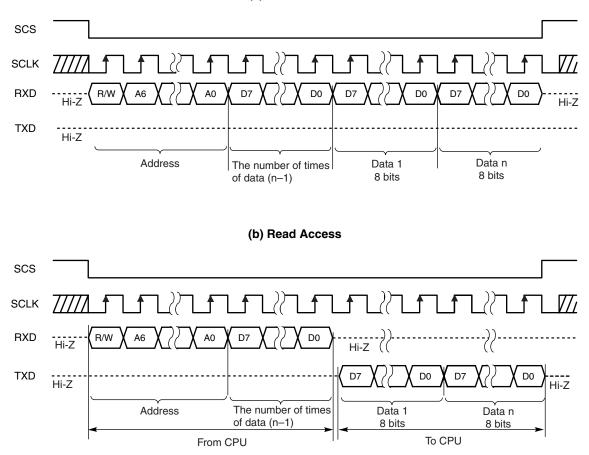

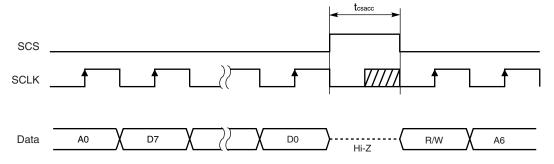

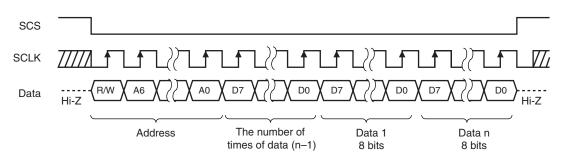

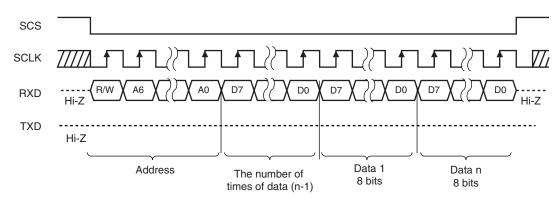

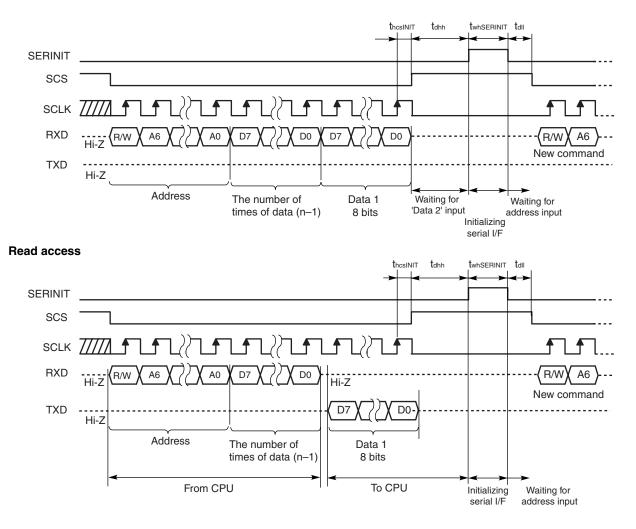

| 3.2.3 Access formats (3-wire SPI mode)                                                                        | 26 |

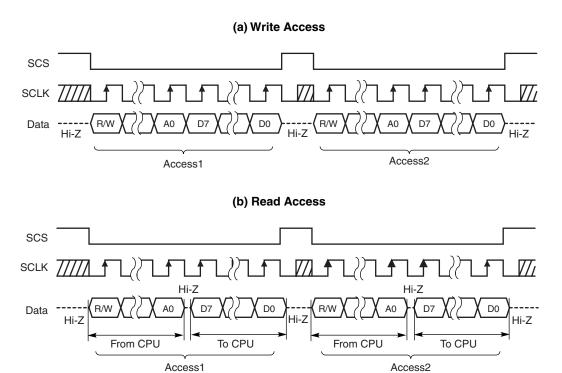

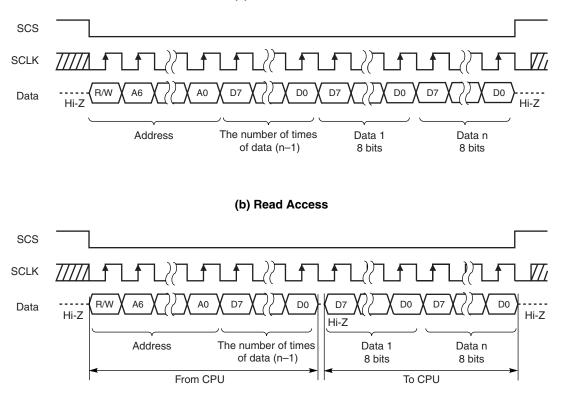

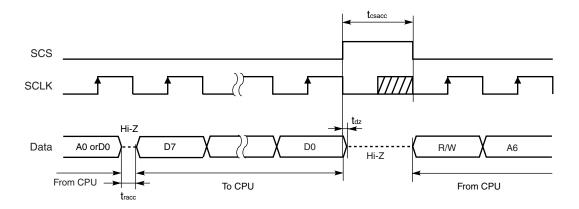

| 3.2.4 Access formats (4-wire SPI mode)                                                                        | 28 |

| 3.2.5 Initialization of serial interface                                                                      |    |

|                                                                                                               |    |

| 4. MUSIC SERIAL INTERFACE                                                                                     |    |

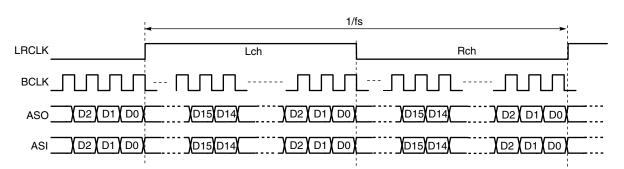

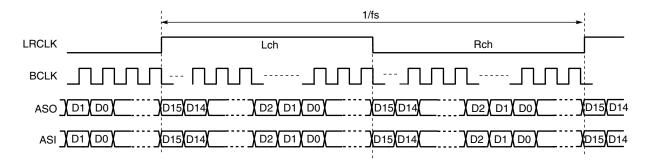

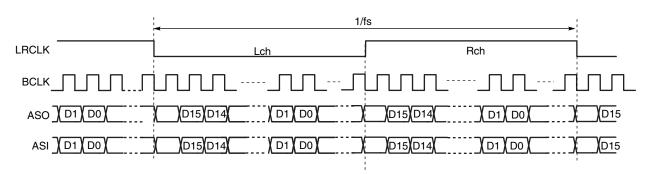

| 4.1 Audio Serial Interface (ASIO)                                                                             |    |

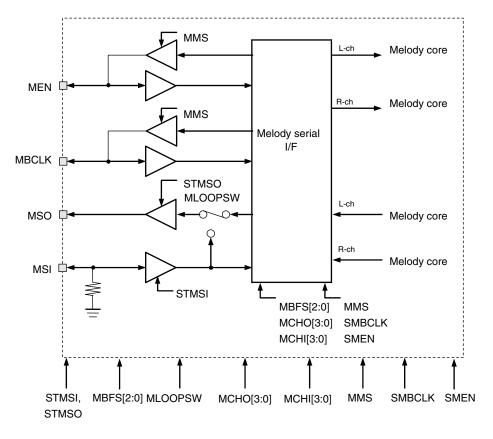

| 4.2 Serial Interface Dedicated to Sound Generator Core External Connection (MSIO)                             | 33 |

| 5. BLOCK FUNCTIONS                                                                                            | 24 |

| 5.1 Reference Voltage and Current Source Block                                                                |    |

|                                                                                                               |    |

| 5.2 Regulator Block<br>5.3 PLL Block                                                                          |    |

|                                                                                                               |    |

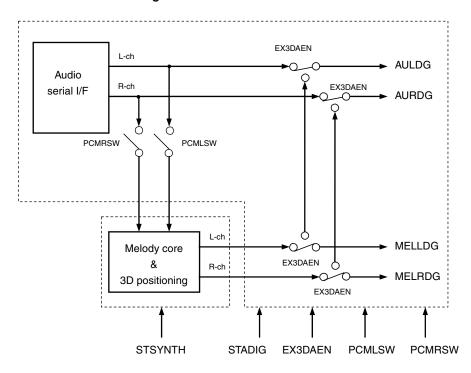

| 5.4 Sound Generator Core (Sound Generator/3D Positioning/Equalizer) Interface Block                           |    |

| 5.5 Audio Serial Interface Block (ASIO)                                                                       |    |

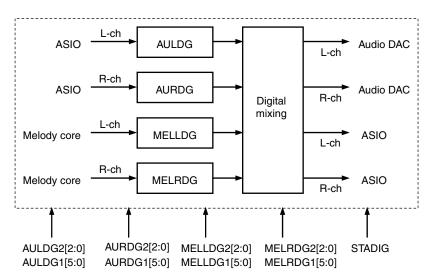

| 5.6 Audio Playback and Digital Gain Adjustment Block                                                          |    |

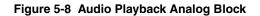

| 5.7 Audio Playback Analog Block                                                                               |    |

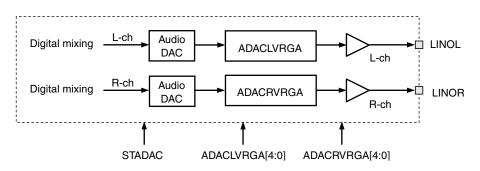

| 5.8 Digital Mixing Block<br>5.9 Serial Interface Dedicated to Sound Generator Core External Connection (MSIO) |    |

| 5.9 Serial Interface Dedicated to Sound Generator Core External Connection (MSIC)                             | 40 |

| 6. REGISTERS (CONTROL REGISTER BANK)                                                                          | 48 |

| 6.1 Standby Setting (STNBY)                                                                                   |    |

| 6.1.1 STADIG                                                                                                  |    |

| 6.1.2 STPLL2                                                                                                  |    |

| 6.1.3 STPLL1                                                                                                  |    |

| 6.1.4 STASI                                                                                                   |    |

| 6.1.5 STASI                                                                                                   |    |

| 6.1.6 STSYNTH                                                                                                 | -  |

| 6.1.7 STADAC                                                                                                  |    |

|                                                                                                               |    |

| 6.1.8 STREF                                                                                                      | 50 |

|------------------------------------------------------------------------------------------------------------------|----|

| 6.2 Master Clock Switching (MCLK1A, MCLK1B, MCLK2A, and MCLK2B)                                                  | 51 |

| 6.2.1 MCLK1A[6:0]                                                                                                | 51 |

| 6.2.2 MLCK1B[7:0]                                                                                                | 51 |

| 6.2.3 MCLK2A[4:0]                                                                                                | 51 |

| 6.2.4 MCLK2B[7:0]                                                                                                | 51 |

| 6.3 Selecting Input Clock (MCLKSEL)                                                                              | 52 |

| 6.3.1 MCLKSEL                                                                                                    | 52 |

| 6.3.2 CSTRTEN                                                                                                    | 52 |

| 6.4 FS Switching and BCLK Switching for ASIO (SEL_FS)                                                            | 55 |

| 6.4.1 FS[2:0]                                                                                                    | 55 |

| 6.4.2 BFS[4:0]                                                                                                   | 56 |

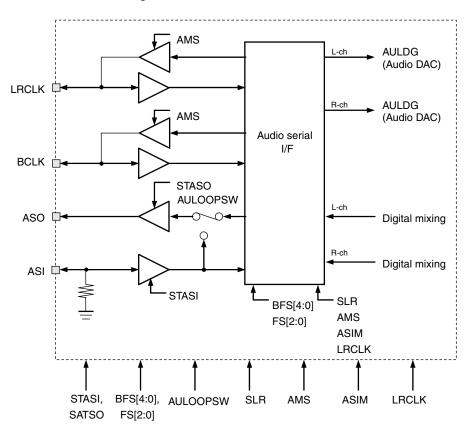

| 6.5 ASIO Mode Setting (SEL_ASI)                                                                                  | 57 |

| 6.5.1 EX3DAEN                                                                                                    | 57 |

| 6.5.2 AULOOPSW                                                                                                   | 57 |

| 6.5.3 SLR                                                                                                        | 57 |

| 6.5.4 AMS                                                                                                        | 57 |

| 6.5.5 ASIM                                                                                                       | 57 |

| 6.5.6 LRCLK                                                                                                      | 57 |

| 6.6 Digital Mixing Path (ASI Input Data) Selection (MIXING1)                                                     | 58 |

| 6.6.1 DACLMIX[1:0]                                                                                               | 58 |

| 6.6.2 DACRMIX[1:0]                                                                                               | 58 |

| 6.6.3 DACLSW[1:0]                                                                                                | 58 |

| 6.6.4 DACRSW[1:0]                                                                                                | 58 |

| 6.7 Digital Mixing Path (Sound Generator Output Data) Selection (MIXING2)                                        | 59 |

| 6.7.1 MELLMIX[1:0]                                                                                               |    |

| 6.7.2 MELRMIX[1:0]                                                                                               | 59 |

| 6.7.3 MELLSW[1:0]                                                                                                | 59 |

| 6.7.4 MELRSW[1:0]                                                                                                | 59 |

| 6.8 Digital Mixing Path (ASI to Sound Generator) Selection (MIXING3)                                             |    |

| 6.8.1 PCMLSW                                                                                                     | 60 |

| 6.8.2 PCMRSW                                                                                                     |    |

| 6.9 VIB and LED Settings (LEDVIB)                                                                                |    |

| 6.9.1 VIB                                                                                                        |    |

| 6.9.2 LED                                                                                                        |    |

| 6.10 Setting of General-Purpose Output Pins (POUT)                                                               |    |

| 6.10.1 POUT0 to POUT3                                                                                            |    |

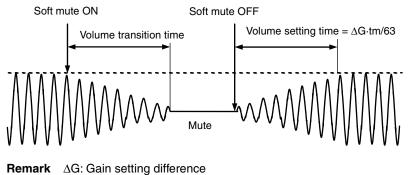

| 6.11 Audio Soft Mute Control (SMUTE)                                                                             | 61 |

| 6.11.1 SLOPE[1:0]                                                                                                |    |

| 6.11.2 AUSMUTE                                                                                                   | 61 |

| 6.11.3 MELSMUTE                                                                                                  |    |

| 6.12 Digital Volume (Sound generator Output L-ch) Setting for Audio DAC (MELLDG)                                 |    |

| 6.12.1 MELLDG2[1:0]                                                                                              |    |

| 6.12.2 MELLDG1[5:0]                                                                                              |    |

| 6.13 Digital Volume (Sound generator Output R-ch) Setting for Audio DAC (MELRDG)                                 |    |

|                                                                                                                  |    |

| 6.13.1 MELRDG2[1:0]                                                                                              |    |

| 6.13.1 MELRDG2[1:0]<br>6.13.2 MELRDG1[5:0]<br>6.14 Digital Volume (ASI Input L-ch) Setting for Audio DAC (AULDG) | 63 |

|       | 6.14.1 AULDG2[1:0]                                                     | 63 |

|-------|------------------------------------------------------------------------|----|

|       | 6.14.2 AULDG1[5:0]                                                     | 63 |

| 6     | .15 Digital Volume (ASI Input R-ch) Setting for Audio DAC (AURDG)      | 64 |

|       | 6.15.1 AURDG2[1:0]                                                     | 64 |

|       | 6.15.2 AURDG1[5:0]                                                     | 64 |

| 6     | 5.16 Setting of Analog Master Volume (L-ch) for Audio DAC (ADACLVR)    | 66 |

|       | 6.16.1 ADACLVRGA[4:0]                                                  | 66 |

| 6     | 5.17 Setting of Analog Master Volume (R-ch) for Audio DAC (ADACRVR)    | 66 |

|       | 6.17.1 ADACRVRGA[4:0]                                                  | 66 |

| 6     | .18 Setting of LSI Standby (MSIO) (STNBY2)                             | 67 |

|       | 6.18.1 STMSO                                                           | 67 |

|       | 6.18.2 STMSI                                                           | 67 |

| 6     | .19 Setting of MSIO Mode (SEL_MSIO1)                                   | 67 |

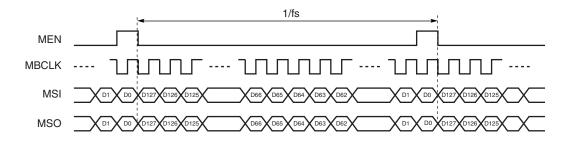

|       | 6.19.1 SMBCLK                                                          | 67 |

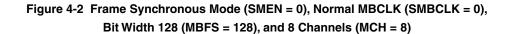

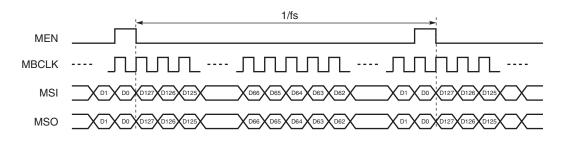

|       | 6.19.2 SMEN                                                            | 67 |

|       | 6.19.3 MMS                                                             | 68 |

|       | 6.19.4 MLOPSW                                                          | 68 |

|       | 6.19.5 MBF[2:0]                                                        | 68 |

| 6     | .20 FS Switching and BCLK Switching in Audio Serial Interface (SEL_FS) | 69 |

|       | 6.20.1 MCHI[3:0]                                                       | 69 |

|       | 6.20.2 MCHO[3:0]                                                       | 69 |

| 6     | 21 Setting of LSI Version (LSIVER)                                     | 70 |

|       | 6.21.1 VER[3:0]                                                        | 70 |

| 6     | 22 Setting of Bank in Serial Interface Mode (BANK)                     | 70 |

|       | 6.22.1 BANK[1:0]                                                       | 70 |

|       |                                                                        |    |

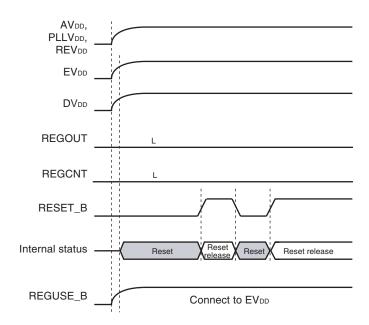

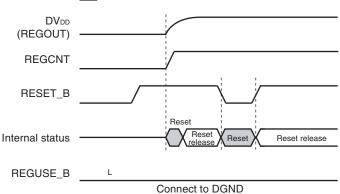

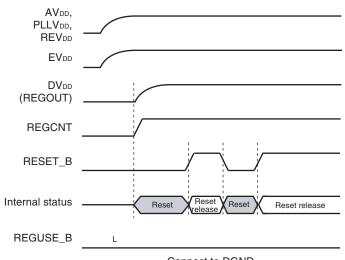

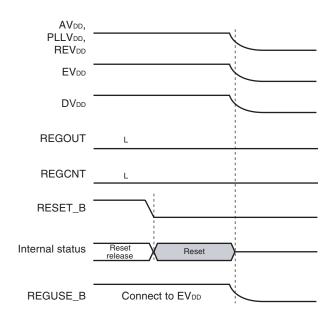

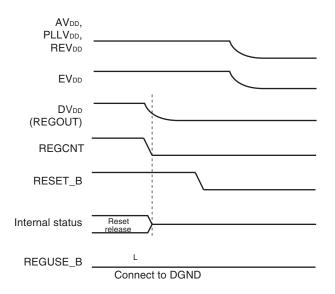

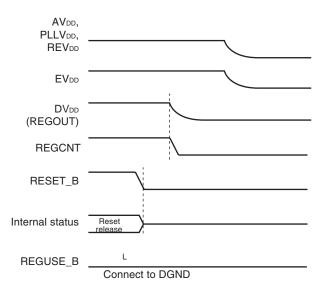

|       | OWER STARTUP PROCEDURE                                                 |    |

| 7     | 7.1 Wakeup Sequence                                                    |    |

|       | 7.1.1 When a regulator is not used                                     |    |

|       | 7.1.2 When a regulator is used                                         |    |

| 7     | 2.2 Shutdown Sequence                                                  | 73 |

|       | 7.2.1 When a regulator is not used                                     |    |

|       | 7.2.2 When a regulator is used                                         |    |

| 7     | 3 Power Saving Functions                                               | 75 |

|       | 7.3.1 Hardware power saving function                                   | 75 |

|       | 7.3.2 Software power saving function                                   | 75 |

| 8. SE | TTING SEQUENCE                                                         |    |

|       | 3.1 Power Up Sequence                                                  |    |

|       | 8.2 Basic Sequence for Switching Among Operation Modes                 |    |

| -     | 8.2.1 Mute setting                                                     |    |

|       | 8.2.2 Standby setting/cancel                                           |    |

|       | 8.2.3 FS switching                                                     |    |

|       | 8.2.4 Path switching                                                   |    |

|       | 8.2.5 3DA/surround switching                                           |    |

|       | 8.2.6 ASIO mode setting                                                |    |

| 8     | 3.3 Setting Sequence Examples                                          |    |

|       | 8.3.1 Sound generator-DAC-line output (Clock: MCLK2 = 12 MHz)          |    |

| 8.3.2 Sound generator-ASO output (Clock: MCLK2 = 12 MHz, in the master mode)        | 82  |

|-------------------------------------------------------------------------------------|-----|

| 8.3.3 Sound generator-ASO output (Clock: MCLK2 = 12 MHz, in the slave mode)         | 83  |

| 8.3.4 ASI-DAC-line output (Clock: MCLK2 = 12 MHz)                                   | 84  |

| 8.3.5 ASI-ASO output (Clock: MCLK = 12 MHz)                                         | 85  |

| 8.3.6 ASI-surround-DAC-line output (Clock: MCLK2 = 12 MHz, fs = 32 kHz)             | 86  |

| 8.3.7 ASI-surround-DAC-line output (Clock: MCLK2 = 12 MHz, fs = 44.1 kHz)           | 87  |

| 8.3.8 ASI-surround-ASO output (Clock: MCLK2 = 12 MHz, fs = 32 kHz)                  | 88  |

| 8.3.9 ASI-surround-ASO output (Clock: MCLK2 = 12 MHz, fs = 44.1 kHz)                |     |

| 9. ELECTRICAL SPECIFICATIONS                                                        |     |

| 9.1 Absolute Maximum Ratings                                                        | 90  |

| 9.2 Recommended Operating Conditions                                                |     |

| 9.3 Capacitance                                                                     |     |

| 9.4 DC Characteristics                                                              | 91  |

| 9.5 AC Characteristics                                                              | 92  |

| 9.5.1 Clock                                                                         | 92  |

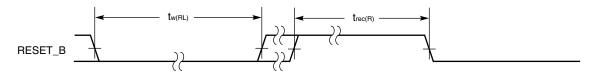

| 9.5.2 Reset                                                                         | 92  |

| 9.5.3 Parallel CPU interface                                                        | 93  |

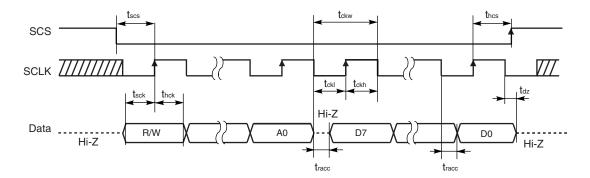

| 9.5.4 Serial CPU interface mode (Common to the 3-wire SPI mode and 4-wire SPI mode) | 95  |

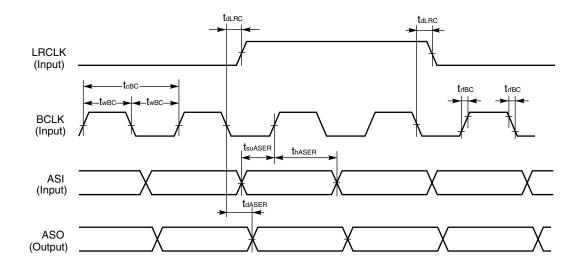

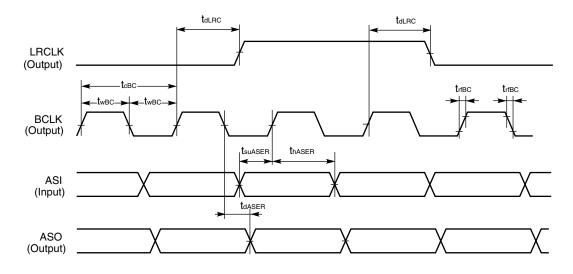

| 9.5.5 Audio serial interface (ASIO)                                                 | 98  |

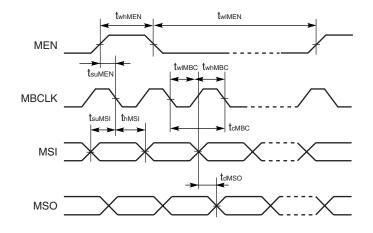

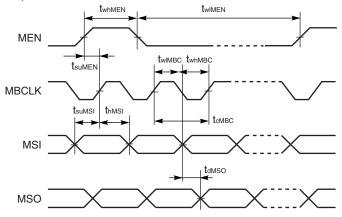

| 9.5.6 Serial interface dedicated to sound generator core external connection (MSIO) | 100 |

| 9.6 Analog Characteristics                                                          | 102 |

| 9.6.1 Analog block characteristics (reference values)                               | 103 |

| 10. CURRENT CONSUMPTION                                                             | 104 |

| 11. PACKAGE DRAWING                                                                 | 106 |

| 12. RECOMMENDED SOLDERING CONDITIONS                                                | 107 |

## **Phase-out/Discontinued**

### 1. FUNCTIONS

### **1.1 General Descriptions of Functions**

### (1) Power supply voltages

| Digital I/O power supply:    | 1.7 to 3.3 V, 1.8 V TYP.     |

|------------------------------|------------------------------|

| Analog power supply:         | 2.7 to 3.3 V, 3.0 V TYP.     |

| Power supply for PLL:        | 2.7 to 3.3 V, 3.0 V TYP.     |

| Power supply for regulators: | 2.7 to 3.3 V, 3.0 V TYP.     |

| (Digital power supply:       | 1.45 to 1.65 V, 1.54 V TYP.) |

### (2) Operating temperatures

–20 to +85°C

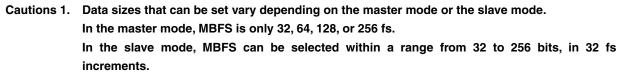

### (3) Function blocks

| Melody Core:       | PCM sound generator core for 128 polyphonic                          |

|--------------------|----------------------------------------------------------------------|

| 3D Positioning:    | 3D positioning surrounds function                                    |

| Digital Mixing:    | Digital mixing circuit                                               |

| Regulator:         | Regulator for digital power supply                                   |

| PLL1/PLL2:         | PLL for sound generator and PLL for audio                            |

| Audio DAC:         | Stereo 16-bit audio DAC                                              |

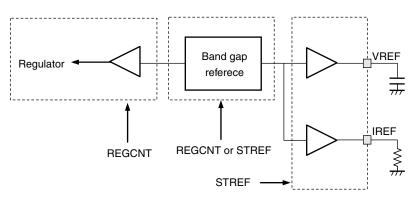

| Band gap:          | Circuit generating reference voltage and current for analog circuits |

| VIB/LED:           | Circuit generating control signals for vibration and LED             |

| Master/Digital VR: | Volume circuit                                                       |

### **1.2 General Descriptions of Circuits**

| Block             | Functions                                                                                                                                                                                                                                  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Melody Core       | Up to 128 tones can be produced at the same time.<br>This block contains a PCM sound generator and a sequencer. The sampling frequency is 32 kHz.                                                                                          |

| 3D Positioning    | 3D positioning surround function                                                                                                                                                                                                           |

| Digital Mixing    | Switching or adding sound generator output and audio serial input.                                                                                                                                                                         |

| PLL               | Generates master clocks for processing internal signals.<br>Input clocks: 3.84 MHz to 15.36 MHz                                                                                                                                            |

| Audio DAC         | 16 bits $\times$ 2 channels (L-ch and R-ch)<br>Sampling frequencies: 48 kHz, 44.1 kHz, 32 kHz, 16 kHz, and 8 kHz (Default: 32 kHz)<br>The interface supports the master and slave modes.<br>Dynamic range: 90 dBr TYP (for a single block) |

| Regulator         | 1.54 V output regulator for digital power supply                                                                                                                                                                                           |

| VIB/LED           | Outputs control signals for VIB and LED.                                                                                                                                                                                                   |

| Master/Digital VR | Master volume: 0 dB to -45 dB/1.5 dB increments<br>Digital volume: +12 dB to -63 dB/1 dB increments                                                                                                                                        |

Phase-out/Discontinued

μPD9971

### 2. PINS FUNCTIONS

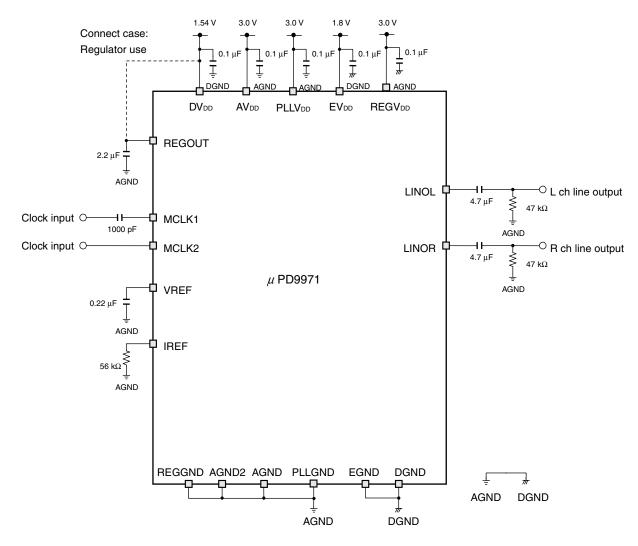

### 2.1 Pin Configuration

### 2.2 Recommended External Circuit

### 2.3 Descriptions of Pin Functions

### (1) Power supply pins and GND pins

| Pin Name | Pin No.                | I/O | Functions                                                                                                                                                                                                                |

|----------|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DVDD     | 4C, 7C, 7H,<br>8F, 10D | _   | Power supply for digital blocks<br>When using an internal regulator, connect this pin and the REGOUT pin on the<br>outside of the $\mu$ PD9971.<br>Be sure to connect a 0.1 $\mu$ F capacitor between this pin and DGND. |

| DGND     | 5C, 5K                 | _   | Ground for digital blocks                                                                                                                                                                                                |

| EVDD     | 8H, 9C                 | _   | Power supply for digital I/O Be sure to connect a 0.1 $\mu F$ capacitor between this pin and EGND.                                                                                                                       |

| EGND     | 6A, 8G                 | -   | Ground for digital I/O                                                                                                                                                                                                   |

| PLLVDD   | 2G                     | _   | Power supply for PLL Be sure to connect a 0.1 $\mu\text{F}$ capacitor between this pin and PLLGND.                                                                                                                       |

| PLLGND   | 1H                     | -   | Ground for PLL                                                                                                                                                                                                           |

| AVdd     | 1E                     | _   | Power supply for analog blocks Be sure to connect a 0.1 $\mu F$ capacitor between this pin and AGND.                                                                                                                     |

| AGND     | 1D                     | -   | Ground for analog blocks                                                                                                                                                                                                 |

| AGND2    | 1G                     | -   | Ground for analog blocks                                                                                                                                                                                                 |

| REGVDD   | 1J, 3H                 | -   | Power supply for regulator band gap reference Be sure to connect a 0.1 $\mu F$ capacitor between this pin and REGGND.                                                                                                    |

| REGGND   | 3G                     | _   | Ground for regulators                                                                                                                                                                                                    |

### (2) Clock and system control pins

| Pin Name | Pin No. | I/O   | Functions                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLK1    | 2H      | Input | Clock input (3.84 MHz to 15.36 MHz)<br>This is the reference clock input to generate the internal master clock.<br>Be sure to input using capacitive coupling (1000 pF).<br>Connect this pin to GND when the pin is not used.                                                                                                                                                                                                          |

| MCLK2    | 3F      | Input | Clock input (3.84 MHz to 15.36 MHz)<br>This is the reference clock input to generate the internal master clock.<br>This pin is also used for inputting square waves of input level EV <sub>DD</sub> .<br>Connect this pin to GND when the pin is not used.                                                                                                                                                                             |

| CSTRT    | 8C      | Input | <ul> <li>Signal input to select clock input from outside</li> <li>Cautions This pin is valid when the CSTRTEN register is high level.<br/>When the CSTRT pin does switching, however, only limited<br/>frequencies can be input. Before using this pin, be sure to<br/>contact NEC Electronics.</li> <li>0: Selects input from MCLK2.</li> <li>1: Selects input from MCLK1</li> <li>This pin is pulled down in the μPD9971.</li> </ul> |

| RESET_B  | 9E      | Input | <ul> <li>Hardware reset signal input</li> <li>This resets the μPD9971.</li> <li>0: Resets.</li> <li>1: Cancels the reset.</li> <li>Registers are initialized to their initial values after a reset.</li> </ul>                                                                                                                                                                                                                         |

# **Phase-out/Discontinued**

μ**ΡD9971**

### (3) Host CPU pins and interface pins

| Pin Name     | Pin No. | I/O   | Functions                                                                                                                                                                                                                                                                                                      |

|--------------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0/Data, TXD | 6К      | I/O   | <ol> <li>Parallel I/F mode (when PS = 0)</li> <li>Host interface address A0 signal input This input pin indicates the internal register address or data during host CPU access.</li> <li>1: When transferring data</li> <li>0: When setting the address of the register to be accessed</li> </ol>              |

|              |         |       | <ul> <li>2. Serial mode (when PS = 1)</li> <li>Bidirectional TX/RX serial input/output (when PS = 1 and RD_B = 0).</li> <li>In this case, this pin is used as 3-wire SPI mode</li> <li>TX serial data output (when PS = 1 and RD_B = 1).</li> <li>In this case, this pin is used as 4-wire SPI mode</li> </ul> |

| A1/RXD       | 5J      | Input | <ol> <li>Parallel I/F mode (when PS = 0)</li> <li>Host interface address A1 signal input This input pin selects the access<br/>destination register during host CPU access.</li> </ol>                                                                                                                         |

|              |         |       | 1: PCM Sound generator register<br>0: Register other than PCM sound generator register                                                                                                                                                                                                                         |

|              |         |       | <ul> <li>2. Serial I/F mode (when PS = 1)</li> <li>This pin is not used in 3-wire SPI mode (RD_B = 0).</li> <li>This pin inputs receive data in 4-wire SPI mode (RD_B = 1).</li> </ul>                                                                                                                         |

| CS_B/SCS     | 6J      | Input | 1. Parallel I/F mode (when PS = 0)<br>Chip select input for parallel I/F This is the input pin for the host interface<br>select signal. This pin is set as active (low) while the host CPU accesses a<br>register                                                                                              |

|              |         |       | 2. Serial I/F mode (when PS = 1)<br>Chip select input for serial I/F                                                                                                                                                                                                                                           |

| RD_B/SPIMODE | 7J      | Input | <ol> <li>Parallel I/F mode (when PS = 0)</li> <li>Host read input This pin is set as active (low) while the host CPU reads a register.</li> <li>Do not set this pin and the WR_B pin as active at the same time.</li> </ol>                                                                                    |

|              |         |       | 2. Serial I/F mode (when PS = 1)         3-wire / 4-wire SPI mode selection                                                                                                                                                                                                                                    |

|              |         |       | 0: 3-wire SPI mode.<br>1: 4-wire SPI mode.                                                                                                                                                                                                                                                                     |

| WR_B/SCLK    | 7K      | Input | 1. Parallel mode (when PS = 0)<br>Host write input This pin is set as active (low) while the host CPU reads a<br>register. Do not set this pin and the RD_B active pin at the same time.                                                                                                                       |

|              |         |       | 2. Serial mode (when PS = 1)<br>Clock for serial I/F at frequencies up to 13 MHz.                                                                                                                                                                                                                              |

(2/2)

| Pin Name    | Pin No.                             | I/O    | Functions                                                                                                                                                                                                                             |

|-------------|-------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0/(SERINT) | 8K                                  | I/O    | 1. Parallel I/F mode (when PS = 0)<br>Bit 0 for 8-bit host data bus<br>When the host CPU accesses $\mu$ PD9971, address and data I/O is performed.<br>When the CS_B signal in inactive (high), this pin is set to high impedance.     |

|             |                                     |        | 2. Serial I/F mode (when PS = 1)<br>Initialization signal for serial I/F                                                                                                                                                              |

| D1 to D7    | 8J, 10H,<br>9H, 10G,<br>9G, 10F, 9F | I/O    | 1. Parallel I/F mode (when PS = 0)<br>Bits 7 -1 for 8-bit host data bus<br>When the host CPU accesses $\mu$ PD9971, address and data I/O is performed.<br>When the CS_B signal in inactive (high), this pin is set to high impedance. |

|             |                                     |        | 2. Serial I/F mode (when PS = 1)<br>This bus is always set to high impedance                                                                                                                                                          |

| INT_B       | 10E                                 | Output | Interrupt request from PCM sound generator<br>This signal requests interrupts from the $\mu$ PD9971 to the host CPU.<br>This is used when requesting data transfer or internal status notification.                                   |

| PS          | 6B                                  | Input  | Parallel/serial I/F mode setting<br>This pin sets the parallel or serial mode of the host CPU interface.<br>1: Serial I/F mode<br>0: Parallel I/F mode<br>This pin has an internal pull-down resistor                                 |

### (4) Audio serial interface pins (ASIO)

| Pin Name | Pin No. | I/O    | Functions                                                                                                                                                                                                                                                                                                                   |

|----------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCLK     | 8B      | I/O    | Bit synchronization clock I/O for audio serial<br>When this pin is not used, connect it to GND.                                                                                                                                                                                                                             |

| LRCLK    | 8A      | I/O    | Audio serial frame synchronization clock I/O<br>When this pin is not used, connect it to GND.                                                                                                                                                                                                                               |

| ASO      | 7B      | Output | Audio serial data output<br>The audio serial data frame size is set via registers. During master mode, either<br>64 bits or 32 bits can be selected. During slave mode, selections can be made<br>in 2-bit steps within a range from 32 to 64 bits. Leave this pin open when not<br>used.                                   |

| ASI      | 7A      | Input  | Audio serial data input<br>The audio serial data frame size is set via registers. During master mode, either<br>64 bits or 32 bits can be selected. During slave mode, selections can be made<br>in 2-bit steps within a range from 32 to 64 bits. Leave this pin open when not<br>used. Pull-down is performed internally. |

| Pin Name | Pin No. | I/O    | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

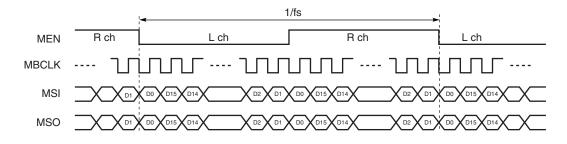

| MBCLK    | 5B      | I/O    | Bit synchronization clock I/O dedicated to PCM sound generator external connection<br>When this pin is not used, connect it to GND.                                                                                                                                                                                                                                                                                                                                                    |

| MEN      | 5A      | I/O    | Frame synchronization clock I/O dedicated to PCM sound generator external connection<br>When this pin is not used, connect it to GND.                                                                                                                                                                                                                                                                                                                                                  |

| MSO      | 3C      | Output | <ul> <li>Data output dedicated to PCM sound generator external connection</li> <li>Frame size of serial data is set by using the register. In the master mode, 32, 64, 128, or 256 bits can be selected (when only MSIO is used).</li> <li>In slave mode, selections can be made in 32-bit increments within a range from 32 to 256 bits (when only MSIO is used).</li> <li>When this pin is not used, leave it open.</li> </ul>                                                       |

| MSI      | 4A      | Input  | <ul> <li>Data input dedicated to PCM sound generator external connection</li> <li>Frame size of serial data is set by using the register.</li> <li>In the master mode, 32, 64, 128, or 256 bits can be selected (when only MSIO is used).</li> <li>In the slave mode, selections can be made in 32-bit increments within a range from 32 to 256 bits (when only MSIO is used).</li> <li>When this pin is not used, leave it open. (This pin contains a pull-down register.)</li> </ul> |

### (5) Serial interface dedicated to sound generator core external connection (MSIO)

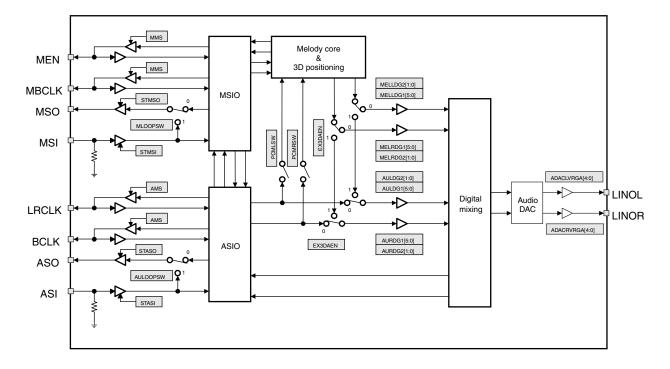

Cautions 1. Data sizes that can be set vary depending on the master mode or the slave mode. In the master mode, MBFS is only 32, 64, 128, or 256 fs. In the slave mode, MBFS can be selected within a range from 32 to 256 bits, in 32-fs increments.

2. When MSIO and ASIO are used at the same time, ASIO can be set to the master mode only (BFS = 32 or 64 fs).

| Pin Name | Pin No. | I/O    | Functions                                                                                                                                                                                                                                                     |

|----------|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED      | 10C     | Output | External LED control output (The drive capacity is 1 mA when $EV_{DD} = 1.8$ V.)<br>This pin is the port output pin. Settings are entered by writing values to the port<br>setting register from the host CPU.<br>When this pin is not used, leave it open.   |

| VIB      | 9D      | Output | External motor control output (The drive capacity is 1 mA when $EV_{DD} = 1.8$ V.)<br>This pin is the port output pin. Settings are entered by writing values to the port<br>setting register from the host CPU.<br>When this pin is not used, leave it open. |

### (6) External LED pin and motor control output pin

#### (7) Reference voltage/current pins for analog circuits

| Pin Name | Pin No. | I/O    | Functions                                                                                                                |

|----------|---------|--------|--------------------------------------------------------------------------------------------------------------------------|

| VREF     | 2E      | Output | Reference voltage for analog blocks Be sure to connect a 0.22 $\mu\text{F}$ capacitor between this pin and AGND.         |

| IREF     | 2D      | Input  | For generating reference current for analog blocks Be sure to connect a 56 $k\Omega$ register between this pin and AGND. |

## **Phase-out/Discontinued**

### (8) Audio DAC output pins

| Pin Name | Pin No. | I/O    | Functions          |

|----------|---------|--------|--------------------|

| LINOL    | 1C      | Output | Line (L-ch) output |

| LINOR    | 1F      | Output | Line (R-ch) output |

### (9) Regulator pins

| Pin Name | Pin No. | I/O    | Functions                                                                                                                                                                                                                          |

|----------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REGOUT   | 2K, 3J  | Output | Regulator output<br>When using regulator output for the digital power supply, connect these pins<br>with DV <sub>DD</sub> pin outside the $\mu$ PD9971.<br>Be sure to connect a 2.2 $\mu$ F capacitor between this pin and REGGND. |

| REGUSE_B | 4H      | Input  | Regulator block enable signal input pin<br>0: When the regulator is used<br>1: When the regulator is not used                                                                                                                      |

| REGCNT   | ЗК      | Input  | Input pin for regulator control<br>0: Stops the output.<br>1: Starts the output.                                                                                                                                                   |

### (10) General-purpose external output pins

| Pin Name   | Pin No.           | I/O    | Functions                                                                                                                                                   |

|------------|-------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PO0 to PO3 | 5H, 6H, 4K,<br>4J | Output | General-purpose external output pins<br>These pins can be used to output control signals to peripheral devices.<br>When they are not used, leave them open. |

### (11) Test pins

| Pin Name   | Pin No.    | I/O   | Functions                                                                                |

|------------|------------|-------|------------------------------------------------------------------------------------------|

| TM0 to TM2 | 2C, 2F, 3B | Input | Input for tests<br>Leave these pins open when using them under normal conditions.        |

| TM3 to TM4 | 3A, 4B     | I/O   | Input/output for tests<br>Leave these pins open when using them under normal conditions. |

| TM5        | 6C         | Input | Input for tests<br>Leave this pin open when using it under normal conditions.            |

### (12) Others

| N.C.        | Pin No.                                                              | I/O | Functions                                     |

|-------------|----------------------------------------------------------------------|-----|-----------------------------------------------|

| N.C         | 1B, 2A, 2B,<br>2J, 3D, 3E,<br>8D, 8E, 9A,<br>9B, 9J, 9L,<br>10B, 10J | _   | Reserved for future use. Leave this pin open. |

| N.C (index) | 4D                                                                   | _   | Reserved for future use. Leave this pin open. |

### 2.4 Connection of Unused Pins

### Table 2-1 Connection of Unused Pins

| Pin Name   | I/O   | Recommended Connection                                                                |

|------------|-------|---------------------------------------------------------------------------------------|

| MCLK1      | I     | Connect to PLLGND.                                                                    |

| MCLK2      | I     | Connect to EGND.                                                                      |

| CSTRT      | I     | Leave open (Internal Pull-down).                                                      |

| A1/RXD     | I     | Connect to DGND.                                                                      |

| D0/SERINIT | I     | Connect to DGND.                                                                      |

| D1 to D7   | I     | Connect to DGND.                                                                      |

| INT_B      | 0     | Leave open.                                                                           |

| LRCLK      | I/O   | Connect to DGND.                                                                      |

| BCLK       | I/O   | Connect to DGND.                                                                      |

| ASI        | I     | Leave open (Internal Pull-down).                                                      |

| ASO        | 0     | Leave open.                                                                           |

| MEN        | I/O   | Connect to DGND.                                                                      |

| MBCLK      | I/O   | Connect to DGND.                                                                      |

| MSI        | I     | Leave open (Internal Pull-down).                                                      |

| MSO        | 0     | Leave open.                                                                           |

| LED        | 0     | Leave open.                                                                           |

| VIB        | 0     | Leave open.                                                                           |

| LINOL      | 0     | Leave open.                                                                           |

| LINOR      | 0     | Leave open.                                                                           |

| REGUSE_B   | I     | Connect to EVDD (when regulator is not used).                                         |

| REGCNT     | I     | Connect to EGND (when regulator is not used).                                         |

| REGVDD     | Power | Connect to a 3.0 V power supply (regardless of whether the regulator is used or not). |

| REGOUT     | 0     | Leave open (when the regulator is not used).                                          |

| PO0 to PO3 | 0     | Leave open.                                                                           |

| TM0 to TM2 | I     | Leave open (Internal Pull-down).                                                      |

| TM3, TM4   | I/O   | Leave open.                                                                           |

| TM5        | I     | Leave open (Internal Pull-down).                                                      |

### 2.5 Pin Statuses

| Pin. I/O |        | A/D     | Pin Name     | Standby Sta    | atus          | RESET_B=0      | After         |       |  |

|----------|--------|---------|--------------|----------------|---------------|----------------|---------------|-------|--|

| No       |        |         |              | Control Signal | Pin<br>Status | Control Signal | Pin<br>Status | Reset |  |

| 2F       | Input  | Digital | TM1          |                | Input         |                | Input         | Input |  |

| 1C       | Output | Analog  | LINOL        | STDAC          | Hi-Z          | STDAC          | Hi-Z          | Hi-Z  |  |

| 1D       |        | Analog  | AGND         |                |               |                |               |       |  |

| 2D       | Output | Analog  | IREF         | STREF          | Hi-Z          | STREF          | Hi-Z          | Hi-Z  |  |

| 2E       | Output | Analog  | VREF         | STREF          | Hi-Z          | STREF          | Hi-Z          | Hi-Z  |  |

| 1E       |        | Analog  | AVDD         |                |               |                |               |       |  |

| 1F       | Output | Analog  | LINOR        | STDAC          | Hi-Z          | STDAC          | Hi-Z          | Hi-Z  |  |

| 1G       |        | Analog  | AGND2        |                |               |                |               |       |  |

| 2G       |        | Analog  | PLLVDD       |                |               |                |               |       |  |

| 2H       | Input  | Analog  | MCLK1        | STPLL1, STPLL2 | Input         | STPLL1, STPLL2 | Input         | Input |  |

| 1H       |        | Analog  | PLLGND       |                |               |                |               |       |  |

| 3G       |        | Analog  | REGGND       |                |               |                |               |       |  |

| ЗH       |        | Analog  | REGVDD       |                |               |                |               |       |  |

| 1J       |        | Analog  | REGVDD       |                |               |                |               |       |  |

| 2K       | Output | Analog  | REGOUT       | REGCNT         | Low           | REGCNT         | Low           | Low   |  |

| ЗJ       | Output | Analog  | REGOUT       | REGCNT         | Low           | REGCNT         | Low           | Low   |  |

| 3F       | Input  | Analog  | MCLK2        | STPLL1, STPLL2 | Input         | STPLL1, STPLL2 | Input         | Input |  |

| ЗK       | Input  | Digital | REGCNT       |                | Input         |                | Input         | Input |  |

| 4H       | Input  | Digital | REGUSE_B     |                | Input         |                | Input         | Input |  |

| 5H       | Output | Digital | PO0          |                | Register      | RESET_B        | Low           | Low   |  |

| 4K       | Output | Digital | PO2          |                | Register      | RESET_B        | Low           | Low   |  |

| 4J       | Output | Digital | PO3          |                | Register      | RESET_B        | Low           | Low   |  |

| 6H       | Output | Digital | PO1          |                | Register      | RESET_B        | Low           | Low   |  |

| 5K       |        | Digital | DGND         |                |               |                |               |       |  |

| 5J       | Input  | Digital | A1/RXD       |                | Input         |                | Input         | Input |  |

| 7H       |        | Digital | DVDD         |                |               |                |               |       |  |

| 6K       | I/O    | Digital | A0/Data, TXD |                | Input         |                | Input         | Input |  |

| 6J       | Input  | Digital | CS_B/SCS     |                | Input         |                | Input         | Input |  |

| 7J       | Input  | Digital | RD_B/SPIMODE |                | Input         |                | Input         | Input |  |

| 7K       | Input  | Digital | WR_B/SCLK    |                | Input         |                | Input         | Input |  |

| 8H       |        | Digital | EVDD         |                |               |                |               |       |  |

| 8K       | I/O    | Digital | D0/SERINIT   |                | Input         | RESET_B        | Hi-Z          | Input |  |

| 8J       | I/O    | Digital | D1           |                | Input         | RESET_B        | Hi-Z          | Input |  |

| 8G       |        | Digital | EGND         |                | -             |                |               |       |  |

| 10H      | I/O    | Digital | D2           |                | Input         | RESET_B        | Hi-Z          | Input |  |

| 9H       | I/O    | Digital | D3           |                | Input         | RESET_B        | Hi-Z          | Input |  |

|      |        | 1       |          |                |               |                |               | (2/2  |

|------|--------|---------|----------|----------------|---------------|----------------|---------------|-------|

| Pin. | I/O    | A/D     | Pin Name | Standby St     | tatus         | RESET_B=0      | status        | After |

| No   |        |         |          | Control Signal | Pin<br>Status | Control Signal | Pin<br>Status | Reset |

| 8F   |        | Digital | DVDD     |                |               |                |               |       |

| 10G  | I/O    | Digital | D4       |                | Input         | RESET_B        | Hi-Z          | Input |

| 9G   | I/O    | Digital | D5       |                | Input         | RESET_B        | Hi-Z          | Input |

| 10F  | I/O    | Digital | D6       |                | Input         | RESET_B        | Hi-Z          | Input |

| 9F   | I/O    | Digital | D7       |                | Input         | RESET_B        | Hi-Z          | Input |

| 10E  | Output | Digital | INT_B    |                | Output        | RESET_B        | High          | High  |

| 9E   | Input  | Digital | RESET_B  |                | Input         |                | Input         | Input |

| 10D  |        | Digital | DVDD     |                |               |                |               |       |

| 9D   | Output | Digital | VIB      |                | Register      | RESET_B        | Low           | Low   |

| 10C  | Output | Digital | LED      |                | Register      | RESET_B        | Low           | Low   |

| 9C   |        | Digital | EVDD     |                |               |                |               |       |

| 8C   | Input  | Digital | CSTRT    |                | Input         |                | Input         | Input |

| 8B   | I/O    | Digital | BCLK     | STASI, STASO   |               | RESET_B        | Hi-Z          | Input |

| 8A   | I/O    | Digital | LRCLK    | STASI, STASO   |               | RESET_B        | Hi-Z          | Input |

| 7C   |        | Digital | DVDD     |                |               |                |               |       |

| 7A   | Input  | Digital | ASI      | STASI, STASO   |               |                | Input         | Input |

| 7B   | Output | Digital | ASO      | STASI, STASO   |               | RESET_B        | Hi-Z          | Hi-Z  |

| 6B   | Input  | Digital | PS       |                | Input         |                | Input         | Input |

| 6A   |        | Digital | EGND     |                |               |                |               |       |

| 6C   | Input  | Digital | TM5      |                | Input         |                | Input         | Input |

| 5B   | I/O    | Digital | MBCLK    | STMSI, STMSO   |               | RESET_B        | Hi-Z          | Input |

| 5A   | I/O    | Digital | MEN      | STMSI, STMSO   |               | RESET_B        | Hi-Z          | Input |

| 5C   |        | Digital | DGND     |                |               |                |               |       |

| 4C   |        | Digital | DVDD     |                |               |                |               |       |

| 4A   | Input  | Digital | MSI      | STMSI, STMSO   |               |                | Input         | Input |

| 4B   | I/O    | Digital | TM4      |                | Low           | RESET_B        | Hi-Z          | Low   |