### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

### RENESAS

### S MOS INTEGRATED CIRCUIT / Phase-out/Discontinued μPD98414

### 2.4 Gbps ATM SONET FRAMER

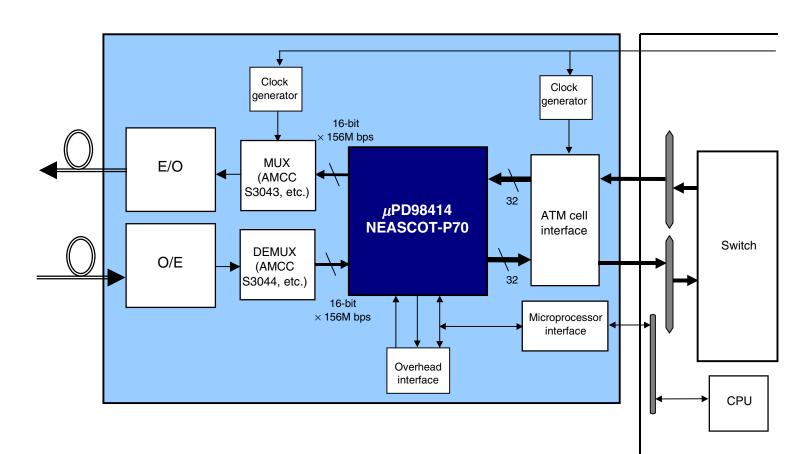

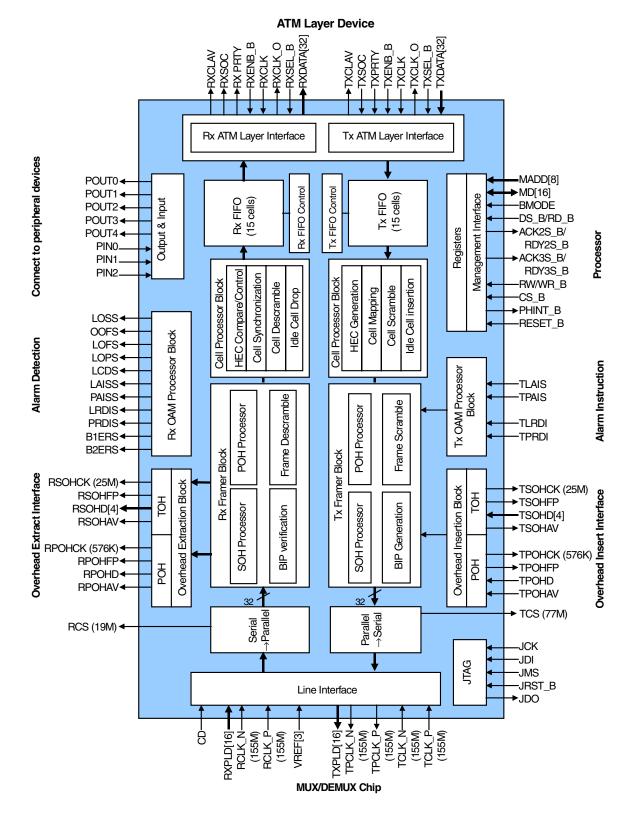

The  $\mu$ PD98414 (NEASCOT-P70<sup>TM</sup>) is one of ATM LSIs and provides the functions of the TC sublayer of the SONET/SDH-base physical layer of the ATM protocol specified by the ATM Forum.

Its main functions include a transmission function for mapping an ATM cell passed from a high-end ATM layer device to the payload of a 2.4 Gbps SONET STS-48c/SDH STM-16c frame and transmitting the cell to a MUX device in the circuit, and a reception function for separating the overhead and ATM cell from the data string received from a DEMUX device and transmitting the ATM cell to the ATM layer device.

This LSI is ideal for systems that constitute the ATM network of a LAN or WAN, such as a transmission system, ATM switch, and high-speed backbone switch.

Detailed descriptions of its functions, etc., are given in the following user's manual. Be sure to read it for design purposes.

#### μPD98414 User's Manual: S14166E

#### **FEATURES**

- Supplies the functions of the TC (Transmission Convergence) sublayer recommended by the ATM Forum and ITU-T.

- Supports the concatenation frame of 2.4 Gbps SONET STS-48c/SDH STM-16c.

- ATM layer interface

- 32-bit, 104-MHz LVTTL FIFO interface

- 15-cell transmit/receive FIFO

- Supports 52-byte/56-byte cell formats.

- Prefixes one-word TAG area to receive cell.

- Circuit side interface

- 16-bit PECL level I/O

- Either of two modes can be selected for CPU interface

- 16-bit data bus

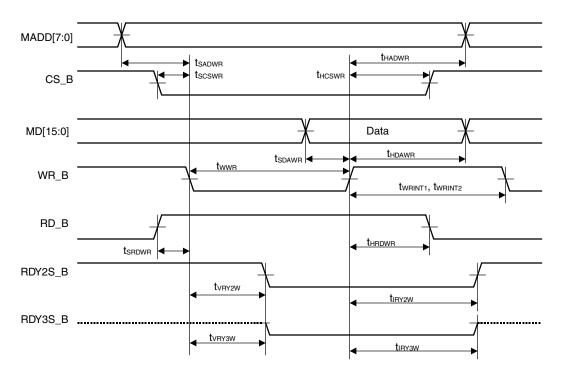

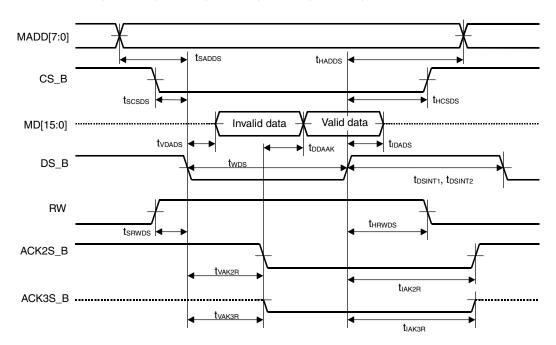

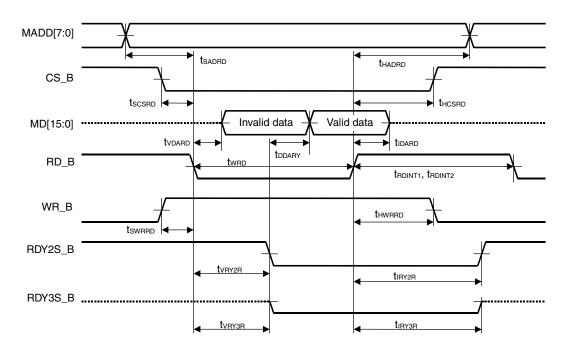

- Intel-compatible mode [RD, WR, RDY-type]/Motorola-compatible mode [DS, R/W, ACK-type]

- Supports two types of overhead interfaces (that can access all overhead areas).

- Incorporates overhead byte insert/drop registers.

- Incorporates dedicated overhead byte insert/extract interfaces.

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

NEC

- Many OAM functions

- Fault: Detection of LOS, OOF, LOF, LOP, OCD, and LCD

- Alarm: Detection and transmission of APS, Line AIS, Line RDI, Path AIS, and Path RDI

- Receive APS signal and Signal Label (C2 byte) monitoring functions

- Bit error rate monitoring function

- Transmit/receive message buffer for J0/J1 trace messages (16 bytes or 64 bytes long)

- Supports loopback function.

- Remote: Two modes (ATM layer loopback and circuit side loopback)

- Supports an error generation pseudo frame transmission function for testing.

- Three general-purpose input and five general-purpose output ports

- Supports JTAG boundary scan test (IEEE1149.1).

- 0.35-µm CMOS process

- +3.3 V single power source

#### **ORDERING INFORMATION**

Part Number

Package

Phase-out/Discontinued

μPD98414F2-RN1

ruonago

F2-RN1 352-pin plastic BGA (cavity down advanced type)  $(35 \times 35)$

NEC

NEC

**Phase-out/Discontinued**

#### **BLOCK DIAGRAM**

μ**PD98414**

**Phase-out/Discontinued**

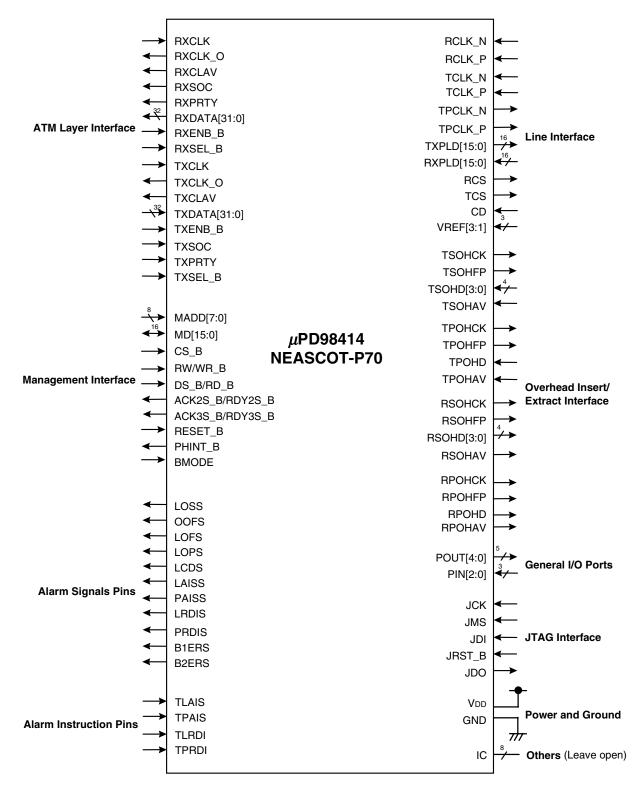

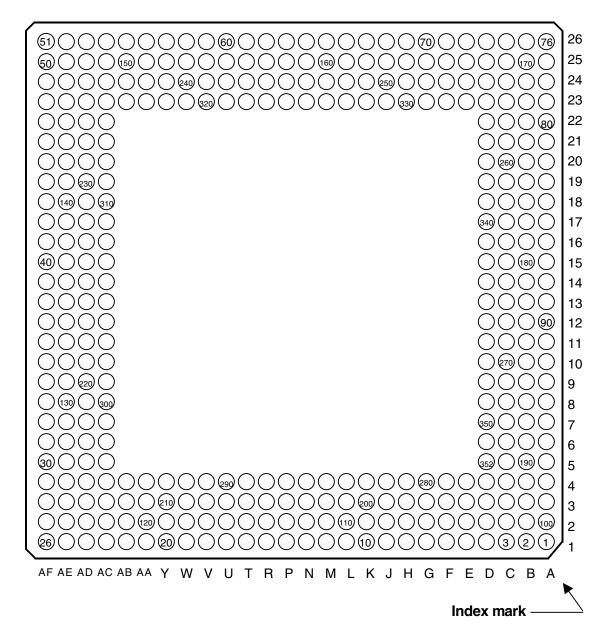

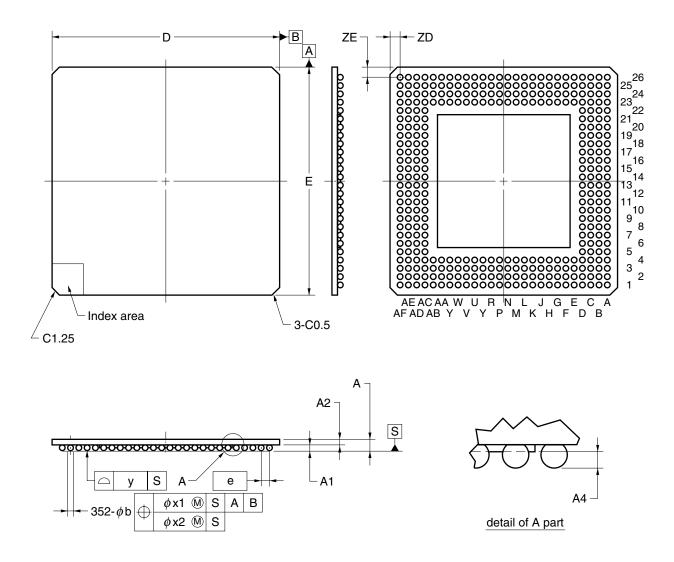

**PIN CONFIGURATION**

**PIN CONFIGURATION (BOTTOM VIEW)**

• 352-pin plastic BGA (cavity down advanced type) (35  $\times$  35)  $\mu \rm PD98414F2\text{-}RN1$

### NEC

### μPD98414

#### PIN ARRANGEMENT TABLE

| Serial No. | Address No. | Pin Name | Serial No. | Address No.  | Pin Name | Serial No. | Address No. | (1)<br>Pin Name |

|------------|-------------|----------|------------|--------------|----------|------------|-------------|-----------------|

| 1          | Address No. | GND      | 36         | Address No.  | RXDATA15 | 71         | F26         | TXCLAV          |

|            | B01         | TCS      |            | AF11<br>AF12 | RXDATA15 | 71         | E26         | GND             |

| 2          |             |          | 37         |              |          |            |             |                 |

| 3          | C01         | IC       | 38         | AF13         | GND      | 73         | D26         | POUT0           |

| 4          | D01         | IC       | 39         | AF14         | RXDATA19 | 74         | C26         | PHINT_B         |

| 5          | E01         | RXPLD15  | 40         | AF15         | GND      | 75         | B26         | GND             |

| 6          | F01         | RXPLD13  | 41         | AF16         | RXDATA24 | 76         | A26         | GND             |

| 7          | G01         | GND      | 42         | AF17         | GND      | 77         | A25         | RW/WR_B         |

| 8          | H01         | RXPLD10  | 43         | AF18         | RXDATA28 | 78         | A24         | MADD6           |

| 9          | J01         | RXPLD8   | 44         | AF19         | RXDATA30 | 79         | A23         | MADD4           |

| 10         | K01         | Vdd      | 45         | AF20         | RXPRTY   | 80         | A22         | MADD1           |

| 11         | L01         | GND      | 46         | AF21         | RXCLAV   | 81         | A21         | MD13            |

| 12         | M01         | RXPLD4   | 47         | AF22         | GND      | 82         | A20         | MD10            |

| 13         | N01         | VDD      | 48         | AF23         | POUT1    | 83         | A19         | MD7             |

| 14         | P01         | GND      | 49         | AF24         | PRDIS    | 84         | A18         | MD3             |

| 15         | R01         | GND      | 50         | AF25         | Vdd      | 85         | A17         | MD0             |

| 16         | T01         | Vdd      | 51         | AF26         | GND      | 86         | A16         | GND             |

| 17         | U01         | RCLK_P   | 52         | AE26         | LAISS    | 87         | A15         | TXPLD13         |

| 18         | V01         | RPOHFP   | 53         | AD26         | OOFS     | 88         | A14         | GND             |

| 19         | W01         | RSOHD2   | 54         | AC26         | GND      | 89         | A13         | GND             |

| 20         | Y01         | RSOHAV   | 55         | AB26         | TXDATA1  | 90         | A12         | Vdd             |

| 21         | AA01        | TPOHAV   | 56         | AA26         | Vdd      | 91         | A11         | Vdd             |

| 22         | AB01        | TSOHD2   | 57         | Y26          | GND      | 92         | A10         | GND             |

| 23         | AC01        | TSOHD0   | 58         | W26          | Vdd      | 93         | A09         | Vdd             |

| 24         | AD01        | POUT4    | 59         | V26          | TXDATA10 | 94         | A08         | TXPLD3          |

| 25         | AE01        | GND      | 60         | U26          | TXDATA12 | 95         | A07         | VDD             |

| 26         | AF01        | GND      | 61         | T26          | TXDATA15 | 96         | A06         | GND             |

| 27         | AF02        | PIN1     | 62         | R26          | TXDATA17 | 97         | A05         | TPCLK_P         |

| 28         | AF03        | TLRDI    | 63         | P26          | GND      | 98         | A04         | IC              |

| 29         | AF04        | POUT2    | 64         | N26          | TXDATA19 | 99         | A03         | JDI             |

| 30         | AF05        | RXDATA1  | 65         | M26          | GND      | 100        | A02         | VDD             |

| 31         | AF06        | Vdd      | 66         | L26          | TXDATA24 | 101        | B02         | VDD             |

| 32         | AF07        | GND      | 67         | K26          | GND      | 102        | C02         | RCS             |

| 33         | AF08        | VDD      | 68         | J26          | TXDATA28 | 103        | D02         | IC              |

| 34         | AF09        | RXDATA10 | 69         | H26          | TXDATA30 | 104        | E02         | VDD             |

| 35         | AF10        | RXDATA12 | 70         | G26          | TXPRTY   | 101        | F02         | GND             |

| Serial No. | Address No. | Pin Name | Serial No. | Address No. | Pin Name        | Serial No. | Address No. | Pin Name |

|------------|-------------|----------|------------|-------------|-----------------|------------|-------------|----------|

| 106        | G02         | RXPLD12  | 141        | AE19        | RXDATA31        | 176        | B19         | MD9      |

| 107        | H02         | RXPLD11  | 142        | AE20        | RXENB_B         | 177        | B18         | MD5      |

| 108        | J02         | RXPLD9   | 143        | AE21        | Vdd             | 178        | B17         | MD1      |

| 109        | K02         | VREF2    | 144        | AE22        | RXCLK_O         | 179        | B16         | GND      |

| 110        | L02         | GND      | 145        | AE23        | B2ERS           | 180        | B15         | Vdd      |

| 111        | M02         | Vdd      | 146        | AE24        | PAISS           | 181        | B14         | TXPLD12  |

| 112        | N02         | RXPLD3   | 147        | AE25        | VDD             | 182        | B13         | TXPLD11  |

| 113        | P02         | RXPLD2   | 148        | AD25        | LOSS            | 183        | B12         | TXPLD9   |

| 114        | R02         | RXPLD0   | 149        | AC25        | LCDS            | 184        | B11         | TXPLD7   |

| 115        | T02         | RCLK_N   | 150        | AB25        | Vdd             | 185        | B10         | GND      |

| 116        | U02         | RPOHD    | 151        | AA25        | TXDATA3         | 186        | B09         | VDD      |

| 117        | V02         | RSOHD3   | 152        | Y25         | TXDATA5         | 187        | B08         | GND      |

| 118        | W02         | RSOHD1   | 153        | W25         | TXDATA6         | 188        | B07         | TXPLD1   |

| 119        | Y02         | RSOHFP   | 154        | V25         | TXDATA9         | 189        | B06         | TCLK_N   |

| 120        | AA02        | TPOHFP   | 155        | U25         | Vdd             | 190        | B05         | TPCLK_N  |

| 121        | AB02        | TSOHD1   | 156        | T25         | GND             | 191        | B04         | JCK      |

| 122        | AC02        | TSOHFP   | 157        | R25         | TXDATA16        | 192        | B03         | JRST_B   |

| 123        | AD02        | PIN2     | 158        | P25         | TXDATA18        | 193        | C03         | Vdd      |

| 124        | AE02        | Vdd      | 159        | N25         | Vdd             | 194        | D03         | IC       |

| 125        | AE03        | PIN0     | 160        | M25         | TXDATA22        | 195        | E03         | VREF3    |

| 126        | AE04        | TPAIS    | 161        | L25         | TXDATA25        | 196        | F03         | GND      |

| 127        | AE05        | Vdd      | 162        | K25         | TXDATA27        | 197        | G03         | Vdd      |

| 128        | AE06        | RXDATA3  | 163        | J25         | GND             | 198        | H03         | Vdd      |

| 129        | AE07        | RXDATA5  | 164        | H25         | TXDATA31        | 199        | J03         | Vdd      |

| 130        | AE08        | RXDATA6  | 165        | G25         | TXENB_B         | 200        | K03         | GND      |

| 131        | AE09        | RXDATA9  | 166        | F25         | Vdd             | 201        | L03         | RXPLD7   |

| 132        | AE10        | Vdd      | 167        | E25         | TXCLK_O         | 202        | M03         | RXPLD5   |

| 133        | AE11        | GND      | 168        | D25         | RESET_B         | 203        | N03         | Vdd      |

| 134        | AE12        | RXDATA16 | 169        | C25         | DS_B/RD_B       | 204        | P03         | RXPLD1   |

| 135        | AE13        | RXDATA18 | 170        | B25         | Vdd             | 205        | R03         | GND      |

| 136        | AE14        | Vdd      | 171        | B24         | ACK3S_B/RDY3S_B | 206        | Т03         | GND      |

| 137        | AE15        | RXDATA22 | 172        | B23         | MADD5           | 207        | U03         | RPOHAV   |

| 138        | AE16        | RXDATA25 | 173        | B22         | MADD2           | 208        | V03         | Vdd      |

| 139        | AE17        | RXDATA27 | 174        | B21         | MD14            | 209        | W03         | RSOHD0   |

| 140        | AE18        | GND      | 175        | B20         | MD11            | 210        | Y03         | TPOHD    |

|            |             |          |            |             |                 |            |             | (3/4     |

|------------|-------------|----------|------------|-------------|-----------------|------------|-------------|----------|

| Serial No. | Address No. | Pin Name | Serial No. | Address No. | Pin Name        | Serial No. | Address No. | Pin Name |

| 211        | AA03        | TSOHD3   | 246        | N24         | TXDATA21        | 281        | H04         | GND      |

| 212        | AB03        | TSOHAV   | 247        | M24         | TXDATA23        | 282        | J04         | GND      |

| 213        | AC03        | POUT3    | 248        | L24         | TXDATA26        | 283        | K04         | VDD      |

| 214        | AD03        | Vdd      | 249        | K24         | Vdd             | 284        | L04         | GND      |

| 215        | AD04        | CD       | 250        | J24         | Vdd             | 285        | M04         | RXPLD6   |

| 216        | AD05        | RXDATA0  | 251        | H24         | Vdd             | 286        | N04         | GND      |

| 217        | AD06        | GND      | 252        | G24         | TXSEL_B         | 287        | P04         | VDD      |

| 218        | AD07        | RXDATA4  | 253        | F24         | TXCLK           | 288        | R04         | VREF1    |

| 219        | AD08        | Vdd      | 254        | E24         | IC              | 289        | T04         | Vdd      |

| 220        | AD09        | RXDATA8  | 255        | D24         | CS_B            | 290        | U04         | RPOHCK   |

| 221        | AD10        | RXDATA11 | 256        | C24         | Vdd             | 291        | V04         | GND      |

| 222        | AD11        | RXDATA13 | 257        | C23         | ACK2S_B/RDY2S_B | 292        | W04         | RSOHCK   |

| 223        | AD12        | Vdd      | 258        | C22         | MADD3           | 293        | Y04         | TPOHCK   |

| 224        | AD13        | Vdd      | 259        | C21         | MADD0           | 294        | AA04        | GND      |

| 225        | AD14        | RXDATA21 | 260        | C20         | MD12            | 295        | AB04        | TSOHCK   |

| 226        | AD15        | RXDATA23 | 261        | C19         | Vdd             | 296        | AC04        | GND      |

| 227        | AD16        | RXDATA26 | 262        | C18         | MD6             | 297        | AC05        | TPRDI    |

| 228        | AD17        | Vdd      | 263        | C17         | MD2             | 298        | AC06        | Vdd      |

| 229        | AD18        | Vdd      | 264        | C16         | Vdd             | 299        | AC07        | RXDATA2  |

| 230        | AD19        | Vdd      | 265        | C15         | TXPLD14         | 300        | AC08        | GND      |

| 231        | AD20        | RXSEL_B  | 266        | C14         | Vdd             | 301        | AC09        | RXDATA7  |

| 232        | AD21        | RXCLK    | 267        | C13         | TXPLD10         | 302        | AC10        | GND      |

| 233        | AD22        | TLAIS    | 268        | C12         | GND             | 303        | AC11        | GND      |

| 234        | AD23        | LRDIS    | 269        | C11         | TXPLD6          | 304        | AC12        | RXDATA14 |

| 235        | AD24        | Vdd      | 270        | C10         | TXPLD5          | 305        | AC13        | GND      |

| 236        | AC24        | LOPS     | 271        | C09         | Vdd             | 306        | AC14        | RXDATA20 |

| 237        | AB24        | TXDATA0  | 272        | C08         | TXPLD2          | 307        | AC15        | Vdd      |

| 238        | AA24        | GND      | 273        | C07         | TXPLD0          | 308        | AC16        | Vdd      |

| 239        | Y24         | TXDATA4  | 274        | C06         | Vdd             | 309        | AC17        | RXDATA29 |

| 240        | W24         | Vdd      | 275        | C05         | IC              | 310        | AC18        | GND      |

| 241        | V24         | TXDATA8  | 276        | C04         | JMS             | 311        | AC19        | GND      |

| 242        | U24         | TXDATA11 | 277        | D04         | GND             | 312        | AC20        | RXSOC    |

| 243        | T24         | TXDATA13 | 278        | E04         | IC              | 313        | AC21        | GND      |

| 244        | R24         | Vdd      | 279        | F04         | Vdd             | 314        | AC22        | B1ERS    |

| 245        | P24         | VDD      | 280        | G04         | RXPLD14         | 315        | AC23        | GND      |

| -          |             |          |            |             |          |            |             | (4/4)    |

|------------|-------------|----------|------------|-------------|----------|------------|-------------|----------|

| Serial No. | Address No. | Pin Name | Serial No. | Address No. | Pin Name | Serial No. | Address No. | Pin Name |

| 316        | AB23        | LOFS     | 331        | G23         | TXSOC    | 346        | D11         | VDD      |

| 317        | AA23        | Vdd      | 332        | F23         | GND      | 347        | D10         | TXPLD4   |

| 318        | Y23         | TXDATA2  | 333        | E23         | BMODE    | 348        | D09         | GND      |

| 319        | W23         | GND      | 334        | D23         | GND      | 349        | D08         | GND      |

| 320        | V23         | TXDATA7  | 335        | D22         | MADD7    | 350        | D07         | TCLK_P   |

| 321        | U23         | GND      | 336        | D21         | Vdd      | 351        | D06         | GND      |

| 322        | T23         | GND      | 337        | D20         | MD15     | 352        | D05         | JDO      |

| 323        | R23         | TXDATA14 | 338        | D19         | GND      |            |             |          |

| 324        | P23         | GND      | 339        | D18         | MD8      |            |             |          |

| 325        | N23         | TXDATA20 | 340        | D17         | MD4      |            |             |          |

| 326        | M23         | Vdd      | 341        | D16         | GND      |            |             |          |

| 327        | L23         | Vdd      | 342        | D15         | TXPLD15  |            |             |          |

| 328        | K23         | TXDATA29 | 343        | D14         | GND      |            |             |          |

| 329        | J23         | GND      | 344        | D13         | Vdd      |            |             |          |

| 330        | H23         | GND      | 345        | D12         | TXPLD8   |            |             |          |

#### PIN NAME

| ACK2S_B            | Acknowledge 2 State                        | RSOHFP         | Rx SOH Insert Frame Pulse         |

|--------------------|--------------------------------------------|----------------|-----------------------------------|

| ACK2S_B<br>ACK3S_B | Acknowledge 2 State<br>Acknowledge 3 State | RW             | Management Data Read/Write        |

| B1ERS              | -                                          | RXCLAV         | Rx Cell Available                 |

| BIERS<br>B2ERS     | B1 Error Rate Degrade                      | RXCLAV         | UTOPIA Rx Clock In                |

|                    | B2 Error Rate Degrade                      | -              |                                   |

| BMODE              | Bus Mode                                   | RXCLK_O        | UTOPIA Rx Clock Out               |

| CD                 | Carrier Detect                             | RXDATA0-       | UTOPIA Rx Data                    |

| CS_B               | Chip Select                                | RXDATA31       |                                   |

| DS_B               | Data Strobe                                | RXENB_B        | Rx Cell Enable                    |

| GND                | Ground                                     | RXPLD0-RXPLD15 | Rx Line Data                      |

| IC                 | Internal Circuits Connection               | RXPRTY         | Rx Parity                         |

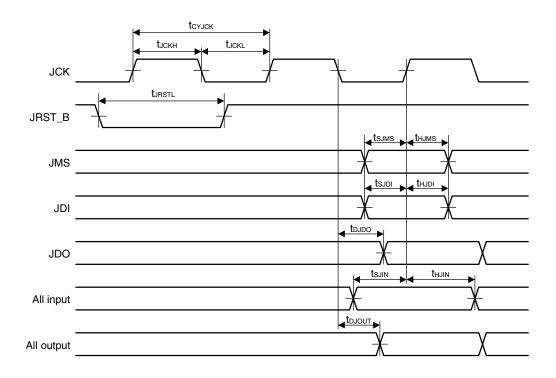

| JCK                | JTAG Test Clock                            | RXSEL_B        | Rx Cell Select                    |

| JDI                | JTAG Test Data In                          | RXSOC          | Rx Start Of Cell                  |

| JDO                | JTAG Test Data Out                         | TCLK_N         | Tx Clock In – (155 MHz)           |

| JMS                | JTAG Test Mode Select                      | TCLK_P         | Tx Clock In + (155 MHz)           |

| JRST_B             | JTAG Test Reset                            | TCS            | Tx Line Clock Signal Out (77 MHz) |

| LAISS              | Line AIS State                             | TLAIS          | Tx Line AIS Frame Send            |

| LCDS               | LCD State                                  | TLRDI          | Tx Line RDI Frame Send            |

| LOFS               | LOF State                                  | TPAIS          | Tx Path AIS Frame Send            |

| LOPS               | LOP State                                  | TPCLK_N        | Tx Clock Out – (155 MHz)          |

| LOSS               | LOS State                                  | TPCLK_P        | Tx Clock Out + (155 MHz)          |

| LRDIS              | Line RDI State                             | TPOHAV         | Tx POH Insert Available           |

| MADD0-MADD7        | Management Address                         | TPOHCK         | Tx POH Insert Clock               |

| MD0-MD15           | Management Data                            | TPOHD          | Tx POH Insert Data                |

| OOFS               | OOF State                                  | TPOHFP         | Tx POH Insert Frame Pulse         |

| PAISS              | Path AIS State                             | TPRDI          | Tx Path RDI Frame Send            |

| PHINT_B            | Interrupt                                  | TSOHAV         | Tx TOH Insert Available           |

| PIN0-PIN2          | General In                                 | TSOHCK         | Tx TOH Insert Clock               |

| POUT0-POUT4        | General Out                                | TSOHD0-TSOHD3  | Tx TOH Insert Data                |

| PRDIS              | Path RDI State                             | TSOHFP         | Tx TOH Insert Frame Pulse         |

| RCLK_N             | Rx Line Clock – (155 MHz)                  | TXCLAV         | Tx Cell Available                 |

| RCLK_P             | Rx Line Clock + (155 MHz)                  | TXCLK          | UTOPIA Tx Clock In                |

| RCS                | Rx Line Clock Signal Out (19 MHz)          | TXCLK_O        | UTOPIA Tx Clock Out               |

| RD_B               | Read                                       | TXDATA0-       | UTOPIA Tx Data                    |

| RDY2S_B            | Ready 2-State                              | TXDATA31       |                                   |

| RDY3S_B            | Ready 3-State                              | TXENB_B        | Tx Cell Enable                    |

| RESET_B            | Reset                                      | TXPLD0-TXPLD15 | Tx Line Data                      |

| RPOHAV             | Rx POH Insert Available                    | TXPRTY         | Tx Parity                         |

| RPOHCK             | Rx POH Insert Clock                        | TXSEL_B        | Tx Cell Select                    |

| RPOHD              | Rx POH Insert Data                         | TXSOC          | Tx Start Of Cell                  |

| RPOHFP             | Rx POH Insert Frame Pulse                  | Vdd            | Vdd                               |

| RSOHAV             | Rx SOH Insert Available                    | VREF1-VREF3    | Voltage Reference For PECL In     |

| RSOHCK             | Rx SOH Insert Clock                        | WR_B           | Write                             |

| RSOHD0-RSOHD3      | Rx SOH Insert Data                         |                |                                   |

|                    |                                            |                |                                   |

#### CONTENTS

| 1. | PIN F | UNCTION                               |

|----|-------|---------------------------------------|

|    | 1.1   | Line Interface                        |

|    | 1.2   | ATM Layer Interface14                 |

|    | 1.3   | Management Interface                  |

|    | 1.4   | Overhead Interface18                  |

|    | 1.5   | General-Purpose I/O Port              |

|    | 1.6   | Alarm Signal Input/Output             |

|    | 1.7   | JTAG Boundary Scan                    |

|    | 1.8   | Power and Grounding Pins              |

|    | 1.9   | Others                                |

|    | 1.10  | Handling Unused Pins                  |

|    | 1.11  | Initial States of Each Pin            |

|    |       |                                       |

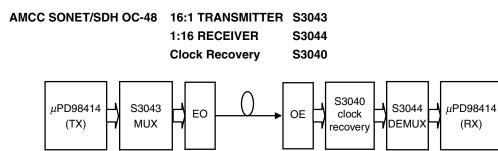

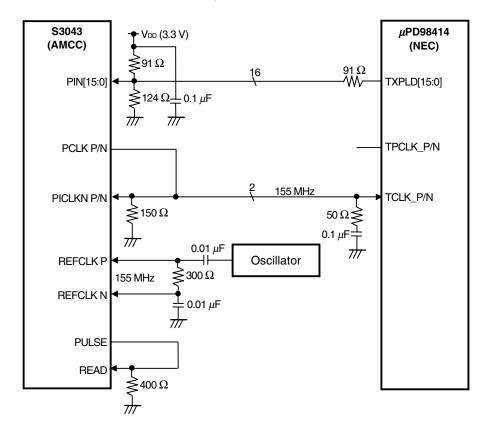

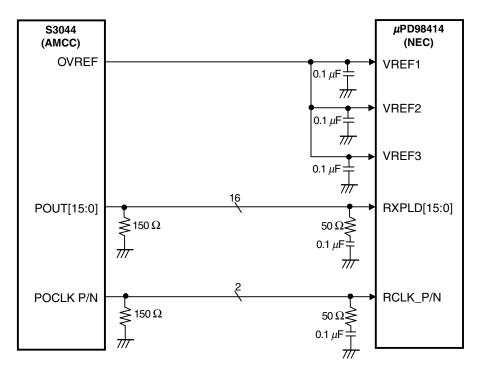

| 2. | CON   | NECTION EXAMPLE OF MUX/DEMUX DEVICE25 |

|    |       |                                       |

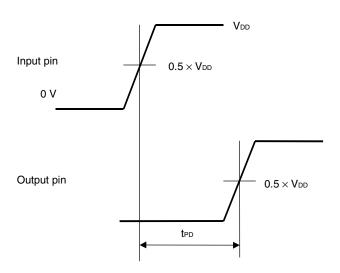

| 3. | ELEC  | CTRIC CHARACTERISTICS                 |

|    |       |                                       |

| 4. | PAC   | AGE DRAWING                           |

|    |       |                                       |

| 5. | RECO  | OMMENDED SOLDERING CONDITIONS42       |

#### 1. PIN FUNCTION

#### 1.1 Line Interface

The line interface connects MUX and DEMUX devices in the circuit.

| Pin Name           | Serial No.                                                                                  | Address No.                                                                                   | I/O, Level                  | Function                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCLK_N<br>RCLK_P   | 115<br>17                                                                                   | T02<br>U01                                                                                    | I<br>PECL                   | Receive clock input (155.52 MHz).<br>These pins input a 155.52-MHz clock, synchronized with the<br>receive data.                                                                                                                                                                                                                                                              |

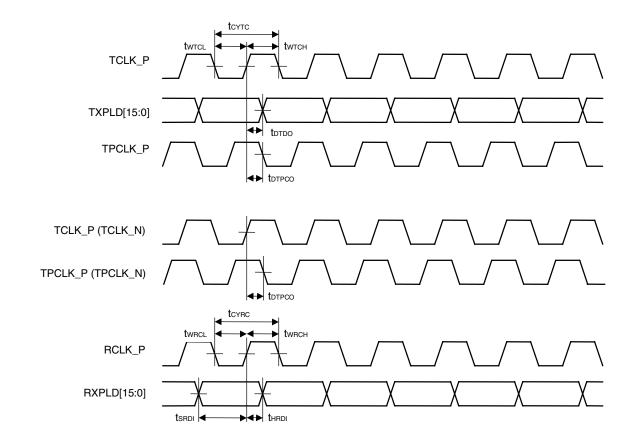

| TCLK_N             | 189                                                                                         | B06                                                                                           | I<br>PECL                   | Transmit clock input (155.52 MHz).<br>These pins input a transmit clock. The $\mu$ PD98411 updates                                                                                                                                                                                                                                                                            |

| TCLK_P             | 350                                                                                         | D07                                                                                           |                             | transmit data TXPLD15 through TXPLD0 at the rising edge of this clock.                                                                                                                                                                                                                                                                                                        |

| TPCLK_N            | 190                                                                                         | B05                                                                                           | 0                           | Transmit clock output (155.52 MHz).                                                                                                                                                                                                                                                                                                                                           |

| TPCLK_P            | 97                                                                                          | A05                                                                                           | PECL                        | The clocks input to TCLK_N and TCLK_P are internally inverted and output from these pins.                                                                                                                                                                                                                                                                                     |

| RXPLD15-<br>RXPLD0 | 5, 280, 6,<br>106, 107, 8,<br>108, 9, 201,<br>285, 202, 12,<br>112, 113, 204,<br>114        | E01, G04, F01,<br>G02, H02, H01,<br>J02, J01, L03,<br>M04, M03, M01,<br>N02, P02, P03,<br>R02 | I<br>PECL                   | Receive 16-bit parallel data input.                                                                                                                                                                                                                                                                                                                                           |

| TXPLD15-<br>TXPLD0 | 342, 265, 87,<br>181, 182, 267,<br>183, 345, 184,<br>269, 270, 347,<br>94, 272, 188,<br>273 | D15, C15, A15,<br>B14, B13, C13,<br>B12, D12, B11,<br>C11, C10, D10,<br>A08, C08, B07,<br>C07 | O<br>PECL                   | Transmit 16-bit parallel data output.                                                                                                                                                                                                                                                                                                                                         |

| TCS                | 2                                                                                           | B01                                                                                           | O<br>LVTTL                  | Transmit system clock output (77.76 MHz).<br>The transmit clocks input to TCLK_N and TCLK_P are<br>divided by two in the $\mu$ PD98414 and output from this pin.                                                                                                                                                                                                              |

| RCS                | 102                                                                                         | C02                                                                                           | O<br>LVTTL                  | Receive system clock output (19.44 MHz).<br>The receive clocks input to RCLK_N and RCLK_P are<br>divided by eight in the $\mu$ PD98414 and output from this pin.                                                                                                                                                                                                              |

| CD                 | 215                                                                                         | AD04                                                                                          | I<br>LVTTL<br>(5V tolerant) | Receive framer function reset.<br>While the input level of this pin is low, the receive framer<br>block (from the circuit up to the receive FIFO) is reset. The<br>transition of this signal from high to low can be used as a<br>condition for LOS detection. The optical input failure alarm<br>signal output by a receive optical link module can be input to<br>this pin. |

| VREF3-<br>VREF1    | 195, 109, 288                                                                               | E03, K02, R04                                                                                 | l<br>VREF                   | These pins input reference potentials (intermediate potentials) for single-end PECL input signals (RXPLD[15:0]).                                                                                                                                                                                                                                                              |

#### 1.2 ATM Layer Interface

The ATM layer interface transfers cells to and from a high-end ATM layer device.

| Pin Name | Serial No. | Address No. | I/O, Level | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|------------|-------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

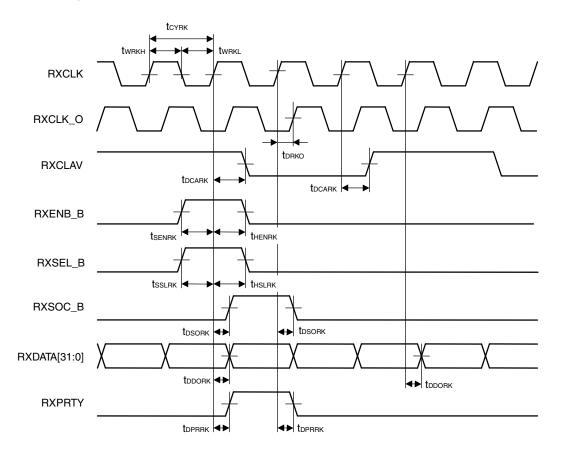

| RXCLK    | 232        | AD21        | I<br>LVTTL | Receive FIFO clock input.<br>This pin inputs the clock, from 8 to 104 MHz, used to<br>transfer receive data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RXCLK_O  | 144        | AE22        | O<br>LVTTL | Receive FIFO clock return output.<br>This pin returns and outputs the clock input to RXCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RXSOC    | 312        | AC20        | O<br>LVTTL | Receive cell start position signal output.<br>This pin goes high during the clock cycle in which the first<br>byte of the receive cell is output to RXDATA, to post<br>notification to the ATM layer device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RXCLAV   | 46         | AF21        | O<br>LVTTL | Receive FIFO cell data transfer enable signal output.<br>The $\mu$ PD98414 drives RXCLAV high if one or more cells of<br>receive data to be transferred exists in the receive FIFO, to<br>post notification to the ATM layer device. RXCLAV is held<br>high if one or more cells of valid data exists in the receive<br>FIFO at the seventh clock cycle or later after the start of<br>output of the cell; otherwise, RXCLAV goes low.                                                                                                                                                                                                                                                                                                                                       |

| RXENB_B  | 142        | AE20        | I<br>LVTTL | Receive enable signal input (byte unit control).<br>The ATM layer device enables or disables the receive cell data output by the $\mu$ PD98414 in byte units. The $\mu$ PD98414 samples RXENB_B at the rising edge of RXCLK. When it detects the low level of RXENB_B, it updates the output of RSOC and RXDATA starting from the next clock cycle, and then transfers the receive cell data. If RXENB_B is high, the $\mu$ PD98414 stops the output of RSOC and RXDATA, starting from the next clock cycle.                                                                                                                                                                                                                                                                 |

|          |            |             |            | Caution This signal cannot be used with RXSEL_B at<br>the same time. Fix this signal to the low level<br>when it is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RXSEL_B  | 231        | AD20        | I<br>LVTTL | Receive enable signal input (cell unit control).<br>The ATM layer device enables the $\mu$ PD98414 to output<br>receive cell data in cell units. The $\mu$ PD98414 samples<br>RXSEL_B at the rising edge, one clock cycle before RXSOC<br>goes high, and starts outputting receive cell data from the<br>next clock cycle if RXSEL_B is low. Once the $\mu$ PD98414<br>has detected that RXSEL_B has gone low, it does not<br>sample RXSEL_B until the next sampling timing (one clock<br>before RXSOC goes high). When the $\mu$ PD98414 detects<br>that RXSEL_B has gone high at the sampling timing, it<br>continues sampling RXSEL_B at every clock, and starts<br>outputting cells from the clock cycle next to that in which the<br>low level of RXSEL_B was detected. |

|          |            |             |            | Caution This signal cannot be used with RXENB_B at<br>the same time. Fix this signal to the low level<br>when it is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

μ**PD98414**

| Pin Name             | Serial No.                                                                                                                                                                          | Address No.                                                                                                                                                                                                                  | I/O, Level | (2/3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXPRTY               | 45                                                                                                                                                                                  | AF20                                                                                                                                                                                                                         | O<br>LVTTL | Parity bit output.<br>This pin generates an odd parity bit for the output data on<br>RXDATA and outputs it from RXPRTY. The parity bit is<br>always output.<br>The parity bit to be generated can be changed to even parity<br>depending on the setting of the RRPM bit of the MDR5<br>register.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RXDATA31-<br>RXDATA0 | 141, 44, 309,<br>43, 139, 227,<br>138, 41, 226,<br>137, 225, 306,<br>39, 135, 37,<br>134, 36, 304,<br>222, 35, 221,<br>34, 131, 220,<br>301, 130, 129,<br>218, 128, 299,<br>30, 216 | AE19, AF19, AC17,<br>AF18, AE17, AD16,<br>AE16, AF16, AD15,<br>AE15, AD14, AC14,<br>AF14, AE13, AF12,<br>AE12, AF11, AC12,<br>AD11, AF10, AD10,<br>AF09, AE09, AD09,<br>AC09, AE08, AE07,<br>AD07, AE06, AC07,<br>AF05, AD05 | O<br>LVTTL | Receive cell data output bus.<br>These pins form a 32-bit data bus through which receive cell<br>data is output to the ATM layer device. The data on this bus<br>is updated at the rising edge of RXCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

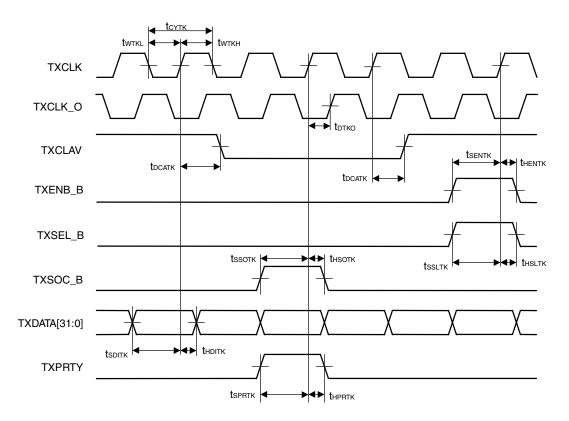

| TXCLK                | 253                                                                                                                                                                                 | F24                                                                                                                                                                                                                          | l<br>LVTTL | Transmit FIFO clock input.<br>This pin inputs the clock, from 8 to 104 MHz, used to<br>transfer transmit data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TXCLK_O              | 167                                                                                                                                                                                 | E25                                                                                                                                                                                                                          | O<br>LVTTL | Transmit FIFO clock return output.<br>This pin returns and outputs the clock input to TXCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TXSOC                | 331                                                                                                                                                                                 | G23                                                                                                                                                                                                                          | I<br>LVTTL | Transmit cell start position signal input.<br>This pin inputs a signal that indicates the start position of a transmit cell. The $\mu$ PD98414 recognizes the clock cycle in which TXSOC is high as the first word of a cell.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TXCLAV               | 71                                                                                                                                                                                  | F26                                                                                                                                                                                                                          | O<br>LVTTL | Transmit FIFO cell data reception enable signal output.<br>This signal posts notification of the vacancy of the transmit<br>FIFO to the ATM layer device. If the number of cells stored<br>in the transmit FIFO has reached the threshold value set by<br>the TCAV[1:0] bits of the MDR5 register, the $\mu$ PD98414<br>drives TXCLAV low. The threshold value can be selected<br>from 9, 11, 13, or 15 cells. The default value is 15 cells, at<br>which point the transmit FIFO is full. The $\mu$ PD98414 keeps<br>receiving cells, even if TXCLAV is driven low, until the<br>transmit FIFO is full (i.e., 15 cells). The 16th and<br>subsequent cells are dropped and the $\mu$ PD98414 reports an<br>overflow of the transmit FIFO. |

| Pin Name             | Serial No.                                                                                                                                                                          | Address No.                                                                                                                                                                                     | I/O, Level                          | (3/3) Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXENB_B              | 165                                                                                                                                                                                 | G25                                                                                                                                                                                             | I<br>LVTTL                          | <ul> <li>Transmit enable signal input (byte unit control).</li> <li>This signal indicates, in byte units, that the ATM layer device has output valid transmit cell data to TXDATA. The μPD98414 samples TXENB_B at the rising edge of TXCLK.</li> <li>If TXENB_B is low, it loads the data on TXSOC and TXDATA to the transmit FIFO at the edge of TXCLK. If TXENB_B is high, the data on TXSOC and TXDATA is not loaded to the transmit FIFO.</li> <li>Caution This signal cannot be used with RXSEL_B at the same time. Fix this signal to the low level</li> </ul>                                                                                                                                                                                                                                                                                                                                               |

| TXSEL_B              | 252                                                                                                                                                                                 | G24                                                                                                                                                                                             | I<br>LVTTL                          | when it is not used.Transmit enable signal input (cell unit control).This signal informs the $\mu$ PD98414, in cell units, that theATM layer device is outputting valid transmit cell data toTXDATA.The $\mu$ PD98414 samples TXSEL_B at the rising edge of theTXCLK clock immediately before a high level is input toTXSOC when it receives a transmit cell from the ATM layerdevice. If TXSEL_B is low, the $\mu$ PD98414 loads the cellinput in the next clock cycle to the transmit FIFO. Once the $\mu$ PD98414 has detected the low level of TXSEL_B andstarted loading the cell, it does not sample TXSEL_B untilthe next TXSOC input). If TXSEL_B is high at the clockimmediately before the high level is input to TXSOC, the $\mu$ PD98414 loads the next cell to the transmit FIFO.Caution This signal cannot be used with RXSEL_B atthe same time. Fix this signal to the low levelwhen it is not used. |

| TXPRTY               | 70                                                                                                                                                                                  | G26                                                                                                                                                                                             | I<br>LVTTL<br>(Internal<br>pull-up) | Parity bit input.<br>This pin inputs the odd parity bit of the data input to<br>TXDATA. The $\mu$ PD98414 calculates a parity based on the<br>input data and parity bit. If it detects an error, it sets the<br>UPED bit of the UEDR register to report the error. The<br>$\mu$ PD98414 calculates a parity only within the range of 53<br>bytes of the a transmit cell (H1 to P48). An even parity can<br>be also used depending on the setting of the TRPM bit of<br>the MDR5 register.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TXDATA31-<br>TXDATA0 | 164, 69, 328,<br>68, 162, 248,<br>161, 66, 247,<br>160, 246, 325,<br>64, 158, 62,<br>157, 61, 323,<br>243, 60, 242,<br>59, 154, 241,<br>320, 153, 152,<br>239, 151, 318,<br>55, 237 | H25, H26, K23,<br>J26, K25, L24,<br>L25, L26, M24,<br>M25, N24, N23,<br>N26, P25, R26,<br>R25, T26, R23,<br>T24, U26, U24,<br>V26, V25, V24,<br>V23, W25, V25,<br>Y24, AA25, Y23,<br>AB26, AB24 | I<br>LVTTL                          | Transmit cell data input bus.<br>These pins form a 32-bit data bus through which transmit<br>cell data is input. The $\mu$ PD98414 inputs the data on this bus<br>at the rising edge of TXCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

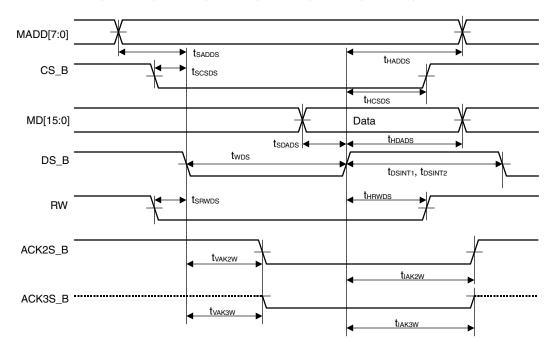

#### 1.3 Management Interface

The management interface is used to access the registers of the  $\mu$ PD98414.

| Pin Name             | Serial No.                                                                               | Address No.                                                                                   | I/O, Level                             | Function                                                                                                                                                                                                                                                                                                                                           |

|----------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

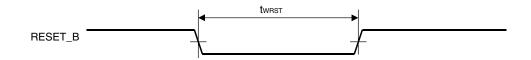

| RESET_B              | 168                                                                                      | D25                                                                                           | I<br>LVTTL<br>(5V tolerant)            | System reset input.<br>This signal initializes the $\mu$ PD98414. Input a low-pulse<br>signal having a width of at least 100 ns.                                                                                                                                                                                                                   |

| PHINT_B              | 74                                                                                       | C26                                                                                           | O<br>LVTTL<br>(5V tolerant)            | Interrupt signal output.<br>This signal informs the host of occurrence of an interrupt<br>cause.                                                                                                                                                                                                                                                   |

| BMODE                | 333                                                                                      | E23                                                                                           | I<br>LVTTL<br>(5V tolerant)            | Bus mode select input.<br>The mode of the management interface is determined from<br>the input level of this signal after a reset.<br>BMODE =<br>Low: <ds, ack="" r="" w,=""> -type is selected.<br/>High: <rd, rdy="" wr,=""> -type is selected.</rd,></ds,>                                                                                      |

| MADD7-<br>MADD0      | 335, 78, 172,<br>79, 258, 173,<br>80, 259                                                | D22, A24, B23,<br>A23, C22, B22,<br>A22, C21                                                  | I<br>LVTTL<br>(5V tolerant)            | Address input.<br>These pins form the 8-bit bus used to input the addresses of<br>the internal registers.                                                                                                                                                                                                                                          |

| MD15-MD0             | 337, 174, 81,<br>260, 175, 82,<br>176, 339, 83,<br>262, 177, 340,<br>84, 263, 178,<br>85 | D20, B21, A21,<br>C20, B20, A20,<br>B19, D18, A19,<br>C18, B18, D17,<br>A18, C17, B17,<br>A17 | I/O<br>LVTTL<br>(5V tolerant)          | 16-bit data bus.<br>This 16-bit data bus is used to exchange data with the<br>internal registers.                                                                                                                                                                                                                                                  |

| RW<br>(WR_B)         | 77                                                                                       | A25                                                                                           | I<br>LVTTL<br>(5V tolerant)            | Read/write signal input or write signal input.<br>The function of this signal differs depending on the mode set<br>by BMODE.<br>When BMODE = low, it functions as a read/write control<br>signal (RW).<br>RW = High: Ready cycle<br>Low: Write cycle<br>When BMODE = high, it functions as a write signal<br>(WR_B) that specifies a write access. |

| ACK2S_B<br>(RDY2S_B) | 257                                                                                      | C23                                                                                           | O<br>LVTTL<br>(5V tolerant)            | Acknowledge signal output or ready signal two-state output.<br>This pin indicates that data is ready when it is accessed for<br>read. It outputs an acknowledge ready signal, which<br>indicates that data can be received, in two states during the<br>write cycle.                                                                               |

| ACK3S_B<br>(RDY3S_B) | 171                                                                                      | B24                                                                                           | O<br>3-state<br>LVTTL<br>(5V tolerant) | Acknowledge signal output or ready signal tristate output.<br>This pin indicates that data is ready when it is accessed for<br>read. It outputs an acknowledge ready signal, which<br>indicates that data can be received, in tristate during the<br>write cycle.                                                                                  |

| CS_B                 | 255                                                                                      | D24                                                                                           | I<br>LVTTL<br>(5V tolerant)            | Chip select signal input.<br>When this signal is low, access to the internal registers of the $\mu$ PD98414 is enabled.                                                                                                                                                                                                                            |

|                |            |             |                             | (2/2)                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|------------|-------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name       | Serial No. | Address No. | I/O, Level                  | Function                                                                                                                                                                                                                                                                                                                                                                 |

| DS_B<br>(RD_B) | 169        | C25         | I<br>LVTTL<br>(5V tolerant) | Data strobe signal input or read signal input.<br>The function of this pin differs depending on the<br>management interface mode selected by the input to the<br>BMODE pin.<br>BMODE = low: Functions as a data strobe signal<br>(DS_B) that indicates that data is output<br>to MD.<br>BMODE = high: Functions as a read signal (RD_B) that<br>specifies a read access. |

#### 1.4 Overhead Interface

The overhead interface is used to transfer the contents of the section overhead (SOH) and path overhead (POH) that are exchanged between the peripheral device and  $\mu$ PD98414.

|                   | -                   |                           |                                                       | (1/2)                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|---------------------|---------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name          | Serial No.          | Address No.               | I/O, Level                                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

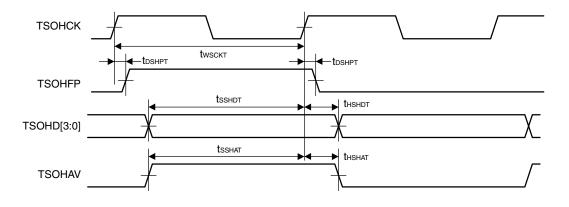

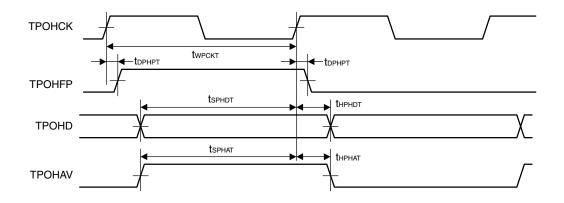

| TSOHCK            | 295                 | AB04                      | O<br>LVTTL                                            | Transmit TOH interface clock output (25.92 MHz).<br>This pin outputs a 25.92-MHz clock obtained by internally<br>dividing transmit clock TCLK (155.52 MHz) by six. TSOHFP<br>and TSOHD are output in sync with this divided clock.                                                                                                                                                                                                                       |