# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

#### 16/8 BIT SINGLE-CHIP MICROCOMPUTER

The μPD78P368A is produced by replacing the internal mask ROM of the μPD78366A with a one-time PROM or EPROM. One-time PROM products, in which data can be written once are effective for manufacture of small quantities of multiple products and early stage start-up of application. EPROM products, to which programs can be re-written after previously written programs have been erased, are suited for system evaluation.

The following user's manual describes the details of functions. Be sure to read it before design.

$\mu$ PD78366A User's Manual, Hardware: U10205E  $\mu$ PD78356 User's Manual, Instructions: IEU-1395

#### **FEATURES**

- Compatible with the μPD78366A

- Can be replaced with the  $\mu$ PD78366A containing mask ROM on a full-production basis.

- Internal PROM: 48K bytes

- Data can be written once (one-time PROM product without an erasure window)

- · Written data can be erased by exposure to ultraviolet light and re-written electrically (EPROM product with an

- PROM programming characteristics: Compatible with the  $\mu$ PD27C1001A

- QTOP<sup>TM</sup> microcomputer

Remark The QTOP microcomputer is a single-chip microcomputer with a built-in one-time PROM that is totally supported by NEC. The support includes writing application programs, marking, screening, and verification.

#### ORDERING INFORMATION

| Part number                                    | Package                                                    | Internal ROM           |

|------------------------------------------------|------------------------------------------------------------|------------------------|

| μPD78P368AGF-3B9<br>μPD78P368AKL-S <b>Note</b> | 80-pin plastic QFP (14 $\times$ 20 mm) 80-pin ceramic WQFN | One-time PROM<br>EPROM |

Note Under development

In this manual, the description of the PROM is for both a one-time PROM and EPROM.

The information in this document is subject to change without notice.

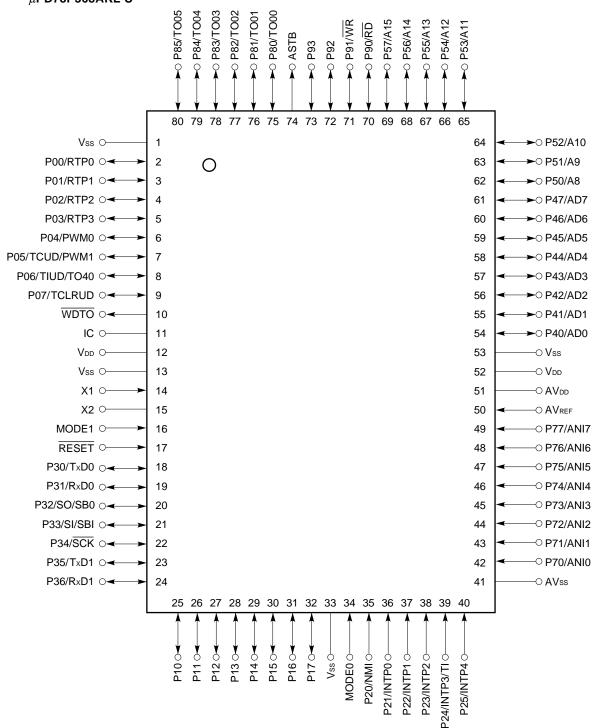

## **PIN CONFIGURATION (TOP VIEW)**

- (1) Normal operation mode (MODE0 = L, MODE1 = L)

- 80-pin plastic QFP (14  $\times$  20 mm)  $\mu$ PD78P368AGF-3B9

- 80-pin ceramic WQFN μPD78P368AKL-S

Caution Directly connect the IC pin to Vss.

**Remark** Pin compatible with the  $\mu$ PD78366AGF

Port 0 P00-P07: P10-P17: Port 1 P20-P25: Port 2 P30-P36: Port 3 Port 4 P40-P47: P50-P57: Port 5 P70-P77: Port 7 P80-P85: Port 8 P90-P93: Port 9

RTP0-RTP3: Real-time port

NMI: Nonmaskable interrupt INTP0-INTP4: Interrupt from peripherals

TO00-TO05, TO40: Timer output TI: Timer input

TIUD: Timer input for up/down

counter

TCUD: Timer control for up/down

counter

TCLRUD: Timer clear for up/down

counter

ANI0-ANI7: Analog input TxD0, TxD1: Transmit data RxD0, RxD1: Receive data

SI: Serial input

SO: Serial output

SB0, SB1: Serial bus

SCK: Serial clock

PWM0, PWM1: Pulse width modulation output

WDTO: Watchdog timer output

MODE0, MODE1: Mode

AD0-AD7: Address/data bus

A8-A15: Address bus

ASTB: Address strobe

RD: Read strobe

WR: Write strobe

RESET: Reset

X1, X2: Crystal

AVDD: Analog VDD

AVSS: Analog VSS

AVREF: Analog reference voltage

VDD: Power supply

Vss: Ground

IC:

Internally connected

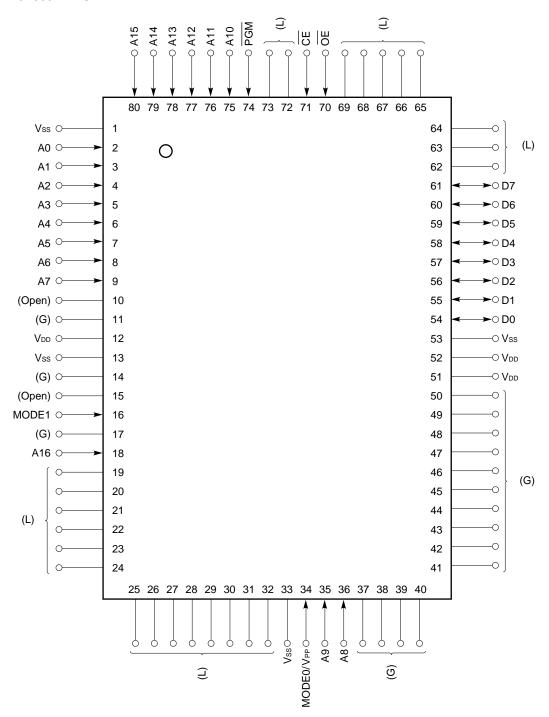

- (2) PROM programming mode (MODE0/VPP = H, MODE1 = L)

- 80-pin plastic QFP (14  $\times$  20 mm)  $\mu$ PD78P368AGF-3B9

- 80-pin ceramic WQFN μPD78P368AKL-S

Caution Symbols in parentheses denote how the pins not used in the PROM programming mode should be treated.

- L: Connect these pins to the Vss pins through separate resistors.

- G: Connect these pins to the Vss pins.

Open: Do not connect these pins to anything.

A0-A16: Address bus MODE0, MODE1: Programming mode set

D0-D7: Data bus VPP: Programming power supply

CE:Chip enableVDD:Power supplyOE:Output enableVss:Ground

PGM: Programming mode

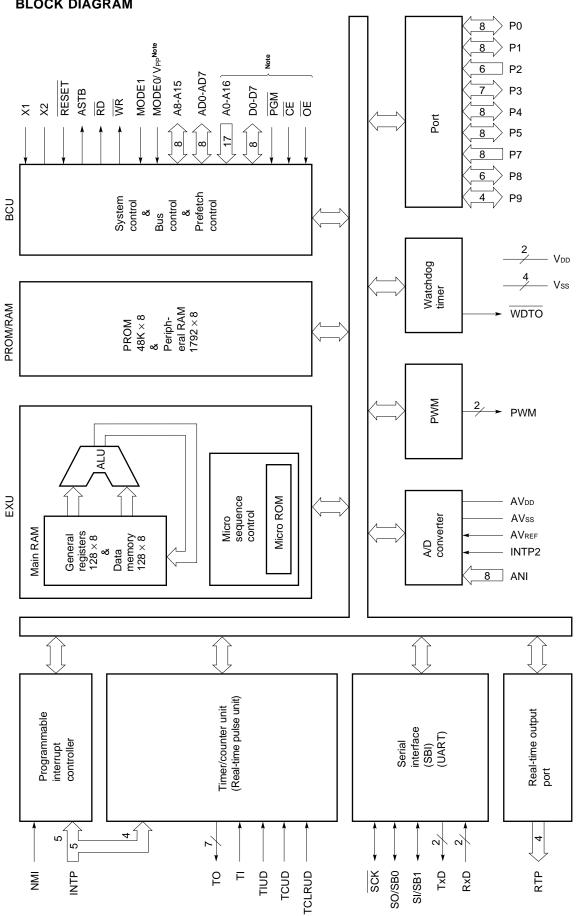

## **BLOCK DIAGRAM**

Note Shading indicates the pins used in the PROM programming mode.

# **CONTENTS**

| 1.  | PIN FUNCTIONS                                                          | 8  |

|-----|------------------------------------------------------------------------|----|

|     | 1.1 NORMAL OPERATION MODE (MODE0 = L, MODE1 = L)                       | 8  |

|     | 1.2 PROM PROGRAMMING MODE (MODE0/VPP = H, MODE1 = L)                   | 10 |

|     | 1.3 INPUT/OUTPUT CIRCUIT TYPE FOR EACH PIN AND HANDLING OF UNUSED PINS | 11 |

| 2.  | MEMORY CONFIGURATION                                                   | 13 |

| 3.  | DIFFERENCES BETWEEN THE $\mu$ PD78P368A AND $\mu$ PD78366A             | 14 |

| 4.  | PROM PROGRAMMING                                                       | 15 |

|     | 4.1 OPERATION MODE                                                     | 15 |

|     | 4.2 PROCEDURE FOR WRITING ON PROM (PAGE PROGRAM MODE)                  | 16 |

|     | 4.3 PROCEDURE FOR WRITING ON PROM (BYTE PROGRAM MODE)                  | 18 |

|     | 4.4 PROCEDURE FOR READING FROM PROM                                    | 21 |

| 5.  | ERASURE CHARACTERISTICS (μPD78P368AKL-S ONLY)                          | 22 |

| 6.  | PROTECTIVE FILM COVERING THE ERASURE WINDOW (µPD78P368AKL-S ONLY)      | 22 |

| 7.  | SCREENING ONE-TIME PROM PRODUCTS                                       | 22 |

| 8.  | ELECTRICAL SPECIFICATIONS                                              | 23 |

| 9.  | PACKAGE DRAWINGS                                                       | 39 |

| 10. | RECOMMENDED SOLDERING CONDITIONS                                       | 41 |

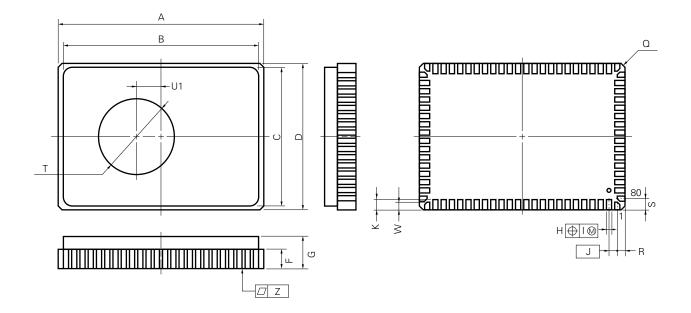

| ΑP  | PENDIX A TOOLS                                                         | 42 |

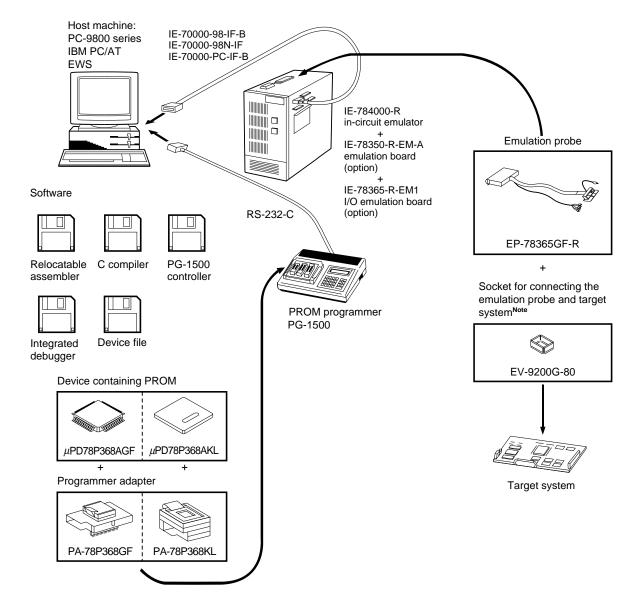

|     | A.1 DEVELOPMENT TOOLS                                                  | 42 |

|     | A.2 EMBEDDED SOFTWARE                                                  | 47 |

| ΑP  | PENDIX B DIMENSIONS OF THE CONVERSION SOCKET AND RECOMMENDED           |    |

|     | DATTEDN ON BOADDS                                                      | 40 |

# 1. PIN FUNCTIONS

# 1.1 NORMAL OPERATION MODE (MODE0 = L, MODE1 = L)

# (1) Port pins

| Pin name | I/O | Function                                                                        | Dual-function pin |

|----------|-----|---------------------------------------------------------------------------------|-------------------|

| P00-P03  | I/O | Port 0.                                                                         | RTP0-RTP3         |

| P04      |     | 8-bit I/O port.                                                                 | PWM0              |

| P05      |     | Can be specified as input or output bit by bit.                                 | TCUD/PWM1         |

| P06      |     |                                                                                 | TIUD/TO40         |

| P07      |     |                                                                                 | TCLRUD            |

| P10-P17  | I/O | Port 1. 8-bit I/O port. Can be specified as input or output bit by bit.         | -                 |

| P20      | I   | Port 2.                                                                         | NMI               |

| P21      |     | Port used only for 6-bit input.                                                 | INTP0             |

| P22      |     |                                                                                 | INTP1             |

| P23      |     |                                                                                 | INTP2             |

| P24      |     |                                                                                 | INTP3/TI          |

| P25      |     |                                                                                 | INTP4             |

| P30      | I/O | Port 3.                                                                         | TxD0              |

| P31      |     | 7-bit I/O port.  Can be specified as input or output bit by bit.                | RxD0              |

| P32      |     |                                                                                 | SO/SB0            |

| P33      |     |                                                                                 | SI/SB1            |

| P34      |     |                                                                                 | SCK               |

| P35      |     |                                                                                 | TxD1              |

| P36      |     |                                                                                 | RxD1              |

| P40-P47  | I/O | Port 4. 8-bit I/O port. Can be specified as input or output in units of 8 bits. | AD0-AD7           |

| P50-P57  | I/O | Port 5. 8-bit I/O port. Can be specified as input or output bit by bit.         | A8-A15            |

| P70-P77  | 1   | Port 7. Port used only for 8-bit input.                                         | ANIO-ANI7         |

| P80-P85  | I/O | Port 8. 6-bit I/O port. Can be specified as input or output bit by bit.         | TO00 - TO05       |

| P90      | I/O | Port 9.                                                                         | RD                |

| P91      |     | 4-bit I/O port.                                                                 | WR                |

| P92      |     | Can be specified as input or output bit by bit.                                 | _                 |

| P93      |     |                                                                                 | _                 |

# (2) Non-port pins (1/2)

| Pin name  | I/O | Function                                                                                                                                                           | Dual-function pin |

|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| RTP0-RTP3 | 0   | Outputs a pulse in real time as triggered by a trigger signal sent from the real-time pulse unit.                                                                  | P00-P03           |

| NMI       | I   | Nonmaskable interrupt request input                                                                                                                                | P20               |

| INTP0     |     | External interrupt request input                                                                                                                                   | P21               |

| INTP1     |     |                                                                                                                                                                    | P22               |

| INTP2     |     |                                                                                                                                                                    | P23               |

| INTP3     |     |                                                                                                                                                                    | P24/TI            |

| INTP4     |     |                                                                                                                                                                    | P25               |

| TI        | 1   | External count clock input to timer 1                                                                                                                              | P24/INTP3         |

| TCUD      |     | Input for the control signal to determine whether the up/down counter (timer 4) counts up or down.                                                                 | P05/PWM1          |

| TIUD      |     | External count clock input to the up/down counter (timer 4)                                                                                                        | P06/TO40          |

| TCLRUD    |     | Clear signal input to the up/down counter (timer 4)                                                                                                                | P07               |

| TO00-TO05 | 0   | Pulse output from the real-time pulse unit                                                                                                                         | P80-P85           |

| TO40      |     |                                                                                                                                                                    | P06/TIUD          |

| ANI0-ANI7 | I   | Analog input to the A/D converter                                                                                                                                  | P70-P77           |

| TxD0      | 0   | Serial data output from the asynchronous serial interface                                                                                                          | P30               |

| TxD1      |     |                                                                                                                                                                    | P35               |

| RxD0      | I   | Serial data input to the asynchronous serial interface                                                                                                             | P31               |

| RxD1      |     |                                                                                                                                                                    | P36               |

| SCK       | I/O | Serial clock I/O for the clock synchronous serial interface                                                                                                        | P34               |

| SI        | I   | Serial data input to the clock synchronous serial interface in the 3-wire mode                                                                                     | P33/SB1           |

| so        | 0   | Serial data output from the clock synchronous serial interface in the 3-wire mode                                                                                  | P32/SB0           |

| SB0       | I/O | Serial data I/O for the clock synchronous serial interface in the SBI mode                                                                                         | P32/SO            |

| SB1       |     |                                                                                                                                                                    | P33/SI            |

| PWM0      | 0   | PWM signal output                                                                                                                                                  | P04               |

| PWM1      |     |                                                                                                                                                                    | P05/TCUD          |

| WDTO      | 0   | Output for the signal which indicates the watchdog timer overflowed. (A nonmaskable interrupt is generated.)                                                       | -                 |

| AD0-AD7   | I/O | Multiplexed address/data bus used when external memory is expanded                                                                                                 | P40-P47           |

| A8-A15    |     | Address bus used when external memory is expanded                                                                                                                  | P50-P57           |

| ASTB      | 0   | Output for the timing signal used in externally latching address information output from the AD0 to AD7 and A8 to A15 pins, in order to access the external memory | -                 |

| RD        |     | Read strobe signal output to the external memory                                                                                                                   | P90               |

| WR        |     | Write strobe signal output to the external memory                                                                                                                  | P91               |

## (2) Non-port pins (2/2)

| Pin name        | I/O | Function                                                                             | Dual-function pin |

|-----------------|-----|--------------------------------------------------------------------------------------|-------------------|

| MODE0           | I   | Input for the control signal which sets the operation mode. Normally, both           | -                 |

| MODE1           |     | MODE0 and MODE1 are directly connected to the Vss pin.                               |                   |

| RESET           | I   | System reset input                                                                   | -                 |

| X1              | I   | Crystal input pin for the system clock. A clock signal provided externally is        | -                 |

| X2              | _   | input to the X1 pin. The reversed signal of the clock signal is input to the X2 pin. |                   |

| AVREF           | I   | A/D converter reference voltage input                                                | -                 |

| AVDD            | _   | Analog power supply for the A/D converter                                            | -                 |

| AVss            | _   | Ground for the A/D converter                                                         | _                 |

| V <sub>DD</sub> | _   | Positive power supply                                                                | -                 |

| Vss             | -   | Ground                                                                               | -                 |

| IC              | _   | Internally connected. Directly connect the IC pin to Vss.                            | _                 |

## 1.2 PROM PROGRAMMING MODE (MODE0/VPP = H, MODE1 = L)

| Pin name              | I/O | Function                                             |

|-----------------------|-----|------------------------------------------------------|

| MODE0/V <sub>PP</sub> | ı   | PROM programming mode set/programming supply voltage |

| MODE1                 | ı   | PROM programming mode set                            |

| A0-A16                | ı   | Address bus                                          |

| D0-D7                 | I/O | Data bus                                             |

| PGM                   | ı   | Program input                                        |

| CE                    | I   | Enable PROM                                          |

| ŌĒ                    | I   | Read strobe to PROM                                  |

| V <sub>DD</sub>       | _   | Positive power supply                                |

| Vss                   |     | GND                                                  |

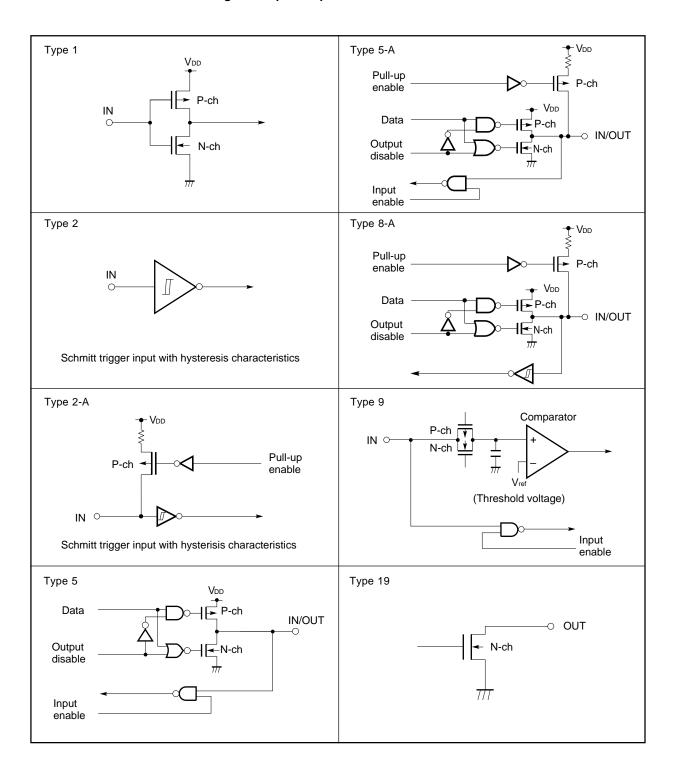

## 1.3 INPUT/OUTPUT CIRCUIT TYPE FOR EACH PIN AND HANDLING OF UNUSED PINS

Table 1-1 lists the input and output circuit type for each pin and how to handle it when it is not used. Fig. 1-1 shows the circuits.

Table 1-1 Input/Output Circuit Type for Each Pin and Recommended Connection Methods for Unused Pins

| Pin               | I/O circuit type | Recommended connection method                                |

|-------------------|------------------|--------------------------------------------------------------|

| P00/RTP0-P03/RTP3 | 5-A              | Input state: Each pin is connected to the V <sub>DD</sub> or |

| P04/PWM0          |                  | Vss pin via a separate resistor. Output state: Open          |

| P05/TCUD/PWM1     |                  | Output state: Open                                           |

| P06/TIUD/TO40     |                  |                                                              |

| P07/TCLRUD        |                  |                                                              |

| P10-P17           |                  |                                                              |

| P20/NMI           | 2                | Connected to the Vss pin.                                    |

| P21/INTP0         | 2-A              |                                                              |

| P22/INTP1         |                  |                                                              |

| P23/INTP2         |                  |                                                              |

| P24/INTP3/TI      |                  |                                                              |

| P25/INTP4         |                  |                                                              |

| P30/TxD0          | 5-A              | Input state: Each pin is connected to the VDD or             |

| P31/RxD0          |                  | Vss pin via a separate resistor.                             |

| P32/SO/SB0        | 8-A              | Output state: Open                                           |

| P33/SI/SB1        |                  |                                                              |

| P34/SCK           |                  |                                                              |

| P35/TxD1          | 5-A              |                                                              |

| P36/RxD1          |                  |                                                              |

| P40/AD0-P47/AD7   |                  |                                                              |

| P50/A8-P57/A15    |                  |                                                              |

| P70/ANI0-P77/ANI7 | 9                | Connected to the Vss pin.                                    |

| P80/TO00-P85/TO05 | 5-A              | Input state: Each pin is connected to the V <sub>DD</sub> or |

| P90/RD            |                  | Vss pin via a separate resistor.                             |

| P91/WR            |                  | Output state: Open                                           |

| P92, P93          |                  |                                                              |

| ASTB              | 5                |                                                              |

| WDTO              | 19               | Connected to the Vss pin.                                    |

| MODE0, MODE1      | 1                | -                                                            |

| RESET             | 2                |                                                              |

| AVREF, AVSS       | _                | Connected to the Vss pin.                                    |

| AVDD              |                  | Connected to the VDD pin.                                    |

Fig. 1-1 Input/Output Circuits of Each Pin

#### 2. MEMORY CONFIGURATION

The  $\mu$ PD78P368A can access memory of up to 64K bytes. Fig. 2-1 shows the memory map.

MODE 0, 1 = LL **FFFFH** Special function register (SFR) FEFFH General register  $(256 \times 8)$ FF00H  $(128 \times 8)$ FE80H **FEFFH** FE25H Main RAM Macro service control  $(256 \times 8)$  $(32 \times 8)$ FE06H Data memory FDFFH Peripheral RAM Data area  $(1792 \times 8)$  $(2048 \times 8)$ F700H F700H F6FFH BFFFH Memory Program area space External memory Note 1000H  $(64K \times 8)$  $(14080 \times 8)$ 0FFFH CALLF instruction entry area  $(2048 \times 8)$ H0080 07FFH Program C000H Program area memory **BFFFH** 0080H Data 007FH memory **CALLT** instruction table area  $(64 \times 8)$ Internal PROM 0040H  $(49152 \times 8)$ 003FH Vector table area  $(64 \times 8)$ 0000H 0000H

Fig. 2-1 Memory Map

Note Access in the external memory expansion mode.

Caution When word access (including the stack operation) to the main RAM space (FE00H to FEFFH) is executed, the addresses specified in the operand must be even numbers.

## 3. DIFFERENCES BETWEEN THE $\mu$ PD78P368A AND $\mu$ PD78366A

The  $\mu$ PD78P368A is produced by replacing the internal mask ROM of the  $\mu$ PD78366A with a 48K-byte PROM. Both have the same functions except some differences in ROM specifications, such as write and verify modes. Table 3-1 shows the differences.

In this manual, the functions specific to the  $\mu$ PD78P368A are explained. For details of the other functions, refer to the  $\mu$ PD78366A document.

Table 3-1 Differences between the  $\mu$ PD78P368A and  $\mu$ PD78366A

| Part number Item                           | μPD78                                                                                                                            | μPD78366A                                                                   |                    |  |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------|--|--|

| ROM                                        | 48K bytes                                                                                                                        | 32K bytes                                                                   |                    |  |  |

| Internal program memory (Electrical write) | One-time PROM EPROM (Data can be Written multiple times)                                                                         |                                                                             | Mask ROM           |  |  |

| PROM programming pin                       | Provided                                                                                                                         | Not provided                                                                |                    |  |  |

| Setting of MODE0 and MODE1                 | Normal operation mode     MODE0, 1 = LL     PROM programming mode     MODE0, 1 = HL                                              | Normal operation mode     MODE0, 1 = LL     ROM-less mode     MODE0, 1 = HH |                    |  |  |

| Package                                    | 80-pin plastic QFP 80-pin ceramic WQFN                                                                                           |                                                                             | 80-pin plastic QFP |  |  |

| Electrical characteristics                 | They differ in supply current and other factors.                                                                                 |                                                                             |                    |  |  |

| Others                                     | Since each product has a different circuit scale and mask layout, the noise immunity and noise radiation of each product differ. |                                                                             |                    |  |  |

- Cautions 1. The PROM and mask ROM products differ in noise immunity and noise radiation. Use not ES products but CS products (mask ROM products) to evaluate them thoroughly when considering the change from the PROM products to the mask ROM products during processes from preproduction to volume production.

- 2. Connect the MODE0 and MODE1 pins directly to the VDD or Vss pin.

#### 4. PROM PROGRAMMING

The  $\mu$ PD78P368A is provided with an electrically writable PROM of 48K×8 bits. When programming this PROM, use the MODE0/V<sub>PP</sub> and MODE1 pins to set the  $\mu$ PD78P368A to the PROM programming mode.

The  $\mu$ PD78P368A provides programming characteristics compatibility with the  $\mu$ PD27C1001A.

Table 4-1 Pin Functions in Programming Mode

| Function        | Normal operation mode Programming mod |        |  |  |  |

|-----------------|---------------------------------------|--------|--|--|--|

| Address input   | P00-P07, P21, P20, P80-P85, P30       | A0-A16 |  |  |  |

| Data input      | P40-P47                               | D0-D7  |  |  |  |

| Program pulse   | ASTB                                  | PGM    |  |  |  |

| Chip enable     | P91 CE                                |        |  |  |  |

| Output enable   | P90 OE                                |        |  |  |  |

| Program voltage | MODE0/V <sub>PP</sub>                 |        |  |  |  |

| Mode control    | MODE1                                 |        |  |  |  |

#### **4.1 OPERATION MODE**

To enter the program write/verify mode, set each pin as follows: MODE0/VPP = H, MODE1 = L. In addition, any of the operation modes listed in Table 4-2 can be selected by setting the  $\overline{\text{CE}}$ ,  $\overline{\text{OE}}$ , and  $\overline{\text{PGM}}$  pins in this mode.

Set the  $\mu$ PD78P368A to the read mode in order to read the contents of PROM.

Handle unused pins as described in PIN CONFIGURATION (2).

Table 4-2 Operation Modes for PROM Programming

| Mode            | MODE1 | CE | ŌE | PGM | MODE0/V <sub>PP</sub> | V <sub>DD</sub> | D0-D7          |

|-----------------|-------|----|----|-----|-----------------------|-----------------|----------------|

| Page data latch | L     | Н  | L  | Н   | +12.5 V               | +6.5 V          | Data input     |

| Page program    |       | Н  | Н  | L   |                       |                 | High impedance |

| Byte program    |       | L  | Н  | L   |                       |                 | Data input     |

| Program verify  |       | L  | L  | Н   |                       |                 | Data output    |

| Program inhibit |       | ×  | L  | L   |                       |                 | High impedance |

|                 |       | ×  | Н  | Н   |                       |                 |                |

| Read            |       | L  | L  | Н   | +5 V                  | +5 V            | Data output    |

| Output disable  |       | L  | Н  | ×   |                       |                 | High impedance |

| Standby         |       | Н  | ×  | ×   |                       |                 | High impedance |

Remark ×: L or H

#### 4.2 PROCEDURE FOR WRITING ON PROM (PAGE PROGRAM MODE)

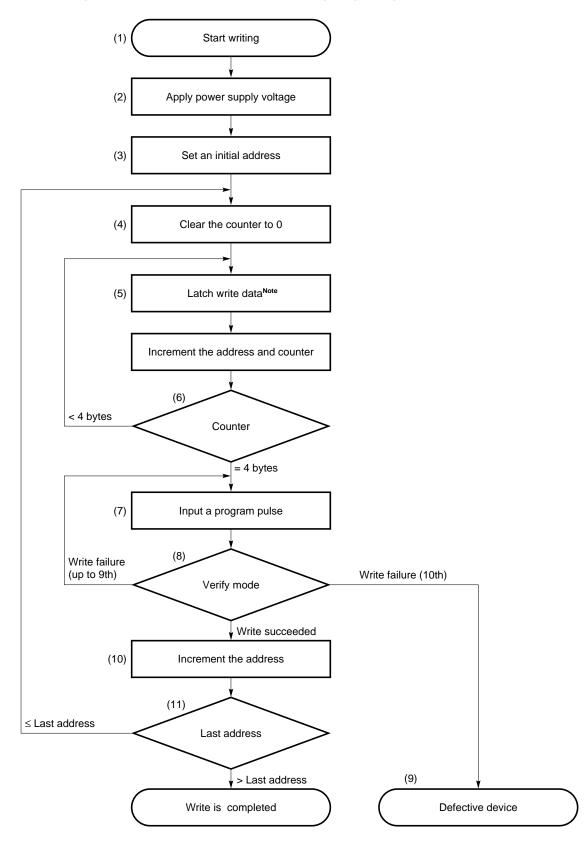

The following is a procedure for writing on PROM. (See Fig. 4-1.)

In the page program mode, data is written in units of pages (four bytes). When write data completes midway of a page, latch FFH after the data so that the data fits into pages.

- (1) Always set each pin as follows: MODE0/VPP = H and MODE1 = L. Connect unused pins according to PIN CONFIGURATION (2).

- (2) Apply +6.5 V to the VDD pin and +12.5 V to the VPP pin.

- (3) Input an initial address to the A0 to A16 pins.

- (4) Clear the page counter.

- (5) Data latch mode. Input write data to the D0 to D7 pins and input an active-low pulse to the  $\overline{\sf OE}$  pin. Increment the address and the page counter.

- (6) Repeat step (5) for a page (four bytes).

- (7) Input a 0.1 ms program pulse (active low) to the  $\overline{PGM}$  pin.

- (8) Verify mode. Checks if data has been written in PROM.

Apply a low level to the  $\overline{CE}$  pin, input an active-low pulse to the  $\overline{OE}$  pin, and then read the write data from the D0 to D7 pins. Repeat this for a page (four bytes). When verification completes, apply a high level to the  $\overline{CE}$  pin.

- If data has been written, go to step (10).

- If not, repeat steps (7) and (8). If no data is written yet after the steps have been repeated 10 times, go to step (9).

- (9) Assume the device to be defective and stop write operation.

- (10) Increment the address.

- (11) Repeat steps (4) to (10) until the address exceeds the last address.

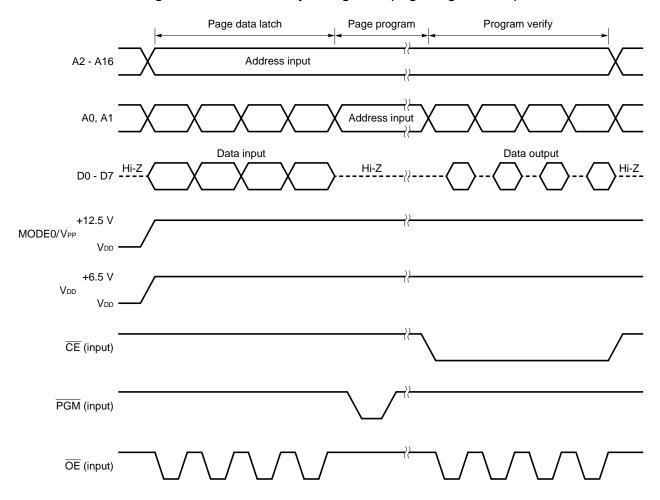

Fig. 4-2 is a timing chart of these steps (2) to (9).

Fig. 4-1 Flowchart of Procedure for Writing (Page Program Mode)

**Note** If write data does not fill a page, latch FFH for the rest of the page.

Fig. 4-2 PROM Write/Verify Timing Chart (Page Program Mode)

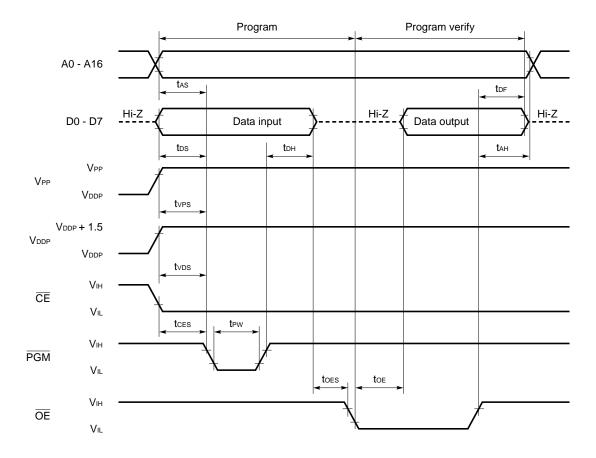

#### 4.3 PROCEDURE FOR WRITING ON PROM (BYTE PROGRAM MODE)

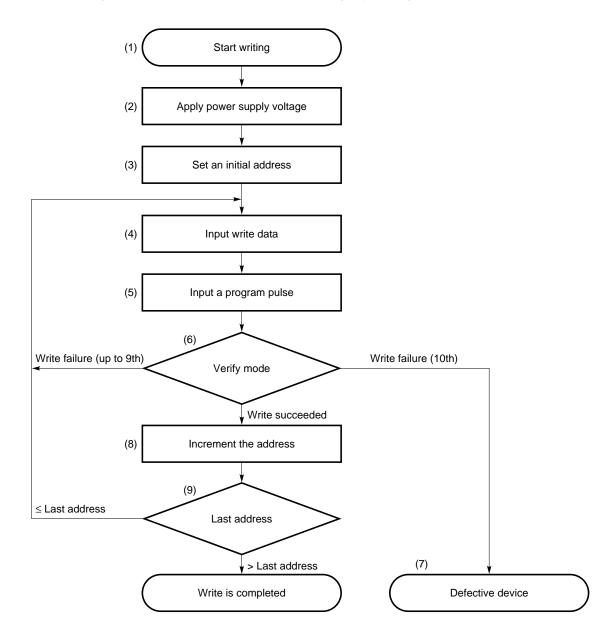

The following is a procedure for writing on PROM. (See Fig. 4-3.)

- (1) Always set each pin as follows: MODE0/VPP = H and MODE1 = L. Connect unused pins according to PIN CONFIGURATION (2).

- (2) Apply +6.5 V to the V<sub>DD</sub> pin and +12.5 V to the MODE0/V<sub>PP</sub> pin, and input a low-level signal to the  $\overline{\text{CE}}$  pin.

- (3) Input an initial address to the A0 to A16 pins.

- (4) Input write data to the D0 to D7 pins.

- (5) Input a 0.1 ms program pulse (active low) to the  $\overline{PGM}$  pin.

- (6) Verify mode. Checks if data has been written in PROM.

Input an active-low pulse to the  $\overline{OE}$  pin and read the write data from the D0 to D7 pins.

- If data has been written, go to step (8).

- If not, repeat steps (4) to (6). If no data is written yet after the steps have been repeated 10 times, go to step (7).

- (7) Assume the device to be defective and stop write operation.

- (8) Increment the address.

- (9) Repeat steps (4) to (8) until the address exceeds the last address.

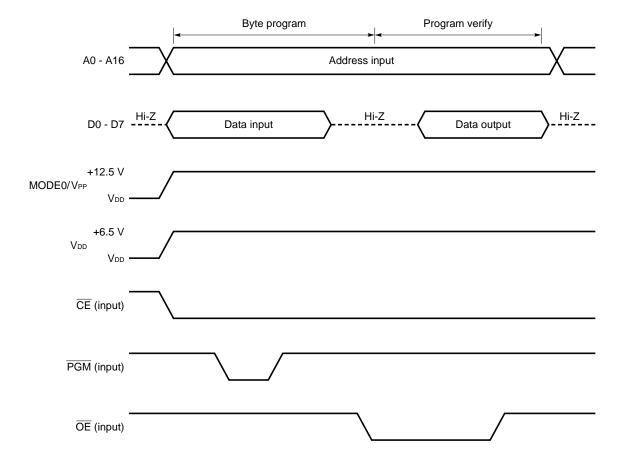

Fig. 4-4 is a timing chart of these steps (2) to (7).

Fig. 4-3 Flowchart of Procedure for Writing (Byte Program Mode)

Fig. 4-4 PROM Write/Verify Timing Chart (Byte Program Mode)

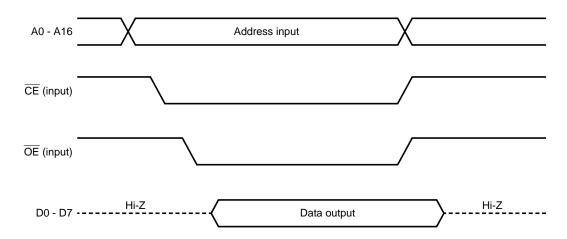

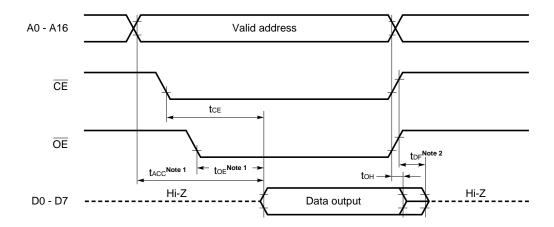

## 4.4 PROCEDURE FOR READING FROM PROM

The following is a procedure for reading out the contents of PROM to the external data bus (D0 to D7).

- (1) Always set each pin as follows: MODE0/VPP = H and MODE1 = L. Connect unused pins according to PIN CONFIGURATION (2).

- (2) Apply +5 V to the VDD and MODEO/VPP pins.

- (3) Input the address of data to be read into the A0 to A16 pins.

- (4) Read mode ( $\overline{CE} = L$ ,  $\overline{OE} = L$ )

- (5) Output the data on the D0 to D7 pins.

Fig. 4-5 is a timing chart of these steps (2) to (5).

Fig. 4-5 PROM Read Timing Chart

#### 5. ERASURE CHARACTERISTICS (µPD78P368AKL-S ONLY)

Data written in the  $\mu$ PD78P368AKL-S program memory can be erased (FFH); therefore users can write other data in the memory.

To erase the written data, expose the erasure window to light with a wavelength shorter than approx. 400 nm. Normally, ultraviolet light with a wavelength of 254 nm is employed. The amount of light required to completely erase the data is as follows:

- Intensity of ultraviolet light × erasing time: 15 W•s/cm² min.

- Erasing time: 15 to 20 minutes (When using a 12,000 μW/cm² ultraviolet lamp. It may, however, take more time due to lamp deterioration, dirt on the erasure window, or the like.)

The ultraviolet lamp should be placed within 2.5 cm from the erasure window during erasure. In addition, if a filter is attached to the ultraviolet lamp, remove the filter before erasure.

#### 6. PROTECTIVE FILM COVERING THE ERASURE WINDOW (μPD78P368AKL-S ONLY)

After the erasure window of the  $\mu$ PD78P368AKL-S has been exposed to sunlight or a fluorescent lamp for a long time, data in EPROM may be erased and the internal circuits may malfunction. To prevent these failures, the erasure window should be covered with a protective film when it is not used for erasure.

EPROM package products with a window are supplied with a NEC-guaranteed protective film when they are delivered.

## 7. SCREENING ONE-TIME PROM PRODUCTS

NEC cannot execute a complete test of one-time PROM products ( $\mu$ PD78P368AGF-3B9) due to their structure before shipment. It is recommended that you screen (verify) PROM products after writing necessary data into them and storing them at 125 °C for 24 hours.

NEC offers a charged service called QTOP microcomputer service. This service includes writing to one-time PROM, marking, screening, and verification. Ask your sales representative for details.

#### 8. ELECTRICAL SPECIFICATIONS

#### ABSOLUTE MAXIMUM RATINGS (TA = 25 °C)

| Parameter                             | Symbol           | Conditions                               | Rating                        | Unit |

|---------------------------------------|------------------|------------------------------------------|-------------------------------|------|

| Power supply voltage                  | V <sub>DD</sub>  |                                          | -0.5 to +7.0                  | V    |

|                                       | AVDD             |                                          | -0.5 to V <sub>DD</sub> + 0.5 | V    |

|                                       | VPP              |                                          | -0.5 to +13.5                 | V    |

|                                       | AVss             |                                          | -0.5 to +0.5                  | V    |

| Input voltage                         | Vı               | Pins other than<br>P70/ANI0-P77/ANI7     | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| Output voltage                        | Vo               |                                          | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| Low-level output current              | Іоь              | Note                                     | 20                            | mA   |

|                                       |                  | Output pins other than those in the note | 4.0                           | mA   |

|                                       |                  | Total of all output pins                 | 200                           | mA   |

| High-level output current             | Іон              | All output pins                          | -3.0                          | mA   |

|                                       |                  | Total of all output pins                 | -25                           | mA   |

| Analog input voltage                  | VIAN             | P70/ANI0-P77/ANI7 pins                   | AVss - 0.5 to AVDD + 0.5      | V    |

| A/D converter reference input voltage | AVREF            |                                          | AVss - 0.5 to AVDD + 0.5      | V    |

| Operating ambient temperature         | Та               |                                          | -40 to +85                    | °C   |

| Storage temperature                   | T <sub>stg</sub> |                                          | -60 to +150                   | °C   |

**Note** P00/RTP0-P03/RTP3, P04/PWM0, P05/TCUD/PWM1, P06/TIUD/TO40, P07/TCLRUD, P10-P17, and P80/TO00-P85/TO05 pins.

Caution Absolute maximum ratings are rated values beyond which some physical damages may be caused to the product; if any of the parameters in the table above exceeds its rated value even for a moment, the quality of the product may deteriorate. Be sure to use the product within the rated values.

## RECOMMENDED OPERATING CONDITIONS

| Oscillation frequency | TA            | V <sub>DD</sub> |

|-----------------------|---------------|-----------------|

| 3 MHz - fxx - 8 MHz   | −40 to +85 °C | +5.0 V ±10 %    |

#### CAPACITANCE (TA = 25 °C, Vss = VDD = 0 V)

| Parameter          | Symbol | Conditions               | Min. | Тур. | Max. | Unit |

|--------------------|--------|--------------------------|------|------|------|------|

| Input capacitance  | Cı     | f = 1 MHz                |      |      | 20   | pF   |

| Output capacitance | Со     | 0 V except measured pins |      |      | 20   | pF   |

| I/O capacitance    | Сю     |                          |      |      | 20   | pF   |

## OSCILLATOR CHARACTERISTICS (TA = -40 to +85 °C, VDD = +5 V ±10 %, Vss = 0 V)

| Resonator                    | Recommended circuit | Parameter                                   | Min. | Max. | Unit |

|------------------------------|---------------------|---------------------------------------------|------|------|------|

| Ceramic resonator or crystal | Vss X1 X2  C1 — C2  | Oscillation frequency (fxx)                 | 3    | 8    | MHz  |

| External clock               | 1                   | X1 input frequency (fx)                     | 3    | 8    | MHz  |

|                              | X1 X2 Open          | X1 rise/fall time (txR, txF)                | 0    | 30   | ns   |

|                              | HCMOS<br>inverter   | X1 input high-/low-level width (twxH, twxL) | 40   | 170  | ns   |

Caution When using system clock oscillation circuits, to reduce the effect of the wiring capacitance, etc, wire the area indicated by dotted-line as follows:

- · Make the wiring as short as possible.

- Do not allow the wiring to intersect other signal lines. Keep it away from other lines in which varying high currents flow.

- Make sure that the ground point of the oscillation circuit capacitor is always at the same electric

potential as Vss. Do not allow the wiring to be grounded to a ground pattern in which very high

currents are flowing.

- Do not extract signals from the oscillation circuit.

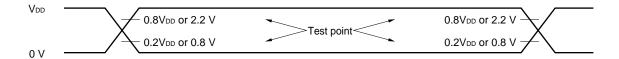

#### DC CHARACTERISTICS (TA = -40 to +85 °C, VDD = +5 V ±10 %, Vss = 0 V)

| Parameter                      | Symbol           |                | Conditions          | Min.                  | Тур. | Max.               | Unit |

|--------------------------------|------------------|----------------|---------------------|-----------------------|------|--------------------|------|

| Low-level input voltage        | VIL1             | Note 1         |                     | 0                     |      | 0.8                | ٧    |

|                                | VIL2             | Note 2         |                     | 0                     |      | 0.2V <sub>DD</sub> | ٧    |

| High-level input voltage       | V <sub>IH1</sub> | Note 1         |                     | 2.2                   |      |                    | ٧    |

|                                | V <sub>IH2</sub> | Note 2         |                     | 0.8Vpp                |      |                    | ٧    |

| Low-level output voltage       | V <sub>OL1</sub> | Note 3         | IoL = 2.0 mA        |                       |      | 0.45               | ٧    |

|                                | V <sub>OL2</sub> | Note 4         | IoL = 15 mA         |                       |      | 1.5                | ٧    |

|                                | Vol3             | Note 5         | IoL = 10 mA         |                       |      | 1.5                | ٧    |

| High-level output voltage      | Vон              | Іон = -400 μΑ  |                     | V <sub>DD</sub> - 1.0 |      |                    | ٧    |

| Input leakage current          | lu               | 0 V - Vı - VDD | , AVDD = VDD        |                       |      | ±10                | μΑ   |

| Output leakage current         | ILO              | 0 V - Vo - VD  | o, AVDD = VDD       |                       |      | ±10                | μΑ   |

| V <sub>DD</sub> supply current | I <sub>DD1</sub> | Operating mod  | de                  |                       | 70   | 120                | mA   |

|                                | I <sub>DD2</sub> | HALT mode      |                     |                       | 45   | 70                 | mA   |

| Data retention voltage         | VDDDR            | STOP mode      |                     | 2.5                   |      |                    | ٧    |

| Data retention current         | IDDDR            | STOP mode      | VDDDR = 2.5 V       |                       | 2    | 10                 | μΑ   |

|                                |                  |                | VDDDR = 5.0 V ±10 % |                       | 10   | 50                 | μΑ   |

| Pull-up resistance             | RL               | Vı = 0 V       |                     | 15                    | 60   | 150                | Κý   |

Notes 1. Pins other than those specified in Note 2.

- **2.** RESET, X1, X2, P20/NMI, P21/INTP0, P22/INTP1, P23/INTP2, P24/INTP3/TI, P25/INTP4, P32/SO/SB0, P33/SI/SB1 and P34/SCK pins.

- 3. Pins other than those specified in Notes 4 and 5.

- **4.** P80/T000-P85/T005 pins (When lo<sub>L</sub> = 15 mA is in operation, up to three pins can be ON simultaneously.)

- 5. P00/RTP0-P03/RTP3, P04/PWM0, P05/TCUD/PWM1, P06/TIUD/TO40 and P07/TCLRUD pins (When IoL = 10 mA is in operation, up to four pins can be ON simultaneously.) as well as P10-P17 pins (When IoL = 10 mA is in operation, up to four pins can be ON simultaneously.).

Caution When the P80-P85, P00-P07, and P10-P17 pins are not used under the conditions specified in Notes 4 and 5, they have the same characteristics as in Note 3.

AC CHARACTERISTICS (TA = -40 to +85 °C, VDD = +5 V  $\pm 10$  %, Vss = 0 V, CL = 100 pF, fxx = 8 MHz)

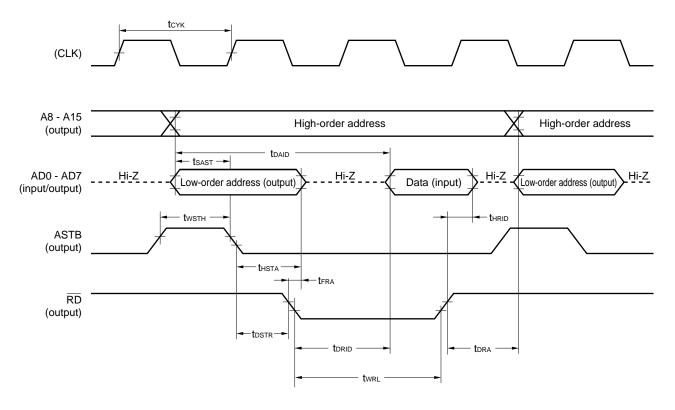

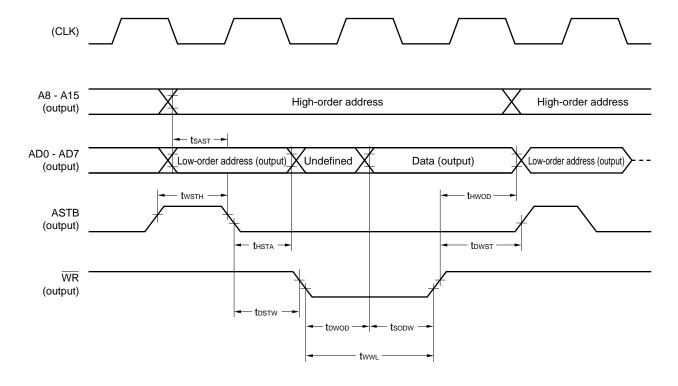

#### Read/Write Operation (when general-purpose memory is connected)

| Parameter                                                            | Symbol        | Conditions | Min. | Max.  | Unit |

|----------------------------------------------------------------------|---------------|------------|------|-------|------|

| System clock cycle time                                              | <b>t</b> cyk  |            | 62.5 | 166.7 | ns   |

| Address setup time (vs. ASTB ↓)                                      | <b>t</b> sast |            | 7    |       | ns   |

| Address hold time (vs. ASTB ↓)                                       | <b>t</b> HSTA |            | 11   |       | ns   |

| $\overline{RD} \downarrow 	o$ address float time                     | tfra          |            |      | 24    | ns   |

| Address → data input time                                            | tdaid         |            |      | 100   | ns   |

| $\overline{RD} \downarrow \to data$ input time                       | torid         |            |      | 49    | ns   |

| $ASTB \downarrow \to \overline{RD} \downarrow delay \ time$          | <b>t</b> DSTR |            | 15   |       | ns   |

| Data hold time (vs. $\overline{RD}$ ∞)                               | thrid         |            | 0    |       | ns   |

| $\overline{\text{RD}} \infty \rightarrow \text{address active time}$ | <b>t</b> DRA  |            | 17   |       | ns   |

| RD low-level width                                                   | twrL          |            | 63   |       | ns   |

| ASTB high-level width                                                | <b>t</b> wsTH |            | 14   |       | ns   |

| $\overline{\overline{WR}}\downarrow 	o data$ output time             | towod         |            |      | 21    | ns   |

| $ASTB \downarrow \to \overline{WR} \downarrow delay \; time$         | <b>t</b> DSTW |            | 15   |       | ns   |

| $\overline{WR}  \bowtie  ASTB  \bowtie  delay  time$                 | towst         |            | 78   |       | ns   |

| Data setup time (vs. WR ∞)                                           | tsodw         |            | 57   |       | ns   |

| Data hold time (vs. WR ∞)                                            | thwod         |            | 8    |       | ns   |

| WR low-level width                                                   | twwL          |            | 63   |       | ns   |

## tcүк-dependent Bus Timing Definition

| Parameter         | Arithmetic expression | Min./Max. | Unit |

|-------------------|-----------------------|-----------|------|

| tsast             | (0.5 + a) T – 24      | Min.      | ns   |

| <b>t</b> hsta     | 0.5T - 20             | Min.      | ns   |

| twsтн             | (0.5 + a) T – 17      | Min.      | ns   |

| tdstr             | 0.5T – 16             | Min.      | ns   |

| twrl              | (1.5 + n) T – 30      | Min.      | ns   |

| t <sub>DAID</sub> | (2.5 + a + n) T – 56  | Max.      | ns   |

| torio             | (1.5 + n) T – 44      | Max.      | ns   |

| tdra              | 0.5T – 14             | Min.      | ns   |

| tostw             | 0.5T – 16             | Min.      | ns   |

| towst             | 1.5T – 15             | Min.      | ns   |

| twwL              | (1.5 + n) T – 30      | Min.      | ns   |

| towod             | 0.5T - 10             | Max.      | ns   |

| tsopw             | (1 + n) T – 5         | Min.      | ns   |

**Remarks 1.** T = tcyk = 1/fck (fck refers to the internal system clock frequency.)

- 2. a becomes 1 when the address wait is inserted. Otherwise, it becomes 0.

- 3. n refers to the number of wait cycles that is inserted by specifying the PWC register.

- 4. Only the bus timings indicated in this table depend on tcyk.

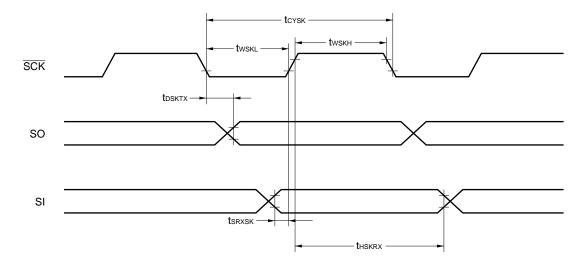

## SERIAL OPERATION (TA = -40 to +85 °C, V<sub>DD</sub> = +5 V $\pm 10$ %, Vss = 0 V)

| Parameter                                     | Symbol | Cond                 | litions             | Min. | Max. | Unit |

|-----------------------------------------------|--------|----------------------|---------------------|------|------|------|

| Serial clock cycle time                       | tcysk  | SCK output           | Internal 8 dividing | 500  |      | ns   |

|                                               |        | SCK input            | External clock      | 500  |      | ns   |

| Serial clock low-level width                  | twsĸL  | SCK output           | Internal 8 dividing | 210  |      | ns   |

|                                               |        | SCK input            | External clock      | 210  |      | ns   |

| Serial clock high-level width                 | twsкн  | SCK output           | Internal 8 dividing | 210  |      | ns   |

|                                               |        | SCK input            | External clock      | 210  |      | ns   |

| SI setup time (vs. SCK ∞)                     | tsrxsk |                      |                     | 80   |      | ns   |

| SI hold time (vs. SCK ∞)                      | thskrx |                      |                     | 80   |      | ns   |

| $\overline{SCK} \downarrow \to SO$ delay time | tosktx | R = 1 ký, C = 100 pF |                     |      | 210  | ns   |

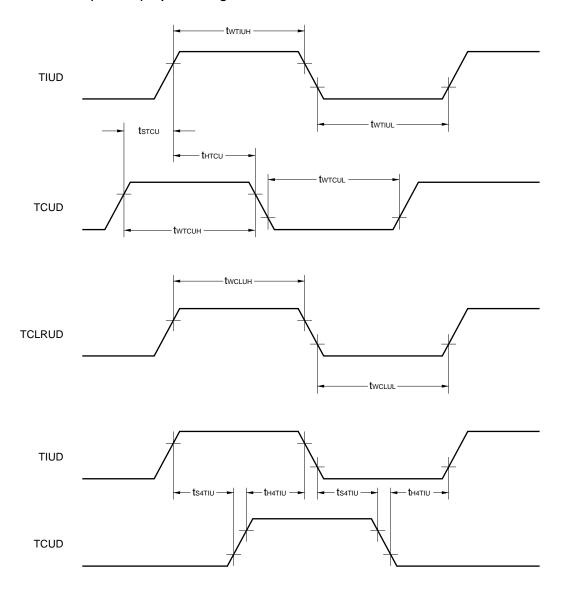

## UP/DOWN COUNTER OPERATION (TA = -40 to +85 °C, VDD = +5 V ±10 %, Vss = 0 V)

| Parameter                    | Symbol         | Conditions        | Min. | Max. | Unit |

|------------------------------|----------------|-------------------|------|------|------|

| TIUD high-/low-level width   | twтiuн, twтiuL | Other than mode 4 | 2T   |      | ns   |

|                              |                | Mode 4            | 4T   |      | ns   |

| TCUD high-/low-level width   | twтсин, twтсиL | Other than mode 4 | 2T   |      | ns   |

|                              |                | Mode 4            | 4T   |      | ns   |

| TCLRUD high-/low-level width | twcluн, twcluL |                   | 2T   |      | ns   |

| TCUD setup time (vs. TIUD ∞) | <b>t</b> sTCU  | Mode 3            | Т    |      | ns   |

| TCUD hold time (vs. TIUD ∞)  | tнтси          | Mode 3            | Т    |      | ns   |

| TIUD setup time (vs. TCUD)   | ts4TIU         | Mode 4            | 2T   |      | ns   |

| TIUD hold time (vs. TCUD)    | <b>t</b> н4ті∪ | Mode 4            | 2T   |      | ns   |

| TIUD & TCUD cycle time       | tcyc           | Other than mode 4 |      | 4    | MHz  |

|                              | tcYC4          | Mode 4            |      | 2    | MHz  |

**Remark** T = tcyk = 1/fclk (fclk refers to the internal system clock frequency.)

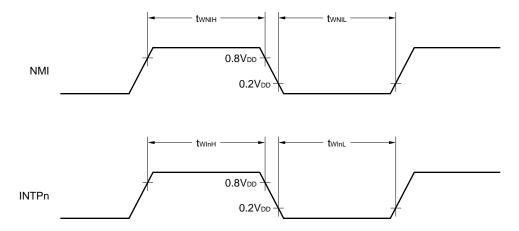

## OTHER OPERATIONS (TA = -40 to +85 °C, VDD = +5 V $\pm 10$ %, Vss = 0 V)

| Parameter                       | Symbol       | Conditions | Min. | Max. | Unit |

|---------------------------------|--------------|------------|------|------|------|

| NMI high-/low-level width       | twnih, twnil |            | 2    |      | μs   |

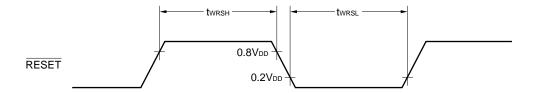

| RESET high-/low-level width     | twrsh, twrsl |            | 1.5  |      | μs   |

| INTP0 high-/low-level width     | twioh, twiol | Ts = T     | 250  |      | ns   |

|                                 |              | Ts = 4T    | 1.0  |      | μs   |

|                                 |              | Ts = 8T    | 2.0  |      | μs   |

|                                 |              | Ts = 16T   | 4.0  |      | μs   |

| INTP1 high-/low-level width     | twi1H, twi1L | Ts = T     | 250  |      | ns   |

|                                 |              | Ts = 4T    | 1.0  |      | μs   |

|                                 |              | Ts = 8T    | 2.0  |      | μs   |

|                                 |              | Ts = 16T   | 4.0  |      | μs   |

| INTP2 high-/low-level width     | twizh, twizl | Ts = T     | 250  |      | ns   |

|                                 |              | Ts = 4T    | 1.0  |      | μs   |

| INTP3(TI) high-/low-level width | twish, twish | Ts = T     | 250  |      | ns   |

|                                 |              | Ts = 4T    | 1.0  |      | μs   |

|                                 |              | Ts = 8T    | 2.0  |      | μs   |

|                                 |              | Ts = 16T   | 4.0  |      | μs   |

|                                 |              | Ts = 64T   | 16.0 |      | μs   |

|                                 |              | Ts = 128T  | 32.0 |      | μs   |

|                                 |              | Ts = 256T  | 64.0 |      | μs   |

| INTP4 high-/low-level width     | twi4H, twi4L | Ts = T     | 250  |      | ns   |

|                                 |              | Ts = 4T    | 1.0  |      | μs   |

|                                 |              | Ts = 8T    | 2.0  |      | μs   |

|                                 |              | Ts = 16T   | 4.0  |      | μs   |

**Remarks 1.** T = tcyk = 1/fck (fck refers to the internal system clock frequency.)

2. Ts refers to the input sampling frequency. INTP0-INTP4 can be selected to programmable.

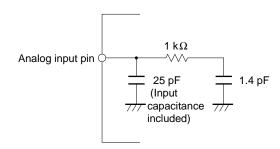

# A/D CONVERTER CHARACTERISTICS (Ta = -40 to +85 °C, $V_{DD}$ = +5 V ±10 %, $V_{SS}$ = AVss = 0 V, $V_{DD}$ - 0.5 V - AVDD - $V_{DD}$ )

| Parameter                  | Symbol        |                | Conditions         | Min. | Тур.   | Max.             | Unit         |

|----------------------------|---------------|----------------|--------------------|------|--------|------------------|--------------|

| Resolution                 |               |                |                    | 10   |        |                  | bit          |

| Total errorNote 1          |               | 4.5 V - AVREF  | - AV <sub>DD</sub> |      |        | ±0.4             | %FSR         |

|                            |               | 3.4 V - AVREF  | - AVDD             |      |        | ±0.7             | %FSR         |

| Quantization error         |               |                |                    |      |        | ±1/2             | LSB          |

| Conversion time            | tconv         | 62.5 ns - tcүк | < 80 ns            | 208  |        |                  | <b>t</b> cyk |

|                            |               | 80 ns - tсүк - | 166.6 ns           | 169  |        |                  | <b>t</b> cyk |

| Sampling time              | <b>t</b> SAMP | 62.5 ns - tcүк | < 80 ns            | 8    |        |                  | <b>t</b> cyk |

|                            |               | 80 ns - tсүк - | 166.6 ns           | 6    |        |                  | <b>t</b> cyk |

| Zero-scale errorNote 1     |               | 4.5 V - AVREF  | - AV <sub>DD</sub> |      | ±1.5   | ±2.5             | LSB          |

|                            |               | 3.4 V - AVREF  | - AVDD             |      | ±1.5   | ±4.5             | LSB          |

| Full-scale errorNote 1     |               | 4.5 V - AVREF  | - AV <sub>DD</sub> |      | ±1.5   | ±2.5             | LSB          |

|                            |               | 3.4 V - AVREF  | - AV <sub>DD</sub> |      | ±1.5   | ±4.5             | LSB          |

| Nonlinearity errorNote 1   |               | 4.5 V - AVREF  | - AV <sub>DD</sub> |      | ±1.5   | ±2.5             | LSB          |

|                            |               | 3.4 V - AVREF  | - AV <sub>DD</sub> |      | ±1.5   | ±4.5             | LSB          |

| Analog input voltageNote 2 | VIAN          |                |                    | -0.3 |        | AVREF + 0.3      | V            |

| Analog input impedance     | RAN           | When not sam   | pling              |      | 10     |                  | МΩ           |

|                            |               | When samplin   | g                  |      | Note 3 |                  |              |

| Reference voltage          | AVREF         |                |                    | 3.4  |        | AV <sub>DD</sub> | V            |

| AVREF1 current             | Alref         |                |                    |      | 1.0    | 3.0              | mA           |

| AVDD supply current        | Aldd          | Operating mode |                    |      | 2.0    | 6.0              | mA           |

| A/D converter data         | Aldddr        | STOP mode      | AVDDDR = 2.5 V     |      | 2      | 10               | μΑ           |

| retention current          |               |                | AVDDDR = 5 V ±10 % |      | 10     | 50               | μΑ           |

**Notes 1.** The quantization error is excluded.

- 2. When  $-0.3 \text{ V} \cdot \text{Vian} \cdot 0 \text{ V}$ , the conversion result becomes 000H. When  $0 \text{ V} \cdot \text{Vian} \cdot \text{AVREF}$ , the conversion is performed with the 10-bit resolution. When AVREF Vian AVREF + 0.3 V, the conversion result becomes 3FFH.

- 3. The analog input impedance at the time of sampling is the same as the equivalent circuit shown below. (The values in the diagram are TYP. values; they are not guaranteed values.)

- Cautions 1. When using the P70/ANI0-P77/ANI7 pins for both digital and analog inputs, the previously described characteristics are not guaranteed. Therefore, ensure that all of the eight P70/ANI0-P77/ANI7 pins are used either for analog input or digital input.

- 2. When using the P70/ANI0-P77/ANI7 pins as digital input, make sure to set that AVDD = VDD, and AVss = Vss.

#### **AC Timing Test Point**

#### **Read Operation**

#### **Write Operation**

## **Serial Operation**

## **Up/Down Counter (Timer 4) Input Timing**

# Interrupt Input Timing

Remark n = 0 - 4

## **Reset Input Timing**

# DC PROGRAMMING CHARACTERISTICS (TA = 25 ±5 °C, Vss = 0 V)

| Parameter                       | Symbol           | SymbolNote 1    | Conditions                                   | Min.                  | Тур.            | Max.                  | Unit |

|---------------------------------|------------------|-----------------|----------------------------------------------|-----------------------|-----------------|-----------------------|------|

| High-level input voltage        | Viн              | Viн             |                                              | 2.4                   |                 | VDDP + 0.3            | V    |

| Low-level input voltage         | VIL              | VıL             |                                              | -0.3                  |                 | 0.8                   | V    |

| Input leakage current           | ILIP             | lu              | 0 - V <sub>I</sub> - V <sub>DDP</sub> Note 2 |                       |                 | ±10                   | μΑ   |

| High-level output voltage       | Vон              | Vон             | $I_{OH} = -400 \ \mu A$                      | 2.4                   |                 |                       | V    |

| Low-level output voltage        | Vol              | Vol             | lo <sub>L</sub> = 2.1 mA                     |                       |                 | 0.45                  | V    |

| Output leakage current          | Ісо              | -               | 0 - Vo - VDDP, $\overline{OE} = V_{IH}$      |                       |                 | ±10                   | μΑ   |

| V <sub>DDP</sub> supply voltage | V <sub>DDP</sub> | Vcc             | Program memory write mode                    | 6.25                  | 6.5             | 6.75                  | V    |

|                                 |                  |                 | Program memory read mode                     | 4.5                   | 5.0             | 5.5                   | V    |

| V <sub>PP</sub> supply voltage  | V <sub>PP</sub>  | V <sub>PP</sub> | Program memory write mode                    | 12.2                  | 12.5            | 12.8                  | V    |

|                                 |                  |                 | Program memory read mode                     | V <sub>DD</sub> - 0.6 | V <sub>DD</sub> | V <sub>DD</sub> + 0.6 | V    |

| VDDP supply current             | loo              | IDD             | Program memory write mode                    |                       |                 | 50                    | mA   |

|                                 |                  |                 | Program memory read mode                     |                       |                 | 50                    | mA   |

| VPP supply current              | <b>I</b> PP      | <b>I</b> PP     | Program memory write mode                    |                       |                 | 50                    | mA   |

|                                 |                  |                 | Program memory read mode                     |                       |                 | 100                   | μΑ   |

Notes 1. Symbols for the corresponding  $\mu PD27C1001A$

2. The VDDP represents the VDD pin as viewed in the programming mode.

# AC PROGRAMMING CHARACTERISTICS (TA = 25 ±5 °C, Vss = 0 V)

## PROM Write Mode (Page Program Mode)

| Parameter                        | Symbol <sup>Note 1</sup> | Conditions | Min.  | Тур. | Max.  | Unit |

|----------------------------------|--------------------------|------------|-------|------|-------|------|

| Address set up time              | tas                      |            | 2     |      |       | μs   |

| CE set time                      | tces                     |            | 2     |      |       | μs   |

| Input data setup time            | tos                      |            | 2     |      |       | μs   |

| Address hold time                | tah                      |            | 2     |      |       | μs   |

|                                  | tahl                     |            | 2     |      |       | μs   |

|                                  | tahv                     |            | 0     |      |       | μs   |

| Input data hold time             | tон                      |            | 2     |      |       | μs   |

| Output data hold time            | <b>t</b> DF              |            | 0     |      | 250   | ns   |

| V <sub>PP</sub> setup time       | tvps                     |            | 1     |      |       | ms   |

| VDDP setup time                  | t <sub>VDS</sub> Note 2  |            | 1     |      |       | ms   |

| Initial program pulse width      | tpw                      |            | 0.095 |      | 0.105 | ms   |

| OE set time                      | toes                     |            | 2     |      |       | μs   |

| Valid data delay time from OE    | toe                      |            |       |      | 1.0   | μs   |

| OE pulse width in the data latch | tuw                      |            | 1     |      |       | μs   |

| PGM setup time                   | tрдмs                    |            | 2     |      |       | μs   |

| CE hold time                     | tсен                     |            | 2     |      |       | μs   |

| OE hold time                     | tоен                     |            | 2     |      |       | μs   |

**Notes 1.** These symbols (except tvps) correspond to those of the  $\mu$ PD27C1001A.

**2.** For  $\mu$ PD27C1001A, read tvps as tvcs.

## PROM Write Mode (Byte Program Mode)

| Parameter                     | Symbol <sup>Note 1</sup> | Conditions | Min.  | Тур. | Max.  | Unit |

|-------------------------------|--------------------------|------------|-------|------|-------|------|

| Address set up time           | tas                      |            | 2     |      |       | μs   |

| CE set time                   | tces                     |            | 2     |      |       | μs   |

| Input data setup time         | tos                      |            | 2     |      |       | μs   |

| Address hold time             | tан                      |            | 2     |      |       | μs   |

| Input data hold time          | tон                      |            | 2     |      |       | μs   |

| Output data hold time         | tor                      |            | 0     |      | 250   | ns   |

| V <sub>PP</sub> setup time    | tvps                     |            | 1     |      |       | ms   |

| VDDP setup time               | t <sub>VDS</sub> Note 2  |            | 1     |      |       | ms   |

| Initial program pulse width   | tpw                      |            | 0.095 |      | 0.105 | ms   |

| OE set time                   | toes                     |            | 2     |      |       | μs   |

| Valid data delay time from OE | toe                      |            |       |      | 1.0   | μs   |

**Notes 1.** These symbols (except typs) correspond to those of the  $\mu$ PD27C1001A.

**2.** For  $\mu$ PD27C1001A, read tvps as tvcs.

## **PROM Read Mode**

| Parameter                                       | Symbol Note | Conditions    | Min. | Тур. | Max. | Unit |

|-------------------------------------------------|-------------|---------------|------|------|------|------|

| Data output time from address                   | tacc        | CE = OE = VIL |      |      | 1.0  | μs   |

| $\overline{CE} \downarrow \to data$ output time | tce         | OE = VIL      |      |      | 1.0  | μs   |

| $\overline{OE} \downarrow \to data$ output time | toe         | CE = VIL      |      |      | 1.0  | μs   |

| Data hold time to OE ∞                          | tor         | CE = VIL      | 0    |      | 250  | ns   |

| Data hold time to address                       | toн         | CE = OE = VIL | 0    |      |      | ns   |

Note These symbols correspond to those of the  $\mu$ PD27C1001A.

# PROM Write Mode Timing (Page Program Mode)

#### **PROM Write Mode Timing (Byte Program Mode)**

- Cautions 1. VDDP must be applied before VPP, and must be cut after VPP.

- 2. VPP including overshoot must not exceed +13.5 V.

- 3. Plugging in or out the board with the VPP pin supplied with +12.5 V may adversely affect its reliability.

#### **PROM Read Mode Timing**

- **Notes 1.** For reading within tacc, the delay of the  $\overline{OE}$  input from falling edge of  $\overline{CE}$  must be within tacc toe.

- 2.  $t_{DF}$  is the time measured from when either  $\overline{OE}$  or  $\overline{CE}$  reaches  $V_{IH}$ , whichever is faster.

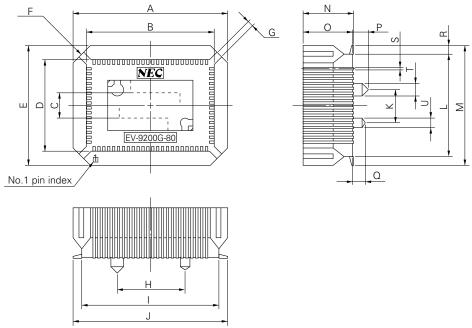

## 9. PACKAGE DRAWINGS

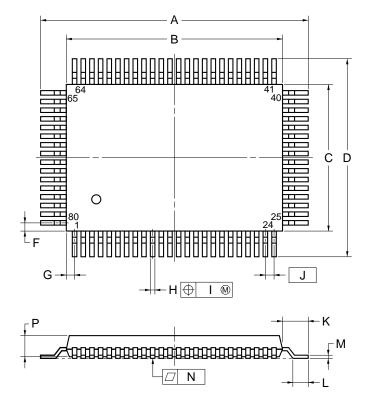

# 80 PIN PLASTIC QFP (14×20)

detail of lead end

#### NOTE

Each lead centerline is located within 0.15 mm (0.006 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS                            | INCHES                    |

|------|----------------------------------------|---------------------------|

| Α    | 23.6±0.4                               | 0.929±0.016               |

| В    | 20.0±0.2                               | $0.795^{+0.009}_{-0.008}$ |

| С    | 14.0±0.2                               | 0.551+0.009               |

| D    | 17.6±0.4                               | 0.693±0.016               |

| F    | 1.0                                    | 0.039                     |

| G    | 0.8                                    | 0.031                     |

| Н    | 0.35±0.10                              | $0.014^{+0.004}_{-0.005}$ |

| I    | 0.15                                   | 0.006                     |

| J    | 0.8 (T.P.)                             | 0.031 (T.P.)              |

| K    | 1.8±0.2                                | $0.071^{+0.008}_{-0.009}$ |

| L    | 0.8±0.2                                | 0.031+0.009               |

| М    | 0.15 <sup>+0.10</sup> <sub>-0.05</sub> | 0.006+0.004               |

| N    | 0.10                                   | 0.004                     |

| Р    | 2.7                                    | 0.106                     |

| Q    | 0.1±0.1                                | 0.004±0.004               |

| R    | 5°±5°                                  | 5°±5°                     |

| S    | 3.0 MAX.                               | 0.119 MAX.                |

P80GF-80-3B9-3

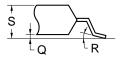

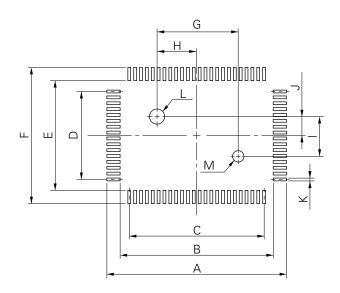

## **80 PIN CERAMIC WQFN**

#### NOTE

Each lead centerline is located within 0.08 mm (0.003 inch) of its true position (T.P.) at maximum material condition.

#### X80KW-80A1

| ITEM | MILLIMETERS | INCHES                                    |

|------|-------------|-------------------------------------------|