## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## MOS INTEGRATED CIRCUIT μ**PD78243, 78244**

**8-BIT SINGLE-CHIP MICROCOMPUTER**

The information in this document is subject to change without notice.

Document No. IC-2774C (O. D. No. IC-8070C) Date Published February 1994 P Printed in Japan

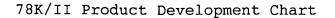

The uPD78243, 78244 is one of the 78K/II series products containing 512-byte EEPROM (electrically erasable programmable read-only memory). The 78K/II series provides 8-bit single chip microcomputers where 1M-byte memory space can be accessed by external expansion.

Please refer to the following User's Manual for details of functions explanation. Be sure to read the manual when starting design.

- uPD78244 Series User's Manual/Hardware: IEU-747

- 78K/II Series User's Manual/Instructions: IEU-754

FEATURES

- o Pins are compatible with the uPD78213, 78214 pins

- Internal EEPROM: 512 bytes (data memory area)

Automatic erasion and write function

- o High performance interrupt controller

- o A/D converter (8 bits x 8 channels)

- o Number of I/O pins: 54 (uPD78244), 36 (uPD78243)

- o Real-time output port (8 x 1 or 4 x 2)

- o Serial interface: Two channels

- o Timer/counter (16 x 1 and 8 x 3)

### APPLICATIONS

Printers, Typewriters, Cameras, PPCs, FAXs, etc.

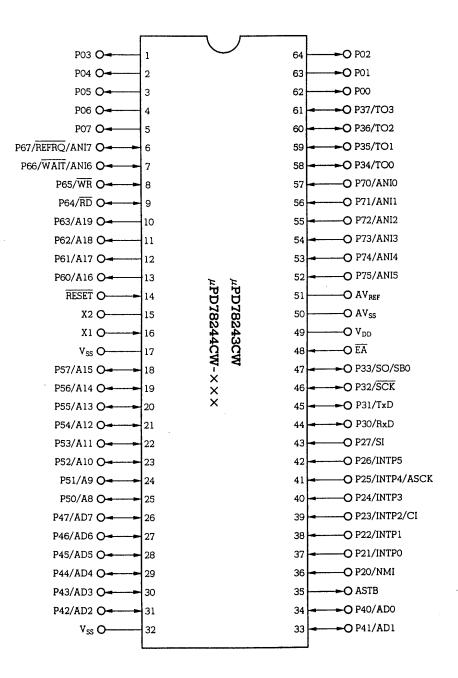

### ORDERING INFORMATION

| Ordering code      | Package                                                   | Internal<br>ROM | Internal<br>RAM |

|--------------------|-----------------------------------------------------------|-----------------|-----------------|

| uPD78243CW         | 64-pin plastic shrinked-dual<br>in-line package (750 mil) | None            | 512             |

| uPD78243GC-AB8     | 64-pin plastic quad-flat<br>package ( 🗌 14mm)             | None            | 512             |

| uPD78244CW-xxx     | 64-pin plastic shrinked-dual<br>in-line package (750 mil) | 16K             | 512             |

| uPD78244GC-xxx-AB8 | 64-pin plastic quad-flat<br>package ( 🗌 14mm)             | 16K             | 512             |

Remarks: xxx is ROM code specification number.

QUALITY GRADE

### Standard

Refer to "Quality Grade on NEC Semiconductor Devices" (Document Number IEI-620) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

## Function List

|                                     |                                   |                          | (1/2                |  |

|-------------------------------------|-----------------------------------|--------------------------|---------------------|--|

| Paramet                             | er                                | uPD78243                 | uPD78244            |  |

| No. of basic in<br>(mnemonics)      | structions                        | 6.                       | 5                   |  |

| Minimum instruc<br>time (during 12  | tion execution<br>-MHz operation) | 500ns                    | 333ns               |  |

|                                     | Mask ROM                          | None                     | 16K bytes           |  |

| On-chip memory capacity             | EEPROM                            | 512 1                    | bytes               |  |

| 1 5                                 | RAM                               | 512 1                    | oytes               |  |

| Memory space                        |                                   | Program: 64K bytes       | Data: 1M bytes      |  |

|                                     | Input                             | 14                       |                     |  |

| Number of I/O                       | Output                            | 12                       |                     |  |

| pins                                | Input/output                      | 10                       | 28                  |  |

|                                     | Total                             | 36                       | 54                  |  |

| (Note)                              | Pins with pull-<br>up resistor    | 16                       | 34                  |  |

| Pins with<br>additional<br>function | LED direct<br>drive output        | - 16                     |                     |  |

|                                     | Transistor direct<br>drive output | 8                        |                     |  |

| ROMless mode setting                |                                   | None                     | EA pin=low level    |  |

| Real-time outpu                     | t port                            | 4 bits x 2 or 8 bits x 1 |                     |  |

| General purpose register            |                                   | 8 bits x 8 x 4 ban       | ks (memory mapping) |  |

Note: The pins with additional an function are contained in the  $\ensuremath{\mbox{I/O}}$  pins.

| Parameter           | Function                                                                                                                                                                         |                                                                                      |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|

|                     | 16-bit timer/ { Timer register x 1<br>counter { Capture register x 1<br>Compare register x 2                                                                                     | Pulse output enable<br>(Toggle output<br>PWM/PPG output<br>One-shot pulse<br>output) |  |  |  |

| Timer/counter       | 8-bit timer/<br>counter 1 { Timer register x 1<br>Capture/compare register x 1<br>Compare register x 1                                                                           | Pulse output enable<br>(real-time output:<br>4 bits x 2)                             |  |  |  |

|                     | 8-bit timer/<br>counter 2 { Timer register x 1<br>Capture register x 1<br>Compare register x 2                                                                                   | Pulse output enable<br>(Toggle output<br>PWM/PPG output)                             |  |  |  |

|                     | 8-bit timer/ { Timer register x 1<br>counter 3 { Compare register x 1                                                                                                            |                                                                                      |  |  |  |

| Serial<br>interface | UART: One channel (containing a dedicated baud rate generator)<br>CSI (3-line serial I/O, SBI): One channel                                                                      |                                                                                      |  |  |  |

| A/D converter       | 8-bit resolution x 8 channels                                                                                                                                                    |                                                                                      |  |  |  |

| Interrupt           | 21 sources (seven external and 14 internal sources) + BRK<br>instruction<br>Two programmable priority levels<br>Two processing modes (vectored interrupt and macro service)      |                                                                                      |  |  |  |

| Instruction set     | <pre>16-bit arithmetic and logical operation<br/>Multiplication and division (8 bits x 8 bits and 16 bits<br/>÷ 8 bits)<br/>Bit manipulation<br/>BCD adjustment and others</pre> |                                                                                      |  |  |  |

| Package             | 64-pin plastic shrinked-dual-in-line package (750mil)<br>64-pin plastic quad-flat package ( 🗆 14 mm)                                                                             |                                                                                      |  |  |  |

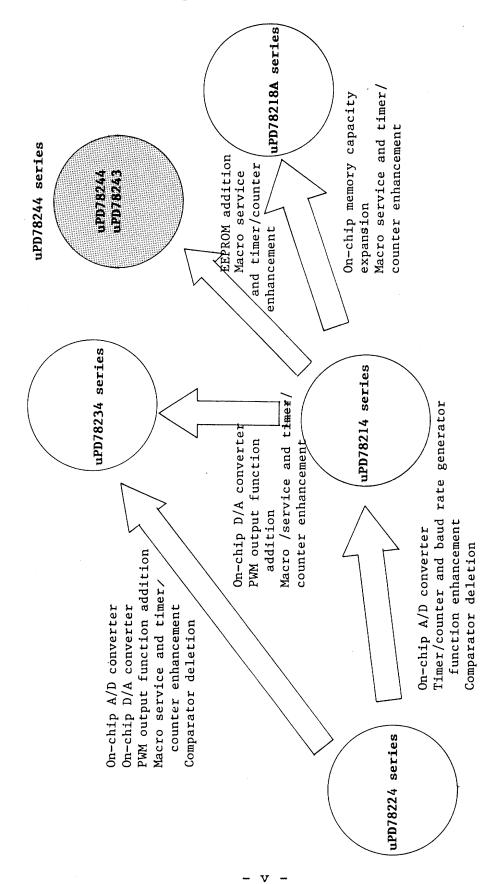

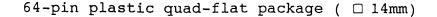

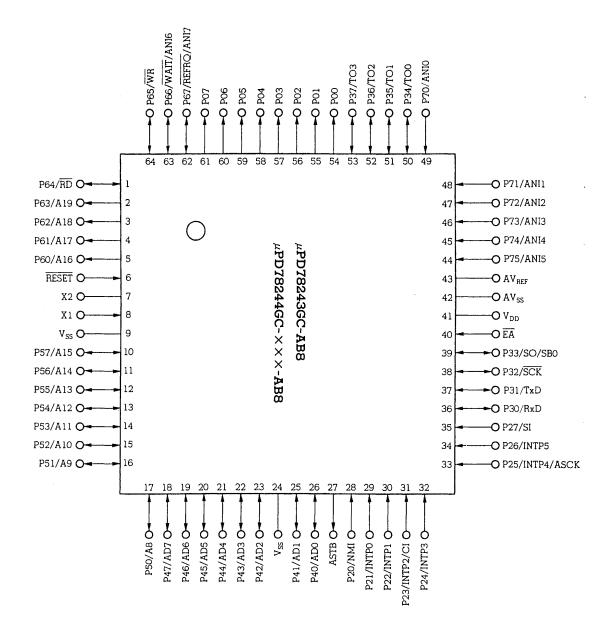

Pin Configuration (Top View)

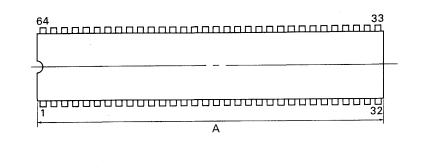

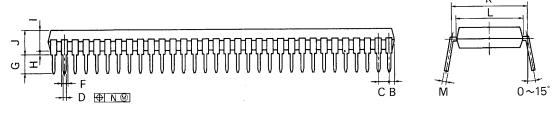

64-pin plastic shrinked-dual-in-line package (750mil)

Remarks: The pins are compatible with the uPD78213CW, 78214CW pins.

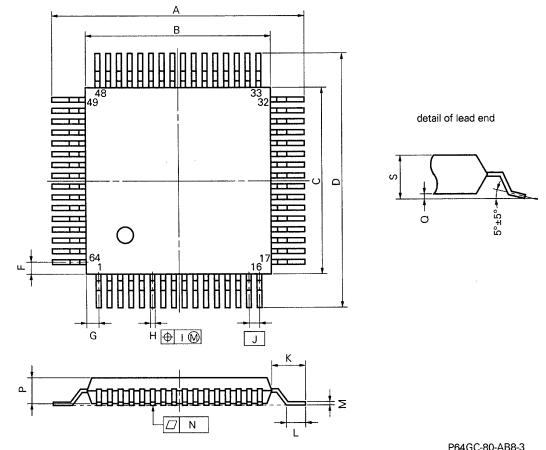

Remarks: The pins are compatible with the uPD78213GC, 78214GC pins.

| P00-P07     | : | Port 0                     | RD                | :  | Read Strobe       |

|-------------|---|----------------------------|-------------------|----|-------------------|

| P20-P27     | : | Port 2                     | WR                | :  | Write Strobe      |

| P30-P37     | : | Port 3                     | WAIT              | :  | Wait              |

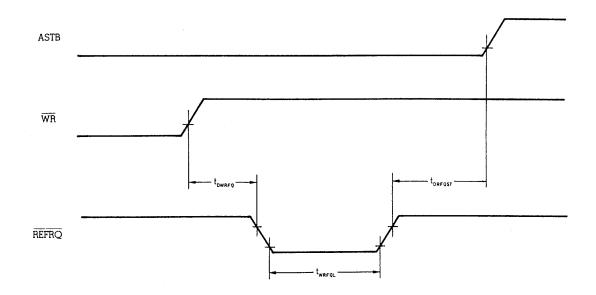

| P40-P47     | : | Port 4                     | ASTB              | :  | Address Strobe    |

| P50-P57     | : | Port 5                     | REFRQ             | :  | Refresh Request   |

| P60-P67     | : | Port 6                     | RESET             | :  | Reset             |

| P70-P75     | : | Port 7                     | X1, X2            | :  | Crystal           |

| T00-T03     | : | Timer Output               | ĒĀ                | :  | External Access   |

| CI          | : | Clock Input                | ANIO-ANI          | 7: | Analog Input      |

| RxD         | : | Receive Data               | AV <sub>REF</sub> | :  | Reference Voltage |

| TxD         | : | Transmit Data              | AVSS              | :  | Analog Ground     |

| SCK         | : | Serial Clock               | v <sub>DD</sub>   | :  | Power Supply      |

| ASCK        | : | Asynchronous Serial Clock  | v <sub>ss</sub>   | :  | Ground            |

| SBO         | : | Serial Bus                 |                   |    |                   |

| SI          | : | Serial Input               |                   |    |                   |

| SO          | : | Serial Output              |                   |    |                   |

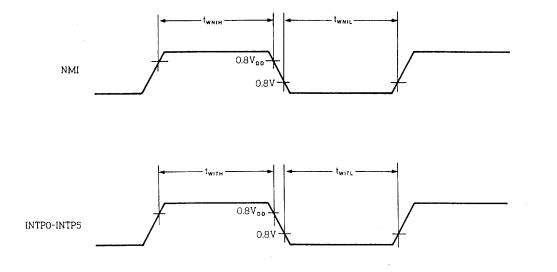

| NMI         | : | Non-maskable Interrupt     |                   |    |                   |

| INTPO-INTP5 | : | Interrupt From Peripherals |                   |    |                   |

| AD0-AD7     | : | Address/Data Bus           |                   |    |                   |

| A8-A19      | : | Address Bus                |                   |    |                   |

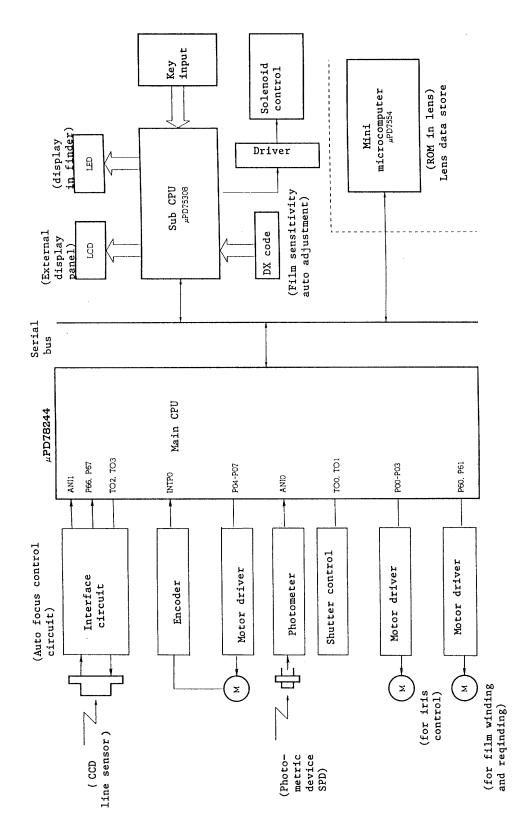

System Configuration Example (auto focus single-lens reflex camera)

- ix -

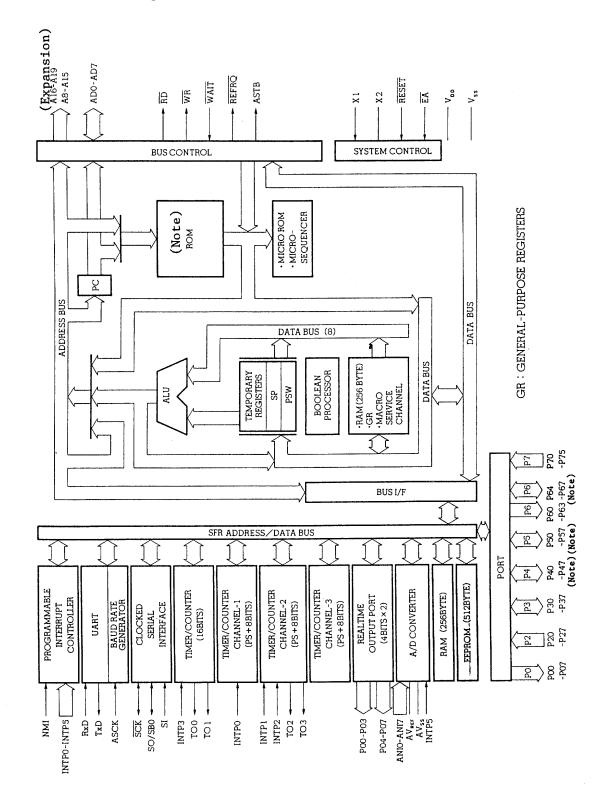

Internal Block Diagram

Note: uPD78243 does not contain internal ROM and P40-P47, P50-P57, P64 and P65.

### CONTENTS

|    |      |                                                                                                                              | Page                     |

|----|------|------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 1. | PIN  | FUNCTION                                                                                                                     | 1-1                      |

|    | 1.1  | Ports                                                                                                                        | 1-1                      |

|    | 1.2  | Pins other than Ports                                                                                                        | 1-3                      |

|    | 1.3  | Input/Output Circuits and<br>Treatment of Unused Pins                                                                        | 1-5                      |

| 2. | INTE | ERNAL BLOCK FUNCTION                                                                                                         | 2-1                      |

|    | 2.1  | Memory Space                                                                                                                 | 2-1                      |

|    | 2.2  | Ports                                                                                                                        | 2-4                      |

|    | 2.3  | Real-Time Output Port                                                                                                        | 2-6                      |

|    | 2.4  | Timer/Counter Units                                                                                                          | 2-7                      |

|    | 2.5  | A/D Converter                                                                                                                | 2-9                      |

|    | 2.6  | Serial Interface                                                                                                             | 2-12                     |

|    |      | <ul><li>6.1 Asynchronous serial interface</li><li>6.2 Clocked serial interface</li></ul>                                     | 2-14<br>2-16             |

|    | 2.7  | EEPROM                                                                                                                       | 2-18                     |

| 3. | INTE | RNAL AND EXTERNAL CONTROL FUNCTION                                                                                           | 3-1                      |

|    | 3.1  | Interrupts                                                                                                                   | 3-1                      |

|    | 3.   | <pre>1.1 Interrupt sources<br/>1.2 Vectored interrupt<br/>1.3 Macro service<br/>1.4 Macro service application examples</pre> | 3-2<br>3-5<br>3-6<br>3-7 |

|     |                                                                                                            | <u>Page</u>          |

|-----|------------------------------------------------------------------------------------------------------------|----------------------|

|     | 3.2 Local Bus Interface                                                                                    | 3-10                 |

|     | <pre>3.2.1 Memory expansion<br/>3.2.2 Programmable wait<br/>3.2.3 Pseudo-static RAM refresh function</pre> | 3-11<br>3-11<br>3-11 |

|     | 3.3 Standby                                                                                                | 3-12                 |

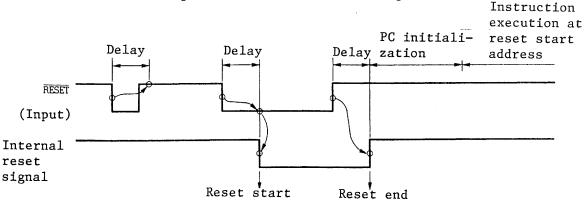

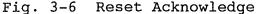

|     | 3.4 Reset                                                                                                  | 3-14                 |

| 4.  | INSTRUCTION SET                                                                                            | 4-1                  |

| 5.  | ELECTRIC CHARACTERISTICS                                                                                   | 5-1                  |

| 6.  | PACKAGE INFORMATION                                                                                        | 6-1                  |

| 7.  | RECOMMENDED CONDITIONS FOR SOLDERING                                                                       | 7-1                  |

| API | PENDIX A. DEVELOPMENT TOOLS                                                                                | A-1                  |

| API | PENDIX B. RELATED DOCUMENTS                                                                                | A-3                  |

## 1. PIN FUNCTION

## 1.1 Ports (1/2)

| Pin name          | 1/0 | Dual<br>function<br>pin | Function                                                                                                                                                                                                                                    |

|-------------------|-----|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00-P07           | 0   |                         | Port 0 (P0):<br>Can be used as two 4-bit real-time output<br>ports.<br>Can drive transistors directly.                                                                                                                                      |

| P20               |     | NMI                     |                                                                                                                                                                                                                                             |

| P21               |     | INTPO                   |                                                                                                                                                                                                                                             |

| P22               |     | INTP1                   | Port 2 (P2):<br>P20 cannot be used as a general purpose port                                                                                                                                                                                |

| P23               | _   | INTP2/CI                | pin (nonmaskable interrupt), but the input<br>level can be checked by the interrupt                                                                                                                                                         |

| P24               | I   | INTP3                   | routine.<br>Internal pull-up resistor connection can be                                                                                                                                                                                     |

| P25               |     | INTP4/ASCK              | specified for P22-P27 in a batch (six bits)<br>by software.                                                                                                                                                                                 |

| P26               |     | INTP5                   |                                                                                                                                                                                                                                             |

| P27               |     | SI                      |                                                                                                                                                                                                                                             |

| P30               |     | RxD                     |                                                                                                                                                                                                                                             |

| P31               |     | TxD                     | Port 3 (P3):                                                                                                                                                                                                                                |

| P32               | I/O | SCK                     | The input/output mode can be specified<br>bit-wise.                                                                                                                                                                                         |

| P33               |     | SO/SB0                  | Internal pull-up resistor connection can be specified bit-wise.                                                                                                                                                                             |

| P34-P37           |     | T00-T03                 |                                                                                                                                                                                                                                             |

| (Note)<br>P40-P47 | I/0 | AD0-AD7                 | Port 4 (P4)<br>The input/output mode can be specified<br>for eight bits in a batch.<br>For P40-P47 in input mode, connection of<br>internal pull-up resistor can be specified<br>in batch by software.<br>The port can drive LEDs directly. |

Note: With the uPD78243, P40-P47, P50-P57, P64, and P65 cannot be used as ports.

## 1.1 Ports (2/2)

| Pin name          | I/0 | Dual<br>function<br>pin | Function                                                                                                                                                                                                                    |

|-------------------|-----|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Note)<br>P50-P57 | 1/0 | A8-A15                  | Port 5 (P5):<br>The input/output mode can be specified<br>bit-wise.<br>For P50-P57 in input mode, connection of<br>internal pull-up resistor can be specified<br>in batch by software.<br>The port can drive LEDs directly. |

| P60-P63           | 0   | A16-A19                 |                                                                                                                                                                                                                             |

| P64(Note)         |     | RD                      | Port 6 (P6):                                                                                                                                                                                                                |

| P65(Note)         |     | ŴŔ                      | The input/output mode can be specified for<br>P64-P67 bit-wise.                                                                                                                                                             |

| P66               | 1/0 | WAIT/ANI6               | Internal pull-up resistor connection can be specified for P64-P67 bit-wise.                                                                                                                                                 |

| P67               |     | REFRQ/AN17              |                                                                                                                                                                                                                             |

| P70-P75           | I   | ANIO-ANI5               | Port 7 (P7)                                                                                                                                                                                                                 |

Note: With the uPD78243, P40-P47, P50-P57, P64, and P65 cannot be used as ports.

## 1.2 Pins other than Ports (1/2)

| Pin nameI/0Dual<br>functionT00-T030Timer outputFunctionT00-T030Timer outputP34-P37CIICount clock input to 8-bit timer/counter 2P23/INTP2RxDISerial data input (UART)P30TxD0Serial data output (UART)P31ASCKIBaud rate clock input (UART)P25/INTP4SB0I/0Serial data input/output (SBI)P33/S0SIISerial data output (3-line serial I/0)P27S00Serial clock input/output (SBI, 3-line<br>serial I/0)P32SCKI/0Serial clock input/output (SBI, 3-line<br>serial I/0)P32INTP0IExternal interrupt requestsP21INTP1IExternal interrupt requestsP23/CIIINTP4INTP4P24P25/ASCKINTP5P26P26 |          |     |                                            |           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|--------------------------------------------|-----------|

| CIIClant chapterCIICount clock input to 8-bit timer/counter 2P23/INTP2RxDISerial data input (UART)P30TxDOSerial data output (UART)P31ASCKIBaud rate clock input (UART)P25/INTP4SB0I/OSerial data input/output (SBI)P33/SOSIISerial data input (3-line serial I/O)P27SOOSerial clock input/output (SBI, 3-line serial I/O)P33/SB0SCKI/OSerial clock input/output (SBI, 3-line serial I/O)P32NMI<br>P20P21P20INTPOIExternal interrupt requestsP23/CIINTP3IP24P25/ASCK                                                                                                          | Pin name | 1/0 | Function                                   | function  |

| RxDISerial data input (UART)P30TxD0Serial data output (UART)P31ASCKIBaud rate clock input (UART)P25/INTP4SB0I/0Serial data input/output (SBI)P33/S0SIISerial data input (3-line serial I/0)P27S00Serial clock input/output (SBI, 3-line serial I/0)P33/SB0 $\overline{SCK}$ I/0Serial clock input/output (SBI, 3-line serial I/0)P32NMI<br>P20P21P21INTP0IExternal interrupt requestsP23/CIINTP3IExternal interrupt requestsP24INTP4P24P25/ASCK                                                                                                                              | T00-T03  | 0   | Timer output                               | P34-P37   |

| TxD0Serial data output (UART)P31ASCKIBaud rate clock input (UART)P25/INTP4SB0I/0Serial data input/output (SBI)P33/S0SIISerial data input (3-line serial I/0)P27S00Serial data output (3-line serial I/0)P33/SB0SCKI/0Serial clock input/output (SBI, 3-lineP32NMIP20INTP0INTP1P22INTP2IExternal interrupt requestsP23/CIINTP4P24P25/ASCK                                                                                                                                                                                                                                     | CI       | I   | Count clock input to 8-bit timer/counter 2 | P23/INTP2 |

| ASCKIBaud rate clock input (UART)P25/INTP4SB0I/0Serial data input/output (SBI)P33/S0SIISerial data input (3-line serial I/0)P27S00Serial data output (3-line serial I/0)P33/SB0SCKI/0Serial clock input/output (SBI, 3-line serial I/0)P32NMI<br>serial I/0)P20P21INTP0INTP2IExternal interrupt requestsP22INTP3INTP4P24P24                                                                                                                                                                                                                                                  | RxD      | I   | Serial data input (UART)                   | P30       |

| SB0I/0Serial data input/output (SBI)P33/S0SIISerial data input (3-line serial I/0)P27SOOSerial data output (3-line serial I/0)P33/SB0SCKI/0Serial clock input/output (SBI, 3-line serial I/0)P32NMIP20P21INTP0IExternal interrupt requestsP23/CIINTP3IExternal interrupt requestsP23/CIINTP4P24P24                                                                                                                                                                                                                                                                           | TxD      | 0   | Serial data output (UART)                  | P31       |

| SIISerial data input (3-line serial I/0)P27SOOSerial data output (3-line serial I/0)P33/SB0SCKI/OSerial clock input/output (SBI, 3-line serial I/0)P32NMI<br>Serial I/O)P20INTP0<br>P21P20INTP1<br>P22P21INTP2IExternal interrupt requestsP23/CIINTP4<br>P25/ASCK                                                                                                                                                                                                                                                                                                            | ASCK     | I   | Baud rate clock input (UART)               | P25/INTP4 |

| SOOSerial data output (3-line serial I/O)P33/SBOSCKI/OSerial clock input/output (SBI, 3-line<br>serial I/O)P32NMIP20P20INTPOP21P21INTP1IExternal interrupt requestsP23/CIINTP3INTP4P25/ASCK                                                                                                                                                                                                                                                                                                                                                                                  | SBO      | I/0 | Serial data input/output (SBI)             | P33/S0    |

| SCKI/OSerial clock input/output (SBI, 3-line<br>serial I/O)P32NMIP20INTP0P21INTP1P22INTP2IINTP3External interrupt requestsP23/CIINTP4P24P25/ASCK                                                                                                                                                                                                                                                                                                                                                                                                                             | SI       | I   | Serial data input (3-line serial I/O)      | P27       |

| SCK1/0serial I/0)P32NMIP20INTP0P21INTP1P22INTP2IINTP3External interrupt requestsINTP4P24P25/ASCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SO       | 0   | Serial data output (3-line serial I/O)     | P33/SB0   |

| INTP0     P21       INTP1     P22       INTP2     I       External interrupt requests     P23/CI       P24     P24       P25/ASCK     P25/ASCK                                                                                                                                                                                                                                                                                                                                                                                                                               | SCK      | I/0 |                                            | P32       |

| INTP1   P22     INTP2   I     External interrupt requests   P23/CI     P24   P25/ASCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NMI      |     |                                            | P20       |

| INTP2   I   External interrupt requests   P23/CI     INTP3   P24     INTP4   P25/ASCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | INTPO    | 1   |                                            | P21       |

| INTP3 P24 P25/ASCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | INTP1    | 1   |                                            | P22       |

| INTP4 P25/ASCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | INTP2    | ] I | External interrupt requests                | P23/CI    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | INTP3    |     |                                            | P24       |

| INTP5 P26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | INTP4    |     |                                            | P25/ASCK  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | INTP5    |     |                                            | P26       |

## 1.2 Pins other than Ports (2/2)

.

| Pin name        | 1/0                     | Function                                                                                                                                                                                        | Dual<br>function<br>pin |

|-----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| AD0-AD7         | I/0                     | Time-multiplexed address/data bus (external memory connection)                                                                                                                                  | (Note)<br>P40-P47       |

| A8-A15          | 0                       | High-order address bus (external memory connection)                                                                                                                                             | (Note)<br>P50-P57       |

| A16-A19         | 0                       | High-order address in address extension (external memory connection)                                                                                                                            | P60-P63                 |

| RD              | 0                       | Read strobe to external memory                                                                                                                                                                  | P64 <sup>(Note)</sup>   |

| WR              | 0                       | Write strobe to external memory                                                                                                                                                                 | P65 <sup>(Note)</sup>   |

| WAIT            | I                       | Wait insertion                                                                                                                                                                                  | P66/ANI6                |

| ASTB            | 0                       | Address (A0-A7) latch timing output (when external memory is accessed)                                                                                                                          | _                       |

| REFRQ           | 0                       | Refresh pulse output to external psudo-static memory                                                                                                                                            | P67/ANI7                |

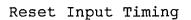

| RESET           | I                       | Chip reset                                                                                                                                                                                      | _                       |

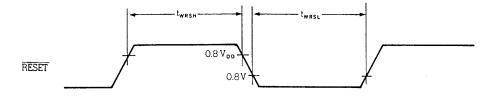

| X1              | I                       | Crystal input for system clock oscillation                                                                                                                                                      |                         |

| X2              | -                       | (clock can also be input to X1)                                                                                                                                                                 |                         |

| ĒĀ              | I                       | ROMless operation indication (external<br>access to the same space as internal ROM).<br>With the uPD78244, set the EA pin high for<br>use and with the uPD78243, set the EA pin<br>low for use. | _                       |

| ANIO-ANI5       | -                       |                                                                                                                                                                                                 | P70-P75                 |

| ANI6, ANI7      |                         | A/D converter analog voltage input                                                                                                                                                              | P66/WAIT<br>P67/REFRQ   |

| AVREF           |                         | A/D converter reference voltage application                                                                                                                                                     | _                       |

| AVSS            |                         | A/D converter GND                                                                                                                                                                               |                         |

| V <sub>DD</sub> | -                       | Positive power supply pin                                                                                                                                                                       | -                       |

| V <sub>SS</sub> | V <sub>SS</sub> GND pin |                                                                                                                                                                                                 |                         |

Note: With the uPD78243, P40-P47, P50-P57, P64, and P65 cannot be used as ports.

## 1.3 Input/Output Circuits and Treatment of Unused Pins

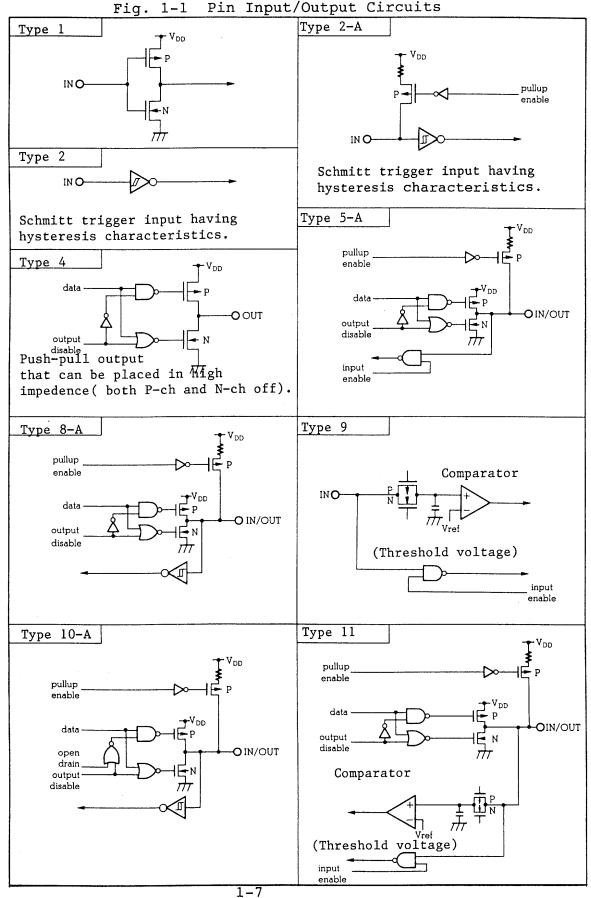

Table 1-1 lists the pin input/output circuit types and the recommended conditions for unused pins. Fig. 1-1 shows the input/output circuit types.

| Table 1-1 | Pin Input/Output Circuit Types and Recommended |

|-----------|------------------------------------------------|

|           | Conditions for Unused Pins (1/2)               |

| Pin             | I/O<br>circuit<br>type | 1/0 | Recommended conditions<br>for unused pins                      |  |  |

|-----------------|------------------------|-----|----------------------------------------------------------------|--|--|

| P00-P07         | 4                      | 0   | No connection required                                         |  |  |

| P20/NMI         | 2                      |     | Concept to V on V                                              |  |  |

| P21/INTP0       |                        |     | Conenct to $v_{DD}^{}$ or $v_{SS}^{}$                          |  |  |

| P22/INTP1       |                        |     |                                                                |  |  |

| P23/INTP2/CI    |                        | I   |                                                                |  |  |

| P24/INTP3       | - 2-A                  |     | Correct to M                                                   |  |  |

| P25/INTP4/ASCK  |                        |     | Connect to V <sub>DD</sub>                                     |  |  |

| P26/INTP5       |                        |     |                                                                |  |  |

| P27/SI          |                        |     |                                                                |  |  |

| P30/RxD         | 5-A                    |     |                                                                |  |  |

| P31/TxD         | 5-A                    |     |                                                                |  |  |

| P32/SCK         | 8-A                    |     | Tanut , Cononat to V                                           |  |  |

| P33/SB0/SO      | 10-A                   | I/O | Input : Conenct to V <sub>DD</sub> .<br>Output: Not connection |  |  |

| P34/T00-P37/T03 |                        |     | required.                                                      |  |  |

| P40/AD0-P47-AD7 | 5-A                    |     |                                                                |  |  |

| P50/A8-P57/A15  |                        |     |                                                                |  |  |

Table 1-1 Pin Input/Output Circuit Types and Recommended Conditions for Unused Pins (2/2)

| Pin               | I/O<br>circuit<br>type | 1/0 | Recommended conditions<br>for unused pins |  |

|-------------------|------------------------|-----|-------------------------------------------|--|

| P60/A16-P63/A19   | 4                      | 0   | No connection required                    |  |

| P64/RD            |                        | 1/0 | Input : Connect to V <sub>DD</sub>        |  |

| P65/WR            | 5-A                    |     | Output: No connection<br>required         |  |

| P66/WAIT/ANI6     | 1 1                    |     | Input : Connect to V <sub>DD</sub>        |  |

| P67/REFRQ/ANI7    | 11                     |     | Output: No conenction<br>required         |  |

| P70/ANI0-P75/ANI5 | 9                      | I   | Connect to V <sub>SS</sub>                |  |

| ASTB              | 4                      | 0   | No connection required                    |  |

| RESET             | RESET 2                |     |                                           |  |

| ĒĀ                | 1                      | I   |                                           |  |

| AV <sub>REF</sub> |                        |     | Connect to $V_{SS}$ or $V_{DD}$           |  |

| AV <sub>SS</sub>  |                        |     | Connect to V <sub>SS</sub>                |  |

- Note: When A/D conversion operation is being performed, do not apply any voltage outside the AV<sub>SS</sub>-AV<sub>REF</sub> range. The uPD78243, 78244 may be destroyed.

- Caution: If the dual function pins used for both input and output mode is not defined, connect the pins to  $V_{DD}$  via serveral tens k $\Omega$  resistors (particularly when the reset input pin voltage exceeds the input low voltage when the power is turned on or when the input and output modes are changed by software.)

- Remarks: The type numbers are standardized in the 78K series and are not necessarily serial numbers in each product (some circuit types are not contained).

#### 2. INTERNAL BLOCK FUNCTION

2.1 Memory Space

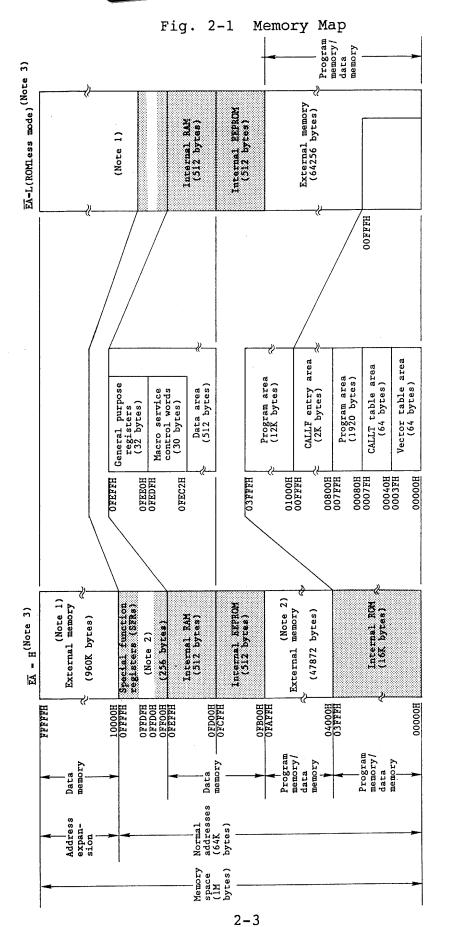

The lM-byte memory space can be accessed. Fig. 2-1 shows a memory map. Mapping the program memory varies depending on the state of the  $\overline{EA}$  pin. The uPD78243 is used with  $\overline{EA}=L$ .

#### (1) uPD78243

The program memory is mapped in external memory (64256 bytes; 00000H-OFAFFH). This area can also be shared with the data memory.

The data memory consists of an internal EEPROM and an internal RAM.

The internal EEPROM area has a capacity of 512 bytes and is mapped in OFB00H-OFCFFH.

The internal RAM also has a capacity of 512 bytes and is mapped in 0FD00H-0FEFFH.

In the 1M-byte extension mode, external memory (960K bytes, 10000H-FFFFFH) can be mapped as an extended data memory.

#### (2) uPD78244

The program memory is mapped in the 16K-byte internal ROM (00000H-03FFFH) and 47872-byte external memory (04000H-OFAFFH). The external memory is accessed in the external memory expansion mode. The area mapped in the external memory can also be used as data memory.

The data memory consists of internal EEPROM and internal RAM.

2-1

The internal EEPROM area has a 512-byte capacity and is mapped in OFB00H-OFCFFH.

The internal RAM also has a 512-byte capacity and is mapped in OFD00H-OFEFFH.

In the 1M-byte expansion mode, the 960K-byte external memory (10000H-FFFFFH) can be mapped as data memory expansion.

- the 1M-byte expansion mode. in memory is accessed External .. ,--Note

- : Internal memory

- expansion mode. the external memory in memory is accessed External 2:

- The uPD78243 cannot be used with EA=H. The uPD78243 can only be used with  $\overline{EA}=L$ . •• m

## 2.2 Ports

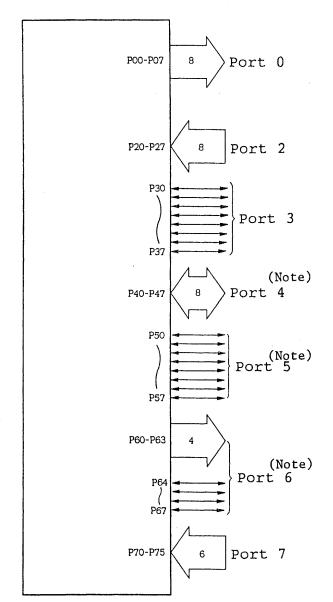

The uPD78243, 78244 contains the ports as shown in Fig. 2-2 for various control purposes. Table 2-1 lists the port function. On-chip pull-up resistor connection can be specified for ports 2 to 6 in the input mode by software.

Note: With the uPD78243, P40-P47, P50-P57, P64, and P65 cannot be used as ports.

Table 2-1 Port Configuration

| Name             | Pin name | Function                                                                                                                                                                                                   | Software<br>pull-up<br>specification               |  |

|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|

| Port O           | P00-P07  | Output mode or high impedance can be<br>specified for eight bits in a batch.<br>Port 0 can also operate as 4-bit real<br>time output (P00-P03 and P04-P07).<br>The port can drive transistors<br>directly. |                                                    |  |

| Port 2           | P20-P27  | Input port.                                                                                                                                                                                                | Six bits in a batch<br>(P22-P27)                   |  |

| Port 3           | P30-P37  | Input or output mode can be specified bit-wise.                                                                                                                                                            | Input mode pins can<br>be specified in a<br>batch. |  |

| (Note)<br>Port 4 | P40-P47  | Input or output mode can be specified<br>for eight bits in a batch.<br>The port can drive LED directly.                                                                                                    | Eight bits in a<br>batch                           |  |

| (Note)<br>Port 5 | P50-P57  | Input or output mode can be specified<br>bit-wise.<br>The port can drive LEDs directly.                                                                                                                    | Input mode pins can<br>be specified in a<br>batch. |  |

|                  | P60-P63  | Output port.                                                                                                                                                                                               |                                                    |  |

| Port 6           | P64-P67  | Input or output mode can be specified bit-wise.                                                                                                                                                            | Input mode pins can<br>be specified in a<br>batch. |  |

| Port 7           | P70-P75  | Input port.                                                                                                                                                                                                |                                                    |  |

Note: With the uPD78243, P40-P47, P50-P57, P64, and P65 cannot be used as ports.

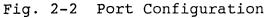

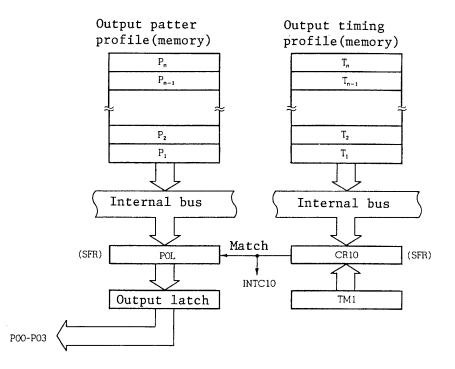

### 2.3 Real-Time Output Port

The real-time output port outputs data stored in a buffer in synchronization with a timer match interrupt or external interrupt to provide pulse output with no jitter.

Thus, it is appropriate for application to output any desired pattern at any desired intervals, such as open loop control of a stepping motor.

The real-time output port consists mainly of port 0 and a buffer register, as shown in Fig. 2-3.

Fig. 2-3 Real Time Output Port Block Diagram

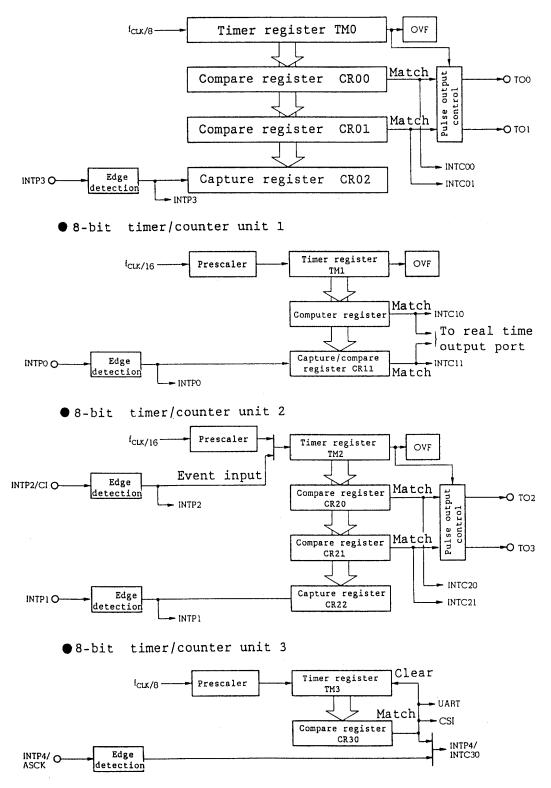

### 2.4 Timer/Counter Units

One channel of the 16-bit timer/counter unit and three channels of the 8-bit timer/counter unit are contained.

| Type and | fu                            | Unit                                    | l6-bit<br>timer/counter | 8-bit<br>timer/counter1 | 8-bit<br>timer/counter2 | 8-bit<br>timer/counter3 |

|----------|-------------------------------|-----------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

|          | Interval timer                |                                         | Two channels            | Two channels            | Two channels            | One channel             |

| Туре     | External event counter        |                                         | -                       | -                       | o                       | -                       |

|          | One-shot timer (Note)         |                                         | -                       | -                       | o                       | -                       |

|          | Timer output                  |                                         | Two channels            | -                       | Two channels            | -                       |

|          |                               | Toggle output                           | o                       | -                       | o                       | -                       |

| Function |                               | PWM/PPG output                          | o                       | -                       | o                       | -                       |

|          |                               | One-shot pulse output <sup>(Note)</sup> | o                       | -                       | o                       | -                       |

|          | Real-time output              |                                         | -                       | o                       | -                       | -                       |

|          | Pulse width measurement       |                                         | o                       | o                       | o                       | -                       |

|          | Number of interrupt requests  |                                         | 2                       | 2                       | 2                       | 1                       |

|          | Serial interface clock source |                                         | -                       | -                       | -                       | o                       |

Table 2-2 Timer/Counter Types and Function

Note: Only 8-bit timer/counter 2 has the one-shot timer mode. The function of this mode differs from the 16-bit timer/counter one-shot pulse output function. Thus, the 16-bit timer/counter does not have the one-shot timer mode. The 16-bit timer/counter one-shot pulse output function is added from the uPD78213, 78214.

The timer/counter units support a total of seven interrupt requests, thus can be served as timers of seven channels.

### Fig. 2-4 Timer/Counter Unit Block Diagram

● 16-bit timer/counter unit

OVF: Overflow flag

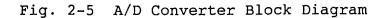

#### 2.5 A/D Converter

An analog/digital (A/D) converter which has eight multiplexed analog inputs (ANI0-ANI7) is contained.

The conversion system is successive approximation and the conversion result is retained in an 8-bit A/D conversion result register (ADCR). Thus, high-speed and high-precision conversion is made (the conversion time is about 30 us during 12-MHz operation).

A/D conversion operation is started in either of the following modes:

- o Hardware start: Conversion is started by trigger input (INTP5).

- o Software start: Conversion is started by setting a specific A/D converter mode register (ADM) bit.

After being started, the A/D conversion operation

- o Scan mode : More than one analog input is selected in sequence and conversion data from all pins is provided.

- o Select mode: Analog input is fixed to one pin and consecutive conversion value is provided.

The modes and conversion operation stop are all specified in the ADM.

When the conversion result is transferred to the ADCR, interrupt request INTAD is generated (except in the select mode with software start). Thus, the conversion value can be transferred consecutively to memory by macro service.

2-9

Table 2-3 Modes Causing INTAD to Occur

|                | Scan mode | Select mode |

|----------------|-----------|-------------|

| Hardware start | 0         | o           |

| Software start | о         |             |

2-11

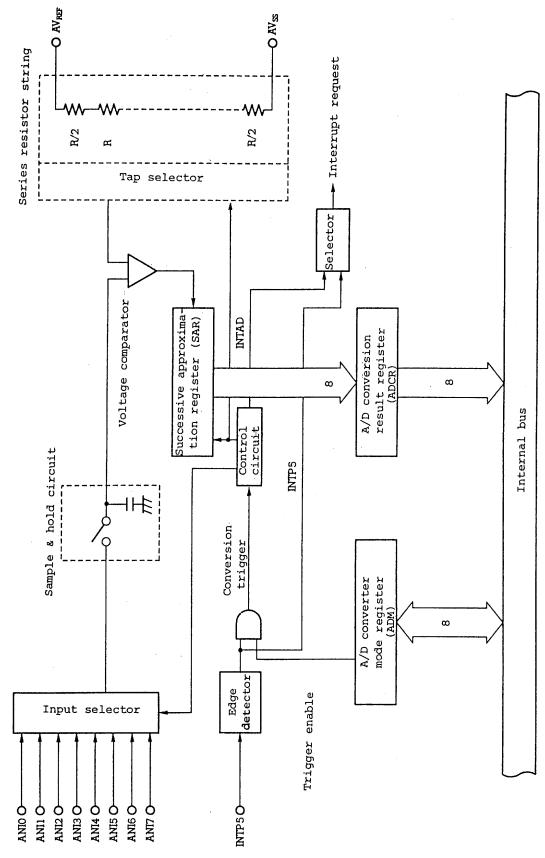

### 2.6 Serial Interface

Two independent serial interface channels are contained.

o Asynchronous serial interface (UART)

- o Clocked serial interface (CSI)

- 3-line serial I/O

- Serial bus interface (SBI)

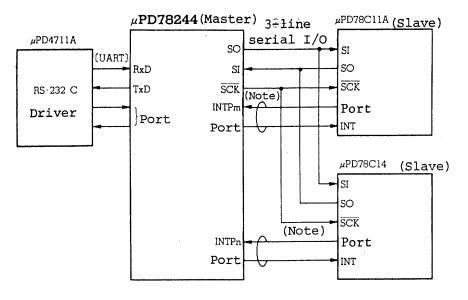

Thus, the uPD78243, 78244 can make communication with the system external and local communication in the system simultaneously (See Fig. 2-6).

Fig. 2-6 Serial Interface Example

### (a) UART+SBI

(b) UART+3-line serial interface

Note: Handshaking lines

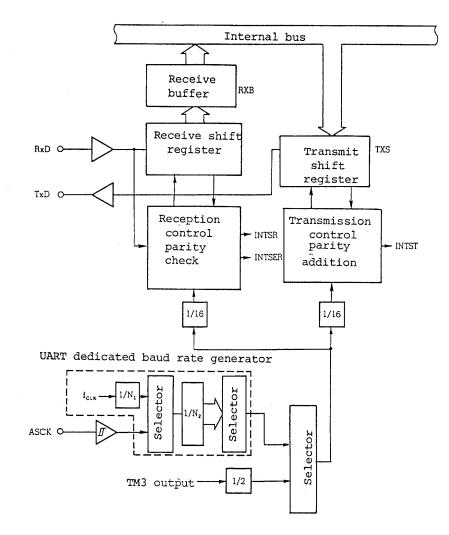

### 2.6.1 Asynchronous serial interface

The uPD78243, 78244 contains UART (Universal Asynchronous Receiver er Transmitter) as an asynchronous serial interface where 1-byte data following a start bit is transmitted.

A baud rate generator dedicated to the UART is provided for communication covering a wide range of desired baud rates. A baud rate can also be defined by dividing the input clock to the ASCK pin.

8-bit timer/counter 3 can also generate a baud rate. The UART dedicated baud rate generator also provides the MIDI specification baud rate (31.25 kbps).

### Fig. 2-7 Asynchronous Serial Interface Block Diagram

f<sub>CLK</sub>: Internal system clock frequency (clock oscillation frequency/2)

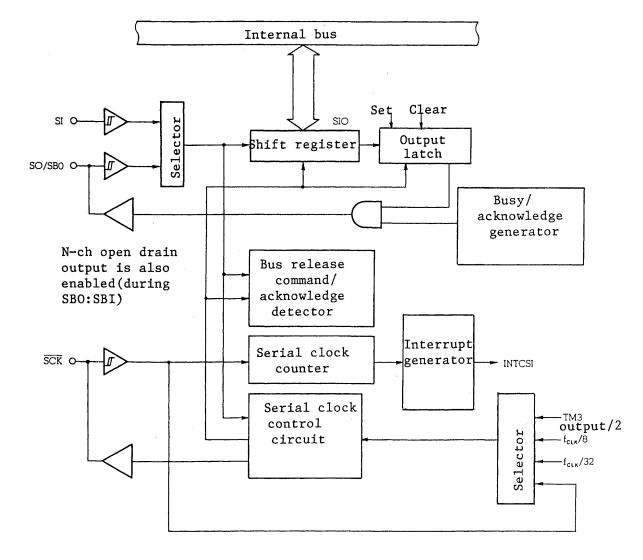

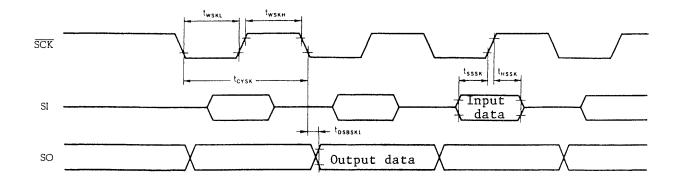

### 2.6.2 Clocked serial interface

The master device activates serial clock and starts transmission. 1-byte data is transferred in synchronization with the serial clock.

Fig. 2-8 Clocked Serial Interface Block Diagram

(1) 3-line serial I/O

The 3-line serial I/O is an interface for communication with a device containing the conventional clocked serial interface.

Basically, the three lines of serial clock (SCK) and serial data (SI and SO) are used for communication. To connect the uPD78243, 78244 to a number of devices, handshaking lines are required.

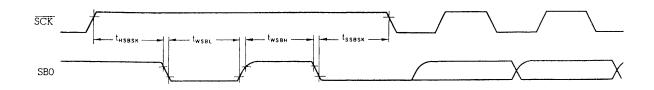

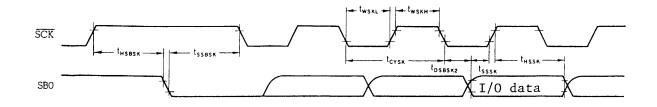

(2) Serial bus interface (SBI)

The uPD78243, 78244 communicates with a number of devices on the two lines of serial clock ( $\overline{SCK}$ ) and serial bus (SB0). The serial bus interface (SBI) is NEC format serial interface.

The master device outputs "address" from the SBO pin to select the slave device to communicate with. Then, "command" and "data" are transferred between the master and slave.

### 2.7 EEPROM

512-byte EEPROM (Electrically Erasable Programmable Read-Only Memory) is contained in addition to 512-byte internal RAM as data memory. EEPROM can be read/written by a program. Unlike normal data memory, EEPROM can also retain data during power failure.

EEPROM is mapped in data memory space addresses OFB00H-OFCFFH.

EEPROM contains a write dedicated timer. When data is written into EEPROM, the EEPROM contents are eased and the data is written automatically. The write operation is performed one byte at a time. The time required for the write is about 10 ms (about 5 ms of erasion time + about 5 ms of write time)

On-chip EEPROM read/write operation is performed in the same manner as on-chip RAM read/write operation. The memory contents can also be read during writing.

The following two interrupts occur from EEPROM:

(1) INTEPW (EEPROM write end interrupt)

Is an interrupt occurring when write into EEPROM is complete.

(2) INTEER (EEPROM write error interrupt)

Is an interrupt occurring when a write error into EEPROM occcurs. The write error occurs in either of the following cases:

- When an EEPROM write instruction is executed during writing into EEPROM

- When EEPROM write is inhibited during writing into EEPROM

2 - 18

### 3. INTERNAL AND EXTERNAL CONTROL FUNCTION

3.1 Interrupts

Either of the interrupt request processing modes listed in Table 3-1 can be selected by a program.

| Processing mode Main part<br>for<br>processing |          | Processing                                                                                     | PC and PSW contents |

|------------------------------------------------|----------|------------------------------------------------------------------------------------------------|---------------------|

| Vectored interrupt Softwa                      |          | Branch to service routine for<br>execution (processing contents<br>are as desired)             | Saved and restored  |

| Macro service                                  | Firmware | Execution of data transfer<br>between memory and I/O, etc.,<br>(processing contents are fixed) | Retained            |

| Table 3- | l Interrupt | Request | Processing |

|----------|-------------|---------|------------|

|----------|-------------|---------|------------|

#### 3.1.1 Interrupt sources

The interrupt sources are seven external and 14 internal sources (21 totally) and BRK instruction execution, as listed in Table 3-2.

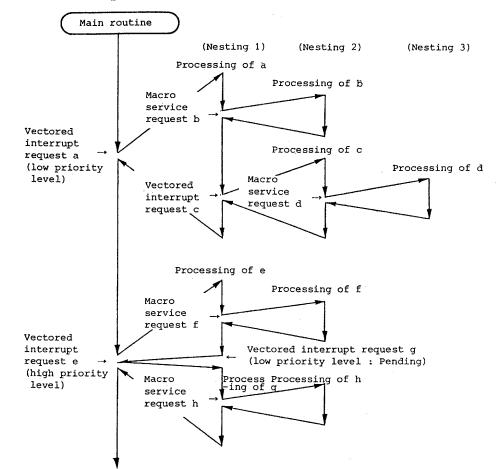

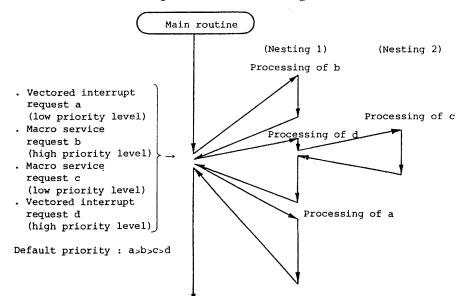

Two interrupt processing priority levels (high and low) can be set for nest control during interrupt processing and for discrimination between levels of interrupt requests occurring at a time. (See Fig. 3-1 and 3-2.) However, when a macro service is executed, interrupt requests are not pending and are always nested.

The default priorities are fixed processing priority levels of interrupt requests having the same priority level occurring at a time. (See Table 3-2.)

|               | Default     |        | Source                           | Internal/ | Macro   |

|---------------|-------------|--------|----------------------------------|-----------|---------|

| Type priority |             | Name   | Trigger                          | external  | service |

| Software      |             | BRK    | Instruction execution            | —         |         |

| Nonmaskable   |             | NMI    | Pin input edge detection         |           |         |

|               | 0 (highest) | INTPO  | " (TM1 capture trigger)          |           |         |

|               | 1           | INTP1  | " (TM2 capture trigger)          | External  |         |

|               | 2<br>3      | INTP2  | " (TM2 event counter input)      |           | o       |

|               |             | INTP3  | " (TMO capture trigger)          |           |         |

| Maskable      | 4           | INTCOO | TMO-CR00 match signal generation |           |         |

|               | 5           | INTCO1 | TMO-CRO1 "                       |           |         |

|               | 6           | INTC10 | TM1-CR10 "                       | Internal  |         |

|               | 7           | INTC11 | TM1-CR11 "                       |           |         |

|               | 8           | INTC21 | TM2-CR21 "                       |           |         |

|               | 9           | INTP4  | Pin input edge detection         | External  |         |

|               | У           | INTC30 | TM3-CR30 match signal generation | Internal  |         |

Table 3-2 Interrupt Sources (1/2)

Table 3-2 Interrupt Sources (2/2)

| Туре     | Default                    |                                       | Source                                          | Internal/ | Macro   |

|----------|----------------------------|---------------------------------------|-------------------------------------------------|-----------|---------|

|          | priority Name              |                                       | Trigger                                         | external  | service |

|          | 10                         | INTP5                                 | Pin input edge detection                        | External  |         |

|          | 10                         | INTAD                                 | A/D converter conversion end (transfer to ADCR) |           | 0       |

|          | 11                         | INTC20                                | TM2-CR20 match signal generation                |           |         |

| Maskable | 12                         | INTSER ASI reception error occurrence |                                                 |           | -       |

| MASKADIG | 13                         | INTSR                                 | INTSR ASI reception end                         |           |         |

|          | 14 INTST                   |                                       | ASI transmission end                            |           | o       |

|          | 15 INTCSI CSI transfer end |                                       | CSI transfer end                                |           |         |

|          | 16                         | INTEER                                | EER EEPROM write error occurrence               |           |         |

|          | 17 (lowest)                | INTEPW                                | EEPROM write completion                         |           | -       |

| TMO    | :   | 16-bit timer                  |

|--------|-----|-------------------------------|

| TM1-TM | 13: | 8-bit timers                  |

| ASI    | :   | Asynchronous serial interface |

| CSI    | :   | Clocked serial interface      |

Fig. 3-1 Processing Example when Another Interrupt Request Occurs during Interrupt Processing

Fig. 3-2 Processing Example of Interrupt Requests Occurring Simultaneously

### 3.1.2 Vectored interrupt

A branch is taken to a specific interrupt service routine at the address addressed by the memory contents at the vector table address corresponding to each interrupt source.

The following are performed for the CPU to perform interrupt processing:

| 0 | At branch : | CPU state (PC and PSW contents) is saved in a    |   |

|---|-------------|--------------------------------------------------|---|

|   |             | stack.                                           |   |

| 0 | At return : | CPU state (PC and PSW contents) is restored from | i |

|   |             | the stack.                                       |   |

To return from the interrupt service routine to the main routine, the RETI instruction is executed.

| Interrupt<br>source | Vector table<br>address |  |  |  |  |

|---------------------|-------------------------|--|--|--|--|

| BRK                 | 003EH                   |  |  |  |  |

| NMI                 | 0002H                   |  |  |  |  |

| INTPO               | 0006н                   |  |  |  |  |

| INTP1               | 0008H                   |  |  |  |  |

| INTP2               | 000AH                   |  |  |  |  |

| INTP3               | 000CH                   |  |  |  |  |

| INTC00              | 0014H                   |  |  |  |  |

| INTC01              | 0016H                   |  |  |  |  |

| INTC10              | 0018H                   |  |  |  |  |

| INTC11              | 001AH                   |  |  |  |  |

| INTC21              | 001CH                   |  |  |  |  |

| Interrupt<br>source | Vector table<br>address |  |  |

|---------------------|-------------------------|--|--|

| INTP4               | 000EH                   |  |  |

| INTC30              | OOOEH                   |  |  |

| INTP5               | 0010H                   |  |  |

| INTAD               |                         |  |  |

| INTC20              | 0012H                   |  |  |

| INTSER              | 0020H                   |  |  |

| INTSR               | 0022H                   |  |  |

0024H

0026H 0028H

002AH

INTST

INTCSI

INTEER INTEPW

Table 3-3 Vector Table Addresses

### 3.1.3 Macro service

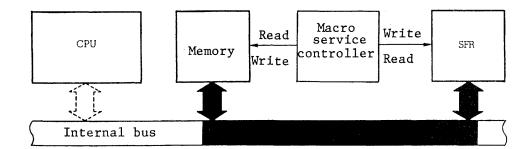

The macro service function transfers data between memory and a given special function register (SFR) without CPU intervention. The macro service controller accesses memory and SFR and directly transfers data without acquiring it.

Data can be transferred at high speed because the CPU state is not saved or restored and data is not acquired.

Fig. 3-3 Macro Service

### 3.1.4 Macro service application examples

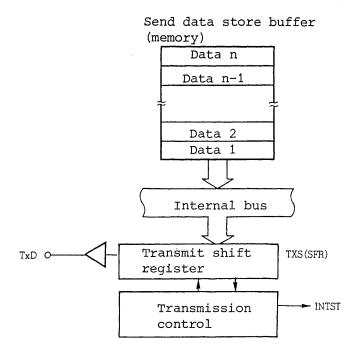

(1) Serial interface transmission operation

Each time macro service request INTST occurs, the next send data is transferred from memory to TXS. When data n (last byte) is transferred to TXS (when the send data store buffer becomes empty), vectored interrupt request INTST is generated.

(2) Serial interface reception operation

Receive data store buffer (memory) Data n Data n-1 Data 2 Data 1 Internal bus  $\langle \rangle$ Receive buffer RXB(SFR)  $\langle \rangle$ Receive shift RxD O register A Reception - INTSR control

Each time macro service request INTSR occurs, receive data is transferred from RXB to memory. When data n (last byte) is transferred to memory (when the receive data store buffer becomes full), vectored interrupt request INTSR is generated.

(3) Real-time output port

INTC10 and INTC11 are used as real-time output port output triggers. In macro service for them, the next output pattern and intervals can be set at the same time. Thus, INTC10 and INTC11 can be used to control two independent stepping motor subsystems. They are also applicable to PWM and DC motor control, etc.

Each time macro service request INTCl0 occurs, a pattern and timing are transferred to POL and CR10 respectively. When the TM1 contents match the CR10 contents, the next INTCl0 is generated and the POL contents are sent to the output latch. When  $T_n$  (last byte) is transferred to CR10, vectored interrupt request INTCl0 is generated.

Each time macro service request INTC11 occurs, the same operation is performed except that CR10 is CR11, POL is POH, or POO-PO3 are PO4-PO7.

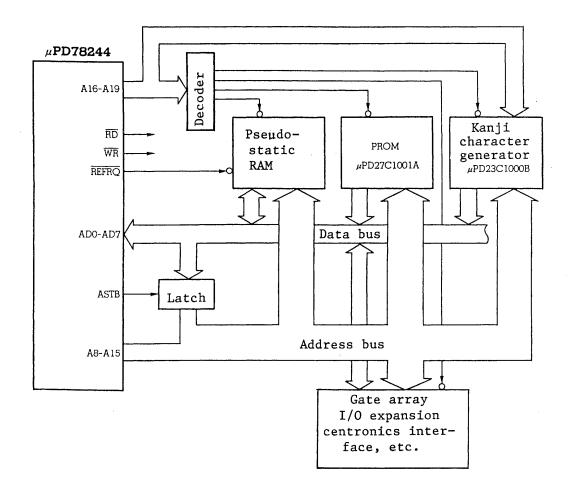

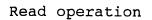

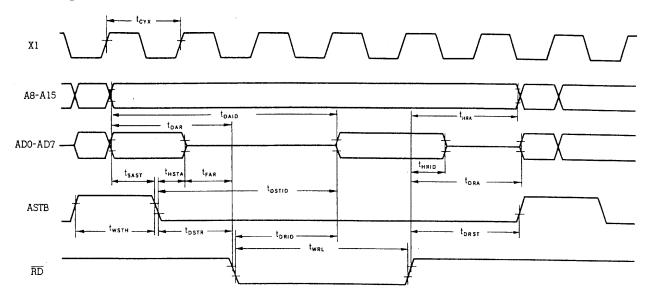

3.2 Local Bus Interface

External memory and I/O (memory-mapped I/O) can be connected to the uPD78243, 78244; the uPD78243, 78244 supports 1M-byte memory space. (See Fig. 2-1.)

Fig. 3-4 Local Bus Interface Example

#### 3.2.1 Memory expansion

The following modes can be used as the memory expansion function:

- o External memory expansion mode: Program memory and data memory can be expanded to the external (47872 bytes). However, in the ROMLess mode (EA=L), the area can be used unconditionally.

- o 1M-byte expansion mode : Data memory can be expanded to the external (960K bytes) to provide 1M-byte memory space.

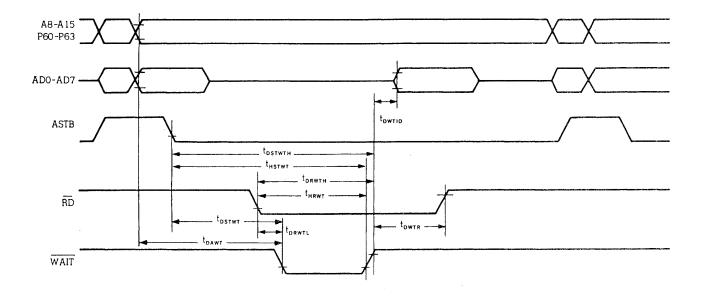

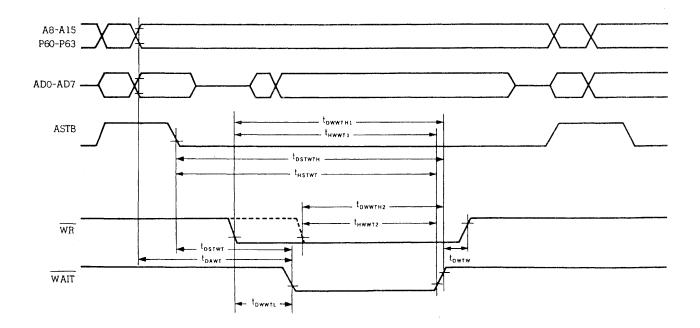

3.2.2 Programmable wait

Wait can be inserted in memory mapped in the normal address area (00000H-OFFFFH) and address expansion area (10000H-FFFFFH) independently. Thus, the lowering of the entire system's efficiency can be avoided although memory with different access time is connected.

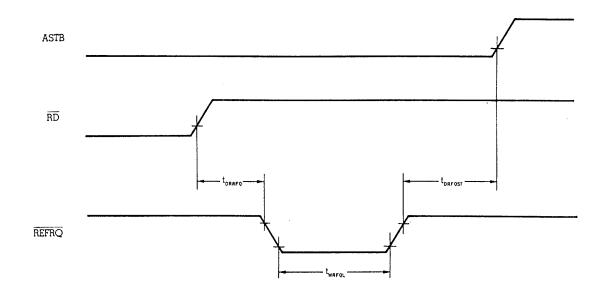

3.2.3 Pseudo-static RAM refresh function

The following refresh operation is performed:

o Pulse refresh : A refresh pulse is output to the REFRQ pin in synchronization with bus cycle.

o Power-down self-refresh: In the standby mode, a low level is output to the REFRQ pin and the pseudo-static RAM contents are re-

tained.

3-11

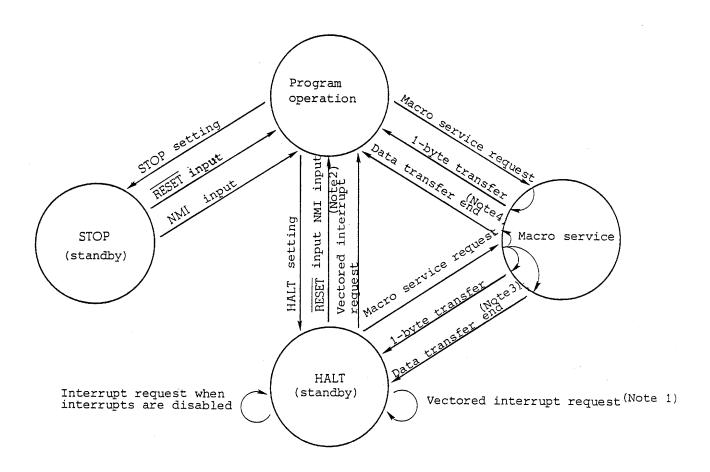

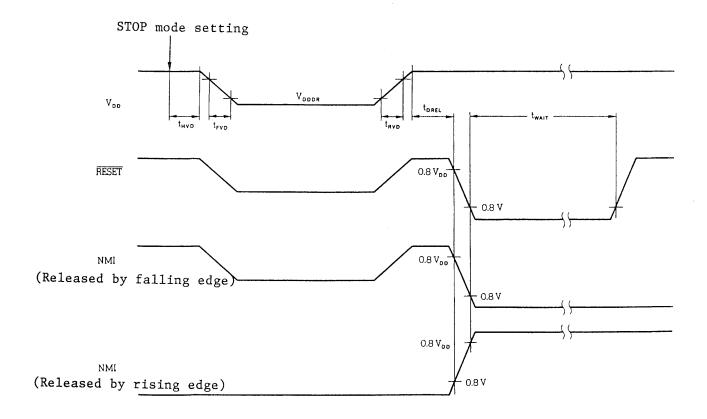

### 3.3 Standby

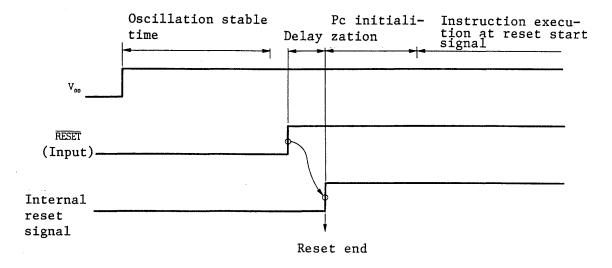

The standby function reduces chip power consumption. It provides the following modes: