#### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

#### **DATA SHEET**

## $\mu \text{PD78146, 78148}$

#### **8 BIT SINGLE-CHIP MICROCOMPUTER**

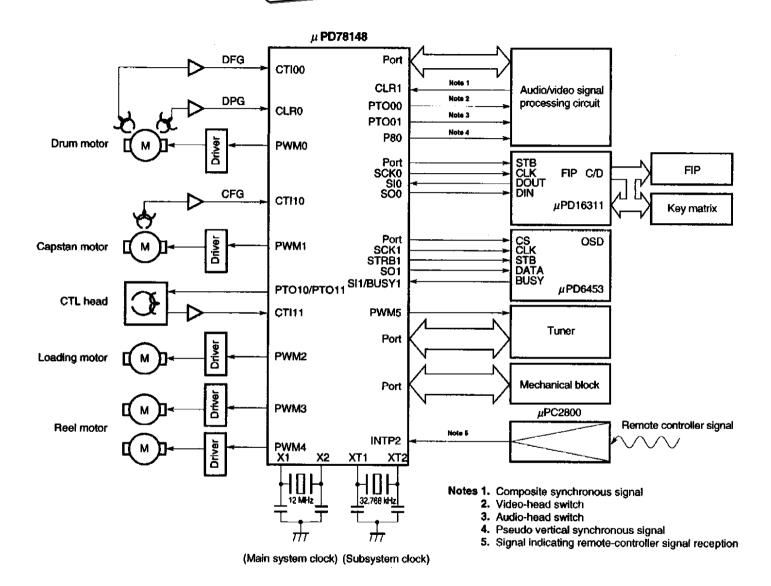

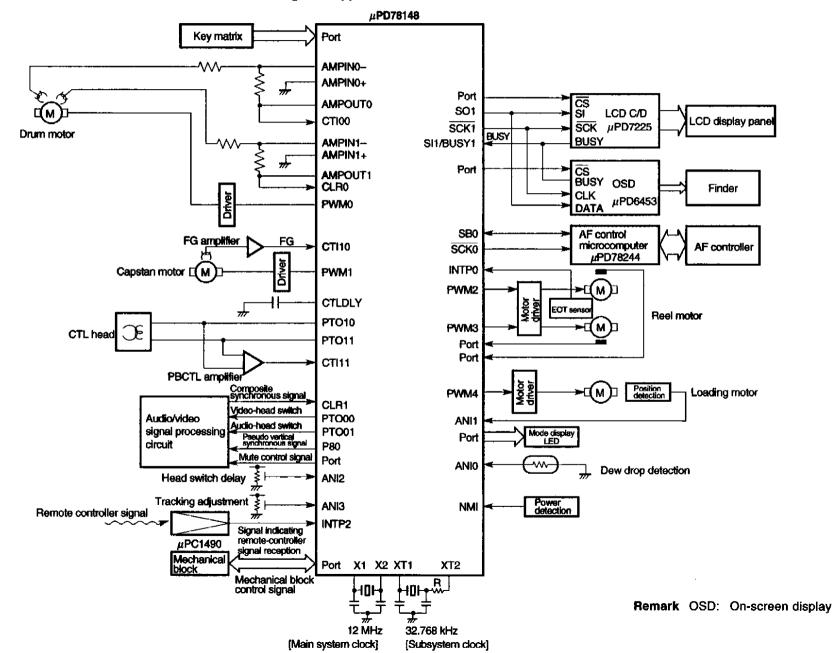

The  $\mu$ PD78148, with on-chip peripheral hardware, can be used in VCRs and other devices that require digital servo control with software.

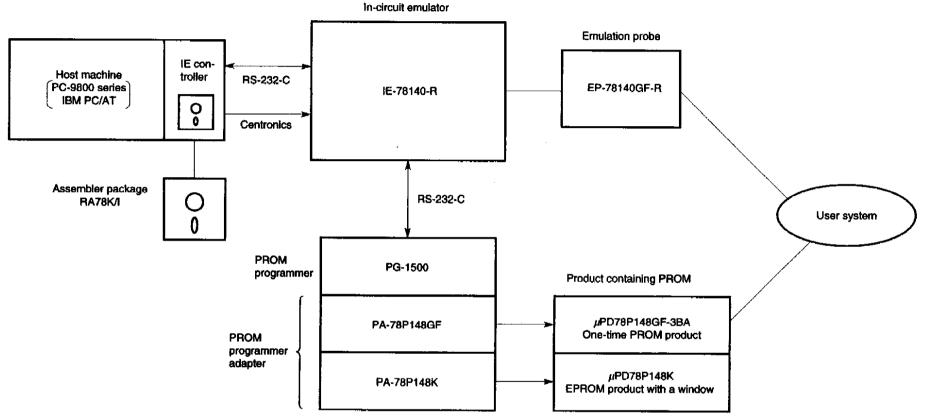

The  $\mu$ PD78P148, with the one-time PROM or EPROM, is also available, which can operate in the same range of the power supply voltage as the mask ROM product. The development tools are also provided for the  $\mu$ PD78148.

The following user's manual completely describes the functions of the  $\mu$ PD78148. Be sure to read it before designing an application system.

µPD78148 User's Manual: IEU-1319

#### FEATURES

**CENESAS**

- Mass-storage program memory

- µPD78146 ROM: 24K bytes, RAM: 688 bytes

- μPD78148 ROM: 32K bytes, RAM: 816 bytes

- I/O lines: 76

- On-chip peripheral hardware suitable for VCR servo control

- Super timer unit

- Real-time output ports: 18

- High-precision A/D converter: 15 channels

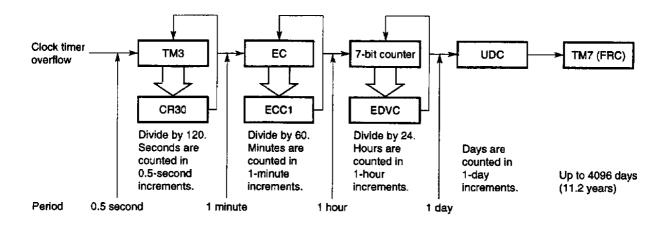

- · Clock operation by the subsystem clock

- Serial interface: 2 channels

- · Hardware for receiving remote control signals

- · Operational amplifiers: 2

- Multiplier

- · Built-in powerful interrupt functions providing two service modes

- Vectored interrupt function/Macro service function

#### APPLICATIONS

System/servo controlling of separate VCRs and camcorders)

#### **ORDERING INFORMATION**

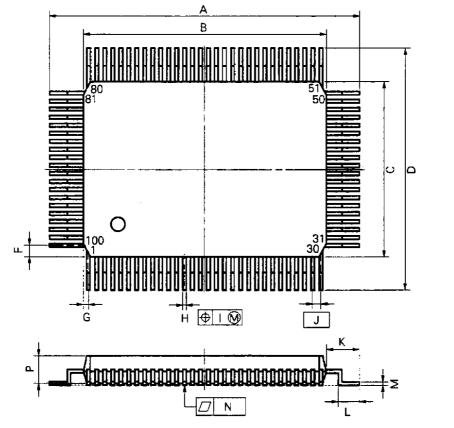

| Part number        | Package                                |

|--------------------|----------------------------------------|

| μPD78146GF-×××-3BA | 100-pin plastic QFP (14 × 20 mm)       |

| µPD78148GF-xxx-3BA | 100-pin plastic QFP (14 $	imes$ 20 mm) |

Remark: xxx: ROM code number

Unless otherwise specified (for functions), the description of the  $\mu$ PD78148 applies to the  $\mu$ PD78146.

The information in this document is subject to change without notice.

Major changes in this revision are indicated by stars (±) in the margins.

/

#### FUNCTIONAL OVERVIEW

| item                                  | Product | μPD78146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | μPD78148                                                                                                                                                                                 |  |  |

|---------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Number of basic in tions              | struc-  | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                          |  |  |

| Minimum instruction<br>execution time | n       | 0.33 $\mu$ s (when the microcomputer operates at 12 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                          |  |  |

| Internal memory                       | ROM     | 24K bytes (24576 × 8 bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32K bytes (32768 × 8 bits)                                                                                                                                                               |  |  |

|                                       | RAM     | 688 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 816 bytes                                                                                                                                                                                |  |  |

| General register                      |         | 8 bits $\times$ 8 $\times$ 4 banks (memory mapping)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                          |  |  |

| Instruction set                       |         | 16-bit addition, subtraction, comparison<br>Signed multiplication (signed 16 bits × unsigned 8 bits)<br>Unsigned multiplication/division (16 bits × 8 bits, 16 bits + 8 bits)<br>Bit manipulation (transfer, Boolean operation, set, reset, test)                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                          |  |  |

| I/O line                              |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>Input port : 24         <ul> <li>(10 ports can also be used as A/D converter input or analog pins for operational amplifiers.)</li> <li>Output port : 12</li> </ul> </li> </ul> |  |  |

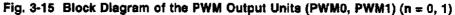

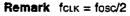

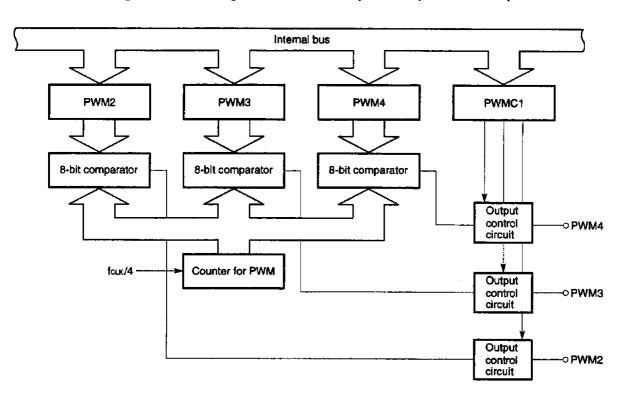

| Super timer unit                      |         | <ul> <li>Timer <ul> <li>16 bits × 3 <ul> <li>8 bits × 3</li> </ul> </li> <li>Counter <ul> <li>22-bit free running counter (FRC) × 1</li> <li>6-bit up/down counter (UDC) × 1</li> </ul> </li> <li>Capture register <ul> <li>22 bits × 2</li> <li>16 bits × 3</li> <li>8 bits × 2</li> </ul> </li> <li>Compare register <ul> <li>16 bits × 7</li> <li>8 bits × 3</li> </ul> </li> <li>PWM output <ul> <li>12 bits × 2 (carrier frequency: 46.9/23.4 kHz)</li> <li>14 bits × 1 (carrier frequency: 5.9 kHz)</li> <li>8 bits × 3 (carrier frequency: 5.9 kHz)</li> </ul> </li> </ul></li></ul> |                                                                                                                                                                                          |  |  |

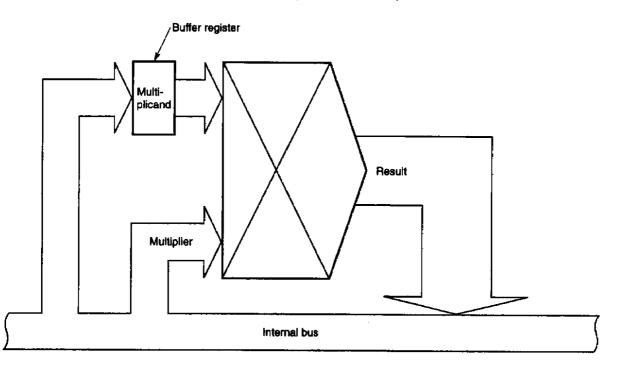

| Multiplier                            |         | Signed 16 bits $\times$ signed 16 bits. Operation time: 2.67 $\mu$ s (when the microcomputer operates at 12 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                          |  |  |

| Real-time output po                   | rt      | <ul> <li>Timer-connected port output function</li> <li>18 built-in ports in total</li> <li>The timer for an output trigger can be selected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                          |  |  |

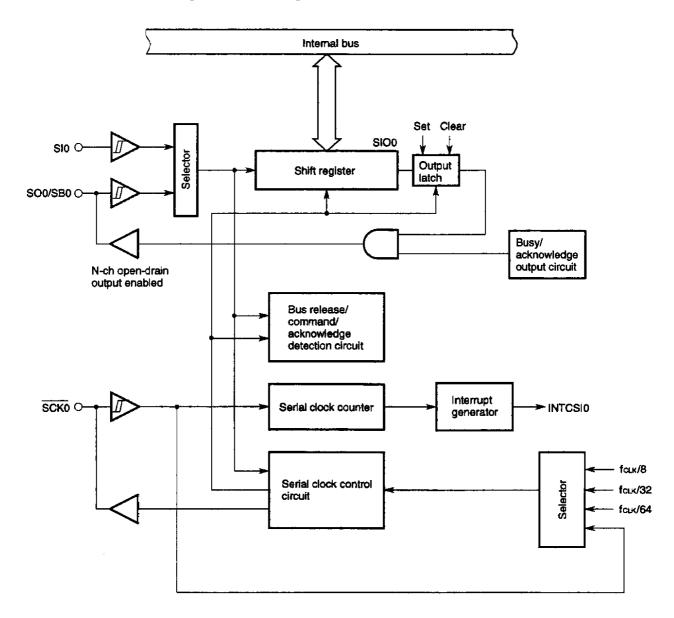

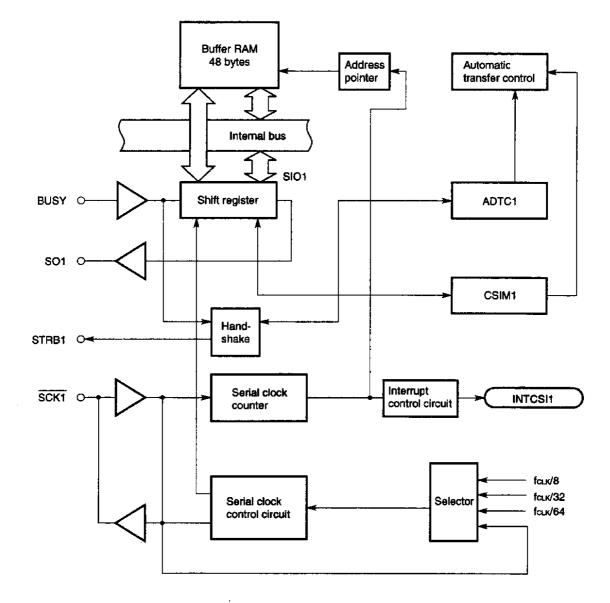

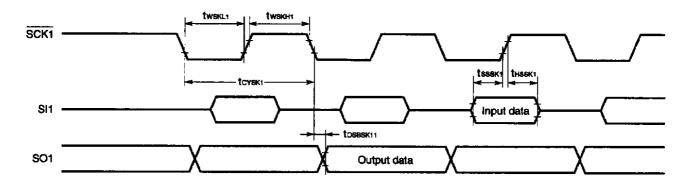

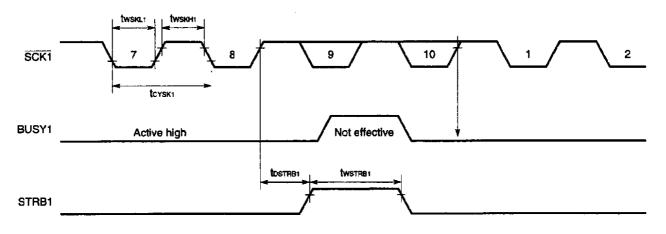

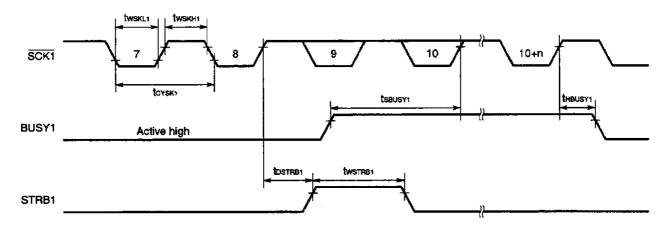

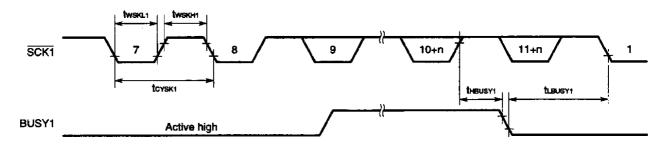

| Serial interface                      |         | <ul> <li>2 built-in channels</li> <li>SIO0 : Either NEC format serial bus interface (SBI) or 3-wire serial interface can be selected.</li> <li>SIO1 : Only a 3-wire serial interface is specified.<br/>The automatic data send/receive function is provided.<br/>(Send/receive buffer: 48 bytes)</li> </ul>                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                          |  |  |

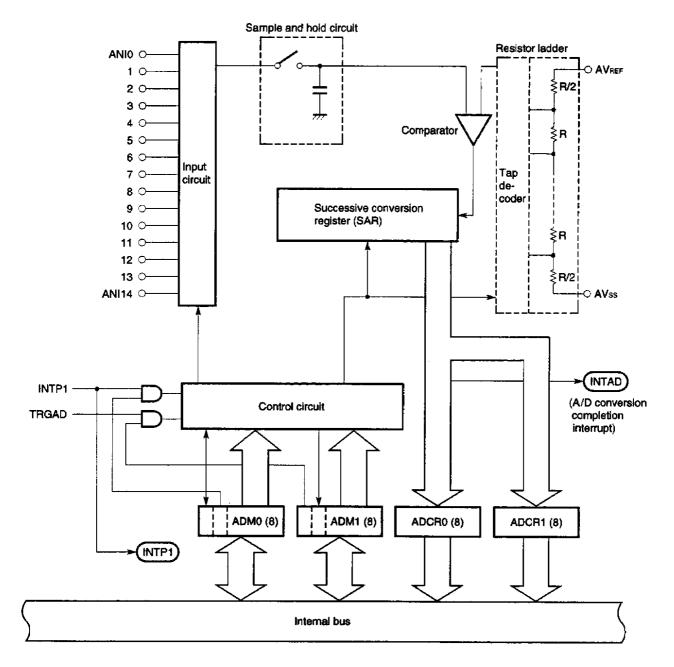

| A/D converter                         |         | 8-bit resolution × 15 inputs (7 inputs can also be used as input ports.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                          |  |  |

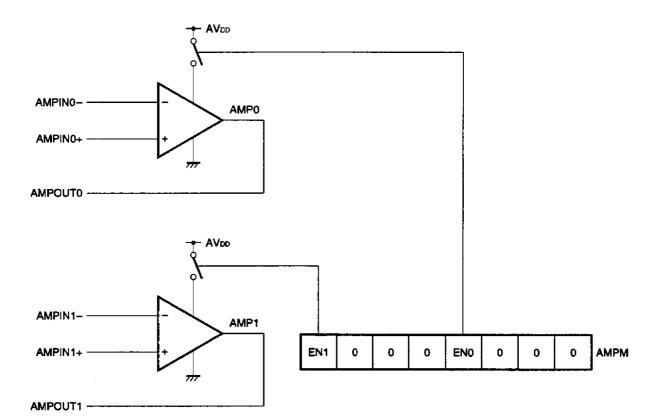

| Analog circuit                        |         | 2 operational amplifiers (Each amplifier can be used separately.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                          |  |  |

| Interrupt                             |         | <ul> <li>Interrupt source: 25 (5 external and 20 internal)</li> <li>One of the two service modes can be selected (vectored interrupt/macro service).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                          |  |  |

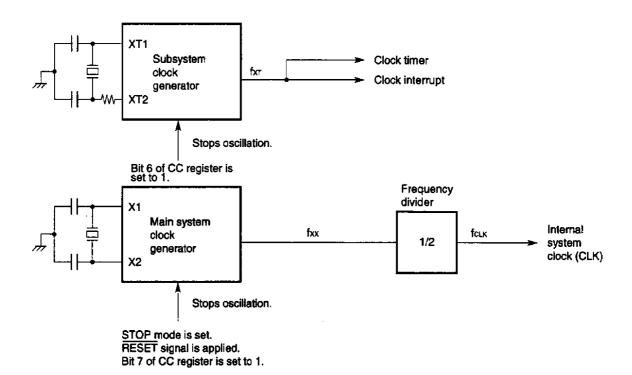

| Clock                                 |         | <ul> <li>Dual clock configuration<br/>(Either a main system clock or subsystem clock can be selected.)</li> <li>Can perform counting in the standby mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                          |  |  |

| Standby                               |         | STOP/HALT mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                          |  |  |

| Pull-up resistor                      |         | 48, built-in (The use of built-in pull-up resistors can be specified by software.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                          |  |  |

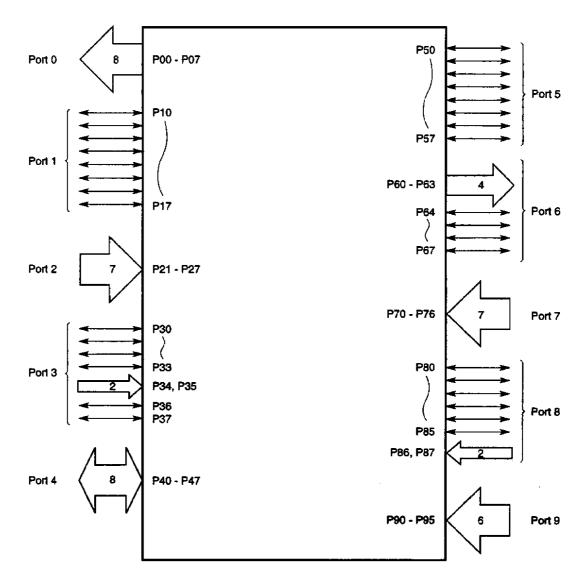

**PIN CONFIGURATION (Top View)**

100-pin plastic QFP

Phase-out/Discontinued

Caution Fix the MODE pin at the ground level.

,

~

| P00 - P07           | : Port 0                                | CTLDLY        | : Control delay input              |

|---------------------|-----------------------------------------|---------------|------------------------------------|

| P10 - P17           | : Port 1                                | ANIO - ANI14  | : Analog input 0 - 14              |

| P21 - P27           | : Port 2                                | AMPINO-, AMF  |                                    |

| P30 - P37           | : Port 3                                |               | : Analog amplifier 0, 1 input ()   |

| P40 - P47           | : Port 4                                | AMPINO+, AMP  |                                    |

| P50 - P57           | : Port 5                                |               | : Analog amplifier 0, 1 input (+)  |

| P60 - P67           | : Port 6                                | AMPOUT0, 1    | : Analog amplifier 0, 1 output     |

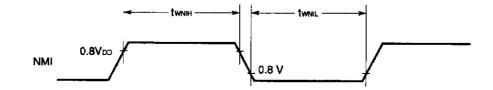

| P70 - P76           | : Port 7                                | NMI           | : Nonmaskable interrupt            |

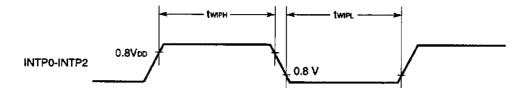

| P80 - P87           | : Port 8                                | INTPO - INTP2 | : Interrupt from peripherals 0 - 2 |

| P90 - P95           | : Port 9                                | CLO           | : Clock output                     |

| PWM0 - PWM          | 5 : Pulse width modulation output 0 - 5 | BUZ           | : Buzzer clock                     |

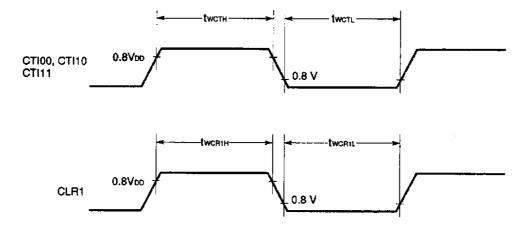

| CTI00, CTI10, CTI11 |                                         | AVREF         | : Analog reference voltage         |

|                     | : Capture trigger input 00, 10, 11      |               | : Analog power supply              |

| CLR0, CLR1          | : Timer clear input 0, 1                | AVss          | : Analog ground                    |

| PTO00 - PTOC        | 2, PTO10, PTO11                         | X1, X2        | : Crystal 1, 2 (Main system clock) |

|                     | : Programmable timer output             | XT1, XT2      | : Crystal 1, 2 (Subsystem clock)   |

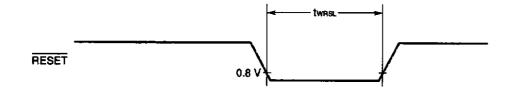

|                     | 00 - 02, 10, 11                         | RESET         | : Reset                            |

| SI0, SI1            | : Serial input 0, 1                     | VDD           | : Power supply                     |

| SO0, SO1            | : Serial output 0, 1                    | Vss           | : Ground                           |

| SB0                 | : Serial bus 0                          | MODE          | : Mode select                      |

| SCKO, SCKI          | : Serial clock 0, 1                     |               |                                    |

| STRB1               | : Serial data transfer strobe 1         |               |                                    |

1

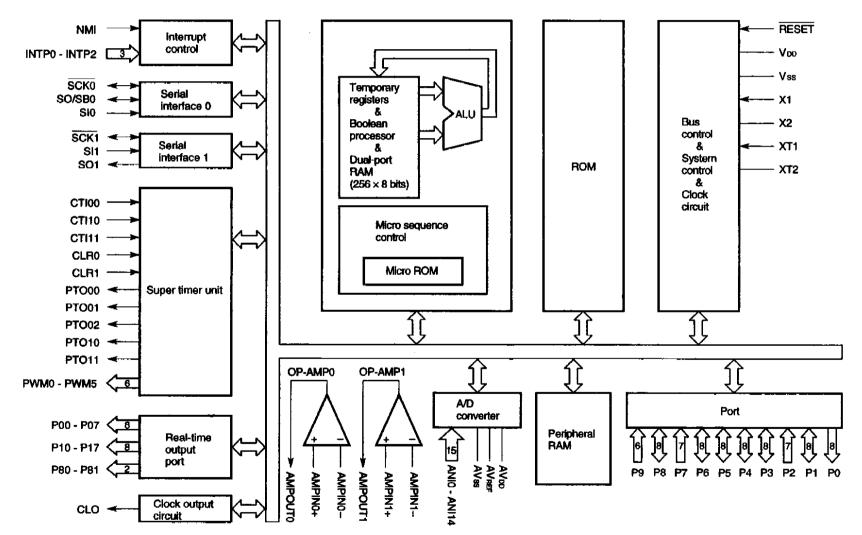

# **BLOCK DIAGRAM**

Π

Π

µPD78146, 78148

)

J

NEC

~

#### CONTENTS

| 1. | PIN F       | UNCTIONS                                            | 8  |

|----|-------------|-----------------------------------------------------|----|

|    | 1.1         | PORT PINS                                           | 8  |

|    | 1.2         | NON-PORT PINS                                       | 10 |

|    | 1.3         | INPUT/OUTPUT CIRCUITS AND CONNECTION OF UNUSED PINS | 12 |

| 2. | CPU         | ARCHITECTURE                                        | 15 |

|    | 2.1         | MEMORY SPACE                                        | 15 |

|    | 2.2         | PROCESSOR REGISTER                                  | 17 |

|    |             | 2.2.1 Control Register                              | 17 |

|    |             | 2.2.2 General Register                              | 18 |

|    |             | 2.2.3 Special Function Register (SFR)               | 19 |

|    | 2.3         | DATA MEMORY ADDRESSING                              | 24 |

| 3. | PERI        | PHERAL HARDWARE FUNCTIONS                           | 25 |

|    | 3.1         | PORT FUNCTIONS                                      | 25 |

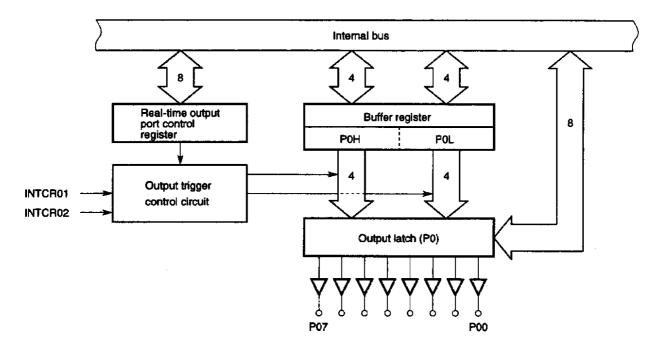

|    | 3.2         |                                                     | 27 |

|    | 3.3         | REAL-TIME OUTPUT PORT (RTP)                         | 29 |

|    | 3.4         | SERIAL INTERFACE                                    | 34 |

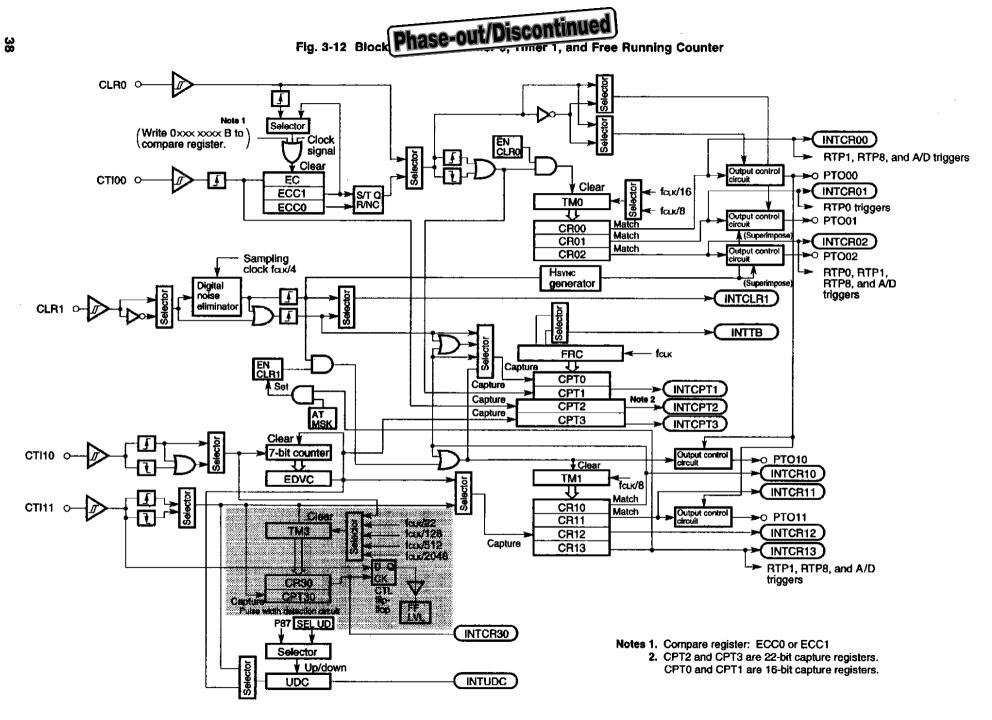

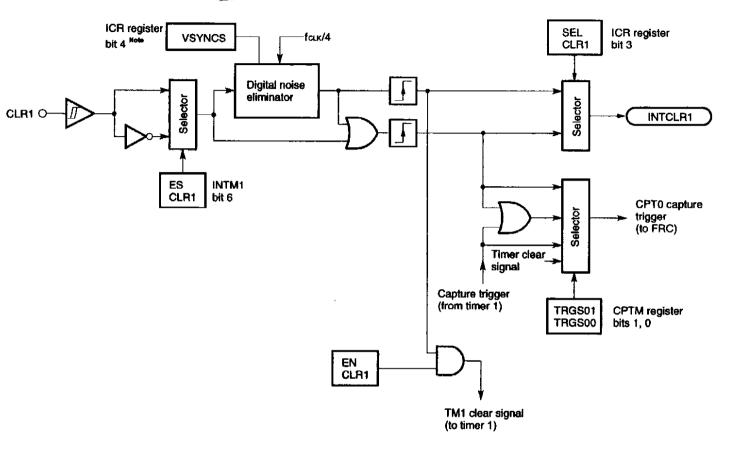

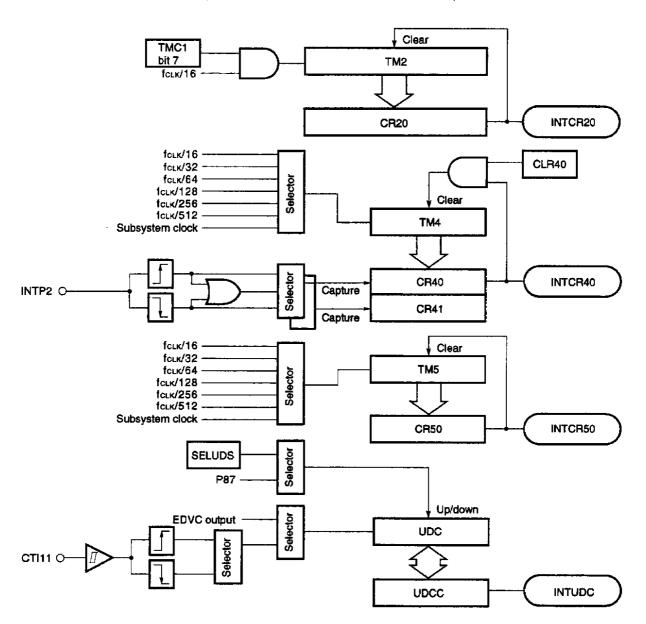

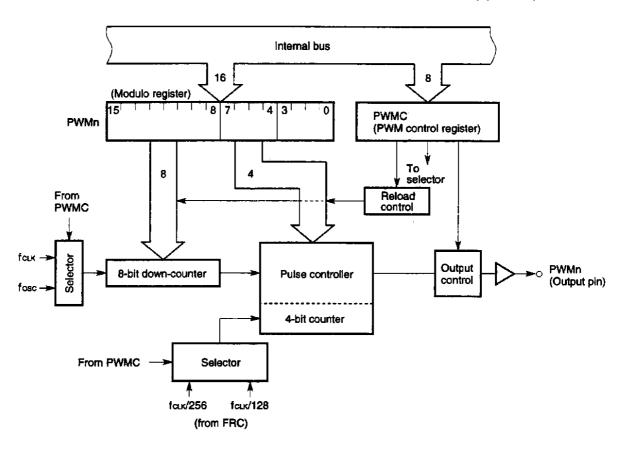

|    | 3.5         | SUPER TIMER UNIT                                    | 37 |

|    |             | 3.5.1 Super Timer Unit Function                     | 39 |

|    | 3.6         | ANALOG CIRCUITRY                                    | 47 |

|    |             | 3.6.1 A/D Converter                                 | 47 |

|    |             | 3.6.2 Operational Amplifier                         | 49 |

|    | 3.7         | CLOCK FUNCTION                                      | 49 |

|    | 3.8         | MULTIPLIER                                          | 50 |

| 4. | INTE        | RRUPT FUNCTIONS                                     | 51 |

|    | <b>4.</b> 1 | VECTORED INTERRUPT AND MACRO SERVICE                | 51 |

|    | 4.2         | INTERRUPT SOURCES                                   | 52 |

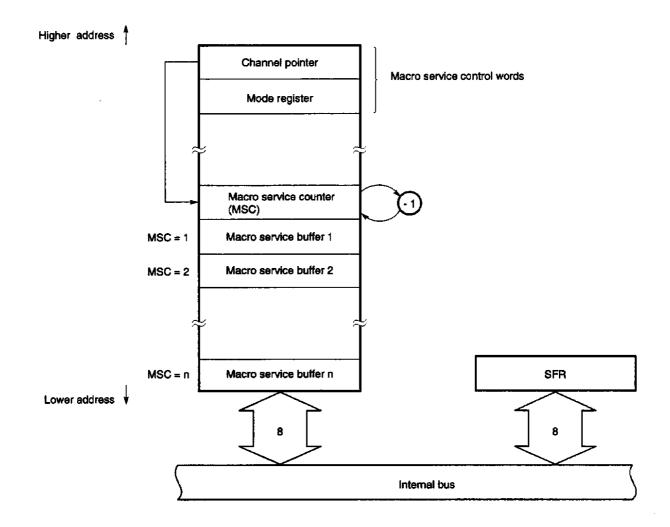

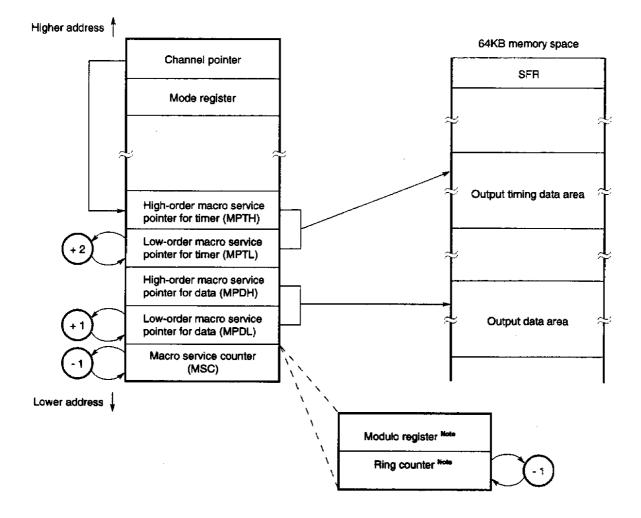

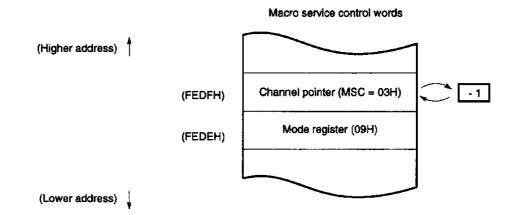

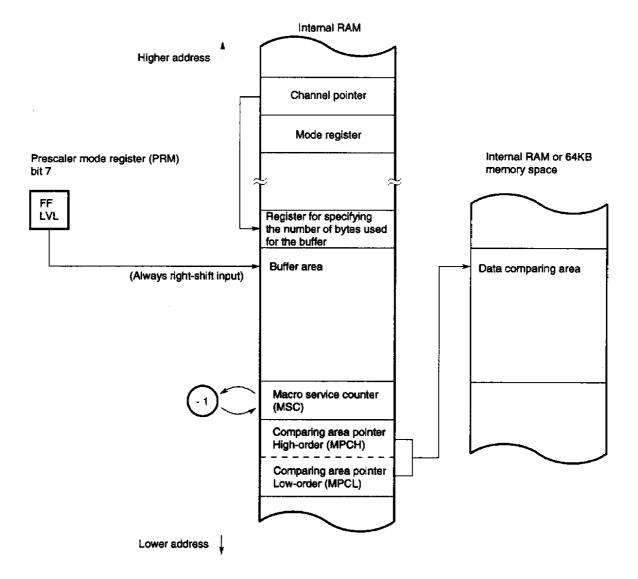

|    | 4.3         | MACRO SERVICE FUNCTIONS                             | 53 |

|    |             | 4.3.1 Macro Service Modes and Interrupt Requests    | 57 |

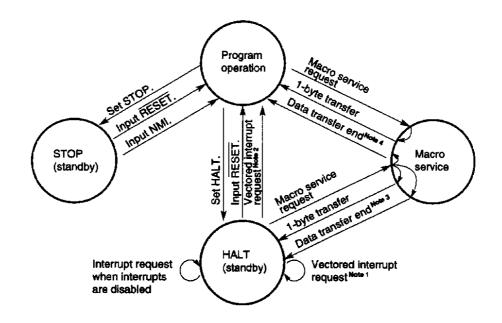

| 5. | STAN        |                                                     | 58 |

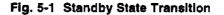

| 6. | RESE        |                                                     | 59 |

| 7. | OPEF        | ATIONS OF INSTRUCTIONS                              | 61 |

|    | 7.1         | INSTRUCTION SET (ALPHABETICAL ORDER)                | 63 |

| 8. | ELEC        | TRICAL CHARACTERISTICS                              | 65 |

#### NEC

#### μ**PD78146, 78148**

| EC          | <b>Phase-out/Discontinued</b> $\mu$ PD78146, 78                                                           | 148 |

|-------------|-----------------------------------------------------------------------------------------------------------|-----|

| 9. EXAMPLE  |                                                                                                           | 78  |

| 10. PACKAGE | DRAWINGS                                                                                                  | 80  |

| 11. RECOMM  | ENDED SOLDERING CONDITIONS                                                                                | 81  |

| APPENDIX A  | DIFFERENCE BETWEEN $\mu$ PD78148 AND RELATED PRODUCTS ( $\mu$ PD78146, $\mu$ PD78P148, AND $\mu$ PD78138) | 82  |

| APPENDIX B  | DEVELOPMENT TOOLS                                                                                         | 83  |

~

#### **1. PIN FUNCTIONS**

#### 1.1 PORT PINS (1/2)

| Pin       | 1/0 | Dual-function pin | Function                                                                                                                                                                                                                                                                             |

|-----------|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00 - P07 | 0   | -                 | <ul> <li>Port 0 (P0):</li> <li>Can be specified to output or high impedance in units of 8 bits.</li> <li>Also function as an 8 bits × 1 or 4 bits × 2 real-time output port.</li> </ul>                                                                                              |

| P10 - P17 | 1/0 | _                 | <ul> <li>Port 1 (P1):</li> <li>Can be specified to input or output bit by bit.</li> <li>Can directly drive LED.</li> <li>The use of built-in pull-up resistors can be specified by software (P10 - P17).</li> <li>Can be specified as a real-time output port bit by bit.</li> </ul> |

| P21       | 1   | INTPO             | Port 2 (P2):                                                                                                                                                                                                                                                                         |

| P22       |     | INTP1             | The use of built-in pull-up resistors can be specified by software                                                                                                                                                                                                                   |

| P23       |     | INTP2             | (P22 - P27).                                                                                                                                                                                                                                                                         |

| P24       |     | CTI10             |                                                                                                                                                                                                                                                                                      |

| P25       |     | СТ100             |                                                                                                                                                                                                                                                                                      |

| P26       |     | CTI11             |                                                                                                                                                                                                                                                                                      |

| P27       |     | CLR1              |                                                                                                                                                                                                                                                                                      |

| P30       | 1/0 | РТО00             | Port 3 (P3):                                                                                                                                                                                                                                                                         |

| P31       |     | PT001             | P30 - P33 : I/O port (Can be specified to input or output bit by                                                                                                                                                                                                                     |

| P32       |     | PTO02             | bit.)<br>P34, P35 : Input port                                                                                                                                                                                                                                                       |

| P33       |     | PTO11             | P36, P37 : I/O port (Can be specified to input or output bit by                                                                                                                                                                                                                      |

| P34       | I.  | CLR0              | bit.)                                                                                                                                                                                                                                                                                |

| P35       |     | SIO               | <ul> <li>The use of built-in pull-up resistors can be specified by software<br/>(P30 - P37).</li> </ul>                                                                                                                                                                              |

| P36       | 1/0 | SO0/SB0           |                                                                                                                                                                                                                                                                                      |

| P37       |     | SCK0              |                                                                                                                                                                                                                                                                                      |

| P40 - P47 | I/O | -                 | <ul> <li>Port 4 (P4):</li> <li>Can be specified to input or output in units of 8 bits.</li> <li>Can directly drive LED.</li> <li>The use of built-in pull-up resistors can be specified by software (P40 - P47).</li> </ul>                                                          |

| P50 - P57 | 1/0 | -                 | <ul> <li>Port 5 (P5):</li> <li>Can be specified to input or output bit by bit.</li> <li>Can directly drive LED.</li> <li>The use of built-in pull-up resistors can be specified by software (P50 - P57).</li> </ul>                                                                  |

Phase-out/Discontinued

#### PORT PINS (2/2)

| Pin      | I/O | Dual-function pin | Function                                                                |

|----------|-----|-------------------|-------------------------------------------------------------------------|

| P60      | 0   | CLO               | Port 6 (P6):                                                            |

| P61      |     | BUZ               | P60 - P63 : Output port                                                 |

| P62      |     | STRB1             | P64 - P67 : I/O port (Can be specified to input or output bit by bit.)  |

| P63      |     | -                 | • The use of built-in puil-up resistors can be specified by software    |

| P64      | 1/0 | _                 | (P64 - P67).                                                            |

| P65      |     |                   |                                                                         |

| P66, P67 |     | _                 |                                                                         |

| P70      | 1   | ANI8              | Port 7 (P7)                                                             |

| P71      |     | ANI9              |                                                                         |

| P72      |     | ANI10             |                                                                         |

| P73      |     | ANI11             |                                                                         |

| P74      |     | AMPOUT0/ANI12     |                                                                         |

| P75      |     | AMPINO-/ANI13     |                                                                         |

| P76      |     | AMPIN0+/ANI14     |                                                                         |

| P80      | 1/0 | -                 | Port 8 (P8):                                                            |

| P81      |     |                   | P80 - P85 : I/O port (Can be specified to input or output bit by        |

| P82      |     | PWM2              | bit.)<br>P86, P87 : Input port                                          |

| P83      |     | РШМЗ              | The use of built-in pull-up resistors can be specified by software      |

| P84      |     | PWM4              | (P80 - P85).                                                            |

| P85      |     | PWM5              | P80 and P81 can be specified as a real-time output port bit by     bit. |

| P86      | 1   | XT1               | ]                                                                       |

| P87      |     | CTLDLY            | m                                                                       |

| P90      | 1   | AMPIN1+           | Port 9 (P9)                                                             |

| P91      |     | AMPIN1-           |                                                                         |

| P92      |     | AMPOUT1           |                                                                         |

| P93      |     | SCK1              | ]                                                                       |

| P94      |     | SO1               | ]                                                                       |

| P95      |     | SI1               | ]                                                                       |

,

~

#### 1.2 NON-PORT PINS (1/2)

| Pin           | 1/0 | Dual-function pin | Function                                                                                                                                                        |

|---------------|-----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWM0, PWM1    | 0   | _                 | Super timer unit PWM output                                                                                                                                     |

| PWM2 - PWM5   | 0   | P82 - P85         | Super timer unit PWM output                                                                                                                                     |

| CLR0          | 1   | P34               | Super timer unit input                                                                                                                                          |

| CT100         |     | P25               |                                                                                                                                                                 |

| CLR1          |     | P27               | ]                                                                                                                                                               |

| CTI10         |     | P24               |                                                                                                                                                                 |

| CT 11         |     | P26               |                                                                                                                                                                 |

| PTO00         | 0   | P30               | Super timer unit output                                                                                                                                         |

| PTO01         |     | P31               |                                                                                                                                                                 |

| PTO02         | ]   | P32               | ]                                                                                                                                                               |

| PTO10         | 1   | _                 | -                                                                                                                                                               |

| PTO11         | 0   | P33               | Super timer unit output<br>Can output the drive waveform corresponding to VISS/VASS<br>postwriting.                                                             |

| SI0           | 1   | P35               | Serial data input 0                                                                                                                                             |

| SOO           | 1/0 | P36/SB0           | Serial data output 0 (3-wire serial I/O mode)                                                                                                                   |

| SB0           | 1/0 | P36/SO0           | Serial data input/output 0 (SBI mode)                                                                                                                           |

| SCK0          | 1/0 | P37               | Serial clock input/output 0                                                                                                                                     |

| SI1           | 1   | P95               | Serial data input 1                                                                                                                                             |

| SO1           | 0   | P94               | Serial data output 1                                                                                                                                            |

| SCK1          | 1/0 | P93               | Serial clock input/output 1                                                                                                                                     |

| STRB1         | 0   | P62               | Strobe output during automatic SIO1 data transfer                                                                                                               |

| NMI           | 4   | _                 | Non-maskable interrupt request input                                                                                                                            |

| INTP0 - INTP2 | 1   | P21 - P23         | External interrupt request input                                                                                                                                |

| CTLDLY        | -   | P87               | External time constant circuit connection:<br>The external time constant circuit of CR is connected to this pin<br>when PTO11 is used as VISS/VASS postwriting. |

| CLO           | -   | P60               | Clock output                                                                                                                                                    |

#### μ**PD78146, 78148**

#### NON-PORT PINS (2/2)

| Pin          | I/O    | Dual-function pin | Function                                              |

|--------------|--------|-------------------|-------------------------------------------------------|

| ANIO - ANI7  | Analog | -                 | Analog signal input to A/D converter                  |

| ANI8 - ANI11 | input  | P70 - P73         |                                                       |

| ANI12        |        | P74/AMPOUT0       |                                                       |

| ANI13        |        | P75/AMPIN0-       |                                                       |

| ANI14        |        | P76/AMPIN0+       |                                                       |

| AMPINO-      | Analog | P75/ANI13         | Inverted input to operational amplifier 0             |

| AMPIN0+      | input  | P76/ANI14         | Uninverted input to operational amplifier 0           |

| AMPOUT0      | 0      | P74/ANI12         | Operational amplifier 0 output                        |

| AMPIN1-      | Analog | P91               | Inverted input to operational amplifier 1             |

| AMPIN1+      | input  | P90               | Uninverted input to operational amplifier 1           |

| AMPOUT1      | 0      | P92               | Operational amplifier 1 output                        |

| RESET        | 1      | -                 | Reset input                                           |

| BUZ          | 0      | P61               | Buzzer output                                         |

| AVDD         | -      | -                 | Positive power supply of an analog circuit            |

| AVss         | -      | -                 | Ground potential of an analog circuit                 |

| AVREF        | -      | -                 | Reference voltage input to A/D converter              |

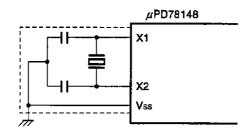

| X1           | 1      | -                 | Crystal connection for main system clock oscillation. |

| X2           | -      | -                 |                                                       |

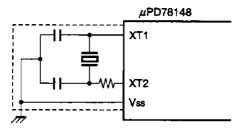

| XT1          | 1      | <br>P86           | Crystal connection for subsystem clock oscillation.   |

| XT2          | -      |                   | Crystal connection for clock oscillation              |

| Voo          |        | -                 | Positive power supply of a digital circuit            |

| Vss          | -      | -                 | Ground potential of a digital circuit                 |

| MODE         | -      | _                 | Fixed at the ground level                             |

Phase-out/Discontinued

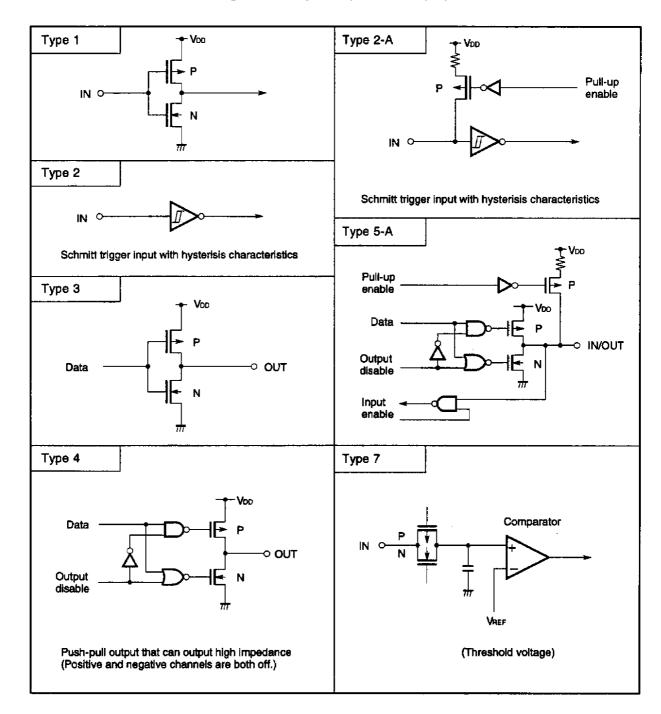

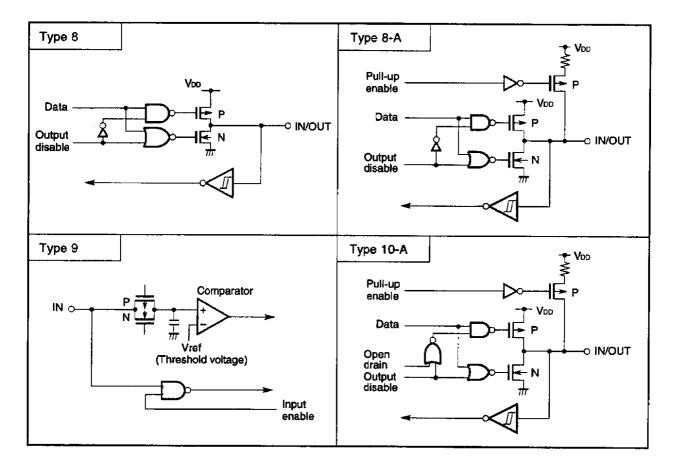

#### 1.3 INPUT/OUTPUT CIRCUITS AND CONNECTION OF UNUSED PINS

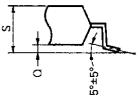

Table 1-1 and Fig. 1-1 show simplified pin input/output circuits.

#### Table 1-1 I/O Circuit Type of Each Pin and Recommended Connection of Unused Pins

**Phase-out/Discontinued**

| Pin         | I/O circuit type | Recommended connection of unused pins                            |

|-------------|------------------|------------------------------------------------------------------|

| P00 - P07   | 4                | Open                                                             |

| P10 - P17   | 5-A              | Input : Connected to Voo via pull-up resistor<br>Output : Open   |

| P21         | 2                | Connected to Vop                                                 |

| P22 - P27   | 2-A              |                                                                  |

| P30 - P33   | 5-A              | Input : Connected to Voo via pull-up resistor<br>Output : Open   |

| P34, P35    | 2-A              | Connected to Voo                                                 |

| P36         | 10 <b>-A</b>     | Input : Connected to Vod via pull-up resistor                    |

| P37         | 8-A              | Output : Open                                                    |

| P40 - P47   | 5-A              | Input : Connected to Vop via pull-up resistor                    |

| P50 - P57   |                  | Output : Open                                                    |

| P60 - P63   | 3                | Open                                                             |

| P64 - P67   | 5-A              | Input : Connected to Voo via pull-up resistor<br>Output : Open   |

| P70 - P76   | 9                | Connected to Vss                                                 |

| P80 - P85   | 5-A              | Input : Connected to Voo via pull-up resistor<br>Output : Open   |

| P86         | 1                | Connected to Vss (Bit 6 of the clock control register is reset.) |

| P87         | 1                | Connected to Voo                                                 |

| P90 - P92   | 1                | Connected to Vss                                                 |

| P93, P94    | 8                | Connected to Veo via pull-up resistor                            |

| P95         | 2                | Connected to Voc                                                 |

| PWM0, PWM1  | 3                | Open                                                             |

| PTO10       |                  |                                                                  |

| ANIO - ANI7 | 7                | Connected to Vss                                                 |

| RESET       | 2                | -                                                                |

| AVREF       | -                | Connected to Vss                                                 |

| AVss        |                  |                                                                  |

#### μ**PD78146, 78148**

Fig. 1-1 Pin Input/Output Circuits (1/2)

13

.

Fig. 1-1 Pin Input/Output Circuits (2/2)

Phase-out/Discontinued

#### 2. CPU ARCHITECTURE

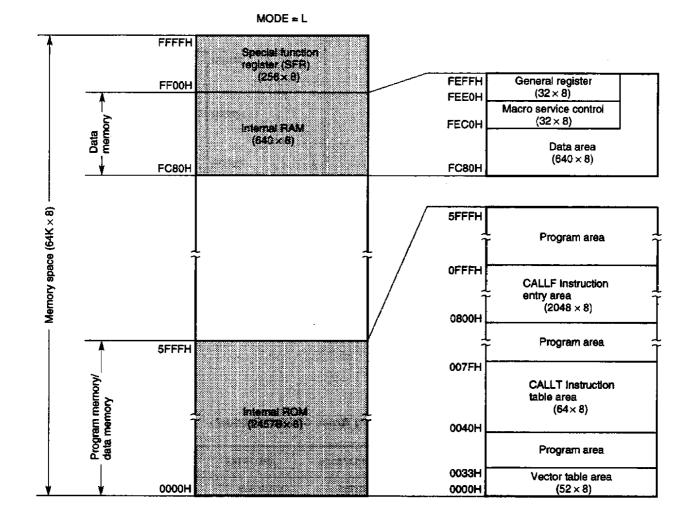

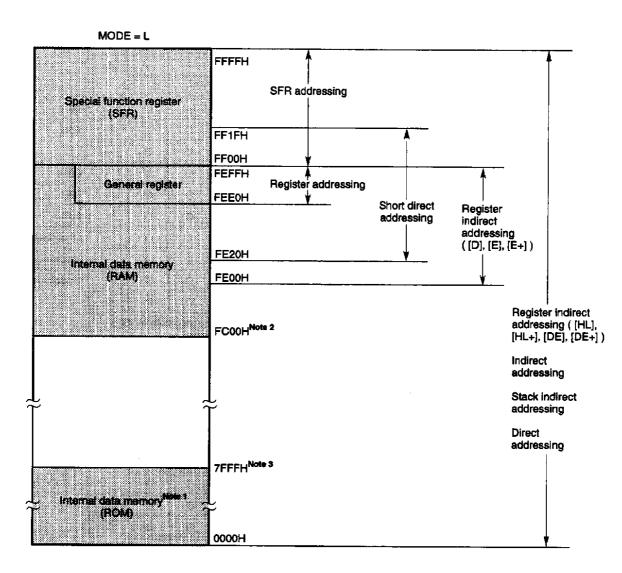

#### 2.1 MEMORY SPACE

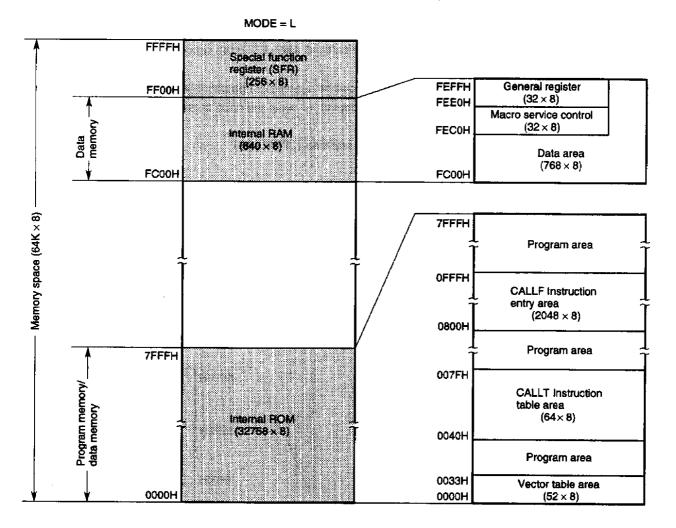

Fig. 2-1 and 2-2 show the memory space of the  $\mu$ PD78146 and  $\mu$ PD78148 respectively.

**Remark** Forty-eight bytes from FF90H to FFBFH can be used as peripheral RAM when they are not used as a buffer for automatic transmission and reception of serial interface channel 1.

Fig. 2-1 Memory Map (µPD78146)

Shaded portions indicate internal memory.

15

Fig. 2-2 Memory Map (µPD78148)

Shaded portions indicate internal memory.

| Table 2-1 Memory Areas of Each Product | Table 2-1 | Memory | Areas o | f Each | Product |

|----------------------------------------|-----------|--------|---------|--------|---------|

|----------------------------------------|-----------|--------|---------|--------|---------|

| Product Item | μPD78146                     | μPD78148                     |

|--------------|------------------------------|------------------------------|

| Internal ROM | 24K bytes<br>(0000H - 5FFFH) | 32K bytes<br>(0000H - 7FFFH) |

| Internal RAM | 688 bytes<br>(FC80H - FEFFH) | 816 bytes<br>(FC00H - FEFFH) |

#### 2.2 PROCESSOR REGISTER

Registers of the  $\mu$ PD78148 are classified into three groups according to their functions:

Phase-out/Discontinued

- Control register

- · General register

- · Special function register (SFR)

#### 2.2.1 Control Register

The control register group controls the program sequence, status, and stack memory. There are three control register:

- Program counter (PC) : 16-bit register

- Program status word (PSW) : 8-bit register

- Stack pointer (SP) : 16-bit register

Fig. 2-3, 2-4, and 2-5 show the configuration of each register.

#### Fig. 2-3 Configuration of Program Counter (PC)

|    | 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| PC | PC15 | PC14 | PC13 | PC12 | PC11 | PC10 | PC9 | PC8 | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |

#### Fig. 2-4 Configuration of Program Status Word (PSW)

|     | 7  | 6 | 5    | 4  | 3    | 2 | 1   | 0  |

|-----|----|---|------|----|------|---|-----|----|

| PSW | IE | Z | RBS1 | AC | RBS0 | 0 | ISP | CY |

| СҮ  | Carry flag                     |

|-----|--------------------------------|

| ISP | Interrupt priority status flag |

|     |                                |

| •   | Auxiliary carry flag           |

| Ζ   |                                |

| IE  | Interrupt request enable flag  |

#### Fig. 2-5 Configuration of Stack Pointer (SP)

|    | 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| SP | SP15 | SP14 | SP13 | SP12 | SP11 | SP10 | SP9 | SP8 | SP7 | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 |

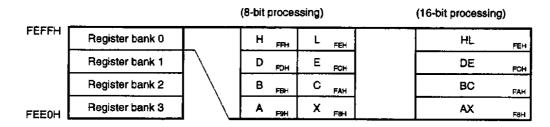

#### 2.2.2 General Register

The general register group of the  $\mu$ PD78148 consists of four banks of general registers. Each bank consists of eight 8-bit registers, so there are 32 registers in total. A pair of 8-bit registers can function as a 16-bit register pair.

Phase-out/Discontinued

The general register group is mapped into addresses from FEE0H to FEFFH of the internal RAM space.

Fig. 2-6 shows the configuration of the general register and Table 2-2 shows the correspondence between function names and absolute names.

#### Table 2-2 Correspondence between Function Names and Absolute Names

| Function name | Absolute name |

|---------------|---------------|

| ×             | R0            |

| A             | R1            |

| С             | R2            |

| В             | R3            |

| E             | R4            |

| D             | R5            |

| L             | R6            |

| н             | <b>R</b> 7    |

| Function name | Absolute name |

|---------------|---------------|

| AX            | RP0           |

| BC            | RP1           |

| DE            | RP2           |

| HL            | RP3           |

#### 2.2.3 Special Function Register (SFR)

The special function register group consists of the registers to which special functions are given such as mode register of the peripheral hardware.

Phase-out/Discontinued

This register group is assigned to the 256-byte space from FF00H to FFFFH. Short direct memory addressing can be applied to the 32-byte area from FF00H to FF1FH, allowing short-word data processing.

Forty-eight bytes from FF90H to FFBFH are used as a buffer for automatic transmission and reception of serial interface channel 1. The area can be accessed in the same way as for peripheral RAM. In SFR addressing, the area cannot be accessed.

Bit manipulation, arithmetic/logical, and move instructions can be executed in all the areas. Table 2-3 lists the special function registers (SFRs). The items in Table 2-2 mean:

- Abbreviation ...... A symbol indicating the address of a built-in special function register

This can be specified in the operand field of an instruction.

- R/W ..... Indicates whether data can be read from the special function register and/or data can

be written into the register.

R/W: Can be read and written.

- R : Can be read. (The bits of the register can be tested.)

- W : Can be written.

Manipulation bit unit ...... Indicates the unit of bits that can be manipulated at one time.

- The SFR which can be manipulated in units of 16 bits can be specified in the sfrp operand. An even address is specified for the address specification. The SFR which can be manipulated bit by bit can be specified by a bit manipulation instruction.

- After reset ...... Indicates the status of each register after the RESET input.

- Cautions 1. The addresses to which a special function register is not assigned in the area from FF00H to FFFFH can not be accessed.

- 2. Do not write data into the register which is only used for data reading. If an attempt is made to write data into such registers, the internal circuit may not operate normally.

| Address | Special function register (SFR) name                       | Abbrevia- | R/W | Manip | ulation | bit unit | After reset |  |

|---------|------------------------------------------------------------|-----------|-----|-------|---------|----------|-------------|--|

| Audress |                                                            | tion      |     | 1     | 8       | 16       | After reset |  |

| FF00H   | Port 0                                                     | P0        | R/W | 0     | 0       | -        | Undefined   |  |

| FF01H   | Port 1                                                     | P1        |     | 0     | 0       | 1        |             |  |

| FF02H   | Port 2                                                     | P2        | R   | 0     | 0       | -        | 1           |  |

| FF03H   | Port 3                                                     | P3        | R/W | 0     | 0       |          |             |  |

| FF04H   | Port 4                                                     | P4        | 1   | 0     | 0       | -        | -           |  |

| FF05H   | Port 5                                                     | P5        |     | 0     | 0       |          |             |  |

| FF06H   | Port 6                                                     | P6        |     | 0     | 0       | -        | FOH         |  |

| FF07H   | Port 7                                                     | P7        | R   | 0     | 0       | -        | Undefined   |  |

| FF08H   | 16-bit timer 0 compare register 0                          | CR00      | R/W | _     | _       | 0        | Undefined   |  |

| FF09H   |                                                            |           |     | -     | -       |          |             |  |

| FFOAH   | 16-bit timer 0 compare register 1                          | CR01      | -   | _     | -       | 0        | 4           |  |

| FF0BH   |                                                            |           |     | _     |         | 1        |             |  |

| FF0CH   | 16-bit timer 0 compare register 2                          | CR02      |     | -     | _       | 0        |             |  |

| FFODH   |                                                            |           |     | -     | -       |          |             |  |

| FFOEH   | 16-bit timer 1 compare register 0                          | CR10      |     | -     | _       | 0        |             |  |

| FFOFH   |                                                            |           |     | _     | _       |          |             |  |

| FF10H   | 16-bit timer 1 compare register 1                          | CR11      |     | -     | _       | 0        |             |  |

| FF11H   |                                                            |           |     | -     | _       |          |             |  |

| FF12H   | 16-bit timer 1 compare register 2                          | CR12      | R   |       | _       | 0        | ĺ           |  |

| FF13H   |                                                            |           |     | -     | -       |          |             |  |

| FF14H   | 16-bit FRC capture register 0                              | CPT0      |     | -     | -       | 0        |             |  |

| FF15H   |                                                            | 16<br>1   |     | -     | -       |          |             |  |

| FF16H   | 16-bit FRC capture register 1                              | CPT1      | 1   | _     | _       | 0        |             |  |

| FF17H   |                                                            |           |     | -     | -       |          |             |  |

| FF18H   | 22-blt FRC capture register 2                              | CPT2H     | R   | -     | _       | 0        | Undefined   |  |

| FF19H   | (Bits 2 to 17)                                             |           |     | -     | _       |          |             |  |

| FF1AH   | 22-bit FRC capture register 3 Note                         | СРТЭН     | 1   | _     | _       | 0        | 1           |  |

| FF18H   | (Bits 2 to 17)                                             |           |     | _     | -       |          |             |  |

| FF1CH   | 22-bit FRC capture register 2<br>(Bits 0, 1, and 18 to 21) | CPT2L     |     | 0     | 0       | _        |             |  |

| FF1DH   | Prescaler mode register 3                                  | PRM3      | R/W | 0     | 0       | _        | 0xxxx000    |  |

| FF1EH   | 16-bit timer 2 compare register                            | CR20      | 1   | _     | -       | 0        | Undefined   |  |

| F1FH    |                                                            |           |     |       | _       |          |             |  |

#### Table 2-3 Special Function Registers (SFRs) (1/4)

Note Address of six low-order bits is FF42H.

#### Table 2-3 Special Function Registers (SFRs) (2/4)

| Address | Special function register (SFR) name                    | Abbrevia- | B/W | Manip    | ulation | bit unit | After reset                      |

|---------|---------------------------------------------------------|-----------|-----|----------|---------|----------|----------------------------------|

|         |                                                         | tion      | 1   | 1        | 8       | 16       | Alto 1030(                       |

| FF20H   | Port 0 mode register                                    | PM0       | w   |          | 0       | _        | FFH                              |

| FF21H   | Port 1 mode register                                    | PM1       |     | -        | 0       | -        |                                  |

| FF23H   | Port 3 mode register                                    | РМЗ       |     | -        | 0       | -        |                                  |

| FF25H   | Port 5 mode register                                    | PM5       |     | 1        | 0       | -        |                                  |

| FF26H   | Port 6 mode register                                    | PM6       |     | 1        | 0       | -        | FOH                              |

| FF28H   | Port 8 mode register                                    | PM8       | w   | -        | 0       | -        | FFH                              |

| FF2CH   | Multiplicand/multiplication result register             | MULL      | R/W | ł        | -       | 0        | Undefined                        |

| FF2DH   |                                                         |           |     | I        | -       |          |                                  |

| FF2EH   | Multiplicator/multiplication result register            | MULH      |     | -        | -       | 0        |                                  |

| FF2FH   |                                                         |           |     | -        | -       |          |                                  |

| FF30H   | 16-bit timer register 0                                 | тмо       | R   | -        | -       | 0        | Undefined for                    |

| FF31H   |                                                         |           |     | -        | -       |          | up to 16 clocks                  |

| FF32H   | 16-bit timer register 1                                 | TM1       |     | -        | -       | 0        | Cleared to 0<br>after 17th close |

| FF33H   |                                                         |           |     | -        | -       |          |                                  |

| FF34H   | 22-bit free running counter                             | FRC       | R   | -        | -       | 0        | Undefined for<br>up to 16 clocks |

| FF35H   |                                                         |           |     | -        | -       | ]        | Cleared to 0<br>after 17th clock |

| FF36H   | 16-bit timer register 2                                 | TM2       | R   | -        | -       | 0        | Undefined for<br>up to 16 clocks |

| FF37H   |                                                         |           |     |          | -       |          | Cleared to 0<br>after 17th clock |

| FF38H   | Timer control register 0                                | TMC0      | F/W | -        | 0       | -        | 00H                              |

| FF39H   | Timer control register 1                                | TMC1      | R/W | -        | 0       | _        | оон                              |

| FF3AH   | Capture mode register                                   | СРТМ      | R/W | -        | 0       | -        | 30H                              |

| FF3BH   | 7-bit counter register                                  | TM6       | R   | -        | 0       | _        | Undefined                        |

| FF3CH   | 6-bit counter register                                  | TM7       |     | -        | 0       | _        |                                  |

| FF3DH   | 8-bit timer register 3 Note                             | TM3       | ₽/W | _        | 0       | -        |                                  |

| FF3EH   | 8-bit timer 3 compare register                          | CR30      | R/W | -        | 0       | -        | Undefined                        |

| FF3FH   | 8-bit timer 3 capture register                          | CPT30     | R   | -        | 0       | -        | Undefined                        |

| FF40H   | Register for optional pull-up register                  | PUO       | R/W | 0        | 0       | -        | 00H                              |

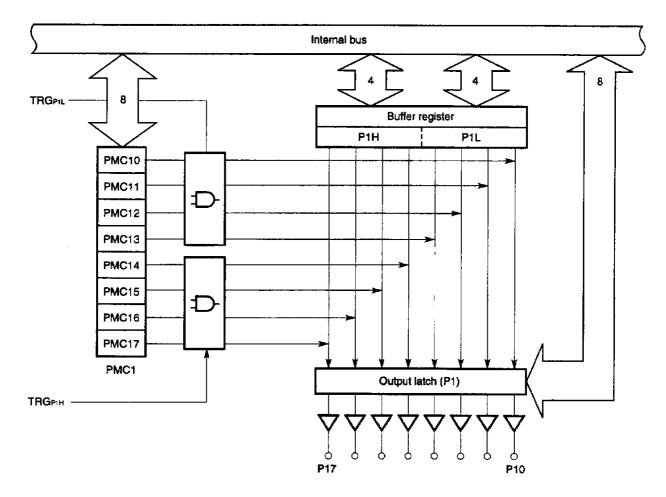

| FF41H   | Port 1 mode control register                            | PMC1      | R/W | 0        | 0       | -        | 00H                              |

| FF42H   | 22-bit FRC capture register 3 (bits 0, 1, and 18 to 21) | CPT3L     | R   | 0        | 0       | -        | Undefined                        |

| FF43H   | Port 3 mode control register                            | PMC3      | R/W | 0        | 0       | -        | 30H                              |

| FF44H   | 16-bit timer 1 compare register 3                       | CR13      | -   | _        |         | 0        | Undefined                        |

| FF45H   |                                                         |           |     | -        | -       | ł        |                                  |

| FF46H   | Port 1 buffer register                                  | P1L       | 1   | -<br>0   | 0       |          | 1                                |

| FF47H   | Port 1 buffer register                                  | P1H       | 1   | 0        | 0       | _        |                                  |

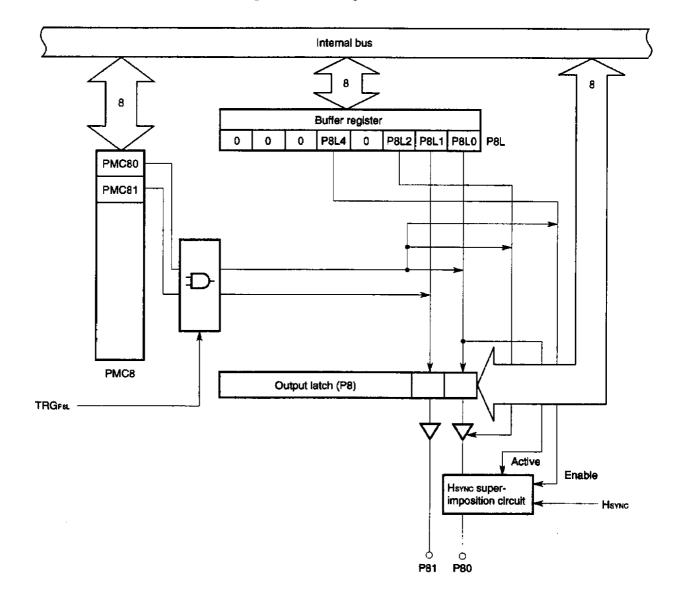

| FF48H   | Port 8 mode control register                            | PMC8      | -   | 0        | 0       | _        | СОН                              |

| FF49H   | Port 9 mode control register                            | PMC9      | w   | <u> </u> | 0       | _        | 27H                              |

Note TM3 can only be read. Writing on TM3 clears TM3 to 00H.

| Address | Special function register (SFR) name   | Abbrevia- | B/W                 | Mani | pulation | After reset |                           |

|---------|----------------------------------------|-----------|---------------------|------|----------|-------------|---------------------------|

| Add1633 |                                        | tion      |                     | 1    | 8        | 16          | After reset               |

| FF4AH   | Port 0 buffer register                 | POL       | R/W                 | 0    | 0        | -           | Undefined                 |

| FF4BH   | Port 0 buffer register                 | P0H       |                     | 0    | 0        | -           | -                         |

| FF4CH   | Real-time output port control register | RTPC      |                     | 0    | 0        | -           | 00Н                       |

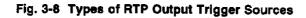

| FF4DH   | Trigger source selection register      | TRGS      | R/W                 | 0    | 0        | <u> </u>    | OOH                       |

| FF4EH   | Port 8 buffer register                 | P8L       |                     | 0    | 0        | -           | Undefined                 |

| FF4FH   | Clock mode register                    | WM        | 1                   | 0    | 0        | _           | 0xxx0x00                  |

| FF50H   | Input control register                 | ICR       | W                   | -    | 0        |             | 00H                       |

| FF51H   | Up/down counter count register         | UDC       | R/W                 | -    | 0        |             | Undefined                 |

| FF52H   | Capture compare control register       | CRC       | w                   | -    | 0        | -           | оон                       |

| FF53H   | Event divider control register         | EDVC      | w                   | -    | 0        | † <u>-</u>  | Undefined                 |

| FF54H   | Event counter compare register 1       | ECC1      |                     | _    | 0        | -           | Undefined                 |

| FF55H   | Event counter compare register 0       | ECC0      |                     |      | 0        |             | Undefined                 |

| FF56H   | Event counter                          | EC        | R                   |      | 0        | -           | Undefined                 |

| FF57H   | Prescaler 4 mode register              | PRM4      | R/ W                | 0    | 0        | _           | 00Н                       |

| FF58H   | Timer 0 output mode register           | TOM0      | W                   | -    | 0        | -           | ××000000                  |

| FF59H   | Timer 0 output control register        | тосо      | w                   | _    | 0        | -           | оон                       |

| FF5AH   | Timer 1 output mode register           | TOM1      | W                   | -    | 0        |             | 80H                       |

| FF5BH   | Timer 1 output control register        | TOC1      | R/W <sup>Note</sup> | -    | 0        | -           | 00Н                       |

| FF5CH   | 8-bit timer register 4                 | TM4       | R                   | -    | 0        | -           | Cleared for 16th<br>clock |

| FF5DH   | 8-bit timer 4 capture compare register | CR40      | R/W                 | 0    | 0        |             | Undefined                 |

| FF5EH   | 8-bit timer register 5                 | TM5       | R                   | -    | 0        | -           | Cleared for 16th<br>clock |

| FF5FH   | 8-bit timer 5 compare register         | CR50      | R/W                 | 0    | 0        | -           | Undefined                 |

| FF60H   | Port 8                                 | P8        | R/W                 | 0    | 0        | _           | Undefined                 |

| FF61H   | Port 9                                 | P9        | R                   | 0    | 0        | -           | i                         |

| FF62H   | Amplifier mode register                | АМРМ      | W                   |      | 0        | -           | 00H                       |

| FF63H   | Up/down counter compare register       | UDCC      | W                   | _    | 0        | -           | Undefined                 |

| FF64H   | A/D conversion mode register 0         | ADM0      | R/W                 | 0    | 0        | -           | 00H                       |

| FF65H   | A/D conversion mode register 1         | ADM1      | R/W                 | 0    | 0        | -           | 01H                       |

| FF66H   | A/D conversion result register 0       | ADCR0     | R                   | _    | 0        |             | Undefined                 |

| FF67H   | A/D conversion result register 1       | ADCR1     | R                   | _    | 0        | -           | Undefined                 |

| FF70H   | PWM control register 0                 | PWMC0     | F/ W                | 0    | 0        | -           | 05H                       |

| FF71H   | PWM control register 1                 | PWMC1     | w                   | -    | ο        | -           | 40H                       |

| FF72H   | PWM0 modulo register                   | PWM0      | w                   | -    | _        | 0           | Undefined                 |

| FF73H   |                                        |           |                     | -    |          |             |                           |

| FF74H   | PWM1 modulo register                   | PWM1      | 1 1                 | _    | -        | 0           |                           |

|         |                                        | <b>1</b>  |                     |      |          |             |                           |

#### Table 2-3 Special Function Registers (SFRs) (3/4)

Note Only bit 0 of TOC1 can be read.

| Address        | Special function register (SFR) name  | Abbrevia | B/W        | Mani               | pulation | bit unit | After reset |

|----------------|---------------------------------------|----------|------------|--------------------|----------|----------|-------------|

|                |                                       | tion     | <b>1 1</b> | 1                  | 8        | 16       | Alter reset |

| FF76H          | PWM2 modulo register                  | PWM2     | w          | _                  | 0        | -        | Undefined   |

| FF77H          | PWM3 modulo register                  | PWM3     |            | -                  | 0        | -        |             |

| FF7AH          | PWM4 modulo register                  | PWM4     |            | -                  | 0        | -        |             |

| FF7BH          | 8-bit timer 4 capture register        | CR41     | R          | -                  | 0        | -        | Undefined   |