# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## **DATA SHEET**

# MOS INTEGRATED CIRCUIT

$\mu$ PD72862

### **IEEE1394 OHCI HOST CONTROLLER**

The  $\mu$ PD72862 is IEEE1394 OHCI-Link controller. The  $\mu$ PD72862 complies with the P1394a draft 2.0 specifications and works up to 400 Mbps.

It supports both of the Cardbus interface and the PCI bus interface.

### **FEATURES**

- Compliant with Link Layer Services as defined in 1394 Open Host Controller Interface specification release 1.0

- Compliant with protocol enhancement as defined in P1394a draft 2.0

- Modular 32-bit host interface compliant to PCI Specification release 2.1

- Supports PCI-Bus Power Management Interface Specification release 1.0

- Supports Cardbus

- Equipped CIS register

- Cycle Master and Isochronous Resource Manager capable

- Compatible to PHY Layer implementation of 100/200/400 Mbps via 2/4/8-bit data interface

- Built-in FIFOs for isochronous transmit (1024 bytes), asynchronous transmit (1024 bytes), and receive (2048 bytes)

- 32-bit CRC generation and checking for receive/transmit packets

- · 4-isochronous transmit DMAs and 4-isochronous receive DMAs supported

- Support both IEEE1394-1995 compliant PHY and P1394a compliant PHY

- · Internal control and operational registers direct-mapped to PCI configuration space

- 2-wire Serial EEPROM™ interface supported

### ORDERING INFORMATION

| Part number    | Package                                     |

|----------------|---------------------------------------------|

| μPD72862GC-9EU | 100-pin plastic TQFP (Fine pitch) (14 x 14) |

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

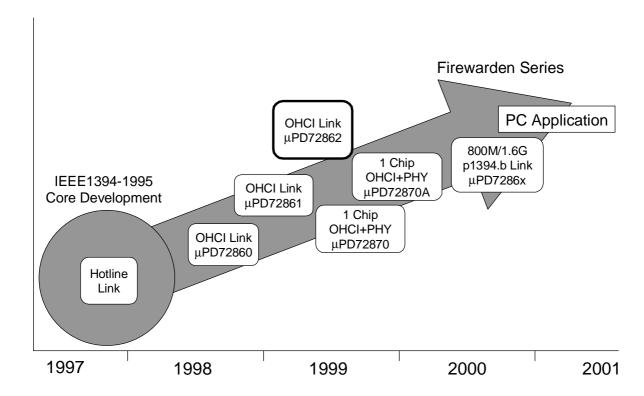

## Firewarden™ ROADMAP

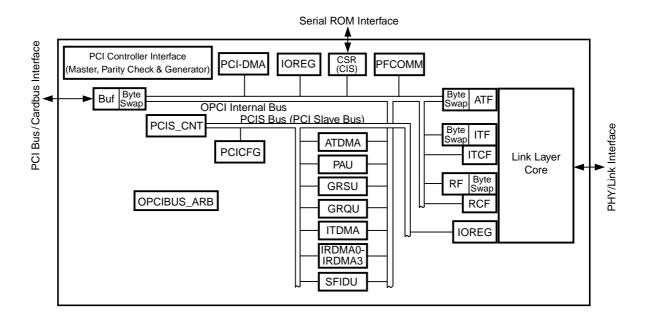

### **BLOCK DIAGRAM**

ATDMA : Asynchronous Transmit DMA ATF : Asynchronous Transmit FIFO

CIS : CIS Register

CSR : Control and Status Registers

IOREG : IO Registers

IRDMA : Isochronous Receive DMA

ITCF : Isochronous Transmit Control FIFO

ITDMA : Isochronous Transmit DMA

ITF : Isochronous Transmit FIFO

OPCIBUS ARB : OPCI Internal Bus Arbitration

PAU : Physical Response and Request Unit

PCICFG : PCI Configuration Registers

PCIS\_CNT : PHY Control Isochronous Control

PFCOMM : Pre Fetch Command FIFO RCF : Receive Control FIFO

RF : Receive FIFO SFIDU : Self-ID DMA

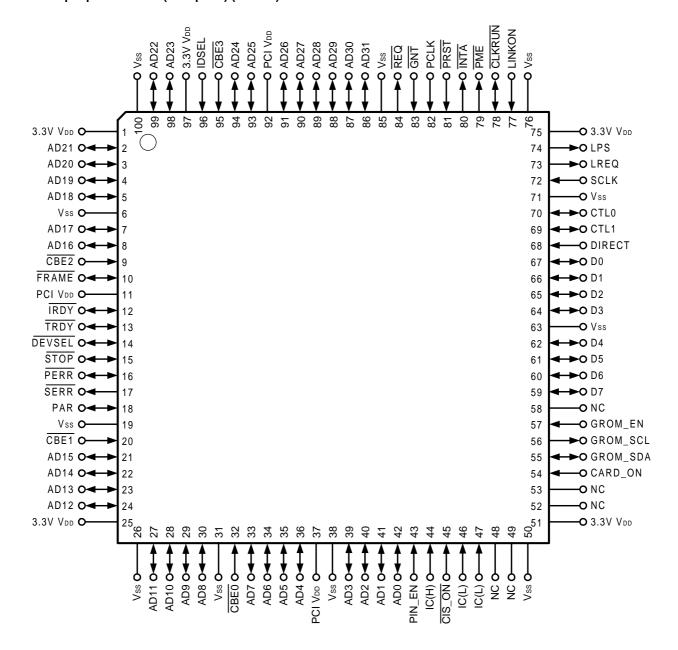

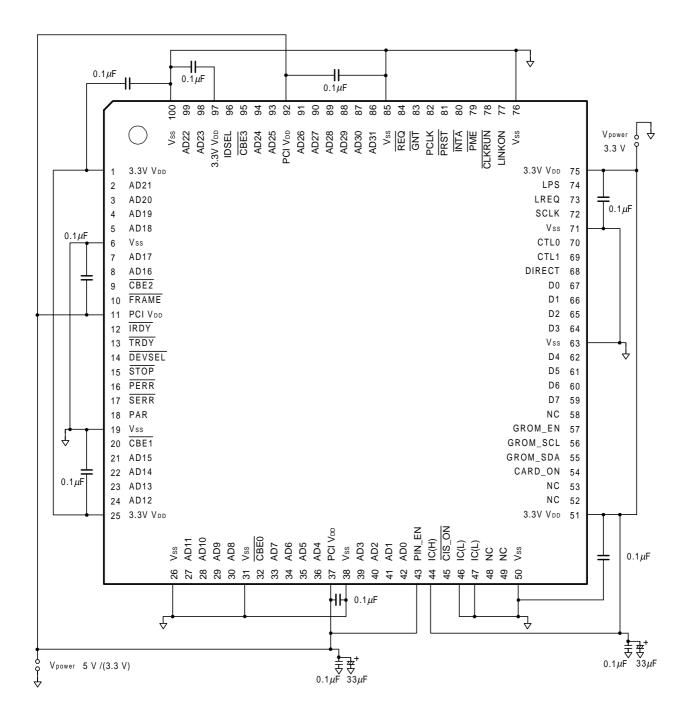

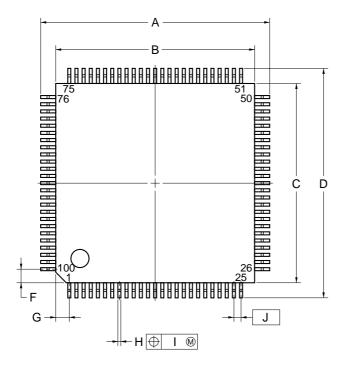

### PIN CONFIGURATION (Top View)

Though the current implementation of the  $\mu$ PD72862 includes signal pins for debugging and testing purpose, the package remains a cost efficient 100-pin TQFP package.

### • 100-pin plastic TQFP (Fine pitch) (14 x 14)

### **PIN NAME**

AD0-AD31 : PCI Multiplexed Address and Data

CARD\_ON : PCI/Card Select

CBE0-CBE3 : Command/Byte Enables

CIS\_ON

: CIS Register ON

CLKRUN

: PCICLK Running

CTL0, CTL1 : PHY/Link Bi-directional Control

DEVSEL : Device Select

DIRECT : Auxiliary PHY/Link Signal

D0-D7 : PHY/Link Bi-directional Data

FRAME : Cycle Frame

GNT : Bus\_master Grant

GROM\_EN : Serial EEPROM Enable

GROM\_SCL : Serial EEPROM Clock Output

GROM\_SDA : Serial EEPROM Data Input / Output

IC (H) : Internally Connected (High Clamped)

IC (L) : Internally Connected (Low Clamped)

IDSEL : ID Select

INTA : Interrupt

IRDY : Initiator Ready

LINKON : Link-On Request

LPS : Link Power Status

LREQ : PHY/Link Request

NC : Non-Connection

PAR : Parity

PCLK : PCI Clock

PERR : Parity Error

PIN\_EN : Pin Enable Input

PME : PME Output

PRST : Reset

REQ : Bus\_master Request

SCLK: PHY ClockSERR: System ErrorSTOP: PCI StopTRDY: Target ReadyVDD: Supply Voltage

Vss : Ground

## **CONTENTS**

| 1. | PIN FUNCTIONS                                                           |    |

|----|-------------------------------------------------------------------------|----|

|    | 1.1 PCI Bus Interface Signals: (52 pins)                                | 8  |

|    | 1.2 PCI/Cardbus Select Signals: (2 pins)                                | 9  |

|    | 1.3 PHY/Link Interface Signals: (15 pins)                               | 10 |

|    | 1.4 Serial ROM Interface Signals: (3 pins)                              | 10 |

|    | 1.5 Miscellaneous Signal: (1 pin)                                       | 10 |

|    | 1.6 IC: (3 pins)                                                        | 10 |

|    | 1.7 NC: (5 pins)                                                        | 10 |

|    | 1.8 Vdd: (8 pins)                                                       | 10 |

|    | 1.9 Vss: (11 pins)                                                      | 10 |

| 2. | REGISTER DESCRIPTIONS                                                   | 11 |

|    | 2.1 PCI Bus Mode Configuration Register ( CARD_ON=Low )                 | 11 |

|    | 2.1.1 Offset_00 VendorID Register                                       | 12 |

|    | 2.1.2 Offset_02 DeviceID Register                                       | 12 |

|    | 2.1.3 Offset_04 Command Register                                        | 12 |

|    | 2.1.4 Offset_06 Status Register                                         | 13 |

|    | 2.1.5 Offset_08 Revision ID Register                                    | 14 |

|    | 2.1.6 Offset_09 Class Code Register                                     | 14 |

|    | 2.1.7 Offset_0C Cache Line Size Register                                | 14 |

|    | 2.1.8 Offset_0D Latency Timer Register                                  | 14 |

|    | 2.1.9 Offset_0E Header Type Register                                    | 14 |

|    | 2.1.10 Offset_0F BIST Register                                          | 14 |

|    | 2.1.11 Offset_10 Base Address 0 Register                                | 15 |

|    | 2.1.12 Offset_2C Subsystem Vendor ID Register                           | 15 |

|    | 2.1.13 Offset_2E Subsystem ID Register                                  | 15 |

|    | 2.1.14 Offset_30 Expansion Rom Base Address Register                    | 15 |

|    | 2.1.15 Offset_34 Cap_Ptr Register                                       | 15 |

|    | 2.1.16 Offset_3C Interrupt Line Register                                | 16 |

|    | 2.1.17 Offset_3D Interrupt Pin Register                                 | 16 |

|    | 2.1.18 Offset_3E Min_Grant Register                                     | 16 |

|    | 2.1.19 Offset_3F Max Lat Register                                       | 16 |

|    | 2.1.20 Offset_40 PCI_OHCI_Control Register                              | 16 |

|    | 2.1.21 Offset_60 Cap_ID & Next_Item_Ptr Register                        | 17 |

|    | 2.1.22 Offset_62 Power Management Capabilities Register                 | 17 |

|    | 2.1.23 Offset_64 Power Management Control/Status Register               |    |

|    | 2.2 CardBus Mode Configuration Register ( CARD_ON=High )                | 18 |

|    | 2.2.1 Offset_14/18 Base_Address_1/2 Register (CardBus Status Registers) | 19 |

|    | 2.2.2 Offset_28 Cardbus CIS Pointer                                     | 20 |

|    | 2.2.3 Offset_80 CIS Area                                                | 20 |

| 3. | SERIAL ROM INTERFACE                                                    | 21 |

|    | 3.1 Serial EEPROM Register                                              | 21 |

|    | 3.2 Serial EEPROM Register Description                                  | 21 |

|    | 3.3 Load Control                                                        |    |

|    | 3.4 Programming Sequence Example                                        | 25 |

| 4. | ELECTRICAL SPECIFICATIONS        | . 27 |

|----|----------------------------------|------|

| 5. | APPLICATION CIRCUIT EXAMPLE      | 30   |

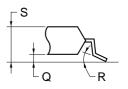

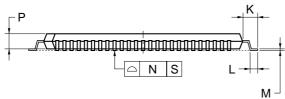

| 6. | PACKAGE DRAWING                  | 31   |

| 7. | RECOMMENDED SOLDERING CONDITIONS | . 32 |

## 1. PIN FUNCTIONS

# 1.1 PCI Bus Interface Signals: (52 pins)

(1/2)

| Name      | I/O | Pin No.    | loL         | Volts(V) | Function                                                              |

|-----------|-----|------------|-------------|----------|-----------------------------------------------------------------------|

| PAR       | I/O | 18         | PCI/Cardbus | 5/3.3    | Parity is even parity across AD0-AD31 and CBE0-CBE3. It is an         |

|           |     |            |             |          | input when AD0-AD31 is an input; it is an output when AD0-AD31 is     |

|           |     |            |             |          | an output.                                                            |

| AD0-AD31  | I/O | 2-5, 7, 8, | PCI/Cardbus | 5/3.3    | PCI Multiplexed Address and Data                                      |

|           |     | 21-24,     |             |          |                                                                       |

|           |     | 27-30,     |             |          |                                                                       |

|           |     | 33-36,     |             |          |                                                                       |

|           |     | 39-42,     |             |          |                                                                       |

|           |     | 86-91,     |             |          |                                                                       |

|           |     | 93, 94,    |             |          |                                                                       |

|           |     | 98, 99     |             |          |                                                                       |

| CBE0-CBE3 | I   | 9, 20,     | -           | 5/3.3    | Command/Byte Enables are multiplexed Bus Commands & Byte              |

|           |     | 32, 95     |             |          | enables.                                                              |

| FRAME     | I/O | 10         | PCI/Cardbus | 5/3.3    | Cycle Frame is asserted by the initiator to indicate the cycle        |

|           |     |            |             |          | beginning and is kept asserted during the burst cycle.                |

|           |     |            |             |          | If Cardbus mode (CARD_ON = 1), this pin is should be pulled up to     |

|           |     |            |             |          | V <sub>DD</sub> .                                                     |

| TRDY      | I/O | 13         | PCI/Cardbus | 5/3.3    | Target Ready indicates that the current data phase of the             |

|           |     |            |             |          | transaction is ready to be completed.                                 |

| IRDY      | I/O | 12         | PCI/Cardbus | 5/3.3    | Initiator Ready indicates that the current bus master is ready to     |

|           |     |            |             |          | complete the current data phase. During a write, its assertion        |

|           |     |            |             |          | indicates that the initiator is driving valid data onto the data bus. |

|           |     |            |             |          | During a read, its assertion indicates that the initiator is ready to |

|           |     |            |             |          | accept data from the currently-addressed target.                      |

| REQ       | 0   | 84         | PCI/Cardbus | 5/3.3    | Bus_master Request indicates to the bus arbiter that this device      |

|           |     |            |             |          | wants to become a bus master.                                         |

| GNT       | I   | 83         | -           | 5/3.3    | Bus_master Grant indicates to this device that access to the bus      |

|           |     |            |             |          | has been granted.                                                     |

| IDSEL     | I   | 96         | -           | 5/3.3    | ID Select when actively driven, indicates that the IUHC is chip-      |

|           |     |            |             |          | selected for configuration read/write transaction during the phase of |

|           |     |            |             |          | device initialization.                                                |

|           |     |            |             |          | If Cardbus mode (CARD_ON = 1), this pin is should be pulled up to     |

|           |     |            |             |          | V <sub>DD</sub> .                                                     |

| DEVSEL    | I/O | 14         | PCI/Cardbus | 5/3.3    | Device Select when actively driven, indicates that the driving device |

|           |     |            |             |          | has decoded its address as the target of the current access.          |

| STOP      | I/O | 15         | PCI/Cardbus | 5/3.3    | PCI Stop when actively driven, indicates that the target is           |

|           |     |            |             |          | requesting the current bus master to stop the transaction.            |

8

(2/2)

| Name   | I/O | Pin No. | Іоь         | Volts(V) | Function                                                                                                                                                                                                                                                         |

|--------|-----|---------|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PME    | 0   | 79      | PCI/Cardbus | 5/3.3    | PME Output for power management enable.                                                                                                                                                                                                                          |

|        |     |         |             |          | Caution The PME pin is not an N-channel open drain structure pin.  Therefore, when using S3, S4, S5 state in ACPI, a circuit that can separate between the power supply and the PME pin externally is needed.  ACPI: Advanced Configuration and Power Interface. |

|        |     |         |             |          | Please refer to ACPI Specification.                                                                                                                                                                                                                              |

| CLKRUN | I/O | 78      | PCI/Cardbus | 5/3.3    | PCICLK Running as input, to determine the status of PCLK; as                                                                                                                                                                                                     |

|        |     |         |             |          | output, to request starting or speeding up clock.                                                                                                                                                                                                                |

| ĪNTA   | 0   | 80      | PCI/Cardbus | 5/3.3    | Interrupt the PCI interrupt request A.                                                                                                                                                                                                                           |

| PERR   | I/O | 16      | PCI/Cardbus | 5/3.3    | Parity Error is used for reporting data parity errors during all PCI transactions, except a Special Cycle. It is an output when AD0-                                                                                                                             |

|        |     |         |             |          | AD31 and PAR are both inputs. It is an input when AD0-AD31 and                                                                                                                                                                                                   |

|        |     |         |             |          | PAR are both outputs.                                                                                                                                                                                                                                            |

| SERR   | 0   | 17      | PCI/Cardbus | 5/3.3    | System Error is used for reporting address parity errors, data parity                                                                                                                                                                                            |

|        |     |         |             |          | errors during the Special Cycle, or any other system error where the                                                                                                                                                                                             |

|        |     |         |             |          | effect can be catastrophic. When reporting address parity errors, it                                                                                                                                                                                             |

|        |     |         |             |          | is an output.                                                                                                                                                                                                                                                    |

| PRST   | I   | 81      | -           | 5/3.3    | Reset PCI reset                                                                                                                                                                                                                                                  |

| PCLK   | I   | 82      | -           | 5/3.3    | PCI Clock 33 MHz system bus clock.                                                                                                                                                                                                                               |

## 1.2 PCI/Cardbus Select Signals: (2 pins)

| Name    | I/O | Pin No. | Іоь | Volts(V) |                 |             | Functio | n       |

|---------|-----|---------|-----|----------|-----------------|-------------|---------|---------|

| CARD_ON | I   | 54      | -   | 3.3      | PCI/Card Select | (1:Cardbus, | 0:PCI b | us)     |

| CIS_ON  | I   | 45      | -   | 3.3      | CIS Register ON |             |         |         |

|         |     |         |     |          | _ CARD_ON       | CIS_ON      | CIS     | PME     |

|         |     |         |     |          | 0               | 1           | off     | PME     |

|         |     |         |     |          | 0               | 0           | on      | CSTSCHG |

| ı       |     |         |     |          | 1               | Χ           | on      | CSTSCHG |

## 1.3 PHY/Link Interface Signals: (15 pins)

| Name      | I/O | Pin No. | Іоь | Volts(V) | Function                                                        |

|-----------|-----|---------|-----|----------|-----------------------------------------------------------------|

| D0-D7     | I/O | 59-62,  | 9mA | 3.3      | PHY/Link Bi-directional Data (ISO-barrier supported)            |

|           |     | 64-67   |     |          |                                                                 |

| CTL0,CTL1 | I/O | 69, 70  | 9mA | 3.3      | PHY/Link Bi-directional Control (ISO-barrier supported)         |

| LREQ      | 0   | 73      | 9mA | 3.3      | PHY/Link Request (ISO-barrier supported)                        |

| LINKON    | Ι   | 77      | -   | 3.3      | Link-On Request (ISO-barrier supported)                         |

| LPS       | 0   | 74      | 9mA | 3.3      | Link Power Status (ISO-barrier supported)                       |

| SCLK      | I   | 72      | -   | 3.3      | PHY Clock 49.152 MHz (ISO-barrier supported)                    |

| DIRECT    |     | 68      | -   | 3.3      | Auxiliary PHY/Link Signal is used to determine whether the      |

|           |     |         |     |          | interconnection between Link and PHY has isolation ('low': ISO- |

|           |     |         |     |          | barrier; 'high': no ISO-barrier).                               |

## 1.4 Serial ROM Interface Signals: (3 pins)

| Name     | I/O | Pin No. | Іоь | Volts(V) | Function                                                     |

|----------|-----|---------|-----|----------|--------------------------------------------------------------|

| GROM_SDA | I/O | 55      | 6mA | 3.3      | Serial EEPROM Data Input / Output                            |

| GROM_SCL | 0   | 56      | 6mA | 3.3      | Serial EEPROM Clock Output                                   |

| GROM_EN  | ı   | 57      | -   | 3.3      | Serial EEPROM Enable ('high': GUID Load enabled; 'low': GUID |

|          |     |         |     |          | Load disabled)                                               |

## 1.5 Miscellaneous Signal: (1 pin)

| Name   | I/O | Pin No. | lol | Volts(V) | Function                        |

|--------|-----|---------|-----|----------|---------------------------------|

| PIN_EN | I   | 43      | -   | 5/3.3    | Pin Enable Input (High clamped) |

## 1.6 IC: (3 pins)

| Name  | I/O | Pin No. | loL | Volts(V) | Function                            |

|-------|-----|---------|-----|----------|-------------------------------------|

| IC(H) | I   | 44      | -   | 3.3      | Internally Connected (High clamped) |

| IC(L) | I   | 46, 47  | -   | 3.3      | Internally Connected (Low clamped)  |

## 1.7 NC: (5 pins)

| Name | I/O | Pin No. | lol | Volts(V) | Function                |

|------|-----|---------|-----|----------|-------------------------|

| NC   | -   | 48, 49, | -   | -        | Non- Connection (Open)  |

|      |     | 52, 53, |     |          | Leave them unconnected. |

|      |     | 58      |     |          |                         |

### 1.8 V<sub>DD</sub>: (8 pins)

$V_{\text{DD}}$  (5 V PCI or 3.3 V PCI) for PCI I/Os: 11, 37, 92  $V_{\text{DD}}$  3 V for digital core & PHY/Link I/Os: 1, 25, 51, 75, 97

### 1.9 Vss: (11 pins)

Vss: 6, 19, 26, 31, 38, 50, 63, 71, 76, 85, 100

# 2. REGISTER DESCRIPTIONS

## 2.1 PCI Bus Mode Configuration Register ( CARD\_ON=Low )

| 31 24          | 23 16             | 15 08               | 07                 | 00 |  |  |  |  |  |

|----------------|-------------------|---------------------|--------------------|----|--|--|--|--|--|

| Dev            | viceID            | VendorID            |                    |    |  |  |  |  |  |

| St             | atus              | Com                 | mand               |    |  |  |  |  |  |

|                | Class Code        | Revision ID         |                    |    |  |  |  |  |  |

| BIST           | Header Type       | Latency Timer       | Cache Line Size    |    |  |  |  |  |  |

|                | Base Address 0    | (OHCI Registers)    |                    |    |  |  |  |  |  |

| Base Address 1 |                   |                     |                    |    |  |  |  |  |  |

|                | Base Ad           | ddress 2            |                    |    |  |  |  |  |  |

|                | Base Ad           | ddress 3            |                    |    |  |  |  |  |  |

|                | Base Ad           | ddress 4            |                    |    |  |  |  |  |  |

|                | Base Ad           | ddress 5            |                    |    |  |  |  |  |  |

|                | CardBus C         | CIS Pointer         |                    |    |  |  |  |  |  |

| Subsy          | rstem ID          | <u> </u>            | Nendor ID          |    |  |  |  |  |  |

|                | Expansion Rom Bas | se Address Register | ı                  |    |  |  |  |  |  |

|                | H000000           |                     | Cap_Ptr            |    |  |  |  |  |  |

|                | 00000             | 0000H               |                    |    |  |  |  |  |  |

| Max_Lat        | Min_Gnt           | Interrupt Pin       | Interrupt Line     |    |  |  |  |  |  |

|                | PCI_OHO           | CI_Control          |                    |    |  |  |  |  |  |

|                | 00000             |                     |                    |    |  |  |  |  |  |

|                | 00000             |                     |                    |    |  |  |  |  |  |

|                | 00000             |                     |                    |    |  |  |  |  |  |

|                | Diagnostic        | c register0         |                    |    |  |  |  |  |  |

|                | Diagnostic        | c register1         |                    |    |  |  |  |  |  |

|                |                   | c register2         |                    |    |  |  |  |  |  |

|                |                   | c register3         |                    | _  |  |  |  |  |  |

|                | ment Capabilities | Next_Item_Ptr       | Cap_ID             | 4  |  |  |  |  |  |

| Data           | PMCSR_BSE         |                     | ent Control/Status | _  |  |  |  |  |  |

|                |                   | 0000H               |                    |    |  |  |  |  |  |

|                |                   | 0000H               |                    |    |  |  |  |  |  |

|                | ·                 | ERAL_RegisterA)     |                    | _  |  |  |  |  |  |

|                |                   | ERAL_RegisterB)     |                    | 4  |  |  |  |  |  |

|                |                   | ERAL_RegisterC)     |                    |    |  |  |  |  |  |

|                |                   | ERAL_RegisterD)     |                    |    |  |  |  |  |  |

|                | 00000             | 0000H               |                    |    |  |  |  |  |  |

### 2.1.1 Offset\_00 VendorID Register

This register identifies the manufacturer of the  $\mu$ PD72862. The ID is assigned by the PCI\_SIG committee.

| Bits | R/W | Description              |

|------|-----|--------------------------|

| 15-0 | R   | Constant value of 1033H. |

## 2.1.2 Offset\_02 DeviceID Register

This register identifies the type of the device for the  $\mu$ PD72862. The ID is assigned by NEC Corporation.

| Bits | R/W | Description              |

|------|-----|--------------------------|

| 15-0 | R   | Constant value of 0063H. |

### 2.1.3 Offset\_04 Command Register

The register provides control over the device's ability to generate and respond to PCI cycles.

| Bits  | R/W | Description                                                                                                             |

|-------|-----|-------------------------------------------------------------------------------------------------------------------------|

| 0     | R   | <b>I/O enable</b> Constant value of 0. The $\mu$ PD72862 does not respond to PCI I/O accesses.                          |

| 1     | R/W | <b>Memory enable</b> Default value of 1. It defines if the $\mu$ PD72862 responds to PCI memory                         |

|       |     | accesses. This bit should be set to one upon power-up reset.                                                            |

|       |     | 0: The $\mu$ PD72862 does not respond to PCI memory cycles                                                              |

|       |     | 1: The μPD72862 responds to PCI memory cycles                                                                           |

| 2     | R/W | <b>Master enable</b> Default value of 1. It enables the $\mu$ PD72862 as bus-master on the PCI-bus.                     |

|       |     | 0: The μPD72862 cannot generate PCI accesses by being a bus-master                                                      |

|       |     | 1: The $\mu$ PD72862 is capable of acting as a bus-master                                                               |

| 3     | R   | Special cycle monitor enable Constant value of 0. The special cycle monitor is always                                   |

|       |     | disabled.                                                                                                               |

| 4     | R/W | Memory write and invalidate enable Default value of 0. It enables Memory Write and Invalid                              |

|       |     | Command generation.                                                                                                     |

|       |     | 0: Memory write must be used                                                                                            |

|       |     | 1: The $\mu$ PD72862, when acts as PCI master, can generate the command                                                 |

| 5     | R   | VGA color palette invalidate enable Constant value of 0. VGA color palette invalidate is                                |

|       |     | always disabled.                                                                                                        |

| 6     | R/W | <b>Parity error response</b> Default value of 0. It defines if the $\mu$ PD72862 responds to $\overline{\text{PERR}}$ . |

|       |     | 0: Ignore parity error                                                                                                  |

|       |     | 1: Respond to parity error                                                                                              |

| 7     | R   | Stepping enable Constant value of 0. Stepping is always disabled.                                                       |

| 8     | R/W | <b>System error enable</b> Default value of 0. It defines if the $\mu$ PD72862 responds to SERR.                        |

|       |     | 0: Disable system error checking                                                                                        |

|       |     | 1: Enable system error checking                                                                                         |

| 9     | R   | Fast back-to-back enable Constant value of 0. Fast back-to-back transactions are only                                   |

|       |     | allowed to the same agent.                                                                                              |

| 15-10 | R   | Reserved Constant value of 000000.                                                                                      |

## 2.1.4 Offset\_06 Status Register

This register tracks the status information of PCI-bus related events which are relevant to the  $\mu$ PD72862. "Read" and "Write" are handled somewhat differently.

| Bits | R/W | Description                                                                                      |

|------|-----|--------------------------------------------------------------------------------------------------|

| 3-0  | R   | Reserved Constant value of 0000.                                                                 |

| 4    | R   | New capabilities Constant value of 1. It indicates the existence of the Capabilities List.       |

| 6,5  | R   | Reserved Constant value of 00.                                                                   |

| 7    | R   | Fast back-to-back capable Constant value of 1. It indicates that the $\mu$ PD72862, as a target, |

|      |     | cannot accept fast back-to-back transactions when the transactions are not to the same agent.    |

| 8    | R/W | Signaled parity error Default value of 0. It indicates the occurrence of any "Data Parity".      |

|      |     | 0: No parity detected (default)                                                                  |

|      |     | 1: Parity detected                                                                               |

| 10,9 | R   | <b>DEVSEL timing</b> Constant value of 01. These bits define the decode timing for DEVSEL.       |

|      |     | 0: Fast (1 cycles)                                                                               |

|      |     | 1: Medium (2 cycles)                                                                             |

|      |     | 2: Slow (3 cycles)                                                                               |

|      |     | 3: undefined                                                                                     |

| 11   | R/W | Signaled target abort Default value of 0. This bit is set by a target device whenever it         |

|      |     | terminates a transaction with "Target Abort".                                                    |

|      |     | 0: The $\mu$ PD72862 did not terminate a transaction with Target Abort                           |

|      |     | 1: The $\mu$ PD72862 has terminated a transaction with Target Abort                              |

| 12   | R/W | Received target abort Default value of 0. This bit is set by a master device whenever its        |

|      |     | transaction is terminated with a "Target Abort".                                                 |

|      |     | 0: The $\mu$ PD72862 has not received a Target Abort                                             |

|      |     | 1: The $\mu$ PD72862 has received a Target Abort from a bus-master                               |

| 13   | R/W | Received master abort Default value of 0. This bit is set by a master device whenever its        |

|      |     | transaction is terminated with "Master Abort". The $\mu$ PD72862 asserts "Master Abort" when a   |

|      |     | transaction response exceeds the time allocated in the latency timer field.                      |

|      |     | 0: Transaction was not terminated with a Master Abort                                            |

|      |     | 1: Transaction has been terminated with a Master Abort                                           |

| 14   | R/W | Signaled system error Default value of 0. It indicates that the assertion of SERR by the         |

|      |     | μPD72862.                                                                                        |

|      |     | 0: System error was not signaled                                                                 |

|      |     | 1: System error was signaled                                                                     |

| 15   | R/W | Received parity error Default value of 0. It indicates the occurrence of any PERR.               |

|      |     | 0: No parity error was detected                                                                  |

|      |     | 1: Parity error was detected                                                                     |

## 2.1.5 Offset\_08 Revision ID Register

This register specifies a revision number assigned by NEC Corporation for the  $\mu$ PD72862.

| Bits | R/W | Description                                                                                    |

|------|-----|------------------------------------------------------------------------------------------------|

| 7-0  | R   | Default value of 02H. It specifies the silicon revision. It will be incremented for subsequent |

|      |     | silicon revisions.                                                                             |

### 2.1.6 Offset\_09 Class Code Register

This register identifies the class code, sub-class code, and programming interface of the  $\mu$ PD72862.

| Bits  | R/W | Description                                                                        |

|-------|-----|------------------------------------------------------------------------------------|

| 7-0   | R   | Constant value of 10H. It specifies an IEEE1394 OpenHCI-compliant Host Controller. |

| 15-8  | R   | Constant value of 00H. It specifies an "IEEE1394" type.                            |

| 23-16 | R   | Constant value of 0CH. It specifies a "Serial Bus Controller".                     |

### 2.1.7 Offset\_0C Cache Line Size Register

This register specifies the system cache line size, which is PC-host system dependent, in units of 32-bit words. The following cache line sizes are supported: 2, 4, 8, 16, 32, 64, and 128. All other values will be recognized as 0, i.e. cache disabled.

| Bits | R/W | Description           |

|------|-----|-----------------------|

| 7-0  | R/W | Default value of 00H. |

## 2.1.8 Offset\_0D Latency Timer Register

This register defines the maximum amount of time that the  $\mu$ PD72862 is permitted to retain ownership of the bus after it has acquired bus ownership and initiated a subsequent transaction.

| Bits | R/W | Description                                                                                     |

|------|-----|-------------------------------------------------------------------------------------------------|

| 7-0  | R/W | Default value of 00H. It specifies the number of PCI-bus clocks that the $\mu$ PD72862 may hold |

|      |     | the PCI bus as a bus-master.                                                                    |

### 2.1.9 Offset\_0E Header Type Register

| Bits | R/W | Description                                                   |

|------|-----|---------------------------------------------------------------|

| 7-0  | R   | Constant value of 00H. It specifies a single function device. |

### 2.1.10 Offset\_0F BIST Register

| Bits | R/W | Description                                                                              |

|------|-----|------------------------------------------------------------------------------------------|

| 7-0  | R   | Constant value of 00H. It specifies whether the device is capable of Built-in Self Test. |

### 2.1.11 Offset\_10 Base Address 0 Register

This register specifies the base memory address for accessing all the "Operation registers" (i.e. control, configuration, and status registers) of the  $\mu$ PD72862, while the BIOS is expected to set this value during power-up reset.

| Bits  | R/W | Description                                         |

|-------|-----|-----------------------------------------------------|

| 11-0  | R   | Constant value of 000H. These bits are "read-only". |

| 31-12 | R/W | -                                                   |

### 2.1.12 Offset\_2C Subsystem Vendor ID Register

This register identifies the subsystem that contains the NEC's  $\mu$ PD72862 function. While the ID is assigned by the PCI\_SIG committee, the value should be loaded into the register from the external serial EEPROM after power-up reset. Access to this register through PCI-bus is prohibited.

| Bits | R/W | Description             |

|------|-----|-------------------------|

| 15-0 | R   | Default value of 1033H. |

### 2.1.13 Offset\_2E Subsystem ID Register

This register identifies the type of the subsystem that contains the NEC's  $\mu$ PD72862 function. While the ID is assigned by the manufacturer, the value should be loaded into the register from the external serial EEPROM after power-up reset. Access to this register through PCI-bus is prohibited.

| Bits | R/W | Description             |

|------|-----|-------------------------|

| 15-0 | R   | Default value of 0063H. |

### 2.1.14 Offset\_30 Expansion Rom Base Address Register

This register is not supported by the current implementation of the  $\mu$ PD72862.

| Bits | R/W | Description                   |

|------|-----|-------------------------------|

| 31-0 | R   | Reserved Constant value of 0. |

### 2.1.15 Offset\_34 Cap\_Ptr Register

This register points to a linked list of additional capabilities specific to the  $\mu$ PD72862, the NEC's implementation of the 1394 OpenHCI specification.

| Bits | R/W | Description                                                                                      |  |

|------|-----|--------------------------------------------------------------------------------------------------|--|

| 7-0  | R   | Constant value of 60H. The value represents an offset into the $\mu$ PD72862's PCI Configuration |  |

|      |     | Space for the location of the first item in the New Capabilities Linked List.                    |  |

### 2.1.16 Offset\_3C Interrupt Line Register

This register provides the interrupt line routing information specific to the  $\mu$ PD72862, the NEC's implementation of the 1394 OpenHCI specification.

| Bits | R/W | Description                                                                                |  |

|------|-----|--------------------------------------------------------------------------------------------|--|

| 7-0  | R/W | Default value of 00H. It specifies which input of the host system interrupt controller the |  |

|      |     | nterrupt pin of the $\mu$ PD72862 is connected to.                                         |  |

### 2.1.17 Offset\_3D Interrupt Pin Register

This register provides the interrupt line routing information specific to the  $\mu$ PD72862, the NEC's implementation of the 1394 OpenHCI specification.

| Bits | R/W | Description                                                                            |  |

|------|-----|----------------------------------------------------------------------------------------|--|

| 7-0  | R   | Constant value of 01H. It specifies PCI INTA is used for interrupting the host system. |  |

### 2.1.18 Offset\_3E Min\_Grant Register

This register specifies how long of a burst period the  $\mu$ PD72862 needs, assuming a clock rate of 33MHz. Resolution is in units of  $\frac{1}{4}$   $\mu$ s. The value should be loaded into the register from the external serial EEPROM upon power-up reset, and access to this register through PCI-bus is prohibited.

| Bits | R/W | Description                                                                                 |  |

|------|-----|---------------------------------------------------------------------------------------------|--|

| 7-0  | R   | Default value of 00H. Its value contributes to the desired setting for Latency Timer value. |  |

### 2.1.19 Offset\_3F Max Lat Register

This register specifies how often the  $\mu$ PD72862 needs to gain access to the PCI-bus, assuming a clock rate of 33MHz. Resolution is in units of  $\frac{1}{4}$   $\mu$ s. The value should be loaded into the register from the external serial EEPROM after hardware reset, and access to this register through PCI-bus is prohibited.

| Bits | R/W | Description                                                                                 |  |

|------|-----|---------------------------------------------------------------------------------------------|--|

| 7-0  | R   | Default value of 00H. Its value contributes to the desired setting for Latency Timer value. |  |

### 2.1.20 Offset\_40 PCI\_OHCI\_Control Register

This register specifies the control bits that are IEEE1394 OpenHCl specific. Vendor options are not allowed in this register. It is reserved for OpenHCl use only.

| Bits | R/W                                                                                                                                                                                  | Description                                                                                    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 0    | R/W                                                                                                                                                                                  | PCI global SWAP Default value of 0. When this bit is 1, all quadrates read from and written to |

|      | the PCI Interface are byte swapped, thus a "PCI Global Swap". PCI addresses for expansion ROM and PCI Configuration registers, are, however, unaffected by this bit. This bit is not |                                                                                                |

|      |                                                                                                                                                                                      | ROM and PCI Configuration registers, are, however, unaffected by this bit. This bit is not     |

|      |                                                                                                                                                                                      | required for motherboard implementations.                                                      |

| 31-1 | R                                                                                                                                                                                    | Reserved Constant value of all 0.                                                              |

### 2.1.21 Offset\_60 Cap\_ID & Next\_Item\_Ptr Register

The Cap\_ID signals that this item in the Linked List is the registers defined for PCI Power Management, while the Next\_Item\_Ptr describes the location of the next item in the  $\mu$ PD72862's Capability List.

| Bits | R/W | Description                                                                                    |  |

|------|-----|------------------------------------------------------------------------------------------------|--|

|      |     | Cap_ID Constant value of 01H. The default value identified the Link List item as being the PCI |  |

|      |     | Power Management registers, while the ID value is assigned by the PCI SIG.                     |  |

| 15-8 | R   | Next_Item_Ptr Constant value of 00H. It indicated that there are no more items in the Link     |  |

|      |     | List.                                                                                          |  |

## 2.1.22 Offset\_62 Power Management Capabilities Register

This is a 16-bit read-only register that provides information on the power management capabilities of the  $\mu$ PD72862.

| Bits  | R/W | Description                                                                                 |  |

|-------|-----|---------------------------------------------------------------------------------------------|--|

| 2-0   | R   | version Constant value of 001. The power management registers are implemented as defined    |  |

|       |     | in revision 1.0 of PCI Bus Power Management Interface Specification.                        |  |

| 3     | R   | PME clock Constant value of 0.                                                              |  |

| 4     | R   | Auxiliary power source Constant value of 0. The alternative power source is not supported.  |  |

| 5     | R   | DIS Constant value of 0.                                                                    |  |

| 8,6   | R   | Reserved Constant value of 000.                                                             |  |

| 9     | R   | <b>D1_support</b> Constant value of 0. The μPD72862 does not support the D1 Power           |  |

|       |     | Management state.                                                                           |  |

| 10    | R   | <b>D2_support</b> Constant value of 1. The μPD72862 supports the D2 Power Management state. |  |

| 15-11 | R   | PME_support Constant value of 01100.                                                        |  |

### 2.1.23 Offset\_64 Power Management Control/Status Register

This is a 16-bit read-only register that provides control status information of the  $\mu$ PD72862.

| Bits                                                                                | R/W                                                                                      | Description                                                                                    |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| 1,0                                                                                 | R/W                                                                                      | PowerState Default value is undefined. This field is used both to determine the current power  |  |

|                                                                                     |                                                                                          | state of the $\mu$ PD72862 and to set the $\mu$ PD72862 into a new power state. As D1 is not   |  |

|                                                                                     |                                                                                          | supported in the current implementation of the $\mu$ PD72862, writing of '01' will be ignored. |  |

|                                                                                     |                                                                                          | 00: D0 (DMA contexts: ON, Link Layer: ON)                                                      |  |

|                                                                                     |                                                                                          | 01: Reserved (D1 state not supported)                                                          |  |

|                                                                                     |                                                                                          | 10: D2 (DMA contexts: OFF, Link Layer: OFF, LPS: OFF, PME will be asserted upon                |  |

|                                                                                     |                                                                                          | LinkON being active)                                                                           |  |

|                                                                                     |                                                                                          | 11: D3 (DMA contexts: OFF, Link Layer: OFF, LPS: OFF, PME will be asserted upon                |  |

|                                                                                     |                                                                                          | LinkON being active, Power can be removed)                                                     |  |

| 7-2                                                                                 | R                                                                                        | Reserved Constant value of 000000.                                                             |  |

| 8                                                                                   | R/W PME_En Default value of 0. This field is used to enable the specific power managemen |                                                                                                |  |

|                                                                                     |                                                                                          | features of the $\mu$ PD72862.                                                                 |  |

| 12-9                                                                                | R                                                                                        | Data_Select Constant value of 0000.                                                            |  |

| 14,13                                                                               | R                                                                                        | Data_Scale Constant value of 00.                                                               |  |

| 15 R/W PME_Status Default value is undefined. A write of '1' clears this bit, while |                                                                                          | PME_Status Default value is undefined. A write of '1' clears this bit, while a write of '0' is |  |

|                                                                                     |                                                                                          | ignored.                                                                                       |  |

# 2.2 CardBus Mode Configuration Register ( CARD\_ON=High )

| 1 24                          | 23 16                | 15 08                 | 07 0               |  |

|-------------------------------|----------------------|-----------------------|--------------------|--|

| De                            | viceID               | Ven                   | dorlD              |  |

| S                             | tatus                | Command               |                    |  |

|                               | Class Code           |                       | Revision ID        |  |

| BIST                          | Header Type          | Latency Timer         | Cache Line Size    |  |

|                               | Base Address 0       | (OHCI Registers)      |                    |  |

|                               | Base Address 1 (Care | dBus Status Reg) Note |                    |  |

|                               | Base Address 2 (Card | dBus Status Reg) Note |                    |  |

|                               | Base Ad              | ddress 3              |                    |  |

|                               | Base Ad              | ddress 4              |                    |  |

|                               | Base Ad              | ddress 5              |                    |  |

|                               | CardBus CIS          | S Pointer Note        |                    |  |

| Subs                          | ystem ID             | Subsystem             | n Vendor ID        |  |

|                               | Expansion Rom Bas    | se Address Register   | <del>,</del>       |  |

| 000000H Ca                    |                      |                       |                    |  |

|                               | 00000                | 0000H                 | <del>,</del>       |  |

| Max_Lat                       | Min_Gnt              | Interrupt Pin         | Interrupt Line     |  |

|                               | PCI_OHO              | CI_Control            |                    |  |

|                               | 00000                | 0000H                 |                    |  |

|                               | 00000                | 0000H                 |                    |  |

|                               | 00000                | 0000H                 |                    |  |

|                               | Diagnostic           | c register0           |                    |  |

|                               | Diagnostic           | c register1           |                    |  |

|                               | Diagnostic           | c register2           |                    |  |

|                               | Diagnostic           | c register3           | T                  |  |

| Power Manage                  | ement Capabilities   | Next_Item_Ptr         | Cap_ID             |  |

| Data                          | PMCSR_BSE            | Power Managem         | ent Control/Status |  |

|                               | 00000                | 0000H                 |                    |  |

|                               | 00000                | 0000H                 |                    |  |

| User Area (GENERAL_RegisterA) |                      |                       |                    |  |

| User Area (GENERAL_RegisterB) |                      |                       |                    |  |

|                               | User Area (GENE      | ERAL_RegisterC)       |                    |  |

|                               | User Area (GEN       | ERAL_RegisterD)       |                    |  |

|                               | CIS Ar               | ea Note               |                    |  |

Note Different from PCI Bus Mode Configuration Register.

# 2.2.1 Offset\_14/18 Base\_Address\_1/2 Register (CardBus Status Registers)

| Bits | R/W | Description           |  |  |  |  |

|------|-----|-----------------------|--|--|--|--|

| 7-0  | R   | Constant value of 00. |  |  |  |  |

| 31-8 | R/W | -                     |  |  |  |  |

## (1) Function Event Register (FER) ( Base Address 1 ( 2 )+ 0H )

| Bits  | R/W | Description                        |  |  |  |

|-------|-----|------------------------------------|--|--|--|

| 0     | R   | Write Protect (No Use).            |  |  |  |

|       |     | Read only as '0'                   |  |  |  |

| 1     | R   | Ready Status (No Use).             |  |  |  |

|       |     | Read only as '0'                   |  |  |  |

| 2     | R   | Battery Voltage Detect 2 (No Use). |  |  |  |

|       |     | Read only as '0'                   |  |  |  |

| 3     | R   | Battery Voltage Detect 1 (No Use). |  |  |  |

|       |     | Read only as '0'                   |  |  |  |

| 4     | R/W | General Wakeup                     |  |  |  |

| 14-5  | R   | Reserved. Read only as '0'         |  |  |  |

| 15    | R/W | nterrupt                           |  |  |  |

| 31-16 | R   | Reserved. Read only as '0'         |  |  |  |

## (2) Function Event Mask Register (FEMR) ( Base Address 1 ( 2 )+ 4H )

| Bits  | R/W | Description                        |  |  |

|-------|-----|------------------------------------|--|--|

| 0     | R   | Write Protect (No Use).            |  |  |

|       |     | Read only as '0'                   |  |  |

| 1     | R   | Ready Status (No Use).             |  |  |

|       |     | Read only as '0'                   |  |  |

| 2     | R   | Battery Voltage Detect 2 (No Use). |  |  |

|       |     | Read only as '0'                   |  |  |

| 3     | R   | Battery Voltage Detect 1 (No Use). |  |  |

|       |     | Read only as '0'                   |  |  |

| 4     | R/W | General Wakeup Mask                |  |  |

| 5     | R   | BAM. Read only as '0'              |  |  |

| 6     | R   | PWM. Read only as '0'              |  |  |

| 13-7  | R   | Reserved. Read only as '0'         |  |  |

| 14    | R/W | Vakeup Mask                        |  |  |

| 15    | R/W | Interrupt                          |  |  |

| 31-16 | R   | Reserved. Read only as '0'         |  |  |

## (3) Function Reset Status Register (FRSR) (Base Address 1 (2)+8H)

| Bits  | R/W | Description                        |  |  |  |

|-------|-----|------------------------------------|--|--|--|

| 0     | R   | Write Protect (No Use).            |  |  |  |

|       |     | Read only as '0'                   |  |  |  |

| 1     | R   | Ready Status (No Use).             |  |  |  |

|       |     | Read only as '0'                   |  |  |  |

| 2     | R   | Battery Voltage Detect 2 (No Use). |  |  |  |

|       |     | Read only as '0'                   |  |  |  |

| 3     | R   | Battery Voltage Detect 1 (No Use). |  |  |  |

|       |     | Read only as '0'                   |  |  |  |

| 4     | R/W | General Wakeup Mask                |  |  |  |

| 14-5  | R   | Reserved. Read only as '0'         |  |  |  |

| 15    | R/W | nterrupt                           |  |  |  |

| 31-16 | R   | Reserved. Read only as '0'         |  |  |  |

## (4) Function Force Event Register (FFER) ( Base Address 1 ( 2 )+ CH )

| Bits  | R/W | Description                        |  |  |  |

|-------|-----|------------------------------------|--|--|--|

| 0     | R   | Write Protect (No Use).            |  |  |  |

|       |     | Read only as '0'                   |  |  |  |

| 1     | R   | Ready Status (No Use).             |  |  |  |

|       |     | Read only as '0'                   |  |  |  |

| 2     | R   | Battery Voltage Detect 2 (No Use). |  |  |  |

|       |     | Read only as '0'                   |  |  |  |

| 3     | R   | Battery Voltage Detect 1 (No Use). |  |  |  |

|       |     | Read only as '0'                   |  |  |  |

| 4     | R/W | General Wakeup Mask                |  |  |  |

| 14-5  | -   | No Use                             |  |  |  |

| 15    | R/W | Interrupt                          |  |  |  |

| 31-16 | R   | Reserved. Read only as '0'         |  |  |  |

### 2.2.2 Offset 28 Cardbus CIS Pointer

This register specifies start memory address of the Cardbus CIS Area.

| Bits | R/W | Description                   |  |  |  |

|------|-----|-------------------------------|--|--|--|

| 31-0 | R   | Starting Pointer of CIS Area. |  |  |  |

|      |     | Constant value of 00000080H.  |  |  |  |

### 2.2.3 Offset\_80 CIS Area

The  $\mu\text{PD72862}$  supports external Serial ROM(AT24C02 compatible) interface.

CIS Area Register can be loaded from external Serial ROM in the CIS area when CARD\_ON are HIGH.

| CARD_ON | CIS_ON | Bus     | CIS | FUNCTION |

|---------|--------|---------|-----|----------|

| 0       | 1      | PCI     | OFF | PME      |

| 0       | 0      | PCI     | ON  | CSTSCHG  |

| 1       | X      | Cardbus | ON  | CSTSCHG  |

### 3. SERIAL ROM INTERFACE

The  $\mu$ PD72862 provides a serial ROM interface to initialize the 1394 Global Unique ID Register and the PCI/Cardbus Mode Configuration registers from a serial EEPROM.

## 3.1 Serial EEPROM Register

| Register Address     | Register Name             | R/W |

|----------------------|---------------------------|-----|

| Base address + 0x930 | SUBID register            | R/W |

| Base address + 0x934 | LATVAL register           | R/W |

| Base address + 0x938 | W_GUIDHi register         | R/W |

| Base address + 0x93C | W_GUIDLo register         | R/W |

| Base address + 0x940 | Parameters Write register | R/W |

| Base address + 0x95C | W_GENERAL register        | R/W |

| Base address + 0x960 | W_PHYS register           | R/W |

| Base address + 0x984 | W_CIS register            | R/W |

Remark Base address: Base Address 0 in Configuration register

## 3.2 Serial EEPROM Register Description

### (1) SUBID register (Base address + 0x930)

| 31 16      | 3 15 0     |

|------------|------------|

| W_SUBSYSID | W_SUBVNDID |

| Field      | Bits  | R/W | Default value | Description                                                             |

|------------|-------|-----|---------------|-------------------------------------------------------------------------|

| W_SUBSYSID | 31-16 | R/W | 0063H         | Subsystem ID value. The value is loaded into Subsystem ID register in   |

|            |       |     |               | Configuration register (offset+2CH bit 31-16).                          |

| W_SUBVNDID | 15-0  | R/W | 1033H         | Subsystem Vendor ID value. The value is loaded into Subsystem Vendor ID |

|            |       |     |               | register in Configuration register (Offset+2CH bit 15-0).               |

### (2) LATVAL register (Base address + 0x934)

| 31 24    | 23 16    | 15 12 | 11 | 10 4  | 3 0       |

|----------|----------|-------|----|-------|-----------|

| W_MAXLAT | W_MINGNT | - 0 - | 1  | - 0 - | W_MAX_REC |

| Field     | Bits  | R/W | Default value | Description                                                                   |

|-----------|-------|-----|---------------|-------------------------------------------------------------------------------|

| W_MAXLAT  | 31-24 | R/W | 00H           | Max Latency value. The value is loaded into Max Latency register in           |

|           |       |     |               | Configuration register (Offset+3CH bit 31-24).                                |

| W_MINGNT  | 23-16 | R/W | 00H           | Min Grant value. The value is loaded into Min Grant register in Configuration |

|           |       |     |               | register (Offset+3CH bit 23-16).                                              |

| -         | 15-12 | 1   | -             | Reserved. Write 0 to these bits.                                              |

|           | 11    | -   | -             | Reserved. Write 1 to this bit.                                                |

|           | 10-4  | -   | -             | Reserved. Write 0 to these bits.                                              |

| W_MAX_REC | 3-0   | R/W | 9H            | MAXREC value. The value is loaded into the max_rec field of OHCI              |

|           |       |     |               | BusOption register in OHCI register (Offset+020H bit 15-12).                  |

## (3) W\_GUIDHi register (Base address + 0x938)

| 31 |          | 0 |

|----|----------|---|

|    | W_GUIDHi |   |

| Field    | Bits | R/W | Default value | Description                                                                   |  |

|----------|------|-----|---------------|-------------------------------------------------------------------------------|--|

| W_GUIDHi | 31-0 | R/W | Undefined     | GlobalUniqueIDHi value. The value is loaded into OHCI GlobalUniqueIDHi        |  |

|          |      |     |               | register in OHCI register (Offset+024H bit 31-0).                             |  |

|          |      |     |               | Please refer to the 1394 Open Host Controller Interface Specification/Release |  |

|          |      |     |               | 1.0 [5.5.5].                                                                  |  |

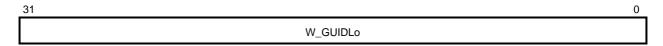

## (4) W\_GUIDLo register (Base address + 0x93C)

| Field    | Bits | R/W | Default value | Description                                                                   |  |

|----------|------|-----|---------------|-------------------------------------------------------------------------------|--|

| W_GUIDLo | 31-0 | R/W | Undefined     | GlobalUniqueIDLo value. The value is loaded into GlobalUniqueIDLo register    |  |

|          |      |     |               | in OHCI register (Offset+028H bit 31-0).                                      |  |

|          |      |     |               | Please refer to the 1394 Open Host Controller Interface Specification/Release |  |

|          |      |     |               | 1.0 [5.5.5].                                                                  |  |

## (5) Parameters Write register (Base address + 0x940)

| 31    | 7 | 6 4    | 3 | 1     | 0         |

|-------|---|--------|---|-------|-----------|

| - 0 - |   | PAGE_S |   | - 0 - | PAR<br>_W |

| Field  | Bits | R/W | Default value | Description                                                             |  |

|--------|------|-----|---------------|-------------------------------------------------------------------------|--|

| -      | 31-7 | -   | -             | Reserved. Write 0 to these bits.                                        |  |

| PAGE_S | 6-4  | R/W | 000           | Write register select page. The bit field returns zero when read.       |  |

|        |      |     |               | 000: Select SUBID register and LATVAL register.                         |  |

|        |      |     |               | 001: Select W_GUIDHi register and W_GUIDLo register.                    |  |

|        |      |     |               | 010: Select W_GENERAL register (W_GENERAL_0 and W_GENERAL_1).           |  |

|        |      |     |               | 011: Select W_GENERAL register (W_GENERAL_2 and W_GENERAL_3).           |  |

|        |      |     |               | 100: Select W_PHYS register (W_ programPhyEnable,                       |  |

|        |      |     |               | W_aPhyEnhanceEnable).                                                   |  |

|        |      |     |               | 101: Select W_CIS register (W_CIS_EVEN - W_CIS_ODD).                    |  |

| -      | 3-1  | -   | -             | Reserved. Write 0 to these bits.                                        |  |

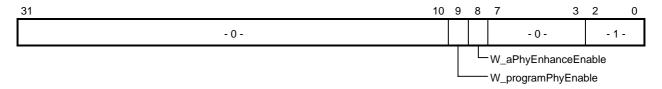

| PAR_W  | 0    | R/W | 0             | Write control signal. The bit field returns zeros when read.            |  |