# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# MOS INTEGRATED CIRCUIT $\mu$ PD703177(A) / $\mu$ PD703445(A)

# V850E/CG2<sup>TM</sup> CarGate-F / V850E/CG5<sup>TM</sup>CarGate-S 32-/16-BIT ROMLESS MICROCONTROLLER

#### **DESCRIPTION**

The V850E/CG2 ("CarGate-F") and V850E/CG5 ("CarGate-S") ROM-less microcontroller, are members of NEC's V850 32-bit RISC family, which match the performance gains attainable with RISC-based controllers to the needs of embedded control applications. The V850 CPU offers easy pipeline handling and programming, resulting in compact code size comparable to 16-bit CISC CPUs. The V850E/CG2 ("CarGate-F") and V850E/CG5 ("CarGate-S") are specially designed for the high performance requirements of sophisticated algorithms and calculations. They combine a powerful CPU-Core with a 32-bit wide external memory interface and iCache. The V850E/CG2 ("CarGate-F") has an additional hardware FPU. Furthermore, they offer an excellent combination of general purpose peripheral functions, like serial communication interfaces (UART, clocked SI) and measurement inputs (A/D converter), with dedicated CAN network support. Thus equipped, the V850E/CG2 ("CarGate-F") and V850E/CG5 ("CarGate-S") are ideally suited for automotive applications, like CAN Gateways. They are also an excellent choice for other applications where a combination of sophisticated peripheral functions and CAN network support is required.

#### **FEATURES**

- 32-bit RISC CPU with Harvard Architecture

- 8 K iCache (2-way associative)

- Full-CAN Interface: 5 channels

- Serial Interfaces: 5 channels

- 3-wire mode: 3 channels

- UART mode: 2 channels

- Timers: 2 channels

- 16-bit multi purpose timer/event counter: channels: 2 channels

- 10-bit resolution A/D Converter: 6 channels

- External Bus Interface (32- / 16- / 8-bit data / 24-bit address)

- I/O lines: max. 71

- 5 V tolerant: 13 ×

- Power supply voltage range:

- $+3.0 \text{ V} \le \text{V}_{DD3} \le +3.6 \text{ V}$

- Frequency range: up to 40 MHz

- Built-in low power saving mode

- · Built-in clock oscillator circuit with internal PLL

- Built-in clock oscillator circuit with internal spread spectrum PLL for CPU/ BCU clock operation

- Temperature range:

- -40 °C to +85 °C

- Package:

- 144 LQFP, 0.5 mm pin-pitch (20 × 20 mm)

#### **ORDERING INFORMATION**

| Device    | Part Number  | Package            | ROM      | RAM  | FCAN Option | Operating<br>Temperature (T <sub>A</sub> ) |

|-----------|--------------|--------------------|----------|------|-------------|--------------------------------------------|

| V850E/CG2 | μPD703177(A) | LQFP144 20 × 20 mm | ROM-less | 32 K | 5 Channels  | -40°C ~ +85°C                              |

| V850E/CG5 | μPD703445(A) | LQFP144 20 × 20 mm | ROM-less | 32 K | 5 Channels  | -40°C ~ +85°C                              |

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

## INTERNAL BLOCK DIAGRAM

Interrupt INTP0-9 Controller **CPU Core** PC FPU 8 kB TIC00, TIC01 Note 16-bit timer iCache barrel hardware TMC 0 shifter multiplier TOC0 system TIC10, TIC11 16-bit timer registers TMC 1 TOC1 Α L general 32 kB registers U FCRxD01 RAM bus FCAN 01 External interface FCTxD01◀ Memory FCRxD02 Controller FCAN 02 (MEMC) FCTxD02◀ FCRxD03 FCAN 03 FCTxD03◀ Bus control Unit (BCU) FCRxD11-FCAN 11 internal peripheral bus FCTxD11◀ FCRxD12 power supply FCAN 12 FCTxD12⁴ 10-bit A/D  $\rm V_{\rm DD}$ Ports 6 channels  $V_{\rm SS}$ RXD60 UART60 TXD60 ◀ BRG AV<sub>Ref</sub> AV<sub>SS</sub> ANIO to ANI5 RXD61 UART61 Bootstrap TXD61 ◀ Loader BRG  $\text{CV}_{\text{SS}}$ Oscillator and  $CV_{DD}$ SI00 clock generator BRG0 SO00 **←** CSI00 ► PCLKOUT with Spread SCK00 ◆ X1 X2 Spectrum PLL, SI01 PLL RESET CSI01 SO01 **◆** SCK01 ◀ MODE2 SI02 -System control MODE1 CSI02 BRG1 MODE0 SCK02 ◀

Figure IN-1: V850E/CG2 CarGate-F / V850E/CG5 CarGate-S Internal Block Diagram

Note: The Floating Point Unit is only available on V850E/CG2 ("CarGate-F")

## **PIN IDENTIFICATION**

| A0 to A23          | Address Bus                    | PCLKOUT                                                  | Peripheral Clock Output |

|--------------------|--------------------------------|----------------------------------------------------------|-------------------------|

| D0 to D31          | Data Bus                       | PCM0                                                     | Port CM0                |

| ANI0 to ANI5       | Analog Input                   | PCS0-PCS4, PCS6                                          | Port CS                 |

| $AV_{DD}$          | Analog Power Supply            | PCT0, PCT1,<br>PCT4, PCT5                                | Port CT                 |

| $AV_{REF}$         | Analog Reference Voltage       | PCD2 to PCD5                                             | Port CD                 |

| AV <sub>SS</sub>   | Analog Ground                  | PDH0 to PDH16                                            | Port DH                 |

| $CV_{DD}$          | Clock Generator Power Supply   | RXD60 to RXD61                                           | Receive Data Input      |

| CV <sub>SS</sub>   | Clock Generator Ground         | SCK00 to SCK02                                           | Serial Clock            |

| FCRXD01 to FCRXD03 | CAN Receive Line Input 0       | SI00 to SI02                                             | Serial Input            |

| FCTXD01 to FCTXD03 | CAN Transmit Line Output0      | SO00 to SO02                                             | Serial Output           |

| FCRXD11 to FCRXD12 | CAN Receive Line Input 1       | TIC00, TIC01,<br>TIC10, TIC11                            | Timer Input             |

| FCTXD11 to FCTXD12 | CAN Transmit Line Output1      | TOC0, TOC1                                               | Timer Output            |

| $GND_3$            | Ground for 3 V Power Supply    | TXD60 to TXD61                                           | Transmit Data Output    |

| INTP0 to INTP9     | External interrupt request     | $V_{DD3}$                                                | 3 V Power Supply        |

| MODE0 to MODE2     | Mode Inputs                    | RESET                                                    | Reset                   |

| NMI                | Non-Maskable Interrupt Request | WAIT                                                     | Wait                    |

| P10 to P17         | Port 1                         | $\overline{WRZ}$ , $\overline{WRZ0}$ , $\overline{WRZ1}$ | Write Enable            |

| P20 to P27         | Port 2                         | RDZ                                                      | Read                    |

| P30 to P37         | Port 3                         | CS0-CS4, CS6                                             | Chip Select             |

| P40 to P47         | Port 4                         | X1, X2                                                   | Crystal (Main-OSC)      |

| P70 to P75         | Port 7                         |                                                          |                         |

|                    |                                |                                                          |                         |

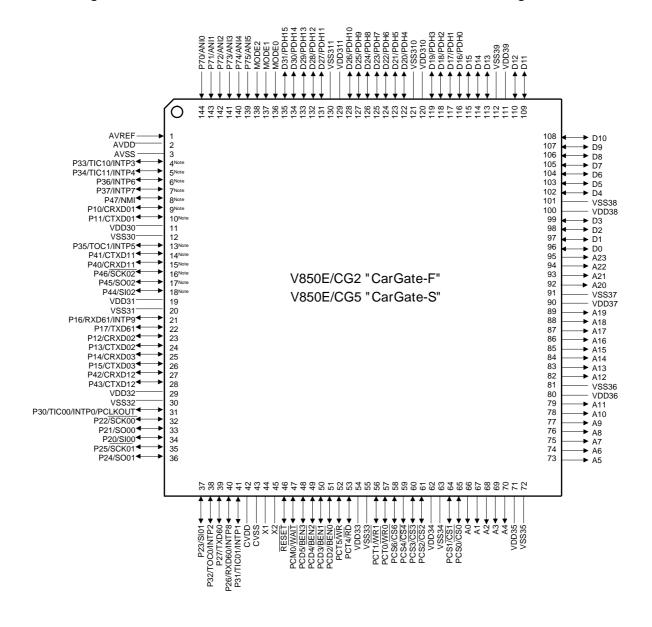

## PIN CONFIGURATION (Top View)

- 144 pin QFP (fine pitch) (20 × 20 × 1.4 mm)

- μPD703177(A)

- μPD703445(A)

Figure IN-2: V850E/CG2 CarGate-F / V850E/CG5 CarGate-S Pin Configuration

Note: Marked Pins are 5 V tolerant

# **Table of Contents**

|    |     | IN    | TERNAL BLOCK DIAGRAM                                      | 2   |

|----|-----|-------|-----------------------------------------------------------|-----|

|    |     | PII   | N IDENTIFICATION                                          | 3   |

|    |     | PII   | N CONFIGURATION (Top View)                                | 4   |

| 1. |     | Pir   | n Functions                                               | 9   |

|    | 1.1 |       | Pins                                                      |     |

|    | 1.2 |       | Port Pins                                                 |     |

|    | 1.3 |       | Circuits                                                  |     |

| _  |     | _     |                                                           | 4.0 |

| 2. |     | Pro   | ogramming External Flash Memory                           | 16  |

| 3. |     |       | ectrical Specifications                                   |     |

|    | 3.1 |       | olute Maximum Ratings                                     |     |

|    | 3.2 |       | eral Characteristics                                      |     |

|    |     | 3.2.1 | Oscillator recommendations (main system clock oscillator) |     |

|    |     | 3.2.2 | Oscillator characteristics                                |     |

|    |     | 3.2.3 | Peripheral PLL characteristics                            |     |

|    |     | 3.2.4 | Spread spectrum PLL characteristics                       |     |

|    |     | 3.2.5 | Capacitances                                              |     |

|    | 3.3 | •     | rating Conditions                                         |     |

|    |     | 3.3.1 | Peripheral clock                                          |     |

|    |     | 3.3.2 | CPU/BCU clock                                             |     |

|    | 3.4 |       | Characteristics                                           |     |

|    | 3.5 |       | Characteristics                                           |     |

|    |     | 3.5.1 | General                                                   |     |

|    |     | 3.5.2 | AC test load condition                                    |     |

|    |     | 3.5.3 | Clock timing                                              |     |

|    |     | 3.5.4 | External memory access read timing                        |     |

|    |     | 3.5.5 | External memory access write timing                       |     |

|    |     | 3.5.6 | RESET (power up/down sequence)                            |     |

|    |     | 3.5.7 | Interrupt timing                                          |     |

|    | 3.6 |       | pheral Function Characteristics                           |     |

|    |     | 3.6.1 | Timer C                                                   |     |

|    |     | 3.6.2 | CSI                                                       |     |

|    |     | 3.6.3 | UART6                                                     |     |

|    |     | 3.6.4 | FCAN                                                      |     |

|    |     | 3.6.5 | Serial flash programming operating characteristics        |     |

|    |     | 3.6.6 | A/D converter                                             | 36  |

| 4. |     | Pa    | ckage Drawing                                             | 37  |

| 5. |     | Re    | commended Soldering Conditions                            | 38  |

| 6. |     | Re    | evision History                                           | 39  |

# **List of Figures**

| Figure IN-1: | V850E/CG2 CarGate-F / V850E/CG5 CarGate-S Internal Block Diagram | 2  |

|--------------|------------------------------------------------------------------|----|

| Figure IN-2: | V850E/CG2 CarGate-F / V850E/CG5 CarGate-S Pin Configuration      |    |

| Figure 1-1:  | Input / Output Circuits (1/2)                                    | 14 |

| Figure 2-1:  | Programming Mode Selection Format                                | 16 |

| Figure 3-1:  | Main Oscillator Recommendations                                  | 18 |

| Figure 3-2:  | AC Test Input/Output Waveform SCHMITT                            | 24 |

| Figure 3-3:  | AC Test Input/Output Waveform CMOS                               | 24 |

| Figure 3-4:  | AC Test Load Condition                                           |    |

| Figure 3-5:  | Clock Timing                                                     | 25 |

| Figure 3-6:  | External Memory Access Read Timing                               | 27 |

| Figure 3-7:  | External Memory Access Write Timing                              | 29 |

| Figure 3-8:  | RESET Timing                                                     |    |

| Figure 3-9:  | Interrupt Timing                                                 | 31 |

| Figure 3-10: | Timer C Characteristics                                          |    |

| Figure 3-11: | CSI Slave Mode Characteristics                                   | 34 |

| Figure 3-12: | Serial Flash Programming Operating Characteristics               | 35 |

| Figure 4-1:  | Package Drawing                                                  |    |

|              |                                                                  |    |

# **List of Tables**

| Table 1-1:  | Pin Function                                                              | 9  |

|-------------|---------------------------------------------------------------------------|----|

| Table 1-2:  | Non-Port Pins                                                             | 11 |

| Table 3-1:  | Absolute Maximum Ratings (T <sub>A</sub> = 25°C, V <sub>SS3x</sub> = 0 V) | 17 |

| Table 3-2:  | Main Oscillator Characteristics                                           |    |

| Table 3-3:  | Peripheral PLL Characteristics                                            | 19 |

| Table 3-4:  | Spread Spectrum PLL Characteristics                                       | 19 |

| Table 3-5:  | Capacitances                                                              | 20 |

| Table 3-6:  | Peripheral Clock                                                          | 21 |

| Table 3-7:  | CPU/BCU Clock                                                             | 21 |

| Table 3-8:  | DC Characteristics Conditions                                             | 22 |

| Table 3-9:  | Power Supply Currents                                                     | 23 |

| Table 3-10: | Clock Timing                                                              | 25 |

| Table 3-11: | External Memory Access Read Timing                                        | 26 |

| Table 3-12: | External Memory Access Write Timing                                       | 28 |

| Table 3-13: | RESET Timing                                                              | 30 |

| Table 3-14: | Interrupt Timing                                                          | 31 |

| Table 3-15: | Timer C Characteristics                                                   | 32 |

| Table 3-16: | CSI Master Mode Characteristics                                           | 33 |

| Table 3-17: | CSI Slave Mode Characteristics                                            | 33 |

| Table 3-18: | UART Characteristics                                                      | 34 |

| Table 3-19: | FCAN Characteristics                                                      | 34 |

| Table 3-20: | Serial Flash Programming Operating Characteristics                        | 35 |

| Table 3-21: | A/D Converter Characteristics                                             | 36 |

| Table 5-1:  | Soldering Conditions                                                      | 38 |

|             |                                                                           |    |

## 1. Pin Functions

## 1.1 Port Pins

Table 1-1: Pin Function (1/2)

| Port       | I/O       | Function                          | Port Type | Alternate                    |

|------------|-----------|-----------------------------------|-----------|------------------------------|

| P10        |           |                                   | 5-K       | CRXD01 <sup>Note</sup>       |

| P11        |           |                                   | 5-K/ 19   | CTXD01 <sup>Note</sup>       |

| P12        | I/O       |                                   | 5-K       | CRXD02                       |

| P13        |           |                                   | 5-K       | CTXD02                       |

| P14        | ,,,       | 8-bit input/output port           | 5-K       | CRXD03                       |

| P15        |           |                                   | 5-K       | CTXD03                       |

| P16        |           |                                   | 5-K       | RXD61/INTP9                  |

| P17        |           |                                   | 5-K       | TXD61                        |

| P20        |           |                                   | 5-K       | SI00                         |

| P21        |           |                                   | 5-K       | SO00                         |

| P22        |           |                                   | 5-K       | SCK00                        |

| P23        | I/O       | Port 2<br>8-bit input/output port | 5-K       | SI01                         |

| P24        | 1/0       |                                   | 5-K       | SO01                         |

| P25        |           |                                   | 5-K       | SCK01                        |

| P26        |           |                                   | 5-K       | RXD60/INTP8                  |

| P27        |           |                                   | 5-K       | TXD60                        |

| P30        |           |                                   | 5-K       | TIC00/INTP0/<br>PCLKOUT      |

| P31        |           |                                   | 5-K       | TIC01/ INTP1                 |

| P32        | I/O       | Port 3                            | 5-K       | TOC0 / INTP2                 |

| P33        |           |                                   | 5-K       | TIC10/INTP3 <sup>Note</sup>  |

| P34        |           | 8-bit input/output port           | 5-K       | TIC11 / INTP4Note            |

| P35        | -         |                                   | 5-K       | TOC1 / INTP5 <sup>Note</sup> |

| P36        | -         |                                   | 5-K       | INTP6 <sup>Note</sup>        |

| P37        |           |                                   | 5-K       | INTP7 <sup>Note</sup>        |

| P40        |           |                                   | 5-K       | CRXD11 <sup>Note</sup>       |

| P41        |           |                                   | 5-K / 19  | CTXD11 <sup>Note</sup>       |

| P42        | ]         |                                   | 5-K       | CRXD12                       |

| P43        | I/O       | Port 4                            | 5-K       | CTXD12                       |

| P44        |           | 8-bit input/output port           | 5-K       | SI02 <sup>Note</sup>         |

| P45        |           |                                   | 5-K       | SO02 <sup>Note</sup>         |

| P46        |           |                                   | 5-K       | SCK02Note                    |

| P47        |           |                                   | 5-K       | NMI <sup>Note</sup>          |

| Note: Mark | ed pins a | re 5 V tolerant                   |           |                              |

Table 1-1: Pin Function (2/2)

| Port      | I/O         | Function                                          | Port Type        | Alternate |

|-----------|-------------|---------------------------------------------------|------------------|-----------|

| P70       |             |                                                   |                  | ANI0      |

| P71       |             |                                                   |                  | ANI1      |

| P72       | T .         | Port 7                                            | 0.0              | ANI2      |

| P73       |             | 6-bit input port                                  | 9-C              | ANI3      |

| P74       |             |                                                   |                  | ANI4      |

| P75       |             |                                                   |                  | ANI5      |

| PDH0      |             |                                                   |                  | D16       |

| PDH1      |             |                                                   |                  | D17       |

| PDH2      |             |                                                   |                  | D18       |

| PDH3      |             |                                                   |                  | D19       |

| PDH4      |             |                                                   |                  | D20       |

| PDH5      |             | Port DH <sup>Note</sup> 16-bit input/output port  |                  | D21       |

| PDH6      |             |                                                   |                  | D22       |

| PDH7      | I/O         |                                                   | 5                | D23       |

| PDH8      | 7 1/0       |                                                   | 5                | D24       |

| PDH9      |             |                                                   |                  | D25       |

| PDH10     |             |                                                   |                  | D26       |

| PDH11     |             |                                                   |                  | D27       |

| PDH12     |             |                                                   |                  | D28       |

| PDH13     |             |                                                   |                  | D29       |

| PDH14     |             |                                                   |                  | D30       |

| PDH15     |             |                                                   |                  | D31       |

| PCS0      |             |                                                   |                  | CS0       |

| PCS1      |             |                                                   | 5                | CS1       |

| PCS2      | I/O         | Port CS<br>6-bit input/output port                |                  | CS2       |

| PCS3      | 1/0         |                                                   |                  | CS3       |

| PCS4      |             |                                                   |                  | CS4       |

| PCS6      |             |                                                   |                  | CS6       |

| PCD2      |             |                                                   |                  | BEN0      |

| PCD3      | I/O         | Port CD                                           | 5                | BEN1      |

| PCD4      |             | 4-bit input/output port                           | 3                | BEN2      |

| PCD5      |             |                                                   |                  | BEN3      |

| РСМ0      | I/O         | Port CM<br>1-bit input/output port                | 5                | WAIT      |

| PCT0      |             |                                                   |                  | WR0       |

| PCT1      | I/O         | Port CT                                           | _                | WR1       |

| PCT4      | 7 1/0       | 4-bit input/output port                           | 5                | RD        |

| PCT5      |             |                                                   |                  | WR        |

| Note: PDF | l is only a | vailable for ROM-less mode 1 (16-bit wide externa | al bus at reset) |           |

## 1.2 Non-Port Pins

Table 1-2: Non-Port Pins (1/3)

| Pin Name                                    | I/O     | Function                                              | Port Type | Alternate   |

|---------------------------------------------|---------|-------------------------------------------------------|-----------|-------------|

| V <sub>DD30</sub> -V <sub>DD36</sub> Note 2 | _       | Power supply 3.3 V                                    | -         | -           |

| V <sub>SS30</sub> -V <sub>SS36</sub>        | _       | GND potential for 3.3 V power supply                  | -         | -           |

| CV <sub>DD</sub> Note 3                     | _       | Connection for 3.3 V clock oscillator power supply    | -         | -           |

| CV <sub>SS</sub>                            |         | GND potential for 3.3 V clock oscillator power supply | -         | -           |

| X1                                          | input   | System clock oscillator connection pins.              | 16        | -           |

| X2                                          | output  | System clock oscillator connection pins.              | 16        | -           |

| PCKLOUT                                     | output  | Peripheral clock output                               | 5-K       | P30 / INTP0 |

| MODE0-MODE2                                 | input   | Selects operating mode                                | 2         | -           |

| RESET                                       | input   | System reset input                                    | 2         | -           |

| AV <sub>DD</sub>                            | _       | Power supply for A/D converter                        | -         | -           |

| AV <sub>SS</sub>                            | _       | Ground potential for A/D converter                    | -         | -           |

| AV <sub>REF</sub>                           | input   | reference voltage input for A/D converter             | -         | -           |

| NMI <sup>Note 1</sup>                       | input   | non maskable interrupt input                          | 5-K       | P47         |

| ANI0-ANI5                                   | input   | analog input to A/D converter                         | 9-C       | P70 to P75  |

| SI00                                        |         |                                                       | 5-K       | P20         |

| SI01                                        | input   | serial receive data input to CSI00-CSI02              | 5-K       | P23         |

| SI02 <sup>Note 1</sup>                      |         |                                                       | 5-K       | P44         |

| SO00                                        |         |                                                       | 5-K       | P21         |

| SO01                                        | output  | serial transmit data output from CSI00-CSI02          | 5-K       | P24         |

| SO02 <sup>Note 1</sup>                      |         |                                                       | 5-K       | P45         |

| SCK00                                       |         |                                                       | 5-K       | P22         |

| SCK01                                       | I/O     | serial clock I/O from/to CSI00-CSI02                  | 5-K       | P25         |

| SCK02Note 1                                 |         |                                                       | 5-K       | P46         |

| RXD60                                       |         | and an advantage of the inventor HARTON HARTON        | 5-K       | P26 / INTP8 |

| RXD61                                       | input   | serial receive data input to UART60-UART61            | 5-K       | P16 / INTP9 |

| TXD60                                       | output  | corial transmit data output from LIADT60 LIADT64      | 5-K       | P27         |

| TXD61                                       | Jourpul | tput serial transmit data output from UART60-UART61   |           | P17         |

| CRXD01 <sup>Note 1</sup>                    |         |                                                       | 5-K       | P10         |

| CRXD02                                      | input   | serial receive data input to FCAN01-FCAN03            | 5-K       | P12         |

| CRXD03                                      | 1       |                                                       | 5-K       | P14         |

| CRXD11 <sup>Note 1</sup>                    | input   | serial receive data input to FCAN11-FCAN12            | 5-K       | P40         |

| CRXD12                                      | 1       | Serial receive data iliput to FOAIVII-FOAIVIZ         | 5-K       | P42         |

|                                             | •       |                                                       | •         | •           |

Notes: 1. Marked pins are 5 V tolerant

- 2. All V<sub>DD3</sub> pins have to be connected to each other. On each pin V<sub>DD3</sub>, a capacitor containing a very low serial impedance has to be attached as tight as possible to the pin

- 3. On  $CV_{DD}$ , a capacitor containing a very low serial impedance has to be attached as tight as possible to the pin.  $V_{DD3}$  and  $CV_{DD}$  must be connected to each other

- 4. PDH is only available for ROM-less mode 1 (16-bit wide ext. bus at reset)

Table 1-2: Non-Port Pins (2/3)

| Pin Name                 | I/O    | Function                                           | Port Type | Alternate               |

|--------------------------|--------|----------------------------------------------------|-----------|-------------------------|

| CTXD01 <sup>Note 1</sup> | output |                                                    | 5-K / 19  | P11                     |

| CTXD02                   |        | serial transmit data output to FCAN01-FCAN03       | 5-K       | P13                     |

| CTXD03                   |        |                                                    | 5-K       | P15                     |

| CTXD11 <sup>Note 1</sup> | output | serial transmit data output to FCAN01-FCAN03       | 5-K / 19  | P41                     |

| CTXD12                   |        | Serial transmit data output to FCANOT-FCANOS       | 5-K       | P43                     |

| INTP0                    |        |                                                    |           | P30 / TIC00/<br>PCKLOUT |

| INTP1                    |        |                                                    |           | P31 / TIC01             |

| INTP2                    |        |                                                    |           | P32 / TOC0              |

| INTP3 <sup>Note 1</sup>  |        |                                                    |           | P33 / TIC10             |

| INTP4 <sup>Note 1</sup>  | input  | external interrupt request                         | 5-K       | P34 / TIC11             |

| INTP5 <sup>Note 1</sup>  | ,      |                                                    |           | P35 / TOC1              |

| INTP6 <sup>Note 1</sup>  |        |                                                    |           | P36                     |

| INTP7 <sup>Note 1</sup>  |        |                                                    |           | P37                     |

| INTP8                    |        |                                                    |           | P26/RXD60               |

| INTP9                    |        |                                                    |           | P16/RXD61               |

| TIC00                    | input  | Timer C 0 capture input 0                          | 5-K       | P30/INTP0/<br>PCKLOUT   |

| TIC01                    | input  | Timer C 0 capture input 1                          | 5-K       | P31/INTP1               |

| TOC0                     | output | Timer C 0 compare output 1                         | 5-K       | P32/INTP2               |

| TIC10 <sup>Note 1</sup>  | input  | Timer C 1 capture input 0                          | 5-K       | P33/INTP3               |

| TIC11Note 1              | input  | Timer C 1 capture input 1                          | 5-K       | P34/INTP4               |

| TOC1Note 1               | output | Timer C 1 compare output 1                         | 5-K       | P35/INTP5               |

| D0-D15                   | I/O    | Note 4                                             | 5         | -                       |

| D16-D31                  | I/O    | Data bus of external bus <sup>Note 4</sup>         | 5         | PDH0-PDH15              |

| A0-A7                    |        |                                                    |           | -                       |

| A8-A15                   | output | Address bus of external bus                        | 3         | -                       |

| A16-A23                  |        |                                                    |           | -                       |

| WR0                      | output | Write strobe signal for lower byte (bit 0 - bit 7) | 5         | PCT0                    |

| WR1                      | output | Write strobe signal for upper byte (bit 0 - bit 7) | 5         | PCT1                    |

| RD                       | output | Read strobe signal for external bus                | 5         | PCT4                    |

| WR                       | output | Write strobe signal for external bus               | 5         | PCT5                    |

| WAIT                     | input  | Control signal input for external bus              | 5         | PCM0                    |

## Notes: 1. Marked pins are 5 V tolerant

- 2. All  $V_{DD3}$  pins have to be connected to each other. On each pin  $V_{DD3}$ , a capacitor containing a very low serial impedance has to be attached as tight as possible to the pin

- 3. On  $CV_{DD}$ , a capacitor containing a very low serial impedance has to be attached as tight as possible to the pin.  $V_{DD3}$  and  $CV_{DD}$  must be connected to each other

- 4. PDH is only available for ROM-less mode 1 (16-bit wide ext. bus at reset)

Table 1-2: Non-Port Pins (3/3)

| Pin Name | I/O | Function                            | Port Type | Alternate |

|----------|-----|-------------------------------------|-----------|-----------|

| CS0      |     |                                     | 5         | PCS0      |

| CS1      |     | Chip select output for external bus |           | PCS1      |

| CS2      |     |                                     |           | PCS2      |

| CS3      |     |                                     |           | PCS3      |

| CS4      |     |                                     |           | PCS4      |

| CS6      |     |                                     |           | PCS6      |

| BEN0     |     | Byte enable for external bus        | 5         | PCD2      |

| BEN1     |     |                                     |           | PCD3      |

| BEN2     |     |                                     |           | PCD4      |

| BEN3     |     |                                     |           | PCD5      |

Notes: 1. Marked pins are 5 V tolerant

- 2. All  $V_{DD3}$  pins have to be connected to each other. On each pin  $V_{DD3}$ , a capacitor containing a very low serial impedance has to be attached as tight as possible to the pin

- 3. On  $CV_{DD}$ , a capacitor containing a very low serial impedance has to be attached as tight as possible to the pin.  $V_{DD3}$  and  $CV_{DD}$  must be connected to each other

- 4. PDH is only available for ROM-less mode 1 (16-bit wide ext. bus at reset)

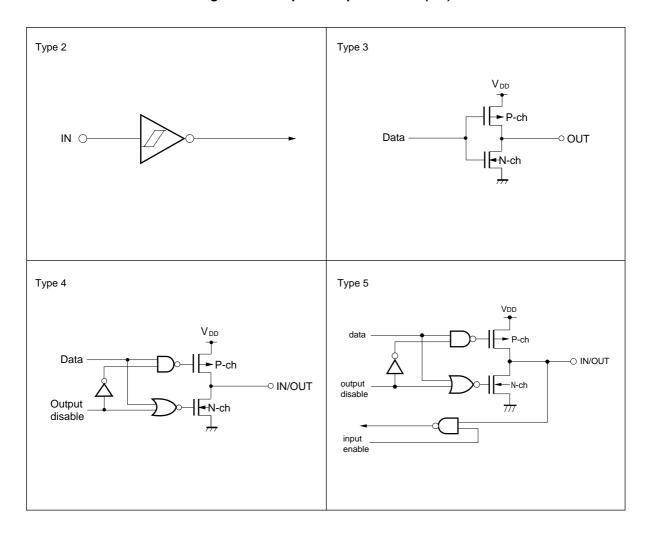

## 1.3 I/O Circuits

Figure 1-1: Input / Output Circuits (1/2)

Figure 1-1: Input / Output Circuits (2/2)

## 2. Programming External Flash Memory

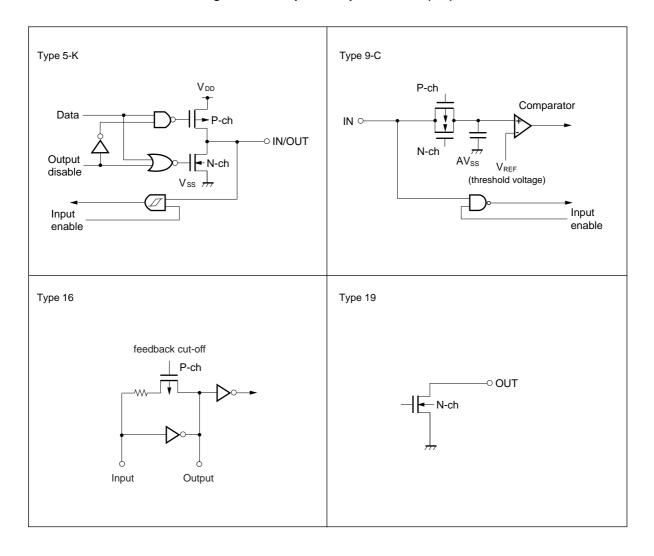

The devices  $\mu PD703177(A)$  and  $\mu PD703445(A)$  support the programming of external flash memories using 2 dedicated flash-programming mode (ROM-less mode0 & ROM-less mode1), dependent on the used bus width for external flash access. These modes will be entered if the MODE pins have been configured accordingly and in addition a system reset has been performed.

In the flash-programming mode, an integrated Boot-Loader is enabled to download the programming and control algorithms to the CarGate-F's and CarGate-S's iRAM. This feature offers a high flexibility to be able to program various external flash memories.

Naturally, it is also possible to program the external flash memory by performing self-programming software functions and I/O communications.

For programming details, see the User's Manual.

Figure 2-1: Programming Mode Selection Format

**Note:** Refer to the chapter "RESET (power up/down sequence)" on page 30.

## 3. Electrical Specifications

## 3.1 Absolute Maximum Ratings

Table 3-1: Absolute Maximum Ratings ( $T_A = 25^{\circ}C$ ,  $V_{SS3x} = 0 V$ )

| Parameter                                   |                                        | Symbol              | Test Conditions                               | Ratings     | Unit |

|---------------------------------------------|----------------------------------------|---------------------|-----------------------------------------------|-------------|------|

|                                             |                                        | $AV_DD$             |                                               | -0.5 ~ +4.6 | V    |

|                                             |                                        | AV <sub>SS</sub>    |                                               | -0.5 ~ +0.5 | V    |

| Supply voltage                              |                                        | V <sub>DD3</sub>    |                                               | -0.5 ~ +4.6 | V    |

|                                             |                                        | CV <sub>DD</sub>    |                                               | -0.5 ~ +4.6 | V    |

|                                             |                                        | CV <sub>SS</sub>    |                                               | -0.5 ~ +0.5 | V    |

|                                             | 5 V tolerant<br>pins <sup>Note 1</sup> | V <sub>I4</sub>     | V <sub>I4</sub> < V <sub>DD3</sub> + 3.0 V    | -0.5 ~ +6.6 | V    |

| Input voltage                               | 3.3 V pins <sup>Note 2</sup>           | V <sub>I3</sub>     | $V_{13} < V_{DD3} + 0.5 V$                    | -0.5 ~+4.6  | V    |

|                                             | A <sub>VREF</sub>                      | V <sub>IAVREF</sub> | V <sub>IAVREF</sub> < AV <sub>DD</sub> +0.3 V | -0.3 ~ +4.6 | V    |

|                                             | P7                                     | V <sub>IA</sub>     | $V_{IA} < AV_{DD} + 0.3 V$                    | -0.3 ~ +4.6 | V    |

| Output current low                          | 1 pin                                  | I <sub>OL0</sub>    |                                               | 4.0         | mA   |

| Output current low                          | All pins                               | I <sub>OL1</sub>    |                                               | 50          | mA   |

| Output current high                         | 1 pin                                  | I <sub>OH0</sub>    |                                               | -4.0        | mA   |

| Output current nigh                         | All pins                               | I <sub>OH1</sub>    |                                               | -50         | mA   |

| Output voltage 3.3 V pins <sup>Note 2</sup> |                                        | V <sub>O1</sub>     | $V_{O1} < V_{DD3} + 0.5 V$                    | -0.5 ~ +4.6 | V    |

| Operating temperature                       |                                        | T <sub>OPR</sub>    |                                               | -40 ~ +85   | °C   |

| Storage temperature                         |                                        | T <sub>STGB</sub>   |                                               | -55 ~ +150  | °C   |

**Notes: 1.** 5 V tolerant pins are P10, P11, P33, P34, P35, P36, P37, P40, P41, P44, P45, P46, P47

2. 3.3 V pins are Ax, Dx, PCSx, PCM0, PCTx, MODEx, PCDx, P12~P17, P2x, P30~P32, P42, P43, RESET

## 3.2 General Characteristics

- 3.2.1 Oscillator recommendations (main system clock oscillator)

- (1) Ceramic resonator or crystal resonator connection

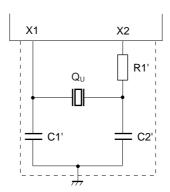

Figure 3-1: Main Oscillator Recommendations

**Remark:** Values of capacitors C1', C2' and R1' depend on used resonator and must be specified in cooperation with the manufacturer.

Cautions: 1. External clock input is prohibited.

- 2. When using the main system clock oscillator, wire as follows in the area enclosed by the broken lines in the above figure to avoid an adverse effect from wiring capacitance.

- · Keep the wiring length as short as possible.

- · Do not cross the wiring with the other signal lines.

- Do not route the wiring near a signal line through which a high fluctuating current flows.

- Always make the ground point of the oscillator capacitor the same potential as V<sub>SS</sub>.

- Do not ground the capacitor to a ground pattern through which a high current flows.

- Do not fetch signals from the oscillator.

## 3.2.2 Oscillator characteristics

$$(T_A = -40 \sim +85^{\circ}C, V_{DD3x} = CV_{DD} = AV_{DD} = 3.0 \text{ V} \sim 3.6 \text{ V}, V_{SS3x} = CV_{SS} = AV_{SS} = 0 \text{ V})$$

Table 3-2: Main Oscillator Characteristics

| Parameter                      | Symbol           | Test Conditions | MIN.                | TYP. | MAX. | Unit |

|--------------------------------|------------------|-----------------|---------------------|------|------|------|

| Oscillation stabilization time | T <sub>OST</sub> |                 | 500 <sup>Note</sup> |      |      | ns   |

| Main oscillator frequency      | f <sub>OSC</sub> |                 | 4                   |      | 5    | MHz  |

**Note:** The above specified value is the time needed to stabilize internally. It does not include the stabilization time of the external crystal. This value is specified for an external quartz which reached 10% / 90% maximum oscillation level. The oscillation stabilization time for the external crystal has to be added to above specified value.

## 3.2.3 Peripheral PLL characteristics

$$(T_A = -40 \sim +85^{\circ}C, V_{DD3x} = CV_{DD} = AV_{DD} = 3.0 \text{ V} \sim 3.6 \text{ V}, V_{SS3x} = CV_{SS} = AV_{SS} = 0 \text{ V})$$

Table 3-3: Peripheral PLL Characteristics

| Parameter     | Symbol           | Test Conditions | MIN. | TYP. | MAX. | Unit |

|---------------|------------------|-----------------|------|------|------|------|

| PLL lock time | T <sub>PLL</sub> |                 |      |      | 1    | ms   |

## 3.2.4 Spread spectrum PLL characteristics

$$(T_A = -40 \sim +85^{\circ}C, V_{DD3x} = CV_{DD} = AV_{DD} = 3.0 \text{ V} \sim 3.6 \text{ V}, V_{SS3x} = CV_{SS} = AV_{SS} = 0 \text{ V})$$

Table 3-4: Spread Spectrum PLL Characteristics

| Parameter                       | Symbol            | Test Conditions          | MIN. | TYP. | MAX. | Unit |

|---------------------------------|-------------------|--------------------------|------|------|------|------|

| SSCG lock time                  | T <sub>SSCG</sub> |                          |      |      | 3    | ms   |

| Frequency multiplication Note 1 | M <sub>SSCG</sub> | F <sub>OSC</sub> = 4 MHz |      | 60/3 |      | -    |

|                                 |                   | F <sub>OSC</sub> = 5 MHz |      | 48/3 |      | -    |

| Frequency modulation Note 2     |                   | Dithering enabled        |      | 1    |      | %    |

Notes: 1. Frequency multiplication is given as n/m where n means setup values for register SCFC0/SCFC1and m means divider factor determined by register SCFMC Please refer to CarGate-F UM.

2. Frequency modulation is determined by register values of SCFC0 and SCFC1.

## 3.2.5 Capacitances

$$(\mathsf{T_A} = 25^{\circ}\mathsf{C},\,\mathsf{V_{DD3x}} = \mathsf{V_{SS3x}} = \mathsf{CV_{DD}} = \mathsf{CV_{SS}} = \mathsf{AV_{DD}} = \mathsf{AV_{SS}} = \mathsf{0}\,\,\mathsf{V})$$

Table 3-5: Capacitances

| Parameter                | Symbol          | Test Conditions        | MIN. | TYP. | MAX. | Unit |

|--------------------------|-----------------|------------------------|------|------|------|------|

| Input capacitance        | C <sub>I</sub>  | f <sub>C</sub> = 1 MHz |      |      | 15   | pF   |

| Input/output capacitance | C <sub>IO</sub> | Unmeasured pins        |      |      | 15   | pF   |

| Output capacitance       | Co              | returned to 0 V        |      |      | 15   | pF   |

## 3.3 Operating Conditions

#### 3.3.1 Peripheral clock

$$(T_A = -40 \sim +85^{\circ}C, V_{DD3x} = CV_{DD} = AV_{DD} = 3.0 \text{ V} \sim 3.6 \text{ V}, V_{SS3x} = CV_{SS} = AV_{SS} = 0 \text{ V})$$

Table 3-6: Peripheral Clock

| Clock Mode     | Inside Peripheral<br>Operation Clock Frequency |

|----------------|------------------------------------------------|

| PLL on Note 1  | 16 to 20 MHz                                   |

| PLL off Note 2 | 4 to 5 MHz                                     |

**Notes: 1.** The inside peripheral operation clock frequency is the crystal frequency multiplied with the multiplication factor ×4.

2. The inside peripheral operation clock frequency is the crystal frequency.

## 3.3.2 CPU/BCU clock

$$(T_A = -40 \sim +85^{\circ}C, V_{DD3x} = CV_{DD} = AV_{DD} = 3.0 \text{ V} \sim 3.6 \text{ V}, V_{SS3x} = CV_{SS} = AV_{SS} = 0 \text{ V})$$

Table 3-7: CPU/BCU Clock

| Clock Mode                  | Inside Operation<br>Clock Frequency |

|-----------------------------|-------------------------------------|

| SSCG on Note 1              | 20 & 40 MHz                         |

| PLL on Note 2               | 16 to 20 MHz<br>32 to 40 MHz        |

| SSCG off,<br>PLL off Note 3 | 4 to 5 MHz                          |

**Notes: 1.** The max. inside operation clock frequency is the crystal frequency multiplied with a multiplication factor configured in the SSCG Frequency Control Register 1 (SCFC1) and divided by a factor configured in the SSCG Frequency Modulation Control Register (SCFMC).

- 2. The inside operation clock frequency is the crystal frequency multiplied with the multiplication factor ×4 or ×8 according to the setting of the Processor Clock Control Register (PCC).

- **3.** The inside operation clock frequency is the crystal frequency.

## 3.4 DC Characteristics

$(T_A = -40 \sim +85^{\circ}C, V_{DD3x} = CV_{DD} = AV_{DD} = 3.0 \text{ V} \sim 3.6 \text{ V}, V_{SS3x} = CV_{SS} = AV_{SS} = 0 \text{ V})$

| Paramet                    | er          | Symbol            | Test<br>Conditions        | MIN.                   | TYP. | MAX.                 | Unit |

|----------------------------|-------------|-------------------|---------------------------|------------------------|------|----------------------|------|

| Input voltage high         | Pin group 1 | V <sub>IH1</sub>  |                           | 0.7 V <sub>DD3</sub>   |      | $V_{DD3}$            | V    |

| Input voltage low          | Pin group 1 | V <sub>IL1</sub>  |                           | 0                      |      | 0.3 V <sub>DD3</sub> | V    |

| Input voltage high         | Pin group 2 | V <sub>IH3</sub>  |                           | 0.8 V <sub>DD3</sub>   |      | $V_{DD3}$            | V    |

| Input voltage low          | Pin group 3 | V <sub>IL3</sub>  |                           | 0                      |      | 0.2 V <sub>DD3</sub> | V    |

| Input voltage high         | Pin group 4 | V <sub>IH7</sub>  |                           | 0.8 V <sub>DD3</sub>   |      | 5.5                  | V    |

| Input voltage high         | P7x         | V <sub>IHA</sub>  |                           | 0.7 AV <sub>DD</sub>   |      | AV <sub>DD</sub>     | V    |

| Input voltage low          | P7x         | V <sub>ILA</sub>  |                           | 0                      |      | 0.3 AV <sub>DD</sub> | V    |

|                            | Pin group 5 | \/                | I <sub>OH</sub> = -2.5 mA | V <sub>DD3</sub> - 1 V |      |                      | V    |

| Output voltage high        | Pin group 4 | V <sub>OH1</sub>  | I <sub>OH</sub> = -1.0 mA | V <sub>DD3</sub> - 1 V |      |                      | V    |

| Output voltage low         | Pin group 6 | V <sub>OL1</sub>  | I <sub>OL</sub> = 2.5 mA  |                        |      | 0.4                  | V    |

|                            | Pin group 7 | I <sub>LIH1</sub> | $V_I = V_{DD3}$           |                        |      | 5                    | μΑ   |

| Input leakage current high | Pin group 4 | I <sub>LIH2</sub> | V <sub>I</sub> = 5.5 V    |                        |      | 5                    | μΑ   |

| 3                          | P7x         | I <sub>LIHA</sub> | $AV_{IN} = AV_{DD}$       |                        |      | 5                    | μΑ   |

| Input leakage current      | Pin group 8 | I <sub>LIL1</sub> | V <sub>I</sub> = 0 V      |                        |      | -5                   | μΑ   |

| low                        | P7x         | I <sub>LILA</sub> | AV <sub>IN</sub> = 0 V    |                        |      | -5                   | μA   |

Table 3-8: DC Characteristics Conditions

Remarks: 1. Pin group 1: D0-15, PDHx, PCSx, PCM0, PCTx (All pins with CMOS input characteristic)

- 2. Pin group 2: MODEx, P12~17, P2x, P30~P32, P42, P43, RESET (All 3.3 V pins with SCHMITT input characteristic)

- 3. Pin group 3: P1x, P2x, P3x, P4x, MODEx, RESET (All pins with SCHMITT input characteristic)

- **4.** Pin group 4: P10, P11, P33, P34, P35, P36, P37, P40, P41, P44, P45, P46, P47 (All 5 V tolerant pins)

- 5. Pin group 5: Ax, Dx, PDHx, PCSx, PCM0, PCTx, PCDx, P12~P17, P2x, P30~P32, P42, (All 3.3 V pins with output capability)

- 6. Pin group 6: Ax, Dx, PDHx, PCSx, PCM0, PCTx, PCDx, P1x, P2x, P3x, P4x (All pins with output capability)

- 7. Pin group 7: Dx, PDHx, PCSx, PCM0, PCTx, PCDx, MODEx, P12~P17, P2x, P30~P32, P42, P43, RESET (All 3.3 V pins except P7x)

- 8. Pin group 8: Dx, PDHx, PCSx, PCM0, PCTx, PCDx, MODEx, P1x, P2x, P3x, P4x, RESET (All pins except P7x)

Table 3-9: Power Supply Currents

| Parameter      | Symbol              | Test Conditions                                                                                        | MIN. | TYP. | MAX. | Unit |

|----------------|---------------------|--------------------------------------------------------------------------------------------------------|------|------|------|------|

|                | I <sub>DD1SC1</sub> | Operating (SSCG1)<br>(f <sub>CPU</sub> = 40 MHz)<br>(f <sub>Perph</sub> = 20 MHz)<br>SSCG: on; PLL: on |      | 105  | 158  | mA   |

|                | I <sub>DD1SC2</sub> | Operating (SSCG2)<br>(f <sub>CPU</sub> = 20 MHz)<br>(f <sub>Perph</sub> = 20 MHz)<br>SSCG: on; PLL: on |      | 73   | 110  | mA   |

|                | I <sub>DD1P1</sub>  | Operating (PLL1) (f <sub>CPU</sub> = 40 MHz) (f <sub>Perph</sub> = 20 MHz) SSCG: off; PLL: on          |      | 97   | 146  | mA   |

|                | I <sub>DD10</sub>   | Operating (OSC)<br>(f <sub>CPU</sub> = 5 MHz)<br>(f <sub>Perph</sub> = 5 MHz)<br>SSCG: off; PLL: off   |      | 16   | 24   | mA   |

| Supply current | I <sub>DD2SC1</sub> | HALT(SSCG1)<br>(f <sub>CPU</sub> = 40 MHz)<br>(f <sub>Perph</sub> = 20 MHz)<br>SSCG: on; PLL: on       |      | 70   | 105  | mA   |

|                | I <sub>DD2P1</sub>  | HALT (PLL1)<br>(f <sub>CPU</sub> = 40 MHz)<br>(f <sub>Perph</sub> = 20 MHz)<br>SSCG: off; PLL: on      |      | 63   | 95   | mA   |

|                | I <sub>DD3SC1</sub> | IDLE (SSCG1)<br>(f <sub>CPU</sub> = 40 MHz)<br>(f <sub>Perph</sub> = 20 MHz)<br>SSCG: on; PLL: on      |      | 6.5  | 10   | mA   |

|                | I <sub>DD3P1</sub>  | IDLE (PLL1)<br>(f <sub>CPU</sub> = 40 MHz)<br>(f <sub>Perph</sub> = 20 MHz)<br>SSCG: off; PLL: off     |      | 2    | 3    | mA   |

|                | I <sub>DD5P</sub>   | STOP                                                                                                   |      | 100  | 500  | μΑ   |

**Remark:** The current values listed above are valid for current consumed by the chip logic itself, i.e. excluding ADC and I/O buffer power supply.

## 3.5 AC Characteristics

$$\begin{split} &T_A=-40\sim +85^{\circ}\text{C},\\ &V_{DD3x}=\text{CV}_{DD}=\text{AV}_{DD}=3.0~\text{V}\sim 3.6~\text{V},\\ &V_{SS3x}=\text{CV}_{SS}=\text{AV}_{SS}=0~\text{V},\\ &\text{output pin load capacitance: }C_L=50~\text{pF} \end{split}$$

## 3.5.1 General

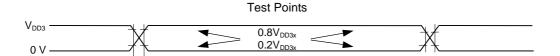

For pins P1x, P2x, P3x, P4x, MODEx, RESET (All 3.3 V pins with SCHMITT input characteristics)

Figure 3-2: AC Test Input/Output Waveform SCHMITT

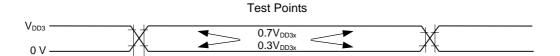

For pins D0-D15, PDHx, PCSx, PCM0, PCTx, P7x (All pins with CMOS input characteristics)

Figure 3-3: AC Test Input/Output Waveform CMOS

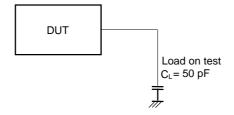

## 3.5.2 AC test load condition

Figure 3-4: AC Test Load Condition

## 3.5.3 Clock timing

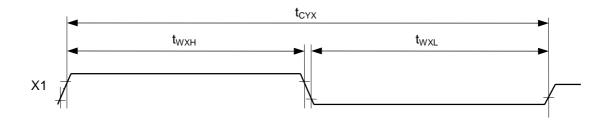

Table 3-10: Clock Timing

| Parameter                 | Symbol           | Test Conditions | MIN. | MAX. | Unit |

|---------------------------|------------------|-----------------|------|------|------|

| X1 input cycle            | t <sub>CYX</sub> | OSC Mode        | 200  | 250  | ns   |

| X1 input high-level width | t <sub>WXH</sub> | OSC Mode        | 95   |      | ns   |

| X1 input low-level width  | t <sub>WXL</sub> | OSC Mode        | 95   |      | ns   |

Figure 3-5: Clock Timing

## 3.5.4 External memory access read timing

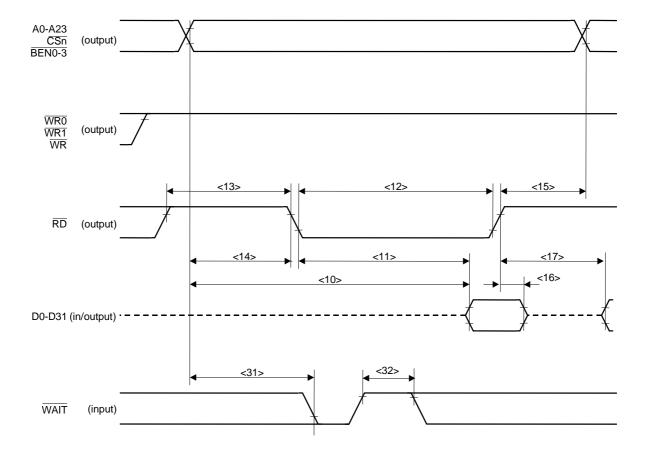

Table 3-11: External Memory Access Read Timing

| Parameter                                                                              |       | Symbol             | MIN.                        | MAX.                          | Unit |

|----------------------------------------------------------------------------------------|-------|--------------------|-----------------------------|-------------------------------|------|

| Data input set up time (vs. address)                                                   | <10>  | T <sub>SAID</sub>  |                             | (2+W <sub>T</sub> )T-23       | ns   |

| Data input set up time (vs. RD↓)                                                       | <11>  | T <sub>SRDID</sub> |                             | (1.5+W <sub>D</sub> +W)T-20.5 | ns   |

| RD Low level width                                                                     | <12>  | T <sub>WRDL</sub>  | (1.5+W <sub>D</sub> +W)T-5  |                               | ns   |

| RD High level width                                                                    | <13>  | T <sub>WRDH</sub>  | (0.5+W <sub>AS</sub> +i)T-5 |                               | ns   |

| Address, $\overline{\text{CSn}} \to \overline{\text{RD}} \downarrow \text{delay time}$ | <14>  | T <sub>DARD</sub>  | (0.5+W <sub>AS</sub> )T-12  |                               | ns   |

| RD↑ → address delay time                                                               | <15>  | T <sub>DRDA</sub>  | iT-2                        |                               | ns   |

| Data input hold time (vs. RD↑)                                                         | <16>  | T <sub>HRDID</sub> | -2                          |                               | ns   |

| $\overline{\text{RD}} \uparrow \rightarrow$ data output delay time                     | <17>  | T <sub>DRDOD</sub> | (0.5+i)T-6                  |                               | ns   |

| WAIT set up time (vs. address)                                                         | < 31> | T <sub>SAW</sub>   |                             | (1+W <sub>AS</sub> )T-22.5    | ns   |

| WAIT high level width                                                                  | <32>  | T <sub>WWH</sub>   | T+10                        |                               | ns   |

Remarks: 1. T: 1/f<sub>CPU</sub>

2. i: Number of idle states specified by BCC register

3.  $W_T$ : Total Number of waits,  $W_T = W_{AS} + W_D + W$

4. WAS: Number of waits specified by ASC register

5.  $W_D$ : Number of waits specified by DWC1, DWC2 register;  $W_D \ge 1$

**6.** W: Number of waits due to  $\overline{\text{WAIT}}$

Figure 3-6: External Memory Access Read Timing

## 3.5.5 External memory access write timing

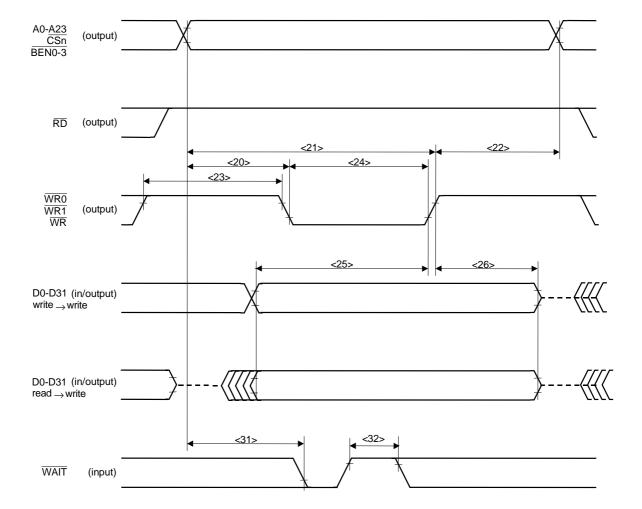

Table 3-12: External Memory Access Write Timing

| Parameter                                                              |      | Symbol             | MIN.                         | MAX.                       | Unit |

|------------------------------------------------------------------------|------|--------------------|------------------------------|----------------------------|------|

| Address, <del>CSn</del> → <del>WR0</del> , <del>WR1</del> ↓ delay time | <20> | T <sub>DAWR</sub>  | (0.5+W <sub>AS</sub> )T-8.5  |                            | ns   |

| Address set up (vs. WR0, WR1↑)                                         | <21> | T <sub>SAWR</sub>  | (1.5+W <sub>T</sub> )T-8.5   |                            | ns   |

| WR0, WR1↑ → address delay time                                         | <22> | T <sub>DWRA</sub>  | (0.5+i)T-10                  |                            | ns   |

| WR0, WR1 High level width                                              | <23> | T <sub>WWRH</sub>  | (0.5+i+W <sub>AS</sub> )T-10 |                            | ns   |

| WR0, WR1 Low level width                                               | <24> | T <sub>WWRL</sub>  | (1+W+W <sub>D</sub> )T-8.0   |                            | ns   |

| Data output set up time (vs. WR0, WR1↑)                                | <25> | T <sub>SODWR</sub> | (0.5+W <sub>T</sub> )T-6.0   |                            | ns   |

| Data output hold time (vs. WR0, WR1↑)                                  | <26> | T <sub>HWROD</sub> | (0.5+i)-6.0                  |                            | ns   |

| WAIT set up time (vs. address)                                         | <31> | T <sub>SAW</sub>   |                              | (1+W <sub>AS</sub> )T-22.5 | ns   |

| WAIT high level width                                                  | <32> | T <sub>WWH</sub>   | T+10                         |                            | ns   |

Remarks: 1. T: 1/f<sub>CPU</sub>

2. i: Number of idle states specified by BCC register

3.  $W_T$ : Total Number of waits,  $W_T = W_{AS} + W_D + W$

**4.** W<sub>AS</sub>: Number of waits specified by ASC register

5.  $W_D$ : Number of waits specified by DWC1, DWC2 register;  $W_D \ge 1$

**6.** W: Number of waits due to  $\overline{\text{WAIT}}$

Figure 3-7: External Memory Access Write Timing

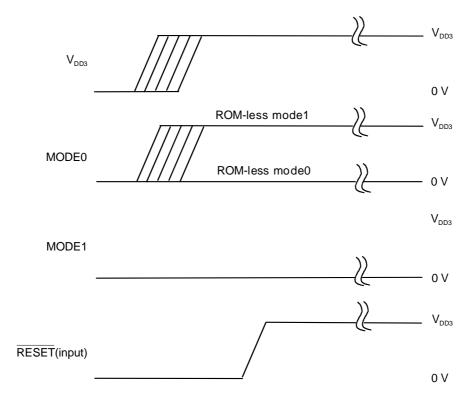

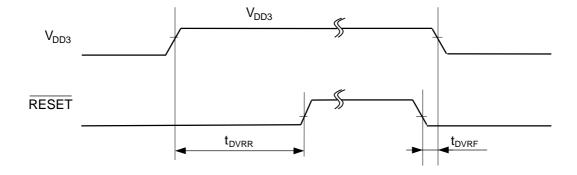

## 3.5.6 RESET (power up/down sequence)

Table 3-13: RESET Timing

| Parameter              | Symbol             | Test Conditions          | MIN.                  | MAX. | Unit |

|------------------------|--------------------|--------------------------|-----------------------|------|------|

| RESET high-level width | t <sub>WRSH</sub>  |                          | 500                   |      | ns   |

| RESET low-level width  | t <sub>WRSL0</sub> | STOP mode release        | T <sub>OST</sub> Note |      | ms   |

| RESET IOW-level width  | t <sub>WRSL2</sub> | except STOP Mode release | 500                   |      | ns   |

| RESET hold time        | t <sub>DVRR</sub>  | OSC Mode on power-on     | T <sub>OST</sub> Note |      | ms   |

| RESET setup time       | t <sub>DVRF</sub>  | OSC Mode on power-off    | 0                     |      | ns   |

$\textbf{Note:} \quad \textbf{$T_{OST}$: Oscillation stabilization time of main oscillator}$

Figure 3-8: RESET Timing

Caution:  $\overline{\text{RESET}}$  must be applied whenever  $V_{DD3}$  is out of operating condition.

## 3.5.7 Interrupt timing

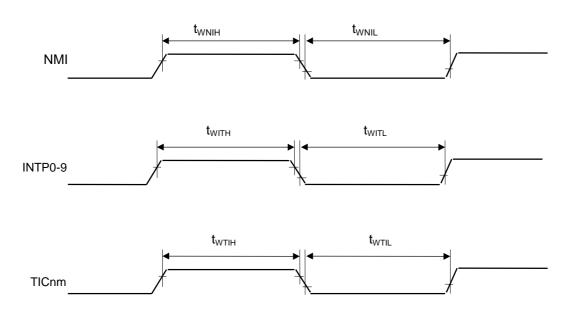

Table 3-14: Interrupt Timing

| Parameter                     | Symbol            | Test Conditions | MIN. | MAX. | Unit |

|-------------------------------|-------------------|-----------------|------|------|------|

| NMI high-level width          | t <sub>WNIH</sub> |                 | 500  |      | ns   |

| NMI low-level width           | t <sub>WNIL</sub> |                 | 500  |      | ns   |

| INTPi Note 1 high-level width | t <sub>WITH</sub> |                 | 500  |      | ns   |

| INTPi Note 1 low-level width  | t <sub>WITL</sub> |                 | 500  |      | ns   |

| TICmn Note 2 high-level width | t <sub>WTIH</sub> |                 | 500  |      | ns   |

| TICmn Note 2 low-level width  | t <sub>WTIL</sub> |                 | 500  |      | ns   |

**Notes: 1.** i = 0 to 9

**2.** m & n = 0 to 1

Figure 3-9: Interrupt Timing

## 3.6 Peripheral Function Characteristics

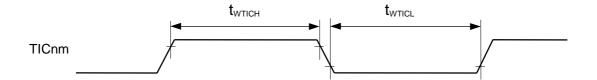

## 3.6.1 Timer C

Table 3-15: Timer C Characteristics

| Parameter                     | Symbol             | Test Conditions | MIN.                        | MAX. | Unit |

|-------------------------------|--------------------|-----------------|-----------------------------|------|------|

| TICmn Note 1 high-level width | t <sub>WTICH</sub> |                 | 100 + T <sub>T</sub> Note 2 |      | ns   |

| TICmn Note 1 low-level width  | t <sub>WTICL</sub> |                 | 100 + T <sub>T</sub> Note 2 |      | ns   |

**Notes: 1.** m & n = 0 to 1

**2.** T<sub>T</sub>: Depends on selected clock source for the peripheral clock supply and the setup of the respective timer macro clock and timer channel setup

Figure 3-10: Timer C Characteristics

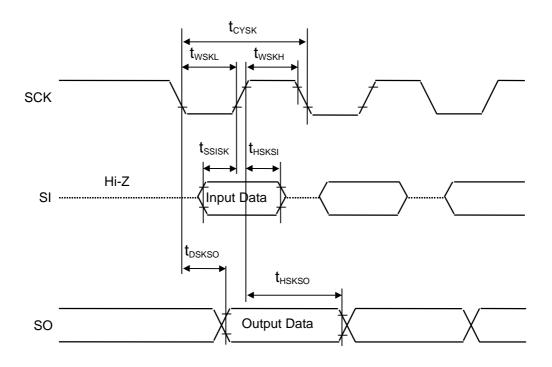

## 3.6.2 CSI

Table 3-16: CSI Master Mode Characteristics

| Parameter                                                       | Symbol              | Test Conditions | MIN.                       | MAX. | Unit |

|-----------------------------------------------------------------|---------------------|-----------------|----------------------------|------|------|

| SCK cycle time                                                  | t <sub>CYSKM</sub>  | Output          | 200                        |      | ns   |

| SCK high level width                                            | t <sub>WSKHM</sub>  | Output          | 0.5 t <sub>CYSK</sub> - 15 |      | ns   |

| SCK low level width                                             | t <sub>WSKLM</sub>  | Output          | 0.5 t <sub>CYSK</sub> - 15 |      | ns   |

| SI set up time (to SCK ↑)                                       | t <sub>SSISKM</sub> |                 | 30                         |      | ns   |

| SI hold time (from SCK ↑)                                       | t <sub>HSKSIM</sub> |                 | 30                         |      | ns   |

| SO output delay time (from $\overline{\text{SCK}} \downarrow$ ) | t <sub>DSKSOM</sub> |                 |                            | 30   | ns   |

| SO output hold time (from SCK ↑)                                | t <sub>HSKSOM</sub> |                 | 0.5 t <sub>CYSK</sub> - 5  |      | ns   |

Table 3-17: CSI Slave Mode Characteristics

| Parameter                                                       | Symbol              | Test Conditions | MIN.              | MAX. | Unit |

|-----------------------------------------------------------------|---------------------|-----------------|-------------------|------|------|

| SCK cycle time                                                  | t <sub>CYSKS</sub>  | Input           | 200               |      | ns   |

| SCK high level width                                            | t <sub>WSKHS</sub>  | Input           | 90                |      | ns   |

| SCK low level width                                             | t <sub>WSKLS</sub>  | Input           | 90                |      | ns   |

| SI set up time (to SCK ↑)                                       | t <sub>SSISKS</sub> |                 | 15                |      | ns   |

| SI hold time (from SCK ↑)                                       | t <sub>HSKSIS</sub> |                 | 15                |      | ns   |

| SO output delay time (from $\overline{\text{SCK}} \downarrow$ ) | t <sub>DSKSOS</sub> |                 |                   | 30   | ns   |

| SO output hold time (from SCK ↑)                                | t <sub>HSKSOS</sub> |                 | t <sub>WSKH</sub> |      | ns   |

Figure 3-11: CSI Slave Mode Characteristics

## 3.6.3 UART6

Table 3-18: UART Characteristics

| Parameter     | Symbol             | Test Conditions                 | MIN. | MAX.   | Unit |

|---------------|--------------------|---------------------------------|------|--------|------|

| Transfer rate | T <sub>UART6</sub> | f <sub>Peripheral</sub> ≥ 5 MHz |      | 312500 | bps  |

## 3.6.4 FCAN

Table 3-19: FCAN Characteristics

| Parameter     | Symbol            | Test Conditions                  | MIN. | MAX. | Unit |

|---------------|-------------------|----------------------------------|------|------|------|

| Transfer rate | T <sub>FCAN</sub> | f <sub>Peripheral</sub> ≥ 16 MHz |      | 1    | Mbps |

## 3.6.5 Serial flash programming operating characteristics

Table 3-20: Serial Flash Programming Operating Characteristics

| Parameter                                     | Symbol                            | Test Conditions | MIN.                       | MAX. | Unit |

|-----------------------------------------------|-----------------------------------|-----------------|----------------------------|------|------|

| Count start setup time from RESET↑            | T <sub>RFCF</sub>                 |                 | 5T <sup>Note 1</sup> + 500 |      | μs   |

| Times of MODE1 counting                       | T <sub>COUNT</sub>                |                 |                            | 10   | ms   |

| MODE1 count High/Low level width              | T <sub>CH</sub> , T <sub>CL</sub> |                 | 1                          |      | μ    |

| V <sub>DD3</sub> ↑ setup time MODE1↑          | T <sub>DRPSR</sub>                |                 | 100                        |      | ns   |

| V <sub>DD3</sub> ↑ setup time RESET↑          | T <sub>DRRR</sub>                 |                 | T <sub>OST</sub>           |      | ms   |

| MODE1↑ setup time RESET↑                      | T <sub>PSRRF</sub>                |                 | T <sub>OST</sub>           |      | ms   |

| MODE1 <sup>Note 2</sup> pulse count for UART0 | N <sub>PUART0</sub>               |                 | 0                          |      | -    |

| MODE1Note 2 pulse count for CSI0              | N <sub>PCSI0</sub>                |                 | 8                          |      | -    |

**Notes: 1.**  $T = 1/f_{OSC}$

2. MODE1 input pin is a schmitt-trigger input buffer

Figure 3-12: Serial Flash Programming Operating Characteristics

## 3.6.6 A/D converter

Table 3-21: A/D Converter Characteristics

| Parameter                                 | Symbol             | Test Conditions      | MIN.             | TYP.                 | MAX.              | Unit |

|-------------------------------------------|--------------------|----------------------|------------------|----------------------|-------------------|------|

| Resolution                                | -                  |                      |                  | 10                   |                   | Bit  |

| Overall error Note 1                      | -                  | $AV_{REF} = AV_{DD}$ |                  |                      | ±8                | LSB  |

| Conversion time Note 2                    | t <sub>CONV</sub>  |                      | 5                |                      | 12                | μs   |

| Sampling time                             | t <sub>SAM</sub>   |                      |                  | T <sub>CONV</sub> /6 |                   | μs   |

| Analogue input voltage                    | V <sub>IAN</sub>   |                      | AV <sub>SS</sub> |                      | AV <sub>REF</sub> | V    |

| Analogue supply current                   | I <sub>AVDD</sub>  |                      |                  |                      | 3.0               | mA   |

| Reference voltage                         | AV <sub>REF</sub>  |                      | 3.0              |                      | $AV_DD$           | V    |

| Reference voltage input current operation | I <sub>AVREF</sub> | $AV_{REF} = AV_{DD}$ |                  | 1                    | 2                 | mA   |

Notes: 1. Quantization error is not included

2. Conversion time is determined by the number of clocks set by the ADM1 register.

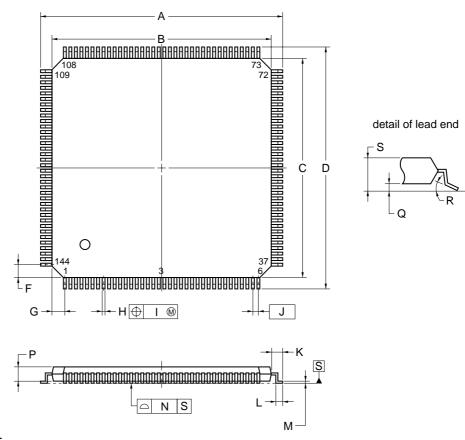

## 4. Package Drawing

Figure 4-1: Package Drawing

## 144-PIN PLASTIC LQFP (FINE PITCH) (20x20)

#### NOTE

Each lead centerline is located within 0.08 mm of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            |

|------|------------------------|

| A    | 22.0±0.2               |

| В    | 20.0±0.2               |

| С    | 20.0±0.2               |

| D    | 22.0±0.2               |

| F    | 1.25                   |