To our customers,

---

## Old Company Name in Catalogs and Other Documents

---

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <http://www.renesas.com>

April 1<sup>st</sup>, 2010

Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<http://www.renesas.com>)

Send any inquiries to <http://www.renesas.com/inquiry>.

## Notice

1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

(Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

(Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## DOT MATRIX LCD CONTROLLER/DRIVER

**DESCRIPTION**

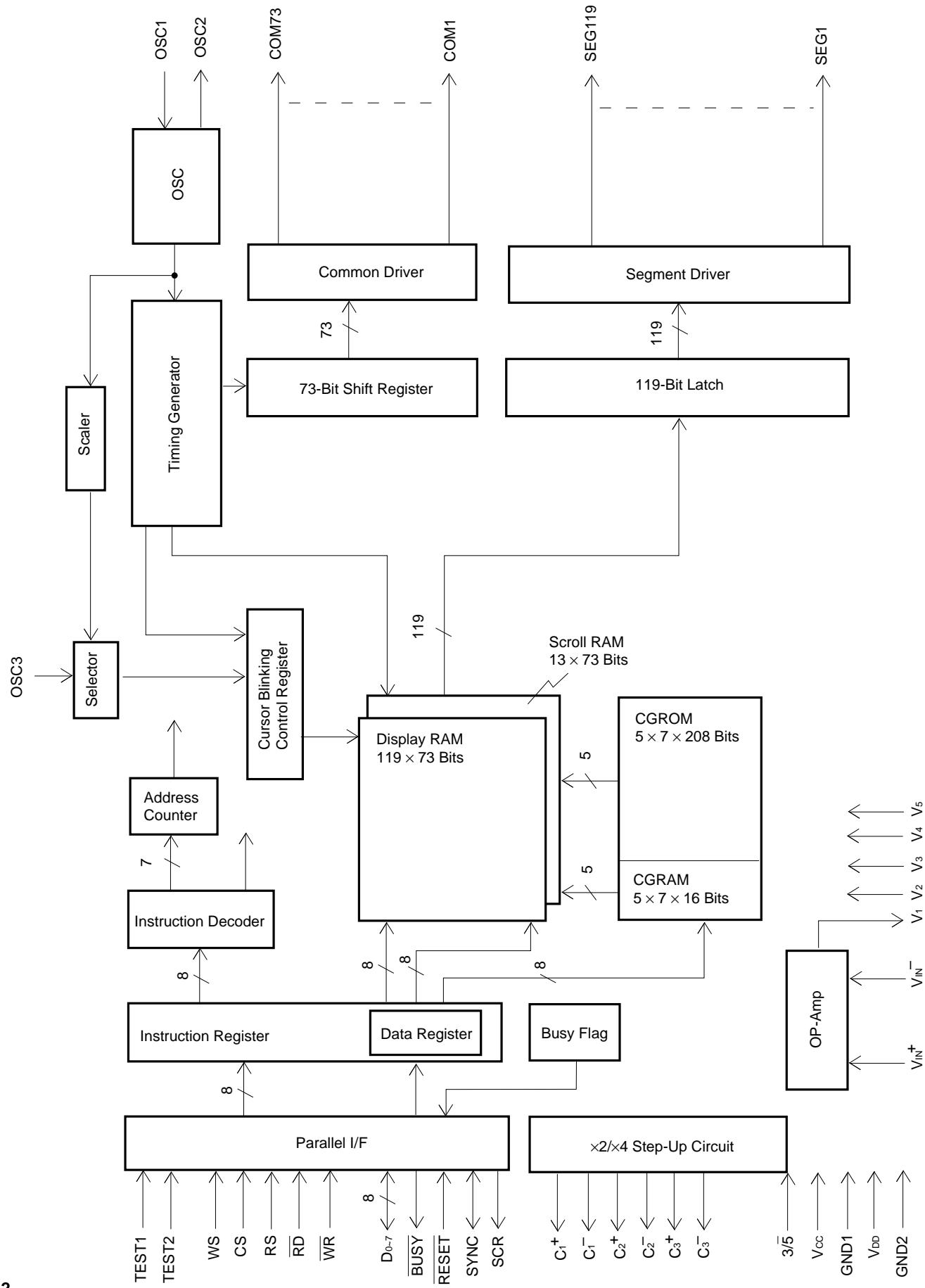

The  $\mu$ PD16435 and 16435A are controllers/drivers for a  $119 \times 73$ -dot LCD, and perform LCD full-dot and character composite display by means of control by a microprocessor that has a 4 or 8-bit data bus. A charge pump type DC/DC converter is also incorporated, enabling 3 or 5 V single power supply drive.

The  $\mu$ PD16435 uses an external reference clock. The  $\mu$ PD16435A has the on-chip oscillation circuit (external crystal resonator).

**FEATURES**

- Can interface to 4 or 8-bit CPU.

- Incorporates 119 segment outputs and 73 common outputs.

(Display duty selectable from 1/35, 1/37, 1/71, 1/73)

- $5 \times 7$  character font 208 character data configuration character generation ROM and 16 character data configuration character generation RAM, allowing composite full-dot and character display

- Incorporates extended display functions such as magnification, lateral scrolling, blink, reverse, etc.

- Operating voltage: 2.7 V to 5.5 V

- On-chip DC/DC converter: Selectable between  $\times 4$  set-up circuit and  $\times 2$  step-up circuit

- On-chip temperature correction circuit

- Master/slave operation capability

- On-chip power-on reset circuit

- On-chip oscillation circuit ( $\mu$ PD16435A)

- 232-pin TCP (Tape Carried Package)

**ORDERING INFORMATION**

| Part Number             | Package                                                          |

|-------------------------|------------------------------------------------------------------|

| $\mu$ PD16435N-001-xxx  | TCP (TAB), Standard ROM code                                     |

| $\mu$ PD16435N-001-001  | Standard quad TCP (Conforms to EIAJ), Standard ROM code          |

| $\mu$ PD16435N-001-002  | Standard dual TCP (Output OLB: 0.25 mm pitch), Standard ROM code |

| $\mu$ PD16435AN-001-xxx | TCP (TAB), Standard ROM code                                     |

| $\mu$ PD16435AN-001-001 | Standard quad TCP (Conforms to EIAJ), Standard ROM code          |

| $\mu$ PD16435AN-001-052 | Standard dual TCP (Output OLB: 0.25 mm pitch), Standard ROM code |

**Explanation of Part Number** $\mu$ PD16435 (A) N-xxx-xxx

The TCP model is a custom model. For details, consult NEC sales representative.

## BLOCK DIAGRAM

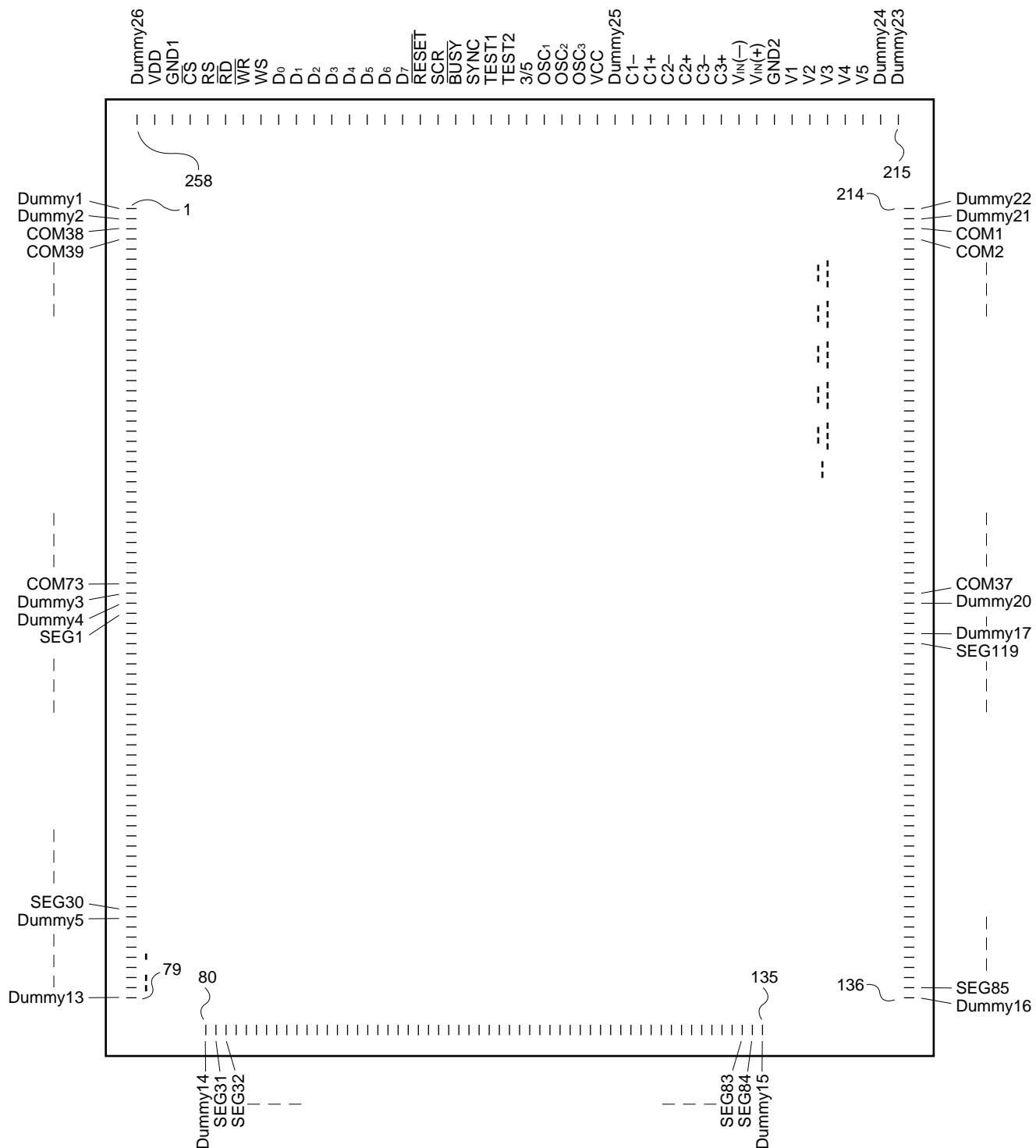

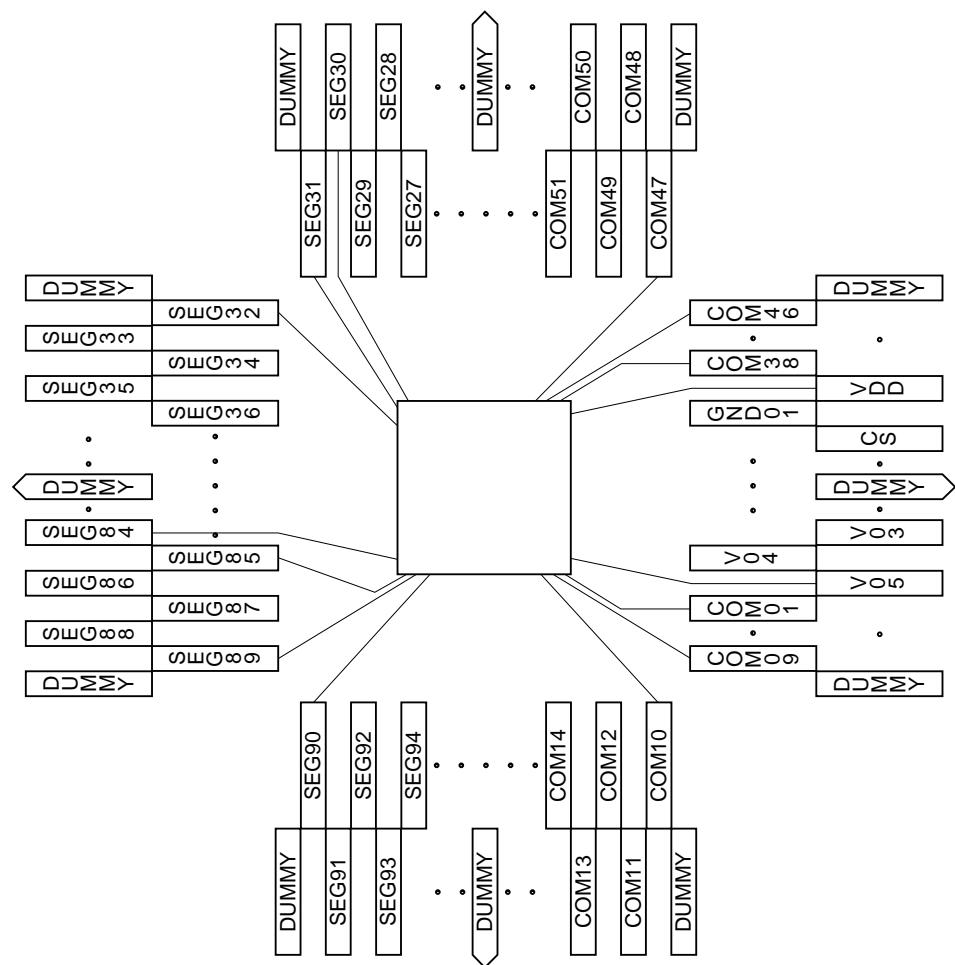

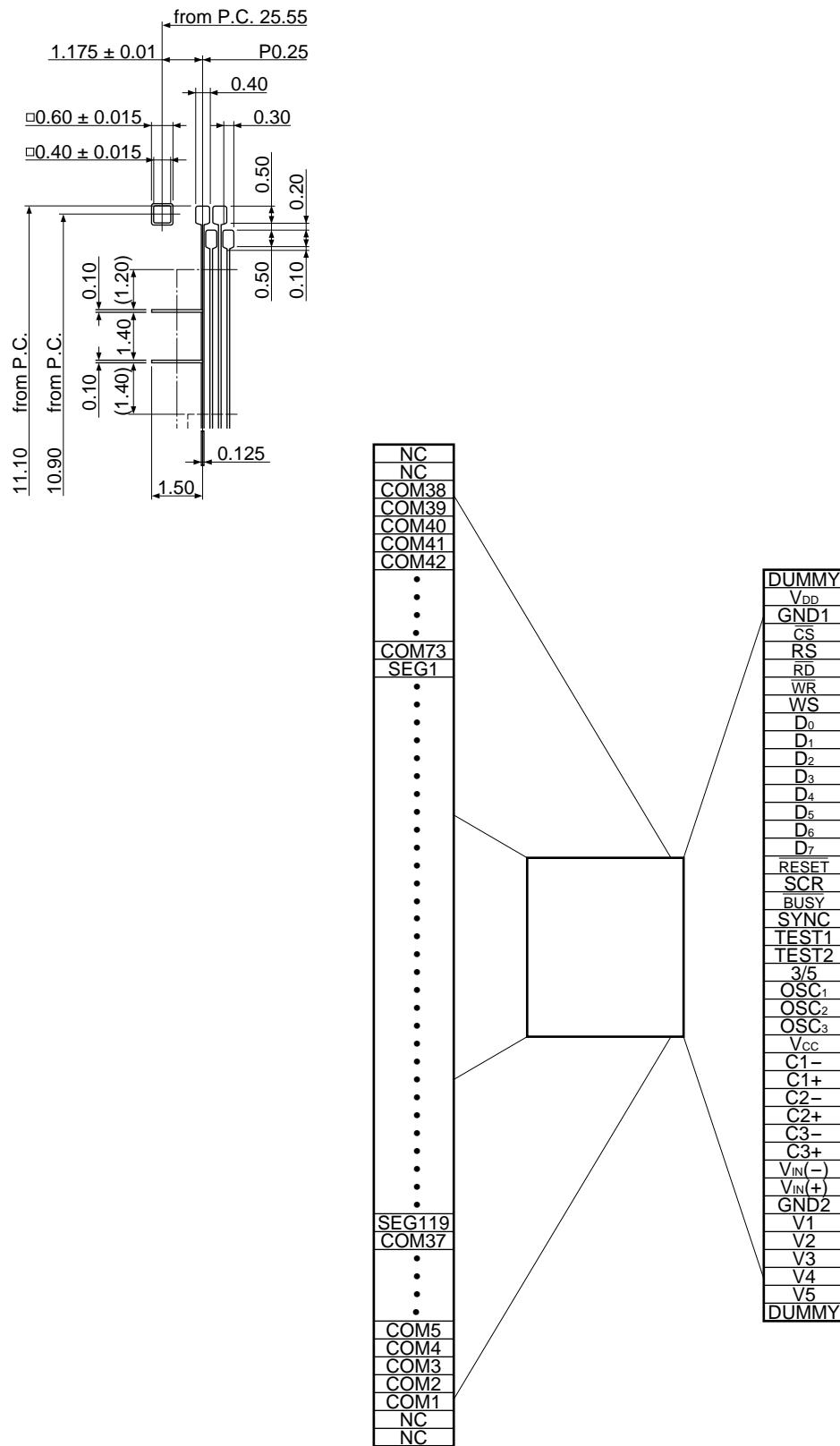

## PIN CONFIGURATION (CHIP)

## PIN DESCRIPTIONS

| Pin Name                             | Pin No.                             | Input/Output    | Output Type    | Description                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------|-------------------------------------|-----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>CS</u>                            | 255                                 | Input           | —              | Chip select signal                                                                                                                                                                                                                                                                                                                                       |

| RS                                   | 254                                 | Input           | —              | Register selection signal (specifies address register when "0", control register when "1").                                                                                                                                                                                                                                                              |

| <u>RD</u>                            | 253                                 | Input (Schmitt) | —              | Read enable signal. Reads write address when scrolling. Active edge is falling edge.                                                                                                                                                                                                                                                                     |

| <u>WR</u>                            | 252                                 | Input (Schmitt) | —              | Write enable signal. Active edge is falling edge.                                                                                                                                                                                                                                                                                                        |

| WS                                   | 251                                 | Input           | —              | Word length selection signal (4-bit input when "1", 8-bit input when "0").                                                                                                                                                                                                                                                                               |

| D <sub>0</sub> to D <sub>7</sub>     | 250 to 243                          | Input/output    | CMOS 3-state   | Transmit/receive data (3-state bidirectional)<br>Upper → D <sub>4</sub> to D <sub>7</sub><br>Lower → D <sub>0</sub> to D <sub>3</sub> (These pins should be set as unused in case of 4-bit data).<br>In test mode, these pins are output pins.<br>In a 4-bit transfer, storage is performed in the upper (MSB) in order from the data transferred first. |

| <u>BUSY</u>                          | 240                                 | Output          | Nch open-drain | "0" indicates busy state.                                                                                                                                                                                                                                                                                                                                |

| <u>RESET</u>                         | 242                                 | Input           | —              | "0" → Initialization of all internal registers and commands is performed. Output is fixed at V <sub>1</sub> .                                                                                                                                                                                                                                            |

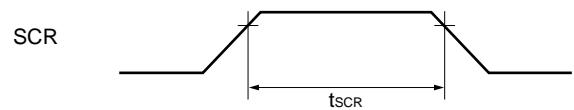

| SCR                                  | 241                                 | Output          | CMOS           | Signal is output to CPU on completion of one-character scroll.                                                                                                                                                                                                                                                                                           |

| SYNC                                 | 239                                 | Input/output    | Nch open-drain | Synchronization signal input/output pins for master/slave operation.                                                                                                                                                                                                                                                                                     |

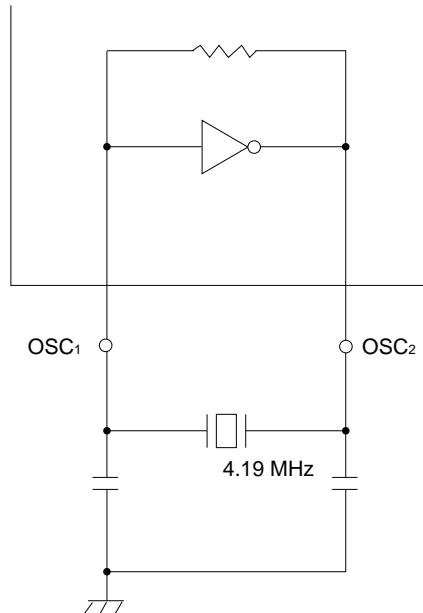

| OSC <sub>1</sub><br>OSC <sub>2</sub> | 235<br>234                          | —               | —              | μPD16435: Input the 4.19 MHz reference clock to the OSC <sub>1</sub> pin externally. Leave the OSC <sub>2</sub> pin open. (Always outputs high level.)<br>μPD16435A: This is the pin to which the 4.19 MHz crystal resonator is connected. Input the external clock to OSC <sub>1</sub> first.                                                           |

| OSC <sub>3</sub>                     | 233                                 | Input (Schmitt) | —              | 2 Hz external clock input pin. Scaled by 2 internally to generate 1 Hz, used as blink synchronization signal.                                                                                                                                                                                                                                            |

| COM1 to COM73                        | 212 to 176<br>3 to 38               | Output          | Analog switch  | Common output signals                                                                                                                                                                                                                                                                                                                                    |

| SEG1 to SEG119                       | 41 to 70<br>81 to 134<br>137 to 171 | Output          | Analog switch  | Segment output signals                                                                                                                                                                                                                                                                                                                                   |

| TEST1<br>TEST2                       | 238<br>237                          | Output          | —              | "1" → Test mode<br>"0" or open → Normal operating mode                                                                                                                                                                                                                                                                                                   |

| Pin Name                                | Pin No.    | Input/Output | Output Type | Description                                                                                                                                           |

|-----------------------------------------|------------|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

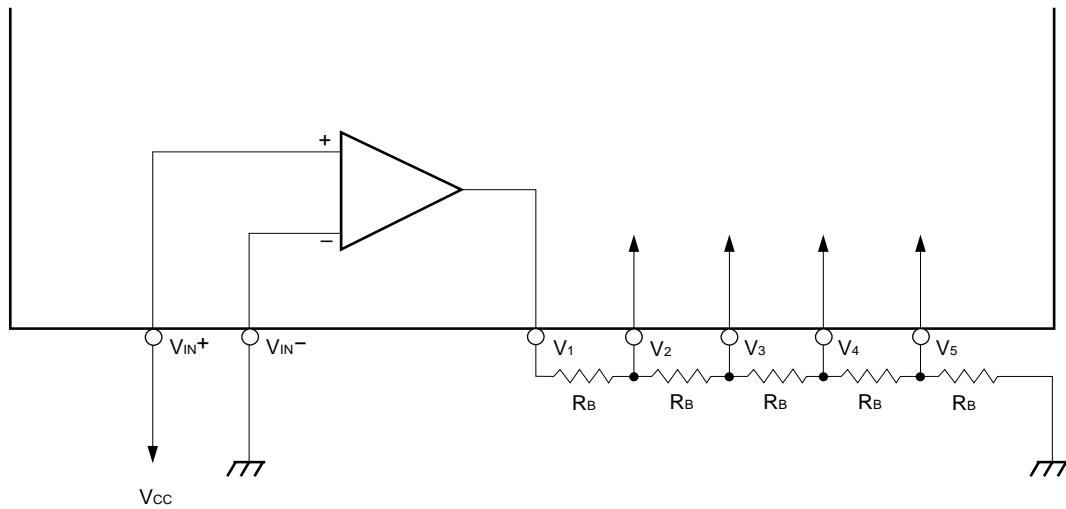

| V1                                      | 221        | Output       | —           | LCD drive power supply pin<br>Internal OP-amp output                                                                                                  |

| V2 to V5                                | 220 to 217 | Input        | —           | LCD drive power supply pins<br>Can be adjusted by addition of external resistor.                                                                      |

| V <sub>IN</sub> (-) V <sub>IN</sub> (+) | 224 223    | Input        | —           | Liquid crystal drive power supply OP-amp input pins                                                                                                   |

| V <sub>CC</sub> , GND1                  | 232, 256   | —            | —           | Logic power supply, GND                                                                                                                               |

| V <sub>DD</sub> , GND2                  | 257, 222   | —            | —           | Liquid crystal drive (step-up) power supply, GND                                                                                                      |

| 3/5                                     | 236        | Input        | —           | Drive voltage selection pin<br>"1" → V <sub>DD</sub> = 3 V (x4 step-up circuit selected)<br>"0" → V <sub>DD</sub> = 5 V (x2 step-up circuit selected) |

| C1±, C2±, C3±                           | 230 to 225 | —            | —           | A 1 μF tantalum or ceramic capacitor should be connected externally.                                                                                  |

## REFERENCE CLOCK

| Product Name | Reference Clock                                          |

|--------------|----------------------------------------------------------|

| μPD16435     | External input                                           |

| μPD16435A    | On-chip oscillation circuit (External crystal resonator) |

## OSC CIRCUIT (μPD16435A)

## REGISTER FUNCTIONS

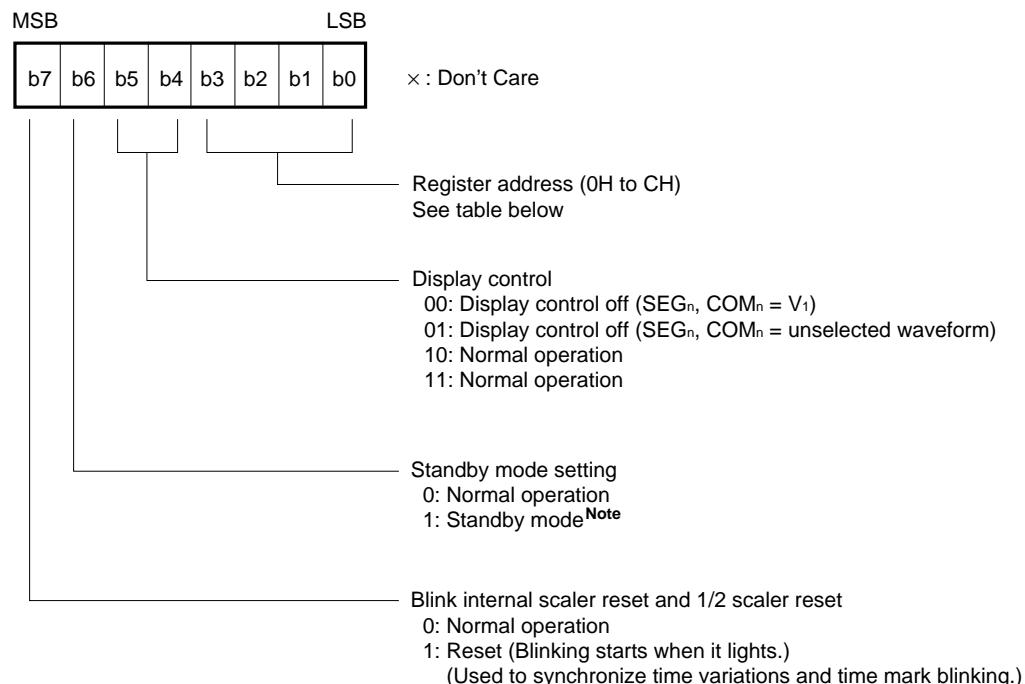

## (1) Address Register

Sets the address of each register, and also sets display control, standby mode, and scaler resetting.

**Note** Standby mode = { DC/DC converter stopped

OSC<sub>1</sub> input invalid (μPD16435)

OSC stopped (μPD16435A)

SEG<sub>n</sub>, COM<sub>n</sub> = V<sub>1</sub>

Data write/read prohibited

After powering on

## Register address list

| Address |    |    |    | Register Name                         |

|---------|----|----|----|---------------------------------------|

| b3      | b2 | b1 | b0 |                                       |

| 0       | 0  | 0  | 0  | Full-dot X address register           |

| 0       | 0  | 0  | 1  | Full-dot Y address register           |

| 0       | 0  | 1  | 0  | Full-dot data register                |

| 0       | 0  | 1  | 1  | Character X address register          |

| 0       | 1  | 0  | 0  | Character Y address register          |

| 0       | 1  | 0  | 1  | Character data register               |

| 0       | 1  | 1  | 0  | CGRAM address register                |

| 0       | 1  | 1  | 1  | CGRAM data register                   |

| 1       | 0  | 0  | 0  | Extension register                    |

| 1       | 0  | 0  | 1  | Extension register X address register |

| 1       | 0  | 1  | 0  | Extension register Y address register |

| 1       | 0  | 1  | 1  | Scroll register                       |

| 1       | 1  | 0  | 0  | Control register                      |

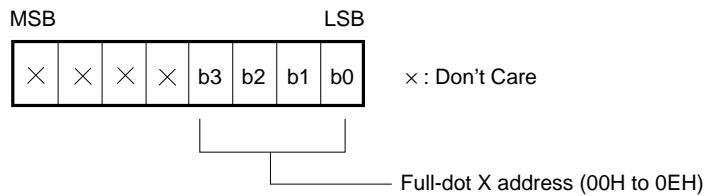

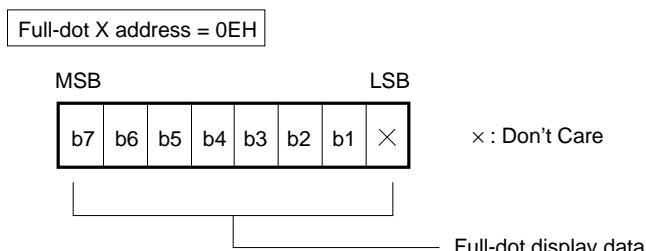

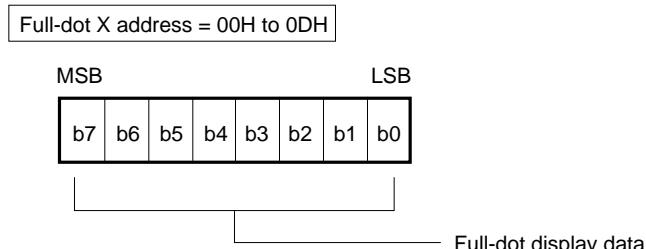

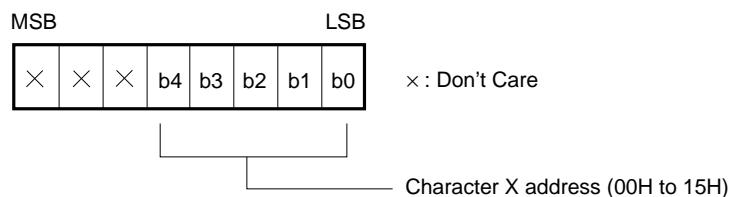

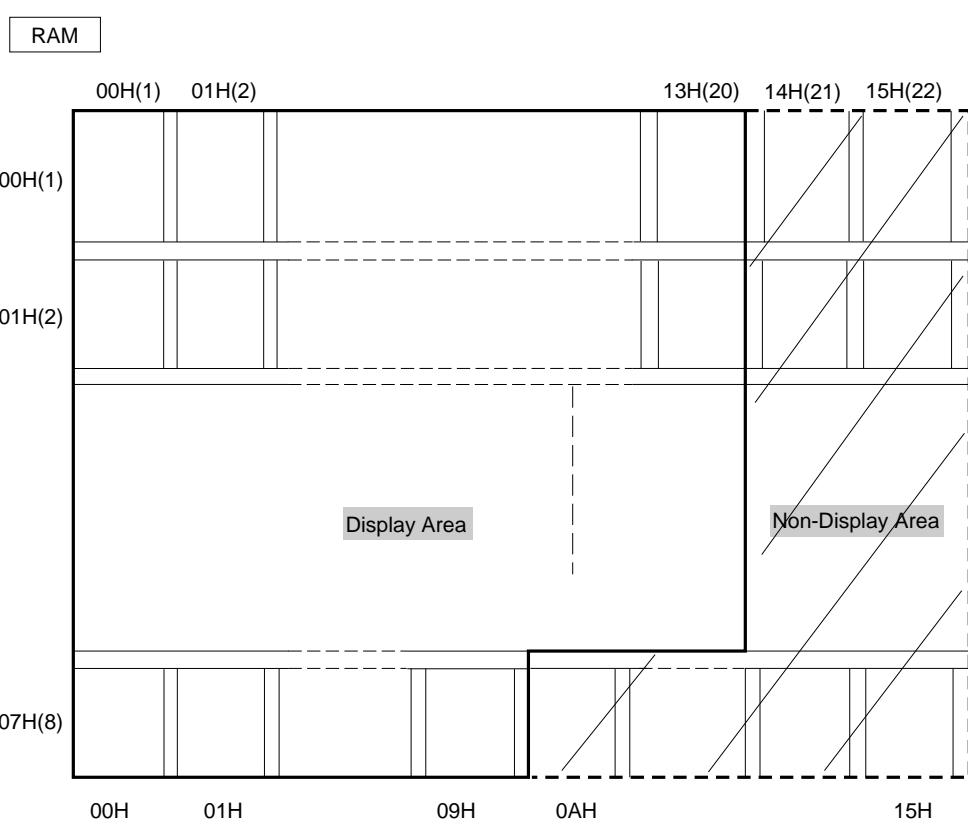

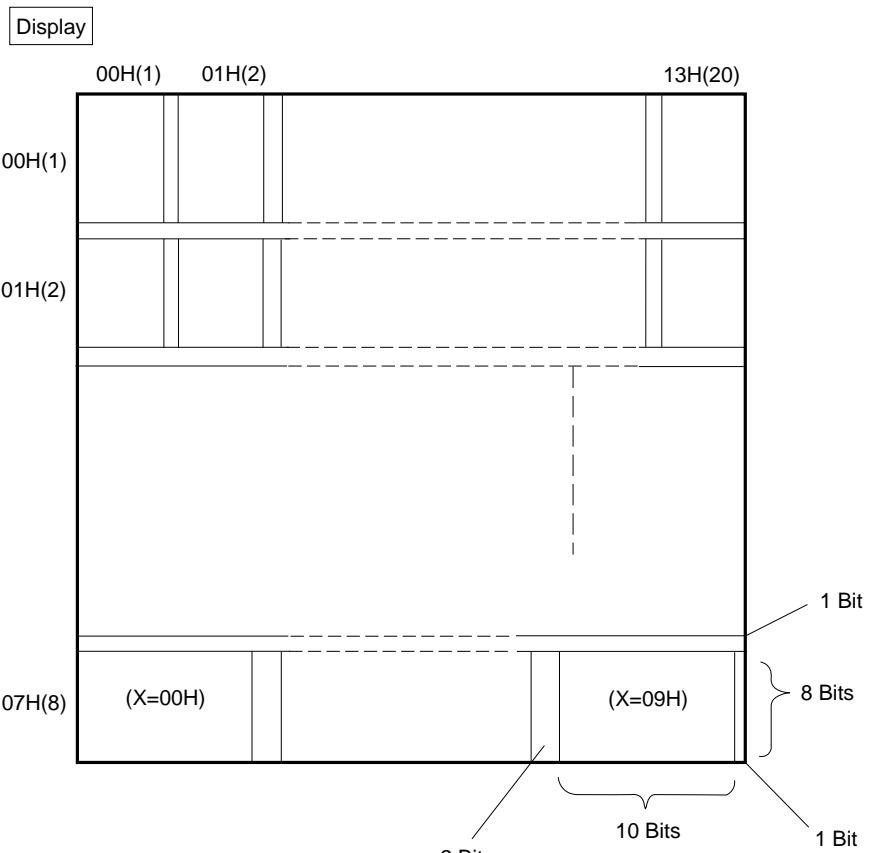

## (2) Full-Dot X Address Register (Register Address = 0000B)

Performs full-dot display, display screen X (segment) direction address setting. As scrolling is not possible with a full-dot display, addresses are not allocated to the scroll RAM area.

After powering on: Undefined

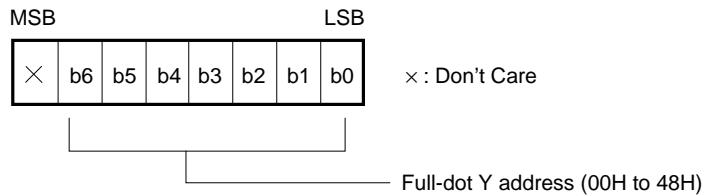

### (3) Full-Dot Y Address Register (Register Address = 0001B)

Performs full-dot display, display screen Y (common) direction address setting.

After powering on: Undefined

#### (4) Full-Dot Data Register (Register Address = 0010B)

Inputs full-dot display data. Display data is stored in the display memory with the MSB on the left, and display data “1” corresponds to illumination.

After powering on: Undefined

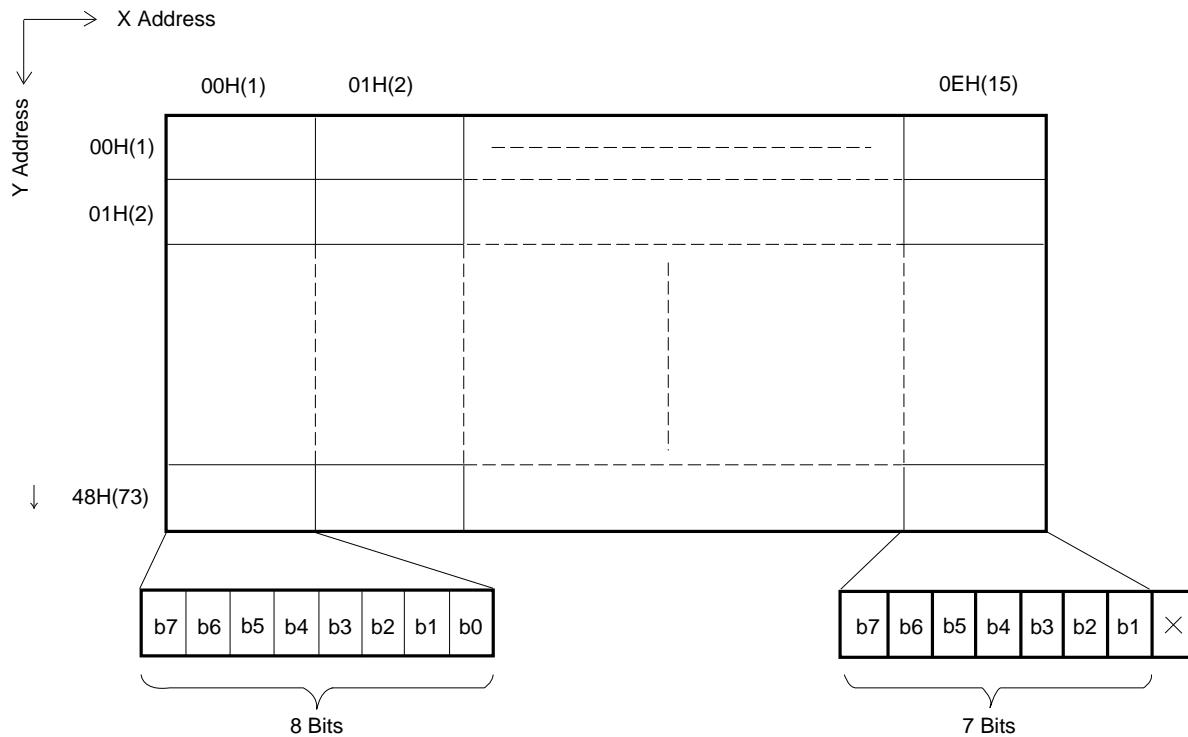

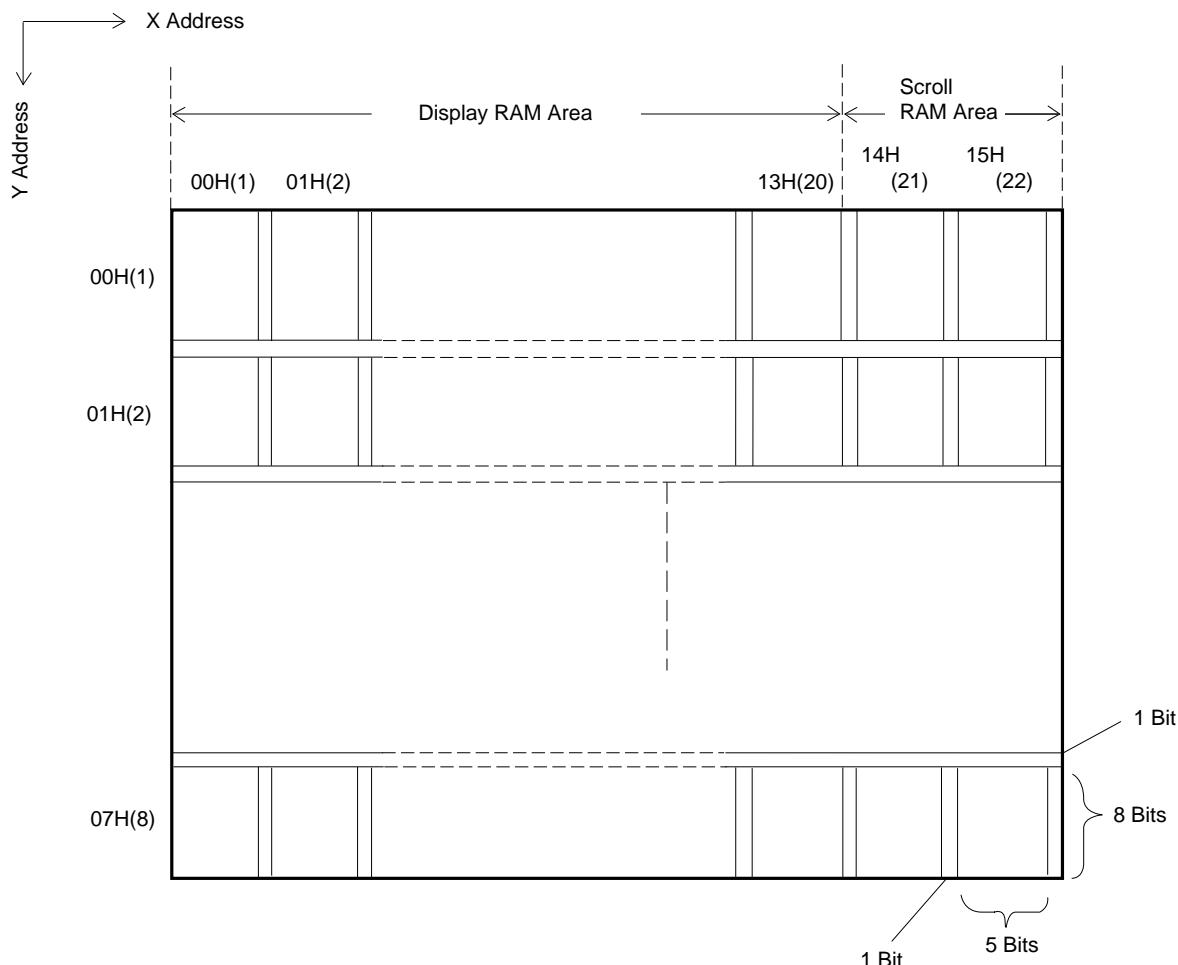

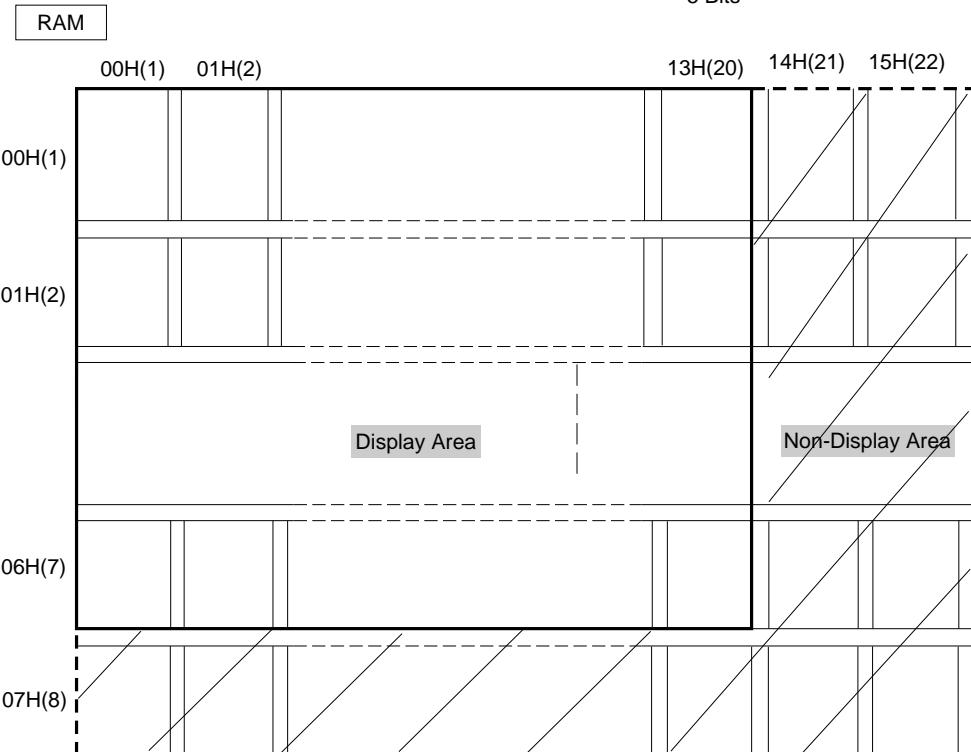

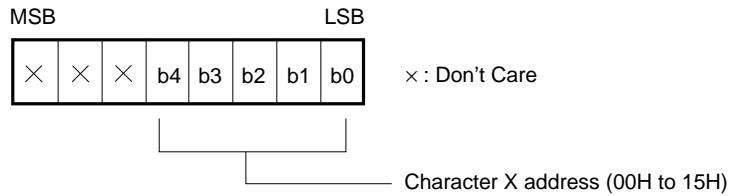

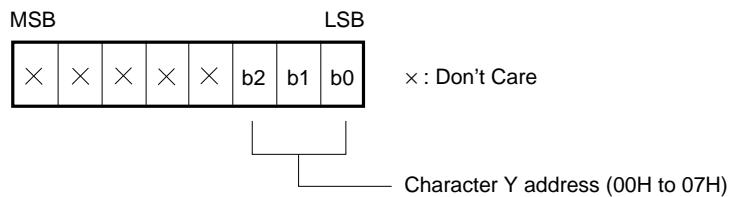

**Full-Dot X Address and Y Address Allocation****(5) Character X Address Register (Register Address = 0011B)**

Performs character display display, screen X (segment) direction address setting. X addresses include the scroll RAM area.

After powering on: Undefined

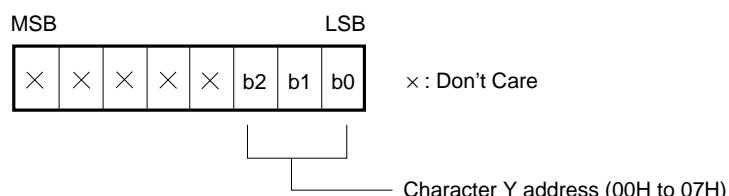

**(6) Character Y Address Register (Register Address = 0100B)**

Performs character display display, screen Y (common) direction address setting.

After powering on: Undefined

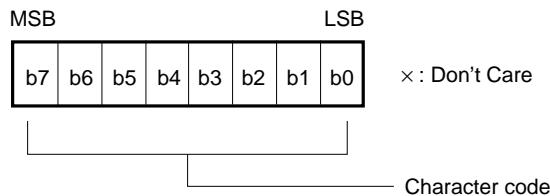

#### (7) Character Data Register (Register Address = 0101B)

The character indicated in the character code table is displayed at the position indicated by the character X and Y address registers.

After powering on: Undefined

## Character X Address and Y Address Allocation

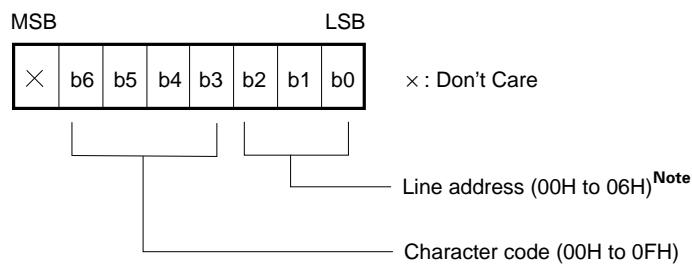

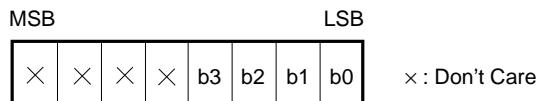

**(8) CGRAM Address Register (Register Address = 0110B)**

Performs address setting when display data is written to CGRAM. Bits b6 to b3 of the CGRAM address indicate the character code, and bits b2 to b0 indicate the character line.

**Note** If auto increment is set with the control register, 06H is followed by 07H. Dummy data should be sent when the address is 07H.

Example: (CGRAM address with auto increment)

--- → 15H → 16H → 17H → 18H → ---

After powering on: Undefined

**(9) CGRAM Data Register (Register Address = 0111B)**

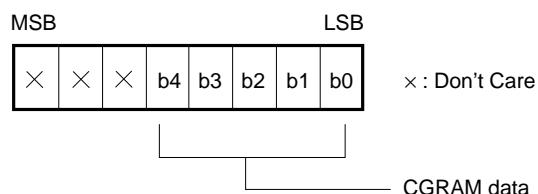

CGRAM display data. The lower 5 bits of the write data are valid.

After powering on: Undefined

**(10) Extension Register (Register Address = 1000B)**

Performs magnification, reverse, cursor, and time mark setting.

**In case of magnification setting**

- 00: Standard

- 01:  $\times 2$  horizontal

- 10:  $\times 2$  vertical

- 11:  $\times 4$  magnification ( $\times 2$  horizontal & vertical)

Magnification display is performed at any line position; characters of different sizes cannot be displayed on the same line.

Line specification magnification display is possible by setting an extension Y address after this command, and multiple-line magnification display is possible by setting consecutive extension Y address.

**In case of reverse setting**

- 00: Reverse cancellation (line specification)

- 01: Reverse (line specification)

- 10: Reverse cancellation (full screen)

- 11: Reverse (full screen)

Line specification reverse display is possible by setting an extension Y address after this command, and multiple-line reverse display is possible by setting consecutive extension Y addresses.

Regarding the reverse display Y address direction, a total of 9 dots (7 character part dots + 1 cursor part dot + 1 top space dot) are reversed.

In the case of  $\times 2$  vertical magnification or  $\times 4$  magnification, a total of 18 dots (14 character part dots + 2 cursor part dots + 2 top space dots) are reversed.

**In case of cursor setting**

- 00: Cursor non-display

- 01: Cursor display (blinking stopped)

- 10: Cursor display (blink operation)

- 11: Don't Care

Blinking display can be performed at any address by specifying an extension X and Y address after this command. The specification is for one address only.

The address specification should be performed in the order: X address → Y address.

**In case of character blink setting**

- X0: Blinking stopped

- X1: Blink operation

Blinking can be performed at any address by specifying an extension X and Y address after this command. The specification is for one address only.

The address specification should be performed in the order: X address → Y address.

**Extension function setting**

- 00: Magnification setting

- 01: Reverse setting

- 10: Cursor setting

- 11: Character blink setting

After powering on

### Display and RAM Allocation in Case of Magnification Setting

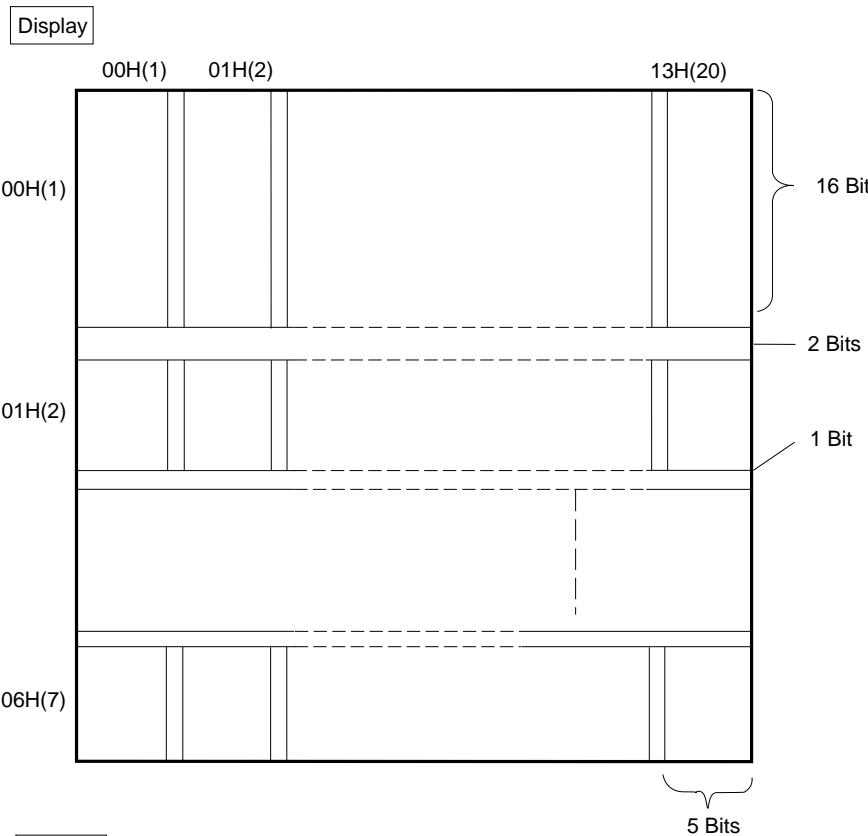

(1) Example of  $\times 2$  horizontal magnification (line 07H specified)

**Note** Lines 0AH to 15H for which  $\times 2$  horizontal magnification is specified can be used as scroll RAM.

(2) Example of  $\times 2$  vertical magnification (line 00H specified)

**Note** If  $\times 2$  vertical magnification is specified for line 07H, the lower half will be outside the display area. Also, if  $\times 2$  vertical magnification is specified for line 06H, the bottom dot will be a space.

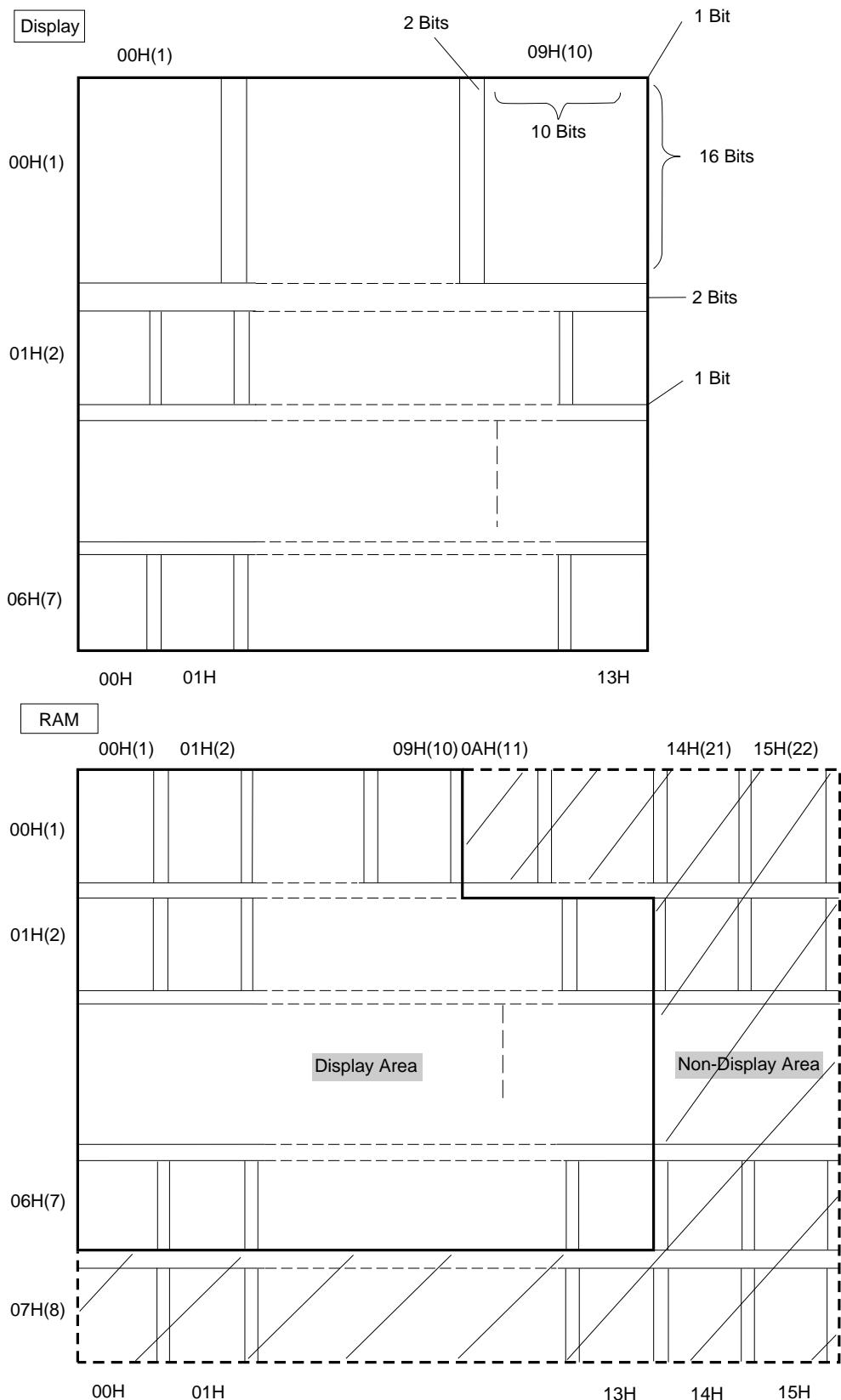

(3) Example of  $\times 4$  magnification (line 00H specified)

**Note** Lines 0AH to 15H for which  $\times 4$  magnification is specified can be used as scroll RAM.

If  $\times 4$  magnification is specified for line 07H, the lower half will be outside the display area, and if  $\times 4$  magnification is specified for line 06H, the bottom dot will be a space.

### (11) Extension X Address Register (Register Address = 1001B)

Performs extension display, display screen X (segment) direction address setting. X addresses include the scroll RAM area. This register must be executed before the extension Y address register.

After powering on: Undefined

## (12) Extension Y Address Register (Register Address = 1010B)

Performs extension display, display screen Y (common) direction address setting. This register must be executed after the X address.

After powering on: Undefined

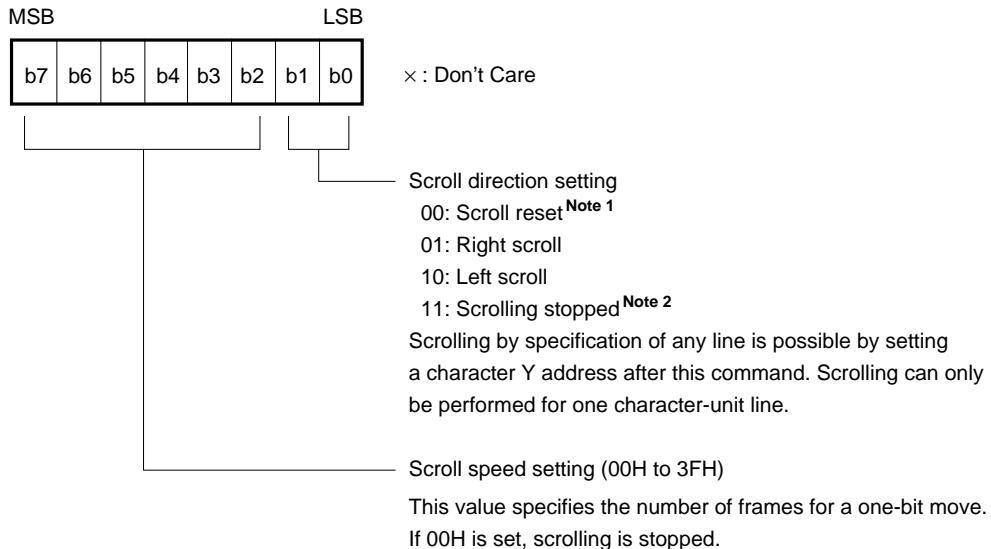

### (13) Scroll Register (Register Address = 1011B)

Performs scroll setting.

**Notes**

- 1. When scroll reset is executed, the screen leftmost character X address returns to 00H, and scrolling is stopped.

- 2. After scrolling has been stopped, character Y address setting is necessary when scrolling is restarted. It is not possible to set a different address from the character Y address before scrolling was stopped.

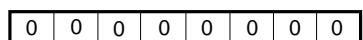

After powering on

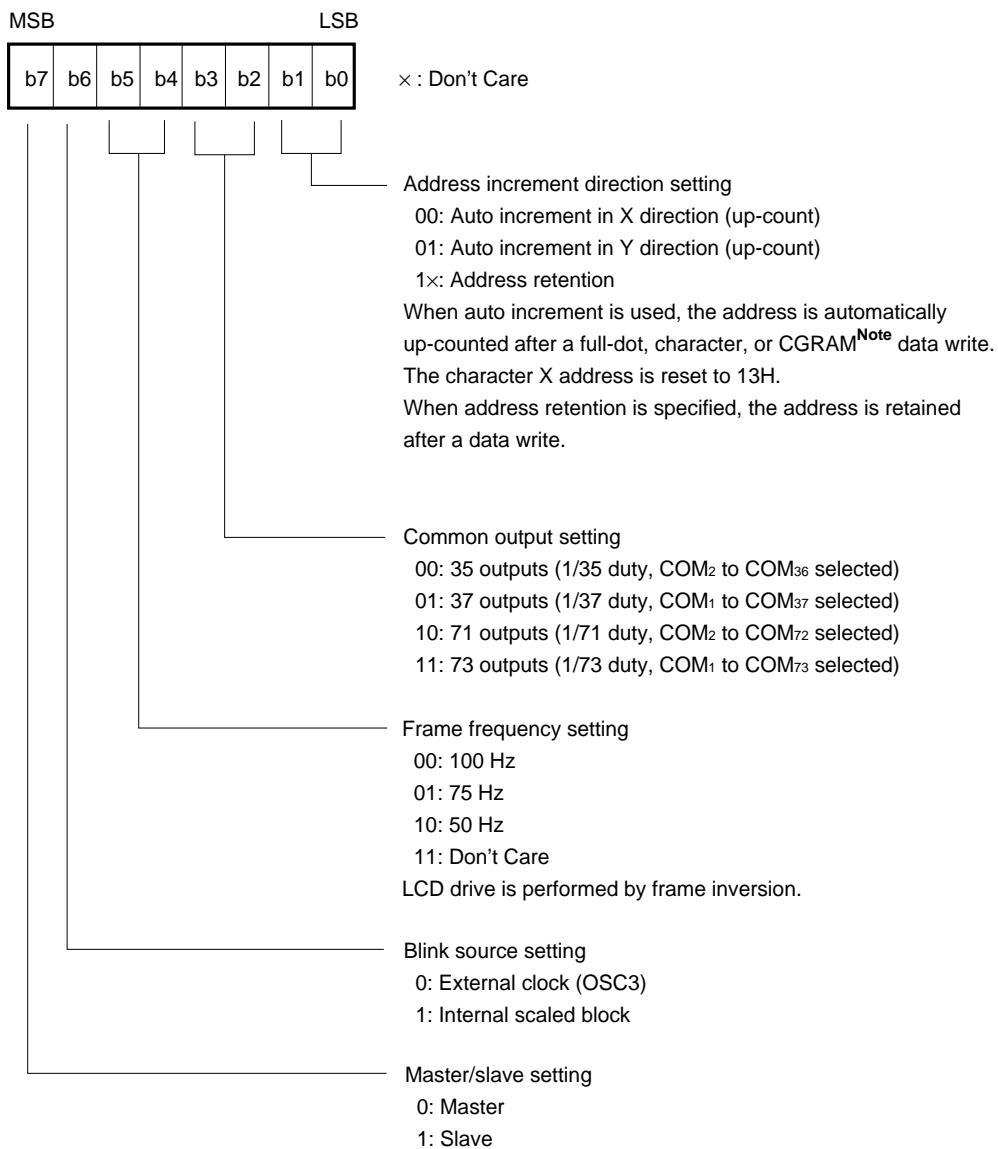

#### **(14) Control Register (Register Address = 1100B)**

Performs address increment direction, common output, frame frequency, blinking, and master/slave setting.

**Note** CGRAM is incremented in the Y direction even if 00H is set.

After powering on

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|

## Standard ROM Code (001)

| Higher Bit<br>Lower 4 Bits<br>Bit 4 Bits | 0000             | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

|------------------------------------------|------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| xxxx0000                                 | CC<br>RAM<br>(1) | Δ    |      | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx0001                                 | (2)              | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx0010                                 | (3)              | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx0011                                 | (4)              | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx0100                                 | (5)              | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx0101                                 | (6)              | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx0110                                 | (7)              | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx0111                                 | (8)              | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx1000                                 | (9)              | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx1001                                 | (10)             | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx1010                                 | (11)             | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx1011                                 | (12)             | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx1100                                 | (13)             | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx1101                                 | (14)             | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx1110                                 | (15)             | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

| xxxx1111                                 | (16)             | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    | Δ    |

**ABSOLUTE MAXIMUM RATINGS (T<sub>A</sub> = 25 °C, GND1 = GND2 = 0 V)**

| Parameter                               | Symbol                                   | Rating                        | Unit |

|-----------------------------------------|------------------------------------------|-------------------------------|------|

| Supply voltage 1 (3/5 = L)              | V <sub>CC1</sub>                         | −0.3 to +7.0                  | V    |

| Supply voltage 2 (3/5 = H)              | V <sub>CC2</sub>                         | −0.3 to +4.0                  | V    |

| Logic input voltage                     | V <sub>IN</sub>                          | −0.3 to V <sub>CC</sub> +0.3  | V    |

| Logic output voltage                    | V <sub>OUT1</sub>                        | −0.3 to V <sub>CC</sub> +0.3  | V    |

| LCD drive power supply voltage          | V <sub>DD</sub>                          | V <sub>CC</sub> −0.3 to +16.0 | V    |

| LCD drive power supply input voltage    | V <sub>2</sub> to V <sub>5</sub>         | −0.3 to V <sub>DD</sub> +0.3  | V    |

| LCD drive power supply output voltage   | V <sub>1</sub>                           | −0.3 to V <sub>DD</sub> +0.3  | V    |

| Amplifier input voltage                 | V <sub>IN</sub> (+), V <sub>IN</sub> (−) | −0.3 to V <sub>DD</sub> +0.3  | V    |

| Driver output voltage (Segment, common) | V <sub>OUT2</sub>                        | −0.3 to V <sub>DD</sub> +0.3  | V    |

| Storage temperature range               | T <sub>stg.</sub>                        | −55 to +150                   | °C   |

**RECOMMENDED OPERATING RANGES**

| Parameter                             | Symbol                           | MIN.            | TYP. | MAX.            | Unit |

|---------------------------------------|----------------------------------|-----------------|------|-----------------|------|

| Supply voltage 1 (3/5 = L)            | V <sub>CC1</sub>                 | 4.5             | 5.0  | 5.5             | V    |

| Supply voltage 2 (3/5 = H)            | V <sub>CC2</sub>                 | 2.7             | 3.0  | 3.6             | V    |

| LCD drive supply voltage              | V <sub>DD</sub>                  | V <sub>CC</sub> | 8.0  | 14.5            | V    |

| Logic input voltage                   | V <sub>IN</sub>                  | 0               |      | V <sub>CC</sub> | V    |

| LCD drive power supply input voltage  | V <sub>2</sub> to V <sub>5</sub> | 0               |      | V <sub>DD</sub> | V    |

| LCD drive power supply output voltage | V <sub>1</sub>                   | 0               |      | V <sub>DD</sub> | V    |

| External capacitance                  | C <sub>0</sub> to C <sub>3</sub> | 1               |      | 4.7             | μF   |

| Operating temperature range           | T <sub>A</sub>                   | −40             |      | +85             | °C   |

**ELECTRICAL SPECIFICATIONS** (Unless specified otherwise,  $T_A = -40$  to  $+85$  °C,  $C_0$  to  $C_3 = 1 \mu F$ ,  $V_{CC} = 5 V \pm 10\%$  :  $3/5 = L$  or  $V_{CC} = 2.7 V$  to  $3.6 V$  :  $3/5 = H$ )

| Parameter                                    | Symbol    | Test Conditions                                                                                                                                  | MIN.         | TYP. | MAX.        | Unit    |

|----------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------------|---------|

| Input voltage high                           | $V_{IH1}$ | Except Schmitt inputs                                                                                                                            | $0.7V_{CC}$  |      |             | V       |

| Input voltage low                            | $V_{IL1}$ | Except Schmitt inputs                                                                                                                            |              |      | $0.3V_{CC}$ | V       |

| Input voltage high                           | $V_{IH2}$ | Schmitt inputs                                                                                                                                   | $0.8V_{CC}$  |      |             | V       |

| Input voltage low                            | $V_{IL2}$ | Schmitt inputs                                                                                                                                   |              |      | $0.2V_{CC}$ | V       |

| Hysteresis voltage                           | $V_H$     | Schmitt inputs                                                                                                                                   | $0.05V_{CC}$ |      | $0.2V_{CC}$ | V       |

| Input current high                           | $I_{IH1}$ | $\overline{CS}, \overline{RS}, \overline{RD}, \overline{WR}, \overline{WS}, \overline{RESET}, 3/5, OSC_3, V_{IN}(+), V_{IN}(-), V_{IN} = V_{CC}$ |              |      | 1           | $\mu A$ |

| Input current low                            | $I_{IH1}$ | $\overline{CS}, \overline{RS}, \overline{RD}, \overline{WR}, \overline{WS}, \overline{RESET}, 3/5, OSC_3, V_{IN}(+), V_{IN}(-), V_{IN} = 0 V$    |              |      | -1          | $\mu A$ |

| Input current high                           | $I_{IH2}$ | TEST1, TEST2, $V_{IN} = V_{CC}$                                                                                                                  |              |      | 6           | mA      |

| Input current low                            | $I_{IL2}$ | TEST1, TEST2, $V_{IN} = 0 V$                                                                                                                     |              |      | -100        | $\mu A$ |

| Output voltage high                          | $V_{OH1}$ | $D_n, SCR, 3/5 = L$<br>$I_{OH} = -1 mA$                                                                                                          | $0.9V_{CC}$  |      |             | V       |

| Output voltage low                           | $V_{OL1}$ | $D_n, BUSY, SCR, SYNC, 3/5 = L$<br>$I_{OL} = 4 mA$                                                                                               |              |      | $0.1V_{CC}$ | V       |

| Output voltage high                          | $V_{OH2}$ | $D_n, SCK, 3/5 = H$<br>$I_{OH} = -0.6 mA$                                                                                                        | $0.9V_{CC}$  |      |             | V       |

| Output voltage low                           | $V_{OL2}$ | $D_n, BUSY, SCR, SYNC, 3/5 = H$<br>$I_{OL} = 2.4 mA$                                                                                             |              |      | $0.1V_{CC}$ | V       |

| Output voltage high                          | $V_{OH3}$ | $V_1$ pin<br>$I_{OH} = -1 mA$<br>$V_{IN}(+) = V_{DD}, V_{IN}(-) = 0 V$                                                                           | $0.9V_{CC}$  |      |             | V       |

| Output voltage low                           | $V_{OL3}$ | $V_1$ pin<br>$I_{OL} = -10 \mu A$<br>$V_{IN}(+) = 0 V, V_{IN}(-) = V_{DD}$                                                                       |              |      | $0.1V_{DD}$ | V       |

| Leak current high                            | $I_{LOH}$ | $D_n, SYNC, BUSY$<br>$V_{IN/OUT} = V_{CC}$                                                                                                       |              |      | 10          | $\mu A$ |

| Leak current low                             | $I_{LOL}$ | $D_n, SYNC, BUSY$<br>$V_{IN/OUT} = 0 V$                                                                                                          |              |      | -10         | $\mu A$ |

| Common output on-resistance                  | $R_{COM}$ | COM <sub>1</sub> to COM <sub>73</sub><br>$ I_o  = 100 \mu A$                                                                                     |              |      | 5           | kΩ      |

| Segment output on-resistance                 | $R_{SEG}$ | SEG <sub>1</sub> to SEG <sub>119</sub><br>$ I_o  = 100 \mu A$                                                                                    |              |      | 10          | kΩ      |

| Driver unit supply voltage (step-up voltage) | $V_{DD1}$ | $R_B = 10 k\Omega$<br>$3/5 = L$                                                                                                                  | $1.9V_{CC}$  |      | $2.0V_{CC}$ | V       |

| Driver unit supply voltage (step-up voltage) | $V_{DD2}$ | $R_B = 10 k\Omega$<br>$3/5 = H$                                                                                                                  | $3.6V_{CC}$  |      | $4.0V_{CC}$ | V       |

**ELECTRICAL SPECIFICATIONS** (Unless specified otherwise,  $T_A = -40$  to  $+85$  °C,  $C_0$  to  $C_3 = 1 \mu F$ ,  $V_{CC} = 5 V \pm 10\% : 3/\bar{5} = L$  or  $V_{CC} = 2.7 V$  to  $3.6 V : 3/\bar{5} = H$ )

| Parameter                                | Symbol           | Test Conditions                                                                                | MIN. | TYP. | MAX. | Unit |

|------------------------------------------|------------------|------------------------------------------------------------------------------------------------|------|------|------|------|

| Logic consumption current<br>(μPD16435)  | I <sub>CC1</sub> | $V_{CC} = 3.0 V$ , no load, $3/\bar{5}=H$<br>$f_{osc} = 4.19$ MHz                              |      | 0.35 | 1    | mA   |

|                                          | I <sub>CC2</sub> | $V_{CC} = 5.0 V$ , no load, $3/\bar{5}=L$<br>$f_{osc} = 4.19$ MHz                              |      | 0.35 | 1    | mA   |

|                                          | I <sub>CC3</sub> | $V_{CC} = 3.0 V$ , $3/\bar{5}=H$<br>$R_B = 10 k\Omega$ <sup>Note</sup><br>$f_{osc} = 4.19$ MHz |      | 1.3  | 2.5  | mA   |

|                                          | I <sub>CC4</sub> | $V_{CC} = 5.0 V$ , $3/\bar{5}=L$<br>$R_B = 10 k\Omega$ <sup>Note</sup><br>$f_{osc} = 4.19$ MHz |      | 0.75 | 1.5  | mA   |

| Logic consumption current<br>(μPD16435A) | I <sub>CC1</sub> | $V_{CC} = 3.0 V$ , no load, $3/\bar{5}=H$<br>$f_{osc} = 4.19$ MHz                              |      | 0.6  | 1.5  | mA   |

|                                          | I <sub>CC2</sub> | $V_{CC} = 5.0 V$ , no load, $3/\bar{5}=L$<br>$f_{osc} = 4.19$ MHz                              |      | 0.65 | 1.5  | mA   |

|                                          | I <sub>CC3</sub> | $V_{CC} = 3.0 V$ , $3/\bar{5}=H$<br>$R_B = 10 k\Omega$ <sup>Note</sup><br>$f_{osc} = 4.19$ MHz |      | 1.5  | 3    | mA   |

|                                          | I <sub>CC4</sub> | $V_{CC} = 5.0 V$ , $3/\bar{5}=L$<br>$R_B = 10 k\Omega$ <sup>Note</sup><br>$f_{osc} = 4.19$ MHz |      | 1.05 | 2    | mA   |

**Note** TYP. values are reference values for  $T_A = 25$  °C.

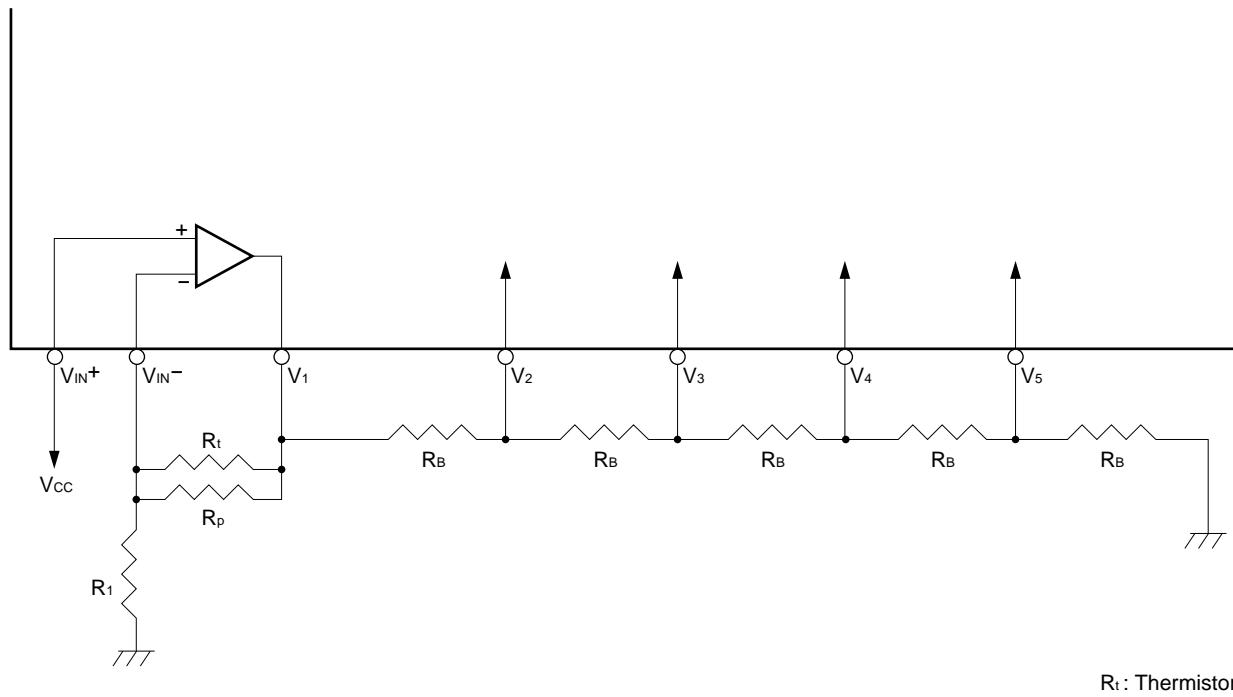

## NOTE MEASUREMENT CIRCUIT

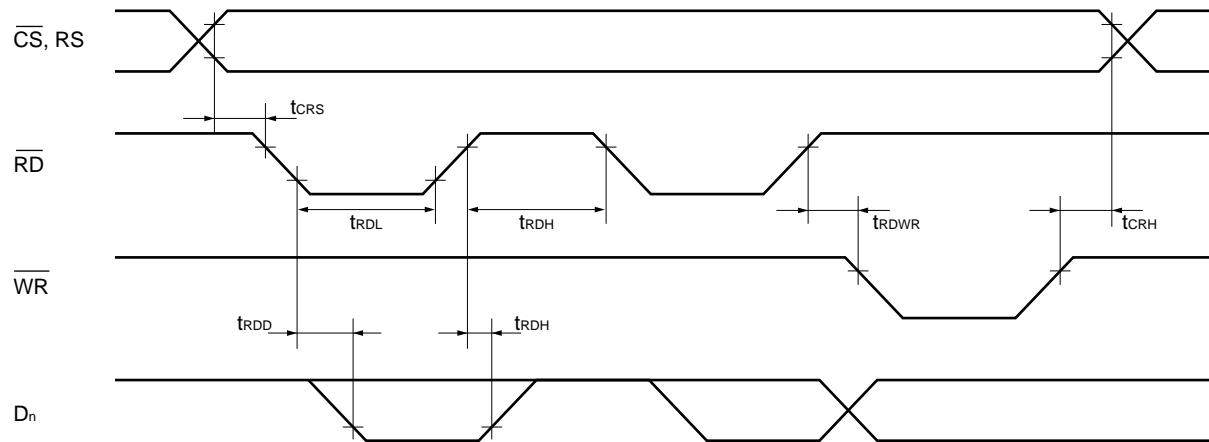

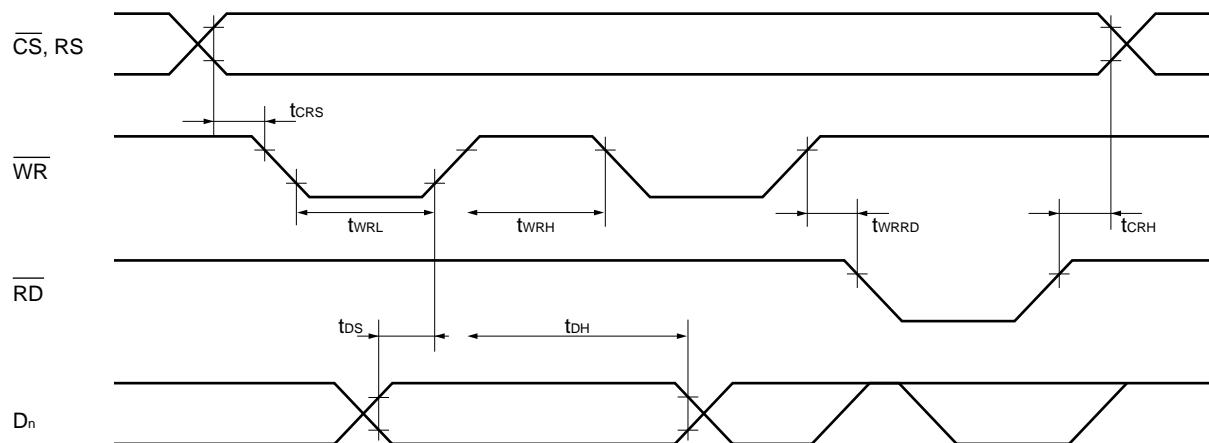

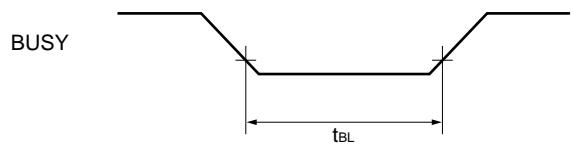

**SWITCHING SPECIFICATIONS** (Unless specified otherwise,  $T_A = -40$  to  $+85$  °C,  $C_0$  to  $C_3 = 1 \mu\text{F}$ ,  $V_{cc} = 5 \text{ V} \pm 10\%$ ,  $R_L = 5 \text{ k}\Omega$ ,  $C_L = 150 \text{ pF}$ )

| Parameter           | Symbol    | Test Conditions                            | MIN. | TYP. | MAX. | Unit                |

|---------------------|-----------|--------------------------------------------|------|------|------|---------------------|

| RD data delay time  | $t_{RDD}$ | $\overline{RD} \downarrow \rightarrow D_n$ |      |      | 150  | ns                  |

| RD data hold time   | $t_{RDH}$ | $\overline{RD} \uparrow \rightarrow D_n$   | 10   |      |      | ns                  |

| BUSY low-level time | $t_{BL}$  | When full-dot data is written              | 3    |      | 9    | CLK <sup>Note</sup> |

| BUSY low-level time | $t_{BL}$  | When character data is written             | 48   |      | 54   | CLK <sup>Note</sup> |

| SCR high-level time | $t_{SCR}$ |                                            | 100  |      | 550  | $\mu\text{s}$       |

**Note** CLK = 4/fosc

**REQUIRED TIMING CONDITIONS** (Unless specified otherwise,  $T_A = -40$  to  $+85$  °C,  $C_0$  to  $C_3 = 1 \mu F$ ,  $V_{CC} = 5 V \pm 10\%$ ,  $R_L = 5 k\Omega$ ,  $C_L = 150 pF$ )

| Parameter                            | Symbol     | Test Conditions                                                                               | MIN. | TYP. | MAX. | Unit |

|--------------------------------------|------------|-----------------------------------------------------------------------------------------------|------|------|------|------|

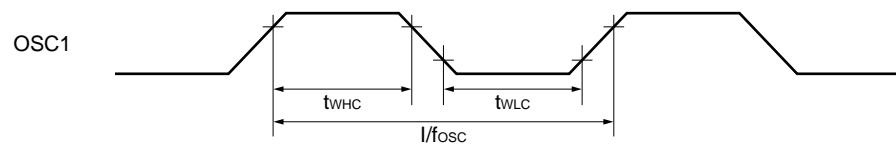

| Clock frequency                      | $f_{osc}$  | $\mu PD16435$ only                                                                            | 3.77 | 4.19 | 4.61 | MHz  |

| High-level clock pulse width         | $t_{WHC}$  | $\mu PD16435$ only                                                                            | 100  |      |      | ns   |

| Low-level clock pulse width          | $t_{WLC}$  | $\mu PD16435$ only                                                                            | 100  |      |      | ns   |

| $\overline{RD}$ high-level width     | $t_{RDH}$  |                                                                                               | 200  |      |      | ns   |

| $\overline{RD}$ low-level width      | $t_{RDL}$  |                                                                                               | 200  |      |      | ns   |

| $\overline{WR}$ high-level width     | $t_{WRH}$  |                                                                                               | 200  |      |      | ns   |

| $\overline{WR}$ low-level width      | $t_{WRL}$  |                                                                                               | 200  |      |      | ns   |

| $\overline{WR} - \overline{RD}$ time | $t_{WRRD}$ | $\overline{WR} \uparrow \rightarrow \overline{RD} \downarrow$                                 | 200  |      |      | ns   |

| $\overline{RD} - \overline{WR}$ time | $t_{RDWR}$ | $\overline{RD} \uparrow \rightarrow \overline{WR} \downarrow$                                 | 200  |      |      | ns   |

| $\overline{CS}$ , $RS$ setup time    | $t_{CRS}$  | $\overline{CS} \downarrow, RS \rightarrow \overline{WR} \downarrow, \overline{RD} \downarrow$ | 0    |      |      | ns   |

| $\overline{CS}$ , $RS$ hold time     | $t_{CRH}$  | $\overline{WR} \uparrow, \overline{RD} \uparrow \rightarrow \overline{CS} \uparrow, RS$       | 300  |      |      | ns   |

| Input data setup time                | $t_{DS}$   | $D_n \rightarrow \overline{WR} \uparrow$                                                      | 0    |      |      | ns   |

| Input data hold time                 | $t_{DH}$   | $\overline{WR} \uparrow \rightarrow D_n$                                                      | 200  |      |      | ns   |

**SWITCHING SPECIFICATIONS** (Unless specified otherwise,  $T_A = -40$  to  $+85$  °C,  $C_0$  to  $C_3 = 1 \mu F$ ,  $V_{CC} = 2.7$  to  $3.6 V$ ,  $R_L = 5 k\Omega$ ,  $C_L = 150 pF$ )

| Parameter                       | Symbol    | Test Conditions                            | MIN. | TYP. | MAX. | Unit         |

|---------------------------------|-----------|--------------------------------------------|------|------|------|--------------|

| $\overline{RD}$ data delay time | $t_{RDD}$ | $\overline{RD} \downarrow \rightarrow D_n$ |      |      | 500  | ns           |

| $\overline{RD}$ data hold time  | $t_{RDH}$ | $\overline{RD} \uparrow \rightarrow D_n$   | 15   |      |      | ns           |

| BUSY low-level time             | $t_{BL}$  | When full-dot data is written              | 3    |      | 9    | $CLK^{Note}$ |

| BUSY low-level time             | $t_{BL}$  | When character data is written             | 48   |      | 54   | $CLK^{Note}$ |

| SCR high-level time             | $t_{SCR}$ |                                            | 100  |      | 550  | $\mu s$      |

**Note**  $CLK = 4/f_{osc}$

**REQUIRED TIMING CONDITIONS** (Unless specified otherwise,  $T_A = -40$  to  $+85$  °C,  $C_0$  to  $C_3 = 1 \mu F$ ,  $V_{CC} = 2.7$  to  $3.6$  V,  $R_L = 5 k\Omega$ ,  $C_L = 150 pF$ )

| Parameter                            | Symbol     | Test Conditions                                                                                     | MIN. | TYP. | MAX. | Unit |

|--------------------------------------|------------|-----------------------------------------------------------------------------------------------------|------|------|------|------|

| Clock frequency                      | $f_{osc}$  | $\mu PD16435$ only                                                                                  | 3.77 | 4.19 | 4.61 | MHz  |

| High-level clock pulse width         | $t_{WHC}$  | $\mu PD16435$ only                                                                                  | 100  |      |      | ns   |

| Low-level clock pulse width          | $t_{WLC}$  | $\mu PD16435$ only                                                                                  | 100  |      |      | ns   |

| $\overline{RD}$ high-level width     | $t_{RDH}$  |                                                                                                     | 400  |      |      | ns   |

| $\overline{RD}$ low-level width      | $t_{RDL}$  |                                                                                                     | 400  |      |      | ns   |

| $\overline{WR}$ high-level width     | $t_{WRH}$  |                                                                                                     | 400  |      |      | ns   |

| $\overline{WR}$ low-level width      | $t_{WRL}$  |                                                                                                     | 400  |      |      | ns   |

| $\overline{WR} - \overline{RD}$ time | $t_{WRRD}$ | $\overline{WR} \uparrow \rightarrow \overline{RD} \downarrow$                                       | 400  |      |      | ns   |

| $\overline{RD} - \overline{WR}$ time | $t_{RDWR}$ | $\overline{RD} \uparrow \rightarrow \overline{WR} \downarrow$                                       | 400  |      |      | ns   |

| $\overline{CS}$ , RS setup time      | $t_{CRS}$  | $\overline{CS} \downarrow$ , RS $\rightarrow \overline{WR} \downarrow$ , $\overline{RD} \downarrow$ | 0    |      |      | ns   |

| $\overline{CS}$ , RS hold time       | $t_{CRH}$  | $\overline{WR} \uparrow$ , $\overline{RD} \uparrow \rightarrow \overline{CS} \uparrow$ , RS         | 600  |      |      | ns   |

| Input data setup time                | $t_{DS}$   | $D_n \rightarrow \overline{WR} \uparrow$                                                            | 0    |      |      | ns   |

| Input data hold time                 | $t_{DH}$   | $\overline{WR} \uparrow \rightarrow D_n$                                                            | 400  |      |      | ns   |

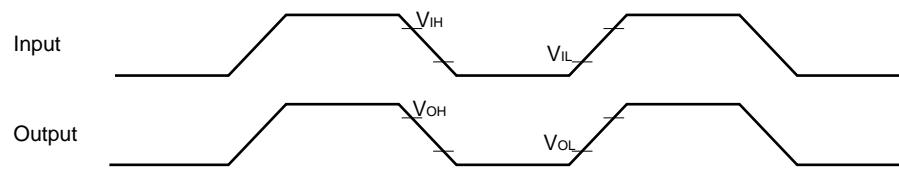

**AC TIMING TEST VOLTAGE****AC CHARACTERISTICS WAVEFORM****OSC****READ TIMING****WRITE TIMING**

**BUSY****SCR**

## EXAMPLE TEMPERATURE CORRECTION CIRCUIT CONNECTION

$R_t$ : Thermistor

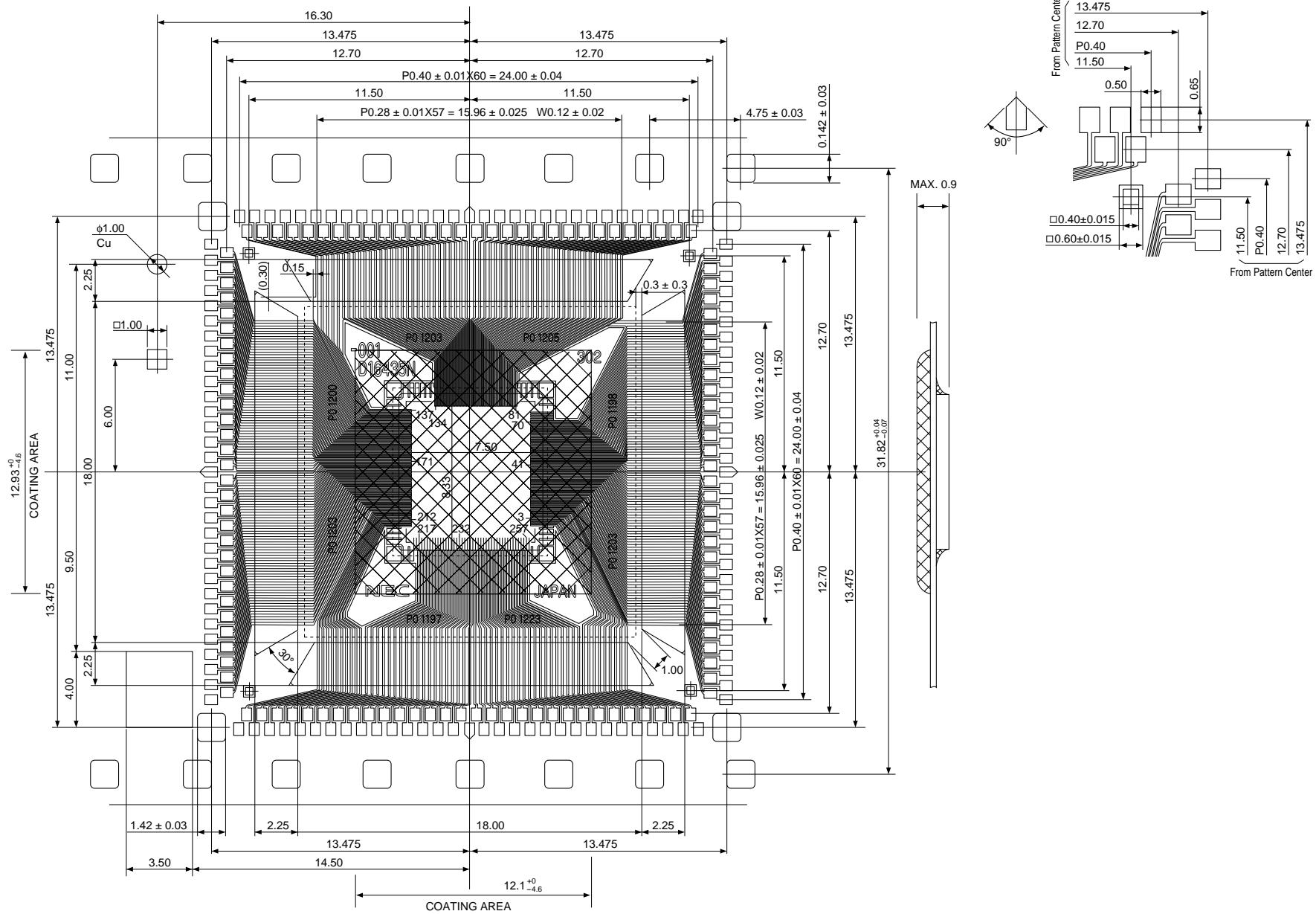

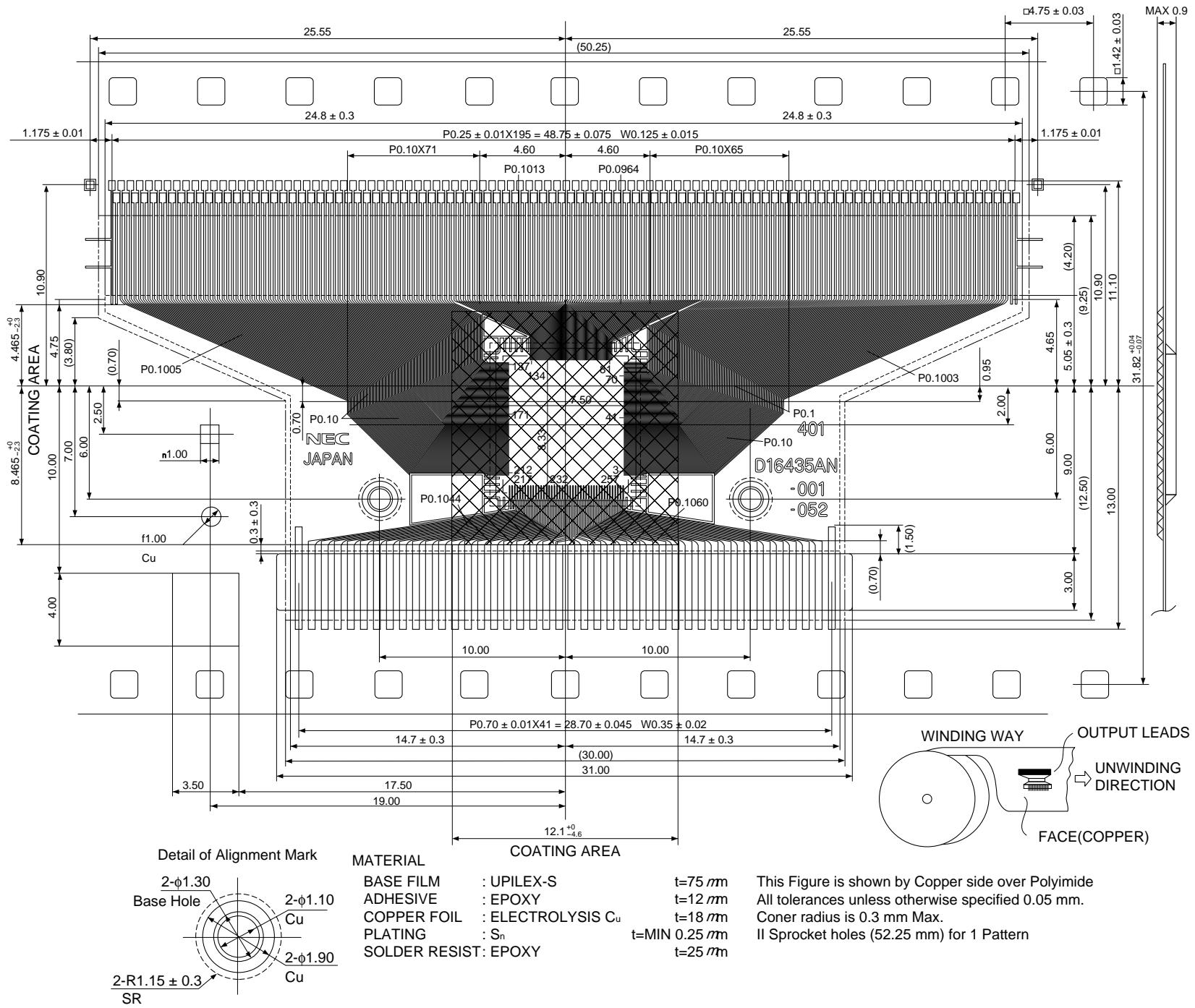

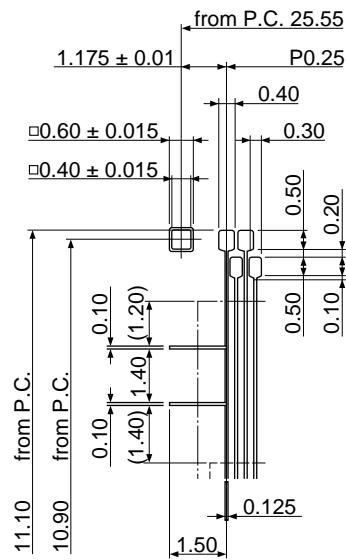

STANDARD TCP PACKAGE DRAWINGS ( $\mu$ PD16435N-001-001,  $\mu$ PD16435AN-001-001)

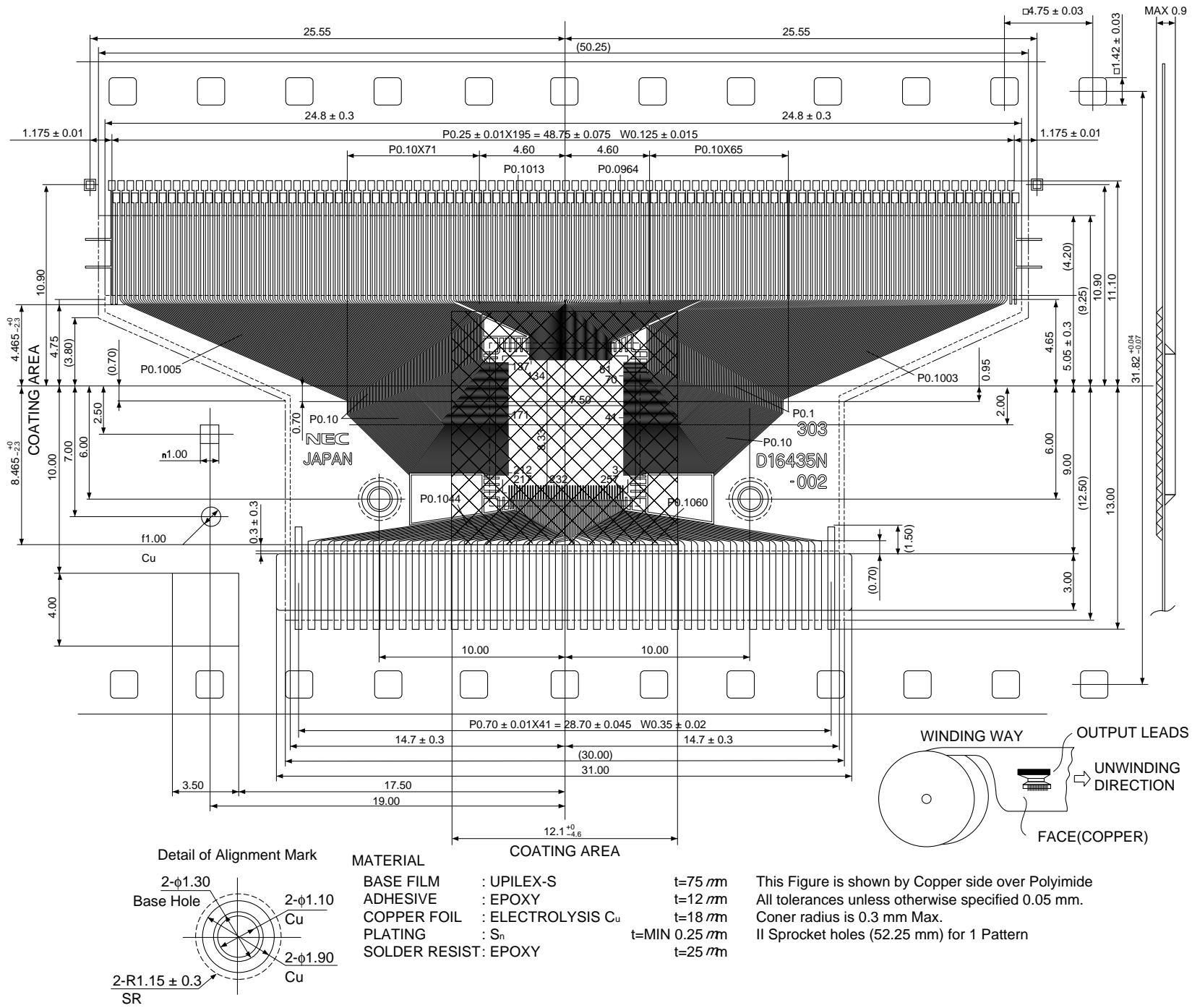

## STANDARD TCP PACKAGE DRAWINGS (μPD16435N-001-002)

### Detail of Test Pad and Alignment Mark

STANDARD TCP PACKAGE DRAWINGS ( $\mu$ PD16435AN-001-052)

Detail of Test Pad

and Alignment Mark

|        |

|--------|

| NC     |

| NC     |

| COM38  |

| COM39  |

| COM40  |

| COM41  |

| COM42  |

| •      |

| •      |

| •      |

| COM73  |

| SEG1   |

| •      |

| •      |

| •      |

| •      |

| •      |

| •      |

| •      |

| SEG119 |

| COM37  |

| •      |

| •      |

| •      |

| COM5   |

| COM4   |

| COM3   |

| COM2   |

| COM1   |

| NC     |

| NC     |

|                  |

|------------------|

| DUMMY            |

| $V_{DD}$         |

| GND1             |

| CS               |

| RS               |

| RD               |

| WR               |

| WS               |

| $D_0$            |

| $D_1$            |

| $D_2$            |

| $D_3$            |

| $D_4$            |

| $D_5$            |

| $D_6$            |

| $D_7$            |

| RESET            |

| SCR              |

| BUSY             |

| SYNC             |

| TEST1            |

| TEST2            |

| 3/5              |

| OSC <sub>1</sub> |

| OSC <sub>2</sub> |

| OSC <sub>3</sub> |

| $V_{CC}$         |

| $C1^-$           |

| $C1^+$           |

| $C2^-$           |

| $C2^+$           |

| $C3^-$           |

| $C3^+$           |

| $V_{IN(-)}$      |

| $V_{IN(+)}$      |

| GND2             |

| $V1$             |

| $V2$             |

| $V3$             |

| $V4$             |

| $V5$             |

| DUMMY            |

**REFERENCE DOCUMENTS**

NEC Semiconductor Device Reliability/Quality Control System (IEI-1212)

Semiconductor Device Mounting Technology Manual (C10535E)

**[MEMO]**

**[MEMO]**

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.