## Router 5000

Model

14315R-100

The Router 5000 chip is used to build high performance half-routers that increase the scalability and survivability of LONWORKS® control networks and lower installation costs by allowing mixed physical media to be used in a single installation.

Based on the Neuron® 5000 core, the Router 5000 provides the design flexibility to interface to the external transceiver of your choice for building a LONWORKS communication channel.

## FEATURES

- 3.3V operation.

- Higher Performance

- Clock rate up to 40 MHz

- Larger buffer size to allow for extended NVs and improved throughput.

- Transceiver-independent design.

- Compact 7mm x 7mm 48-pin QFN package.

- Can be connected to a transceiver running at any LonWORKS® bit rate from 610 bps to 1.25Mbps.

- Logical Isolation between two half-routers improves system reliability by isolating failures between channels.

- Transparent multi-channel and multi-media support.

- -40°C to +85°C operating temperature range.

The Router 5000 includes the Router firmware required to implement a half-router. Its compact form factor minimizes the space required to develop a half-router. Customers can develop two half-routers to build a full router with the same or different external

transceiver types. Commonly used transceiver types include support for TP/FT-10, TP-RS485, TP/XF-78F, TP/XF-1250 channel types and the LPT-11 transceiver. These external transceivers can run at interface bit rates from 9.8 kbps to 1.25 Mbps.

The Router parameters can be stored in an external EEPROM with a maximum size of 2 KB. Customers will need to specify router parameters that are applicable for the external transceiver type used with the Router 5000. For a full router design, customers can use the same crystal and the same power supply to implement the clock and power supply needed for the two half-routers, which helps minimize the overall size needed to implement a full router.

A Router 5000 can use one of four routing algorithms: **Configured router**, **Learning router**, **Bridge** or **Repeater**. The ability to choose these options allows the customer to trade off system performance for ease of installation. Configured and Learning routers fall into a class of routers known as intelligent routers, which use routing tables to selectively forward messages based on the destination address. A Bridge

forwards all valid packets that match its domains, whereas a Repeater forwards all valid packets. Configured routers are easily installed using an installation tool that calculates network topology and layer 4 timing parameters, such as the LonMaker® Integration Tool or an installation tool based on the LNS® network operating system.

### Usage

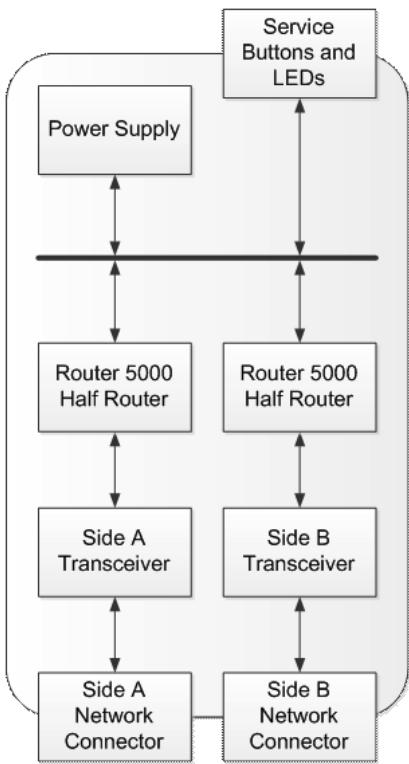

A half-router consists of the Router 5000 chip and an external transceiver along with a crystal to generate the clock and an external memory to hold the router table. Any type of external transceiver can be used with the Router 5000, such as a TP/FT-10, TP-RS485, TP/XF-78, TP/XF-1250 or LPT-11 transceiver. The Router 5000 is compatible with all LonWORKS transceivers, including standard transceivers for free topology, link power, twisted pair, and power line. Using multiple communications media can minimize installation costs and increase system performance by allowing easily installed media, such as power line or link power, to be combined with media such as TP/XF-1250 twisted pair. The two half-routers of a full router are logically isolated so that a failure in one half-router will not affect the other.

Figure 1: Block Diagram of a LONWORKS Router Based on the Router 5000

LONWORKS application programs do not have to be modified to work with routers. Only the network configuration of a device has to be modified when a device is moved to the far side of a router. The required modifications to the network configuration can be done automatically by an installation tool.

Routers are also independent of the network variables and message tags in a system, and can forward an unlimited number of them, which saves development cost because no code development is required to use routers in a system. It also saves installation and maintenance costs because router configuration is automatically managed by network server tools based on LNS Server. Monitoring and Control Applications, such as those based on the LCA Object Server OCX, do not require modifications to work with multi-channel networks when routers are used. All network configuration is performed over the installed network, further minimizing installation and maintenance costs because routers do not have to be physically accessed to change their configuration.

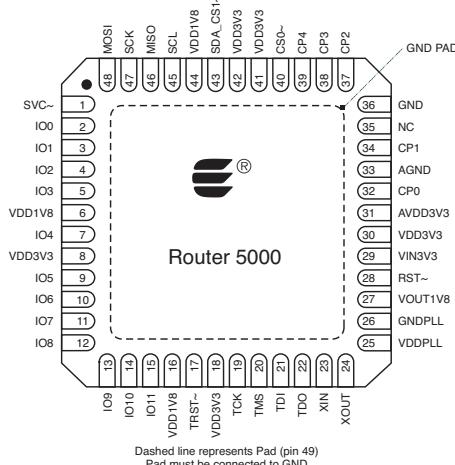

## Router 5000 Pin Configuration

Figure 2: Router 5000 Pinout

## Router 5000 Chip Pin Assignments

| Pin Name | Pin Number | Type                   | Description                                                             |

|----------|------------|------------------------|-------------------------------------------------------------------------|

| SVC~     | 1          | Digital I/O            | Service (active low)                                                    |

| IO0      | 2          | Digital I/O            | IO0 (side A to side B)                                                  |

| IO1      | 3          | Digital I/O            | IO1 (side A to side B)                                                  |

| IO2      | 4          | Digital I/O            | IO2 (side A to side B)                                                  |

| IO3      | 5          | Digital I/O            | IO3 (side A to side B)                                                  |

| VDD1V8   | 6          | Power                  | 1.8 V Power Input (from internal voltage regulator)                     |

| IO4      | 7          | Digital I/O            | IO4 (side A to side B)                                                  |

| VDD3V3   | 8          | Power                  | 3.3 V Power                                                             |

| IO5      | 9          | Digital I/O            | IO5 (side A to side B)                                                  |

| IO6      | 10         | Digital I/O            | IO6 (side A to side B)                                                  |

| IO7      | 11         | Digital I/O            | IO7 (side A to side B)                                                  |

| IO8      | 12         | Digital I/O            | IO8 (side A to side B)                                                  |

| IO9      | 13         | Digital I/O            | IO9 (side A to side B)                                                  |

| IO10     | 14         | Digital I/O            | IO10 (side A to side B)                                                 |

| IO11     | 15         | Digital I/O            | IO11 (not used for routers)                                             |

| VDD1V8   | 16         | Power                  | 1.8 V Power Input (from internal voltage regulator)                     |

| TRST~    | 17         | Digital Input          | JTAG Test Reset (active low)                                            |

| VDD3V3   | 18         | Power                  | 3.3 V Power                                                             |

| TCK      | 19         | Digital Input          | JTAG Test Clock                                                         |

| SDA_CS1~ | 43         | Digital I/O for Memory | I <sup>2</sup> C: serial data (SDA)<br>SPI: slave select 1 (active low) |

| VDD1V8   | 44         | Power                  | 1.8 V Power Input (from internal voltage regulator)                     |

| SCL      | 45         | Digital I/O for Memory | I <sup>2</sup> C: serial clock                                          |

| MISO     | 46         | Digital I/O for Memory | SPI master input, slave output (MISO)                                   |

| SCK      | 47         | Digital I/O for Memory | SPI serial clock                                                        |

| MOSI     | 48         | Digital I/O for Memory | SPI master output, slave input (MOSI)                                   |

| PAD      | 49         | Ground Pad             | Ground                                                                  |

| Pin Name | Pin Number | Type                   | Description                                                             |

|----------|------------|------------------------|-------------------------------------------------------------------------|

| TMS      | 20         | Digital Input          | JTAG Test Mode Select                                                   |

| TDI      | 21         | Digital Input          | JTAG Test Data In                                                       |

| TDO      | 22         | Digital Output         | JTAG Test Data Out                                                      |

| XIN      | 23         | Oscillator In          | Crystal oscillator Input                                                |

| XOUT     | 24         | Oscillator Out         | Crystal oscillator Output                                               |

| VDDPLL   | 25         | Power                  | 1.8 V Power Input (from internal voltage regulator)                     |

| GNDPLL   | 26         | Power                  | Ground                                                                  |

| VOUT1V8  | 27         | Power                  | 1.8 V Power Output (of internal voltage regulator)                      |

| RST~     | 28         | Digital I/O            | Reset (active low)                                                      |

| VIN3V3   | 29         | Power                  | 3.3 V Power Input                                                       |

| VDD3V3   | 30         | Power                  | 3.3 V Power                                                             |

| AVDD3V3  | 31         | Power                  | 3.3 V Power                                                             |

| CP0      | 32         | Communications         | CP0: Receive serial data                                                |

| AGND     | 33         | Ground                 | Ground                                                                  |

| CP1      | 34         | Communications         | CP1: Transmit serial data                                               |

| NC       | 35         | N/A                    | Do Not Connect                                                          |

| GND      | 36         | Ground                 | Ground                                                                  |

| CP2      | 37         | Communications         | CP2: External transceiver enable output                                 |

| CP3      | 38         | Communications         | CP3: Do Not Connect                                                     |

| CP4      | 39         | Communications         | CP4: Collision detect input                                             |

| CS0~     | 40         | Digital I/O            | SPI slave select 0 (active low)                                         |

| VDD3V3   | 41         | Power                  | 3.3 V Power                                                             |

| VDD3V3   | 42         | Power                  | 3.3 V Power                                                             |

| SDA_CS1~ | 43         | Digital I/O for Memory | I <sup>2</sup> C: serial data (SDA)<br>SPI: slave select 1 (active low) |

| VDD1V8   | 44         | Power                  | 1.8 V Power Input (from internal voltage regulator)                     |

| SCL      | 45         | Digital I/O for Memory | I <sup>2</sup> C: serial clock                                          |

| MISO     | 46         | Digital I/O for Memory | SPI master input, slave output (MISO)                                   |

| SCK      | 47         | Digital I/O for Memory | SPI serial clock                                                        |

| MOSI     | 48         | Digital I/O for Memory | SPI master output, slave input (MOSI)                                   |

| PAD      | 49         | Ground Pad             | Ground                                                                  |

Table 1: Router 5000 Chip Pin Description

## Electrical Characteristics

### Router 5000 Operating Conditions

| Parameter <sup>1</sup> | Description                                                                  | Minimum                                 | Typical                                   | Maximum               |

|------------------------|------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------|-----------------------|

| $V_{DD3}$              | Supply voltage                                                               | 3.00 V                                  | 3.3 V                                     | 3.60 V                |

| $T_A$                  | Ambient temperature                                                          | -40° C                                  |                                           | +85° C                |

| $f_{XIN}$              | XIN clock frequency <sup>2</sup>                                             | -                                       | 10,000 MHz                                | -                     |

| Tx Current             | Current consumption <sup>3</sup><br>5 - 80MHz                                |                                         | Rx current<br>+ 15 mA                     | Rx current<br>+ 15 mA |

| Rx Current             | Current consumption <sup>3</sup><br>5MHz<br>10MHz<br>20MHz<br>40MHz<br>80MHz | 9 mA<br>9 mA<br>15 mA<br>23 mA<br>38 mA | 15 mA<br>15 mA<br>23 mA<br>33 mA<br>52 mA |                       |

Table 2: Router 5000 Operating Conditions

#### Notes

- All parameters assume nominal supply voltage ( $V_{DD3} = 3.3 V \pm 0.3 V$ ) and operating temperature ( $T_A$ , between -40°C and +85°C), unless otherwise noted.

- See Clock Requirements in the Series 5000 Chip Data Book for more detailed information about the XIN clock frequency.

- Assumes no load on digital I/O pins, and that the I/O lines are not switching.

## SPECIFICATIONS

### Processor

Neuron 5000 Processor

### Processor Input Clock

10 MHz

### Operating Input Voltage

3.0 V DC to 3.6 V DC

### RoHS-Compliant

The Router 5000 chip is compliant with the European Directive 2002/95/EC on the restriction of the use of certain hazardous substances (RoHS) in electrical and electronic equipment.

### EMC

Depends on network transceiver

### Transmission Speed

Depends on network transceiver:

78 kbit/s for TP/FT-10 channel;

1250 kbit/s for TP/XF-1250 channel.

(See EIA-485 channel specification for transmission speed characteristics.)

### Operating Temperature

-40 to 85°C

## Operating Humidity

25-90% RH @ 50°C, non-condensing.

## Non-operating Humidity

95% RH @ 50°C, non-condensing.

## Reflow Soldering Temperature Profile

Refer to Joint Industry Standard document *IPC/JEDEC J-STD-020D.1* (March 2008).

## Peak Reflow Soldering Temperature

260°C

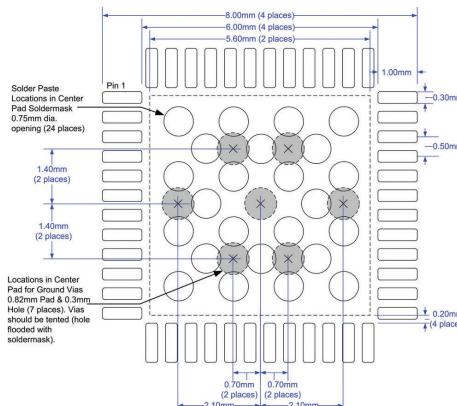

## Recommended Router 5000 Chip Pad Layout

Figure 3: Router 5000 Chip Pad Layout

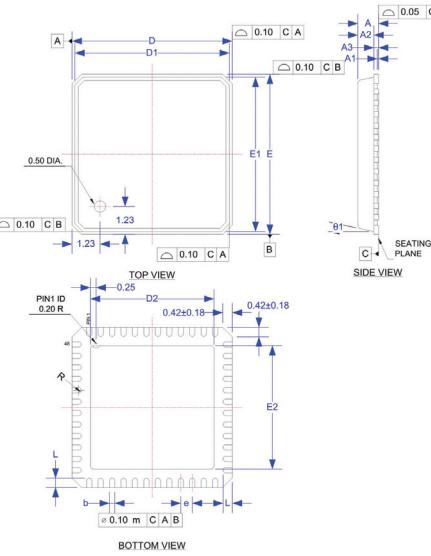

## Router 5000 Chip IC Mechanical Specification

\* CONTROLLING DIMENSION : MM

| SYMBOL                          | MILLIMETER |      |      | INCH       |        |       |

|---------------------------------|------------|------|------|------------|--------|-------|

|                                 | MIN.       | NOM. | MAX. | MIN.       | NOM.   | MAX.  |

| A                               | ---        | ---  | 0.90 | ---        | ---    | 0.035 |

| A1                              | 0.00       | 0.01 | 0.05 | 0.00       | 0.0004 | 0.002 |

| A2                              | ---        | 0.65 | 0.70 | ---        | 0.026  | 0.028 |

| A3                              | 0.20 REF.  |      |      | 0.008 REF. |        |       |

| b                               | 0.18       | 0.23 | 0.30 | 0.007      | 0.009  | 0.012 |

| D                               | 7.00 bsc   |      |      | 0.276 bsc  |        |       |

| D1                              | 6.75 bsc   |      |      | 0.266 bsc  |        |       |

| D2                              | 5.20       | 5.40 | 5.60 | 0.205      | 0.213  | 0.220 |

| E                               | 7.00 bsc   |      |      | 0.276 bsc  |        |       |

| E1                              | 6.75 bsc   |      |      | 0.266 bsc  |        |       |

| E2                              | 5.20       | 5.40 | 5.60 | 0.205      | 0.213  | 0.220 |

| L                               | 0.30       | 0.40 | 0.50 | 0.012      | 0.016  | 0.020 |

| e                               | 0.50 bsc   |      |      | 0.020 bsc  |        |       |

| Ø1                              | 0°         | ---  | 12°  | 0°         | ---    | 12°   |

| R                               | 0.09       | ---  | ---  | 0.004      | ---    | ---   |

| TOLERANCES OF FORM AND POSITION |            |      |      |            |        |       |

| aaa                             | 0.10       |      |      | 0.004      |        |       |

| bbb                             | 0.10       |      |      | 0.004      |        |       |

| ccc                             | 0.05       |      |      | 0.002      |        |       |

Figure 4: Router 5000 Chip IC Mechanical Specifications

#### Notes

- All dimensions are in millimeters.

- Dimensions and tolerances conform to ASME Y14.5M-1994.

- Package warpage max. 0.08 mm.

- Package corners unless otherwise specified are  $R0.175 \pm 0.025$  mm.

## ORDERING INFORMATION

Router 5000 Chip

14315R-100

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).