#### RAA223183

1000V Off-line Flyback Regulator

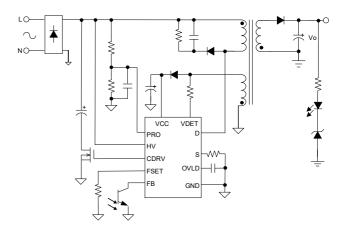

The RAA223183 is an off-line Flyback regulator with a 1000V integrated MOSFET, designed for high-reliability application of single-phase and 3-phase smart meter power supplies and other generally isolated power supplies. The RAA223183 can deliver up to 7W power from the single-phase and 11W from 3-phase universal inputs.

The RAA223183 operates in DCM with constant switching frequency at full load. The system is inherently stable with an easy feedback loop design while switching at constant frequency without interfering with the communication of the smart meter. At light load, the RAA223183 enters burst mode operation to reduce the IC power consumption while keeping the burst frequency below 3kHz to avoid interference to the PLC frequency band.

The RAA223183 features a unique short-time heavy load operation mode, which delivers up to 15w output power for a programmed time. This feature allows the smart meter's AC/DC power supply to be designed at a regular power level without being over-designed for 2x power in the transmission mode, which greatly reduces system cost.

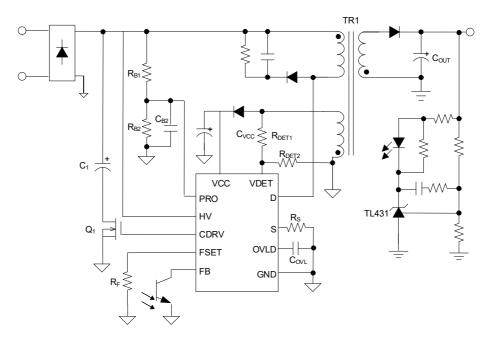

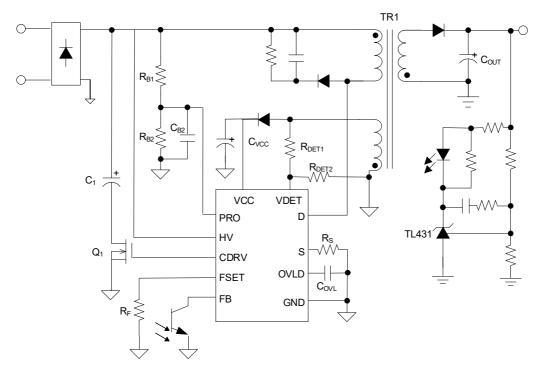

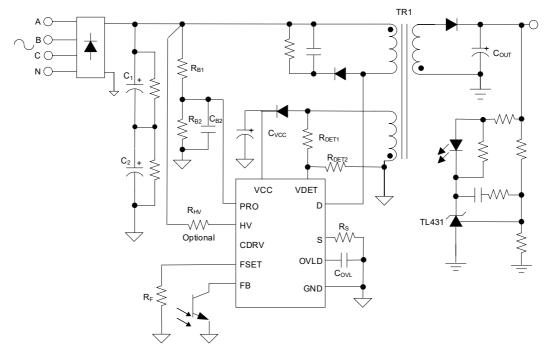

The RAA223183 also has a cap-saving feature for single-phase applications. The IC has a dedicated CDRV pin that can drive an external MOSFET to control the bulk cap across the rectified DC bus, as shown in Figure 1. When the input voltage exceeds a certain value (> 400V rectified DC voltage), the MOSFET disconnects the bulk capacitor from the DC bus to avoid overvoltage damage. During overvoltage, the IC keeps switching to maintain a well-regulated output voltage so all the meter functionalities are not interrupted. In 3-phase applications, the cap-saving feature is not needed. Therefore, the CDRV pin can be floated. See Table 1 for other RAA22318x products with different overvoltage protection features.

In addition, the RAA223183 adopts the valley switching technique to reduce switching losses and EMI noises. It also features VinUV, input brownout, VccUV, VccOV, output overload, output short-circuit, primary winding short, and over-temperature protections. These features are integrated into an SO13 package.

#### **Features**

- Flyback regulator with 1000V 9Ω MOSFET

- Single 400V bulk capacitor for single-phase input up to 460V<sub>AC</sub>

- Frequency doubling for heavy load operation (up to 15W in single-phase and 21W and above in 3-phase), with programmable duration (maximum time depends on thermal capability)

- Valley switching to reduce switching losses

- Programmable constant frequency PWM operation

- Burst mode operation at light load

- Protection features: short-circuit protection (SCP), overload protection (OLP), input undervoltage lockout (VinUV), Input OVP, VCC overvoltage protection (VccOV), VCC undervoltage lockout (VccUV) and over-temperature protection (OTP).

- 4KV surge compliance per IEC61000-4-5 with cap-saving operation

### **Applications**

- Smart Meter

- Large appliances

- Industry control

Figure 1. Typical Flyback Circuit

## **Contents**

| 1.  | Overview     |                                                |    |  |  |  |  |  |  |

|-----|--------------|------------------------------------------------|----|--|--|--|--|--|--|

|     | 1.1          | Block Diagram                                  | 3  |  |  |  |  |  |  |

| 2.  | Pin In       | Pin Information                                |    |  |  |  |  |  |  |

|     | 2.1          | Pin Assignments                                | 4  |  |  |  |  |  |  |

|     | 2.2          | Pin Descriptions                               | 4  |  |  |  |  |  |  |

| 3.  | Speci        | ifications                                     | 5  |  |  |  |  |  |  |

|     | 3.1          | Absolute Maximum Ratings                       | 5  |  |  |  |  |  |  |

|     | 3.2          | Thermal Specifications                         | 5  |  |  |  |  |  |  |

|     | 3.3          | Recommended Operating Conditions               | 5  |  |  |  |  |  |  |

|     | 3.4          | Electrical Specifications                      | 6  |  |  |  |  |  |  |

| 4.  | Typic        | al Characterization Curves                     | 8  |  |  |  |  |  |  |

| 5.  | Detai        | led Description 1                              | 1  |  |  |  |  |  |  |

|     | 5.1          | Constant Frequency PWM Mode                    | 1  |  |  |  |  |  |  |

|     | 5.2          | Burst Mode 1                                   | 2  |  |  |  |  |  |  |

|     | 5.3          | Short-Time Heavy Load Operation (OVL)          | 2  |  |  |  |  |  |  |

|     | 5.4          | Single Cap Operation                           | 3  |  |  |  |  |  |  |

|     | 5.5          | Soft Startup                                   |    |  |  |  |  |  |  |

|     | 5.6          | VCC Overvoltage and Undervoltage Protection    |    |  |  |  |  |  |  |

|     | 5.7          | Overload and Short-Circuit Protection          | 6  |  |  |  |  |  |  |

| 6.  | Appli        | cation Topologies                              | 7  |  |  |  |  |  |  |

| 7.  | Desig        | ın Guidance                                    | 8  |  |  |  |  |  |  |

|     | 7.1          | Input Bulk Capacitor                           |    |  |  |  |  |  |  |

|     | 7.2          | Transformer Primary Inductance and Turns Ratio | 8  |  |  |  |  |  |  |

|     | 7.3          | Current-Sensing Resistor                       |    |  |  |  |  |  |  |

|     | 7.4          | FSET Pin Resistor                              |    |  |  |  |  |  |  |

|     | 7.5          | VDET Pin Resistors                             |    |  |  |  |  |  |  |

|     | 7.6          | PRO Pin Resistors                              |    |  |  |  |  |  |  |

|     | 7.7          | PRO Pin Capacitor                              |    |  |  |  |  |  |  |

|     | 7.8          | MOSFET in Series with C1 (if used)             |    |  |  |  |  |  |  |

|     | 7.9          | OLV Pin Capacitor                              |    |  |  |  |  |  |  |

|     | 7.10<br>7.11 | HV Pin                                         |    |  |  |  |  |  |  |

|     |              | PCB Layout Guidance                            |    |  |  |  |  |  |  |

| 8.  |              | Performance                                    |    |  |  |  |  |  |  |

|     |              |                                                |    |  |  |  |  |  |  |

| 9.  |              | age Outline Drawing                            |    |  |  |  |  |  |  |

| 10. | Orde         | ring Information                               | :4 |  |  |  |  |  |  |

| 11. | Revis        | ion History                                    | :4 |  |  |  |  |  |  |

## 1. Overview

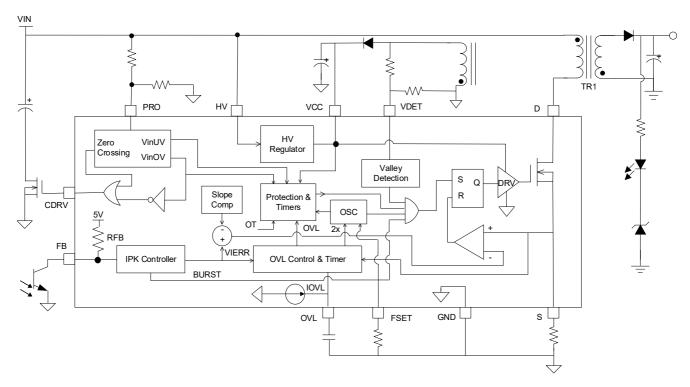

# 1.1 Block Diagram

Figure 2. Block Diagram of RAA223183

## 2. Pin Information

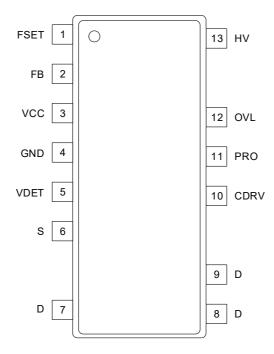

# 2.1 Pin Assignments

Figure 3. Pin Assignments - Top View

# 2.2 Pin Descriptions

| Pin Number | Pin Name | Description                            |

|------------|----------|----------------------------------------|

| 1          | FSET     | Oscillator frequency set               |

| 2          | FB       | Feedback                               |

| 3          | VCC      | IC supply voltage                      |

| 4          | GND      | Signal ground                          |

| 5          | VDET     | Valley detection                       |

| 6          | S        | Source of power FET                    |

| 7, 8, 9    | D        | Drain of power FET                     |

| 10         | CDRV     | Gate of input cap disconnection MOSFET |

| 11         | PRO      | Bus overvoltage sense                  |

| 12         | OVL      | Short-time heavy-load programming      |

| 13         | HV       | High voltage startup                   |

## 3. Specifications

### 3.1 Absolute Maximum Ratings

**Caution:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                                             | Minimum | Maximum | Unit |

|-------------------------------------------------------|---------|---------|------|

| VCC                                                   | -0.3    | +30     | V    |

| VFB                                                   | -0.3    | +5      | V    |

| VDET                                                  | -0.3    | +5      | V    |

| CDRV                                                  | -0.3    | +30     | V    |

| PRO                                                   | -0.3    | +5      | V    |

| HV                                                    | -0.3    | +700    | V    |

| D (to S)                                              | - 0.3   | +1000   | V    |

| Continuous Power Dissipation (T <sub>A</sub> = +25°C) | -       | 1       | W    |

| Maximum Junction Temperature                          | -       | +150    | °C   |

| Maximum Storage Temperature Range                     | -60     | +150    | °C   |

| Human Body Model (Tested per JS-001-2017)             | -       | 1.2     | kV   |

| Charged Device Model (Tested per JS-002-2018)         | -       | 1       | kV   |

| Latch-Up (Tested per JESD78E; Class 2, Level A)       | -       | 100     | mA   |

## 3.2 Thermal Specifications

| Parameter          | Package         | Symbol                         | Conditions          | Typical<br>Value | Unit |

|--------------------|-----------------|--------------------------------|---------------------|------------------|------|

| Thermal Resistance | ance 13 Ld SOIC |                                | Junction to ambient | 27.4             | °C/W |

| Thermal Resistance | 13 Ed 0010      | θ <sub>JC</sub> <sup>[2]</sup> | Junction to case    | 31               | °C/W |

<sup>1.</sup>  $\theta_{JA}$  is measured on a FR4 2oz PCB with copper size of  $\overline{165 mm^2}$  on pin 7, 8, and 9 at  $26^{\circ}$ C ambient.

## 3.3 Recommended Operating Conditions

| Parameter           | Minimum | Maximum | Unit |

|---------------------|---------|---------|------|

| Vcc                 | 10      | 24      | V    |

| Ambient Temperature | -40     | +125    | °C   |

<sup>2.</sup> For  $\theta_{\text{JC}},$  the case temperature location is taken at the package top center.

## 3.4 Electrical Specifications

Typical operating conditions at 25°C,  $V_{DRAIN}$  = 375V,  $V_{CC}$  = 12V,  $T_{J}$  = -40 to +125°C, unless otherwise specified.

| Parameter                                          | Symbol                 | Test Conditions                                                       | Min <sup>[1]</sup> | Тур   | Max <sup>[1]</sup> | Unit |

|----------------------------------------------------|------------------------|-----------------------------------------------------------------------|--------------------|-------|--------------------|------|

| Startup and Power FET                              |                        |                                                                       |                    |       | l                  |      |

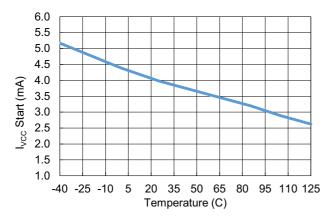

| Internal V <sub>CC</sub> Startup Current           | I <sub>VCC_START</sub> | V <sub>CC</sub> = 8, V <sub>DRAIN</sub> = 100V                        | -                  | 4.0   | 8                  | mA   |

| Drain Leakage Current                              | I <sub>D_LEAK</sub>    | V <sub>CC</sub> = 0, V <sub>D</sub> = 375V, V <sub>FB</sub> = 0V      | -                  | 0.1   | 3.5                | μA   |

| HV Bias                                            | I <sub>HV_BIAS</sub>   | V <sub>CC</sub> = 12, V <sub>DRAIN</sub> = 375V                       | -                  | 1.0   | 5                  | μΑ   |

| Power FET Breakdown Voltage                        | V <sub>(BR)DSS</sub>   | -                                                                     | 1000               | -     | -                  | V    |

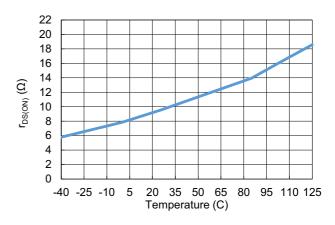

| Power FET On-Resistance                            | r                      | T <sub>J</sub> = 25°C, V <sub>CC</sub> = 12V, I <sub>DS</sub> = 400mA | -                  | 9     | 11                 | Ω    |

| Fower FET Off-Nesistance                           | r <sub>DS(ON)</sub>    | T <sub>J</sub> = 125°C                                                | -                  | 18    | 22                 | Ω    |

| Power FET Output Capacitance                       | C <sub>oss</sub>       | V <sub>DS</sub> = 25V, V <sub>GS</sub> = 0V                           | -                  | 24.7  | -                  | pF   |

| V <sub>CC</sub> Supply                             |                        |                                                                       | •                  |       | •                  |      |

| V <sub>CC</sub> Start (Rising)/HV Regulator<br>Off | V <sub>CC_START</sub>  | V <sub>HV</sub> = 100V                                                | 11                 | 12    | 13                 | ٧    |

| V <sub>CC</sub> (Falling) /HV Regulator On         | V <sub>CC_HVON</sub>   | V <sub>HV</sub> = 100V                                                | 8                  | 9     | 10                 | V    |

| HV Regulator On/Off Hysteresis                     | V <sub>VCC_HYS</sub>   | -                                                                     | 2                  | 3     | 4                  | V    |

| V <sub>CC</sub> Undervoltage Threshold (Falling)   | V <sub>CC_UVLO</sub>   | IC stop switching                                                     | 4.8                | 5.5   | 6                  | ٧    |

| V <sub>CC</sub> OV Clamping Threshold              | V <sub>CC_OVC</sub>    | -                                                                     | 21.4               | 24    | 26.3               | V    |

| V <sub>CC</sub> OV Latch-Off Threshold             | V <sub>CC_OVL</sub>    | -                                                                     | 23                 | 26    | 29.5               | V    |

| V <sub>CC</sub> Quiescent Current                  | I <sub>VCC_Q</sub>     | V <sub>FB</sub> = 0V, no switching                                    | -                  | 480   | 685                | μA   |

| V <sub>CC</sub> Current During Switching           | I <sub>vcc</sub>       | V <sub>FB</sub> > 0.7V, switching frequency = 50kHz, D = 0.4          | -                  | 705   | 825                | μA   |

| Current Sense                                      |                        |                                                                       |                    |       | l                  |      |

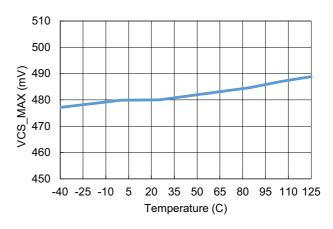

| Max Current Sensing Threshold                      | V <sub>CS_MAX</sub>    | V <sub>FB</sub> = 2.5V                                                | 425                | 500   | 550                | mV   |

| SCP Threshold                                      | V <sub>CS_SC</sub>     | -                                                                     | -                  | 1000  | -                  | mV   |

| Minimum Current Sensing<br>Threshold               | V <sub>CS_MIN</sub>    | -                                                                     | 155                | 205   | 245                | mV   |

| Leading Edge Blank Time                            | t <sub>LEB</sub>       | -                                                                     | 300                | 350   | 425                | ns   |

| Feedback                                           | ı                      |                                                                       | •                  |       | I.                 |      |

| Transconductance                                   | GM                     | V <sub>FB</sub> to V <sub>CS</sub>                                    | -                  | 0.225 | -                  | V/V  |

| FB Pin Pull-Up Resistor                            | R <sub>FB</sub>        | -                                                                     | 24                 | 35    | -                  | kΩ   |

| FB Threshold Entering Burst Mode                   | V <sub>BURL</sub>      | -                                                                     | -                  | 1.5   | -                  | V    |

| FB Threshold Exiting Burst Mode                    | V <sub>BURH</sub>      | -                                                                     | -                  | 1.87  | -                  | V    |

| FB Threshold Into 2x Frequency                     | V <sub>FB_2XF</sub>    | -                                                                     | 2.6                | 3.2   | 4                  | V    |

| FB Threshold Out of 2x Frequency                   | V <sub>FB_1XF</sub>    | -                                                                     | 1.6                | 2.6   | 3.2                | V    |

| FB Threshold for Overload<br>Protection            | V <sub>FB_OLP</sub>    | -                                                                     | 3.8                | 4.4   | 5.1                | ٧    |

| FB Internal Pull-Up Voltage                        | V <sub>FB_MAX</sub>    | -                                                                     | 4.4                | 4.8   | -                  | V    |

Typical operating conditions at 25°C,  $V_{DRAIN}$  = 375V,  $V_{CC}$  = 12V,  $T_{J}$  = -40 to +125°C, unless otherwise specified. (Cont.)

| Parameter                             | Symbol                | Test Conditions                                               |          | Тур  | Max <sup>[1]</sup> | Unit |

|---------------------------------------|-----------------------|---------------------------------------------------------------|----------|------|--------------------|------|

| Programmable Heavy Load               |                       | ,                                                             |          |      | 1                  |      |

| OVL Pin Source Current                | I <sub>OVL</sub>      | -                                                             | -        | 10.5 | 11.8               | μΑ   |

| OVL Pin Discharge Current             | I <sub>OVL_D</sub>    | -                                                             | 1.8      | 2    | -                  | μΑ   |

| OVL Pin Threshold                     | V <sub>OVL</sub>      | -                                                             | 3.7      | 4.2  | 4.7                | V    |

| Input Undervoltage and Overvolt       | age Protection        | ,                                                             |          |      | 1                  |      |

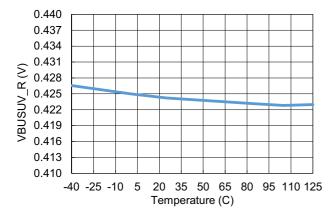

| PRO Pin UV Rising Threshold           | V <sub>BUSUV_R</sub>  | -                                                             | 0.35     | 0.4  | 0.5                | V    |

| PRO Pin UV Falling Threshold          | V <sub>BUSUV_F</sub>  | -                                                             | 0.23     | 0.3  | 0.37               | V    |

| PRO Pin OV Threshold (Rising)         | V <sub>BUSOV_R</sub>  | -                                                             | 4.3      | 4.7  | 5.2                | V    |

| PRO Pin OV Threshold (Falling)        | V <sub>BUSOV_F</sub>  | -                                                             | 3.8      | 4.25 | 4.7                | V    |

| OV Falling Delay                      | T <sub>BUSOV_DL</sub> | -                                                             | 1.3      | 1.6  | -                  | ms   |

| CDRV Driver Low-Side<br>On-Resistance | R <sub>DS_L</sub>     | -                                                             | -        | 17   | 32                 | Ω    |

| CDRV Driver Source Current            | I <sub>DRVS</sub>     | -                                                             | -        | 25   | -                  | mA   |

| Frequency                             | 1                     |                                                               | <b>'</b> |      |                    |      |

| FSET Pin Reference Voltage            | V <sub>FSET</sub>     | -                                                             | 2.3      | 2.5  | 2.7                | V    |

| Oscillator Frequency                  | f <sub>SW</sub>       | R <sub>FSET</sub> = 187k                                      | 42.5     | 50   | 55                 | kHz  |

| Dithering                             | -                     | Percent frequency                                             | -2.5     |      | 2.5                | %    |

| Double Frequency                      | f <sub>SW_2x</sub>    | -                                                             | 85       | 90   | 95                 | kHz  |

| Valley Detection                      | 1                     |                                                               |          |      | ı                  |      |

| Ringing Frequency                     | -                     | Established by design                                         | 550      | -    | 1000               | kHz  |

| Timing                                | 1                     |                                                               |          |      | ı                  |      |

| Maximum Duty Cycle                    | Dmax                  | f <sub>SW</sub> = 50kHz                                       | 42       | 50   | 54                 | %    |

| OVL Blanking                          | T <sub>OVL_BLK</sub>  | 2 Cycles, 50kHz                                               | -        | 40   | -                  | μs   |

| Startup Timer                         | T <sub>ST</sub>       | 4096 cycles, 50kHz                                            | -        | 82   | -                  | ms   |

| Hiccup Restart Delay                  | T <sub>HICC</sub>     | 16384 cycles, 50kHz                                           | -        | 328  | -                  | ms   |

| OLP/OCP Delay Timer                   | T <sub>OLP</sub>      | 2048 cycles, f <sub>SW</sub> = 100kHz, V <sub>FB</sub> > 4.5V | -        | 20.5 | -                  | ms   |

| V <sub>IN</sub> UV Delay Timer        | T <sub>VINUV</sub>    | 2048 cycles, f <sub>SW</sub> = 100kHz                         | -        | 20.5 | -                  | ms   |

| Thermal                               |                       | ,                                                             |          |      | 1                  |      |

| Over-Temperature Threshold            | OTP <sub>TH</sub>     | -                                                             | -        | 150  | -                  | С    |

| Over-Temperature Hysteresis           | OTP <sub>HYS</sub>    | -                                                             | -        | 30   | -                  | С    |

<sup>1.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

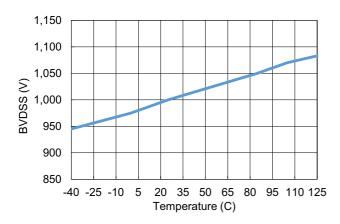

## 4. Typical Characterization Curves

Figure 4. Breakdown Voltage vs Temperature

Figure 5. r<sub>DS(ON)</sub> vs Temperature

Figure 6. VCC Start Current vs Temperature

Figure 7. Maximum Current Sensing Threshold vs

Temperature

Figure 8. BUS Undervoltage Rising vs Temperature

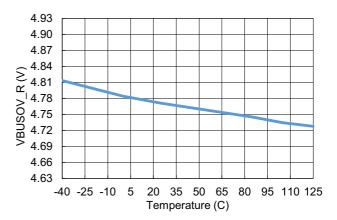

Figure 9. BUS Overvoltage Rising vs Temperature

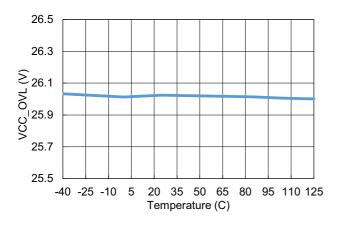

Figure 10. VCC OVP Latch Threshold vs Temperature

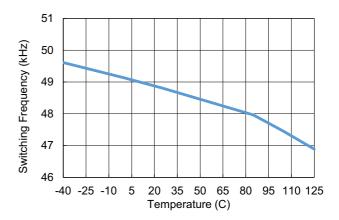

Figure 11. Switching Frequency vs Temperature

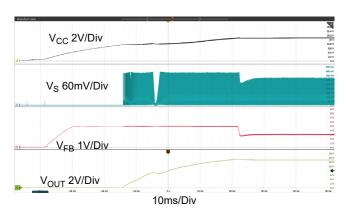

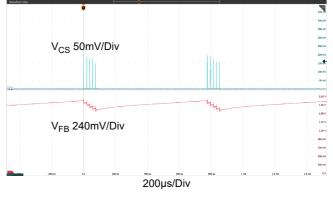

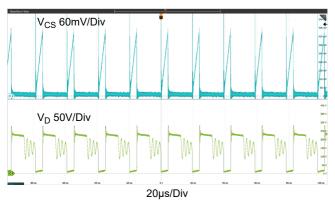

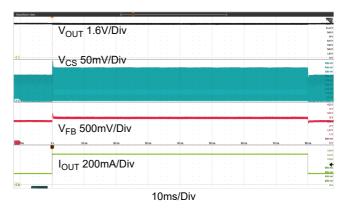

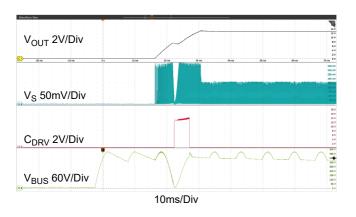

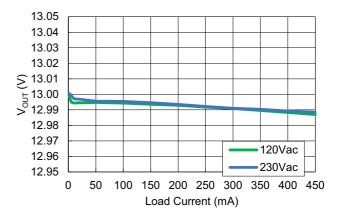

$Typical\ Waveforms\ (V_{IN}=230V_{AC},\ V_{OUT}=13V,\ I_{OUT}=450mA,\ Lpri=1.3mH,\ C_{OUT}=1000\mu F,\ T_{A}=25^{\circ}C)$

Figure 12. Startup

Figure 13. Light Load Operation

Figure 15. Short-Time Heavy Load Operation

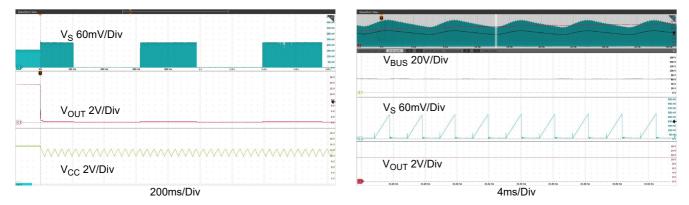

Typical Waveforms ( $V_{IN}$  = 230 $V_{AC}$ ,  $V_{OUT}$  = 13V,  $I_{OUT}$  = 450mA, Lpri = 1.3mH,  $C_{OUT}$  = 1000 $\mu$ F,  $T_A$  = 25°C) (Cont.)

Figure 16. Short-Circuit/Overload Protection

Figure 17. Input Brownout Protection ( $V_{IN} = 80V_{AC}$ )

Figure 18. Startup with V<sub>IN</sub> OV (V<sub>IN</sub> = 350Vac)

Figure 19. Steady State Operation under  $V_{IN}$  OV  $(V_{IN} = 350V_{AC})$

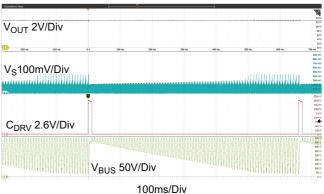

Figure 20. Efficiency

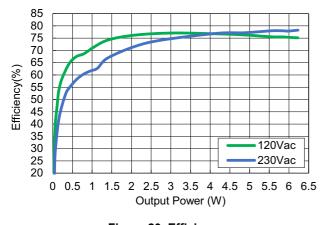

Figure 21. Load Regulation

## 5. Detailed Description

The RAA223183 adopts constant frequency switching with secondary side regulation, as Figure 22 shows. When the power is less than the maximum output power (set by RS, RF, and primary transformer inductance), it operates in DCM at the chosen switching frequency. When the power exceeds the maximum output power, it operates in CCM at the doubled frequency for a programmed period until the overload protection is reached. The IC uses valley detection to reduce switching losses and ensure DCM operation.

Figure 22. RAA223183 Flyback Application Circuit

### 5.1 Constant Frequency PWM Mode

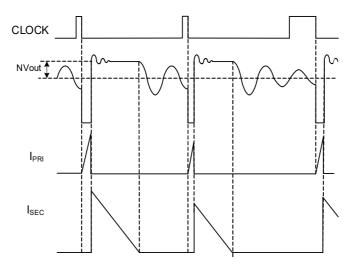

The IC regulates the output voltage with an error amplifier (TL431) through the optocoupler and peak current control at full load. The feedback pin is the error output optocoupled from the secondary side. Its voltage level controls the peak current in every switching cycle. The turn-on point is set by the internal fixed frequency oscillator and valley detection circuit, which senses the voltage on the auxiliary winding. If the valley is undetected, it waits for the nearest valley to turn on the FET. The valley detection is illustrated in Figure 23. Because the ringing

frequency usually ranges from 500kHz to 1MHz, the possible half-ringing cycle delay only causes ~5% frequency variation.

Figure 23. Valley Switching

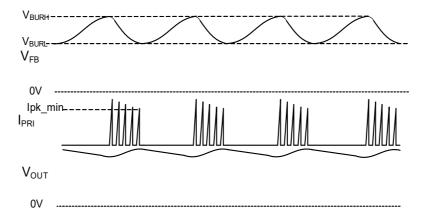

#### 5.2 Burst Mode

At the light load, the regulator transitions into burst mode operation to save power consumption while keeping the switching frequency constant without interfering with the communication. The burst frequency is designed to be less than 3kHz, to avoid the minimum frequency of the narrow-band PLC communication. During light load, the FB voltage is reduced, and when it drops below V<sub>BURL</sub>, the part enters burst mode operation. The IC stops switching. When FB voltage rises to V<sub>BURH</sub>, the IC resumes switching until FB voltage falls back to V<sub>BURL</sub>. In Burst mode, the peak current is less than 200mA, effectively avoiding audible noises. Burst Mode is illustrated in Figure 24.

Figure 24. Burst Mode Operation at Light Load

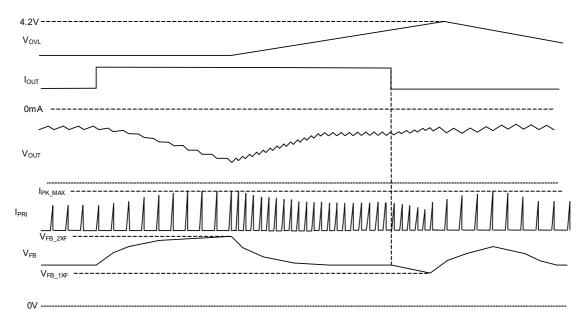

## 5.3 Short-Time Heavy Load Operation (OVL)

The IC allows a short-time heavy load operation over a programmable time (depending on the thermal capability of the design). When  $V_{FB} > V_{FB\_100k}$ , the oscillator frequency is doubled, valley detection is disabled, and the part operates in CCM. At the same time, a programmable timer starts - an internal  $10\mu\text{A}$  current charges the external cap on pin OVL. When the OVL pin reaches  $V_{OVL}$ , the heavy load operation stops, and the IC waits for five times the programmed heavy load operation time before the heavy load operation is allowed again. When  $V_{FB} < V_{FB\_50k}$ , the part exits heavy load operation before the heavy load timer expires. If the load is too heavy, FB continues

rising to  $V_{FB\_OLP}$ , the heavy load operation stops, and the overload protection is triggered. The operation is shown in Figure 25.

Figure 25. Short-Time Heavy Load Operation

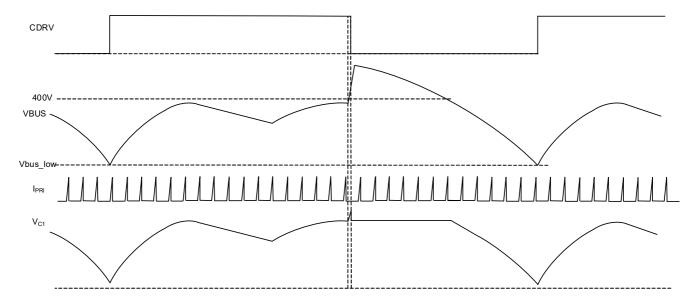

### 5.4 Single Cap Operation

The IC features a cap-saving feature by employing an optional external MOSFET driven by the CDRV pin. The FET is connected in series with a 400V input bulk capacitor, as shown in Figure 22. The FET is on when rectified voltage is less than 400V. When the rectified voltage exceeds 400V (sensed by the PRO pin using a resistor divider), the FET is turned off and disconnects the bulk cap from the BUS, protecting the cap from overvoltage damage. The FET is initially off at the startup, controlled by a low CDRV, until the bus voltage is pulled down low enough by the switching current. It is turned on with minimum inrush current. The operation is illustrated in Figure 26.

Figure 26. Input Overvoltage Protection and Zero-Voltage Turn-On of Bulk Cap MOSFET

This feature allows the customer to use only one 400V bulk cap and a 650V MOSFET to sustain a rectified voltage as high as 650V (limited by the MOSFET voltage rating) without using two stacked 400V caps of twice the capacitance. This feature saves an expensive 400V capacitor at the expense of a cheaper power FET.

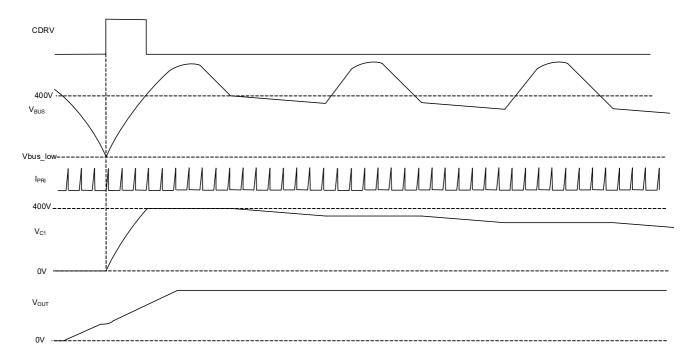

Figure 27. Operation from an Input Voltage Exceeding the VIN OV Point

As illustrated in Figure 27, when the input is connected to an AC voltage well above the maximum operating voltage, the rectified bus voltage quickly rises to the peak value. Because the CDRV is initially off, the cap FET is off, so all the rectified voltage is applied across the FET, not the bulk cap. When the IC's internal voltage is established, the IC detects the overvoltage using the PRO pin. It keeps CDRV low, so the cap FET stays off.

When VCC rises to 12V, the main power FET starts switching, pulling down the DC bus voltage, following a sinusoidal shape of the input AC voltage. When the BUS voltage is low enough, IC detects the point and turns on the cap FET by setting CDRV high. So, the bulk cap is connected to the DC bus. The rising input voltage charges the bulk cap until the rectified DC voltage reaches the set OV point (slightly above 400V). The IC turns off the cap FET, disconnecting the bulk cap from the rectified DC bus.

After the above OV action, the main power FET keeps switching, causing the rectified voltage to drop (due to the lack of the bulk cap). After the rectified bus voltage is below the bulk cap voltage, the bulk cap supplies power until the rectified input voltage is higher than the remaining cap voltage in the next half-line cycle. This process will continue until the energy saved in the bulk cap is completely depleted.

Although a steady state operation in this mode has the maximum rectified input voltage ripple, the IC can still regulate in most cases even when the rectified input voltage is low. High  $V_{IN}$  continuously defeats the  $V_{IN}$  UV protection in every half-line cycle due to the significant ripple voltage in this mode.

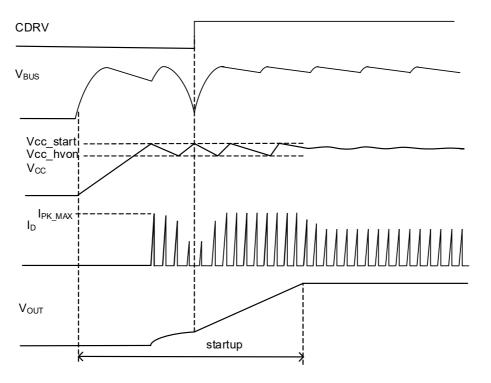

### 5.5 Soft Startup

When the input rectified voltage is higher than a certain level (determined by the PRO pin resistor divider), an internal HV current source ( $I_{VCC\_START}$ ) starts to charge the VCC cap. When the VCC reaches  $V_{CC\_START}$ , the IC switches, a startup timer begins (~82ms), and the internal HV regulator turns off; the regulator turns on again when VCC drops below  $V_{CC\_HVON}$ . Before the timer expires, a DCM operation with a constant maximum peak current is enforced to ensure a soft startup. The SCP is disabled during the startup blanking time. When  $V_{OUT}$  is

fully established, VCC is supplied by the auxiliary winding, and the internal HV current source is mostly off in steady-state operation to save power consumption. The startup process is illustrated in Figure 28 shows.

Figure 28. Startup Diagram

### 5.6 VCC Overvoltage and Undervoltage Protection

VCC voltage provides internal voltage for IC operation and is used to drive the internal power FET. It should stay within a certain range to ensure effective MOSFET driving. In steady-state operation, VCC is normally supplied by an auxiliary winding of a flyback transformer unless supplied by an external power supply. If VCC receives an excessive supply current, the VCC voltage increases. When the VCC voltage reaches  $V_{CC\_OVC}$ , an internal shunt regulator is on to sink a current to prevent it from going higher (clamping). If VCC still increases and reaches a higher level at  $V_{CC\_OVL}$ , the IC is latched off to prevent damage to the gate of the internal MOSFET unless VCC or VIN is recycled. When VCC is less than  $V_{CC\_UVLO}$ , the IC stops switching until it is charged back to  $V_{CC\_START}$ .

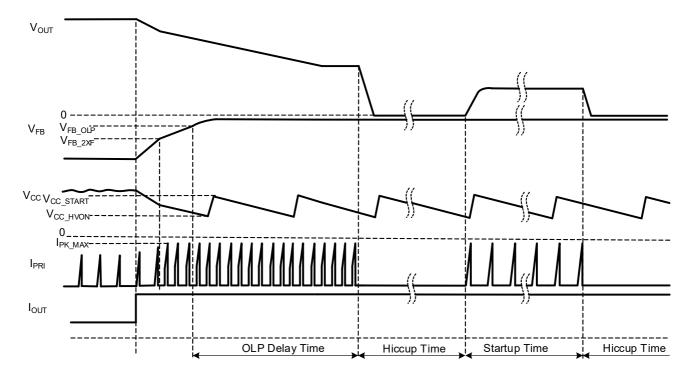

#### 5.7 Overload and Short-Circuit Protection

When an overload or a short-circuit occurs,  $V_{FB}$  rises high. When  $V_{FB}$  reaches  $V_{FB\_2XF}$ , the heavy load operation is enabled with twice the switching frequency. If  $V_{FB}$  continues to rise and reaches another threshold  $V_{FB\_OLP}$ , and the current sense detected above  $V_{CS\_MAX}$  after a blanking time, a fault delay timer starts. If these thresholds are still reached after the timer expires (~20.5ms), the heavy load operation is disabled, and the IC stops switching for a hiccup time (~328ms). The IC resumes switching after the timer expires. Figure 29 shows the logic sequence.

Figure 29. Overload Protection Diagram

# 6. Application Topologies

Figure 30. Single-Phase RAA223183 Flyback with Cap-Saver  $V_{\text{IN}}$  Overvoltage Protection

Figure 31. Three-Phase RAA223183 Flyback without Cap-Saver Feature

## 7. Design Guidance

### 7.1 Input Bulk Capacitor

The input bulk capacitor provides a DC voltage with some voltage ripple for a given power. In other words, how low the bus voltage can drop determines the power Flyback can deliver. Equation 1 calculates the required minimum bus valley voltage for the target output power. To keep the bus valley above this value, the bulk capacitance needs to be big enough to not only support normal output power but also a short-time heavy load up to 2x normal output power. Use Equation 2 to calculate the required capacitance, where  $I_{PKFL}$  is the peak current required for your full load operation.  $D_{MAX}$  is the maximum duty cycle in DCM operation.  $\eta$  is the assumed full load efficiency at  $85V_{AC}$ .

$$\text{(EQ. 1)} \qquad \text{$V_{valley}$} = \frac{2P_{OUT}}{\eta I_{PKFL}D_{MAX}}$$

(EQ. 2)

$$C_{in} = \frac{4P_{OUT} \left(0.25 + \frac{1}{2\pi} asin \frac{\sqrt{2}V_{acmin} - V_{valley}}{\sqrt{2}V_{acmin}}\right)}{\eta(2V_{acmin}^2 - V_{valley}^2)f_{LINF}}$$

In 3-phase applications, when the regular output power is not more than 15W, the required  $V_{\text{valley}}$  is always guaranteed by the rectified voltage, even when AC input is at a minimum. Therefore, theologically, a bulk capacitor is not necessary to maintain the power delivery, even though a capacitor is often added to absorb surge energy.

### 7.2 Transformer Primary Inductance and Turns Ratio

Because the regulator operates in DCM, the primary inductance has to be chosen small enough so that the inductor current always resets within a switching cycle while still big enough to deliver enough power at minimum AC input. Accordingly, use Equation 3 to calculate the required primary inductance, while using Equation 4 to specify its maximum value. In 3-phase applications with regular output power less than 15W,  $V_{valley} = 1.5 \times \sqrt{2} \times V_{acmin}$ .

(EQ. 3)

$$L_P \ge \frac{2P_O}{\eta f_{SW} I^2_{PKFL}}$$

(EQ. 4)

$$L_P \le \frac{D_{MAX}V_{valley}}{f_{SW}I_{PKFI}}$$

The transformer turns ratio needs to be set appropriately so the duty cycle is not too big at the valley of the rectified bus voltage at the minimum AC input, even when it runs into 2x frequency operation. The maximum turns ratio can be calculated using Equation 5.  $D_{max}$  is the maximum duty cycle in 2x frequency operation. It can be chosen around 0.7. In 3-phase applications,  $V_{valley} = 1.5 \times \sqrt{2} \times V_{acmin}$ .

(EQ. 5)

$$N \le \frac{V_{valley}}{V_o} \times \frac{D_{max}}{1 - D_{max}}$$

In the meantime, the turns ratio needs to be big enough so that the maximum peak current can fully reset when Dmax is reached at the valley of the minimum AC input. The minimum turns ratio needs to satisfy Equation 6.

(EQ. 6)

$$N \ge \frac{L_P I_{PKFL} f_{SW}}{(1 - D_{MAX}) V_O}$$

### 7.3 Current-Sensing Resistor

The peak current is sensed through  $R_{SENSE}$  on the S pin and compared with the internal current command. When the sensed voltage reaches the command, the MOSFET is turned off. With the chosen  $R_{SENSE}$ , the max peak current is limited by an internal current sense voltage limit,  $V_{CS\_MAX}$ . To have a good regulation without hitting the peak current limit,  $V_{SENSE}$  should be set around  $0.9V_{CS\_MAX}$ . Use Equation 7 to calculate  $R_{SENSE}$ .

Note: R<sub>SENSE</sub> needs to be evaluated for proper power capability.

$$(EQ. 7) R_{SENSE} = \frac{0.9 V_{CSMAX}}{I_{PKFI}}$$

#### 7.4 FSET Pin Resistor

The FSET pin resistor sets the switching frequency. Use Equation 8 to calculate the resistor value.

(EQ. 8)

$$R_{FSET} = \frac{3.72 V_{FSET}}{f_{SW}} \times 10^6 (k\Omega)$$

#### 7.5 VDET Pin Resistors

The valley switching is detected at the VDET pin by a resistor divider ( $R_{DET1}$  and  $R_{DET2}$ ). Use Equation 9 to calculate the  $R_{DET1}$  value and Equation 10 to calculate the  $R_{DET2}$  value.  $N_{PA}$  is the turn ratio of the primary winding to auxiliary winding, and  $V_{ACMAX}$  is the maximum AC input voltage.  $N_{SA}$  is the turn ratio of the output winding to the auxiliary winding.  $V_{DF}$  is the forward voltage of the output diode.

(EQ. 9)

$$R_{DET1} \ge \frac{\sqrt{2}V_{ACMAX}}{N_{PA}}(k\Omega)$$

(EQ. 10)

$$R_{DET2} < \frac{R_{DET1} \times 5}{\frac{V_{DF} + V_{OUT}}{N_{SA}} - 5}$$

#### 7.6 PRO Pin Resistors

The PRO pin sets the  $V_{IN}$  OV threshold and  $V_{IN}$  UV threshold. The resistor divider must ensure  $V_{IN}$  OV protection at the correct bus voltage.

(EQ. 11)

$$R_{B1} = \frac{V_{BUSOV} - V_{BUSOV}R}{V_{BUSOV}R} \times R_{B2}$$

Where  $V_{BUSOV}$  is the maximum bus voltage allowed and is usually chosen slightly above the voltage rating of the input cap, C1, but below 110% of the rated cap voltage. To minimize the power dissipation,  $R_{B2}$  is usually chosen between  $5k-25k\Omega$ . When  $R_{B1}$  and  $R_{B2}$  are chosen, the  $V_{IN}$  UV threshold is set around

$V_{BUSOV}/(V_{BUSOV}R/V_{BUSUV}R)$  and  $V_{BUSOV}/(V_{BUSOV}R/V_{BUSUV}F)$  for  $V_{IN}$  rising and falling, respectively.

#### 7.7 PRO Pin Capacitor

The cap at the PRO pin,  $C_{B2}$ , helps filter out the noise to ensure normal operation of the IC. It also delays the voltage rise on the PRO pin when an input surge occurs so it does not trigger OV protection and keep the bulky capacitor connected to the BUS using the external FET. The capacitance of  $C_{B2}$  can be calculated according to the IEC61000-4-5 surge time specs by Equation 12, where  $V_{PROMAX} = V_{ACMAX} \times 1.414 \times R_{B1}/(R_{B1} + R_{B2})$ .

$$\text{(EQ. 12)} \quad \begin{array}{c} C_{B2} > \frac{30}{\left(\frac{R_{B1} \times R_{B2}}{R_{B1} + R_{B2}}\right) \times In\left(1 - \frac{V_{BUSOV\_R} - V_{PROMAX}}{625 \times R_{B2} / (R_{B1} + R_{B2}) - V_{PROMAX}}\right)^{-1}} (\mu F) \end{array}$$

### 7.8 MOSFET in Series with C1 (if used)

The MOSFET in series with C1 is turned off during the input OV, so it needs to have voltage rating of 650V so it can sustain a voltage as high as the rectified voltage of 450V<sub>AC</sub> input. Also, it needs to survive a lightning events when a surge current passes through. Together with input surge energy absorbing components, the FET needs to have at least 200V at 10A pulse conduction rating, specified by its SOA curve. For details about the input stage design recommendation for surge energy control, refer to *RTKA223183DE0000BU Evaluation Board Manual*.

### 7.9 OLV Pin Capacitor

The cap on the OLV programs the time duration when the short-time over load is allowed, which is recommended not to be more than 100ms. The absolute maximum over-load duration depends on the thermal capability of IC and circuit components. Use Equation 13 to calculate the cap value (C<sub>OVI</sub>) using 100ms duration.

(EQ. 13)

$$C_{OLV} \le \frac{I_{OVL}}{10V_{OVL}} (\mu F)$$

#### 7.10 HV Pin

When the maximum rectified bus voltage is less than 700V, connect the HV pin to the bus directly. If the application has a rectified voltage higher than 700V, a resistor is required between bus and the HV pin to ensure the HV pin voltage does not exceed its rating. Use Equation 14 to estimate the required resistor value.

(EQ. 14)

$$R_{HV} \ge \frac{V_{bus\_max} - 700}{0.3} (k\Omega)$$

*Note:* The resistor value should not be much bigger than the calculated value to ensure VCC can start up normally.

### 7.11 Output Capacitance

The minimum output capacitance is chosen by consideration of switching ripple, step load response, and in some applications, the required output hold-time when input is cut off.

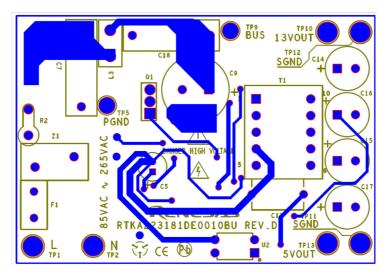

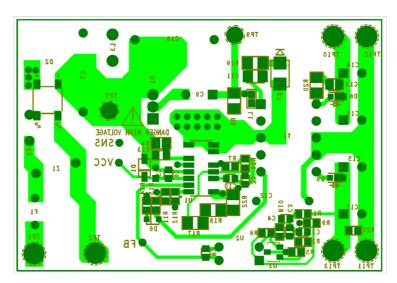

### 7.12 PCB Layout Guidance

Proper layout is important to ensure a stable operation, good thermal behavior, EMI performance, and reliable operation for various operating environments. Pay attention to the following layout recommendations:

- Leave proper spacing. Recommend a minimum of 1.5mm between traces with voltage differences up to 400V and 2mm between traces with voltage differences up to 780V.

- Keep a small loop from the input bulk capacitor, transformer primary winding, D pin, and S pin to the MOSFET source pin that is connected with the input bulk cap. Also keep a small loop consisting of the secondary winding, rectifier diode, and output capacitor.

- Use the star connection of ground traces as shown in the top layout picture (Figure 32). The connection point needs to be close to the IC ground pin.

- Place the VCC decoupling capacitor close to the VCC pin.

- Keep sufficient copper area on the IC drain pin (around 165mm<sup>2</sup> for single-phase 6W output or 3-phase 11W output) for better thermal performance.

- Make the traces connected to secondary rectifier diodes thick enough so they provide enough heat dissipation.

Figure 32 and Figure 33 show the PCB layout example.

Figure 32. Top Layer

Figure 33. Bottom Layer

## 8. EMI Performance

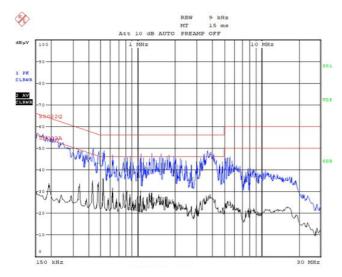

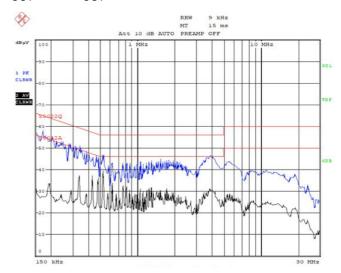

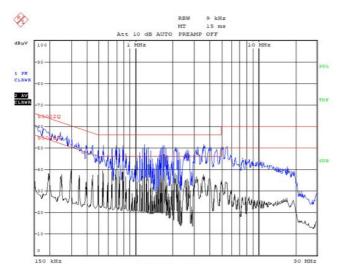

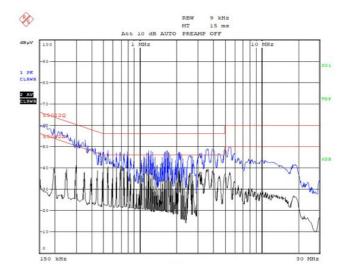

Conducted EMI pre-compliance for EN55022/CISPR22 ( $V_{OUT}$  = 13V,  $I_{OUT}$  = 540mA)

Figure 34. 120V<sub>AC</sub> Line

Figure 35. 120 $V_{\rm AC}$  Neutral

Figure 36. 230V<sub>AC</sub> Line

Figure 37. 230V<sub>AC</sub> Neutral

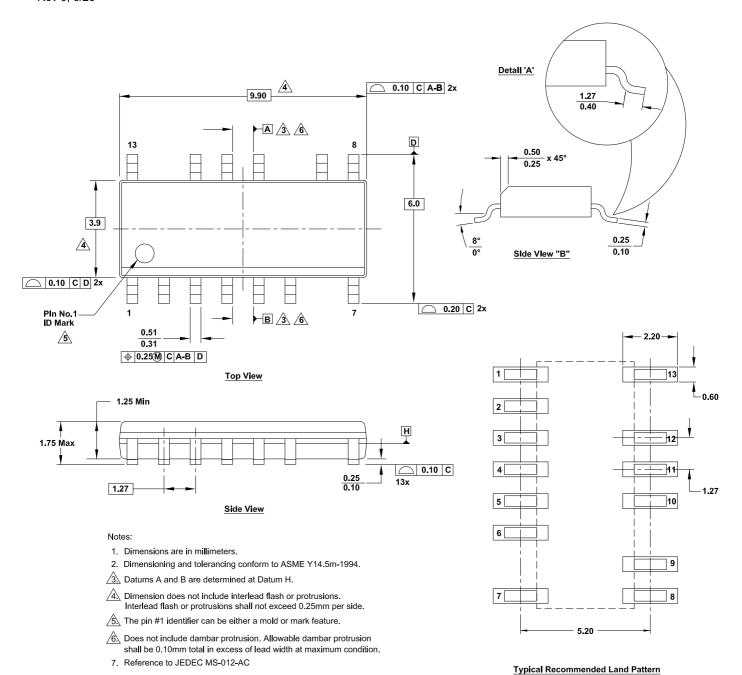

## 9. Package Outline Drawing

For the most recent package outline drawing, see M13.15.

M13.15

13 Lead Narrow Body Small Outline Plastic Package Rev 0, 6/20

## 10. Ordering Information

| Part Number <sup>[1][2]</sup> | Part<br>Marking                                 | Package Description <sup>[3]</sup><br>(RoHS Compliant) | Pkg. Dwg. # | Carrier Type <sup>[4]</sup> | Temp Range (°C) |

|-------------------------------|-------------------------------------------------|--------------------------------------------------------|-------------|-----------------------------|-----------------|

| RAA2231834GSP#HA0             | 223183                                          | SO13                                                   | M13.15      | Reel, 2.5k                  | -40 to +150     |

| RTKA223183DE0000BU            | Evaluation Board with RAA223183 in SO13 package |                                                        |             |                             |                 |

These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

- 2. For Moisture Sensitivity Level (MSL), see the RAA223183 device page. For more information about MSL, see TB363.

- 3. For the Pb-Free Reflow Profile, refer to TB493.

- 4. See TB347 for details about reel specifications.

Table 1. Key Differences of RAA22318x Products

| Devices   | Drain Voltage (V) | V <sub>IN</sub> UV Threshold (V) | V <sub>IN</sub> OV Threshold (V) | Action at V <sub>IN</sub> OV |

|-----------|-------------------|----------------------------------|----------------------------------|------------------------------|

| RAA223181 | 900               | 0.5/0.4                          | 4.5/4                            | Stop Switching               |

| RAA223182 | 1000              | 0.4/0.3                          | 4.7/4.2                          | Stop Switching               |

| RAA223183 | 1000              | 0.4/0.3                          | 4.7/4.2                          | Keep Switching               |

# 11. Revision History

| Revision | Date        | Description      |

|----------|-------------|------------------|

| 1.00     | Jul 6, 2023 | Initial release. |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/