# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

M66291GP/HP

ASSP (USB2.0 Device Controller)

# **1** Overview

The M66291 is a general purpose USB (Universal Serial Bus) device controller compliant with the USB Specification Revision 2.0 and supports full speed transfer. The USB transceiver circuit is included, and the M66291 meets all transfer types which are defined in the USB specification. The M66291 has FIFO of 3 Kbytes for data transfer and can set 7 endpoints (maximum). Each endpoint can be set programmable of its transfer condition, so can correspond to each device class transfer system of USB.

# 1.1 Features

- USB Specification Revision 2.0 compliant

- Supports Full Speed (12 Mbps) transfer

- Built-in USB transceiver circuit

- Built-in oscillation buffer (Supports 6M/12M/24 MHz of oscillator) and PLL at 48 MHz

- Supports Vbus direct connection (5 V withstand voltage input), D+ pin pullup output

- Supports all transfer type which is defined in the USB specification.(Control transfer / Bulk transfer / Interrupt transfer / Isochronous transfer)

- Low power consumption operation (Average 15 mA at operation)

- Robust against signal distortion on USB transfer line due to SIE/DPLL(Digital Phase Lock Loop) of the original design

- Easy making enumeration program and timing design because hardware manages the device state / control transfer state (transition timing)

- Reduction of CPU load due to continuous transmit/receive mode (the mode for buffering several transaction data into FIFO) This enables high performance and throughput improvement.

- Up to 7 endpoints (EP0 to EP6) selectable

- Data transfer condition selectable for each endpoint (EP1 to EP6)

- Compatible to various applications (device class)

- Data transfer type (Bulk transfer / Isochronous transfer / Interrupt transfer)

- Transfer direction (IN, OUT)

- Packet size

- Built-in FIFO buffer (3 Kbytes) for endpoints

- Buffering conditions of FIFO memory settable per endpoint (EP1 to EP6)

- FIFO buffer size (up to 1Kbyte)

- Presence/Absence of double buffer configuration (setting of buffer size x 2)

- Four pieces of configurable FIFO ports

- Endpoint number allocation

- Access method switching (CPU, DMAC)

- Bit width (8-bit / 16-bit)

- Endian switching

- "Interrupt queuing function" that eliminates the need of complicated factor analysis

- Connectable to various CPU/DMAC

- Bus width(8-bit / 16-bit)

- Interface voltage(2.7V to 5.5V)

- Interrupt signal and DMA control signal polarities settable

- Supports multi-word DMA (burst)

- FIFO access cycle of maximum 24 Mbytes/sec

Applications Support all PC peripheral built-in USB

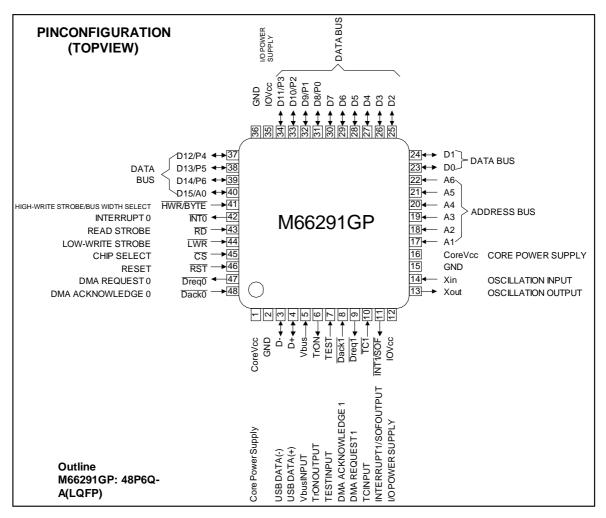

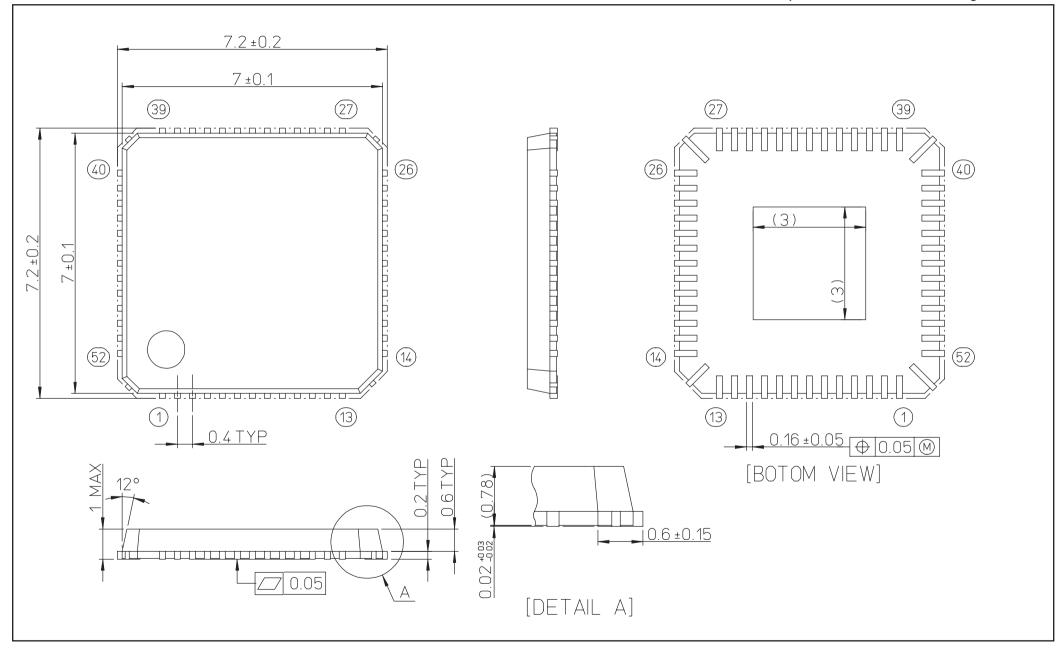

Figure 1.1-1 M66291GP Pin Configuration

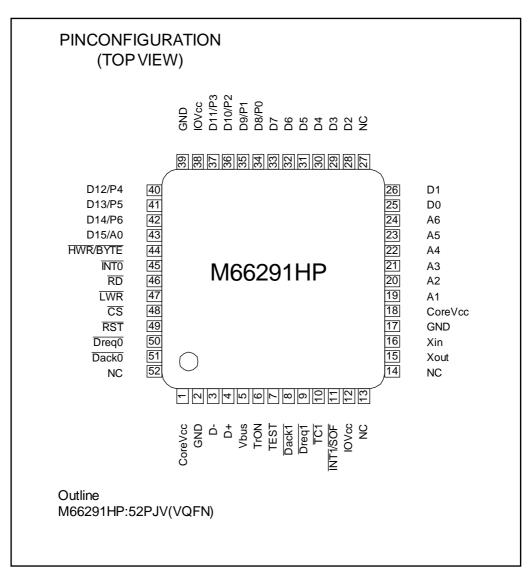

Figure 1.1-2 M66291HP Pin Configuration

# 1.2 Block Diagram

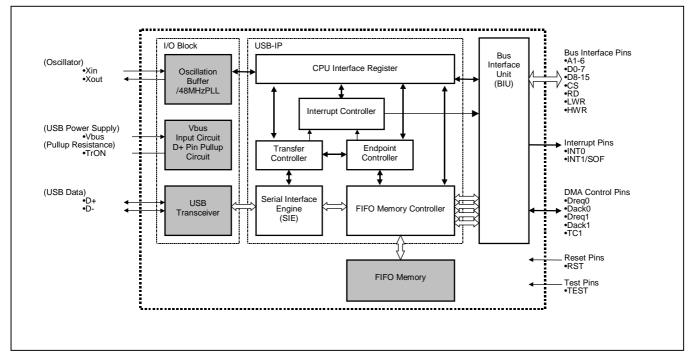

The M66291 contains an USB-IP block, an I/O block, a bus interface unit (BIU), and a FIFO memory.

Figure 1.2 M66291 Block Diagram

#### 1.2.1 USB-IP

The USB-IP block contains a serial interface engine, a transfer controller, an endpoint controller, a FIFO memory controller, an interrupt controller, and a CPU interface register.

#### (1) Serial Interface Engine (SIE)

The serial interface engine (SIE) executes low-order protocols processing of USB as follows:

- Extracts receive data/clock and generates transmit clock

- Serial parallel conversion of transmit/receive data

- NRZI (Non Return Zero Invert) encoding and decoding

- Bit stuffing and destuffing

- SYNC (Synchronization pattern) and EOP (End Of Packet) detection

- USB address and endpoint detection

- CRC (Cyclic Redundancy Check) generation and checking

#### (2) Transfer Controller

The transfer controller executes device state transition control and control transfer sequence control.

#### (3) Endpoint Controller

The endpoint controller executes status control per endpoint.

#### (4) FIFO Memory Controller

The FIFO memory controller controls the write/read of the transmit/receive data at SIE (USB bus) side and internal bus (CPU bus) side under state control by the endpoint controller.

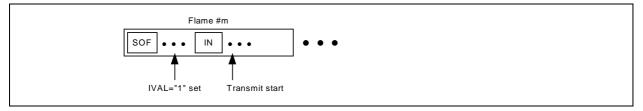

#### (5) Interrupt Controller

The interrupt controller outputs the status signals outputted by transfer controller and endpoint controller to INT0, INT1/SOF interrupt pins according to the CPU interface register setting.

#### (6) CPU Interface Register

The CPU interface register block is composed of the registers for mode setting, command setting and status reading.

#### 1.2.2 Bus Interface Unit (BIU)

The bus interface unit (BIU) is a circuit to conform USB-IP to LSI external bus.

#### 1.2.3 FIFO Memory

The FIFO memory is a FIFO for endpoint transmit/receive. It is possible to set 6 endpoints EP1 to EP6 in addition to EP0, the endpoint for control transfer.

#### 1.2.4 I/O Block

The I/O block is composed of USB transceiver, oscillation buffer, 48 MHz PLL, Vbus input circuit and D+ pin pullup control circuit.

#### (1) USB Transceiver

The USB transceiver, conforming to the USB Specification Revision 2.0, is composed of a pair of 2 pieces of drivers D+/D- complying with full speed transfer mode, a pair of 2 pieces of single end receivers and a differential input receiver. A serial resistance for impedance matching is needed external to the chip.

#### (2) Oscillation Buffer, 48 MHz PLL

The 48 MHz clock with accuracy  $\pm$  0.25% is needed at the USB-IP block. The M66291 has a built-in oscillation buffer and a 48 MHz PLL. The PLL is capable of setting the multiplication number depending on the program and can therefore be connected with an external oscillation of 6, 12 or 24 MHz. Further, it can also be operated by the external 48 MHz clock without using the PLL function.

#### (3) Vbus Input Circuit, D+ Pin Pullup Control Circuit

The M66291 is capable of learning the connection status with host/hub by means of Vbus pin, and can inform the state of preparation at device side to host/hub by turning on/off the 1.5 K $\Omega$  D+ pin pullup.

The Vbus input buffer which is 5 V tolerant can be directly connected to the Vbus pin on the USB bus.

The current from TrON pin is supplied by Vbus input. Since the D+/D- pins of USB bus are operated at 0 V to 3.3 V, the TrON pin reduces the voltage to 3.3 V before output.

Since the USB is constantly pulled down by 15 K $\Omega$  at host/hub side when connected electrically, a current of 0.2 mA continuously flows into the D+ pin through the pullup resistance.

# 1.3 Pin Functions

| Item      | Pin name   | Input/ | Function                                                                               | Pin   |

|-----------|------------|--------|----------------------------------------------------------------------------------------|-------|

|           |            | Output |                                                                                        | Count |

| Bus       | D7~D0      | Input/ | Data Bus                                                                               | 8     |

| interface |            | Output | This is a data bus to access the register from the system bus.                         |       |

|           | D14/P6~    | Input/ | Data Bus / Port Signal                                                                 | 7     |

|           | D8/P0      | Output | P6 to P0 are used as port signals when selected to 8-bit bus interface.                |       |

|           |            |        | D14 to D8 are used as data signals when selected to 16-bit bus interface.              |       |

|           | D15/A0     | Input/ | D15 Signal / A0 Signal                                                                 | 1     |

|           |            | Output | A0 (LSB) is used as an address signal when selected to 8-bit bus interface.            |       |

|           |            |        | D15 (MSB) is used as an data signal when selected to 16-bit bus interface.             |       |

|           | A6~A1      | Input  | Address Bus                                                                            | 6     |

|           |            |        | This is an address bus to access the register from the system bus.                     |       |

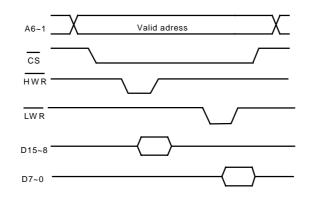

|           | *CS        | Input  | Chip Select                                                                            | 1     |

|           |            |        | "L" level enables communication with the M66291.                                       |       |

|           | *LWR       | Input  | Low-write Strobe                                                                       | 1     |

|           |            |        | The lower data (D7 to D0) is written to the register at "L" level.                     |       |

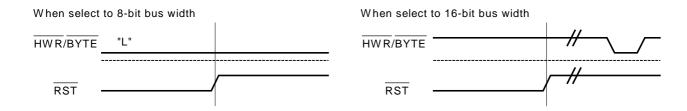

|           | *HWR/*BYTE | Input  | High-write Strobe / Bus Width Select                                                   | 1     |

|           |            |        | With the reset signal set to "H" level, the 8-bit bus interface is selected if this    |       |

|           |            |        | pin is at "L" level. Further, if this pin is at "H" level, the 16-bit bus interface is |       |

|           |            |        | selected. When the 16-bit bus interface is selected, the upper data (D15 to            |       |

|           |            |        | D8) is written to the register at "L" level.                                           |       |

|           |            |        | Fix to "L" level when set to 8-bit bus interface.                                      |       |

|           | *RD        | Input  | Read Strobe                                                                            | 1     |

|           |            |        | Data are read from registers at "L" level                                              |       |

| Interrupt | *INT0      | Output | Interrupt 0                                                                            | 1     |

| interface | (Note 1)   |        | Interrupts are requested to the system at "L" level.                                   |       |

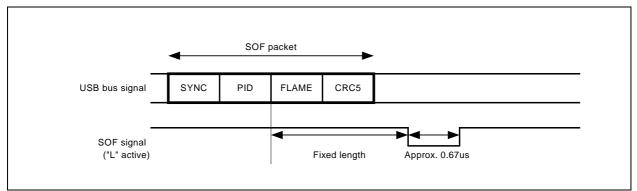

|           | *INT1/*SOF | Output | Interrupt 1 / SOF Output                                                               | 1     |

|           | (Note 1)   |        | This pin is used as an interrupt 1 or as a SOF output pin to transmit USB SOF          |       |

|           |            |        | signal according to register setting.                                                  |       |

| DMA       | *Dreq0     | Output | DMA Request 0                                                                          | 1     |

| interface | (Note 1)   |        | This pin is used to request DMA transfer to endpoint FIFO for DMA channel 0.           |       |

|           | *Dack0     | Input  | DMA Acknowledge 0                                                                      | 1     |

|           | (Note 1)   |        | This pin enables access of FIFO by DMA transfer for DMA channel 0.                     |       |

|           | *Dreq1     | Output | DMA Request 1                                                                          | 1     |

|           | (Note 1)   |        | This pin is used to request DMA transfer to endpoint FIFO for DMA channel 1.           |       |

| Item      | Pin Name | Input/                                        |                  | Function                                                                | Pin   |

|-----------|----------|-----------------------------------------------|------------------|-------------------------------------------------------------------------|-------|

|           |          | Output                                        |                  |                                                                         | Count |

| DMA       | *Dack1   | Input                                         | DMA Acknow       | wledge 1                                                                | 1     |

| interface | (Note1)  |                                               | This pin enat    | bles access of FIFO by DMA transfer for DMA channel 1.                  |       |

|           | *TC1     | Input                                         | Terminal Co      | unt 1                                                                   | 1     |

|           |          |                                               | This pin indic   | ates the final transfer cycle at "L" level for DMA channel 1.           |       |

|           |          |                                               | This is valid of | only in write cycle. Set to "H" level when not used.                    |       |

| USB       | D+       | Input/                                        | USB Data (+      | )                                                                       | 1     |

| interface |          | Output                                        | D+ of USB. C     | Connect an external resistance in series.                               |       |

|           | D-       | Input/                                        | USB Data (-)     |                                                                         | 1     |

|           |          | Output                                        | D- of USB. C     | onnect an external resistance in series.                                |       |

|           | Vbus     | with built-in pulldown resistance)            | 1                |                                                                         |       |

|           |          | ne Vbus of USB bus or to the 5V power supply. |                  |                                                                         |       |

|           |          |                                               | Connection of    | or shutdown of the Vbus can be detected.                                |       |

|           | TrON     | Output                                        | TrON Outpu       | t                                                                       | 1     |

|           |          |                                               | This pin is co   | nnected to the D+ pullup resistance of 1.5 K $\Omega$ .                 |       |

|           |          |                                               | This pin is us   | ed to control ON/OFF of the pullup resistance.                          |       |

| Others    | *RST     | Input                                         | Reset            |                                                                         | 1     |

|           |          |                                               | This pin is us   | sed to initialize the values of the internal register or the counter at |       |

|           |          |                                               | "L" level.       | 1                                                                       |       |

|           | Xin      | Input                                         | Oscillator       | These pins are used to input/output the signals of internal clock       | 1     |

|           |          |                                               | Input            | oscillation circuits. Connect a crystal unit between Xin and Xout       |       |

|           |          |                                               |                  | pins.                                                                   |       |

|           | Xout     | Output                                        | Oscillator       | If an external clock signal is used, connect it to the Xin pin and      | 1     |

|           |          |                                               | Output           | leave the Xout pin open.                                                |       |

|           | TEST     | Input                                         | TEST Input       | (with built-in pulldown resistance)                                     | 1     |

|           |          |                                               | This pin is in   | out for the test. Set to "L" level or keep open.                        |       |

|           | CoreVcc  | —                                             | Core Power       | Supply                                                                  | 2     |

|           | (Note 2) |                                               | These pins a     | re used as the power source for internal logic, FIFO memory, PLL        |       |

|           |          |                                               | circuit, USB t   | ransceiver and oscillation buffer.                                      |       |

|           | IOVcc    |                                               | I/O Power S      | upply                                                                   | 2     |

|           | (Note 3) |                                               |                  |                                                                         |       |

|           | GND      |                                               | Ground           |                                                                         | 3     |

A pin preceded by an asterisk "\*" is an active low pin.

(Example: \*CS pin is an active low,  $\overline{CS}$ )

- Note 1: The polarities of \*Dreq, \*Dack, \*INT, and \*SOF pins can be changed by the internal registers.

- Note 2: The Xin, Xout, Vbus, D+ and D- pins are all driven by CoreVcc.

- Note 3: The pins for bus interface, interrupt, DMA control, reset and test are all driven by IOVcc. See Figure 1.2.

# **2**Registers

| Bit Nu                                                                                                                                                                  | umbers                            | :                                                                                                                   |                                                   | -                    |                                       |                            |                          |          |       |         |   |         |                                                                                                                                                                                   |                                                 | mbers<br>es are l                                   |                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------|---------------------------------------|----------------------------|--------------------------|----------|-------|---------|---|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------|---------------------|

| State                                                                                                                                                                   | of Regi                           | ster at                                                                                                             | Reset                                             | :                    |                                       |                            |                          |          |       |         |   |         |                                                                                                                                                                                   |                                                 |                                                     |                     |

|                                                                                                                                                                         |                                   |                                                                                                                     | The "                                             | H/W re               | eset" is                              | s the re                   | eset by                  | an ex    |       | reset s |   |         |                                                                                                                                                                                   |                                                 |                                                     | al numb<br>et by th |

| At Re                                                                                                                                                                   | ad:                               |                                                                                                                     | ?<br>0                                            | Read<br>Read         | enable<br>disable<br>always<br>always | ed (Rea<br>s as 0          | ad valu                  | ue inva  | alid) |         |   |         |                                                                                                                                                                                   |                                                 |                                                     |                     |

| <ul> <li>1 Read always as 1</li> <li>D At Write:</li> <li>O Write enabled</li> <li>Δ Write enable conditionally (includes some conditions at write)</li> <li></li></ul> |                                   |                                                                                                                     |                                                   |                      |                                       |                            |                          |          |       |         |   |         |                                                                                                                                                                                   |                                                 |                                                     |                     |

|                                                                                                                                                                         |                                   |                                                                                                                     |                                                   |                      |                                       |                            |                          |          |       |         |   |         |                                                                                                                                                                                   |                                                 |                                                     |                     |

| Example                                                                                                                                                                 | of repre                          | esentati                                                                                                            | on>                                               |                      |                                       |                            |                          |          |       |         |   |         |                                                                                                                                                                                   |                                                 |                                                     |                     |

| ot implem                                                                                                                                                               | nented i                          |                                                                                                                     | haded                                             |                      |                                       |                            |                          |          |       |         |   |         |                                                                                                                                                                                   |                                                 |                                                     |                     |

| ot implem<br>① →<br>V reset -<br>V reset -                                                                                                                              | nented i                          | Abit                                                                                                                | haded<br>13<br>Bbit<br>0                          | 12<br>Cbit<br>0      | n.<br>11                              | 10                         | 9                        | 8        | 7     | 6       | 5 | 4       | 3                                                                                                                                                                                 | 2                                               | 1                                                   | b0                  |

| ot implen<br>① →<br>V reset -                                                                                                                                           | nented i                          | in the s<br>14<br>Abit<br>0                                                                                         | haded<br>13<br>Bbit<br>0                          | 12<br>Cbit<br>0      |                                       | 10                         | 9                        | 8        | 7     | 6       | 5 | 4       | 3                                                                                                                                                                                 | 2                                               | 1                                                   | b0                  |

| ot implem<br>① →<br>V reset -<br>V reset -                                                                                                                              | nented i                          | Abit                                                                                                                | haded<br>13<br>Bbit<br>0                          | 12<br>Cbit<br>0      |                                       | 10                         | 9                        | 8        | 7     | 6       | 5 |         | @                                                                                                                                                                                 |                                                 | 1                                                   |                     |

| ot implem<br>① →<br>V reset -<br>V reset -                                                                                                                              | nented i                          | Abit                                                                                                                | haded<br>13<br>Bbit<br>0                          | 12<br>Cbit<br>0      |                                       | 10                         | 9                        | 8        | 7     | 6       | 5 |         | ②<br>I/W res                                                                                                                                                                      | Set : H                                         |                                                     |                     |

| ot implem<br>① →<br>V reset -<br>V reset -                                                                                                                              | nented i                          | Abit                                                                                                                | haded<br>13<br>Bbit<br>0                          | 12<br>Cbit<br>0      |                                       | 10                         | 9                        | 8        | 7     | 6       | 5 | <h></h> | ②<br>I/W res<br><s< td=""><td>set : H</td><td>l'0000&gt;</td><td></td></s<>                                                                                                       | set : H                                         | l'0000>                                             |                     |

| ot implem<br>① →<br>V reset -<br>V reset -                                                                                                                              | nented i<br>b15<br>0<br>0<br>0    | Abit                                                                                                                | haded<br>13<br>Bbit<br>0<br>0                     | 12<br>Cbit<br>0      |                                       |                            | 9<br>Junctio             |          | 7     | 6       | 5 | <h></h> | ②<br>I/W res<br><s< td=""><td>set : H</td><td>l'0000&gt;<br/>set : -&gt;</td><td></td></s<>                                                                                       | set : H                                         | l'0000><br>set : ->                                 |                     |

| Dt implem<br>① →<br>V reset -<br>V reset -<br>B bus reset -                                                                                                             | b15<br>0<br>0<br>0<br>0<br>0      | Abit                                                                                                                | haded<br>13<br>Bbit<br>0<br>0                     | 12<br>Cbit<br>0      |                                       |                            |                          |          | 7     | 6       | 5 | <h></h> | ②<br>I/W res<br><s< td=""><td>set : H<br/>S/W re<br/>ous re</td><td>''0000&gt;<br/>set : -&gt;<br/>set : -&gt;</td><td></td></s<>                                                 | set : H<br>S/W re<br>ous re                     | ''0000><br>set : -><br>set : ->                     |                     |

| Dt implem<br>① →<br>V reset -<br>V reset -<br>B bus reset -                                                                                                             | b15<br>0<br>0<br>0<br>0<br>B<br>R | Abit<br>0<br>0<br>0<br>0                                                                                            | haded<br>13<br>Bbit<br>0<br>0                     | 12<br>Cbit<br>0      |                                       | F                          | unctio                   | n        | 7     |         | 5 | <h></h> | ②<br>I/W res<br><s< td=""><td>Set : H<br/>G/W re<br/>Dus re</td><td>''0000&gt;<br/>set : -&gt;<br/>set : -&gt;<br/>W</td><td></td></s<>                                           | Set : H<br>G/W re<br>Dus re                     | ''0000><br>set : -><br>set : -><br>W                |                     |

| U reset -<br>V reset -<br>B bus reset -                                                                                                                                 | B                                 | Abit<br>Abit<br>0<br>0<br>0<br>8it name                                                                             | haded<br>13<br>Bbit<br>0<br>0<br>0<br>0<br>e<br>e | 12<br>Cbit<br>0<br>0 |                                       | F                          | unctio                   | <u>n</u> |       |         | 5 | <h></h> | ②<br>I/W res<br><s< td=""><td>set : H<br/>S/W re<br/>Dus re<br/>R<br/>0</td><td>1'0000&gt;<br/>set : -&gt;<br/>set : -&gt;<br/>W<br/>-</td><td></td></s<>                         | set : H<br>S/W re<br>Dus re<br>R<br>0           | 1'0000><br>set : -><br>set : -><br>W<br>-           |                     |

| U reset -<br>V reset -<br>B bus reset -                                                                                                                                 | B<br>B<br>R<br>A<br>(-            | Abit<br>Abit<br>0<br>0<br>8it name<br>Reserve                                                                       | haded<br>13<br>Bbit<br>0<br>0<br>0<br>0<br>e<br>e | 12<br>Cbit<br>0<br>0 |                                       | F<br>0<br>1                |                          | n        |       | -       | 5 | <h></h> | ②<br>I/W res<br><s< td=""><td>set : H<br/>S/W re<br/>Dus re<br/>R<br/>0</td><td>1'0000&gt;<br/>set : -&gt;<br/>set : -&gt;<br/>W<br/>-</td><td></td></s<>                         | set : H<br>S/W re<br>Dus re<br>R<br>0           | 1'0000><br>set : -><br>set : -><br>W<br>-           |                     |

| U reset -<br>V reset -<br>B bus reset -<br>B bus reset -                                                                                                                | B<br>B<br>R<br>A<br>(-            | Abit<br>Abit<br>Abit<br>Bit name<br>Reserve                                                                         | haded<br>13<br>Bbit<br>0<br>0<br>0<br>0<br>e<br>e | 12<br>Cbit<br>0<br>0 |                                       | F<br>0<br>1<br>0           |                          | n        |       | -       | 5 | <h></h> | ②<br>I/W res<br><s< td=""><td>Set : H<br/>G/W re<br/>Dus re<br/>R<br/>0<br/>0</td><td>1'0000&gt;<br/>set : -&gt;<br/>set : -&gt;<br/>W<br/>-<br/>0</td><td></td></s<>             | Set : H<br>G/W re<br>Dus re<br>R<br>0<br>0      | 1'0000><br>set : -><br>set : -><br>W<br>-<br>0      |                     |

| U reset -<br>V reset -<br>B bus reset -<br>B bus reset -                                                                                                                | B<br>B<br>R<br>A<br>(-            | Abit<br>Abit<br>Abit<br>Bit name<br>Reserve                                                                         | haded<br>13<br>Bbit<br>0<br>0<br>0<br>0<br>e<br>e | 12<br>Cbit<br>0<br>0 |                                       | F<br>0<br>1<br>0<br>1<br>0 | [unction]<br>:<br>:<br>: | n        |       | -       | 5 | <h></h> | ②<br>I/W res<br><s< td=""><td>Set : H<br/>G/W re<br/>Dus re<br/>R<br/>0<br/>0</td><td>1'0000&gt;<br/>set : -&gt;<br/>set : -&gt;<br/>W<br/>-<br/>0</td><td></td></s<>             | Set : H<br>G/W re<br>Dus re<br>R<br>0<br>0      | 1'0000><br>set : -><br>set : -><br>W<br>-<br>0      |                     |

| U reset<br>V reset<br>V reset<br>B bus reset<br>D<br>15<br>14<br>13                                                                                                     | B<br>B<br>R<br>A<br>(-            | Abit<br>Abit<br>Abit<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O | haded<br>13<br>Bbit<br>0<br>0<br>0<br>0<br>e<br>e | 12<br>Cbit<br>0<br>0 |                                       | F<br>0<br>1<br>0<br>1<br>0 | [unction]<br>:<br>:<br>: | n        |       | -       | 5 | <h></h> | ②<br>I/W res<br><s< td=""><td>set : H<br/>s/W re<br/>bus re<br/>R<br/>0<br/>0<br/>0</td><td>l'0000&gt;<br/>set : -&gt;<br/>set : -&gt;<br/>W<br/>-<br/>0<br/>0</td><td></td></s<> | set : H<br>s/W re<br>bus re<br>R<br>0<br>0<br>0 | l'0000><br>set : -><br>set : -><br>W<br>-<br>0<br>0 |                     |

The M66291 register mapping is shown in Figure 2.1 and Figure 2.2, and each register is described below.

| Address               | +1 ad          | dress         | +0 ad          | dress    |        |        | Reset state | •       |

|-----------------------|----------------|---------------|----------------|----------|--------|--------|-------------|---------|

|                       | b15            | b8            | b7             |          | b0     | H/W    | S/W         | USB bus |

| H'00                  | USE            | 3 Operation   | Enable Regi    | ster     |        | H'0000 | -           | -       |

| H'02                  | F              | Remote Wak    | eup Registe    | r        |        | H'0000 | H'0000      | -       |

| H'04                  | Se             | equence Bit   | Clear Regist   | er       |        | H'0000 | H'0000      | -       |

| H'06                  |                | (Rese         | erved)         |          |        |        |             |         |

| H'08                  |                | USB_Addre     | ess Register   |          |        | H'0000 | H'0000      | H'0000  |

| H'0A                  | lso            | ochronous S   | Status Regist  | er       |        | H'0000 | H'0000      | -       |

| H'0C                  |                | SOF Contr     | ol Register    |          |        | H'0000 | H'0000      | -       |

| H'0E                  |                | Polarity Se   | et Register    |          |        | H'0000 | H'0000      | -       |

| H'10                  | Ir             | terrupt Enal  | ble Register   | 0        |        | H'0000 | H'0000      | -       |

| H'12                  | Ir             | iterrupt Enal | ble Register   | 1        |        | H'0000 | H'0000      | -       |

| H'14                  | Ir             | iterrupt Enal | ble Register   | 2        |        | H'0000 | H'0000      | -       |

| H'16                  | Ir             | iterrupt Enal | ble Register   | 3        |        | H'0000 | H'0000      | -       |

| H'18                  | Ir             | nterrupt Stat | us Register (  | 0        |        | H'0000 | H'0000      | Note    |

| H'1A                  | Ir             | nterrupt Stat | us Register    | 1        |        | H'0000 | H'0000      | -       |

| H'1C                  | Ir             | nterrupt Stat | us Register 2  | 2        |        | H'0000 | H'0000      | -       |

| H'1E                  | Ir             | nterrupt Stat | us Register 3  | 3        |        | H'0000 | H'0000      | -       |

| H'20                  |                | Request       | Register       |          |        | H'0000 | H'0000      | -       |

| H'22                  |                | Value F       | Register       |          |        | H'0000 | H'0000      | -       |

| H'24                  |                | Index F       | Register       |          |        | H'0000 | H'0000      | -       |

| H'26                  |                | Length        | Register       |          |        | H'0000 | H'0000      | -       |

| H'28                  | Cont           | rol Transfer  | Control Reg    | ister    |        | H'0000 | -           | -       |

| H'2A                  | E              | P0 Packet     | Size Registe   | r        |        | H'0008 | -           | -       |

| H'2C                  | Automa         | atic Respon   | se Control R   | egister  |        | H'0000 | -           | -       |

| H'2E                  |                | (Rese         | erved)         |          |        |        |             |         |

| H'30                  | E              | P0_FIFO S     | elect Registe  | er       |        | H'0000 | -           | -       |

| H'32                  | E              | P0_FIFO Co    | ontrol Registe | ər       |        | H'0800 | -           | -       |

| H'34                  | E              | EP0_FIFO D    | Data Register  |          |        | ????   | -           | -       |

| H'36                  | EP0_FIFO Co    | ontinuous Tra | nsmit Data Le  | ngth Rec | jister | H'0000 | -           | -       |

| te : Refer to each re | egister descri | bed below.    |                |          |        |        |             |         |

Figure 2.1 Register Mapping (1)

| Address | 1 address            | 10 address        | 1      | Depet state |         |

|---------|----------------------|-------------------|--------|-------------|---------|

| Address | +1 address<br>b15 b8 | +0 address        | D H/W  | Reset state | USB bus |

| H'38    |                      | erved)            |        | 0,11        | 000 003 |

| H'3A    | · · · · · ·          | erved)            |        |             |         |

| H'3C    |                      | erved)            |        |             |         |

| H'3E    |                      | erved)            |        |             |         |

| H'40    | •                    | Select Register   | H'0000 | -           | -       |

| H'42    |                      | ontrol Register   | H'0800 | -           | -       |

| H'44    | CPU_FIFO             | Data Register     | ????   | -           | -       |

| H'46    | SIE_FIFO S           | tatus Register    | H'0000 | -           | -       |

| H'48    | D0_FIFO S            | elect Register    | H'0000 | -           | -       |

| H'4A    | D0_FIFO Co           | ontrol Register   | H'0800 | -           | -       |

| H'4C    | D0_FIFO D            | Data Register     | ????   | -           | -       |

| H'4E    | DMA0_Transacti       | on Count Register | H'0000 | -           | -       |

| H'50    | D1_FIFO Se           | elect Register    | H'0000 | -           | -       |

| H'52    | D1_FIFO Co           | ontrol Register   | H'0800 | -           | -       |

| H'54    | D1_FIFO D            | ata Register      | ????   | -           | -       |

| H'56    | DMA1_Transacti       | on Count Register | H'0000 | -           | -       |

| H'58    | FIFO Stat            | us Register       | H'0000 | H'0000      | -       |

| H'5A    | Port Cont            | rol Register      | H'0000 | -           | -       |

| H'5C    | Port Dat             | a Register        | H'0000 | -           | -       |

| H'5E    | Drive Current        | Adjust Register   | H'0000 | -           | -       |

| H'60    | EP1 Configura        | ation Register 0  | H'0000 | -           | -       |

| H'62    | EP1 Configura        | ation Register 1  | H'0040 | -           | -       |

| H'64    | EP2 Configura        | ation Register 0  | H'0000 | -           | -       |

| H'66    | EP2 Configura        | ation Register 1  | H'0040 | -           | -       |

| H'68    | EP3 Configura        | ation Register 0  | H'0000 | -           | -       |

| H'6A    | EP3 Configura        | ation Register 1  | H'0040 | -           | -       |

| H'6C    | EP4 Configura        | ation Register 0  | H'0000 | -           | -       |

| H'6E    | EP4 Configura        | ation Register 1  | H'0040 | -           | -       |

| H'70    | EP5 Configura        | ation Register 0  | H'0000 | -           | -       |

| H'72    | EP5 Configura        | ation Register 1  | H'0040 | -           | -       |

| H'74    | EP6 Configura        | ation Register 0  | H'0000 | -           | -       |

| H'76    | EP6 Configura        | ation Register 1  | H'0040 | -           | -       |

Figure 2.2 Register Mapping (2)

# 2.1 USB Operation Enable Register

■ USB Operation Enable Register (USB\_ENABLE)

#### <Address : H'00>

| b15  | 14   | 13 | 12  | 11   | 10    | 9   | 8     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | b0   |

|------|------|----|-----|------|-------|-----|-------|---|---|---|---|---|---|---|------|

| XCKE | PLLC | X  | tal | SCKE | USBPC | Tr_ | Tr_on |   |   |   |   |   |   |   | USBE |

| 0    | 0    | 0  | 0   | 0    | 0     | 0   | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    |

| -    | -    | -  | -   | -    | -     | -   |       |   | - | - | - | - | - | - | -    |

| -    | -    | -  | -   | -    | -     | -   | -     | - | - | - | - | - | - | - | -    |

<H/W reset : H'0000>

<S/W reset : ->

|       | U>                            |                                                               |   |   |  |  |  |  |  |

|-------|-------------------------------|---------------------------------------------------------------|---|---|--|--|--|--|--|

| b     | Bit name                      | Function                                                      | R | W |  |  |  |  |  |

| 15    | XCKE                          | 0: Disable oscillation buffer (Disable clock supply to inside | 0 | 0 |  |  |  |  |  |

|       | Oscillation Buffer Enable     | PLL)                                                          |   |   |  |  |  |  |  |

|       |                               | 1: Enable oscillation buffer (Enable clock supply to inside   |   |   |  |  |  |  |  |

|       |                               | PLL)                                                          |   |   |  |  |  |  |  |

| 14    | PLLC                          | 0: Disable PLL (PLL through)                                  | 0 | 0 |  |  |  |  |  |

|       | PLL Operation Enable          | 1 : Enable PLL                                                |   |   |  |  |  |  |  |

| 13~12 | Xtal                          | 00: External clock frequency : 48 MHz (PLL through)           | 0 | 0 |  |  |  |  |  |

|       | Clock Select                  | 10 : External clock frequency : 24 MHz                        |   |   |  |  |  |  |  |

|       |                               | 01: External clock frequency : 12 MHz                         |   |   |  |  |  |  |  |

|       |                               | 11 : External clock frequency : 6 MHz                         |   |   |  |  |  |  |  |

| 11    | SCKE                          | 0: Disable Internal clock                                     | 0 | 0 |  |  |  |  |  |

|       | Internal Clock Enable         | 1 : Enable Internal clock                                     |   |   |  |  |  |  |  |

| 10    | USBPC                         | 0: Disable USB transceiver                                    | 0 | 0 |  |  |  |  |  |

|       | USB Transceiver Power Control | 1: Enable USB transceiver                                     |   |   |  |  |  |  |  |

| 9~8   | Tr_on                         | 00 : TrON output ="Hi-Z" (SIE operate stop)                   | 0 | 0 |  |  |  |  |  |

|       | Tr_on Output Control          | 01 : TrON output ="L"                                         |   |   |  |  |  |  |  |

|       |                               | 10: Reserved                                                  |   |   |  |  |  |  |  |

|       |                               | 11 : TrON output ="H"                                         |   |   |  |  |  |  |  |

| 7~1   | Reserved. Set it to "0".      |                                                               | 0 | 0 |  |  |  |  |  |

| 0     | USBE                          | 0: S/W reset state                                            | 0 | 0 |  |  |  |  |  |

|       | USB Module Operation Enable   | 1: S/W reset state release                                    |   |   |  |  |  |  |  |

#### (1) XCKE (Oscillation Buffer Enable) Bit (b15)

.

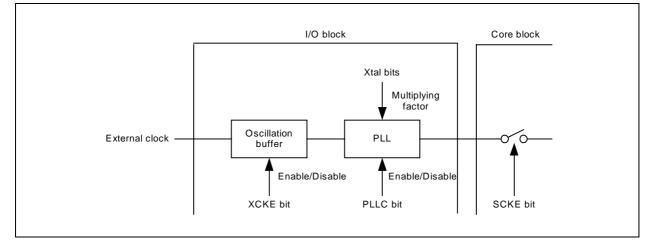

This bit sets enable/disable of the oscillation buffer. The output clock from the oscillation buffer is supplied to the PLL. Refer to Figure 2.3.

#### (2) PLLC (PLL Operation Enable) Bit (b14)

This bit sets enable/disable of PLL.

When this bit is set to "1", the external clock into the PLL is multiplied according to the value set in the Xtal bits before being output to the core block. Set the XCKE bit to "1" and wait until the oscillation circuit starts and becomes stable before setting this bit to "1".

When this bit is set to "0", PLL stops operation and the external clock into the PLL is output to the core block without being multiplied. Hence, be sure to supply the 48 MHz clock to the oscillation buffer when setting this bit to "0".

Refer to Figure 2.3.

#### (3) Xtal (Clock Select) Bits (b13~b12)

These bits set the multiplication factor of the external clock into PLL. Since it is necessary to supply 48 MHz to the core block, the setting values of these bits are determined by the clock frequency to be input into the PLL. Refer to Figure 2.3.

#### (4) SCKE (Internal Clock Enable) Bit (b11)

This bit sets the clock supply into the core block. Set the PLLC bit to "1" and wait until the oscillation of the PLL stabilizes before setting this bit to "1". Refer to Figure 2.3.

#### Figure 2.3 Clock Control

#### (5) USBPC (USB Transceiver Power Control) Bit (b10)

This bit sets the enable/disable of the USB transceiver block of I/O block. Even if this bit is set to "0", it is possible to receive the resume signal during the Suspended state (DVSQ bits = "1xx"). It is necessary that the Tr\_on bits be set to "x1" (during operation of SIE block).

#### (6) Tr\_on (Tr\_on Output Control) Bits (b9~b8)

These bits set the TrON signal output from I/O block and the enable/disable of SIE block in core block.

#### (7) USBE (USB Module Operation Enable) Bit (b0)

```

This bit sets S/W reset.

```

When this bit is set to "0", the M66291 enters the S/W reset state and the registers are set to their S/W reset state.

•

# 2.2 Remote Wakeup Register

■ Remote Wakeup Register (REMOTE\_WAKEUP)

<Address : H'02>

| b15  | 14                       | 13                                                           | 12    | 11  | 10 | 9 | 8     | 7        | 6          | 5        | 4         | 3    | 2 | 1       | b    | 0    |

|------|--------------------------|--------------------------------------------------------------|-------|-----|----|---|-------|----------|------------|----------|-----------|------|---|---------|------|------|

|      |                          |                                                              |       |     |    |   |       |          |            |          |           |      |   |         | WK   | UP.  |

| 0    | 0                        | 0                                                            | 0     | 0   | 0  | 0 | 0     | 0        | 0          | 0        | 0         | 0    | 0 | 0       | 0    | )    |

| 0    | 0                        | 0                                                            | 0     | 0   | 0  | 0 | 0     | 0        | 0          | 0        | 0         | 0    | 0 | 0       | C    | )    |

| -    | -                        | -                                                            | -     | -   | -  | - | -     | -        | -          | -        | -         | -    | - | -       | -    |      |

|      |                          | <h r<br="" w=""><s r<="" td="" w=""><td>&lt;000</td></s></h> |       |     |    |   |       |          |            |          |           |      |   |         |      | <000 |

|      |                          |                                                              |       |     |    |   |       |          |            |          |           |      | < | JSB bus | rese | t:-> |

| b    |                          |                                                              | Bit n | ame |    |   |       |          |            | Functi   | on        |      |   |         | R    | W    |

| 15~1 | Reserved. Set it to "0". |                                                              |       |     |    |   |       |          |            |          |           |      |   |         | 0    | 0    |

| 0    | WKUP Read                |                                                              |       |     |    |   |       |          |            |          |           |      |   | (       | 0    | 0    |

|      | Remo                     | te Wake                                                      | up    |     |    |   | 0: Do | not outp | out the re | emote wa | akeup sig | gnal |   |         |      |      |

# 1: Output the remote wakeup signal Write 0: 0: Invalid (Ignored when written) 1: Output the remote wakeup signal

#### (1) WKUP (Remote Wakeup) Bit (b0)

This bit controls the output of the remote wakeup signal (K state output).

This bit is valid only when the device state is "suspend" (DVSQ bits = "1xx"). The writing of "1" to this bit is ignored when the device state is not suspend.

When "1" is written to this bit, the K state is output for 10 ms. The bit is automatically cleared to "0" after K state output.

The bus idle state continues (this WKUP bit = "1") for 2 ms after the Suspend state is detected when "1" is written to this bit before outputting the K state for 10 ms.

The 2 ms and 10 ms time intervals are counted using a clock. Make sure that the counting stops if the clock is not supplied (Note).

Note : SCKE bit = "0" when XCKE bit = "1 ", or XCKE bit = "0".

# 2.3 Sequence Bit Clear Register

| ■ Seq | uence E | Bit Clea | r Regist | ter (SEC | QUENC | E_BIT) |       |                        |   |        |    |       | <ac< th=""><th>ddress</th><th>: H'</th><th>04&gt;</th></ac<> | ddress | : H' | 04>    |

|-------|---------|----------|----------|----------|-------|--------|-------|------------------------|---|--------|----|-------|--------------------------------------------------------------|--------|------|--------|

| b15   | 14      | 13       | 12       | 11       | 10    | 9      | 8     | 7                      | 6 | 5      | 4  | 3     | 2                                                            | 1      | ł    | o0     |

|       |         |          |          |          |       |        |       |                        |   |        |    | SQCLR |                                                              |        |      |        |

| 0     |         |          |          |          |       |        |       |                        |   |        |    |       |                                                              |        |      | 0      |

| 0     |         |          |          |          |       |        |       |                        |   |        |    |       |                                                              |        |      | 0      |

| b     |         |          |          |          |       |        |       |                        |   |        |    |       |                                                              |        |      | <0000> |

| 15~7  | Deser   | und Cat  |          |          |       |        |       |                        |   | T uncu |    |       |                                                              |        | R    |        |

|       |         | ved. Set | 11 10 0. |          |       |        |       |                        |   |        |    |       |                                                              |        | 0    | 0      |

| 6~0   | SQCL    | .R       |          |          |       |        | Write |                        |   |        |    |       |                                                              |        | 0    | 0      |

|       | Seque   | ence Bit | Clear    |          |       |        |       | valid (Ign<br>ear Sequ |   |        | n) |       |                                                              |        |      |        |

#### (1) SQCLR (Sequence Bit Clear) Bits (b6~b0)

These bits clear the sequence bit (the bit controlled by H/W) and turns the data PID into DATA 0 PID. This bit immediately returns to "0" after writing "1".

corresponds to EP0.

b6 corresponds to EP6, ---b1 corresponds to EP1 and b0

In the transfers after the sequence bit is cleared, the sequence bit is toggled through H/W control. At S/W reset (USBE bit = "1") and USB bus reset, the sequence bit of each endpoint is not cleared.

#### Note : Be sure to set the response PID of the endpoint whose sequence bit is desired to be cleared to NAK (EP0\_PID bits = "00"/EPi\_PID bits = "00") before writing "1" to this bit.

# 2.4 USB\_Address Register

| ■ USB | USB_Address Register (USB_ADDRESS) <address :="" h<="" th=""><th>: H'(</th><th>)8&gt;</th></address> |    |       |     |    |   |   |   |   |        |    |   |   |                                       | : H'( | )8>   |

|-------|------------------------------------------------------------------------------------------------------|----|-------|-----|----|---|---|---|---|--------|----|---|---|---------------------------------------|-------|-------|

| b15   | 14                                                                                                   | 13 | 12    | 11  | 10 | 9 | 8 | 7 | 6 | 5      | 4  | 3 | 2 | 1                                     | b     | 0     |

|       | USB_Addr                                                                                             |    |       |     |    |   |   |   |   |        |    |   |   |                                       |       |       |

| 0     |                                                                                                      |    |       |     |    |   |   |   |   |        |    | 0 | 1 | 0                                     |       |       |

| 0     | 0                                                                                                    | 0  | 0     | 0   | 0  | 0 | 0 | 0 | 0 | 0      | 0  | 0 | 0 | 0                                     |       | 0     |

| 0     | 0                                                                                                    | 0  | 0     | 0   | 0  | 0 | 0 | 0 | 0 | 0      | 0  | 0 | 0 | 0                                     |       | 0     |

|       |                                                                                                      |    |       |     |    |   |   |   |   |        |    |   |   | W reset<br>W reset<br><u>us reset</u> | : H'C | >0000 |

| b     |                                                                                                      |    | Bit n | ame |    |   |   |   |   | Functi | on |   |   |                                       | R     | W     |

| 15~7  | Reserved. Set it to "0".                                                                             |    |       |     |    |   |   |   |   |        |    |   |   |                                       | 0     | 0     |

| 6~0   | USB_Addr  Read                                                                                       |    |       |     |    |   |   |   |   |        |    |   |   | 0                                     | ×     |       |

|       | USB_Address USB address assigned by the host                                                         |    |       |     |    |   |   |   |   |        |    |   |   |                                       |       |       |

|       |                                                                                                      |    |       |     |    |   |   |   |   |        |    |   |   |                                       |       |       |

#### (1) USB\_Addr (USB\_Address) Bits (b6~b0)

These bits store the USB address assigned by the host.

On receiving SET\_ADDRESS request from the host at default state (DVSQ bits = "001"), the requested device address value is set to this register when the response is made through zero-length packet in status stage. The device address value is set to these bits at the time of zero-length packet transmit even if the ASAD bit is set to "0" (automatic response is invalid).

# 2.5 Isochronous Status Register

■ Isochronous Status Register (ISOCHRONOUS\_STATUS)

<Address : H'0A>

| b15   | 14                     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12         | 11   | 10 | 9 | 8      | 7         | 6         | 5        | 4     | 3 | 2 | 1 |        | b0     |

|-------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|----|---|--------|-----------|-----------|----------|-------|---|---|---|--------|--------|

|       |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | FMOD |    |   |        |           |           | FRNM     |       |   |   |   |        |        |

| 0     | 0                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0          | 0    | 0  | 0 | 0      | 0         | 0         | 0        | 0     | 0 | 0 | 0 |        | 0      |

| 0     | 0                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0          | 0    | 0  | 0 | 0      | 0         | 0         | 0        | 0     | 0 | 0 | 0 |        | 0      |

| b     |                        | -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     - <td>t : H'</td> <td>&lt;0000&gt;</td> |            |      |    |   |        |           |           |          |       |   |   |   | t : H' | <0000> |

| 15~12 | Reser                  | ved. Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | it to "0". |      |    |   |        |           |           |          |       |   |   |   | ?      | 0      |

| 11    | FMOD 0: At SOF receive |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |      |    |   |        |           |           |          |       |   |   | 0 | 0      |        |

|       | Frame                  | e Numbe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | r Mode     |      |    |   | 1: At  | Isochroi  | nous tran | sfer com | plete |   |   |   |        |        |

| 10~0  | FRNM                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |      |    |   | Stores | the frame | number    |          |       |   |   |   | 0      | ×      |

This register is valid only for isochronous transfer. In other words, the register is valid status for the endpoint that is set EPi\_TYP bits to "11".

#### (1) FMOD (Frame Number Mode) Bit (b11)

Frame Number

This bit sets the storage timing of the frame number to be stored to the FRNM bits.

When this bit is set to "0", when the SOF packet is properly received, the frame number of the received SOF packet gets stored.

When this bit is set to "1", when the isochronous packet transfer completes, the frame number of the properly received SOF packet gets stored.

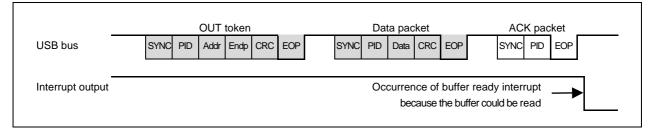

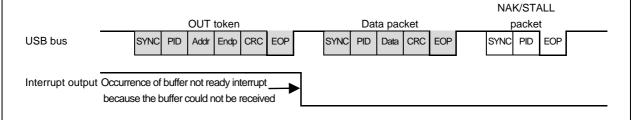

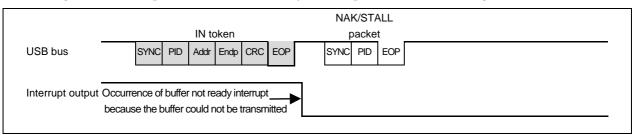

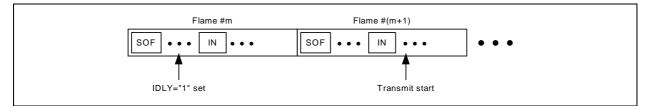

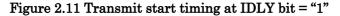

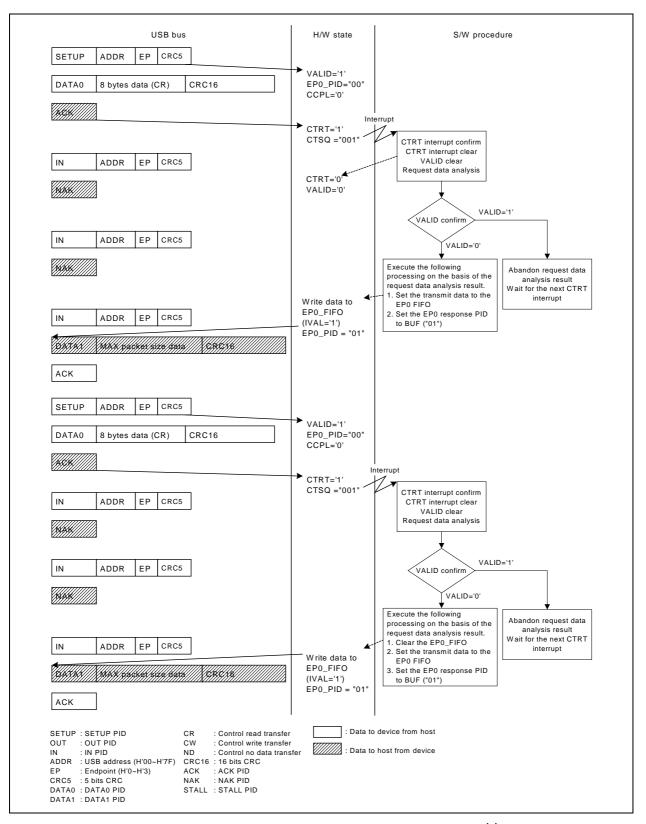

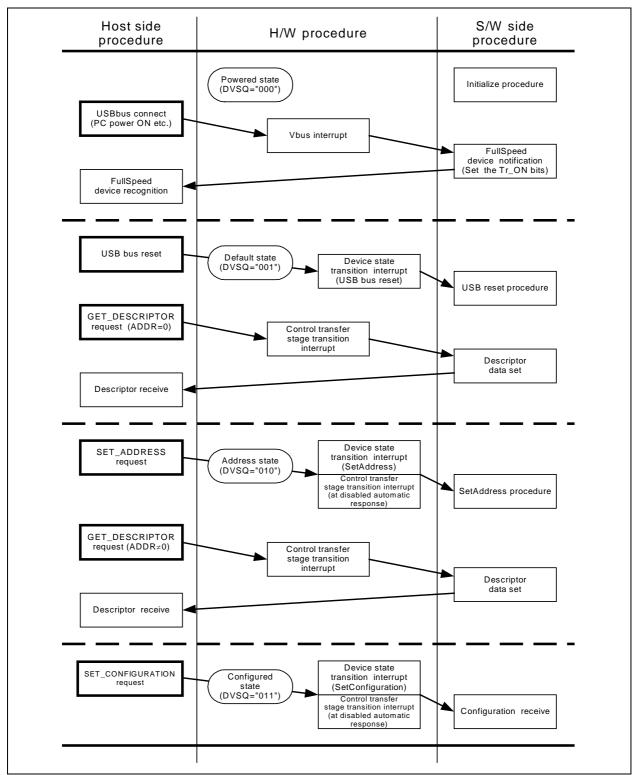

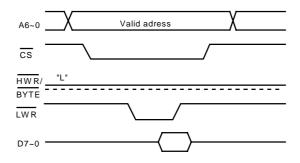

#### (2) FRNM (Frame Number) Bits (b10~b0)