# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

EOL annous

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **MITSUBISHI MICROCOMPUTERS**

Notice: This is not a final specification chan

M37906M4C-XXXFP, M37906M4C-XXXSP, M37906M4H-XXXFP M37906M4H-XXXSP, M37906M6C-XXXFP, M37906M6C-XXXSP M37906M8C-XXXFP, M37906M8C-XXXSP

16-BIT CMOS MICROCOMPUTER

#### **DESCRIPTION**

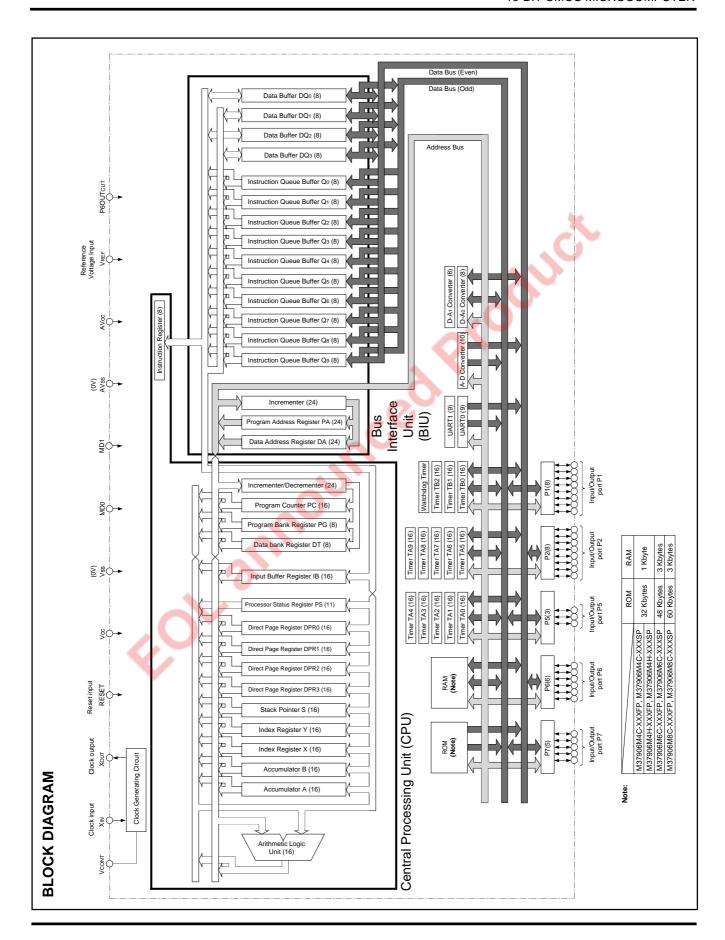

These are single-chip 16-bit microcomputers designed with high-performance CMOS silicon gate technology, being packaged in 42-pin plastic molded SSOP or shrink plastic molded DIP. These microcomputers support the 7900 Series instruction set, which are enhanced and expanded instruction set and are upper-compatible with the 7700/7751 Series instruction set.

The CPU of these microcomputers is a 16-bit parallel processor that can also be switched to perform 8-bit parallel processing. Also, the bus interface unit of these microcomputers enhances the memory access efficiency to execute instructions fast. Therefore, these microcomputers are suitable for office, business, and industrial equipment controller that require high-speed processing of large data. Also, they are suitable for motor-control equipment since each of

#### **DISTINCTIVE FEATURES**

them includes the motor control circuit.

| Number of basic machine instructions      | 203       |

|-------------------------------------------|-----------|

| ● Memory                                  |           |

| [M37906M4C-XXXFP, M37906M4C-XXXSP]        |           |

| [M37906M4H-XXXFP, M37906M4H-XXXSP] (Note) |           |

| ROM                                       | 32 Kbytes |

| RAM                                       | 1 Kbyte   |

| [M37906M6C-XXXFP, M37906M6C-XXXSP]        |           |

| ROM                                       | 48 Kbytes |

| RAM                                       | 3 Kbytes  |

**Note:** The M37906M4C-XXXFP/SP and the M37906M4H-XXXFP/SP have the same functions, distinctive features, and electrical characteristics.

#### **APPLICATION**

- Control devices for office equipment such as copiers and facsimiles

- Control devices for industrial equipment such as communication and measuring instruments

- Control devices for equipment, requiring motor control, such as inverter air conditioners and general-purpose inverters

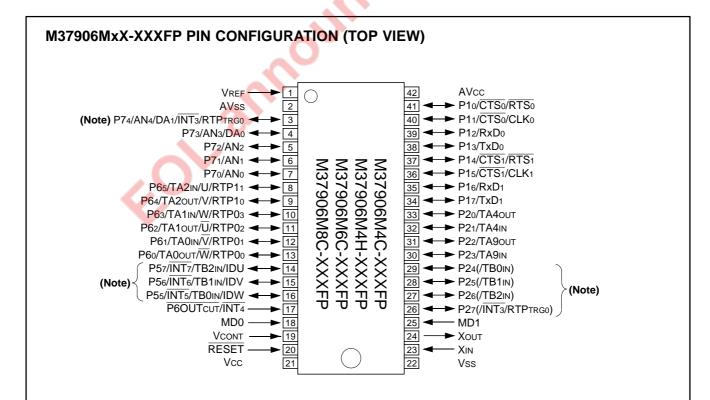

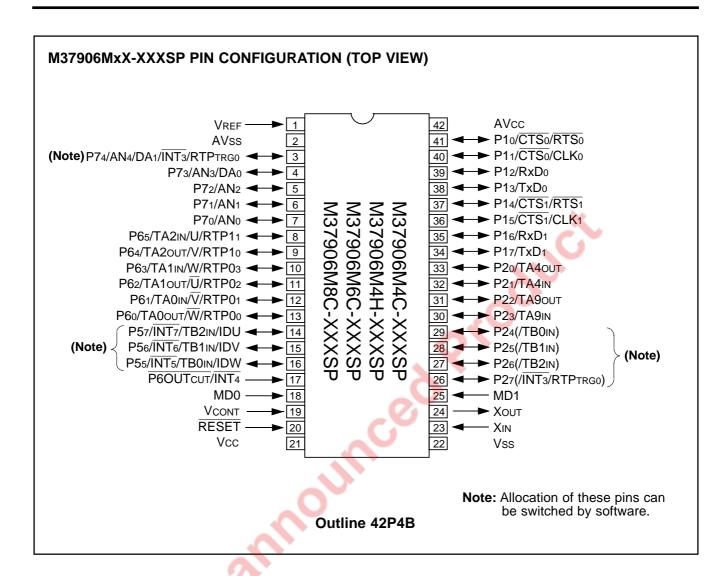

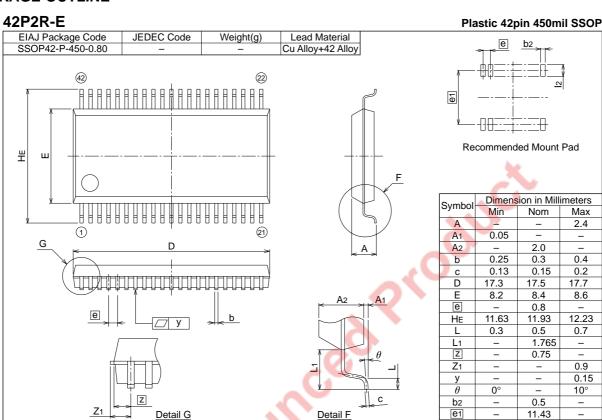

Outline 42P2R-E

**Note:** Allocation of these pins can be switched by software.

MITSUBISHI MICROCOMPUTERS

M37906M4C-XXXFP, M37906M4C-XXXSP, M37906M4H-XXXFP

M37906M4H-XXXXFP, M37906M6C-XXXFP, M37906M6C-XX

16-BIT CMOS MICROCOMPUTER

#### **FUNCTIONS**

| Parameter                            |                                | Functions                                                                                                                   |  |

|--------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Number of basic machine instructions |                                | 203                                                                                                                         |  |

| Instruction execution time           |                                | 50 ns (the fastest instruction at f(fsys) = 20 MHz)                                                                         |  |

| External clock input frequency       | f(XIN)                         | 20 MHz (Max.)                                                                                                               |  |

| System clock input frequency f       | (fsys)                         | 20 MHz (Max.)                                                                                                               |  |

| Memory size                          | ROM                            | (Note 1)                                                                                                                    |  |

|                                      | RAM                            | (Note 1)                                                                                                                    |  |

| Programmable input/output            | P1, P2                         | 8-bit X 2                                                                                                                   |  |

| ports                                | P5                             | 3-bit X 1                                                                                                                   |  |

|                                      | P6                             | 6-bit × 1                                                                                                                   |  |

|                                      | P7                             | 5-bit X 1                                                                                                                   |  |

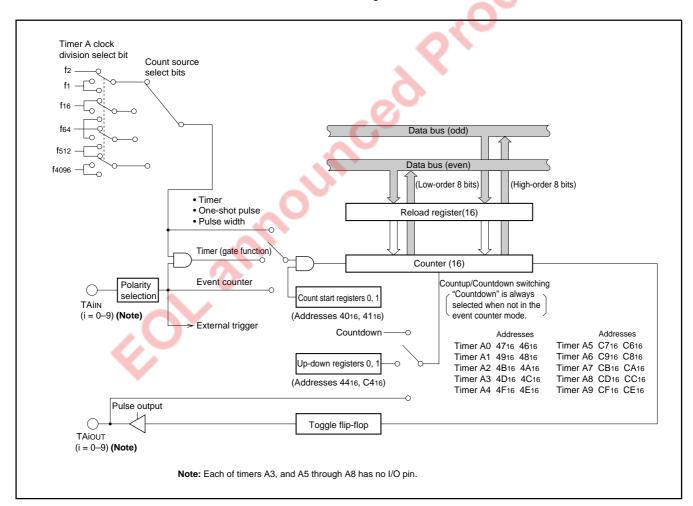

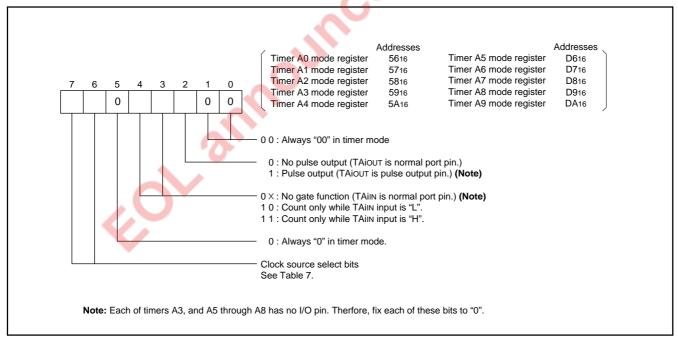

| Multi-functional timers              | ТАО-ТА9                        | 16-bit X 10                                                                                                                 |  |

|                                      | TB0-TB2                        | 16-bit X 3                                                                                                                  |  |

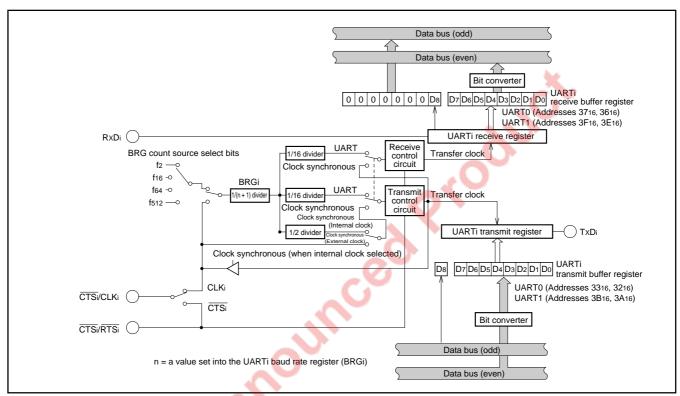

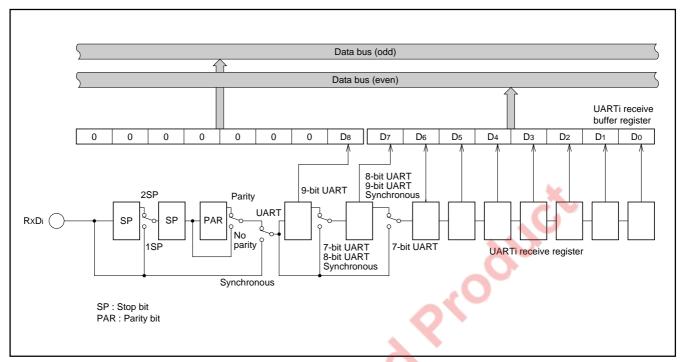

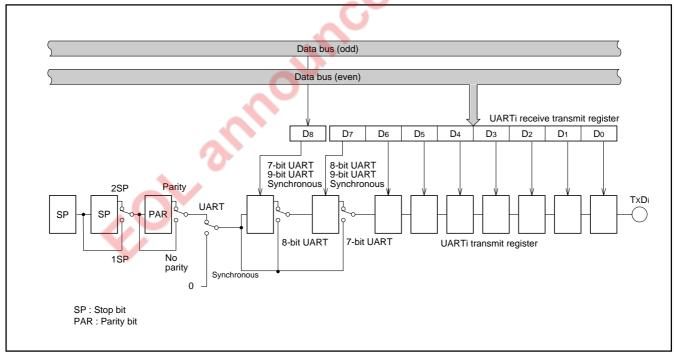

| Serial I/O                           | UART0 and UART1                | (UART or Clock synchronous serial I/O) X 2                                                                                  |  |

| A-D converter                        |                                | 10-bit successive approximation method X 1 (5 channels)                                                                     |  |

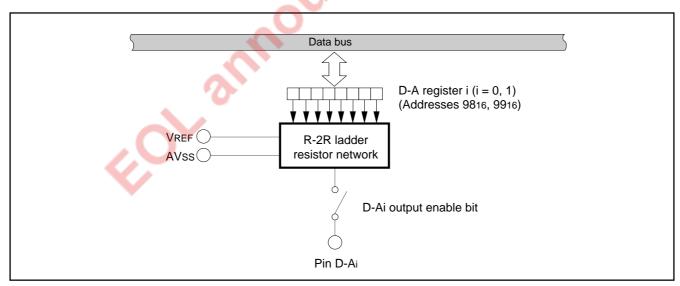

| D-A converter                        |                                | 8-bit × 2                                                                                                                   |  |

| Dead-time timer                      |                                | 8-bit <b>X</b> 3                                                                                                            |  |

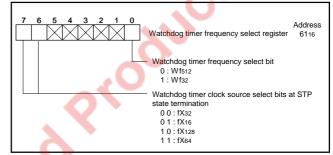

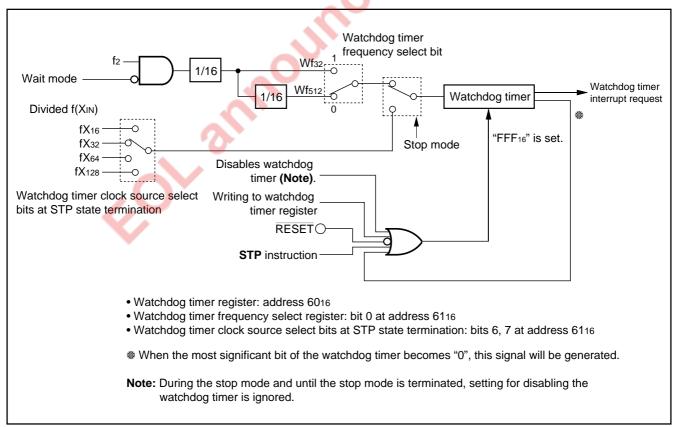

| Watchdog timer                       |                                | 12-bit X 1                                                                                                                  |  |

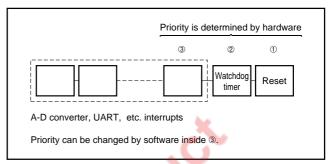

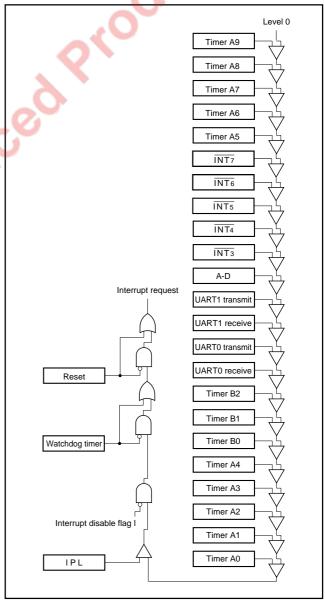

| Interrupts                           | Maskable interrups             | 5 external sources, 18 internal sources. Each interrupt can be set to a priority level within the range of 0–7 by software. |  |

|                                      | Non-maskable interrups         | 3 internal sources                                                                                                          |  |

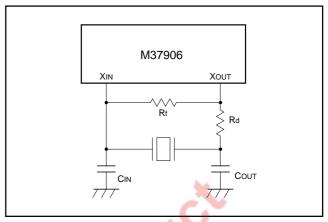

| Clock generating circuit             |                                | Built-in (externally connected to a ceramic resonator or quartz-crystal oscillator).                                        |  |

| PLL frequency multiplier             | _0                             | The following multiplication ratios are available: X 2, X 3, X 4                                                            |  |

| Power supply voltage                 |                                | 5 V±0.5 V                                                                                                                   |  |

| Power dissipation                    |                                | 125 mW (at f(fsys) = 20 MHz, Typ., the PLL frequency multiplier is inactive)                                                |  |

| Ports' input/output                  | Input/Output withstand voltage | 5 V                                                                                                                         |  |

| characteristics Output current       |                                | 5 mA                                                                                                                        |  |

| Memory expansion                     |                                | Not available (single-chip mode only).                                                                                      |  |

| Operating ambient temperature        | e range                        | −20 to 85 °C                                                                                                                |  |

| Device structure                     |                                | CMOS high-performance silicon gate process                                                                                  |  |

| Package                              |                                | (Note 2)                                                                                                                    |  |

#### Notes 1:

| ROM | M37906M4C-XXXFP, M37906M4C-XXXSP | 32 Kbytes |  |

|-----|----------------------------------|-----------|--|

|     | M37906M4H-XXXFP, M37906M4H-XXXSP | 32 Naytes |  |

|     | M37906M6C-XXXFP, M37906M6C-XXXSP | 48 Kbytes |  |

|     | M37906M8C-XXXFP, M37906M8C-XXXSP | 60 Kbytes |  |

| RAM | M37906M4C-XXXFP, M37906M4C-XXXSP | 4 171     |  |

|     | M37906M4H-XXXFP, M37906M4H-XXXSP | 1 Kbyte   |  |

|     | M37906M6C-XXXFP, M37906M6C-XXXSP | 3 Kbytes  |  |

|     | M37906M8C-XXXFP, M37906M8C-XXXSP | 3 Kbytes  |  |

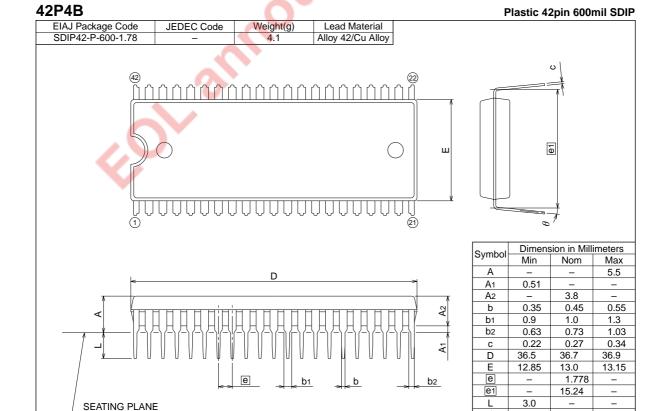

| 2: | Packages | M37906M4C-XXXFP, M37906M4H-XXXFP, M37906M6C-XXXFP, M37906M8C-XXXFP | 42-pin plastic molded SSOP (42P2R-E)     |  |

|----|----------|--------------------------------------------------------------------|------------------------------------------|--|

|    |          | M37906M4C-XXXSP, M37906M4H-XXXSP,                                  | 42-pin shrink plastic molded DIP (42P4B) |  |

|    |          | M37906M6C-XXXSP, M37906M8C-XXXSP                                   | 12 pm o praosio morada 211 (121 12)      |  |

MITSUBISHI MICROCOMPUTERS

M37906M4C-XXXFP, M37906M4C-XXXSP, M37906M4H-XXXFP

M37906M4H-XXXFP, M37906M6C-XXXFP, M37906M6C-XXX

16-BIT CMOS MICROCOMPUTER

#### **PIN DESCRIPTION**

| Pin           | Name                      | Input/<br>Output | Functions                                                                                                                                                                                                                                                                                              |

|---------------|---------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc, Vss      | Power supply input        | _                | Apply 5 V±0.5 V to Vcc, and 0 V to Vss.                                                                                                                                                                                                                                                                |

| MD0           | MD0                       | Input            | Connect this pin to Vss.                                                                                                                                                                                                                                                                               |

| MD1           | MD1                       | Input            | Connect this pin to Vss.                                                                                                                                                                                                                                                                               |

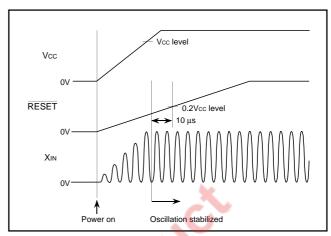

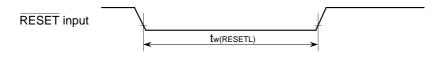

| RESET         | Reset input               | Input            | The microcomputer is reset when "L" level is applies to this pin.                                                                                                                                                                                                                                      |

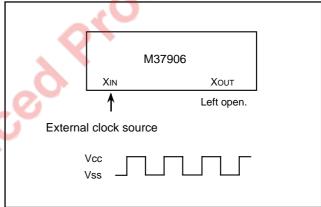

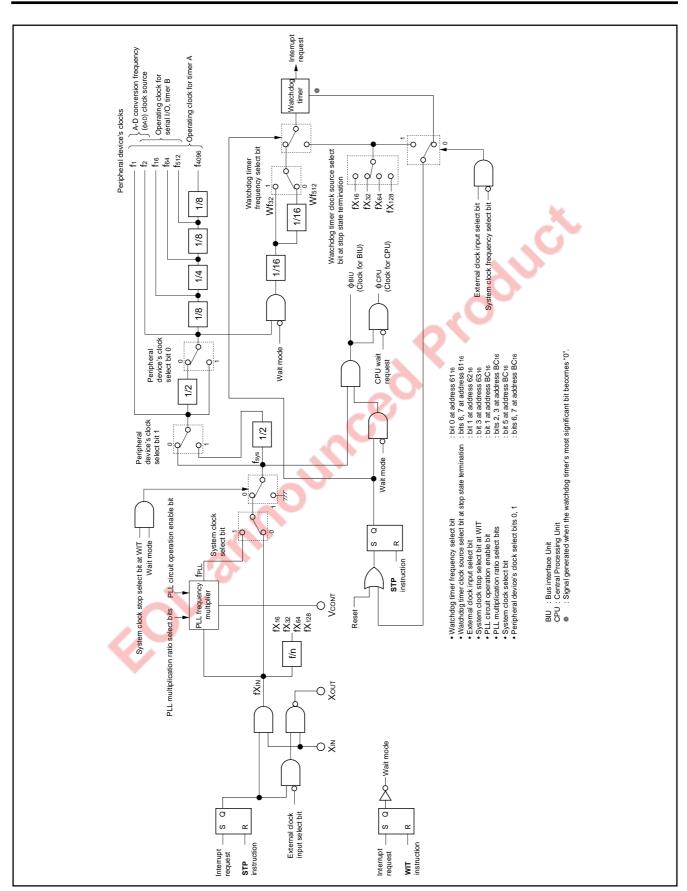

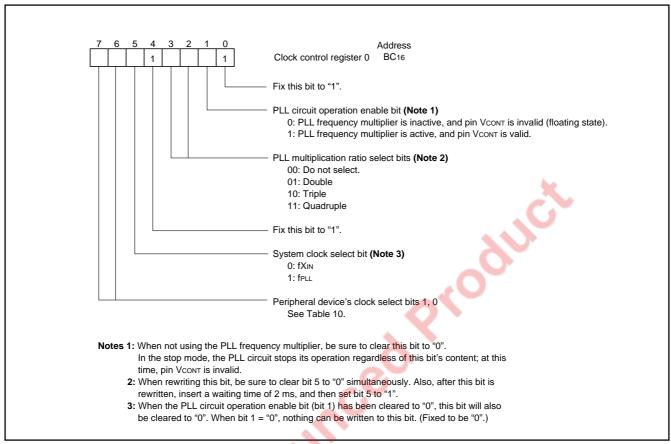

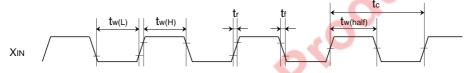

| XIN           | Clock input               | Input            | These are input and output pins of the internal clock generating circuit. Connect a                                                                                                                                                                                                                    |

| Хоит          | Clock output              | Output           | ceramic resonator or quartz-crystal oscillator between pins XIN and XOUT. When an external clock is used, the clock source should be connected to pin XIN, and pin XOUT should be left open.                                                                                                           |

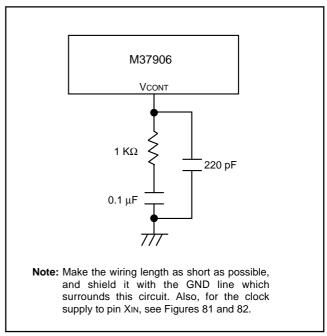

| VCONT         | Filter circuit connection | _                | When using the PLL frequency multiplier, connect this pin to the filter circuit. When not using, this pin should be left open.                                                                                                                                                                         |

| AVcc,<br>AVss | Analog power supply input | _                | Power supply input pins for the A-D and D-A converters. Connect AVcc to Vcc, and AVss to Vss externally.                                                                                                                                                                                               |

| VREF          | Reference voltage input   | Input            | This is the reference voltage input pin for the A-D and D-A converters.                                                                                                                                                                                                                                |

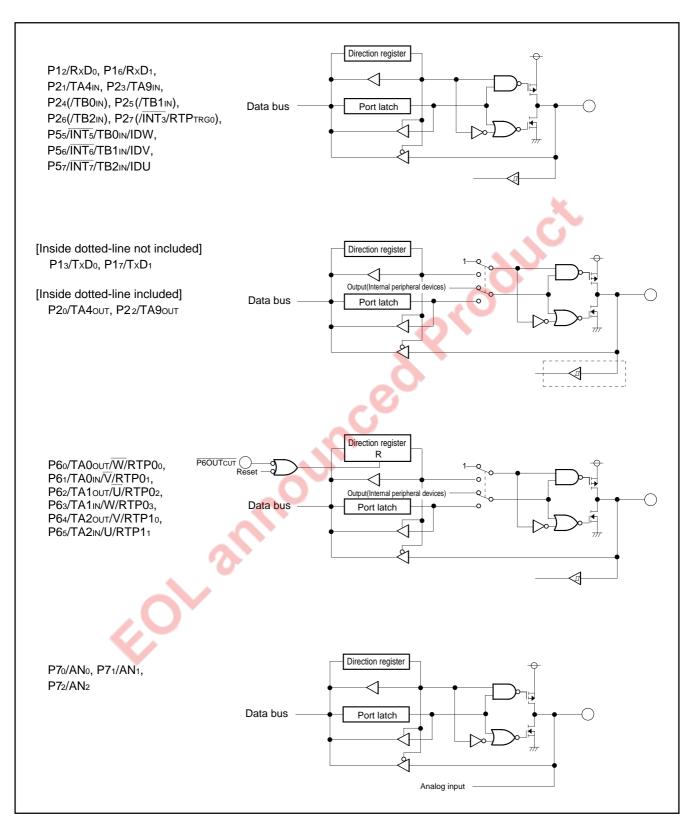

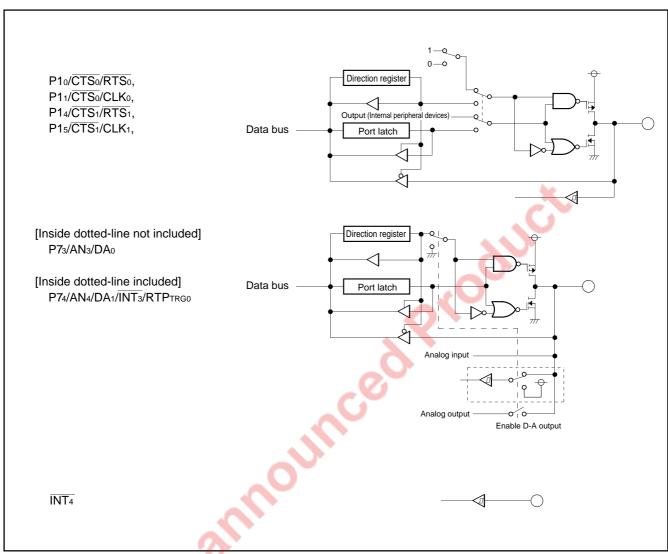

| P10-P17       | I/O port P1               | I/O              | Port P1 is an 8-bit I/O port. This port has an I/O direction register, and each pin can be programmed for input or output. These pins enter the input mode ar reset. These pins also function as I/O pins of UARTO, 1.                                                                                 |

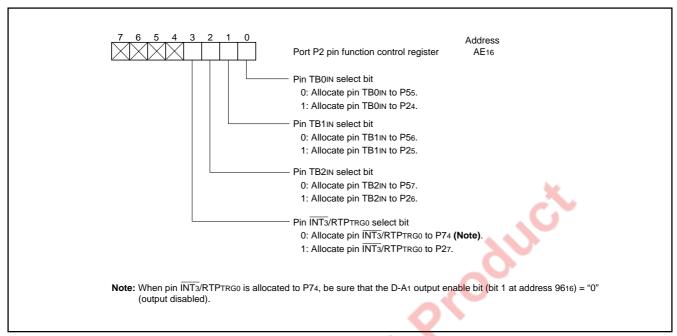

| P20-P27       | I/O port P2               | I/O              | In addition to having the same functions as port P1, these pins function as I/O pins for timers A4 and A9. Also, they can be programmed to function as input pins for timers B0 to B2 and $\overline{\text{INT3}}$ , or as trigger input pins in the pulse output port mode.                           |

| P55-P57       | I/O port P5               | I/O              | In addition to having the same functions as port P1, these pins function as input pins for INT5 to INT7. Also, they function as input pins for timers B0 to B2 and position data input pins in the three-phase waveform mode.                                                                          |

| P60-P65       | I/O port P6               | I/O              | In addition to having the same functions as port P1, these pins function as I/O pins for timers A0 to A2. Also, they function as motor drive waveform output pins.                                                                                                                                     |

| P70–P74       | I/O port P7               | I/O              | In addition to having the same functions as port P1, these pins function as input pins for the A-D converter. Also, P73 functions as an output pin for the D-A converter, P74 as an output pin for the D-A converter and an input pin for INT3, and a trigger input pin in the pulse output port mode. |

| P6OUTcut      | P6OUTcuT input            | Input            | This pin has the function to forcibly place port P6 pins in the input mode (port-out-put-cutoff function). Also, this pin functions as an input pin for $\overline{\text{INT4}}$ , and as an input pin for the port-output-cutoff function in the motor drive waveform output mode.                    |

16-BIT CMOS MICROCOMPUTER

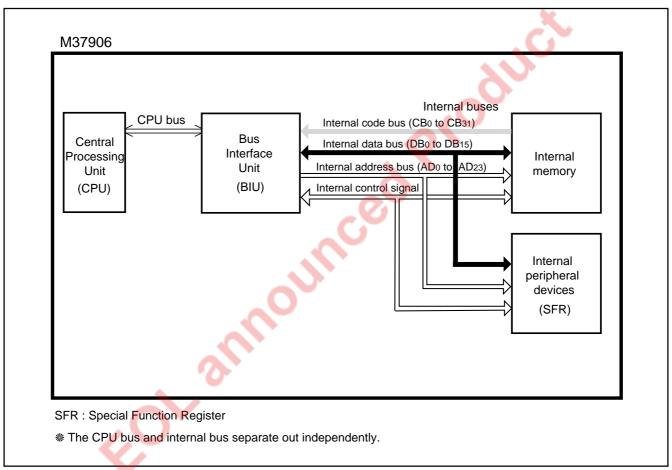

#### **BASIC FUNCTION BLOCKS**

These microcomputers contain the following devices in the single chip: ROM, RAM, CPU, bus interface unit, and peripheral devices such as the interrupt control circuit, timers, serial I/O, A-D converter, D-A converter, I/O ports, clock generating circuit, etc.

#### **MEMORY**

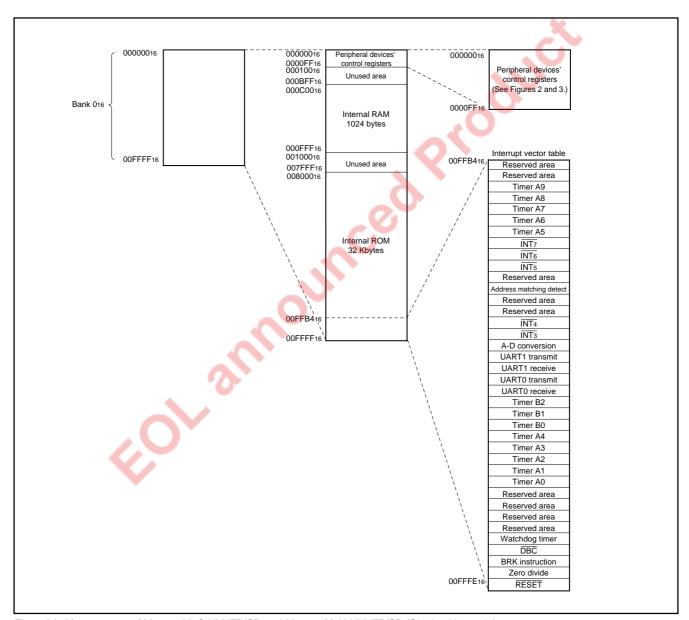

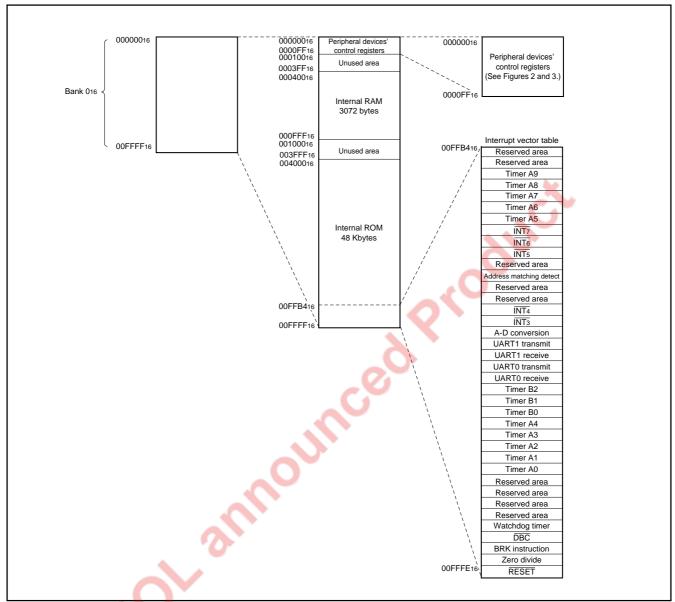

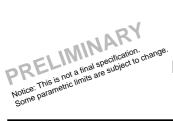

Figures 1 (1) through (3) show the memory maps. The address space is 64 Kbytes from addresses 016 through FFFF16. This ad-

dress space is called "bank 016".

The internal ROM and RAM are allocated as shown in Figures 1 (1) through (3).

Addresses FFB416 through FFFF16 contain the RESET and the interrupt vector addresses, and the interrupt vectors are stored there. For details, refer to the section on interrupts.

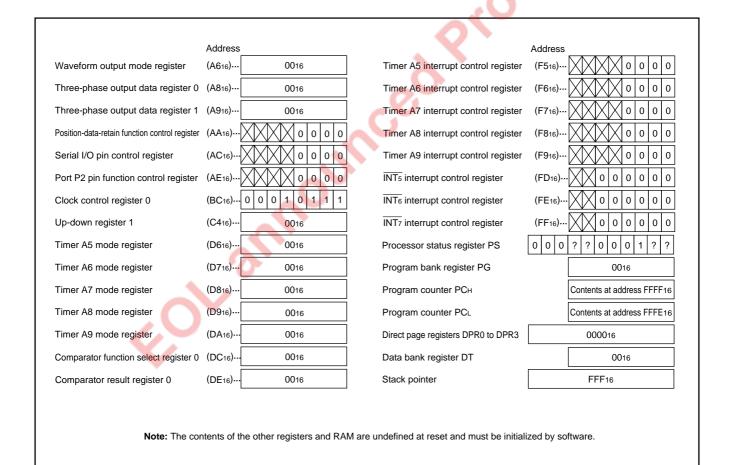

Allocated to addresses 016 through FF16 are peripheral devices such as I/O ports, A-D converter, D-A converter, serial I/O, timers, interrupt control registers, etc. Figures 2 and 3 show the location of SFRs.

Fig. 1 (1) Memory map of M37906M4C-XXXFP/SP and M37906M4H-XXXFP/SP (Single-chip mode)

Fig. 1 (2) Memory map of M37906M6C-XXXFP/SP (Single-chip mode)

Fig. 1 (3) Memory map of M37906M8C-XXXFP/SP (Single-chip mode)

# MITSUBISHI MICROCOMPUTERS M37906M4C-XXXFP, M37906M4C-XXXSP, M37906M4H-XXXFP M37906M4H-XXXFP, M37906M6C-XXXFP, M37906M6C-XXX

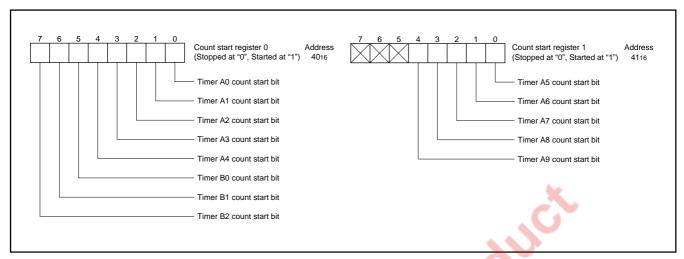

| 00000016             | Reserved area (Note)                      | 00004016             | Count start register 0                    |

|----------------------|-------------------------------------------|----------------------|-------------------------------------------|

| 00000116             | Reserved area (Note)                      | 00004116             |                                           |

| 00000216             | Reserved area (Note)                      | 00004216             |                                           |

| 00000316             |                                           | 00004316             |                                           |

| 00000416             | Reserved area (Note)                      | 00004416             | Up-down register 0                        |

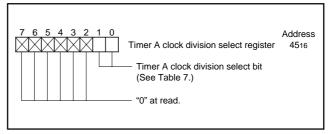

| 00000516             | Port P1 direction register                | 00004516             | Timer A clock division select register    |

| 00000616             | Port P2 register                          | 00004616             | Time and AO and mintage                   |

| 00000716             | Reserved area (Note)                      | 00004716             | Timer A0 register                         |

| 00000816             | Port P2 direction register                | 00004816             | Times A4 segister                         |

| 00000916             | Reserved area (Note)                      | 00004916             | Timer A1 register                         |

| 00000A16             | Reserved area (Note)                      | 00004A16             | Timer A2 register                         |

| 00000B16             | Port P5 register                          | 00004B16             | Timer Az register                         |

|                      | Reserved area (Note)                      | 00004C16             | Timer A3 register                         |

| 00000D16             |                                           | 00004D16             | Tillel A3 register                        |

| 00000E16             |                                           | 00004E16             | Timer A4 register                         |

| 00000F16             | Port P7 register                          | 00004F16             | Timer 74 register                         |

|                      | Port P6 direction register                | 00005016             | Timer B0 register                         |

| 00001116             | Port P7 direction register                | 00005116             |                                           |

| 00001216             | Reserved area (Note)                      | 00005216             | Timer B1 register                         |

| 00001316             |                                           | 00005316             |                                           |

| 00001416             | Reserved area (Note)                      | 00005416             | Timer B2 register                         |

| 00001516             | D                                         | 00005516             |                                           |

| 00001616             | Reserved area (Note)                      | 00005616             | Timer A0 mode register                    |

|                      | Reserved area (Note)                      | 00005716             | Ü                                         |

| 00001816             | Reserved area (Note)                      | 00005816             | - C                                       |

| 00001916             | Reserved area (Note)                      | 00005916             | - C                                       |

| 00001A16             |                                           | 00005A16             | Ü                                         |

| 00001B16             |                                           | 00005B16             | •                                         |

| 00001C16             |                                           | 00005C16             |                                           |

| 00001D16             | A D control register 0                    | 00005D16             |                                           |

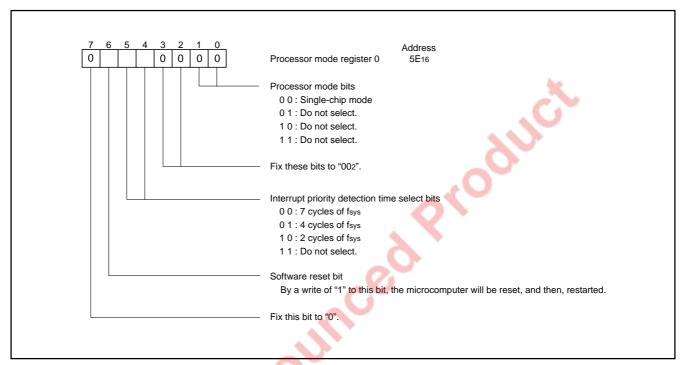

| 00001E16             | A-D control register 0                    | 00005E16             |                                           |

| 00001F16<br>00002016 | A-D control register 1                    | 00005F16<br>00006016 |                                           |

| 00002016             | A-D register 0                            | 00006016             | 0 0                                       |

| 00002116             |                                           | 00006116             |                                           |

| 00002216             | A-D register 1                            | 00006316             |                                           |

| 00002316             |                                           | 00006416             | Ü                                         |

| 00002116             | A-D register 2                            | 00006516             | 8                                         |

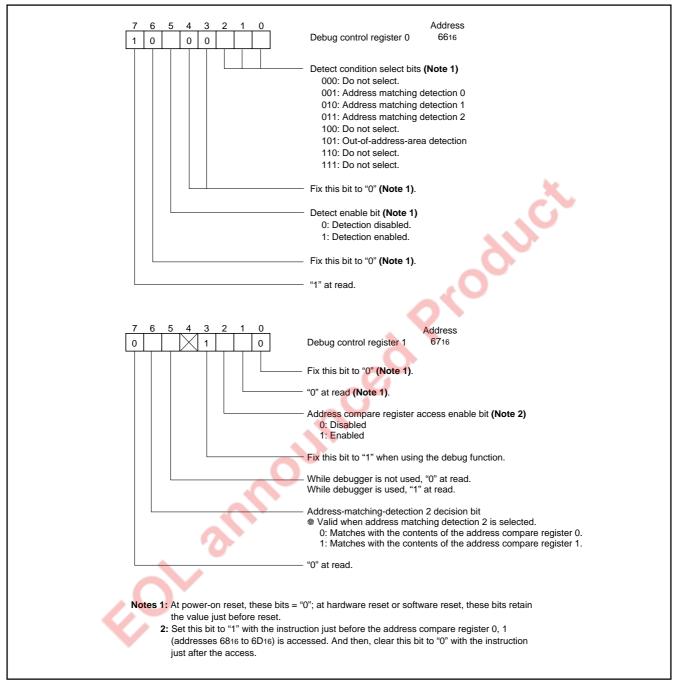

| 00002616             |                                           | 00006616             | Debug control register 0                  |

| 00002716             | A-D register 3                            | 00006716             | Debug control register 1                  |

| 00002816             |                                           | 00006816             |                                           |

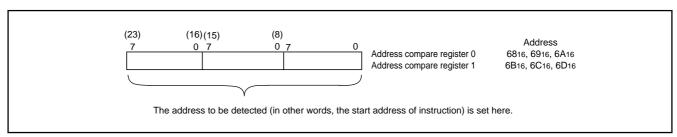

| 00002916             | A-D register 4                            | 00006916             | Address comparison register 0             |

| 00002A16             | Reserved area (Note)                      | 00006A16             |                                           |

|                      | Reserved area (Note)                      | 00006B16             |                                           |

| 00002C16             | Reserved area (Note)                      | 00006C16             | Address comparison register 1             |

| 00002D16             |                                           | 00006D16             |                                           |

| 00002E16             | Reserved area (Note)                      | 00006E16             | INT3 interrupt control register           |

| 00002F16             | Reserved area (Note)                      | 00006F16             |                                           |

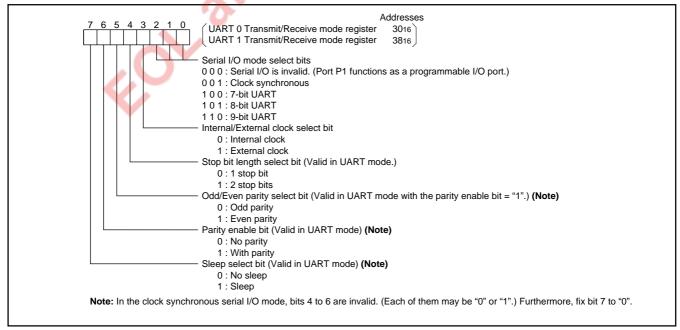

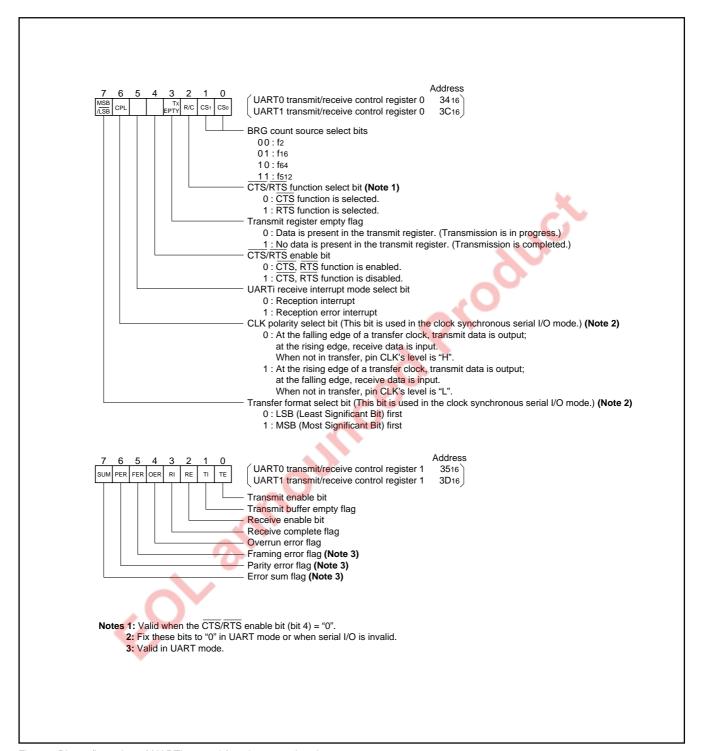

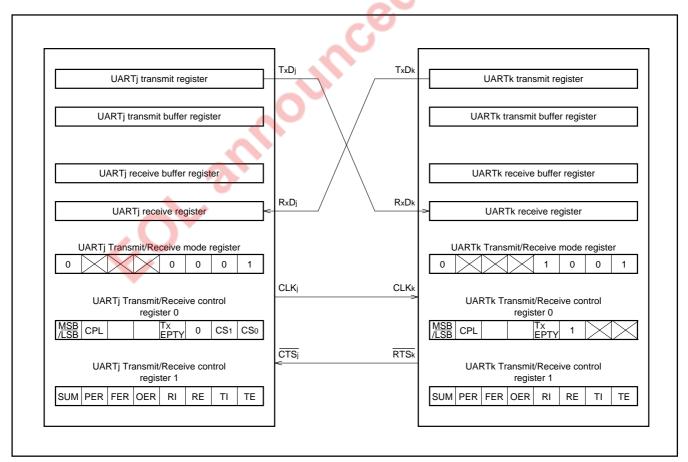

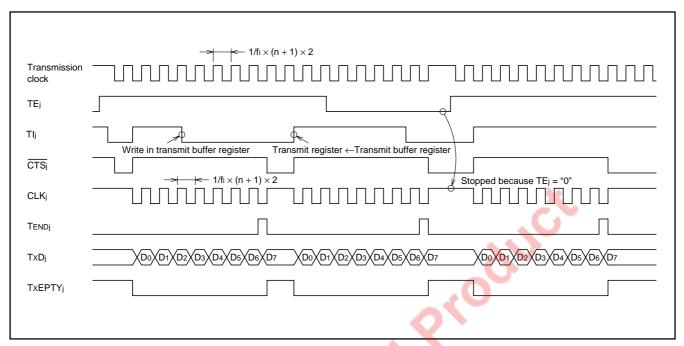

| 00003016             | UART0 transmit/receive mode register      | 00007016             |                                           |

| 00003116             | UART0 baud rate register (BRG0)           | 00007116             |                                           |

| 00003216             | UART0 transmit buffer register            | 00007216             |                                           |

| 00003316             | Unit i di di di di legister               | 00007316             | UART1 transmit interrupt control register |

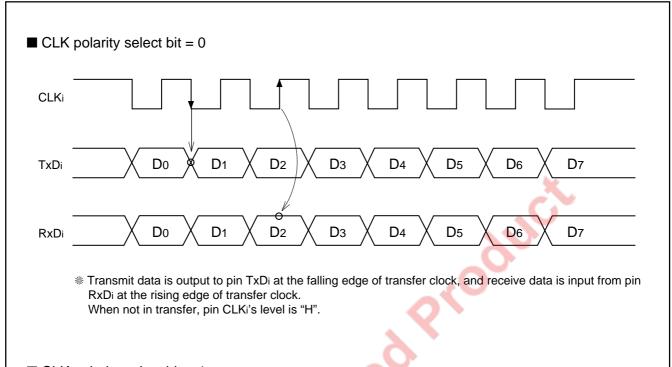

| 00003416             | UART0 transmit/receive control register 0 | 00007416             | UART1 receive interrupt control register  |

| 00003516             | UART0 transmit/receive control register 1 | 00007516             | Timer A0 interrupt control register       |

| 00003616             | UART0 receive buffer register             | 00007616             | ·                                         |

| 00003716             |                                           | 00007716             | , ,                                       |

| 00003816             | UART1 transmit/receive mode register      | 00007816             |                                           |

| 00003916             | UART1 baud rate register (BRG1)           | 00007916             |                                           |

| 00003A16             | UART1 transmit buffer register            | 00007A16             |                                           |

| 00003B16             |                                           | 00007B16             | i ü                                       |

| 00003C16             | UART1 transmit/receive control register 0 | 00007C16             | ·                                         |

| 00003D16             | UART1 transmit/receive control register 1 | 00007D16             |                                           |

| 00003E16             | UART1 receive buffer register             | 00007E16             |                                           |

| 00003F16             | C 1 1000170 Danot Togistor                | 00007F16             | Reserved area (Note)                      |

|                      |                                           |                      |                                           |

Fig. 2 Location of SFRs (1)

# MITSUBISHI MICROCOMPUTERS M37906M4C-XXXFP, M37906M4C-XXXSP, M37906M4H-XXXFP M37906M4H-XXXXFP, M37906M6C-XXXFP, M37906M6C-XX

| `,                   | Hexadecimal notation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0000C016             | exadecimal notation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00008016<br>00008116 | Reserved area (Note) Reserved area (Note)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000C016<br>0000C116 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 00008116             | Reserved area (Note)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000C116             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 00008316             | Reserved area (Note)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000C316             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 00008416             | Reserved area (Note)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000C416             | Up-down register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 00008516             | Reserved area (Note)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000C516             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 00008616             | Reserved area (Note)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000C616             | T: A5 : .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 00008716             | Reserved area (Note)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000C716             | Timer A5 register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

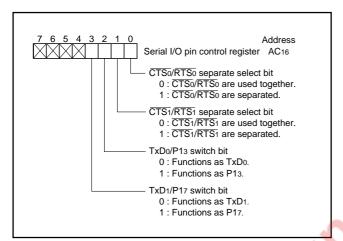

| 00008816             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0000C816             | Timer A6 register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |