## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### MITSUBISHI MICROCOMPUTERS

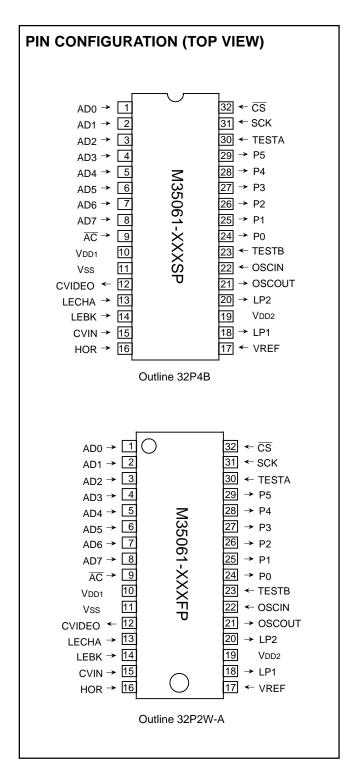

## M35061-XXXSP/FP

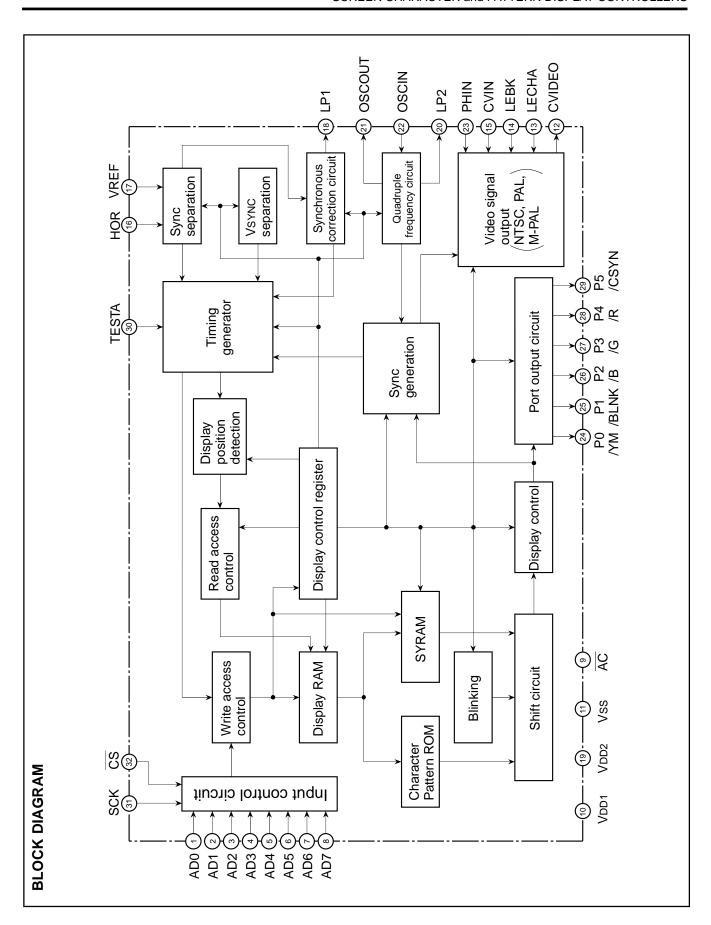

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

#### **DESCRIPTION**

M35061-XXXSP/FP is CATV screen display control IC which can display 40 (horizontal) X 17 (vertical). It has built-in SYRAM which can be used with character ROM.

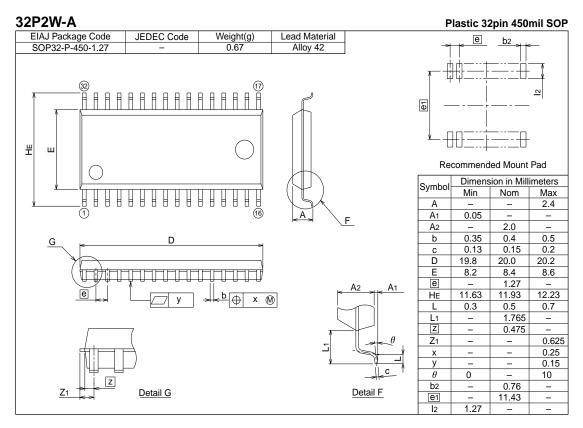

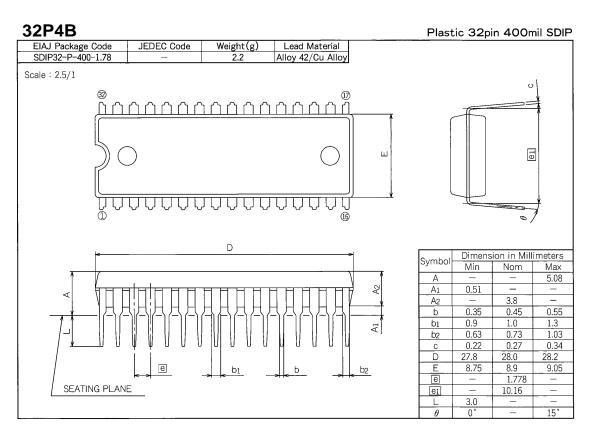

It uses a silicon gate CMOS process and M35061-XXXSP housed in a small 32-pin shrink DIP package, and M35061-XXXFP housed in a small 32-pin shrink SOP package. For M35061-002SP/FP that is a standard ROM version of M35061-XXXSP/FP, the character pattern is also mentioned.

## **FEATURES**

| Consequence WAZ lines                                        |

|--------------------------------------------------------------|

| • Screen composition                                         |

| (at scrolling 40 characters X 16 lines)                      |

| • Number of characters displayed 680 (Max.)                  |

| • Character composition 12 X 13 dot matrix                   |

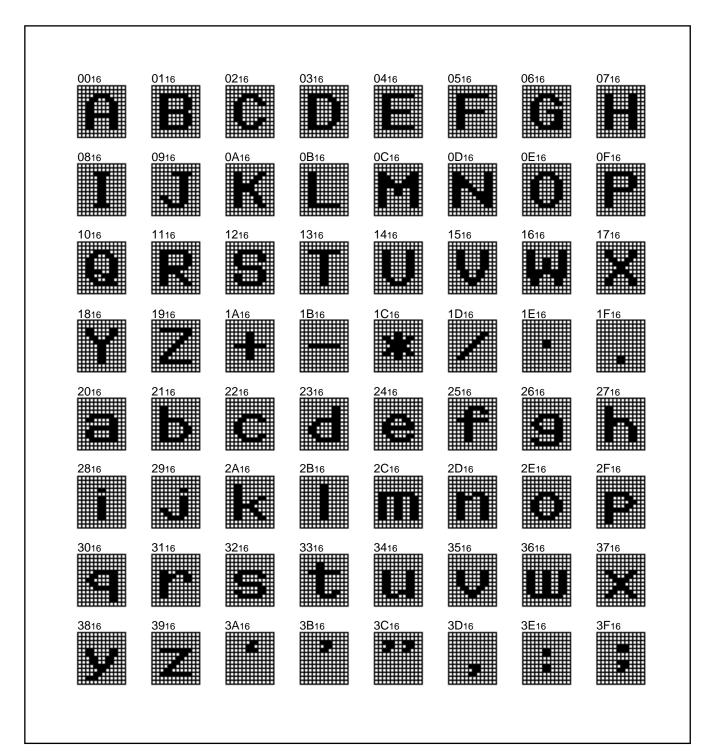

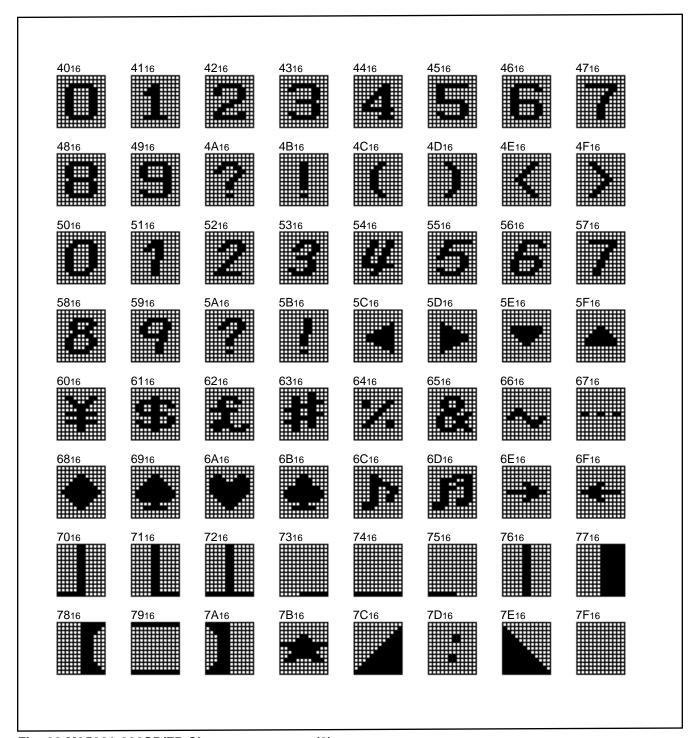

| Characters available character ROM 128 characters            |

| SYRAM7 characters                                            |

| Character sizes available horizontal 2 (once, twice)         |

| vertical 2 (once, twice)                                     |

| setting by every line                                        |

| Display locations available                                  |

| Horizontal direction                                         |

| Vertical direction                                           |

| Blinking character units                                     |

| Cycle approximately 1 second, or approximately 0.5 seconds   |

| (per screen)                                                 |

| Duty25%, 50% or 75%                                          |

| (per screen)                                                 |

| • Data input                                                 |

| • Coloring Character coloring 8 colors choices per character |

| (Note)                                                       |

| Background coloring 8 colors choices per character           |

| (Note)                                                       |

| Raster coloring8 colors choices per screen                   |

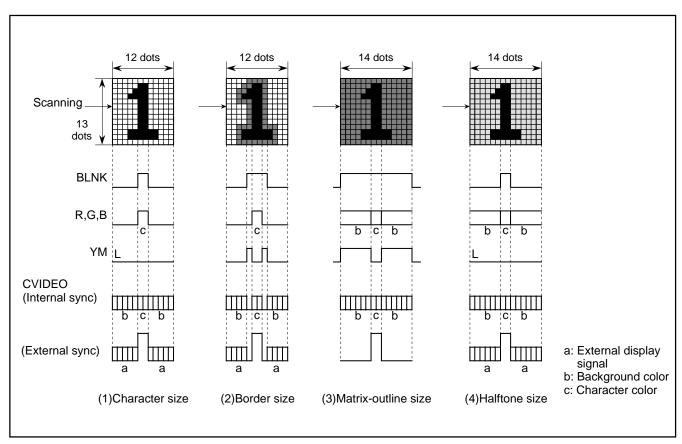

| Blanking     Character size blanking                         |

| Border size blanking                                         |

| Matrix-outline                                               |

| Halftone blanking                                            |

| Can be set by every line                                     |

| •                                                            |

| General-purpose output ports     Combined port output        |

| (switching to RGB output)                                    |

| RAM erase Display RAM erasing by every line                  |

| SYRAM erasing separately                                     |

| Scrolling Bit by bit smooth scroll implemented by software   |

Note: Superimpose coloring is available. (NTSC, PAL, M-PAL)

• Composite synchronizating signal generation ...... Built-in

(PAL, NTSC, M-PAL)

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

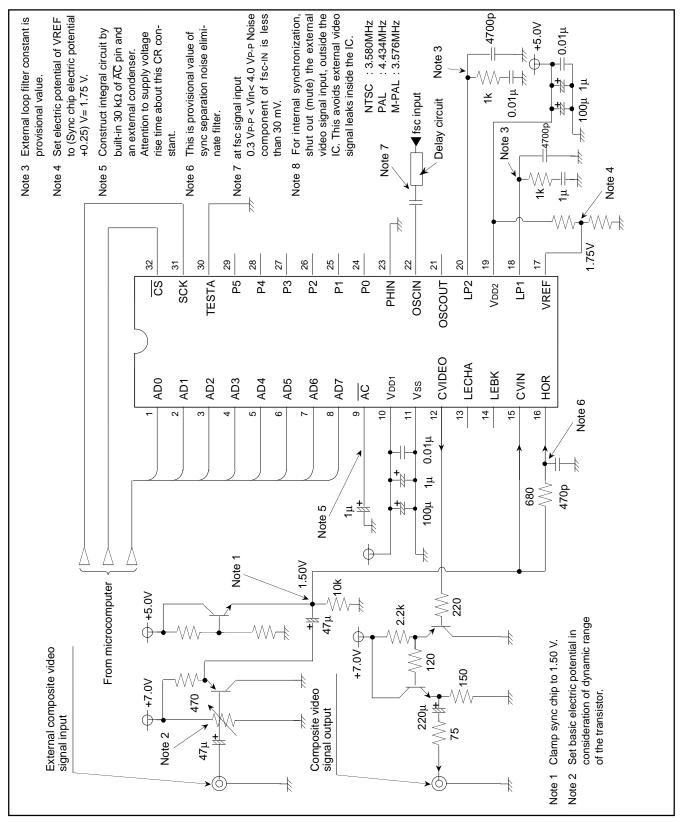

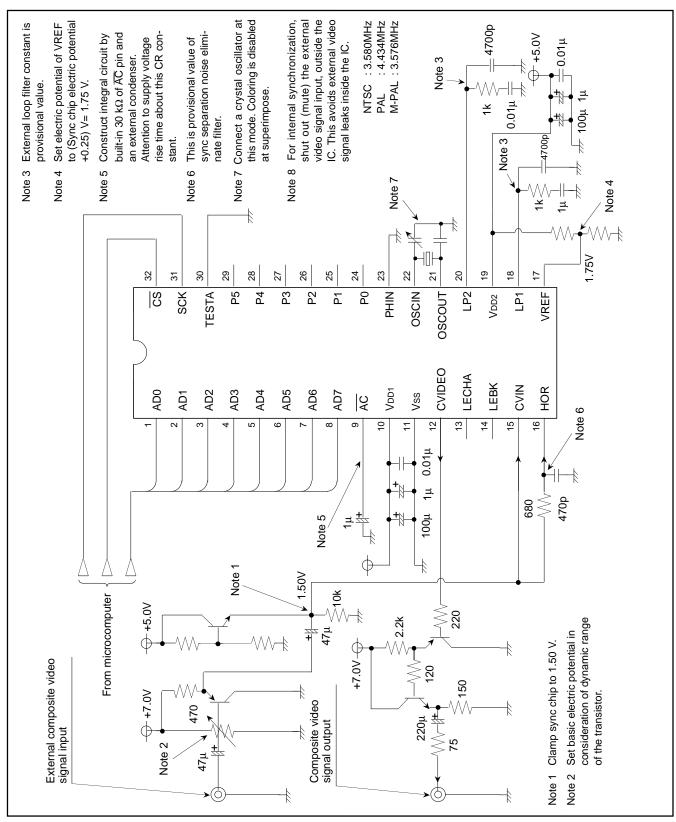

## **PIN DESCRIPTION**

| Symbol  | Pin name                      | Input/Output | Function                                                                                                                                                                                   |

|---------|-------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD0~AD7 | Parallel data input           | Input        | These input pins determine address and data of display control register and display data memory by 8-bit parallel. Hysteresis input is required.                                           |

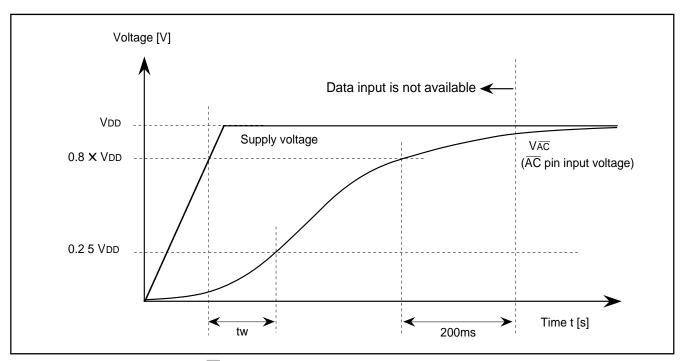

| AC      | Auto-clear input              | Input        | When this input pin transitions from "H" to "L", the device is reset. Built-in a pull-up resistor. Hysteresis input is required.                                                           |

| VDD1    | Power pin                     | _            | Digital power supply pin. This pin must be connected to +5 V.                                                                                                                              |

| Vss     | Earthing pin                  | _            | Ground pin. This pin must be connected to 0 V.                                                                                                                                             |

| CVIDEO  | Composite video signal output | Output       | This pin outputs the composite video signal. The output signal is 2 VP-P. In superimpose mode, this pin's signal consists of the OSD signal combined with the input composite signal CVIN. |

| LECHA   | Character level input         | Input        | This input pin is used for controlling the "white" character color level of the OSD signal.                                                                                                |

| LEBK    | Black level input             | Input        | This input pin is used for controlling the "black" character color level of the OSD signal.                                                                                                |

| CVIN    | Composite video signal input  | Input        | This pin inputs the external composite video signal. In superimpose mode, this pin's signal consists of the OSD signal combined with the external composite video signal.                  |

| HOR     | Synchronous signal input      | Input        | This pin inputs the external composite video signal. This pin inputs the clamped external video signal, sync-sep internal.                                                                 |

| VREF    | Slice level input             | Input        | This input pin is used to determine the slice voltage for extracting the sync signals from the video composite signal.                                                                     |

| LP1     | Filter output 1               | Output       | This is filter output pin 1.                                                                                                                                                               |

| VDD2    | Power pin                     | _            | Analog power supply pin. This pin must be connected to +5 V.                                                                                                                               |

| LP2     | Filter output 2               | Output       | This is filter output pin 2.                                                                                                                                                               |

| OSCOUT  | fsc I/O pin for               | Output       | These are the sub-carrier oscillation (fsc) input pins for synchronous signal generating.                                                                                                  |

| OSCIN   | synchronous signal generating | Input        | NTSC (3.580 MHz), PAL (4.434 MHz), M-PAL (3.576 MHz) (Note).                                                                                                                               |

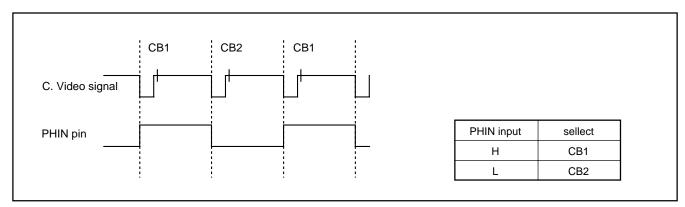

| PHIN    | PHASE control input           | Input        | Control the phase changing by scanning line by PAL, M-PAL method.                                                                                                                          |

| P0      | Port output                   | Output       | This output pin can be configured to port P0 or YM output.                                                                                                                                 |

| P1      | Port output                   | Output       | This output pin can be configured to port P1 or BLNK output.                                                                                                                               |

| P2      | Port output                   | Output       | This output pin can be configured to port P2 or B output.                                                                                                                                  |

| P3      | Port output                   | Output       | This output pin can be configured to port P3 or G output.                                                                                                                                  |

| P4      | Port output                   | Output       | This output pin can be configured to port P4 or R output.                                                                                                                                  |

| P5      | Port output                   | Output       | This output pin can be configured to port P5 or CSYN output.                                                                                                                               |

| TESTA   | Test input                    | Input        | Factory test pin. The pin must be connected to GND.                                                                                                                                        |

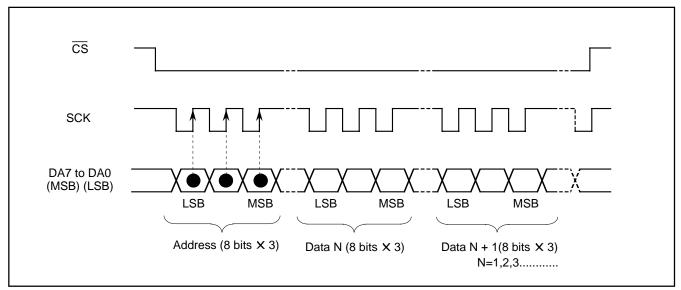

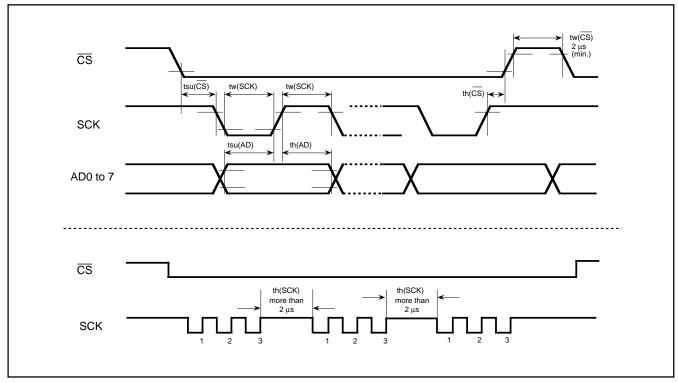

| SCK     | Clock input for data input    | Input        | This pin is enabled when the CS pin is "L". Data input to pins AD0 to AD7 is latched at the rising edge of this signal. This pin is hysteresis input.                                      |

| CS      | Chip select input             | Input        | This is chip selection input pin. When this pin is "L", transmission is enabled. This pin is hysteresis input.                                                                             |

Note: fsc signal input .....refer to "note on when fsc signal input".

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

#### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

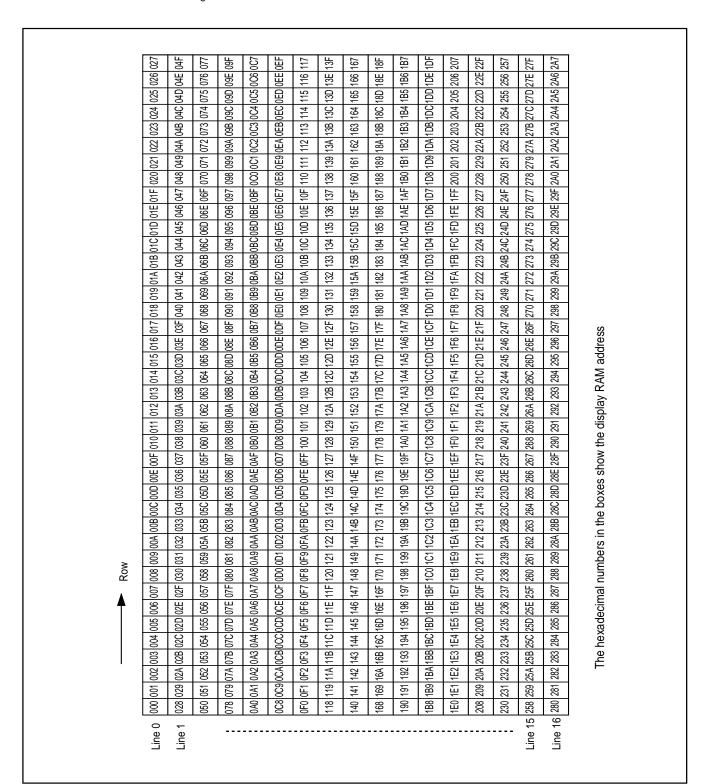

#### **MEMORY CONSTRUCTION**

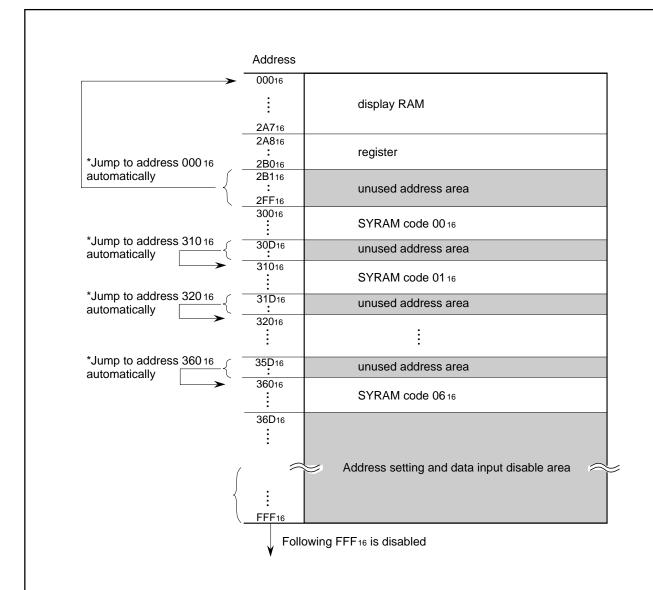

Address 00016 to 2A716 are assigned to the display RAM, 2A816 to 2B016 are assigned to the display control registers and 30016 to 36C16 are assigned to SYRAM.

The internal circuit is reset and all display control registers (address 2A816 to 2B016) are set to "0". The memory constitution of display RAM and register is shown in Figure 1 and the memory constitution of SYRAM is shown in Figure 2.

Table 1 The memory constitution of display RAM and register

| add-<br>ress | DA17 | DA16       | DA15       | DA14       | DA13       | DA12       | DA11       | DA10       | DAF        | DAE         | DAD        | DAC        | DAB        | DAA        | DA9        | DA8        | DA7        | DA6        | DA5        | DA4        | DA3        | DA2        | DA1        | DA0        |

|--------------|------|------------|------------|------------|------------|------------|------------|------------|------------|-------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| 00016        | SB   | SG         | SR         | 0          | 0          | 0          | SYC2       | SYC1       | SYC0       | ВВ          | BG         | BR         | BLINK      | СВ         | CG         | CR         | 0          | C6         | C5         | C4         | СЗ         | C2         | C1         | C0         |

| 1            | SY   | color set  | ting       | 0          | 0          | 0          | SYR        | AM se      | tting      | Raste       | er color s | etting     | BLINK      | Chara      | cter color | setting    | 0          |            | (          | Chara      | cter s     | etting     |            |            |

| 2A716        | SB   | SG         | SR         | 0          | 0          | 0          | SYC2       | SYC1       | SYC0       | ВВ          | BG         | BR         | BLINK      | СВ         | CG         | CR         | 0          | C6         | C5         | C4         | СЗ         | C2         | C1         | C0         |

| 2A816        | ı    | TEST<br>3  | TEST<br>2  | TEST<br>1  | TEST<br>0  | TEST<br>11 | TEST<br>10 | HP8        | HP7        | HP6         | HP5        | HP4        | HP3        | HP2        | HP1        | HP0        | VP7        | VP6        | VP5        | VP4        | VP3        | VP2        | VP1        | VP0        |

| 2A916        | ı    | -          | -          | BLINK<br>3 | BLINK<br>2 | BLINK<br>1 | BLINK<br>0 | HSZ<br>16  | HSZ<br>15  | HSZ<br>14   | HSZ<br>13  | HSZ<br>12  | HSZ<br>11  | HSZ<br>10  | HSZ<br>9   | HSZ<br>8   | HSZ<br>7   | HSZ<br>6   | HSZ<br>5   | HSZ<br>4   | HSZ<br>3   | HSZ<br>2   | HSZ<br>1   | HSZ<br>0   |

| 2AA16        | ı    | -          | -          | TEST<br>12 | EQP        | TEST<br>20 | HIDE       | VSZ<br>16  | VSZ<br>15  | VSZ<br>14   | VSZ<br>13  | VSZ<br>12  | VSZ<br>11  | VSZ<br>10  | VSZ<br>9   | VSZ<br>8   | VSZ<br>7   | VSZ<br>6   | VSZ<br>5   | VSZ<br>4   | VSZ<br>3   | VSZ<br>2   | VSZ<br>1   | VSZ<br>0   |

| 2AB16        | ı    | -          | TEST<br>26 | TEST<br>25 | PHASE<br>2 | PHASE<br>1 | PHASE<br>0 | DSP0<br>16 | DSP0<br>15 | DSP0<br>14  | DSP0<br>13 | DSP0<br>12 | DSP0<br>11 | DSP0<br>10 | DSP0<br>09 | DSP0<br>08 | DSP0<br>07 | DSP0<br>06 | DSP0<br>05 | DSP0<br>04 | DSP0<br>03 | DSP0<br>02 | DSP0<br>01 | DSP0<br>00 |

| 2AC16        | ı    | -          | -          | TEST<br>21 | LINE<br>B  | LINE<br>G  | LINE<br>R  | DSP1<br>16 | DSP1<br>15 | DSP1<br>14  | DSP1<br>13 | DSP1<br>12 | DSP1<br>11 | DSP1<br>10 | DSP1<br>09 | DSP1<br>08 | DSP1<br>07 | DSP1<br>06 | DSP1<br>05 | DSP1<br>04 | DSP1<br>03 | DSP1<br>02 | DSP1<br>01 | DSP1<br>00 |

| 2AD16        | ı    | TEST<br>23 | TEST<br>22 | SERS<br>0  | -          | -          | -          | ERS<br>16  | ERS<br>15  | ERS<br>14   | ERS<br>13  | ERS<br>12  | ERS<br>11  | ERS<br>10  | ERS<br>9   | ERS<br>8   | ERS<br>7   | ERS<br>6   | ERS<br>5   | ERS<br>4   | ERS<br>3   | ERS<br>2   | ERS<br>1   | ERS<br>0   |

| 2AE16        | _    | -          | _          | _          | _          | SEND<br>4  | SEND<br>3  | SEND<br>2  | SEND<br>1  | SEND<br>0   | SST<br>4   | SST<br>3   | SST<br>2   | SST<br>1   | SST<br>0   | SLIN<br>4  | SLIN<br>3  | SLIN<br>2  | SLIN<br>1  | SLIN<br>0  | SBIT<br>3  | SBIT 2     | SBIT<br>1  | SBIT<br>0  |

| 2AF16        | PC7  | PC6        | PC5        | PC4        | PC3        | PC2        | PC1        | PC0        | ALL24      | SRAND<br>2  | SRAND<br>1 | SRAND<br>0 | PTD<br>5   | PTD<br>4   | PTD<br>3   | PTD<br>2   | PTD<br>1   | PTD<br>0   | PTC<br>5   | PTC<br>4   | PTC<br>3   | PTC<br>2   | PTC<br>1   | PTC<br>0   |

| 2B016        | _    | TEST<br>19 | TEST<br>18 | TEST<br>17 | TEST<br>24 | LEVEL<br>2 | LEVEL<br>1 | LEVEL<br>0 | INT<br>NON | PAL<br>NTSC | MPAL       | PALH       | TEST<br>16 | TEST<br>15 | SEPV1      | SEPV0      | BLK        | _          | DSP<br>ONV | DSP<br>ON  | _          | SEL<br>COR | SCOR       | EX         |

$<sup>\</sup>label{eq:TESTn} \mbox{TESTn } \mbox{ (n = number) is MITSUBISHI test memory. Set 0 to all bits.}$

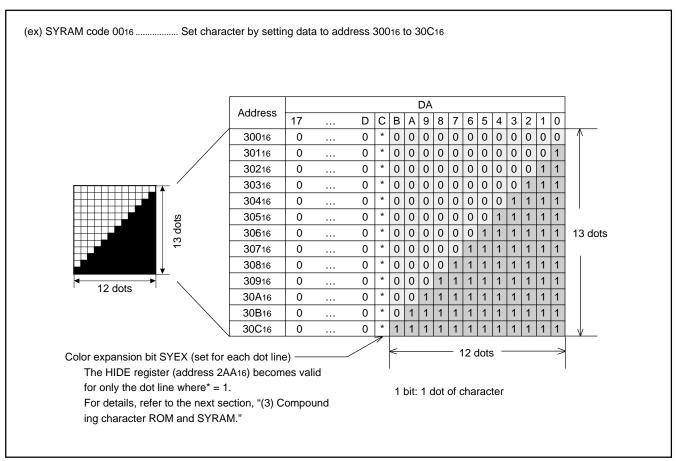

Table 2 The memory constitution of SYRAM

| add-<br>ress        | DA17 ~ DAD | DAC               | DAB               | DAA               | DA9               | DA8               | DA7               | DA6               | DA5               | DA4                 | DA3               | DA2               | DA1               | DA0                 | SYRAM code |

|---------------------|------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|---------------------|------------|

| 30016               | 0          | SYEX              | S00B              | S00A              | S009              | S008              | S007              | S006              | S005              | S004                | S003              | S002              | S001              | S000                | 0016       |

| 30C16               |            | SYEX              | S00B              | S00A              | S009              | S008              | S007              | S006              | S005              | S004                | S003              | S002              | S001              | S000                | 0010       |

| 31016               |            | SYEX              | S01B              | S01A              | S019              | S018              | S017              | S016              | S015              | S014                | S013              | S012              | S011              | S010                |            |

| 31C16               | 0          | :<br>SYEX         | :<br>S01B         | :<br>S01A         | :<br>S019         | :<br>S018         | S017              | :<br>S016         | :<br>S015         | :<br>S014           | :<br>S013         | :<br>S012         | :<br>S011         | <br>S010            | 0116       |

| ı                   | :          |                   |                   |                   |                   |                   |                   | 1                 |                   |                     |                   |                   |                   |                     | ì          |

| 35016<br>≀<br>35C16 | 0          | SYEX<br>:<br>SYEX | S05B<br>:<br>S05B | S05A<br>:<br>S05A | S059<br>:<br>S059 | S058<br>:<br>S058 | S057<br>:<br>S057 | S056<br>:<br>S056 | S055<br>:<br>S055 | S054<br>:<br>S054   | S053<br>:<br>S053 | S052<br>:<br>S052 | S051<br>:<br>S051 | \$050<br>:<br>\$050 | 0516       |

| 36016<br>≀<br>36C16 | 0          | SYEX<br>:<br>SYEX | S06B<br>:<br>S06B | S06A<br>:<br>S06A | S069<br>:<br>S069 | S068<br>:<br>S068 | S067<br>:<br>S067 | S066<br>:<br>S066 | S065<br>:<br>S065 | \$064<br>:<br>\$064 | S063<br>:<br>S063 | S062<br>:<br>S062 | S061<br>:<br>S061 | \$060<br>:<br>\$060 | 0616       |

<sup>¿ :</sup> Name or value changes by definite ratio.

<sup>:</sup> The same name or value continues.

#### **SCREEN CONSTITUTION**

The screen lines and rows are determined from each address of the display RAM.

The screen constitution is shown in Figure 1.

Fig. 1 Screen constitution

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

### **REGISTERS DESCRIPTION**

(1) Address 2A816

| 5.4 | Б        |        | Contents                                             | 5 .                                                              |

|-----|----------|--------|------------------------------------------------------|------------------------------------------------------------------|

| DA  | Register | Status | Function                                             | Remarks                                                          |

| 0   | VP0      | 1      | If VS is the vertical display start location,        | The vertical start location is specified using the 8 bits from   |

| 1   | VP1      | 1      | $VS = H \times \left(\sum_{n=0}^{7} 2^n VP_n\right)$ | VP7 to VP0.<br>VP7 to VP0 < 1416 are not<br>available.           |

| 2   | VP2      | 1      | H: Cycle with the horizontal synchronizing pulse     | available.                                                       |

| 3   | VP3      | 1      |                                                      |                                                                  |

| 4   | VP4      | 1      |                                                      |                                                                  |

| 5   | VP5      | 1      |                                                      |                                                                  |

| 6   | VP6      | ①<br>1 |                                                      |                                                                  |

| 7   | VP7      | 0 1    |                                                      |                                                                  |

| 8   | HP0      | 1      | If HS is the horizontal display start location,      | The horizontal start location is specified using the 9 bits from |

| 9   | HP1      | 0 1    | $HS = T \times (\sum_{n=0}^{8} 2^{n} HPn + 9)$       | HP8 to HP0.<br>HP8 to HP0 < 1916 are not<br>available.           |

| Α   | HP2      | 0 1    | T: Cycle with the display clock                      | avaliable.                                                       |

| В   | HP3      | 1      | HOR                                                  |                                                                  |

| С   | HP4      | 1      | TV screen                                            |                                                                  |

| D   | HP5      | 1      |                                                      |                                                                  |

| E   | HP6      | 1      | HS Character displaying area                         |                                                                  |

| F   | HP7      | 0 1    |                                                      |                                                                  |

| 10  | HP8      | 1      | 1 bit weights 1 clock.                               |                                                                  |

| 11  | TEST10   | 1      | Test mode (Must be cleared to 0.)                    |                                                                  |

| 12  | TEST11   | 0 1    |                                                      |                                                                  |

| 13  | TEST0    | 0 1    |                                                      |                                                                  |

| 14  | TEST1    | 0 1    |                                                      |                                                                  |

| 15  | TEST2    | 0 1    |                                                      |                                                                  |

| 16  | TEST3    | ①<br>1 |                                                      |                                                                  |

| 17  |          | 1      | Must be cleared to 0.                                |                                                                  |

$\textbf{Note} : \text{The mark} \bigcirc \text{ around the status value means the reset status by the "L" level is input to $\overline{AC}$ pin.}$

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

## (2) Address 2A9<sub>16</sub>

|    | 5        |        |                                 | Contents                          |                |                                                                       |

|----|----------|--------|---------------------------------|-----------------------------------|----------------|-----------------------------------------------------------------------|

| DA | Register | Status |                                 | Function                          |                | Remarks                                                               |

| 0  | HSZ0     | 1      | HSZx                            | Horizontal direction character    | size           | Set to line 0 of display RAM                                          |

| 1  | HSZ1     | 1      | 0                               | 1T/dot                            |                | Set to line 1 of display RAM                                          |

| 2  | HSZ2     | 1      | 1                               | 2T/dot                            |                | Set to line 2 of display RAM                                          |

| 3  | HSZ3     | ①<br>1 |                                 | T: Display                        | y clock        | Set to line 3 of display RAM                                          |

| 4  | HSZ4     | 0 1    |                                 |                                   |                | Set to line 4 of display RAM                                          |

| 5  | HSZ5     | 0      |                                 |                                   |                | Set to line 5 of display RAM                                          |

| 6  | HSZ6     | 0 1    |                                 |                                   |                | Set to line 6 of display RAM                                          |

| 7  | HSZ7     | 0 1    |                                 |                                   |                | Set to line 7 of display RAM                                          |

| 8  | HSZ8     | 0 1    |                                 |                                   |                | Set to line 8 of display RAM                                          |

| 9  | HSZ9     | 0 1    |                                 |                                   |                | Set to line 9 of display RAM                                          |

| Α  | HSZ10    | 0 1    |                                 |                                   |                | Set to line 10 of display RAM                                         |

| В  | HSZ11    | 0 1    |                                 |                                   |                | Set to line 11 of display RAM                                         |

| С  | HSZ12    | 0 1    |                                 |                                   |                | Set to line 12 of display RAM                                         |

| D  | HSZ13    | 0 1    |                                 |                                   |                | Set to line 13 of display RAM                                         |

| E  | HSZ14    | ①<br>1 |                                 |                                   |                | Set to line 14 of display RAM                                         |

| F  | HSZ15    | ①<br>1 |                                 |                                   |                | Set to line 15 of display RAM                                         |

| 10 | HSZ16    | 0 1    |                                 |                                   |                | Set to line 16 of display RAM                                         |

| 11 | BLINK0   | 1      | BLINK1                          | 0                                 | 1              | Blinking duty ratio can be altered.                                   |

| 12 | BLINK1   | ①<br>1 | 0                               | -                                 | y 25%<br>y 75% |                                                                       |

| 13 | BLINK2   | ①<br>1 | Cycle approxima Cycle approxima |                                   |                | Blinking cycle can be altered.                                        |

|    |          | 0      | Normal blinking                 |                                   |                | Character is in flashing state.                                       |

| 14 | BLINK3   | 1      | Normal characte                 | r, reversed character alternation | n display.     | Character is always displayed (normal character, reversed character). |

| 15 | _        | 1      | Must be cleared                 | to 0.                             |                |                                                                       |

| 16 | _        | 1      |                                 |                                   |                |                                                                       |

| 17 | _        | 1      |                                 |                                   |                |                                                                       |

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

## (3) Address 2AA<sub>16</sub>

|    | 5        |        |                                        | Contents                             |                                                                |

|----|----------|--------|----------------------------------------|--------------------------------------|----------------------------------------------------------------|

| DA | Register | Status |                                        | Function                             | Remarks                                                        |

| 0  | VSZ0     | 1      | VSZx                                   | Vertical direction character size    | Set to line 0 of display RAM                                   |

| 1  | VSZ1     | 0      | 0                                      | 1H/dot                               | Set to line 1 of display RAM                                   |

| 2  | VSZ2     | 1      | 1                                      | 2H/dot                               | Set to line 2 of display RAM                                   |

| 3  | VSZ3     | 1      |                                        | H: Horizontal synchronous pulse      | Set to line 3 of display RAM                                   |

| 4  | VSZ4     | 1      |                                        |                                      | Set to line 4 of display RAM                                   |

| 5  | VSZ5     | 1      |                                        |                                      | Set to line 5 of display RAM                                   |

| 6  | VSZ6     | 1      |                                        |                                      | Set to line 6 of display RAM                                   |

| 7  | VSZ7     | 1      |                                        |                                      | Set to line 7 of display RAM                                   |

| 8  | VSZ8     | 1      |                                        |                                      | Set to line 8 of display RAM                                   |

| 9  | VSZ9     | 0 1    |                                        |                                      | Set to line 9 of display RAM                                   |

| А  | VSZ10    | 0 1    |                                        |                                      | Set to line 10 of display RAM                                  |

| В  | VSZ11    | 0 1    |                                        |                                      | Set to line 11 of display RAM                                  |

| С  | VSZ12    | 0 1    |                                        |                                      | Set to line 12 of display RAM                                  |

| D  | VSZ13    | 0 1    |                                        |                                      | Set to line 13 of display RAM                                  |

| Е  | VSZ14    | 0 1    |                                        |                                      | Set to line 14 of display RAM                                  |

| F  | VSZ15    | 0 1    |                                        |                                      | Set to line 15 of display RAM                                  |

| 10 | VSZ16    | 0 1    |                                        |                                      | Set to line 16 of display RAM                                  |

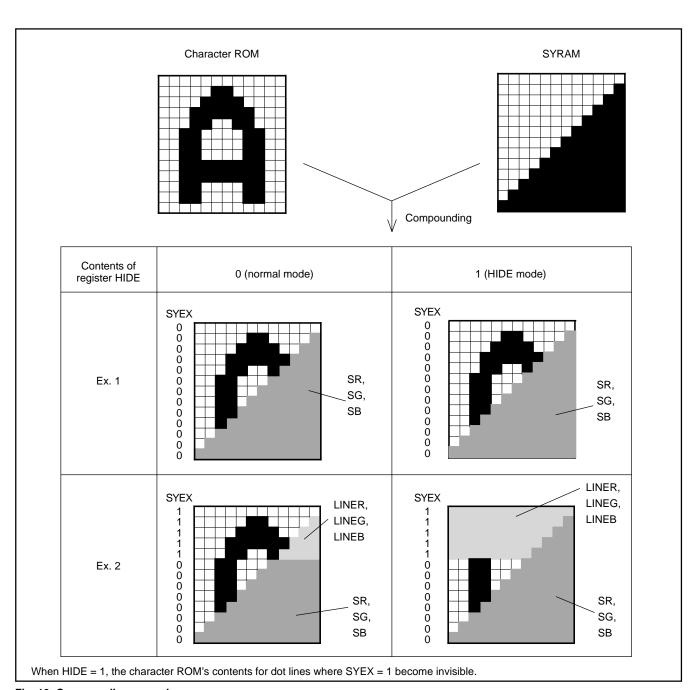

| 11 | HIDE     | 0 1    | SYRAM writting                         | over<br>over or character erasing    | Decided by register LINER, G and B or DAC bit (SYEX) of SYRAM. |

| 12 | TEST20   | 0 1    | Test mode (Must                        | t be cleared to 0.)                  |                                                                |

| 13 | EQP      | 1      | It does not include It includes equiva | de equivalent pulse.<br>alent pulse. |                                                                |

| 14 | TEST12   | 1      | Test mode (Must                        | t be cleared to 0.)                  |                                                                |

| 15 | _        | 1      | Must be cleared                        | to 0.                                |                                                                |

| 16 | _        | 1      |                                        |                                      |                                                                |

| 17 |          | 0      |                                        |                                      |                                                                |

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

### (4) Address 2AB<sub>16</sub>

| DA | Danistan |        |                                                     | Contents                                                                                    |                                            |         | Damada                            |

|----|----------|--------|-----------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------|---------|-----------------------------------|

| DA | Register | Status |                                                     | Functio                                                                                     | n                                          |         | Remarks                           |

| 0  | DSP0 00  | 1      | DSP0XX                                              | 0                                                                                           | 1                                          |         | Set to line 0 of display RAM      |

| 1  | DSP0 01  | 0 1    | DSP1XX<br>0                                         | Character                                                                                   | Border                                     |         | Set to line 1 of display RAM      |

| 2  | DSP0 02  | 0 1    | 1                                                   | Matrix-outline                                                                              | Halftone                                   |         | Set to line 2 of display RAM      |

| 3  | DSP0 03  | 0      |                                                     |                                                                                             | (Note) dress 2AB16) and D                  | SP1XX   | Set to line 3 of display RAM      |

| 4  | DSP0 04  | 0 1    | (address 2AC <sub>16</sub> ).<br>At internal synchr | onous mode (EX                                                                              | = 1), display monito                       |         | Set to line 4 of display RAM      |

| 5  | DSP0 05  | 0 1    | area is all blankin                                 | g signal (BLINK of                                                                          | ліриі) агеа.                               |         | Set to line 5 of display RAM      |

| 6  | DSP0 06  | 0      |                                                     |                                                                                             | cessary to input the<br>ne CVIN pin, and e |         | Set to line 6 of display RAM      |

| 7  | DSP0 07  | 0 1    |                                                     |                                                                                             | tor in series. Howe<br>le only with super  |         | Set to line 7 of display RAM      |

| 8  | DSP0 08  | 1      |                                                     |                                                                                             |                                            |         | Set to line 8 of display RAM      |

| 9  | DSP0 09  | 0 1    |                                                     |                                                                                             |                                            |         | Set to line 9 of display RAM      |

| Α  | DSP0 10  | 0 1    |                                                     |                                                                                             |                                            |         | Set to line 10 of display RAM     |

| В  | DSP0 11  | 0 1    |                                                     |                                                                                             |                                            |         | Set to line 11 of display RAM     |

| С  | DSP0 12  | 1      |                                                     |                                                                                             |                                            |         | Set to line 12 of display RAM     |

| D  | DSP0 13  | 1      |                                                     |                                                                                             |                                            |         | Set to line 13 of display RAM     |

| E  | DSP0 14  | 0 1    |                                                     |                                                                                             |                                            |         | Set to line 14 of display RAM     |

| F  | DSP0 15  | 0 1    |                                                     |                                                                                             |                                            |         | Set to line 15 of display RAM     |

| 10 | DSP0 16  | 1      |                                                     |                                                                                             |                                            |         | Set to line 16 of display RAM     |

| 11 | PHASE 0  | 1      | 0 0 0                                               | SELCOR: Black                                                                               | Black                                      | <       | Raster color setting.             |

| 12 | PHASE 1  | 0 1    | 0 1                                                 | 1         Red           0         Green           1         Yellow           0         Blue | Red-:<br>Green-<br>Yellov<br>Gray          | –2<br>N |                                   |

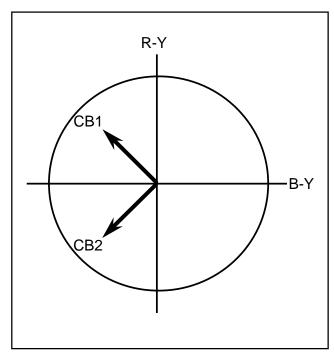

| 13 | PHASE 2  | 0 1    | 1 0                                                 | 1 Magenta Cyan White                                                                        |                                            | –2<br>1 | Refer Fig 3, 4 about phase angle. |

| 14 | TEST25   | 0 1    | Test mode (Must                                     | be cleared to 0.)                                                                           |                                            |         | 3 - ,                             |

| 15 | TEST26   | 0 1    |                                                     |                                                                                             |                                            |         |                                   |

| 16 | _        | 0      | Must be cleared to                                  | o 0.                                                                                        |                                            |         |                                   |

| 17 | _        | 0 1    |                                                     |                                                                                             |                                            |         |                                   |

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

## (5) Address 2AC<sub>16</sub>

| DA | Register  |          |                                                                        | Contents                                                           |                                         |             | Remarks                                                                  |

|----|-----------|----------|------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------|-------------|--------------------------------------------------------------------------|

|    | 1109.0101 | Status   |                                                                        | Functio                                                            | n<br>                                   |             |                                                                          |

| 0  | DSP1 00   | 1        | DSP0XX<br>DSP1XX                                                       | 0                                                                  | 1                                       |             | Set to line 0 of display RAM                                             |

| 1  | DSP1 01   | 0 1      | 0                                                                      | Character                                                          | Border                                  |             | Set to line 1 of display RAM                                             |

| 2  | DSP1 02   | 1        | 1                                                                      | Matrix-outline                                                     | Halftone                                |             | Set to line 2 of display RAM                                             |

| 3  | DSP1 03   | 0 1      | Set by combination                                                     | on of DSP0xx (add                                                  | (Note) dress 2AB16) and [               | OSP1XX      | Set to line 3 of display RAM                                             |

| 4  | DSP1 04   | 0 1      | (address 2AC <sub>16</sub> ).<br>At internal synchrarea is all blankin |                                                                    | = 1), display monit                     | or signal   | Set to line 4 of display RAM                                             |

| 5  | DSP1 05   | 0        | area is all blarikiri                                                  | g signal (BENN of                                                  | ліриі) агеа.                            |             | Set to line 5 of display RAM                                             |

| 6  | DSP1 06   | 0        | composite                                                              | video signal to th                                                 | cessary to input the CVIN pin, and      | externally  | Set to line 6 of display RAM                                             |

| 7  | DSP1 07   | 0 1      |                                                                        |                                                                    | tor in series. How<br>le only with supe |             | Set to line 7 of display RAM                                             |

| 8  | DSP1 08   | 0 1      | 212-111-121                                                            |                                                                    |                                         |             | Set to line 8 of display RAM                                             |

| 9  | DSP1 09   | 0 1      |                                                                        |                                                                    |                                         |             | Set to line 9 of display RAM                                             |

| Α  | DSP1 10   | 0 1      |                                                                        |                                                                    |                                         |             | Set to line 10 of display RAM                                            |

| В  | DSP1 11   | 0 1      |                                                                        |                                                                    |                                         |             | Set to line 11 of display RAM                                            |

| С  | DSP1 12   | 0        |                                                                        |                                                                    |                                         |             | Set to line 12 of display RAM                                            |

| D  | DSP1 13   | 0 1      |                                                                        |                                                                    |                                         |             | Set to line 13 of display RAM                                            |

| E  | DSP1 14   | 0 1      |                                                                        |                                                                    |                                         |             | Set to line 14 of display RAM                                            |

| F  | DSP1 15   | 0        |                                                                        |                                                                    |                                         |             | Set to line 15 of display RAM                                            |

| 10 | DSP1 16   | 0        |                                                                        |                                                                    |                                         |             | Set to line 16 of display RAM                                            |

| 11 | LINER     | 0 1      | LINE LINE LINE B G F                                                   |                                                                    | Color<br>=0 SELCO<br>Blac               |             | SYRAM color setting. Color is decided by DAC bit (SYEX) of SYRAM or HIDE |

| 12 | LINEG     | 0 1      | 0 1                                                                    | 1         Red           0         Green           1         Yellow |                                         | ı–2<br>W    | register.                                                                |

| 13 | LINEB     | 0 1      | 1 0                                                                    | ) Cyan                                                             | Gray<br>a Yellow<br>Cyar<br>Whit        | <i>i</i> –2 | Refer Fig. 3, 4 about phase angle.                                       |

| 14 | TEST21    | <u> </u> | Test mode (Must                                                        | •                                                                  |                                         |             | 3 3, 4444, 444 3                                                         |

| 15 | _         | 0 1      |                                                                        |                                                                    |                                         |             |                                                                          |

| 16 | _         | 0 1      | Must be cleared to                                                     | o 0.                                                               |                                         |             |                                                                          |

| 17 | _         | 0 1      |                                                                        |                                                                    |                                         |             |                                                                          |

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

### (6) Address 2AD<sub>16</sub>

|    |          |        |                                           | Contents                                                           |                                       |

|----|----------|--------|-------------------------------------------|--------------------------------------------------------------------|---------------------------------------|

| DA | Register | Status |                                           | Function                                                           | Remarks                               |

| 0  | ERS0     | 0      | Erase display RA                          |                                                                    | Set to line 0 of display RAM          |

| 1  | ERS1     | 0      | ERSx<br>0                                 | RAM erase<br>do not erase                                          | Set to line 1 of display RAM          |

| 2  | ERS2     | 0      |                                           | do erase ore than 2 bits at the same time.                         | Set to line 2 of display RAM          |

| 3  | ERS3     | 0      | The setting is not<br>Therefore, it is no | retained even if the bit is set to "1". of necessary to cancel it. | Set to line 3 of display RAM          |

| 4  | ERS4     | 0 1    |                                           |                                                                    | Set to line 4 of display RAM          |

| 5  | ERS5     | 0 1    |                                           |                                                                    | Set to line 5 of display RAM          |

| 6  | ERS6     | 0 1    |                                           |                                                                    | Set to line 6 of display RAM          |

| 7  | ERS7     | 1      |                                           |                                                                    | Set to line 7 of display RAM          |

| 8  | ERS8     | 1      |                                           |                                                                    | Set to line 8 of display RAM          |

| 9  | ERS9     | 1      |                                           |                                                                    | Set to line 9 of display RAM          |

| А  | ERS10    | ①<br>1 |                                           |                                                                    | Set to line 10 of display RAM         |

| В  | ERS11    | ①<br>1 |                                           |                                                                    | Set to line 11 of display RAM         |

| С  | ERS12    | 1      |                                           |                                                                    | Set to line 12 of display RAM         |

| D  | ERS13    | 1      |                                           |                                                                    | Set to line 13 of display RAM         |

| Е  | ERS14    | 1      |                                           |                                                                    | Set to line 14 of display RAM         |

| F  | ERS15    | 1      |                                           |                                                                    | Set to line 15 of display RAM         |

| 10 | ERS16    | 1      |                                           |                                                                    | Set to line 16 of display RAM         |

| 11 | _        | ①<br>1 |                                           |                                                                    |                                       |

| 12 | _        | 1      | Must be cleared                           | to 0.                                                              |                                       |

| 13 | _        | 1      |                                           |                                                                    |                                       |

| 14 | SERS0    | 1      | do not erase SYF<br>erase SYRAM           | RAM                                                                | Set to SYRAM code 0016 to 0616 (Note) |

| 15 | TEST22   | 1      | Test mode (Must                           | be cleared to 0.)                                                  |                                       |

| 16 | TEST23   | 1      |                                           |                                                                    |                                       |

| 17 | _        | 0 1    | Must be cleared                           | to 0.                                                              |                                       |

Note: The setting is not retained even if the bit is set to "1". Therefore, it is not necessary to cancel it.

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

## (7) Address 2AE<sub>16</sub>

| D.* | D        |        | Contents                                                                | D I                                                     |

|-----|----------|--------|-------------------------------------------------------------------------|---------------------------------------------------------|

| DA  | Register | Status | Function                                                                | Remarks                                                 |

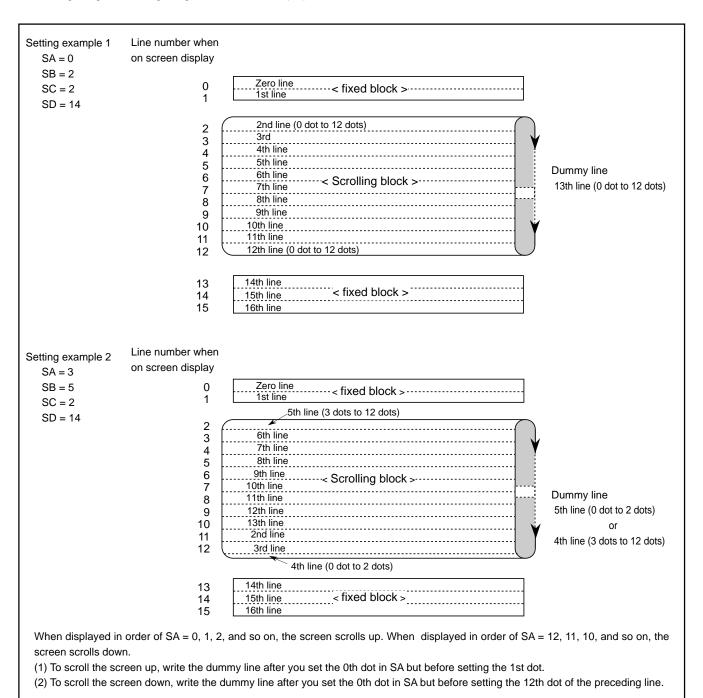

| 0   | SBIT0    | 1      | Set display start bit of scroll block:                                  | Setting valid<br>SA = 0 to 12                           |

| 1   | SBIT1    | 1      | $SA = \sum_{n=0}^{3} 2^n \text{ (SBITn)}$                               | invalid<br>SA = 13 to 15                                |

| 2   | SBIT2    | 0 1    |                                                                         |                                                         |

| 3   | SBIT3    | 0 1    |                                                                         |                                                         |

| 4   | SLIN0    | 1      | Set display start line of scroll block:                                 | Setting valid<br>SB = 0 to 16                           |

| 5   | SLIN1    | 1      | $SB = \sum_{n=0}^{4} 2^{n} (SLIN_n)$                                    | invalid<br>SB = 17 to 31                                |

| 6   | SLIN2    | 0 1    |                                                                         |                                                         |

| 7   | SLIN3    | 1      |                                                                         |                                                         |

| 8   | SLIN4    | 1      |                                                                         |                                                         |

| 9   | SST0     | 1      | Set start line of scroll block (last line number of the fixed block 1): | Setting valid<br>SC = 0 to 15                           |

| Α   | SST1     | 1      | $SC = \sum_{n=0}^{4} 2^{n} (SSTn)$                                      | invalid<br>SC = 16 to 31                                |

| В   | SST2     | 1      |                                                                         |                                                         |

| С   | SST3     | 1      |                                                                         |                                                         |

| D   | SST4     | 1      |                                                                         |                                                         |

| E   | SEND0    | 1      | Set start line of fixed block 2 (last line number of the scroll block): | When the scrolling on setting valid SD = 2 to 17        |

| F   | SEND1    | 1      | $SD = \sum_{n=0}^{4} 2^{n} (SENDn)$                                     | invalid SD = 18 to 31 When the scrolling off set SD = 0 |

| 10  | SEND2    | 1      | n=0                                                                     |                                                         |

| 11  | SEND3    | 1      |                                                                         | SD > SC + 2                                             |

| 12  | SEND4    | 1      |                                                                         |                                                         |

| 13  | _        | 1      | Must be cleared to 0.                                                   |                                                         |

| 14  | _        | 1      |                                                                         |                                                         |

| 15  | _        | 1      |                                                                         |                                                         |

| 16  | _        | 1      |                                                                         |                                                         |

| 17  | _        | 1      |                                                                         |                                                         |

**Note**: When the scrolling on, set the ratio which will be SC < SB < SD.

## SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

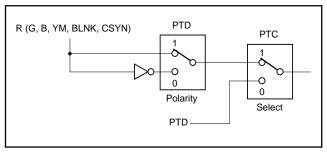

#### (8) Address 2AF<sub>16</sub>

| DΛ | Dogistor |        | Contents                                                                                                                | Pomorko                                                             |

|----|----------|--------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| DA | Register | Status | Function                                                                                                                | Remarks                                                             |

| 0  | PTC0     | 0      | Port P0 output                                                                                                          | - Select P0 pin                                                     |

| U  | F 100    | 1      | YM output                                                                                                               | Select F0 pill                                                      |

| 1  | PTC1     | 0      | Port P1 output                                                                                                          | Select P1 pin                                                       |

| '  | 1 101    | 1      | BLNK output                                                                                                             | Select 1 pill                                                       |

| 2  | PTC2     | 0      | Port P2 output                                                                                                          | Select P2 pin                                                       |

|    | 1 102    | 1      | B output                                                                                                                | Geleat 1 2 pm                                                       |

| 3  | PTC3     | 0      | Port P3 output                                                                                                          | - Select P3 pin                                                     |

|    |          | 1      | G output                                                                                                                | остория                                                             |

| 4  | PTC4     | 0      | Port P4 output                                                                                                          | Select P4 pin                                                       |

|    |          | 1      | R output                                                                                                                |                                                                     |

| 5  | PTC5     | 0      | Port P5 output                                                                                                          | Select P5 pin                                                       |

|    |          | (0)    | CSYN output                                                                                                             |                                                                     |

| 6  | PTD0     |        | When port output: 0 output, when YM output: negative polarity.                                                          | Select data of P0 pin                                               |

|    |          | 0      | When port output: 1 output, when YM output: polarity.  When port output: 0 output, when BLNK output: negative polarity. |                                                                     |

| 7  | PTD1     | 1      | When port output: 1 output, when BLNK output: negative polarity.                                                        | Select data of P1 pin                                               |

|    |          | 0      | When port output: 0 output, when B output: negative polarity.                                                           |                                                                     |

| 8  | PTD2     | 1      | When port output: 1 output, when B output: polarity.                                                                    | Select data of P2 pin                                               |

|    |          | 0      | When port output: 0 output, when G output: negative polarity.                                                           |                                                                     |

| 9  | PTD3     | 1      | When port output: 1 output, when G output: polarity.                                                                    | Select data of P3 pin                                               |

|    |          | 0      | When port output: 0 output, when R output: negative polarity.                                                           |                                                                     |

| Α  | PTD4     | 1      | When port output: 1 output, when R output: polarity.                                                                    | Select data of P4 pin                                               |

|    |          | 0      | When port output: 0 output, when CSYN output: negative polarity.                                                        |                                                                     |

| В  | PTD5     | 1      | When port output: 1 output, when CSYN output: polarity.                                                                 | Select data of P5 pin                                               |

| 0  | ODANDO   | 0      | SRAND SRAND SRAND2                                                                                                      | Condition of border display is                                      |

| С  | SRAND0   | 1      | 1 0 0 1                                                                                                                 | changeable.                                                         |

| D  | SRAND1   | 0      | 0 0 Complete border = 1 dot Right and dot border = 1 dot 0 1 Complete border = 2 dot Right and dot border = 2 dot       |                                                                     |

| U  | SKANDT   | 1      | 1 0 Complete border = 3 dot Right and dot border = 3 dot                                                                |                                                                     |

| Е  | SRAND2   | 0      | 1 1 Complete border = 4 dot Right and dot border = 4 dot                                                                |                                                                     |

| _  | 0104152  | 1      | Vertical direction is 1 dot only.                                                                                       |                                                                     |

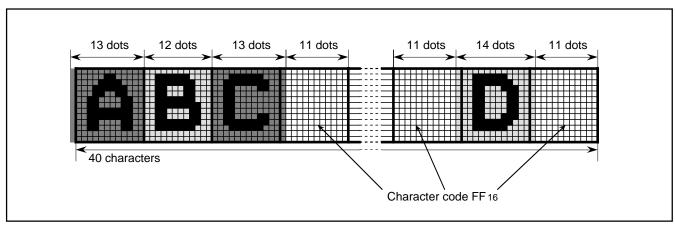

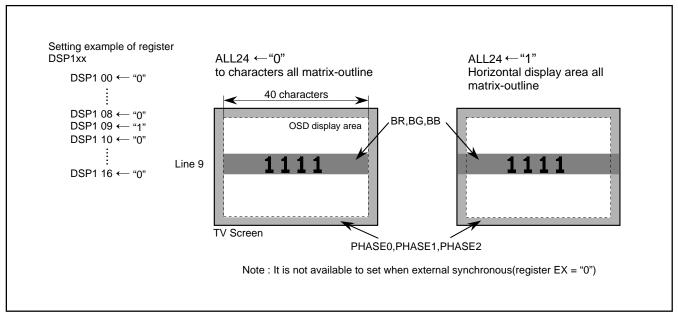

|    |          | 0      | Blanking with all 40 characters in matrix-outline mode                                                                  | Horizontal display range can be altered when all characters are in  |

| F  | ALL24    |        |                                                                                                                         | matrix-outline size.                                                |

| '  | ALLZ4    | 1      | Horizontal display period fully blanked with all characters in                                                          | At external synchronous, set to 0. Operation of character code FF16 |

|    |          |        | matrix-outline size.                                                                                                    | becomes ineffective.                                                |

| 10 | PC0      | 0      | Display frequency f⊤ control                                                                                            | PC7 to PC0 < 3616,                                                  |

|    | . 00     | 1      |                                                                                                                         | PC7 to PC0 > C616 is not available.                                 |

| 11 | PC1      | 0      | $fT = fH \times \left\{ \sum_{n=0}^{7} (2^n PC_n) + 512 \right\}$                                                       |                                                                     |

|    | _        | 1      | n=0                                                                                                                     |                                                                     |

| 12 | PC2      | 0      |                                                                                                                         |                                                                     |

|    |          | 1      |                                                                                                                         |                                                                     |

| 13 | PC3      | 0      |                                                                                                                         |                                                                     |

|    |          | 0      |                                                                                                                         |                                                                     |

| 14 | PC4      | 1      |                                                                                                                         |                                                                     |

|    |          | 0      |                                                                                                                         |                                                                     |

| 15 | PC5      | 1      |                                                                                                                         |                                                                     |

|    |          | 0      |                                                                                                                         |                                                                     |

| 16 | PC6      | 1      |                                                                                                                         |                                                                     |

|    |          | 0      |                                                                                                                         |                                                                     |