#### ISL73007SEH

Radiation Hardened 18V, 3A Point-of-Load Regulator

The ISL73007SEH is a radiation hardened Point-of-Load (POL) buck regulator that provides up to 3A of output current capability with an input voltage ranging from 3V to 18V. The device uses constant frequency peak current mode control architecture for fast loop transient response. The device uses internal compensation or an external Type-II compensation to optimize performance and stabilize the loop. The ISL73007SEH has an internally configured switching frequency of 500kHz. The ISL73007SEH switching frequency can be adjusted from 300kHz to 1MHz using an external resistor.

The ISL73007SEH integrates high-side (P-channel) and low-side (N-channel) power FETs. There are options for external or internal compensation, switching frequency, and slope control that can be implemented with a minimum of external components reducing the BOM count and design complexity.

The ISL73007SEH includes a comprehensive suite of operational features and protections, including preset undervoltage, overvoltage, overcurrent protections, power-good, soft-start, and over-temperature.

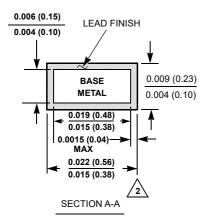

The ISL73007SEH operates across the temperature range of -55°C to +125°C and is available in a 14-lead ceramic dual in-line flat package (CDFP) and die form.

### **Applications**

Low Power Auxiliary Rails for FPGAs, DSPs, CPUs, and ASICs

#### **Features**

- Qualified to Renesas Rad Hard QML-V Equivalent Screening and QCI Flow (R34TB0001EU)

- All screening and QCI is in accordance with MIL-PRF-38535 Class-V

- Input Bias Voltage

- 3V to 18V

- Internal or external loop compensation

- 1% reference voltage over-temperature and radiation

- Switching frequency dependent soft-start

- Positive and negative overcurrent, over/undervoltage, and over-temperature protections

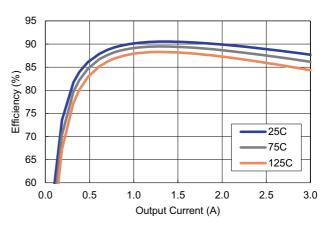

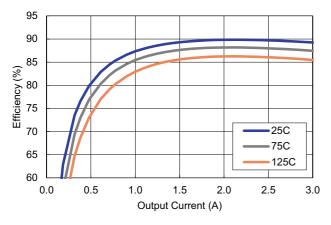

- High 500kHz efficiency ≥90% from 1A to 3A

- 300kHz to 1MHz adjustable switching frequency

- Adjustable slope compensation

- TID Rad Hard Assurance (RHA) wafer-by-wafer testing

- LDR (0.01rad(Si)/s): 75krad(Si)

- SEE Characterization

- No DSEE for V<sub>IN</sub> = 16.5V and V<sub>CC</sub> = 5.8V at 86MeV•cm<sup>2</sup>/mg

- SEFI <21µm<sup>2</sup> at 86MeV•cm<sup>2</sup>/mg

- SET <2.0% on V<sub>OUT</sub> at 86MeV•cm<sup>2</sup>/mg

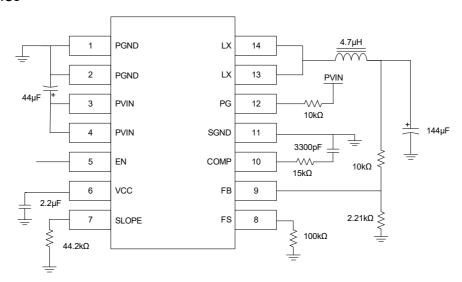

Figure 1. External Compensation Application Diagram for 12V to 3.3V, 500kHz

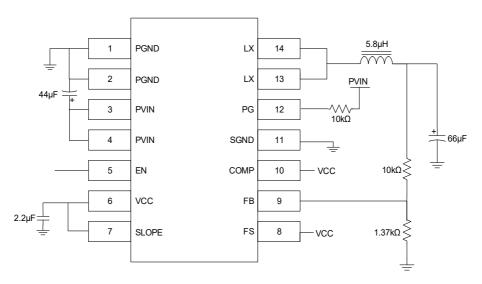

Figure 2. Internal Compensation Application Diagram for 12V to 5V, 500kHz

# **Contents**

| 1.       | Overvi      | ew                                                          |     |

|----------|-------------|-------------------------------------------------------------|-----|

|          | 1.1         | Block Diagram                                               | . 4 |

| 2.       | Pin Inf     | ormation                                                    | . 5 |

|          | 2.1         | Pin Assignments                                             | . 5 |

|          | 2.2         | Pin Descriptions                                            | . 5 |

| 3.       | Specif      | ications                                                    | . 7 |

|          | 3.1         | Absolute Maximum Ratings                                    | . 7 |

|          | 3.2         | Thermal Information                                         | . 7 |

|          | 3.3         | Recommended Operating Conditions                            | . 7 |

|          | 3.4         | Electrical Specifications                                   | . 8 |

|          | 3.5         | Operation Burn-In Deltas                                    |     |

| 4.       | Typica      | l Performance Curves                                        | 13  |

| 5.       | Theory      | y of Operation                                              | 21  |

|          | 5.1         | Description of Features                                     | 21  |

|          | 5.2         | Output Voltage Setting                                      | 21  |

|          | 5.3         | Internal Configuration Summary                              | 21  |

|          | 5.4         | External Configuration Summary                              |     |

|          | 5.5         | Frequency Selection                                         | 22  |

|          | 5.6         | Time Constraints on DC/DC Voltage Conversion                |     |

|          | 5.7         | Overcurrent Protection                                      |     |

|          | 5.8         | Negative Overcurrent Protection (NOCP)                      | 22  |

|          | 5.9         | Power Good                                                  | 23  |

|          | 5.10        | UVLO, Enable, Soft-start, Disable, and Soft-Stop            |     |

|          | 5.11        | Thermal Protection                                          |     |

|          | 5.12        | PWM Control and Compensation                                |     |

|          | 5.13        | Slope Compensation                                          |     |

|          | 5.14        | External Configuration Application Implementation Equations |     |

| 6.       | Typica      | I Application                                               | 25  |

|          | 6.1         | Typical Application Schematic                               |     |

|          | 6.2         | Design Requirements                                         |     |

|          | 6.3         | Set Output Voltage                                          |     |

|          | 6.4         | Set Switching Frequency                                     |     |

|          | 6.5         | Input Capacitor Selection                                   |     |

|          | 6.6         | Output Capacitor Selection                                  |     |

|          | 6.7         | Output Inductor Selection                                   |     |

|          | 6.8         | Slope Compensation Resistor                                 |     |

|          | 6.9         | Compensation Resistor                                       |     |

|          | 6.10        | Compensation Capacitor                                      |     |

| 7.       |             | t Considerations                                            |     |

| 7.<br>8. | •           | paracteristics                                              |     |

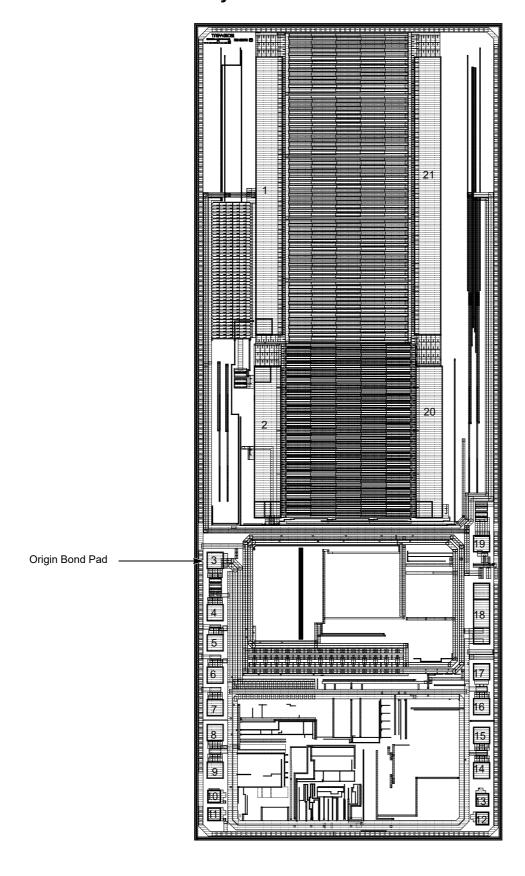

| 0.       | 8.1         | Metallization Mask Layout                                   |     |

| 0        | -           | ·                                                           |     |

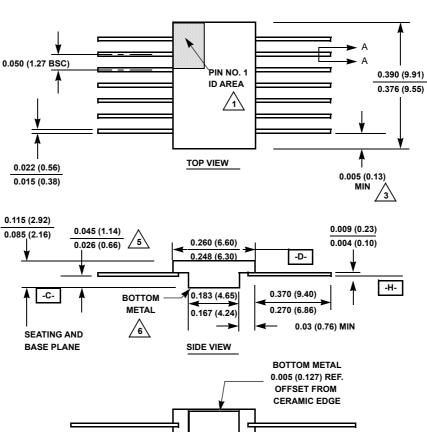

| 9.       |             | nge Outline Drawing                                         |     |

| 10.      |             | ng Information                                              |     |

| 11.      |             | on History                                                  |     |

| A.       | <b>ECAD</b> | Design Information                                          | 37  |

### 1. Overview

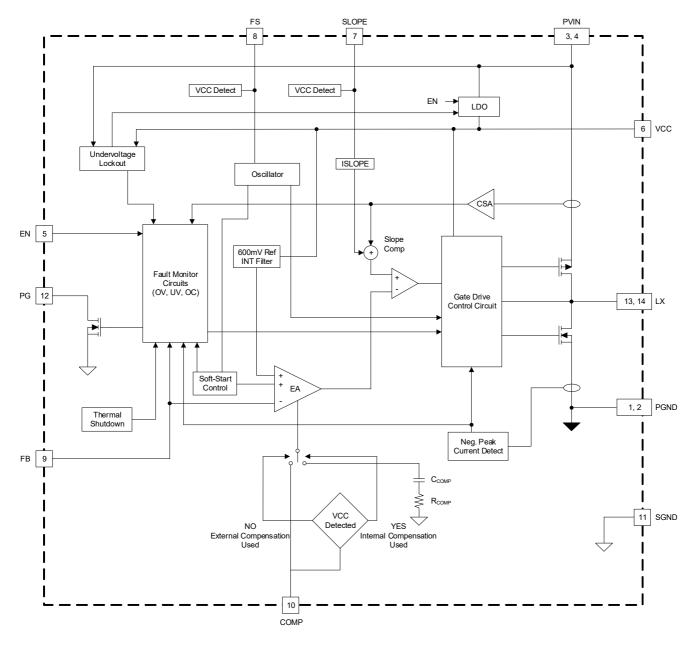

# 1.1 Block Diagram

Figure 3. Block Diagram

## 2. Pin Information

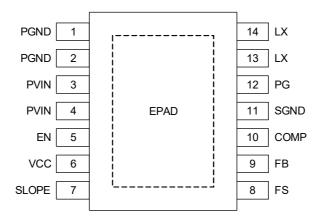

# 2.1 Pin Assignments

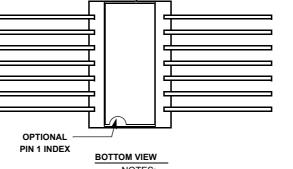

Figure 4. Pin Assignments - Top View

# 2.2 Pin Descriptions

| Pin<br>Number | Pin<br>Name | ESD<br>Circuit | Description                                                                                                                                                                                                                                                                                                                                                       |

|---------------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2          | PGND        | 3              | Power-ground connection. Ground return for the low-side power MOSFET                                                                                                                                                                                                                                                                                              |

| 3, 4          | PVIN        | 1              | Power Input. Supplies the power switches of the buck converter.                                                                                                                                                                                                                                                                                                   |

| 5             | EN          | 2              | Enable input. This input is a comparator-type input with a rising threshold of 1.2V. Bypass this pin to the PCB ground plane with a 10nF ceramic capacitor to mitigate SEE. This pin can be tied to a maximum of 5V.                                                                                                                                              |

| 6             | VCC         | 2              | Linear regulator output from PVIN to provide an internal bias supply rail of up to 5V. Bypass this pin to the PCB ground plane with a 2.2µF ceramic or low ESR Tantalum capacitor for stability, SEE, and noise mitigation. VCC is not intended to bias external circuits                                                                                         |

| 7             | SLOPE       | 2              | Slope Compensation. Connect a resistor from this pin to GND to externally set the slope compensation. This pin is a current source of 12µA into the external resistor. Connect the SLOPE pin to VCC to use the default internal slope compensation voltage of 1.2V.  If not connected to VCC, add a 1nF capacitor from this pin to ground for SEE mitigation.     |

| 8             | FS          | 2              | Frequency select pin. Tie to VCC for 500kHz operation. Connect a resistor to ground to program the frequency from 300kHz to 1MHz. Reference Equation 2 for the frequency setting formula.                                                                                                                                                                         |

| 9             | FB          | 2              | Error Amplifier inverting input. Connect a resistor divider from VOUT to GND with the midpoint driving the FB pin.                                                                                                                                                                                                                                                |

| 10            | COMP        | 2              | Error Amplifier output. The external compensation network is connected from this pin to GND. Tie this pin to VCC to use the internal Error Amplifier compensation setup.                                                                                                                                                                                          |

| 11            | SGND        | 3              | Signal ground. The ground is associated with the internal control circuitry. Connect this pin directly to the PCB ground plane at a single point. Pin 11 is connected to the thermal flash on the package bottom and lid seal ring.                                                                                                                               |

| 12            | PG          | 1              | Power-good output. The pin is an open-drain logic output pulled to SGND when the output is outside of the PGOOD range. The pin can be pulled to any voltage up to the PVIN abs maximum limit. Renesas recommends using a nominal $1k\Omega$ to $10k\Omega$ pull-up resistor. Bypass this pin to the PCB ground plane with a $100pF$ capacitor for SEE mitigation. |

| 13, 14        | LX          | N.A.           | Switch node connection. Connect this pin to the output filter inductor. Internally, this pin is connected to the common node of the synchronous MOSFET power switches.                                                                                                                                                                                            |

#### ISL73007SEH Datasheet

| Pin<br>Number | Pin<br>Name | ESD<br>Circuit | Description                                                 |                                  |                     |

|---------------|-------------|----------------|-------------------------------------------------------------|----------------------------------|---------------------|

| -             | EPAD        | N.A.           | EPAD internally connected to Pin 11 SGND and lid seal ring. |                                  |                     |

| ESD Circui    | ts          |                | PIN  24V CLAMP PGND Circuit 1                               | 8V<br>CLAMP<br>SGND<br>Circuit 2 | SGND PGND Circuit 3 |

## 3. Specifications

### 3.1 Absolute Maximum Ratings

**Caution:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

| Parameter                                        | Minimum    | Maximum               | Unit |

|--------------------------------------------------|------------|-----------------------|------|

| PVIN, LX                                         | PGND - 0.3 | +20                   | V    |

| PVIN <sup>[1]</sup>                              | PGND - 0.3 | PGND + 16.5           | V    |

| SGND                                             | PGND - 0.1 | PGND + 0.1            | V    |

| FB, COMP, SLOPE, FS                              | PGND - 0.3 | VCC + 0.3             | V    |

| EN                                               | PGND - 0.3 | 5.3                   | V    |

| PG                                               | PGND - 0.3 | PVIN                  | V    |

| VCC                                              | PGND - 0.3 | 6.5                   | V    |

| VCC[1]                                           | PGND - 0.3 | 5.8                   | V    |

| Peak Output Current                              | -          | Overcurrent Protected | Α    |

| LX RMS Output Current                            | -          | 3.4                   | Α    |

| Maximum Junction Temperature                     | -55        | +150                  | °C   |

| Maximum Storage Temperature Range                | -65        | +150                  | °C   |

| Human Body Model (Tested per MIL-PRF-883 3015.7) | -          | 2.5                   | kV   |

| Charged Device Model (Tested per JS-002-2022)    | -          | 1                     | kV   |

| Latch-Up (Tested per JESD78E; Class 2, Level A)  | -          | ±100                  | mA   |

<sup>1.</sup> LET =  $86\text{MeV} \cdot \text{cm}^2/\text{mg}$  at  $125^{\circ}\text{C}$  (T<sub>C</sub>)

#### 3.2 Thermal Information

| Parameter          | Package             | Symbol                         | Conditions       | Typical<br>Value | Unit |

|--------------------|---------------------|--------------------------------|------------------|------------------|------|

| Thermal Resistance | 14 Ld CDFP Package  | θ <sub>JA</sub> [1]            | Junction to air  | 29               | °C/W |

| Thermal Nesistance | 14 Lu ODIT I ackage | θ <sub>JC</sub> <sup>[2]</sup> | Junction to case | 3.5              | °C/W |

<sup>1.</sup>  $\theta_{JA}$  is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features. See TB379. 2.For  $\theta_{JC}$ , the case temperature location is the center of the metallization on the package underside.

## 3.3 Recommended Operating Conditions

| Parameter                            | Minimum    | Maximum                                                    | Unit |

|--------------------------------------|------------|------------------------------------------------------------|------|

| Input Voltage (PVIN)                 | PGND + 3.0 | +18                                                        | V    |

| Output Current                       | 0          | 3                                                          | А    |

| Switching Frequency                  | 300        | 1000                                                       | kHz  |

| External R <sub>SLOPE</sub> Resistor | 25         | 100                                                        | kΩ   |

| Ambient Temperature                  | -55        | +125                                                       | °C   |

| Output Voltage                       | 0.6        | Limited by min on/off timing constraints & f <sub>SW</sub> | V    |

## 3.4 Electrical Specifications

Unless otherwise noted, PVIN = 3V and 18V; PGND = SGND = 0V; LX = Open Circuit; PGOOD is pulled up to PVIN with a 10k resistor;  $I_{OUT}$  = 0A;  $T_J$  =  $T_A$ ,  $r_{DS(ON)}$  is pulse tested. **Boldface limits apply across the operating temperature range**, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s.

| Parameter                                               | Symbol                 | Test Conditions                                         | Temp.<br>(°C)         | Min   | Typ <sup>[1]</sup> | Max   | Unit |  |

|---------------------------------------------------------|------------------------|---------------------------------------------------------|-----------------------|-------|--------------------|-------|------|--|

| Input Power Supply                                      |                        |                                                         |                       |       | l .                |       | 1    |  |

| Rising Undervoltage  .ockout  VPVIN_UVLO                |                        | EN = 2.25V                                              | -55 to<br>+125        | -     | 2.86               | 2.95  | V    |  |

| Falling Undervoltage<br>Lockout                         | VPVIN_UVLO             | EN = 2.25V                                              | -55 to<br>+125        | 2.7   | 2.78               | -     | V    |  |

|                                                         |                        |                                                         | -55                   | 25    | 30                 | 35    |      |  |

|                                                         |                        |                                                         | +25                   | 28    | 35                 | 42    |      |  |

| Operating Supply Current <sup>[2]</sup>                 | I <sub>PVIN_OPER</sub> | PVIN = 18V, EN = 5V, ext. 500kHz, no load               | +125                  | 36    | 50                 | 60    | mA   |  |

| Ourient 1                                               |                        |                                                         | +25C<br>(Post<br>Rad) | 28    | 35.2               | 42    |      |  |

| Stand-by Supply                                         | ı                      | PVIN = 3V, EN = 1V                                      | -55 to<br>+125        | 1.1   | 1.37               | 1.7   | mΛ   |  |

| Current                                                 | I <sub>PVIN</sub> SB   | PVIN =18V, EN = 1V                                      | -55 to<br>+125        | 1.1   | 1.29               | 1.4   | - mA |  |

| Shutdown Supply                                         | ı                      | PVIN = 3V, EN = 0V                                      | -55 to<br>+125        | 5     | 25                 | 40    | _ μΑ |  |

| Current                                                 | I <sub>PVIN</sub> SD   | PVIN = 18V, EN = 0V                                     | -55 to<br>+125        | 50    | 128                | 190   |      |  |

| Output Regulation                                       |                        |                                                         |                       |       |                    |       | •    |  |

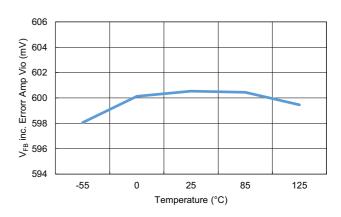

|                                                         | V <sub>FB</sub>        |                                                         | -55                   | 594.5 | 598                | 600.5 | mV   |  |

|                                                         |                        |                                                         | +25                   | 597   | 600                | 603   |      |  |

| Feedback Voltage<br>Accuracy <sup>[2]</sup>             |                        | VFB (including Error Amplifier V <sub>IO</sub> to SGND) | +125                  | 596   | 600                | 603   |      |  |

| Accuracy                                                |                        | COND                                                    | +25<br>(Post<br>Rad)  | 597   | 601                | 603.5 |      |  |

|                                                         |                        |                                                         | -55                   | -20   | 0.492              | 20    |      |  |

|                                                         |                        |                                                         | +25                   | -20   | 0.49               | 20    |      |  |

| FB Leakage Current <sup>[2]</sup>                       | I <sub>FB</sub>        | PVIN = 12V, V <sub>FB</sub> = 0.6V                      | +125                  | -20   | 1.767              | 20    | nA   |  |

| -                                                       | 'ГВ                    |                                                         | +25<br>(Post<br>Rad)  | -20   | 0.49               | 20    |      |  |

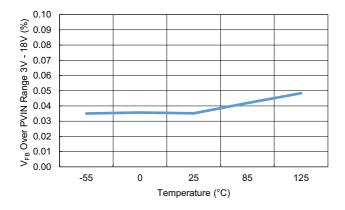

| Output Voltage<br>Tolerance Over Input<br>Voltage Range | LNREG                  | PVIN = 3V, 18V using servo loop                         | -55 to<br>+125        | -0.11 | 0.039              | 0.25  | %    |  |

| Protection Features                                     |                        |                                                         |                       |       |                    |       |      |  |

|                                                         | 1                      | PVIN = 3V                                               | -55 to<br>+125        | 4.3   | 5.3                | 6.1   |      |  |

| Positive Peak Current Limit <sup>[3]</sup>              | I <sub>IPLIMIT1</sub>  | PVIN ≥ 5V                                               | -55 to<br>+125        | 4     | 5                  | 6     | Α    |  |

|                                                         | I <sub>IPLIMIT2</sub>  | PVIN = 18                                               | -55 to<br>+125        | 4.9   | 6.2                | 7.3   |      |  |

Unless otherwise noted, PVIN = 3V and 18V; PGND = SGND = 0V; LX = Open Circuit; PGOOD is pulled up to PVIN with a 10k resistor;  $I_{OUT}$  = 0A;  $T_J$  =  $T_A$ ,  $r_{DS(ON)}$  is pulse tested. Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s. (Cont.)

| Parameter Symbol                                                        |                         | Test Conditions                                                                                                            | Temp.<br>(°C)         | Min  | Typ <sup>[1]</sup> | Max  | Unit |

|-------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------|------|--------------------|------|------|

|                                                                         |                         |                                                                                                                            | -55                   | -5.8 | -4.8               | -3.6 |      |

|                                                                         |                         |                                                                                                                            | +25                   | -5.7 | -4.9               | -3.7 |      |

| Negative Peak Current<br>Limit <sup>[2][3]</sup>                        | -I <sub>IPLIMIT</sub>   | -                                                                                                                          | +125                  | -5.8 | -4.8               | -3.6 | Α    |

| Limitाट्याच्य                                                           | ii Elivii i             |                                                                                                                            | +25<br>(Post<br>Rad)  | -5.7 | -4.7               | -3.7 |      |

| Thermal Shutdown <sup>[4]</sup>                                         | Therm <sub>SD</sub>     | Die Rising Temperature Threshold                                                                                           | -                     | -    | 161                | -    | °C   |

| Thermal Reset <sup>[4]</sup>                                            | Therm <sub>SD</sub>     | Die Falling Temperature Threshold                                                                                          | -                     | -    | 148                | -    | °C   |

| Thermal Shutdown<br>Hysteresis <sup>[4]</sup>                           | Therm <sub>SDHYS</sub>  | -                                                                                                                          | -                     | -    | -                  | 20   | °C   |

| Compensation                                                            |                         |                                                                                                                            |                       |      |                    |      |      |

| Internal Error Amplifier<br>Proportional Voltage<br>Gain <sup>[4]</sup> | A <sub>EAP</sub>        | -                                                                                                                          | +25                   | -    | 12.7               | -    | V/V  |

| Internal Error Amplifier<br>Zero [4]                                    | EA <sub>fz</sub>        | -                                                                                                                          | +25                   | -    | 5.8                | -    | kHz  |

| Internal Error Amplifier<br>Gain-Bandwidth<br>Product <sup>[4]</sup>    | EA <sub>GBP1</sub>      | -                                                                                                                          | +25                   | -    | 33                 | -    | MHz  |

| Internal Error Amplifier                                                | E 4                     | 411-                                                                                                                       | +25                   | 55.3 | 82                 | -    | .ID  |

| DC Gain <sup>[2][4]</sup>                                               | EA <sub>AV1</sub>       | 1Hz                                                                                                                        | +125                  | 58.5 | 82                 | -    | dB   |

|                                                                         |                         |                                                                                                                            | -55                   | 0.93 | 1.057              | 1.18 |      |

| Fustament France                                                        |                         |                                                                                                                            | +25                   | 0.82 | 0.923              | 1.02 |      |

| External Error<br>Amplifier                                             | EA <sub>transcon2</sub> | PVIN = 5V, delta COMP current/delta FB Voltage (10mV)                                                                      | +125                  | 0.68 | 0.768              | 0.87 | mA/V |

| Transconductance <sup>[2]</sup>                                         |                         | voltage (10111v)                                                                                                           | +25C<br>(Post<br>Rad) | 0.82 | 0.926              | 1.02 |      |

| External Error<br>Amplifier DC Gain <sup>[4]</sup>                      | EA <sub>AV2</sub>       | 1Hz                                                                                                                        | +25                   | 66   | 80                 | -    | dB   |

| External Error<br>Amplifier Gain-<br>Bandwidth Product <sup>[4]</sup>   | EA <sub>GBP2</sub>      | -                                                                                                                          | +25                   | 15   | -                  | -    | MHz  |

| Modulator<br>Tranconductance [4]                                        | $G_{M}$                 | -                                                                                                                          | -55 to<br>+125        | -    | 12                 | -    | A/V  |

| Oscillator/Slope Genera                                                 | ator                    |                                                                                                                            |                       | •    |                    |      |      |

| Default Switching<br>Frequency                                          | f <sub>SWd</sub>        | FS = VCC                                                                                                                   | -55 to<br>+125        | 450  | 500                | 550  | kHz  |

| 300kHz Switching<br>Frequency                                           | f <sub>SW3</sub>        | FS = 174k $\Omega$ to GND, V <sub>SLOPE</sub> = 1.2V                                                                       | -55 to<br>+125        | 270  | 305                | 330  | kHz  |

| 500kHz Switching<br>Frequency                                           | f <sub>SW5</sub>        | FS = 100kΩ to GND, $V_{SLOPE}$ = 1.2V                                                                                      | -55 to<br>+125        | 450  | 500                | 550  | kHz  |

| 1000kHz Switching<br>Frequency                                          | f <sub>SW10</sub>       | FS = $42.7k\Omega$ to GND, $V_{SLOPE} = 1.2V$                                                                              | -55 to<br>+125        | 900  | 1000               | 1100 | kHz  |

| SLOPE Pin Current<br>Source                                             | I <sub>SLOPE</sub>      | -                                                                                                                          | -55 to<br>+125        | 10.5 | 12                 | 13.5 | μA   |

| Internal SLOPE Ramp<br>Rate                                             | t <sub>SLOPE</sub>      | (V <sub>COMP</sub> at 80%DC - V <sub>COMP</sub> at 20%DC)/<br>(t <sub>MIN_ON</sub> at80%DC - t <sub>MIN_ON</sub> at 20%DC) | -55 to<br>+125        | 0.1  | 0.13               | 0.16 | V/µs |

| Enable                                                                  |                         | (WIIV_OIV IVIIIV_OIV                                                                                                       |                       |      |                    |      |      |

Unless otherwise noted, PVIN = 3V and 18V; PGND = SGND = 0V; LX = Open Circuit; PGOOD is pulled up to PVIN with a 10k resistor;  $I_{OUT}$  = 0A;  $T_J$  =  $T_A$ ,  $r_{DS(ON)}$  is pulse tested. Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s. (Cont.)

| Parameter Symbol                       |                           | Test Conditions                                                   | Temp.<br>(°C)  | Min   | Typ <sup>[1]</sup> | Max    | Unit |

|----------------------------------------|---------------------------|-------------------------------------------------------------------|----------------|-------|--------------------|--------|------|

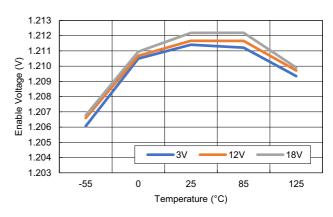

| Rising Enable Voltage<br>Threshold     | EN <sub>VIH</sub>         | Enable Rising to LX Switching                                     | -55 to<br>+125 | 1.18  | 1.21               | 1.3    | ٧    |

| Falling Enable Voltage<br>Threshold    | EN <sub>VIL</sub>         | Enable Falling to LX Stops Switching                              | -55 to<br>+125 | 0.96  | 1                  | 1.06   | ٧    |

| Enable Voltage LX<br>Hysteresis        | EN <sub>VIHhys</sub>      | -                                                                 | -55 to<br>+125 | 20    | 200                | 410    | mV   |

| Standby Enable<br>Voltage              | SB_EN <sub>VIH</sub>      | Enable Rising to VCC Enabled                                      | -55 to<br>+125 | 0.45  | 0.76               | 1      | ٧    |

| Shutdown Enable<br>Voltage             | SB_EN <sub>VIL</sub>      | Enable Falling to VCC Disabled                                    | -55 to<br>+125 | 0.3   | 0.68               | 0.9    | ٧    |

| Enable Hysteresis<br>Voltage           | EN <sub>HYS</sub>         | Enable Rising to VCC Enabled - EN Falling to VCC Disable          | -55 to<br>+125 | 20    | 80                 | 175    | mV   |

| Low Enable Current                     | EN <sub>IIL</sub>         | Enable = 0V                                                       | -55 to<br>+125 | -20   | 0.426              | 20     | nA   |

| High Enable Current                    | EN <sub>IIH</sub>         | Enable = 5V                                                       | -55 to<br>+125 | 1.5   | 2.166              | 2.8    | μA   |

| Enable (EN)<br>Pull-Down Resistance    | R <sub>EN</sub>           | PVIN = 12V                                                        | -55 to<br>+125 | 1.7   | 2.3                | 2.9    | МΩ   |

| vcc                                    |                           |                                                                   |                |       | I.                 | l      |      |

|                                        | VOUT <sub>3V,0mA</sub>    | PVIN = 3V, I <sub>OUT</sub> = 0mA,<br>f <sub>SW</sub> = 500kHz    | -55 to<br>+125 | 2.96  | 2.99               | 3      |      |

| V00 0 to tV / h = 1                    | VOUT <sub>3V,10mA</sub>   | PVIN = 3V, I <sub>OUT</sub> = 10mA,<br>f <sub>SW</sub> = 500kHz   | -55 to<br>+125 | 2.93  | 2.97               | 2.98   | .,   |

| VCC Output Voltage                     | VOUT <sub>5.5V,0mA</sub>  | PVIN = 5.5V, I <sub>OUT</sub> = 0mA,<br>f <sub>SW</sub> = 500kHz  | -55 to<br>+125 | 4.83  | 4.95               | 5      | V    |

|                                        | VOUT <sub>5.5V,10mA</sub> | PVIN = 5.5V, I <sub>OUT</sub> = 10mA,<br>f <sub>SW</sub> = 500kHz | -55 to<br>+125 | 4.82  | 4.94               | 5      |      |

| VCC Foldback Current                   | l <sub>cc_sc</sub>        | PVIN = 18V, V <sub>CC</sub> = 0V, EN = 1.6V                       | -55 to<br>+125 | -     | 72                 | -      | mA   |

| VCC Overcurrent Limit                  | Icc_cl                    | PVIN = 18V, V <sub>CC</sub> = 4.3V, EN = 1.6V                     | -55 to<br>+125 | -     | 98                 | -      | mA   |

| Power-Good                             |                           |                                                                   |                |       | l                  | I.     |      |

| Output Overvoltage<br>Error Threshold  | OVPG                      | PVIN = 5V, FB as a % of V <sub>REF</sub>                          | -55 to<br>+125 | 106   | 106.8              | 107.5  | %    |

| Output Undervoltage<br>Error Threshold | UVPG                      | PVIN = 5V, FB as a % of V <sub>REF</sub>                          | -55 to<br>+125 | 92.25 | 93.2               | 94.25  | %    |

| Output Overvoltage<br>Fault            | OVflt                     | PVIN = 5V, FB as a % of V <sub>REF</sub>                          | -55 to<br>+125 | 113.5 | 115                | 117.25 | %    |

| Output Undervoltage<br>Fault           | UVflt                     | PVIN = 5V, FB as a % of V <sub>REF</sub>                          | -55 to<br>+125 | 82.5  | 85                 | 87     | %    |

| Low Current Drive                      | PG_I <sub>OL</sub>        | PVIN = 3V, PG = 0.4V, EN = 0V                                     | -55 to<br>+125 | 11    | 22                 | 35     | mA   |

| Low V <sub>OUT</sub>                   | PG_V <sub>OL</sub>        | PVIN = 18V, FB = 0V, EN = 0V, IPG = 10mA                          | -55 to<br>+125 | -     | 0.15               | 0.27   | ٧    |

| Leakage                                | I <sub>LKGPG</sub>        | PVIN = PG = 18V                                                   | -55 to<br>+125 | -     | -                  | 1      | μΑ   |

Unless otherwise noted, PVIN = 3V and 18V; PGND = SGND = 0V; LX = Open Circuit; PGOOD is pulled up to PVIN with a 10k resistor;  $I_{OUT}$  = 0A;  $T_{J}$  =  $T_{A}$ ,  $r_{DS(ON)}$  is pulse tested. **Boldface limits apply across the operating temperature range, -55°C to +125°C by production** testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s. (Cont.)

| Parameter                             | Symbol                   | Test Conditions                                       | Temp.<br>(°C)  | Min | Typ <sup>[1]</sup> | Max  | Unit      |

|---------------------------------------|--------------------------|-------------------------------------------------------|----------------|-----|--------------------|------|-----------|

|                                       |                          | PVIN = 5.5V From EN edge to PG high, 300kHz           | -55 to<br>+125 | 8   | 12.5               | 16.5 | ms        |

| Power Good Rising<br>Delay            | <sup>t</sup> sspgdlyr    | PVIN = 5.5V From EN edge to PG high, 500kHz           | -55 to<br>+125 | 6.6 | 7.4                | 8.4  | ms        |

|                                       |                          | PVIN = 5.5V From EN high to PG high,<br>1000kHz       | -55 to<br>+125 | 3.7 | 4                  | 4.5  | ms        |

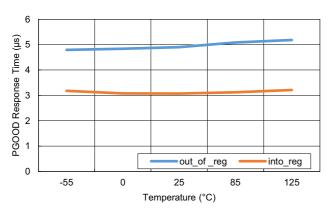

| Rising Edge Delay                     | t <sub>PGdlyr</sub>      | Return to regulation to PG response                   | -55 to<br>+125 | 1.9 | 3                  | 4.2  | μs        |

| Falling Edge Delay                    | t <sub>PGdlyf</sub>      | Out of regulation to PG response                      | -55 to<br>+125 | 3.5 | 4.3                | 5    | μs        |

| Phase                                 |                          |                                                       |                |     |                    |      |           |

| Minimum LX<br>On-Time <sup>[5]</sup>  | t <sub>MIN_ON</sub>      | PVIN = 12V, Forced Min On-Time by COMP bias, No Load  | -55 to<br>+125 | -   | 230                | 260  | ns        |

| Minimum LX<br>Off-Time <sup>[5]</sup> | t <sub>MIN_OFF</sub>     | PVIN = 12V, Forced Min Off-Time by COMP bias, No Load | -55 to<br>+125 | -   | 171                | 210  | ns        |

|                                       | -55UPR <sub>DSON_3</sub> | PVIN = 3.0V, I <sub>OUT</sub> = 200mA                 | -55            | 62  | 71                 | 80   | - mΩ      |

|                                       | -55UPR <sub>DSON_5</sub> | PVIN = 5.5V, I <sub>OUT</sub> = 200mA                 | -55            | 52  | 61                 | 68   |           |

|                                       | 25UPR <sub>DSON_3</sub>  | PVIN = 3.0V, I <sub>OUT</sub> = 200mA                 | +25            | 83  | 93                 | 105  |           |

| CDFP Upper FET                        | 25UPR <sub>DSON_5</sub>  | PVIN = 5.5V, I <sub>OUT</sub> = 200mA                 | +23            | 69  | 78                 | 89   |           |

| r <sub>DS(ON)</sub> <sup>[2][3]</sup> | 125UPR <sub>DSON_3</sub> | PVIN = 3.0V, I <sub>OUT</sub> = 200mA                 | +125           | 115 | 127                | 140  |           |

|                                       | 125UPR <sub>DSON_5</sub> | PVIN = 5.5V, I <sub>OUT</sub> = 200mA                 |                | 95  | 106                | 115  |           |

|                                       | 25UPR <sub>DSON_3</sub>  | PVIN = 3.0V, I <sub>OUT</sub> = 200mA                 | +25            | 83  | 102                | 117  |           |

|                                       | 25UPR <sub>DSON_5</sub>  | PVIN = 5.5V, I <sub>OUT</sub> = 200mA                 | (Post<br>Rad)  | 69  | 86                 | 102  | mΩ        |

|                                       | -55LWR <sub>DSON_3</sub> | PVIN = 3.0V, I <sub>OUT</sub> = 200mA                 | -55            | 28  | 34                 | 39   | -<br>- mΩ |

|                                       | -55LWR <sub>DSON_5</sub> | PVIN = 5.5V, I <sub>OUT</sub> = 200mA                 | -55            | 24  | 31                 | 37   |           |

|                                       | 25LWR <sub>DSON_3</sub>  | PVIN = 3.0V, I <sub>OUT</sub> = 200mA                 | +25            | 41  | 49                 | 55   |           |

| CDFP Lower FET                        | 25LWR <sub>DSON_5</sub>  | PVIN = 5.5V, I <sub>OUT</sub> = 200mA                 | +25            | 36  | 44                 | 50   |           |

| r <sub>DS(ON)</sub> <sup>[2][3]</sup> | 125LWR <sub>DSON_3</sub> | PVIN = 3.0V, I <sub>OUT</sub> = 200mA                 | +125           | 62  | 72                 | 77   |           |

|                                       | 125LWR <sub>DSON_5</sub> | PVIN = 5.5V, I <sub>OUT</sub> = 200mA                 | +125           | 56  | 64                 | 69   |           |

|                                       | 25LWR <sub>DSON_3</sub>  | PVIN = 3.0V, I <sub>OUT</sub> = 200mA                 | +25            | 41  | 48                 | 55   |           |

|                                       | 25LWR <sub>DSON_5</sub>  | PVIN = 5.5V, I <sub>OUT</sub> = 200mA                 | (Post<br>Rad)  | 36  | 42                 | 50   | mΩ        |

| DIE Upper FET                         | 25DUPR <sub>DSON_3</sub> | PVIN = 3.0V, I <sub>OUT</sub> = 200mA                 |                | 70  | 83                 | 96   | mΩ        |

| r <sub>DS(ON)</sub> [3]               | 25DUPR <sub>DSON_5</sub> | PVIN = 5.5V, I <sub>OUT</sub> = 200mA                 | 105            | 55  | 67                 | 80   |           |

| DIE Lower FET                         | 25DLWR <sub>DSON_3</sub> | PVIN = 3.0V, I <sub>OUT</sub> = 200mA                 | +25            | 27  | 33                 | 38   | - mΩ      |

| $r_{DS(ON)}^{[3]}$                    | 25DLWR <sub>DSON_5</sub> | PVIN = 5.5V, I <sub>OUT</sub> = 200mA                 |                | 23  | 28                 | 34   |           |

- 1. Typical values are at 25°C and are not guaranteed.

- 2. Typical values shown are at stated temperature and are not guaranteed.

- 3. Parameter tested in a Test Mode not available to user.

- 4. Limits established by characterization and/or design analysis and are not production tested.

- 5. The operating envelope may be reduced by Minimum On-Time and Minimum Off Time constraints.

## 3.5 Operation Burn-In Deltas

Unless otherwise noted, PVIN = 12V and 18V; PGND = SGND = 0V; LX = Open Circuit; PGOOD is pulled up to PVIN with a 10k resistor;  $I_{OUT} = 0A$ ;  $T_{J} = T_{A} = 25$ °C.

| Parameter <sup>[1]</sup>       | Symbol                    | Test Conditions                                                    | Min    | Max    | Unit |

|--------------------------------|---------------------------|--------------------------------------------------------------------|--------|--------|------|

| Operating Supply Current       | I <sub>PVIN_OPER</sub>    | PVIN = 18V, EN = 5V, 500kHz, no load                               | -2     | +2     | mA   |

| Shutdown Supply Current        | I <sub>PVIN_SD</sub>      | PVIN = 18V, EN = 0V                                                | -15    | +15    | μΑ   |

| Reference Voltage Tolerance    | V <sub>FB</sub>           | PVIN = 4.5V, $V_{FB}$ (including Error Amplifier $V_{IO}$ to SGND) | -2.35  | +2.35  | mV   |

| Positive Peak Current Limit    | I <sub>IPLIMIT1</sub>     | PVIN = 12                                                          | -0.5   | +0.5   | Α    |

| 500kHz Switching Frequency     | f <sub>SWd</sub>          | PVIN = 12, $V_{SLOPE}$ = 1.2V,<br>FS = 100kΩ to GND                | -5     | +5     | kHz  |

| Default Switching Frequency    | f <sub>SW5</sub>          | PVIN = 12, FS = V <sub>CC</sub>                                    | -5     | +5     | kHz  |

| V <sub>CC</sub> Output Voltage | VOUT <sub>5.5V,10mA</sub> | PVIN = 5.5V, I <sub>OUT</sub> = 10mA                               | -0.015 | +0.015 | V    |

| SLOPE Pin Current Source       | I <sub>SLOPE</sub>        | PVIN = 12                                                          | -0.2   | +0.2   | μΑ   |

<sup>1.</sup> This data table shows the delta limits of critical parameters after 2000hrs of HTOL at 135°C.

# 4. Typical Performance Curves

T<sub>A</sub> = Room Ambient, unless otherwise noted

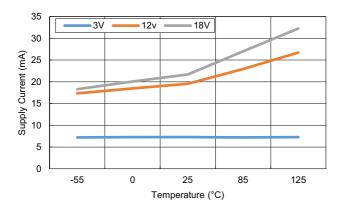

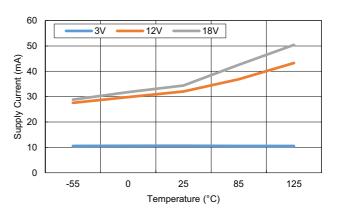

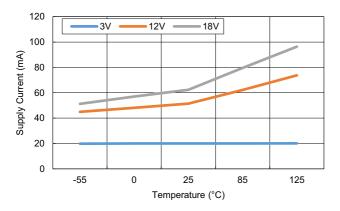

Figure 5. 300kHz - Supply Current vs Temperature

Figure 6. 500kHz - Supply Current vs Temperature

Figure 7. 1000kHz Supply Current vs Temperature

Figure 8. Enable Voltage vs Temperature

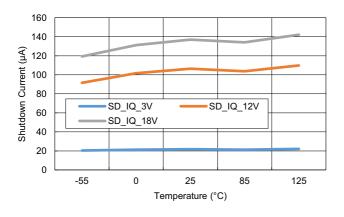

Figure 9. Shutdown Current vs Temperature

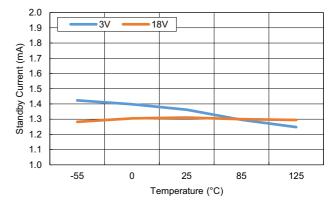

Figure 10. Standby Current vs Temperature

T<sub>A</sub> = Room Ambient, unless otherwise noted (Cont.)

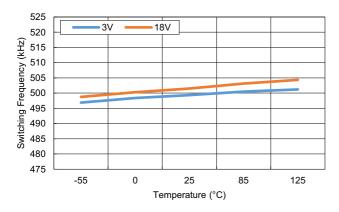

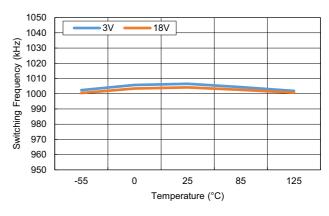

Figure 11. Internal 500kHz Switching Frequency vs

Temperature

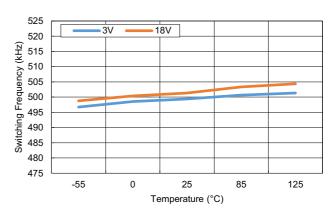

Figure 12. 100kΩ External 500kHz vs Temperature

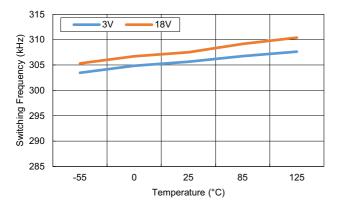

Figure 13. 174k $\Omega$  External 300kHz vs Temperature

Figure 14. 42.7kΩ External 1000kHz vs Temperature

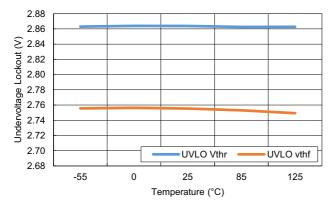

Figure 15. Undervoltage Lockout vs Temperature

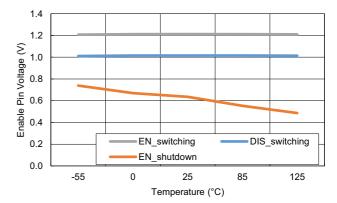

Figure 16. Enable Voltage Threshold vs Temperature

T<sub>A</sub> = Room Ambient, unless otherwise noted (Cont.)

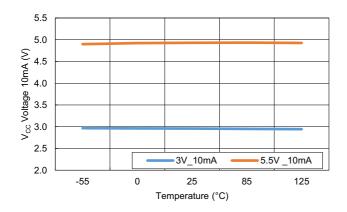

Figure 17.  $V_{CC}$  Voltage vs Temperature

Figure 18. Minimum On-Time/Off-Time vs Temperature

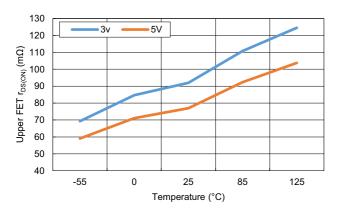

Figure 19. Upper FET  $r_{DS(ON)}$  vs Temperature

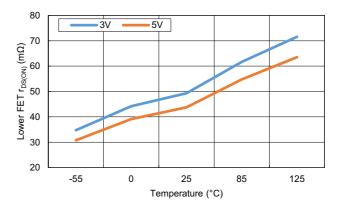

Figure 20. Lower FET  $r_{DS(ON)}$  vs Temperature

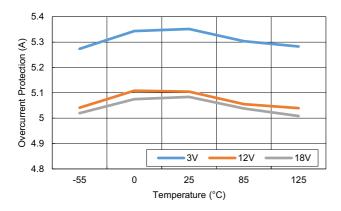

Figure 21. Overcurrent Protection vs Temperature

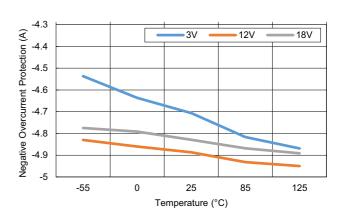

Figure 22. Negative Current Protection vs Temperature

T<sub>A</sub> = Room Ambient, unless otherwise noted (Cont.)

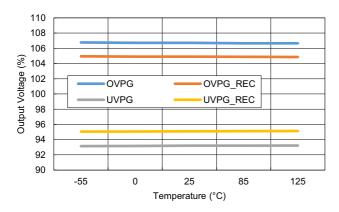

Figure 23. PGOOD Over/Undervoltage Threshold vs

Temperature

Figure 24. FB Voltage vs Temperature

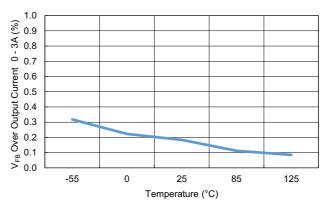

Figure 25. V<sub>FB</sub> Over PVIN Range vs Temperature

Figure 26. V<sub>FB</sub> Over Output Current vs Temperature

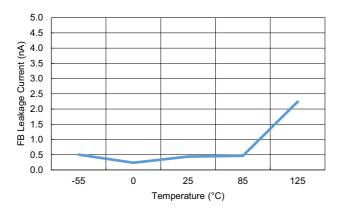

Figure 27. FB Leakage Current vs Temperature

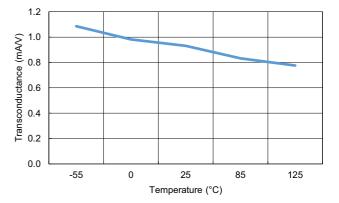

Figure 28. External Compensation Loop Error Amp

Transconductance vs Temperature

T<sub>A</sub> = Room Ambient, unless otherwise noted (Cont.)

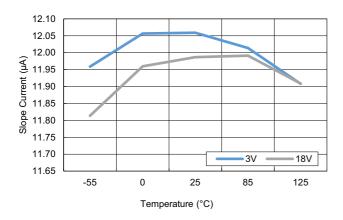

Figure 29. SLOPE Current vs Temperature

Figure 30. Internal Slope Ramp Rate vs Temperature

Figure 31. PGOOD Response Time vs Temperature

Figure 32. EN to PG Time vs Switching Frequency

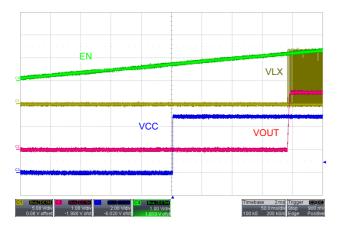

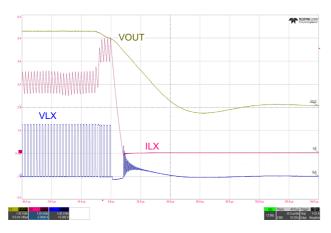

Figure 33. ENABLE to VCC to LX and VOUT Turn-On

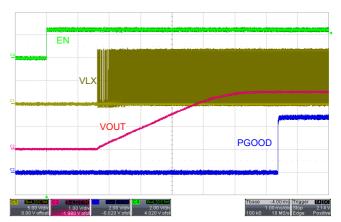

Figure 34. ENABLE to LX and VOUT to PGOOD Turn-On 500kHz

$T_A$  = Room Ambient, unless otherwise noted (Cont.)

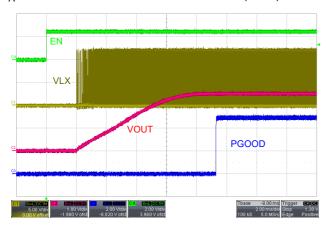

Figure 35. ENABLE to LX and VOUT to PGOOD Turn-On 300kHz

Figure 36. ENABLE to LX and VOUT to PGOOD Turn-On 1000kHz

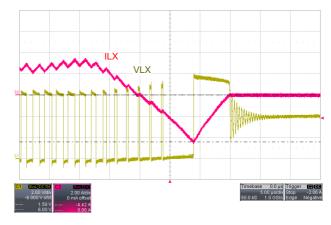

Figure 37. Overcurrent Protection Function

Figure 38. Negative Overcurrent Protection Function

Figure 39. Turn-On Into Overcurrent,  $R_L = 0.44\Omega$

Figure 40. Overcurrent Protection to Turn-On

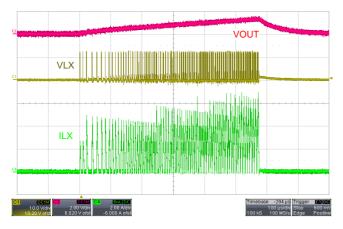

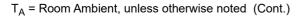

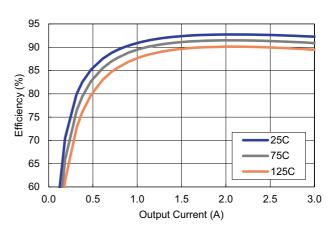

Figure 41. Efficiency  $3.3V_{IN}$ ,  $1.2V_{OUT}$ , 1MHz vs Case Temp

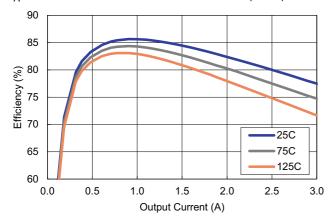

Figure 42. Efficiency 5V<sub>IN</sub>, 2.5V<sub>OUT</sub>, 1MHz vs Case Temp

Figure 43. Efficiency 12V<sub>IN</sub>, 3.3V<sub>OUT</sub>, 500kHz vs Case

Figure 44. Efficiency  $12V_{IN}$ ,  $5V_{OUT}$ , 500kHz vs Case Temp

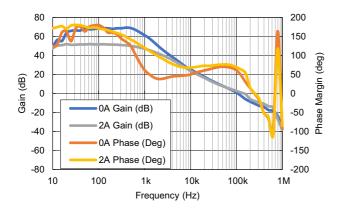

Figure 45. Ext Comp Gain/Phase BODE Plot,  $3.3V_{IN},\,1.0V_{OUT},\,1MHz,\,R_{SLOPE}=34.8k\Omega,\,R_{COMP}=14k\Omega,\\ C_{COMP}=1200pF,\,L_{OUT}=0.82\mu H,\,C_{OUT}=172\mu F$

Figure 46. Int Comp Gain/Phase BODE Plot,  $3.3V_{IN},\,1.0V_{OUT},\,1MHz,\,L_{OUT}=0.82\mu H,\,C_{OUT}=172\mu F$

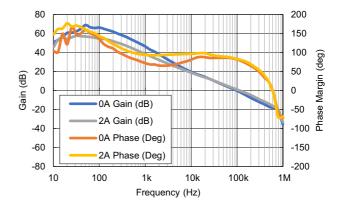

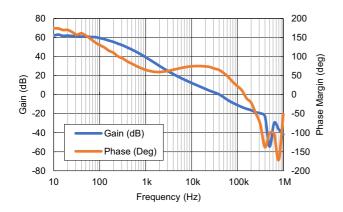

T<sub>A</sub> = Room Ambient, unless otherwise noted (Cont.)

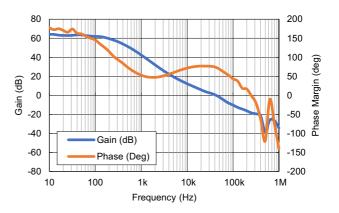

Figure 47. External Comp Gain/Phase BODE Plot,  $12V_{\text{IN}},\,3.3V_{\text{OUT}},\,500\text{kHz},\,I_{\text{OUT}}=1.5\text{A}$   $R_{\text{SLOPE}}=44.2\text{k}\Omega,\,R_{\text{COMP}}=14\text{k}\Omega,\,C_{\text{COMP}}=3900\text{pF},$   $L_{\text{OUT}}=4.7\mu\text{H},\,C_{\text{OUT}}=144\mu\text{F}$

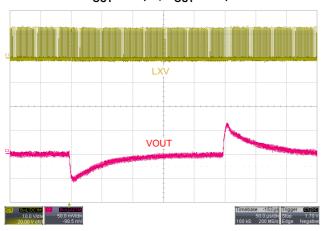

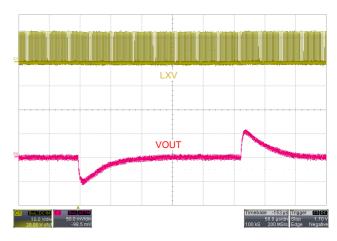

Figure 49. 12VIN,  $3.3V_{OUT}$  500kHz, 2A Load Transient  $R_{SLOPE}$  = 44.2k $\Omega$ ,  $R_{COMP}$  = 14k $\Omega$ ,  $C_{COMP}$  = 3900pF,  $L_{OUT}$  = 4.7 $\mu$ H,  $C_{OUT}$  = 144 $\mu$ F

Figure 48. Internal Comp Gain/Phase BODE Plot,  $12V_{IN}$ ,  $3.3V_{OUT}$ , 500kHz,  $I_{OUT}$  = 1.5A  $L_{OUT}$  = 4.7 $\mu$ H,  $C_{OUT}$  = 144 $\mu$ F

Figure 50. 12VIN, 3.3V $_{\rm OUT}$ , 500kHz, 2A Load Transient (Internal Compensation),  $L_{\rm OUT} = 4.7 \mu H, \, C_{\rm OUT} = 144 \mu F$

### 5. Theory of Operation

### 5.1 Description of Features

The ISL73007SEH is a Radiation Hardened by design buck converter using constant frequency peak current mode control architecture for fast loop transient response with a 3V to 18V input voltage regulating down to a minimum 0.6V output voltage adjusted using external resistors. The ISL73007SEH is capable of >90% efficiency from 1A to the 3A maximum output rated current.

The device operates at a default 500kHz switching frequency and can be resistor adjusted to operate from 300kHz to 1MHz. Implement a wider range of duty cycle operating points at the low end of the switching frequency range. At the high end of the switching frequency range, using smaller inductors and capacitors in the output filter results in a smaller implementation footprint. The  $V_{IN}$  to  $V_{OUT}$  step-down ratio is restricted by the minimum on and off times, making 1MHz a practical maximum switching frequency. The ISL73007SEH can be configured such that the switching frequency, the loop, and slope compensations can either be defaulted to internal attributes by tying pins to the VCC or be adjusted externally with passive components to meet particular design requirements and performance optimization. These features can be mixed externally or internally when implemented. This flexibility allows for a basic functional configuration with a minimal BOM or an optimized configuration for the POL task.

### 5.2 Output Voltage Setting

Use Equation 1 to calculate the required regulated output voltage. For greater voltage accuracy, Renesas recommends using 0.1% feedback resistors.

(EQ. 1)

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_2}{R_1}\right)$$

- V<sub>OUT</sub> is the required regulated output voltage.

- V<sub>REF</sub> is the internal reference voltage on the VFB+ pin, which is 0.6V (typical).

- R<sub>1</sub> is the bottom resistor in the feedback divider.

- R<sub>2</sub> is the top resistor in the feedback divider.

### 5.3 Internal Configuration Summary

The ISL73007SEH switching frequency, loop compensation, and slope compensation can be configured entirely internally or partially internally with any combination of the three adjustable attributes. The corresponding FS, COMP, and SLOPE pins are connected to VCC to configure each of these internally. Tying FS to VCC invokes the default switching frequency of 500kHz. Tying COMP to VCC configures an internal compensation optimized for <2% transient response for the 1.5A current step.

Internal compensation has the additional benefit of significantly reducing Single Event Transients (SET) compared to external compensation. Tying SLOPE to VCC selects the internal slope compensation with 250mV/T slew rate  $(T = 1/f_{SW})$ .

### 5.4 External Configuration Summary

The ISL73007SEH allows for external configuration of each of the switching frequency, loop compensation, and slope compensation attributes. The switching frequency is externally set by connecting a resistor from the FS ( $R_{FS}$ ) pin to ground. Renesas recommends selecting a switching frequency between 300kHz (174k $\Omega$ ) to 1000kHz (42.7k $\Omega$ ). The resulting frequency is within 10% of the nominal targeted frequency.

To program the external loop compensation, connect a Type II compensation network between the COMP pin and the neighboring SGND pin.

Select the external slope compensation by tying a resistor from the SLOPE pin to ground. The SLOPE pin forces  $12\mu\text{A}$  of current into the  $R_{SLOPE}$  resistor ( $25k\Omega \le R_{SLOPE} \le 100k\Omega$ ), which sets the voltage reference for the

internal slope. A  $100k\Omega$  resistor sets a maximum 250mV/T compensation slew rate, while a  $25k\Omega$  resistor sets a minimum 62.5mV/T slew rate.

### 5.5 Frequency Selection

The ISL73007SEH has a default 500kHz internal clock when the FS pin is tied to VCC. The user can program the switching frequency from 300kHz to 1MHz with a resistor ( $R_{FS}$ ) from the FS pin to GND. Table 1 shows the resulting nominal switching frequency for the indicated FS to GND resistance used in production testing.

**Table 1. Resulting Nominal Switching Frequency**

| FS to GND Resistor = 42.7kΩ   | FS to GND Resistor = 100kΩ   | FS to GND Resistor = 174kΩ   |

|-------------------------------|------------------------------|------------------------------|

| Switching Frequency = 1000kHz | Switching Frequency = 500kHz | Switching Frequency = 300kHz |

The oscillator circuitry is SET hardened using a combination of redundant timing and reset paths and reset voter signals. Use Equation 2 to find the R<sub>ES</sub> resistor for the required switching frequency.

(EQ. 2)

$$R_{FS}[k\Omega] = \frac{57356}{Fsw(kHz)} - 14.53$$

### 5.6 Time Constraints on DC/DC Voltage Conversion

The ISL73007SEH can operate across wide ranges of both input and output voltages; however, the step-down conversion has to adhere to the minimum off and minimum on timing requirements. Determine the down conversion suitability by comparing the  $t_{ON}$  and  $t_{OFF}$  specifications to the duty cycle high time and low time, respectively, for the intended switching frequency and duty cycle. The timing constraints mostly impact extremely high or low-duty cycle conversions where the minimum off and on times are infringed up. Lowering the switching frequency or changing PVIN are the simple methods to alleviate minimum on-time and off-time concerns.

#### 5.7 Overcurrent Protection

Two levels of overcurrent protection (OCP) are provided for sourcing output current conditions. An accurate current-sensing pilot device parallel to the upper MOSFET is used for the peak current mode control signal and overcurrent protection. The ISL73007SEH implements cycle-by-cycle peak current limiting, terminating the upper FET on pulse when the FET current reaches the OCP threshold. An OCP fault is triggered if the OCP threshold is exceeded in four of the eight preceding switching periods. On the 4th current peak above the OCP threshold, the upper FET on pulse terminates, the lower FET turns on until the switching cycle is complete, then the device enters the fault state. When entering the fault state, LX output is forced to a Hi-Z state and the output is pulled low by the output loading. When the device attempts to restart, if the OCP occurs again, we go through another hiccup time and repeat until the OCP is not seen during soft-start. When the overcurrent condition goes away, the output soft starts into a regulated output voltage. The typical sourcing OCP threshold is ~5A, ~1.7x the rated output current of 3A, providing headroom for the peak ripple current. Be mindful during inductor selection, as an excessive ripple current lowers the DC output current capability due to OCP.

During the soft-start period, there is an additional level of overcurrent protection of a single instance at ~6A to protect against shorted or otherwise damaged loads. When invoked, this fault goes into hiccup restart cycling until a successful restart occurs.

### 5.8 Negative Overcurrent Protection (NOCP)

Negative overcurrent protection (NOCP) is provided for sinking output current conditions. If an external source drives current into the regulator output, the controller attempts to regulate the output voltage by reversing its inductor current to absorb the externally sourced current. If the external source is low-impedance, it might reverse the current to an unacceptable level, and the controller initiates its negative overcurrent limit protection. The negative overcurrent protection is realized by monitoring the current through the lower FET. When the valley point of the inductor current reaches the negative current limit of typically -4.8A, the NOCP fault is declared, and the LX

out goes into a Hi-Z state. The IC enters into a hiccup mode to restart. There is no valley current counter on the NOCP function.

#### 5.9 Power Good

Power-Good (PG) is the output of a window comparator that continuously monitors the buck regulator output voltage. The PG output is actively held low when EN is low and during the buck regulator soft-start period. After soft-start completes, the PG pin becomes high impedance as long as the output voltage is in nominal regulation of the output voltage. When VFB is typically beyond ±6% of the nominal regulation voltage for ~5µs, the device open drain output pulls the PG output low. Add an external resistor from PG to a maximum of the PVIN voltage for PG signaling purposes.

#### 5.10 UVLO, Enable, Soft-start, Disable, and Soft-Stop

The regulator remains in shutdown mode until PVIN rises above the Undervoltage Lockout (UVLO) threshold of ~2.86V.

The ISL73007SEH Enable pin allows for three states of operation:

- In Shutdown Mode, the ISL73007SEH is disabled and draws a typical 105μA from PVIN. A transition to this shutdown state occurs when EN is below the Shutdown Enable Voltage.

- In Standby Mode, EN is above the Standby Enable Voltage and below the Enable Voltage Threshold. The VCC LDO is on, but switching is disabled.

- When EN is above the Enable Voltage Threshold, normal switching operation and soft-start begin.

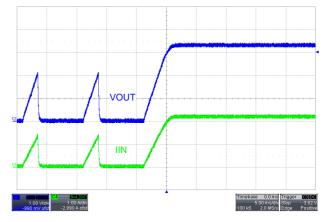

During soft-start, the ISL73007SEH monitors for overvoltage (OV) and over-temperature (OT) faults and remains idle if either fault is active. The soft-start time is dependent on the operating switching frequency during startup (see Figure 32). There is a delay from enable active to LX activity during which the ISL73007SEH internal circuitry is biased. This delay time is frequency dependent, typically 2ms for 300kHz and 1.3ms for 1MHz (see Figure 34 and Figure 35).

The ISL73007SEH can seamlessly start into a pre-biased output, provided the pre-bias voltage is below the set regulation voltage. At the completion of sot-start the FB is monitored against VREF. If the pre-biased output exceeds the regulation set point, the ISL73007SEH does not initiate LX switching but turns on the lower FET at the end of the SS PGOOD time, pulling the output down. The lower FET stays on until VOUT is pulled down to the regulation point or the NOC point is hit. If the NOC point is hit, the part hiccups and repeats the start-up sequence until regulation can be achieved.

#### 5.11 Thermal Protection

The device has integrated thermal protection. When the internal temperature reaches a typical value of +161°C, the regulator stops switching. After the internal temperature falls below a typical value of +148°C, the device resumes operation through soft-start. For continuous operation, do not exceed the +150°C junction temperature rating.

### 5.12 PWM Control and Compensation

The ISL73007SEH employs constant frequency peak current-mode pulse-width modulation (PWM) control for faster transient response and pulse-by-pulse current limiting. The current loop consists of the current-sensing circuit, slope compensation ramp, and PWM comparator.

Any regulator design starting point is knowing the operating conditions and design goals. These would include the input and output voltages, the switching frequency, the maximum transient current step, and the maximum transient output voltage tolerance. The following compensation equations guide completing an external slope and loop control compensation design. Switching frequency selection is discussed in Frequency Selection.

### 5.13 Slope Compensation

The ISL73007SEH offers user-adjustable slope compensation to allow for optimization of power supply performance and stability across the entire PWM duty-cycle range. Slope compensation is a technique in which the current feedback signal is modified by adding slope, that is, a linearly increasing voltage over time. Set the external slope compensation ramp with a resistor (R<sub>SLOPE</sub>) from the SLOPE pin to ground.

For applications with a maximum duty cycle of less than 50%, slope compensation can improve noise immunity, particularly at lighter loads. For applications with a greater than 50% duty cycle, slope compensation is needed to prevent instability, seen as a sub-harmonic oscillation of the switching LX node. The minimum slope compensation typically required is shown in Equation 3.

(EQ. 3) Min Slope Compensation =

$$\frac{-V_{OUT}}{2 \times L_{OUT}}$$

### 5.14 External Configuration Application Implementation Equations

This section guides the design for slope compensation, loop compensation and bandwidth, and load transient response. Use Equation 4 to set the inductor downslope.

(EQ. 4)

$$S_L\left[\frac{A}{\mu s}\right] = \frac{V_{OUT}[V]}{L[\mu H]}$$

The compensation slope is:

$$\text{(EQ. 5)} \qquad \text{S}_{COMP} \bigg[ \frac{A}{\mu s} \bigg] = \ 1.62 \bigg( \frac{R_{SLOPE}[k\Omega]}{R_{FS}[k\Omega]} \bigg)$$

To increase noise immunity and account for inductor tolerances, Renesas recommends using  $S_L = S_{COMP}$  (deadbeat control) so:

(EQ. 6)

$$R_{SLOPE}[k\Omega] = 0.62R_{FS}[k\Omega] \frac{V_{OUT}[V]}{L[\mu H]}$$

Due to headroom issues,  $R_{SLOPE}$  value must be within  $25k\Omega \le R_{SLOPE} \le 100k\Omega$ .

Internal slope compensation is set to maximum slope compensation or:

(EQ. 7)

$$S_{COMP}\left[\frac{A}{\mu s}\right] = \frac{162}{R_{ES}[k\Omega]}$$

The external  $R_{COMP}$  value is set by the transient response requirement on the output voltage, k, calculated using Equation 8, and the load step requirement.

(EQ. 8)

$$k = \frac{\Delta V_{OUT}}{V_{OUT}}$$

The calculation also depends on external error amp transconductance ( $g_m = 0.923 \text{mA/V}$ ) and modulator transconductance ( $G_M = 12 \text{A/V}$ , which means 250mV voltage step at COMP node causes 3A output current step). Calculate external  $R_{\text{COMP}}$  using Equation 9.

(EQ. 9)

$$R_{COMP} = \frac{\Delta I_{OUT}}{kV_{REF}g_mG_M}$$

Internal compensation is set in such a way as to ensure  $\pm 2\%$  V<sub>OUT</sub> transient response for  $\pm 1.5A$  load current step.

The external C<sub>COMP</sub> defines compensator zero frequency, f<sub>z</sub>:

(EQ. 10)

$$f_z = \frac{1}{2\pi R_{COMP} C_{COMP}}$$

Unity gain frequency,  $f_t$ , is typically recommended to target  $f_{SW}/10$ . Set  $f_z$  to  $f_t/10$  to maximize phase margin.  $f_z$  impacts transient response recovery time. Reduce this time by increasing  $f_z$  (at the expense of the phase margin). In general, zero frequency should not exceed  $f_t/3$  (12.7deg loss of phase margin).

After  $R_{COMP}$  is determined, use Equation 11 to calculate the output capacitance, where  $V_{REF} = 0.6V$ .

$$\textbf{(EQ. 11)} \quad \text{C}_{OUT\_MIN} = \frac{\text{V}_{REF} g_m G_M R_{COMP}}{2\pi f_t V_{OUT}}$$

Equation 11 does not guarantee that transient response is met in all cases. The main reason is the nonlinear nature of the switching regulator. To derive equations, approximate the modulator with a simple (and linear)  $G_M$  stage, which means any fast dV/dt at the input of  $G_M$  produces equally fast dI/dt at the output. Because the output inductor (L) limits dI/dt (dI/dt = V/L), in some cases (typically extremely low D or extremely large D), the current slew rate dI/dt = V/L might get limited by V/L in which case transient response is going to be larger than expected. In those cases, reduce L to increase dI/dt or increase  $C_{OLIT}$  to slow down dV/dt at the  $G_M$  input.

In the case of internal compensation (set for  $\pm 2\%$  VOUT transient response with  $\pm 1.5A$  load current step), calculate C<sub>OUT MIN</sub> using Equation 12:

(EQ. 12)

$$C_{OUT\_MIN} = \frac{V_{REF}A_{EAP}G_{M}}{2\pi f_{t}V_{OUT}}$$

Equations are derived for ideal  $C_{OUT}$ . Treat MLCCs as ideal capacitors because of small parasitic components (ESR and ESL). In cases where they cannot be used, carefully consider the ESR value. In the case of extremely fast transients (1A/ns for microprocessors), voltage drop (ESR x dI) appears extremely quickly, and the regulation loop cannot react that fast. In those cases, increase  $C_{OUT}$ . Transient response effectively has two components (ESR and  $C_{OUT}$ ). The solution is to reduce  $C_{OUT}$  transient by the ESR x dI product value. For example, if 2% transient is required and ESR x dI causes 0.5% transient response, use 1.5% transient to determine the external  $R_{COMP}$ .

Regarding loop stability, ESR zero must be canceled by a pole created with C<sub>POLE</sub> such that:

(EQ. 13)

$$ESR \times C_{OUT} = R_{COMP}C_{POLE}$$

The temperature coefficient of the ESR can be significant and cause difficulty with this. Careful evaluation for wide temperature range operations is needed. Consider a combination of Tantalum and MLCC capacitors to achieve high total capacitance with lower ESR.

## 6. Typical Application

### 6.1 Typical Application Schematic

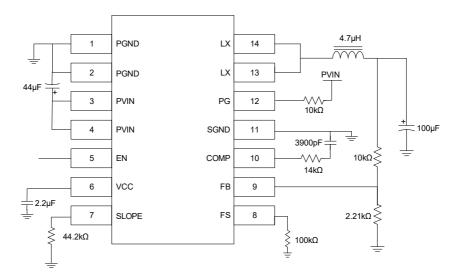

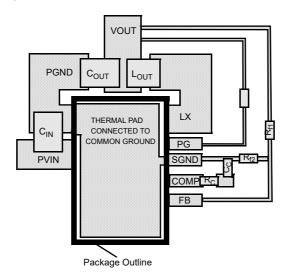

This section guides the design and component selection for a typical buck converter application using the ISL73007. A design calculator is available for download to support designers in component selection. The typical application schematic for an ISL73007 design using external compensation configuration is shown in Figure 51.

Figure 51. External Compensation Application Diagram for 12V to 3.3V, 500kHz

#### 6.2 Design Requirements

Table 2 lists the design requirements for an example application using ISL73007 with external compensation configuration

| Parameter                          | Min  | Тур | Max | Units |

|------------------------------------|------|-----|-----|-------|

| Input Voltage                      | 10.8 | 12  | 18  | V     |

| Output Voltage                     | -    | 3.3 | -   | А     |

| Output Current                     | 0    | -   | 3   | Α     |

| Output Voltage Transient Tolerance | -    | -   | 2   | %     |

| Output Current Load Step           | -    | -   | 2   | А     |

| Switching Frequency                | -    | 500 | -   | kHz   |

**Table 2. Design Requirements**

### 6.3 Set Output Voltage

The output voltage regulation point is set using the feedback resistor divider. Select an upper FB resistor (R2) value of  $10k\Omega$ . Rearrange Equation 1 to calculate the lower FB resistor (R1) value based on the required output voltage of 3.3V.

(EQ. 14)

$$R_1 = \frac{R_2}{\frac{V_{OUT}}{V_{REF}} - 1}$$

$$R_1 = \frac{10k\Omega}{\frac{3.3V}{0.6V} - 1} = 2.22k\Omega$$

Select  $2.21k\Omega$  as a standard resistor value for R1.

### 6.4 Set Switching Frequency

Substitute the target switching frequency into Equation 2 to calculate the required FS resistor.

(EQ. 15)

$$R_{FS}[k\Omega] = \frac{57356}{500[kHz]} - 14.53 = 100.18[k\Omega]$$

Select  $100k\Omega$  as a standard resistor value for R<sub>FS</sub>.

#### 6.5 Input Capacitor Selection

Use a mix of input bypass capacitors to control the voltage overshoot and undershoot across the internal MOSFETs of the synchronous buck regulator. Use small low ESR ceramic capacitors for high-frequency decoupling and bulk capacitors to supply the current needed each time the upper MOSFET turns on. Place the small ceramic capacitors physically close to the IC between the PVIN and PGND pins.

The critical parameters for the bulk input capacitance are the voltage and RMS current ratings. For reliable operation, select bulk capacitors with voltage and current ratings above the maximum input voltage and largest RMS current required by the circuit. Their voltage rating should be at least 1.5 times greater than the maximum input voltage, while a voltage rating of 2.5 times is a conservative guideline when considering voltage derating performance to 125°C. Consult the capacitor datasheets for temperature derating tables. For most cases, the RMS current rating requirement for the input capacitor of a buck regulator is approximately 1/2 the DC load current.

Use Equation 16 to closely approximate the maximum RMS current through the input capacitors.

$$\text{(EQ. 16)} \quad I_{CINrms} = \sqrt{\frac{V_{OUT}}{V_{IN}}x\bigg(I_{OUT}^{}_{MAX}^{} x\bigg(1-\frac{V_{OUT}}{V_{IN}}\bigg) + \frac{1}{12}x\bigg(\frac{V_{IN}^{} - V_{OUT}}{Lxf_{OSC}}x\frac{V_{OUT}^{}}{V_{IN}}\bigg)^2\bigg)}$$

The minimum recommended input capacitance for the ISL73007SEH is 44μF. Place these high-frequency, low-ESR capacitors close to the PVIN and PGND pins. These capacitors provide the instantaneous current into the buck regulator during the high-frequency switching transitions.

### 6.6 Output Capacitor Selection

An output capacitor is required to filter the inductor ripple current and supply the load transient current. The filtering requirements are a function of the switching frequency and the ripple current. The load transient requirements are a function of the slew rate (di/dt) and the magnitude of the transient load current. These requirements are generally achieved with a combination of bulk and decoupling capacitors with a careful layout.

High-frequency, low ESR ceramic capacitors initially supply the transient load current and reduce the current load slew rate seen by the bulk capacitors. The Effective Series Resistance (ESR) and voltage rating requirements generally determine the bulk filter capacitor values rather than actual capacitance requirements. Place high-frequency decoupling capacitors as close to the power pins of the load as physically possible. Be careful not to add inductance in the circuit board wiring that could cancel the usefulness of these low inductance components.

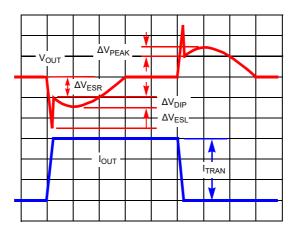

The shape of the output voltage waveform during a load transient that represents the worst-case loading conditions ultimately determines the number of output capacitors and their type. When this load transient is applied to the regulator, most of the current required by the load is initially contributed by the output capacitors. This is due to the finite amount of time required for the inductor current to slew up or down to the level of the output current required by the load. This results in a momentary undershoot or overshoot in the output voltage. At the initial edge of the transient undershoot or overshoot, the Equivalent Series Inductance (ESL) of each capacitor induces a spike that adds on top of the voltage drop due to the ESR. After the initial spike, the output voltage dips down (load step on) or peaks up (load step off) as the output capacitor sources or sinks the transient load current until the output inductor current reaches the load current. Figure 52 shows a typical response of the output voltage to a transient load current.

Figure 52. Typical Transient Response

Use Equation 17 to approximate the amplitudes of the voltage spikes caused by capacitor ESR and ESL, where  $I_{TRAN}$  = Output load current transient.:

$$\Delta V_{ESR} = ESR \times I_{TRAN}$$

(EQ. 17)

$$\Delta V_{ESL} = ESL \times \frac{dI_{TRAN}}{dt}$$

In a typical converter design, the ESR of the output capacitor bank impacts the transient response. The ESR and the ESL determine the number and types of output capacitors required to minimize the initial voltage spike at the output transient response. It may be necessary to place multiple output capacitors of both ceramic (to provide low ESR, ESL) and Tantalum (to provide the bulk capacitance in a small footprint) types in parallel to reduce the parasitic ESR and ESL to achieve minimize the magnitude of the output voltage spike during a load transient response.

The ESL of the capacitor is an important parameter and not usually listed in the datasheet. Use Equation 18 to approximate ESL if an Impedance vs Frequency curve is available, where  $f_{res}$  is the frequency where the lowest impedance is achieved (resonant frequency). The ESL of the capacitor becomes a concern when designing circuits that supply power to loads with high rates of change in the current.

(EQ. 18) ESL =

$$\frac{1}{C(2 \times \pi \times f_{res})^2}$$

If  $\Delta V_{DIP}$  and/or  $\Delta V_{PEAK}$  is too large for the output voltage limits, increasing the capacitance might be needed. A trade-off between output inductance and output capacitance might be necessary in this situation.

Calculate output impedance based on stability and transient response requirement.

Substituting into Equation 11 results in:

(EQ. 19)

$$C_{OUT\_MIN} = \frac{0.6V \times 0.923 \text{mA/V} \times 12 \text{A/V} \times 15 \text{k}\Omega}{2\pi \times 50 \text{kHz} \times 3.3 \text{V}} = 96 \mu \text{F}$$

Using a combination of ceramic and tantalum capacitors and allowing for additional margin, select  $2x 22\mu F$  ceramic and  $1x 100\mu F$  tantalum capacitors.

### 6.7 Output Inductor Selection

The inductor value determines the ripple current of the power supply. A reasonable starting target for inductor ripple current is ~33% of the total load current. The output inductor influences the response time of the regulator to a load transient. A smaller inductance value improves transient response but increases output voltage ripple. The

inductor value determines the inductor ripple current, with the output voltage ripple being a function of the ripple current. Use Equation 20 to approximate the inductor ripple current and Equation 21 to approximate the output voltage ripple, where ESR is the output capacitor equivalent series resistance.

(EQ. 20)

$$I_{RIPPLE} = \frac{(V_{IN} - V_{OUT})}{f_{SW} \times L} \times \frac{V_{OUT}}{V_{IN}}$$

(EQ. 21)

$$V_{OUT\_RIPPLE} = I_{RIPPLE} \left( \frac{1}{8 \times C_{OUT} \times f_{SW}} + ESR \right)$$

Increasing inductance reduces the ripple current and output voltage ripple; however, the regulator response time to transient load increases.

One of the parameters limiting the regulator response to a load transient is the time required to change the inductor current. The response time is the time required to slew the inductor current from its initial level to the transient level. During this interval, the difference between the inductor and transient load current is sourced from or sunk into the output capacitor. Minimizing the response time reduces the amount of transient voltage overshoot and undershoot on the output capacitor.

The worst-case response time can be during either the load step on or off. Check for transient load response for both turn-on and turn-off at the minimum and maximum load current.

Based on Equation 20, a standard inductor value of 4.7µH results in the following inductor ripple current, which is near our starting target of 33%.

(EQ. 22)

$$I_{RIPPLE} = \frac{(12V - 3.3V)}{500kHz \times 4.7\mu H} \times \frac{3.3V}{12V} = 1.018A$$

### 6.8 Slope Compensation Resistor

Substitute the selected FS resistor and inductor values into Equation 6 to calculate the slope compensation resistor.

$$R_{SLOPE}[k\Omega] = 0.62 \times 100 k\Omega \times \frac{3.3V}{4.7 \mu H} = 43.5 k\Omega$$

Select  $44.2k\Omega$  as a standard resistor value for  $R_{SI\ OPE}$ .

### 6.9 Compensation Resistor

The external compensation resistor depends on the target load transient response. For a 2% output voltage ripple requirement at a 2A load step,  $\Delta V_{OLIT}$  = 66mV:

**(EQ. 23)**

$$k = \frac{0.066}{3.3} = 0.02$$

Substituting into Equation 9 results in the below compensation resistor value

$$R_{COMP} = \frac{2A}{0.02 \times 0.6V \times 0.923mA/V \times 12A/V} = 15.048k\Omega$$

Select  $15k\Omega$  as a standard resistor value for  $R_{COMP}$ .

### 6.10 Compensation Capacitor