# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# APPLICATION NOTE

# μPD750008 SUBSERIES

4-BIT SINGLE-CHIP MICROCONTROLLER

μPD750004 μPD750006 μPD750008 μPD75P0016 The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

The application circuits and their parameters are for references only and are not intended for use in actual design-in's.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customer must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices in "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact NEC Sales Representative in advance.

Anti-radioactive design is not implemented in this product.

#### INTRODUCTION

Intended Readers

This application note is intended for engineers who understand the functions of  $\mu$ PD750008

subseries and who design an application system using any of these microcontrollers.

The  $\mu$ PD750008 subseries is a generic name that stands for the  $\mu$ PD750004, 750006, 750008,

and 75P0016.

**Purpose**

The main purpose of this manual is to help you understand the  $\mu$ PD750008 subseries hardware

functions.

How to Read

This application note is prepared on the assumption that its readers have general knowledge

regarding electricity, logic circuitry, and microcontroller.

The examples in this application note refer only to the  $\mu$ PD750008, if there are no differences from a functional standpoint with the other microcontrollers,  $\mu PD750008$  can be read as

$\mu$ PD750004,  $\mu$ PD750006 or  $\mu$ PD75P0016 where appropriate.

Legend

Data significance

: Left-hand digits are higher and right-hand digits are lower

Active low

:  $\overline{\times}$  (a bar over pin or signal name)

Note

: A point to be noted

Caution

: Information requiring your attention

Remark

Supplementary information

Number representation : Binary ......xxx or xxxxB -

Hexadecimal ··················×××H

#### **Related Documents**

#### Documents related to devices

| Document<br>Product | Brochure | Data Sheet | User's Manual | Instruction<br>Apllication<br>Table | Application<br>Note |

|---------------------|----------|------------|---------------|-------------------------------------|---------------------|

| μPD750004           |          | IC-3647    | IEU-1421      |                                     | U10452E             |

| μPD750006           |          |            |               |                                     | (this manual)       |

| μPD750008           |          |            |               |                                     |                     |

| μPD75P0016          |          | U10328E    |               |                                     |                     |

[MEMO]

# CONTENTS

| CHAPTE | ER 1 GENERAL DESCRIPTION                                              | 1  |

|--------|-----------------------------------------------------------------------|----|

| 1.1    | Differences between $\mu$ PD75008 and $\mu$ PD750008                  | 1  |

| 1.2    | Switching between Mk I Mode and Mk II Mode                            | 4  |

|        | 1.2.1 Using Mk I mode and Mk II mode                                  | 4  |

|        | 1.2.2 Using register bank                                             | 6  |

| 1.3    | Explanation of Application Programs                                   | 11 |

| CHAPTE | ER 2 SYSTEM CLOCK SELECTION FUNCTION APPLICATIONS                     | 13 |

| 2.1    | PCC Selection after RESET                                             | 15 |

| 2.2    | System Clock Selection when Commercial Power Line Failure is Detected | 17 |

|        | 2.2.1 Power-off processing                                            | 18 |

|        | 2.2.2 Power-on processing                                             | 18 |

|        | 2.2.3 Power-on/off processing application                             | 19 |

| CHAPTE | ER 3 BASIC INTERVAL TIMER APPLICATIONS                                | 23 |

| 3.1    | Reference Time Generation                                             | 23 |

| 3.2    | Watchdog Timer Application                                            | 25 |

| 3.3    | Remote Control Reception Application                                  |    |

| CHAPTI | ER 4 TIMER/EVENT COUNTER APPLICATIONS                                 | 43 |

| 4.1    | Interval Timer Setting                                                | 43 |

| 4.2    | Example of Output to PTO Pin                                          |    |

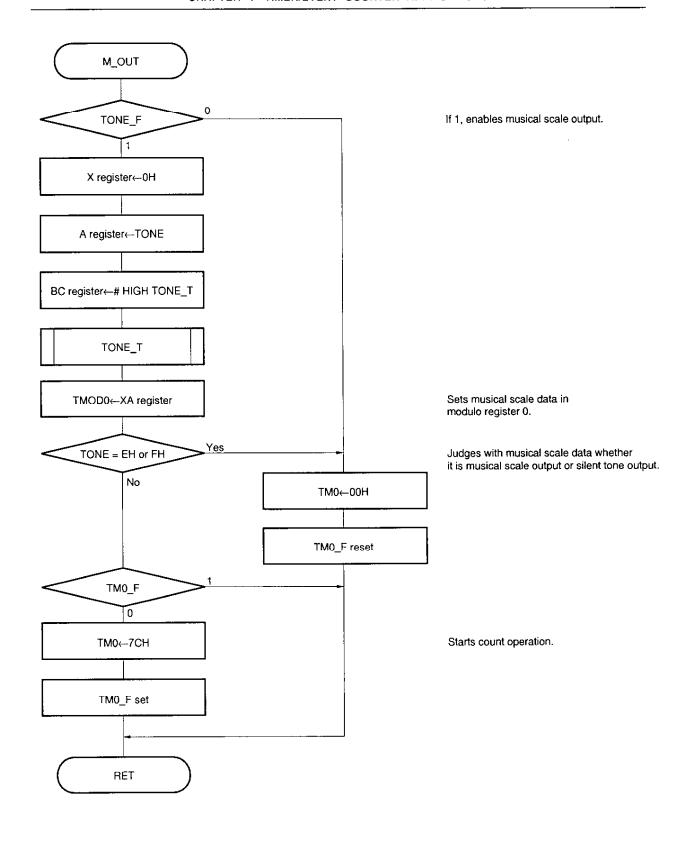

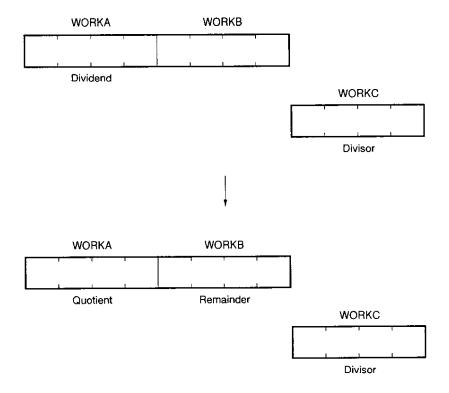

| 7.6    | 4.2.1 Melody output                                                   |    |

|        | 4.2.2 Divided event pulse output                                      |    |

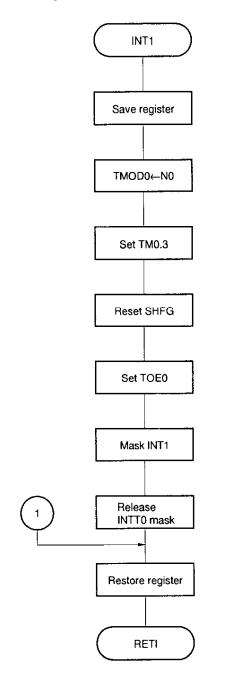

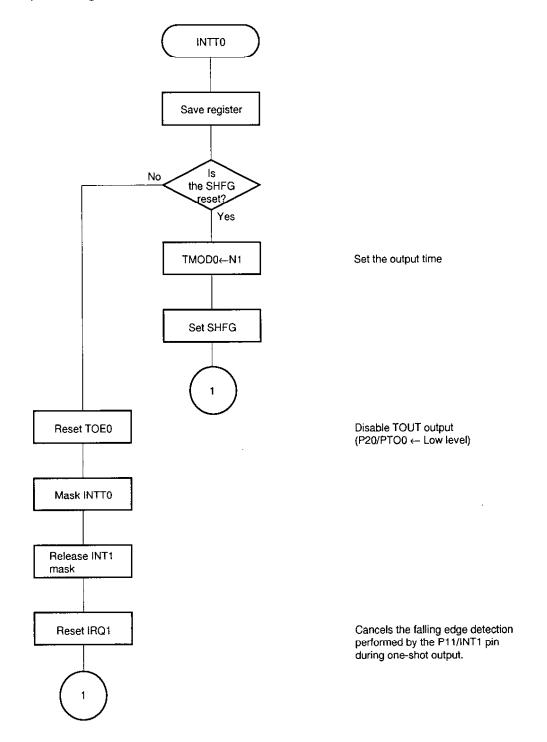

| 4.3    | One-shot Pulse Output                                                 |    |

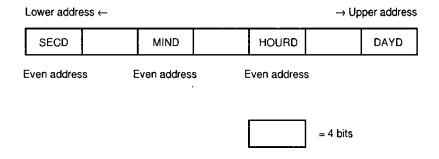

| CHAPTI | ER 5 CLOCK TIMER APPLICATIONS                                         | 65 |

| 5.1    | Clock Program                                                         | 65 |

| CHAPTI | ER 6 CLOCK OUTPUT CIRCUIT APPLICATION                                 | 71 |

| 6.1    | PCL Clock Output                                                      | 71 |

| CHAPTI | ER 7 BIT SEQUENTIAL BUFFER APPLICATIONS                               | 73 |

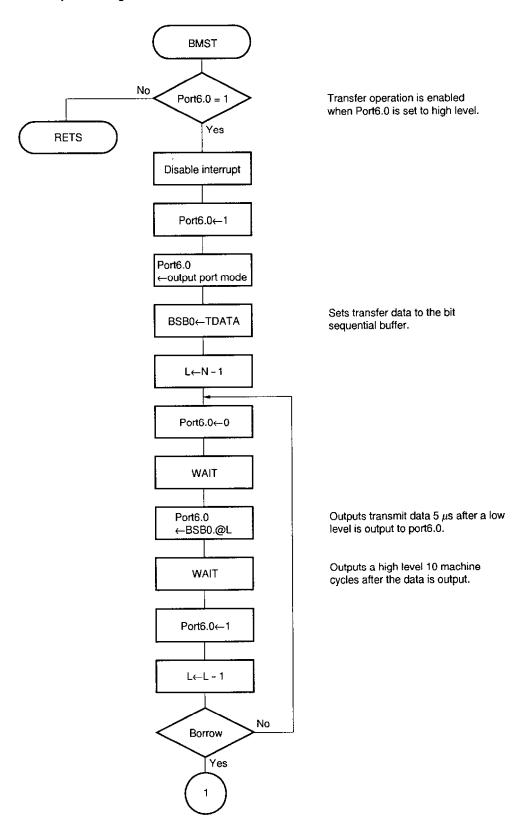

| 71     | High-Speed Serial Data Transfer                                       | 74 |

| CHAPTE                               | R 8 SERIAL INTERFACE APPLICATIONS                                                                                                                                                                                                                                        | 87                                                                               |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 8.1                                  | SBI Mode Application                                                                                                                                                                                                                                                     | 87                                                                               |

| CHAPTE                               | R 9 KEY INPUT SUBROUTINE                                                                                                                                                                                                                                                 | 99                                                                               |

| CHAPTEI                              | R 10 SUBROUTINES                                                                                                                                                                                                                                                         | 107                                                                              |

| 10.1                                 | Data Transfer                                                                                                                                                                                                                                                            | 107                                                                              |

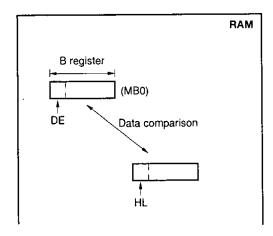

| 10.2                                 | Data Comparison                                                                                                                                                                                                                                                          | 108                                                                              |

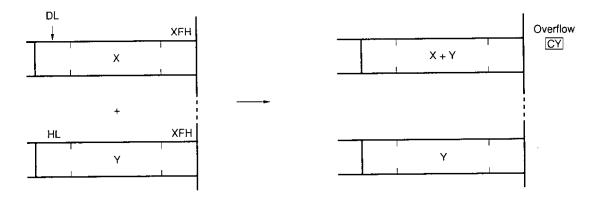

| 10.3                                 | Decimal Addition                                                                                                                                                                                                                                                         | 109                                                                              |

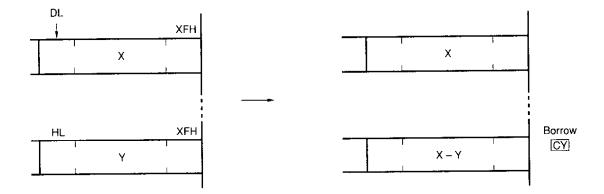

| 10.4                                 | Decimal Subtraction                                                                                                                                                                                                                                                      | 110                                                                              |

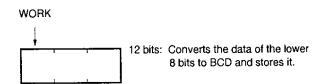

| 10.5                                 | Binary/Decimal Conversion                                                                                                                                                                                                                                                | 112                                                                              |

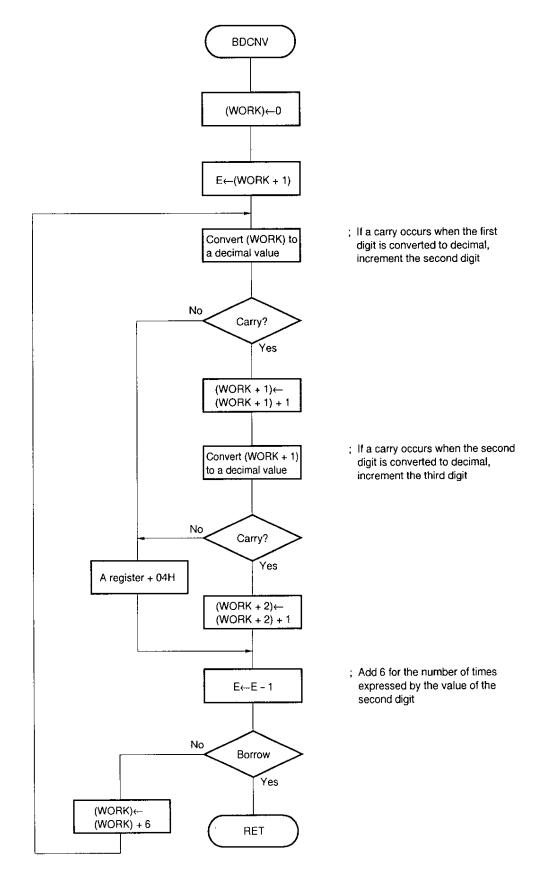

| 10.6                                 | 8-bit Multiplication                                                                                                                                                                                                                                                     | 115                                                                              |

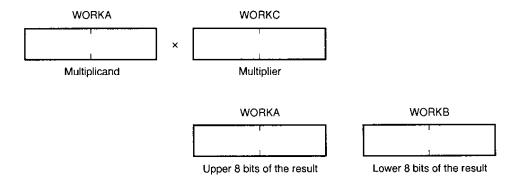

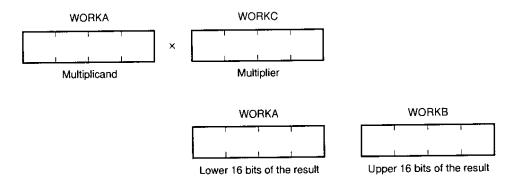

| 10.7                                 | 16-bit Multiplication                                                                                                                                                                                                                                                    | 117                                                                              |

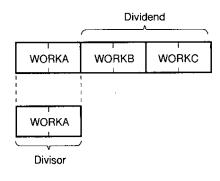

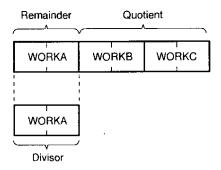

| 10.8                                 | Binary Division (16-bit ÷ 8-bit)                                                                                                                                                                                                                                         | 119                                                                              |

| 10.9                                 | Binary Division (16-bit ÷ 16-bit)                                                                                                                                                                                                                                        | 122                                                                              |

|                                      |                                                                                                                                                                                                                                                                          |                                                                                  |

|                                      | R 11 APPLICATION EXAMPLES OF THIS APPLICATION PROGRAM                                                                                                                                                                                                                    | 125                                                                              |

|                                      | R 11 APPLICATION EXAMPLES OF THIS APPLICATION PROGRAM                                                                                                                                                                                                                    |                                                                                  |

| CHAPTE                               | R 11 APPLICATION EXAMPLES OF THIS APPLICATION PROGRAM                                                                                                                                                                                                                    | 125                                                                              |

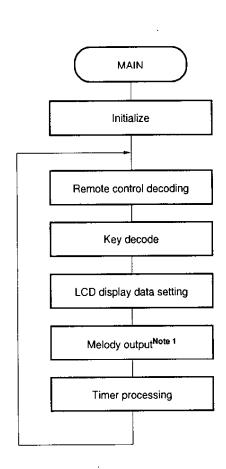

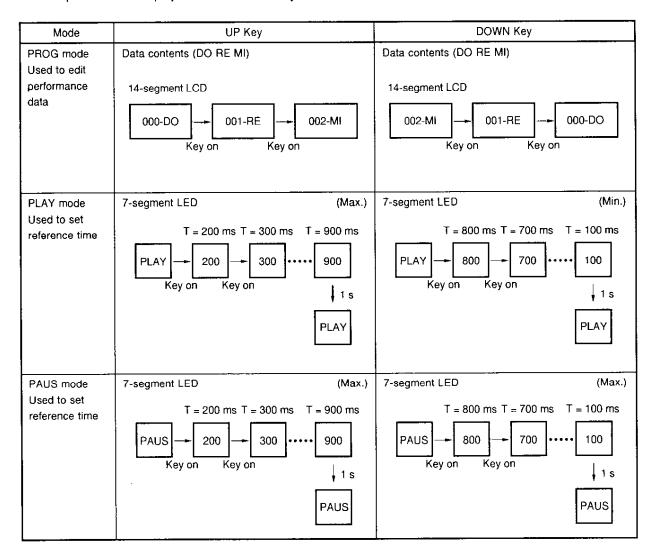

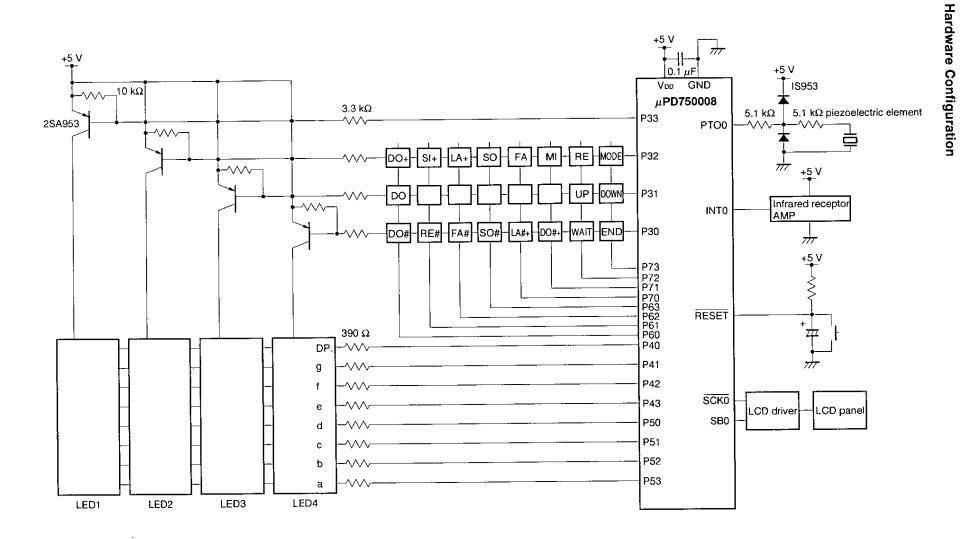

| 11.1<br>11.2                         | Program Outline                                                                                                                                                                                                                                                          | 125<br>127                                                                       |

| CHAPTE                               | Program Outline                                                                                                                                                                                                                                                          | 125<br>127<br>128                                                                |

| 11.1<br>11.2<br>11.3                 | Program Outline                                                                                                                                                                                                                                                          | 125<br>127<br>128<br>130                                                         |

| 11.1<br>11.2<br>11.3<br>11.4         | Program Outline                                                                                                                                                                                                                                                          | 125<br>127<br>128<br>130<br>131                                                  |

| 11.1<br>11.2<br>11.3<br>11.4         | Program Outline                                                                                                                                                                                                                                                          | 125<br>127<br>128<br>130<br>131<br>131<br>132                                    |

| 11.1<br>11.2<br>11.3<br>11.4         | Program Outline                                                                                                                                                                                                                                                          | 125<br>127<br>128<br>130<br>131<br>131<br>132<br>133                             |

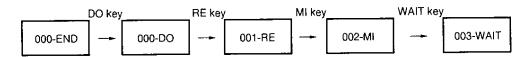

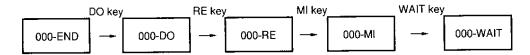

| 11.1<br>11.2<br>11.3<br>11.4         | Program Outline                                                                                                                                                                                                                                                          | 125<br>127<br>128<br>130<br>131<br>132<br>133<br>134                             |

| 11.1<br>11.2<br>11.3<br>11.4         | Program Outline                                                                                                                                                                                                                                                          | 125<br>127<br>128<br>130<br>131<br>132<br>133<br>134<br>134                      |

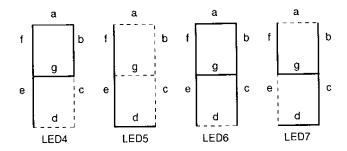

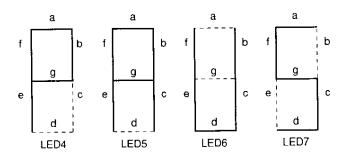

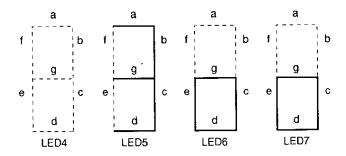

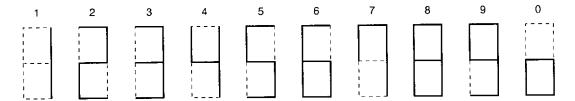

| 11.1<br>11.2<br>11.3<br>11.4<br>11.5 | Program Outline System Configuration Port Assignment State Transition Table Explanation of Function by Key 11.5.1 MODE key 11.5.2 UP/DOWN key 11.5.3 Musical scale keys 11.5.4 END key 11.5.5 Other keys Explanation of Display 11.6.1 LED display                       | 125<br>127<br>128<br>130<br>131<br>132<br>133<br>134<br>134<br>135<br>135        |

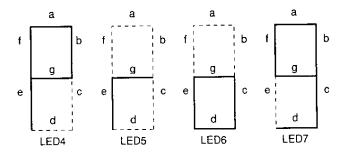

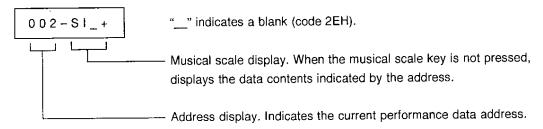

| 11.1<br>11.2<br>11.3<br>11.4<br>11.5 | Program Outline System Configuration Port Assignment State Transition Table Explanation of Function by Key  11.5.1 MODE key 11.5.2 UP/DOWN key 11.5.3 Musical scale keys 11.5.4 END key 11.5.5 Other keys Explanation of Display  11.6.1 LED display  11.6.2 LCD display | 125<br>127<br>128<br>130<br>131<br>132<br>133<br>134<br>134<br>135<br>135        |

| 11.1<br>11.2<br>11.3<br>11.4<br>11.5 | Program Outline System Configuration Port Assignment State Transition Table Explanation of Function by Key 11.5.1 MODE key 11.5.2 UP/DOWN key 11.5.3 Musical scale keys 11.5.4 END key 11.5.5 Other keys Explanation of Display 11.6.1 LED display                       | 125<br>127<br>128<br>130<br>131<br>132<br>133<br>134<br>134<br>135<br>135<br>137 |

# LIST OF FIGURES (1/2)

| No. | Title                                                                     | Page |

|-----|---------------------------------------------------------------------------|------|

| 1-1 | Format of Stack Bank Selection Register                                   | 5    |

| 1-2 | Example of Use of Different Register Banks                                | 7    |

| 1-3 | Configuration of General Registers (In Case of 4-Bit Processing)          | 9    |

| 1-4 | Configuration of General Registers (In Case of 8-Bit Processing)          | 10   |

| 2-1 | Processor Clock Control Register Format                                   |      |

| 2-2 | System Clock Control Register Format                                      | 14   |

| 2-3 | Power Supply Voltage (VDD) v.s. Minimum Instruction Execution Time (tcr)  | 14   |

| 2-4 | CPU Clock Selection after RESET                                           | 16   |

| 2-5 | System Clock Selection when Commercial Power Supply is Turned ON/OFF      | 17   |

| 2-6 | Algorithm of INT4 Interrupt Servicing                                     | 17   |

| 3-1 | Basic Interval Timer Mode Register Format                                 | 23   |

| 3-2 | Format of Watchdog Timer Enable Flag                                      | 25   |

| 3-3 | Typical Remote Control Receiver Circuit Example                           | 27   |

| 3-4 | Remote Control Transmitter IC Output Signal                               | 28   |

| 3-5 | Receiver Preamplifier Output Waveform                                     | 29   |

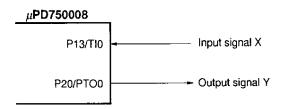

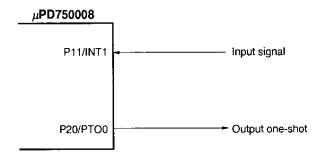

| 4-1 | PTO Pin Using Example                                                     | 46   |

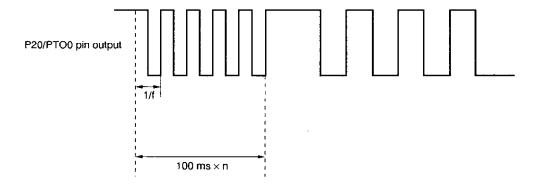

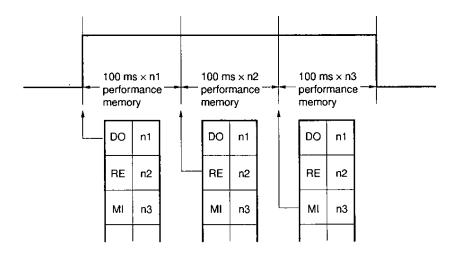

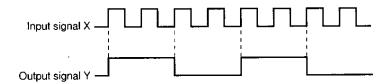

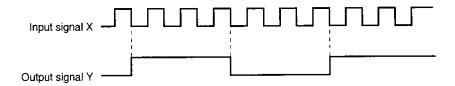

| 4-2 | Conceptual Chart of Output Signal from Pin P20/PTO0                       | 47   |

| 4-3 | Data Format                                                               |      |

| 4-4 | Divided Event Pulse Output                                                | 57   |

| 4-5 | One-shot Pulse Output                                                     | 59   |

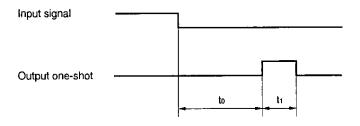

| 4-6 | One-shot Pulse Output Timing (1)                                          | 59   |

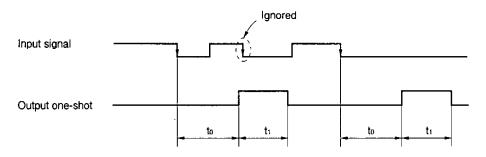

| 4-7 | One-shot Pulse Output Timing (2)                                          | 60   |

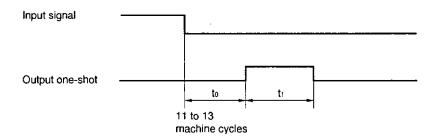

| 4-8 | One-shot Pulse Output Timing (3)                                          | 60   |

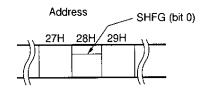

| 4-9 | RAM Area Layout Used in This Program                                      | 61   |

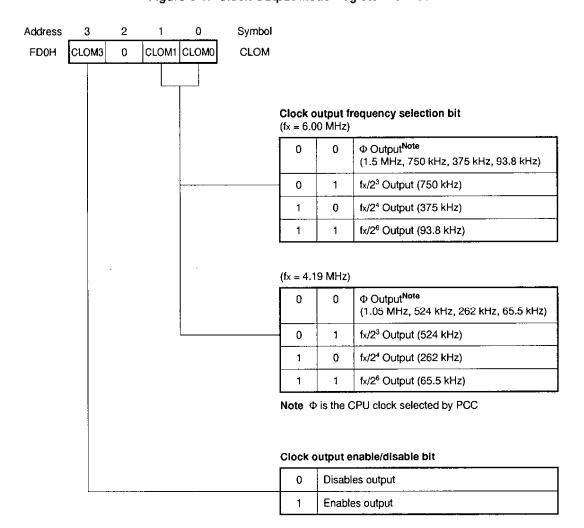

| 6-1 | Clock Output Mode Register Format                                         | 71   |

| 6-2 | Wave Form of Clock Output                                                 | 72   |

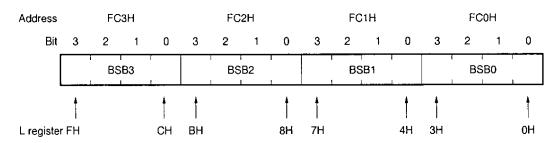

| 7-1 | Bit Sequential Buffer Indirect Addressing                                 | 73   |

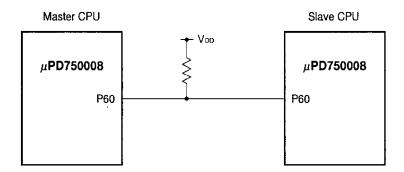

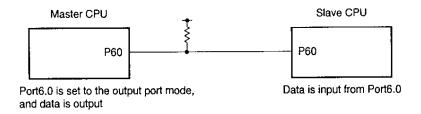

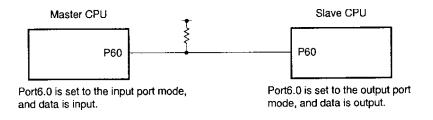

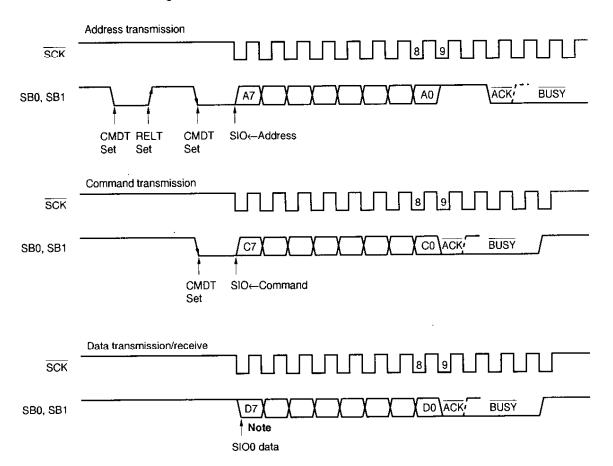

| 7-2 | Configuration of Multi-Processor System (High-Speed Serial Data Transfer) | 74   |

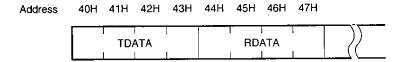

| 7-3 | RAM layout this program                                                   | 76   |

| 8-1 | Typical Configuration of Serial Bus Interface                             | 87   |

# LIST OF FIGURES (2/2)

| No.  | Title                                    | Page |

|------|------------------------------------------|------|

| 8-2  | Address, Command, and Data Format        | 88   |

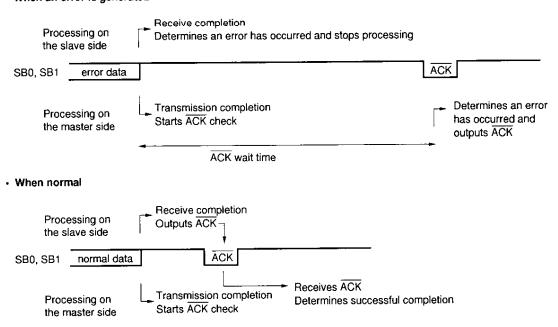

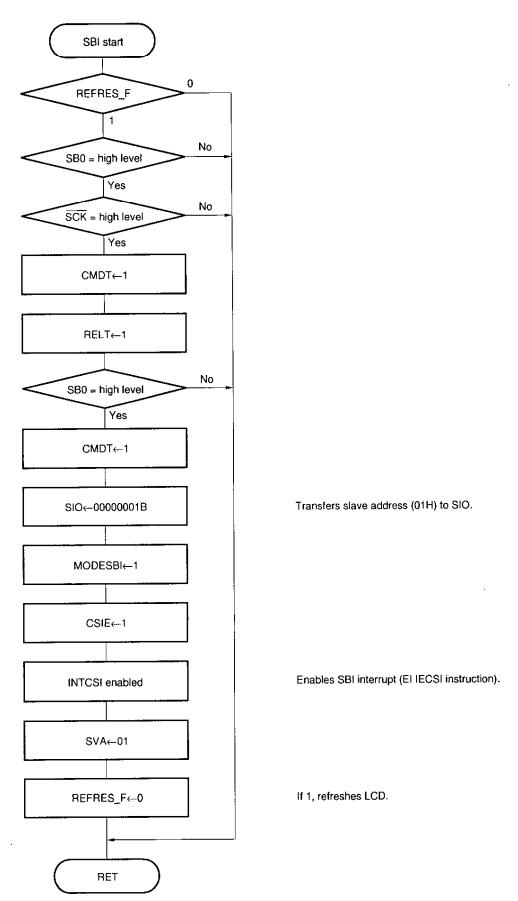

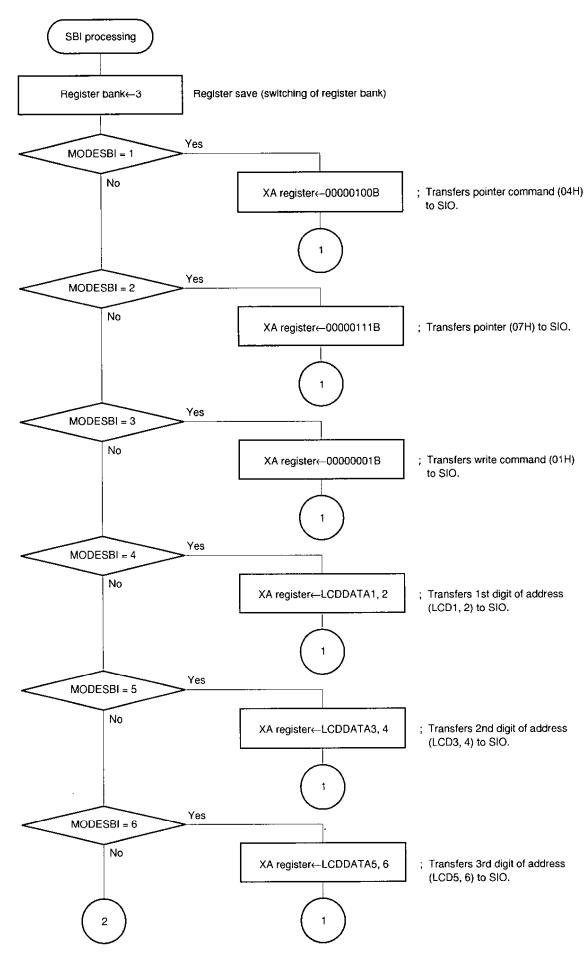

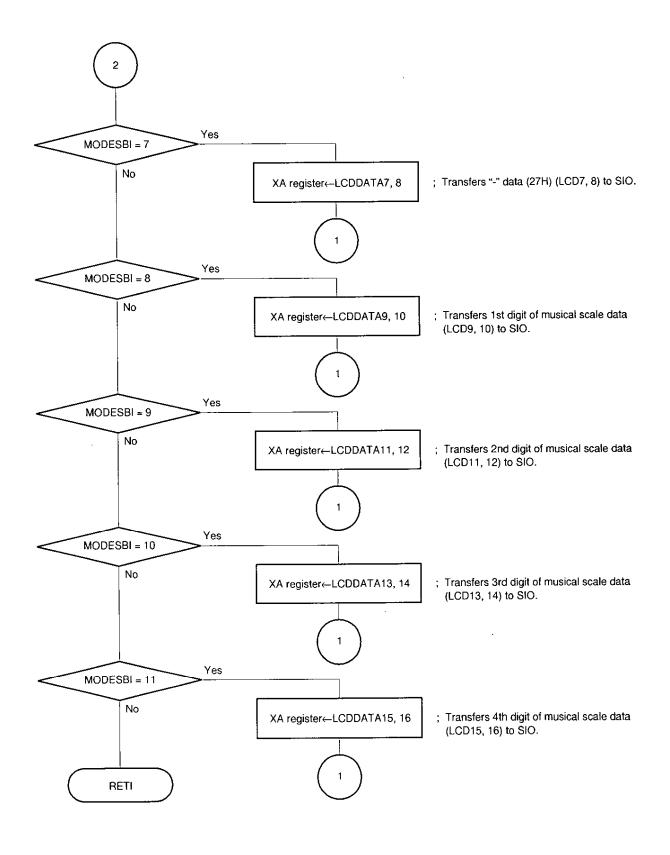

| 8-3  | Error Check using the Acknowledge Signal | 89   |

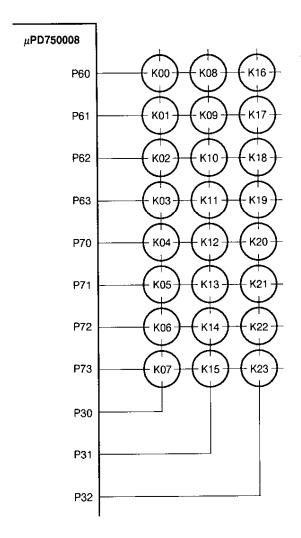

| 9-1  | Key Matrix Configuration                 | 99   |

| 11-1 | System Configuration                     | 127  |

# LIST OF TABLES

| No.  | Title                                                                                   | Page  |

|------|-----------------------------------------------------------------------------------------|-------|

| 1-1  | Differences between μPD750008 Subseries Products                                        | . 1   |

| 1-2  | Differences between μPD75008 and μPD750008                                              | . 2   |

| 1-3  | Differences between Mk I Mode and Mk II Mode                                            | . 4   |

| 1-4  | RBE and RBS, and Register Banks Selected                                                | . 6   |

| 1-5  | Example of Use of Different Register Banks for Normal Routines and Interrupt Routines   | . 6   |

| 4-1  | Resolution and Maximum Timer Value (fx = 4.194304 MHz)                                  | . 44  |

| 4-2  | Values to be Set in Modulo Register for Each Musical Scale, and Error between Frequency | . 47  |

| 4-3  | Produced and Each Musical Scale Frequency                                               | . 47  |

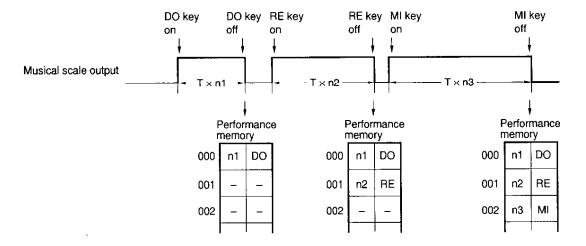

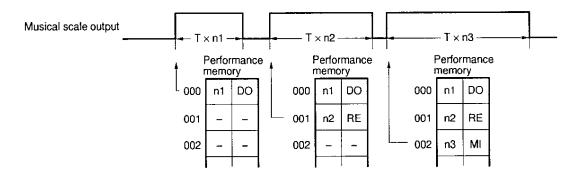

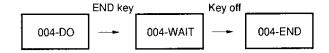

| 4-4  | Relationship between Tone Length Data and Musical Scale Output                          | . 49  |

| 11-1 | μPD750008 Port Assignment                                                               | . 128 |

| 11-2 | State Transition Table                                                                  | . 130 |

# [MEMO]

#### **CHAPTER 1 GENERAL DESCRIPTION**

The  $\mu$ PD750008 subseries comprises 75XL series 4-bit single-chip microcontrollers, successors of the 75X series products, boasting a comprehensive product line-up.

The differences among the  $\mu$ PD750008 subseries products are shown in Table 1-1.

Table 1-1. Differences between μPD750008 Subseries Products

| Product Name | Program Memory (ROM) | ROM Configuration | Program Counter |

|--------------|----------------------|-------------------|-----------------|

| μPD750004    | 4096 bytes           | Mask ROM          | 12 bits         |

| μPD750006    | 6144 bytes           |                   | 13 bits         |

| μPD750008    | 8192 bytes           |                   |                 |

| μPD75P0016   | 16384 bytes          | One-time PROM     | 14 bits         |

# 1.1 Differences between $\mu$ PD75008 and $\mu$ PD750008

The  $\mu$ PD750008 inherits the functions and instructions of the previous  $\mu$ PD75008 (75X series), which facilitates replacement between the old and new products.

Table 1-2 shows the differences between the  $\mu$ PD75008 and  $\mu$ PD750008.

Table 1-2. Differences between  $\mu$ PD75008 and  $\mu$ PD750008 (1/2)

| Item                                |                                                        | μPD75008                                                           | μPD750008                                                                                                                                 |  |

|-------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| Program memory                      |                                                        | 0000H - 1F7FH<br>8064 × 8 bits                                     | 0000H - 1FFFH<br>8192 × 8 bits                                                                                                            |  |

| Data memory                         |                                                        | 000H to 1FFH (512 × 4 bits)                                        |                                                                                                                                           |  |

| CPU                                 |                                                        | 75X Standard                                                       | 75XL                                                                                                                                      |  |

| Oscillation stabilization wait time |                                                        | Fixed at 31.3 ms                                                   | 2 <sup>15</sup> /f <sub>x</sub> , 2 <sup>17</sup> /f <sub>x</sub> Note<br>(selectable by mask option)                                     |  |

| Instruc-<br>tion<br>execu-<br>tion  | When main system clock is selected                     | 0.95, 1.91, 15.3 μs<br>(4.19 MHz operation only)                   | <ul> <li>0.95, 1.91, 3.81, 15.3 μs<br/>(in 4.19 MHz operation)</li> <li>0.67, 1.33, 2.67, 10.7 μs<br/>(in 6.0 MHz operation)</li> </ul>   |  |

| time                                | When subsystem clock is selected                       | 122 μs (in 32.768 kHz operation)                                   |                                                                                                                                           |  |

| Stack                               | SBS register                                           | No                                                                 | Yes SBS.3 = 1: Mk I mode selected SBS.3 = 0: Mk II mode selected                                                                          |  |

|                                     | Stack area                                             | 000H - 0FFH                                                        | n00H - nFFH (n = 0, 1)                                                                                                                    |  |

|                                     | Stack operation of subroutine call instruction         | 2-byte stack                                                       | In Mk I mode: 2-byte stack In Mk II mode: 3-byte stack                                                                                    |  |

| Instruc-<br>tion                    | BRA laddr1 operation<br>CALLA laddr1 operation         | Unusable                                                           | In Mk I mode: Unusable<br>In Mk II mode: Usable                                                                                           |  |

|                                     | MOVT XA, @BCDE<br>MOVT XA, @BCXA<br>BR BCDE<br>BR BCXA |                                                                    | Usable                                                                                                                                    |  |

|                                     | CALL laddr                                             | 3 machine cycles                                                   | In Mk I mode: 3 machine cycles In Mk II mode: 4 machine cycles                                                                            |  |

|                                     | CALLF !faddr                                           | 2 machine cycles                                                   | In Mk I mode: 2 machine cycles In Mk II mode: 3 machine cycles                                                                            |  |

| Timer                               |                                                        | 3 channels  Basic interval timer  Timer/event counter  Watch timer | 4 channels  Basic interval timer/watchdog timer  Timer/event counter  Timer counter  Watch timer                                          |  |

| Clock output (PCL)                  |                                                        | • Ф, 524, 262, 65.5 kHz<br>(in 4.19 MHz operation)                 | <ul> <li>Ф, 524, 262, 65.5 kHz</li> <li>(in 4.19 MHz operation)</li> <li>Ф, 750, 375, 93.7 kHz</li> <li>(in 6.0 MHz operation)</li> </ul> |  |

**Note** 2<sup>15</sup>/fx: 5.46 ms at 6.0 MHz, 7.81 ms at 4.19 MHz 2<sup>17</sup>/fx: 21.8 ms at 6.0 MHz, 31.3 ms at 4.19 MHz

Table 1-2. Differences between  $\mu PD75008$  and  $\mu PD750008$  (2/2)

| ltem                                            |                                         | μPD75008                                                                                                                                 | μPD750008                                                                                                        |  |

|-------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|

| Buzzer output (BUZ)                             |                                         | 2 kHz                                                                                                                                    | <ul> <li>2.4, 32 kHz (in 4.19 MHz operation)</li> <li>2.86, 5.72, 45.8 kHz<br/>(in 6.0 MHz operation)</li> </ul> |  |

| Serial interface                                |                                         | Compatible with 3 types of mode  • 3-wire serial I/O mode ··· MSB first/LSB first can be switched.  • 2-wire serial I/O mode  • SBI mode |                                                                                                                  |  |

| SOS Feedback resistor cut flag register (SÖS.0) |                                         | Feedback resistor can be incorporated using mask option.                                                                                 | Incorporated                                                                                                     |  |

|                                                 | Sub-oscillator current cut flag (SOS.1) | No                                                                                                                                       |                                                                                                                  |  |

| Register                                        | bank selection register (RBS)           | No                                                                                                                                       | Yes                                                                                                              |  |

| Standby                                         | release by INT0                         | Not possible                                                                                                                             | Possible                                                                                                         |  |

| Vectored                                        | d interrupt                             | External: 3 Internal: 3                                                                                                                  | External: 3 Internal: 4                                                                                          |  |

| Process                                         | or clock control register (PCC)         | PCC = 0, 2, 3 can be used.                                                                                                               | PCC = 0 to 3 can be used.                                                                                        |  |

| Supply voltage                                  |                                         | V <sub>DD</sub> = 2.7 to 6.0 V V <sub>DD</sub> = 2.2 to 5.5 V                                                                            |                                                                                                                  |  |

| Package                                         |                                         | 42-pin plastic shrink DIP (600 mil)     44-pin plastic QFP (10 × 10 mm)                                                                  |                                                                                                                  |  |

# 1.2 Switching between Mk I Mode and Mk II Mode

# 1.2.1 Using Mk I mode and Mk II mode

The CPU of the  $\mu$ PD750008 subseries has two modes, Mk I mode and Mk II mode, and can select either of the two. The mode can be switched by bit 3 of the stack bank selection register (SBS).

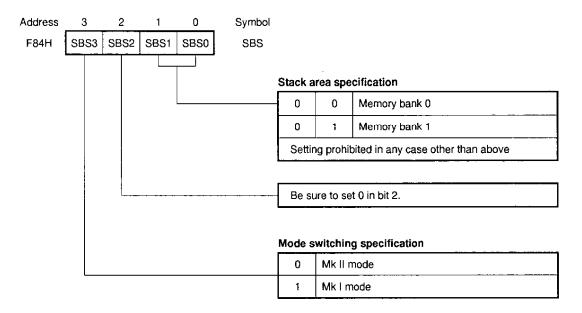

Table 1-3 shows the differences between Mk I mode and Mk II mode, and Figure 1-1 shows the format of the stack bank selection register.

- Mk I mode: Has upward compatibility with the μPD75008 subseries.

Can be used with a 75XL CPU which has a ROM capacity of up to 16K bytes.

- Mk II mode: Does not have upward compatibility with the μPD75008 subseries.

Can be used with all 75XL CPUs including products which have ROM capacity of 16K bytes or more.

Table 1-3. Differences between Mk I Mode and Mk II Mode

|                                                 | Mk I Mode           | Mk II Mode       |

|-------------------------------------------------|---------------------|------------------|

| Number of stack bytes of subroutine instruction | 2 bytes             | 3 bytes          |

| BRA !addr1 instruction CALLA !addr1 instruction | Undefined operation | Normal operation |

| CALL !addr instruction                          | 3 machine cycles    | 4 machine cycles |

| CALLF !faddr instruction                        | 2 machine cycles    | 3 machine cycles |

Remark The Mk II mode is used to maintain software compatibility with those 75X series or 75XL series which have a program memory of 24K bytes or more.

Therefore, when ROM efficiency or speed needs to be given priority, use the Mk I mode.

The stack bank selection register is set by a 4-bit memory manipulation instruction.

When the Mk I mode is used, be sure to initialize the stack bank selection register to 10xxB<sup>Note</sup>. When the Mk II mode is used, be sure to initialize it to 00xxB<sup>Note</sup>.

Figure 1-1. Format of Stack Bank Selection Register

Note Set a desired value in "xx."

Caution SBS.3 becomes "1" after the generation of a RESET signal, and therefore the CPU operates in Mk I mode. When using an instruction in Mk II mode, set SBS.3 to "0" and set Mk II mode before using the instruction.

#### 1.2.2 Using register bank

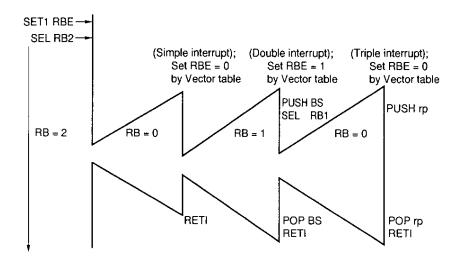

The  $\mu$ PD750008 subseries incorporates 4 register banks, with each bank consisting of 8 general registers X, A, B, C, D, E, H and L. This general register area is mapped at addresses 00H to 1FH of memory bank 0 of the data memory (refer to **Figure 1-3**). A register bank enable flag (RBE) and register bank selection register (RBS) are incorporated in order to specify these general register banks. The RBS register is used to select the register banks and the RBE flag is used to determine whether the register bank selected by RBS should be enabled or disabled. The register banks (RB) enabled in execution of an instruction are as follows.

RB = RBE-RBS

**RBS** RBE Register Bank 3 2 1 0 0 0 0 Fixed at bank 0 × × 1 0 0 0 Bank 0 selected 0 0 Bank 1 selected 1 1 0 Bank 2 selected 1 1 Bank 3 selected

Fixed at 0

Table 1-4. RBE and RBS, and Register Banks Selected

Remark x: don't care

RBE is automatically saved/restored during subroutine processing and so it can freely be set during subroutine processing. Moreover, when an interrupt is serviced, RBE can automatically be saved/restored, and RBE can be set during interrupt servicing by setting an interrupt vector table concurrently with the start of interrupt servicing.

Therefore, as shown in Table 1-5, it is possible to speed up interrupt servicing by using different register banks for normal processing and interrupt servicing so that no save/restore of a general register is required in a simple interrupt, and only RBS save/restore is required in double interrupts.

Table 1-5. Example of Use of Different Register Banks for Normal Routines and Interrupt Routines

| Normal Processing                      | Set RBE = 1 and use register banks 2 and 3.                                        |  |

|----------------------------------------|------------------------------------------------------------------------------------|--|

| Simple interrupt servicing             | Set RBE = 0 and use register bank 0.                                               |  |

| Double interrupt servicing             | Set RBE = 1 and use register bank 1. (In this case, RBS save/restore is required.) |  |

| Triple or superior interrupt servicing | Save register by PUSH and POP.                                                     |  |

Figure 1-2. Example of Use of Different Register Banks

#### (Main program)

When RBS is changed by subroutine processing or interrupt servicing, it should be saved/restored by a PUSH/POP instruction.

RBE is set by the SET1/CLR1 instruction. RBS is set by the SEL instruction.

The general register area incorporated in the  $\mu$ PD750008 can be used not only as a 4-bit register but also as an 8-bit register by a register pair, enabling programming centered on general registers to be performed by transfer, operation, compare, increment/decrement instructions comparable to those of an 8-bit microcontroller.

## (1) Using the general register area as a 4-bit register

When using the general register area as a 4-bit register, a total of eight general registers, X, A, B, C, D, E, H and L of the register banks specified by RB = RBE-RBS can be used as shown in Figure 1-3. Of these, the A register plays a central role as a 4-bit accumulator in transfer, operation and comparison of 4-bit data. The other general registers can perform accumulator transfer, comparison and increment/decrement.

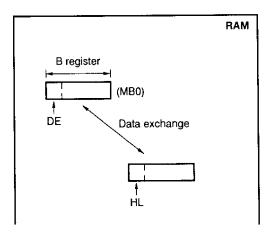

# (2) Using the general register area as an 8-bit register

When using the general register area as an 8-bit register, a total of eight 8-bit registers can be used as shown in Figure 1-4 by designating register pairs of the register banks specified by RB = RBE-RBS as XA, BC, DE and HL, and register pairs of the register banks whose bank (RB) bit 0 is inverted as XA', BC', DE' and HL'. Of these, the XA register pair plays a central role in transfer, operation, comparison, etc. of 8-bit data as an 8-bit accumulator. The other register pairs can perform accumulator transfer, operation, comparison and increment/ decrement. Furthermore, the HL register pair functions mainly as a data pointer. The register pairs DE and DL also function as auxiliary data pointers.

```

Examples 1. INCS

_{\mathrm{HL}}

; HL←HL + 1, skips with HL = 00H

; XA 		XA + BC, skips with a carry

ADDS

XA, BC

; DE'←DE' - XA - CY

SUBC

DE', XA

; XA←XA'

VOM

XA, XA'

MOVT

XA, @PCDE

; XA←(PC<sub>12-8</sub> + DE) ROM, table reference

; Skips if XA = BC.

SKE

XA, BC

```

2. Perform a test to determine whether the value of the count register (T0) of timer/event counter0 is greater than the value of the BC' register pair and wait until it becomes greater.

```

CLR1 MBE ;

NO: MOV XA, TO ; Reading of count register

SUBS XA, BC'; XA ≥ BC?

BR YES ; YES

BR NO ; NO

```

Figure 1-3. Configuration of General Registers (In Case of 4-Bit Processing)

| х | 01H | А | 00Н |                 |

|---|-----|---|-----|-----------------|

| н | 03H | L | 02H | Register bank 0 |

| D | 05H | E | 04H | (RBE·RBS = 0)   |

| В | 07H | С | 06H |                 |

| × | 09H | Α | 08H |                 |

| н | 0ВН | L | 0AH | Register bank 1 |

| D | ODH | E | 0CH | (RBE-RBS = 1)   |

| В | 0FH | С | 0EH |                 |

| х | 11H | A | 10H |                 |

| Н | 13H | L | 12H | Register bank 2 |

| Đ | 15H | E | 14H | (RBE-RBS = 2)   |

| В | 17H | С | 16H |                 |

| х | 19H | Α | 18H |                 |

| Н | 1BH | L | 1AH | Register bank 3 |

| D | 1DH | E | 1CH | (RBE-RBS = 3)   |

| В | 1FH | С | 1EH |                 |

Figure 1-4. Configuration of General Registers (In Case of 8-Bit Processing)

XA

XA

|     |     |                  |                 | T T              |

|-----|-----|------------------|-----------------|------------------|

| XA  | 00Н |                  | XA' 00H         |                  |

| HL  | 02H |                  | HL'<br>02H      |                  |

| DE  | 04H |                  | DE'             |                  |

| ВС  | 06H | Nu               | BC'             | Mar. 555 550 4   |

| ΧA' | 08H | When RBE RBS = 0 | XA<br>08H       | When RBE·RBS = 1 |

| HL' | 0AH |                  | HL<br>0AH       |                  |

| DE' | 0CH |                  | DE OCH          |                  |

| BC' | 0EH |                  | BC 0EH          |                  |

|     |     |                  |                 | <del></del>      |

| XA  | 10H | •                | XA' 10H         |                  |

| HL  | 12H |                  | HL' 12H         |                  |

| DE  | 14H |                  | DE' 14H         |                  |

| BC  | 16H | When RBE-RBS = 2 | BC <sup>1</sup> | When RBE-RBS = 3 |

| XA' | 18H |                  | XA<br>18H       | When uprings = 3 |

| HL' | 1AH |                  | HL 1AH          |                  |

| DE' | 1CH |                  | DE<br>1CH       |                  |

| BC' | 1EH |                  | BC 1EH          |                  |

# 1.3 Explanation of Application Programs

In the chapters of this Application Note, application programs are described on packaged for each function. Therefore, if an application program is combined with a user program (main program) using a linker, it can also function as part of a system program.

Furthermore, in CHAPTER 11 APPLICATION EXAMPLES OF THIS APPLICATION PROGRAM some of the application programs explained in CHAPTER 10 are used to create a system program.

When using each package, follow the explanation of the program corresponding to the package. A brief description of the items used in the program explanations is given below.

<Public declaration symbol> : Indicates the subroutine used in the package.

If this symbol is externally referenced/declared, referencing is

possible within the package.

**Externally referenced/declared symbol>**: Indicates the area of data memory used in the package.

If this symbol is defined and publicly declared, it can be used within

the package.

<Register used> : Indicates the register used in the package.

<RAM used> : Indicates the area of data memory used in the package.

<Nesting> : Indicates the nesting level enabled in the package.

Figures in parentheses denote the maximum value of the stack

used.

**<Hardware used>** : Indicates the hardware used in the package. **<Interrupt>** : Indicates the interrupt used in the package.

<Initialization> : Indicates initialization required to operate the package.

However, SCC = 0 and PCC = 3 are set in each package unless

specified otherwise.

**<Start-up method>** : Indicates the procedure necessary to operate the package.

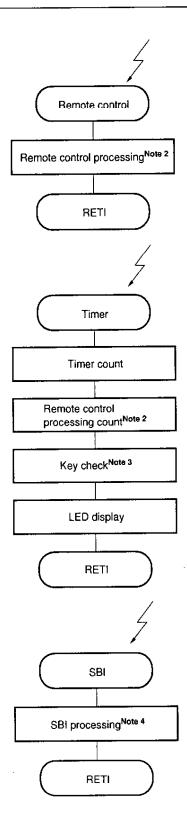

Each package operates in Mk II mode. The register banks can be switched by the following interrupts.

RBE = 0, RBS = 0: Main routine

RBE = 1, RBS = 1: INTO interrupt (reception of remote control)

RBE = 1, RBS = 2: Basic interval timer

RBE = 1, RBS = 3: SBI

An example of program description is shown below.

```

MBE = 0, RBE = 0, INIT

; RESET

VENT0

MBE = 0, RBE = 1, INTBT

; INTBT/INT4

VENT1

MBE = 0, RBE = 1, INT0

; INT0

VENT2

VENT4

MBE = 0, RBE = 1, SBI

; SBI

Initial setting

INIT:

; Disables all interrupts.

DI

; MBE ← 0

CLR1

MBE

MOV

XA, #00H

; Stack pointer ← 00H

SP, XA

MOV

; Memory bank ← 0, Mk II mode selected

SBS,A

MOV

Remote control processing

INT0:

DΙ

PUSH

BS

; Register bank ← 1

RB1

SEL

INTBT:

(

; Register bank ← 2

SEL

RB2

SBI processing

SBI;

; Register bank ← 3

SEL

RB3

```

## CHAPTER 2 SYSTEM CLOCK SELECTION FUNCTION APPLICATIONS

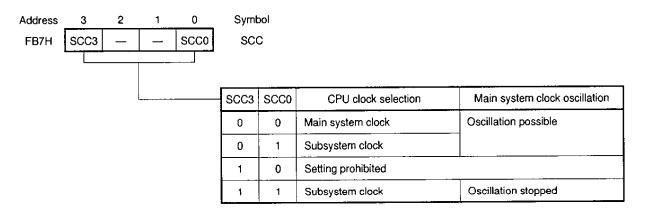

For the  $\mu$ PD750008, the CPU clock and system clock can be switched by modifying the processor clock control register (PCC) and system clock control register (SCC). Figures 2-1 and 2-2 show the formats of PCC and SCC, respectively.

Address Symbol FB3H PCC2 PCC1 PCC0 PCC3 **PCC** CPU clock selection bit (where fx = 6.0 MHz) SCC3, SCC0 = 00 SCC3, SCC0 = 01 or 11 ( ) indicates fx = 6.0 MHz( ) indicates fxT = 32.768 kHz CPU clock One machine CPU clock One machine frequency cycle frequency cycle 0 0  $\Phi = fx/64 (93.7 \text{ kHz})$  $\Phi = fxT/4 (8.192 \text{ kHz})$  $10.7 \,\mu s$ 122 µs 0 1  $\Phi = fx/16 (375 \text{ kHz})$  $2.67 \,\mu s$ 1 0  $\Phi = fx/8 (750 \text{ kHz})$  $1.33 \, \mu s$  $\Phi = fx/4 (1.5 MHz)$  $0.67 \, \mu s$ (where fx = 4.19 MHz) SCC3, SCC0 = 01 or 11 SCC3, SCC0 = 00( ) indicates fxt = 32.768 kHz ( ) indicates fx = 4.19 MHz CPU clock One machine CPU clock One machine frequency cycle frequency cycle 0  $\Phi = fx/64 (65.5 \text{ kHz})$  $\Phi = fx\tau/4 (8.192 \text{ kHz})$  $15.3 \,\mu s$ 122 us 0 1  $\Phi = fx/16 (261.8 \text{ kHz})$  $3.82 \,\mu s$  $\Phi = fx/8 (524 \text{ kHz})$ 1 0  $1.91 \,\mu s$  $\Phi = fx/4 (1.05 \text{ MHz})$  $0.95 \,\mu s$ Remarks 1. fx: Main system clock oscillator output frequency 2. fxr. Subsystem clock oscillator output frequency CPU operation mode control bit 0 Normal operation mode 0 1 HALT mode STOP mode 1 0 1 Setting prohibited

Figure 2-1. Processor Clock Control Register Format

Figure 2-2. System Clock Control Register Format

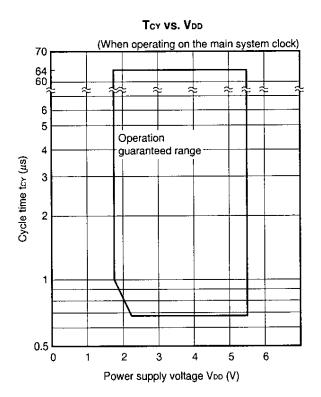

Figure 2-3 shows the minimum instruction execution time (tcv) v.s. power supply voltage (VDD).

Figure 2-3. Power Supply Voltage (VDD) v.s. Minimum Instruction Execution Time (tcv)

# 2.1 PCC Selection after RESET

When a RESET signal is generated, the lowest speed mode of the main system clock is selected as the CPU clock. Therefore, for high-speed operation, the CPU clock must be set to the highest speed mode by modifying the PCC. However, the Vpp pin voltage must reach a voltage at which the CPU can operate at the highest speed before the PCC is modified (refer to Figure 2-3). For a system which uses a subsystem clock, the oscillation of the subsystem clock must be confirmed in advance.

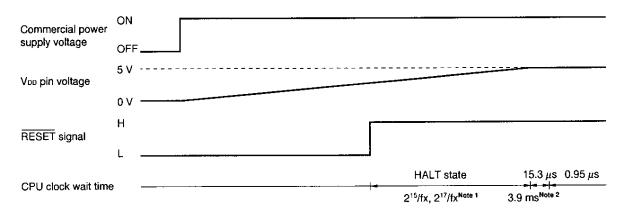

In the following program examples, the system waits until the  $V_{00}$  pin voltage rises and checks the subsystem clock oscillation using the clock timer; the CPU clock is then set to the highest speed mode (fx = 4.19 MHz, fxr = 32.768 kHz). Figure 2-4 shows the timing of this operation.

#### · Program example

#### (1) Wait until Vpp rises

|         | EXTRN   | BIT(SSCOKF)                             | ; Subsystem clock oscillation check flag<br>(Initial value = 0) |

|---------|---------|-----------------------------------------|-----------------------------------------------------------------|

|         | VENT0   | MBE=0, RBE=0, START                     |                                                                 |

| ;;;;;;; | ;;;;;;; | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; |                                                                 |

| START   | CSEG    | INBLOCK                                 | ; Specifies allocation in 4K-byte blocks of program memory      |

|         | VOM     | XA,#00000110B                           | ; Clock timer advance mode                                      |

|         | VOM     | WM, XA                                  | ; (operates on the main system clock)                           |

| INILOP1 | :       |                                         |                                                                 |

|         | SKTCLR  | IRQW                                    | ; 3.9 ms wait <sup>Note</sup>                                   |

|         | BR      | INILOP1                                 |                                                                 |

|         | MOV     | A, #0010B                               | ; Drive current small                                           |

|         | MOV     | SOS,A                                   |                                                                 |

|         | MOV     | XA,#00000110B                           | ; Operates on the clock timer subsystem clock                   |

|         | MOV     | WM, XA                                  |                                                                 |

|         | MOV     | A,#0011B                                | ; Sets the CPU clock to the highest speed mode                  |

|         | MOV     | PCC, A                                  | ; Initialization processing follows                             |

Note This time depends on the hardware. Set the time relevant to each system.

# (2) Subsystem clock oscillation check subroutine (called by user processing)

| SSCCHK | CSEG   | INBLOCK       |                                                                                      |

|--------|--------|---------------|--------------------------------------------------------------------------------------|

|        | SKF    | SSCOKF        | ; If the subsystem clock oscillation has already been checked, nothing is performed. |

|        | RET    |               |                                                                                      |

|        | SKTCLR | IRQW          | ; Subsystem clock oscillation                                                        |

|        | RET    |               |                                                                                      |

|        | MOV    | XA,#00000100B | ; Clock timer normal operation mode                                                  |

|        | MOV    | WM,XA         |                                                                                      |

|        | SET1   | SSCOKF        | ; Subsystem clock oscillation check flag                                             |

|        | RET    |               |                                                                                      |

|        |        | END           |                                                                                      |

It takes approximately 1 second to stabilize the oscillation of the subsystem clock. Therefore, no wait (until the clock oscillation stabilizes) is executed in the initialization processing, and processing is performed in the main routine to check the subsystem clock oscillation. Then a flag is set to inform the other systems that subsystem clock oscillation has been initiated.

Figure 2-4. CPU Clock Selection after RESET

Notes 1. Can be selected by mask option.  $(2^{15}/fx = 7.81 \text{ ms}, 2^{17}/fx = 31.3 \text{ ms} \text{ at } 4.19 \text{ MHz operation}).$

2. This time depends on the hardware. Set the time relevant to each system.

# 2.2 System Clock Selection when Commercial Power Line Failure is Detected

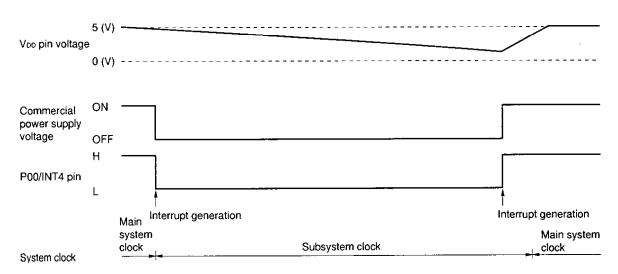

When the subsystem clock (32.768 kHz) is selected by the SCC, the  $\mu$ PD750008 can operate at very low power dissipation. Therefore, if a back-up power system such as a NiCd battery or super capacitor is provided on the system, clock count operation, etc, can be maintained at very low power dissipation in the event of power failure.

In the following program example, an interruption is detected in the commercial power line by external interrupt INT4, and the system clock is switched so as to operate at very low power.

The following describes the system clock selection procedure using Figures 2-5 and 2-6.

Figure 2-5. System Clock Selection when Commercial Power Supply is Turned ON/OFF

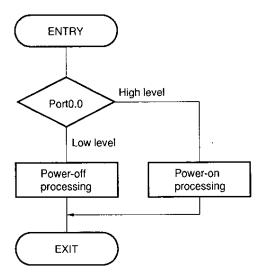

Figure 2-6. Algorithm of INT4 Interrupt Servicing

#### 2.2.1 Power-off processing

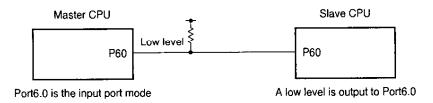

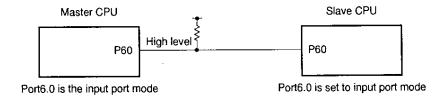

The Port0.0 is checked in INT4 interrupt servicing, and if the level is LOW, it is determined that the commercial power supply is off. Power-off processing is then initiated.

The following describes the power-off processing procedure.

- <1> Set 0011B to PCC.

- Set bit 0 of SCC to select the subsystem clock as the system clock.

All peripheral hardware except the clock timer and basic interval timer (which cannot be stopped) must be stopped before changing the system clock.

- <3> Set the input/output pins in a manner so that the power dissipation is minimized (See note).

- <4> More than 32 machine cycles after bit 0 of SCC is set, set bit 3 of SCC to stop the main system clock oscillation.

#### Caution Handling pins during power-off

When commercial power supply is turned off, normally, the power of the peripheral circuits is also turned off. Therefore, the following procedure is required using the connected peripheral circuits.

- 1. When a peripheral circuit connected to a pin becomes high impedance

- For the pin for which input/output can be selected, set to the output mode and output

a low level.

- · For the input pin, pull down or pull up in advance.

- 2. When the peripheral circuit connected to a pin does not become high impedance

- Output a level which creates no current.

- If the input pin is stable at high or low level, no special procedure is required.

Perform the necessary procedures depending on the condition of each peripheral circuit.

#### 2.2.2 Power-on processing

The Port0.0 is checked in INT4 interrupt servicing, and if the level is HIGH, it is determined that the commercial power supply is on. Power-on processing is then initiated. The following describes the power-on processing procedure.

- <1> Wait until the Vop pin voltage rises at the level that can be operated at highest speed.

- Clear bit 3 of SCC to initiate the main system clock oscillation.

- <3> Wait for a time period necessary for the main system clock to stabilize oscillation, then clear bit 0 of SCC to switch to the system clock.

#### 2.2.3 Power-on/off processing application

An example of a program using power-on/off processing is shown below.

This program is not used in CHAPTER 11 APPLICATION EXAMPLES OF THIS APPLICATION PROGRAM.

## (1) Program description

# <External reference declaration symbol>

SSCOKF: Subsystem clock oscillation check flag

INTD0 to 5: Interrupt-related initialize data

INDBTM: BTM initialization data

INTMO: TMO initialization data

INCSIM: CSIM initialization data

INWM: WM initialization data

WATCH : Clock count processing entry label

## <Registers used>

XA, HL

#### <Nesting>

4 levels (20 words)

#### <Initial setting>

INT4 interrupt enable

## <Start-up procedure>

#### (a) Power on/off

When started up by the INT4 interrupt, one of the following processes is performed depending on the status of Port0.0.

#### (i) When Port0.0 is high (power-on processing):

The main system clock is selected as the system clock and each peripheral device is started up.

#### (ii) When Port0.0 is low (power-off processing):

- If the subsystem clock is oscillating (SSCOKF:1), the peripheral devices (except for the clock timer and basic interval timer) are stopped. The subsystem clock is then selected as the system clock and the main system clock is stopped.

- If the subsystem clock is stopped (SSCOKF:0), the peripheral devices (except for the clock times and basic interval timer) are stopped.

# (b) Clock count check subroutine

When TIMCNT is called, the clock count processing routine (a user program) is called if the subsystem clock is oscillating. If the subsystem clock is not oscillating, the clock count processing routine is not called and processing returns to the point from where TIMCNT was called.

If the power is off (Port0.0 is low), the following processes are repeated until the power is turned on (Port0.0 is high):

- (i) HALT mode setting

- (ii) Recovery by IRQW

- (iii) Clock count processing routine call

#### (2) Program example

```

<INT4 interrupt servicing>

VENT1

MBE=0, RBE=0, INT4

EXTRN

NUMBER(INTD0,INTD1,INTD2,INTD3,INTD4,INTD5)

EXTRN

NUMBER (INDBTM, INTMO, INCSIM, INWM)

EXTRN

BIT(SSCOKF)

CODE (WATCH)

EXTRN

AN12DT1

DSEG

0

AT 0

ROA:

DS

1H

; A register

AN12DT

DSEG

0

AT ODOH

PTSVA:

DS

4

INT4

CSEG

INBLOCK

PUSH

BS

PUSH

XA

PUSH

HL

SEL

MB15

SKT

PORTO.0

; Port0.0 check

BR

POWOFF

CLR1

SCC.3

; Power-ON processing

MOV

XA, #56

:TIAWNO

DECS

; Wait until system clock oscillation stabilizes

Α

BR

ONWAIT

DECS

Χ

BR

ONWAIT

CLR1

SCC.0

; System clock selection

CALLF

! HRDSET

; Hardware restart subroutine

BR

REINT4

POWOFF:

SKT

SSCOKE

; Subsystem clock oscillation check

BR

$HSTPRO

MOV

A,#0011B

MOV

PCC, A

SET1

SCC.0

; System clock selection

HSTPRO:

MOV

XA,#0

; Hardware stop processing

MOV

TM0,XA

MOV

CSIM, XA

MOV

A,#0101B

SKF

SSCOKF

MOV

WM, XA

VOM

A,#8

; Disables interrupts other than INT4

VOM

0B8H,A

SET1

MBE

MOV

HL,#0BCH

VOM

A,#0

DILOP:

VOM

@HL,A

INCS

L

BR

DILOP

CLR1

\mathtt{MBE}

EI

IEW

```

```

; <Subroutine Input/output port processing>

SSCOKF

SKF

SET1

SCC.3

; Main system clock stop

REINT4:

POP

HL

POP

XA

POP

BS

RETI

; <Subroutine hardware restarts>

HRDSET

CSEG

SENT

; Hardware restart

MOV

A, #INDBTM

MOV

BTM, A

MOV

XA,#INTMO

MOV

TMO, XA

XA, #INCSIM

VOM

VOM

CSIM, XA

XA, #INWM

MOV

WM,XA

MOV

PORT RECOVER PROCESS

; Interrupt enable

A, #INTDO

MOV

MOV

0B8H, A

MOV

A, #INTD1

ROA.1

SKT

DI

IEW

A, #INTD2

VOM

OBCH, A

MOV

A, #INTD3

MOV

OBDH, A

MOV

VOM

A, #INTD4

OBEH, A

MOV

MOV

A, #INTD5

MOV

OBFH, A

RET

; <Subroutine clock count check>

CSEG

INBLOCK

TIMCNT

; Clock count is not performed during subsystem clock

SKF

SSCOKF

check

CALL

!WATCH

; Power down check

SKF

PORT0.0

RET

HALT

; Sets standby mode

NOP

```

BR

TIMCNT

#### CHAPTER 3 BASIC INTERVAL TIMER APPLICATIONS

# 3.1 Reference Time Generation

The  $\mu$ PD750008 has an 8-bit basic interval timer (BT). Four different intervals can be selected. The basic interval timer interrupt request flag (IRQBT) is set with this interval time.

The basic interval timer is controlled by the basic interval timer mode register (BTM). Figure. 3-1 shows the format of this register.

Address 3 2 Symbol F85H ВТМ3 BTM2 BTM1 BTM0 **BTM** (fx = 6.00 MHz)Interrupt interval time Input clock specification (Wait time when releasing the standby mode) 0 fx/212 (1.46 kHz) 220/fx (175 ms) 0 0 fx/29 (11.7 kHz) 0 1 1 217/fx (21.8 ms) 1 0 1 fx/27 (46.9 kHz) 215/fx (5.46 ms) 1 fx/25 (188 kHz) 213/fx (1.37 ms) 1 1 Setting prohibited Other than above (fx = 4.19 MHz)Interrupt interval time Input clock specification (Wait time when releasing the standby mode) 0 0 0 fx/212 (1.02 kHz) 2<sup>20</sup>/fx (250 ms) 0 1 1 fx/29 (8.18 kHz) 217/fx (31.3 ms) fx/27 (32.768 kHz) 1 0 215/fx (7.81 ms) 1 fx/25 (131 kHz) 213/fx (1.95 ms) Setting prohibited Other than above Basic interval timer start control bit Basic interval timer operation is started (the counter and interrupt request flag are cleared) when "1" is written to this bit. This bit is automatically reset to 0 when operation is started.

Figure 3-1. Basic Interval Timer Mode Register Format

The following shows four examples of interval time settings (at fx = 4.19 MHz operation).

(1) To set the interval time to 250 ms (IRQBT is set every 250 ms):

| SEL | MB15     |

|-----|----------|

| MOV | A,#1000B |

| MOV | BTM,A    |

(2) To set the interval time to 31.3 ms (IRQBT is set every 31.3 ms):

| SEL | MB15     |

|-----|----------|

| MOV | A,#1011B |

| MOV | BTM,A    |

(3) To set the interval time to 7.81 ms (IRQBT is set every 7.81 ms):

| SEL | MB15     |

|-----|----------|

| MOV | A,#1101B |

| MOV | BTM,A    |

(4) To set the interval time to 1.95 ms (IRQBT is set every 1.95 ms):

| SEL   | MB15     |

|-------|----------|

| الناد | FIDIO    |

| MOT   | x #1111n |

| MOV   | A,#1111B |

| MOV   | BTM,A    |

# 3.2 Watchdog Timer Application

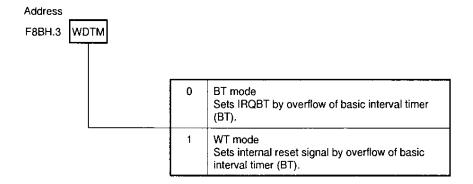

When "1" is set in the watchdog timer enable flag (WDTM), the basic interval timer/watchdog timer operates as a watchdog timer that generates an internal reset signal by overflow of the basic interval timer (BT) (however, once WDTM is set to "1", no operation but a reset can clear it). BT is always incremented by a clock from the clock generator, and cannot stop count operation (refer to Figure 3-2).

In watchdog timer mode, an inadvertent program loop is detected by using the interval time during which BT overflows. Four types of time are available for this interval time by setting BTM bits 2 to 0 (refer to **Figure 3-1**). Determine the time required for detection of any inadvertent program loop among these types according to the user system. After setting the interval time, divide the program into units by which the entire program can be executed within the time so that the instruction clearing BT at the end of each unit is executed. Thus, if the program does not reach the instruction clearing this BT within the set time (an inadvertent program loop will result if execution of the program does not proceed normally), BT will overflow, generating an internal reset signal which will forcibly end the program. As a result, the fact that the internal reset is executed means that an inadvertent program loop has occurred and that it has been successfully detected.

Set the watchdog timer according to the following procedure. (Settings in <1> and <2> can be performed simultaneously.)

```

<1> Set the interval time in BTM.

> Set "1" in BTM bit 3.

<3> Set "1" in WDTM.

<4> After setting <1> to <3>, set "1" in BTM bit 3 within the interval time.

```

Figure 3-2. Format of Watchdog Timer Enable Flag

# Example Used as a 7.81 ms watchdog timer (in 4.19 MHz operation)

The program is divided into several modules whose processing ends within the set time of BTM (7.81 ms) and BT is cleared at the end of each module. In the event of an inadvertent program loop, BT overflows because it has not been cleared within the set time, generating an internal reset signal.

Initial setting:

SET MBE

SEL MB15

MOV A.#1101B

MOV BTM.A ; Time setting and start

SET1 WDTM ; Enables watchdog timer.

:

(Subsequently, "1" is set in BTM bit 3 every 7.81 ms.)

| Module 1: | SET1<br>SEL<br>SET1 | MBE<br>MB15<br>BTM.3 | Processing completed within 7.81 ms |

|-----------|---------------------|----------------------|-------------------------------------|

| Module 2: | SET<br>SEL<br>SET1  | MBE<br>MB15<br>BTM.3 | Processing completed within 7.81 ms |

# 3.3 Remote Control Reception Application

This section introduces an example program which receives transmission data from the  $\mu$ PD6122 transmitter for the general-purpose infrared remote controller using the basic interval timer.

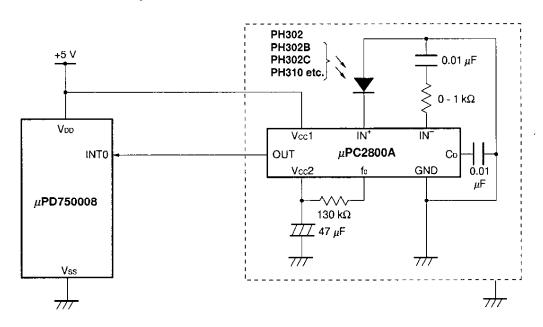

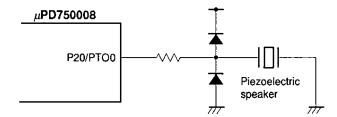

The remote control signal is received with the PIN photo diode, passed through the  $\mu$ PC2800A remote control preamplifier and input to the  $\mu$ PD750008 through the P10/INT0 pin. (Refer to **Figure 3-3**).

For this program, the edge-to-edge length of the remote control signal is counted using INTBT and coded.

Figure 3-3. Remote Control Receiver Circuit Example

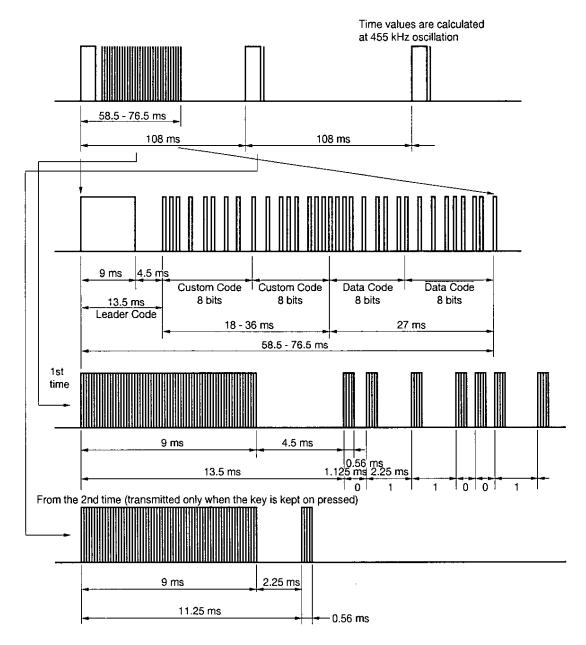

The remote control signal consists of the leader code, custom code, data code, and repeat code.

The remote control signal shown here conforms to that of NEC remote control signal. Figure 3-4 shows the format of the remote control signal.

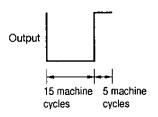

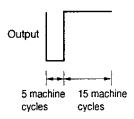

Figure 3-4. Remote Control Transmitter IC Output Signal

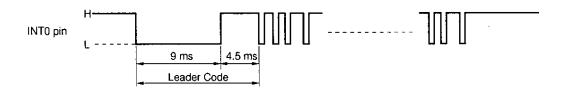

The out put from the  $\mu$ PC2800A remote control preamplifier is low, as shown in Figure 3-5 (a).

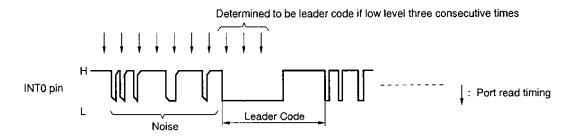

In actual operation, however, electrical noise sometimes appears before the leader code due to external light sources such as fluorescent lights. Therefore, this program confirms the falling edge of the leader code by reading the port level during the basic interval timer interrupt servicing. (Refer to **Figure 3-5 (b)**).

Figure 3-5. Receiver Preamplifier Output Waveform

#### (a) Ideal Wavefrom

#### (b) Actual Waveform

In the following (1) Explanation of program and (2) Flowchart, data recognized as normal by a remote control signal is expressed as "valid."

## (1) Explanation of program

The program explained here is the one used in **CHAPTER 11 APPLICATION EXAMPLES OF THIS APPLICATION PROGRAM** with some modifications to its input/output interface.

## <Registers used>

XA, B, HL

#### <RAM used>

RAM can be placed from address 20H of memory bank 0.

WORK: 2 words ; Work area to store received data RMDATA: 2 words ; Area to store valid data code LDCODE: 1 word ; Counts reader code low level time.

MODEP: 1 word ; Parameter to indicate which edge is being detected RPTIM: 1 word ; Counts time detected from valid data input (up to 200 ms)

RPCODE: 1 word ; Counts valid repeat code.

RMFLG: 1 word ; Stores flag.

REP\_F: 1 bit ; If 1, starts RPTIM count.

#### <Nesting>

2 levels (16 words)

#### <Hardware used>

Port: Port1.0 (used as INT0)

· Timer: Basic interval timer

### <Interrupts used>

INTO and INTBT

#### <Initial setting>

- · RAM initial setting

- · Hardware initial setting

- · INTBT interrupt enabled

## <Start-up procedure>

- · Started by executing initial setting processing (RMT:).

- If a valid remote control code is input, REP\_F = 1 is set, and the code is stored in RMDATA. Then, if no repeat code is input in 200 ms (it is judged that the remote control key has been released) or if a repeat code is input four times or more (it is judged that a remote control signal for 2 or more machines has been received) REP\_F = 0 is set.

- While the system waits for reception of a remote control code, MODEP = 0 is set.

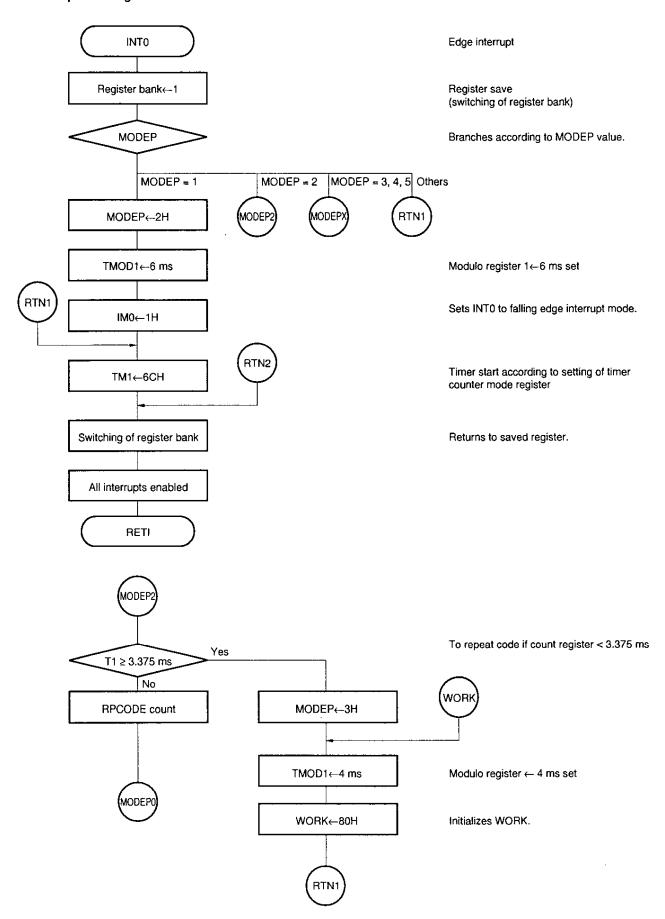

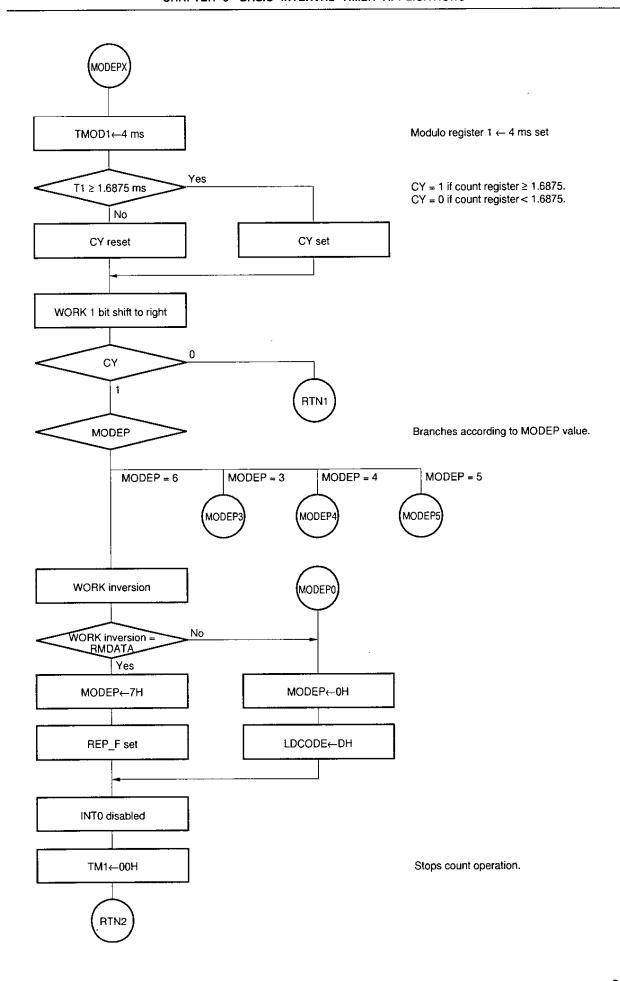

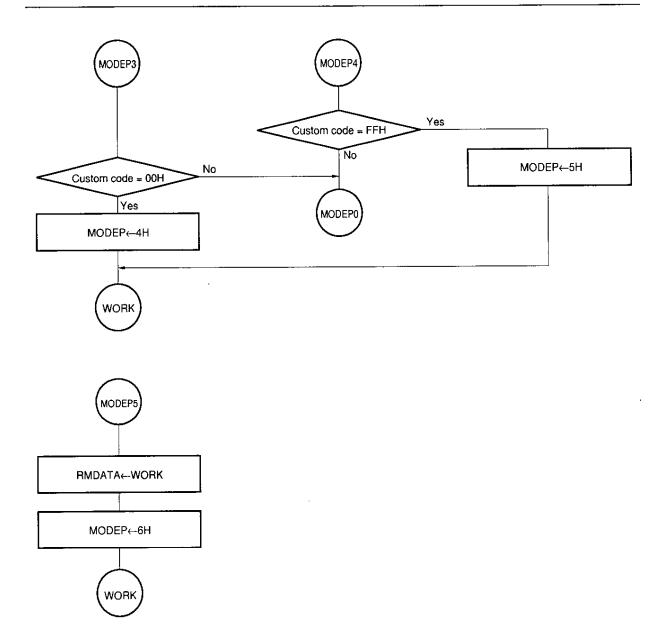

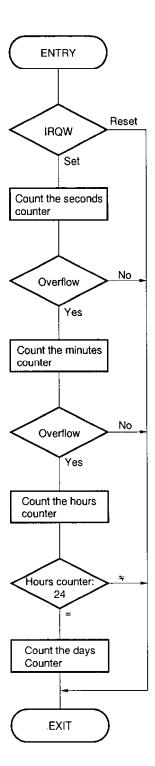

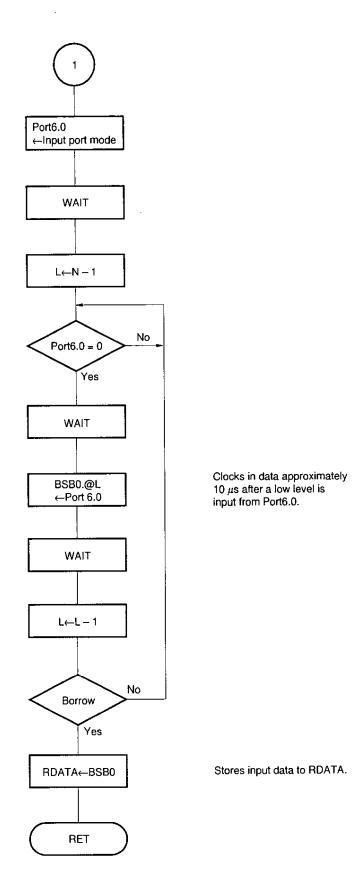

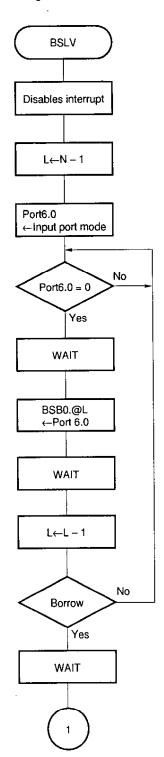

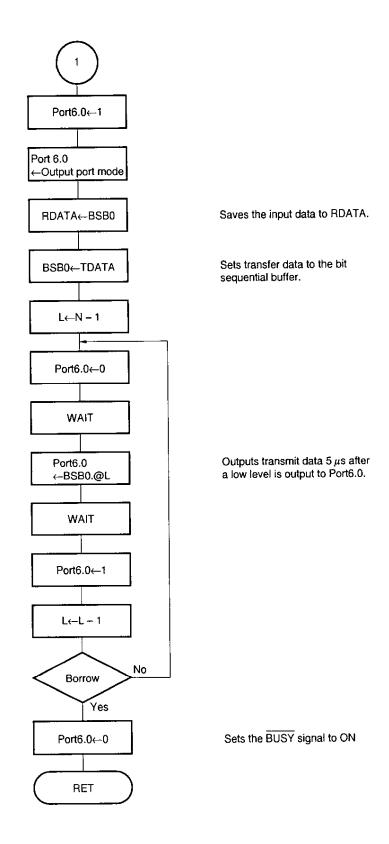

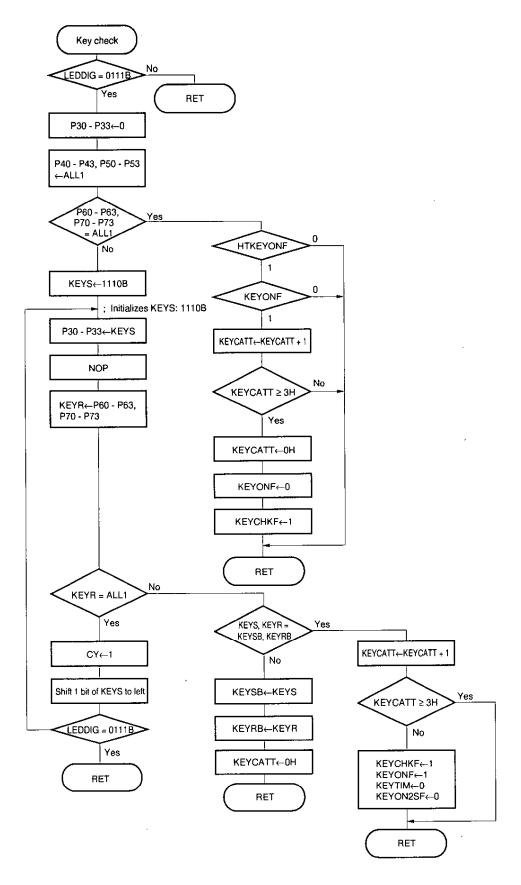

# (2) Flowchart

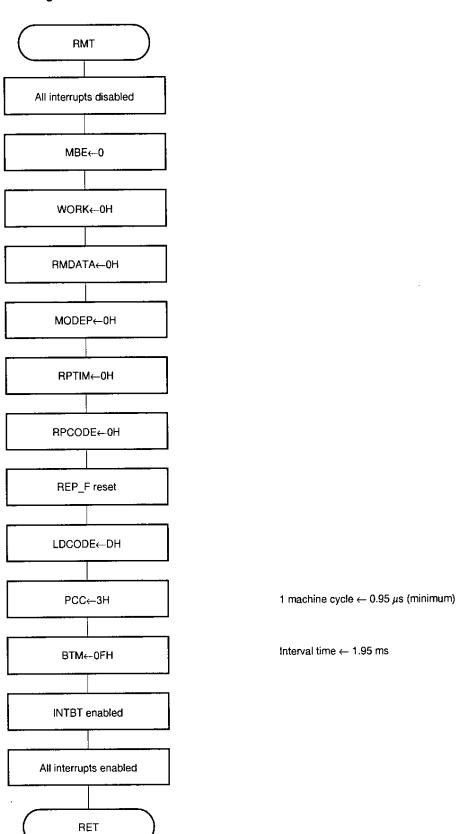

# Initial setting

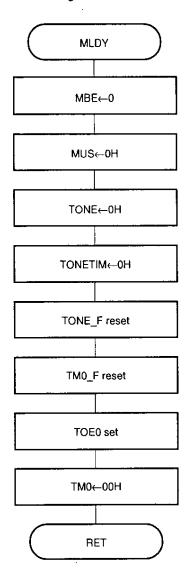

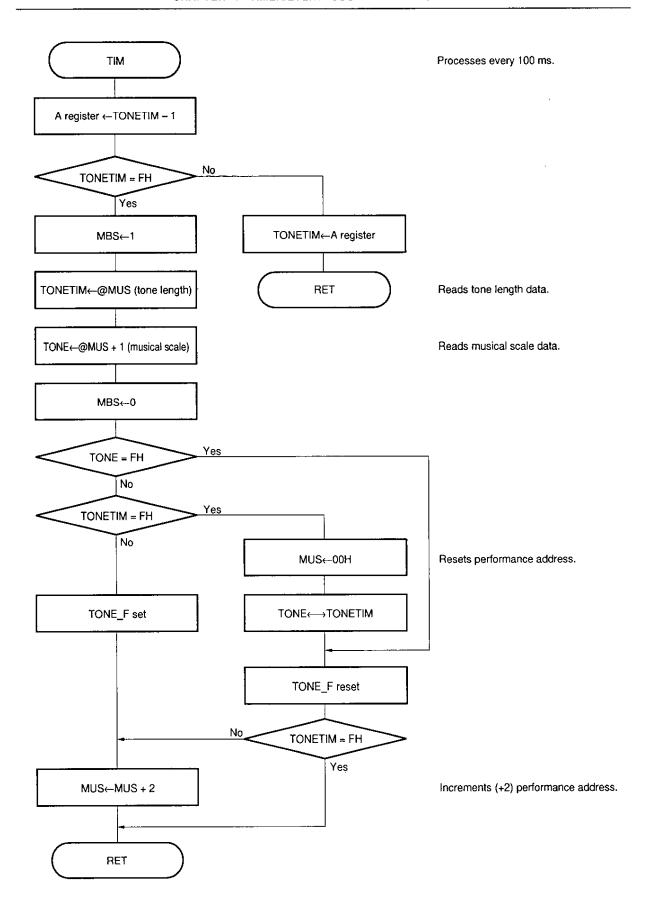

Processes every 100 ms.

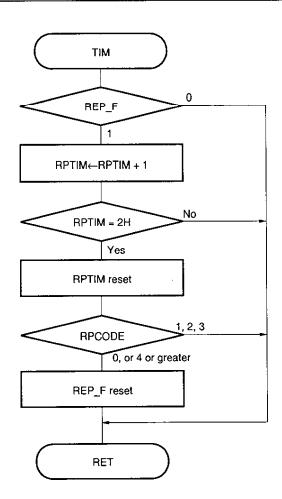

Checks if 200 ms have elapsed.

Checks number of times of repeat code.

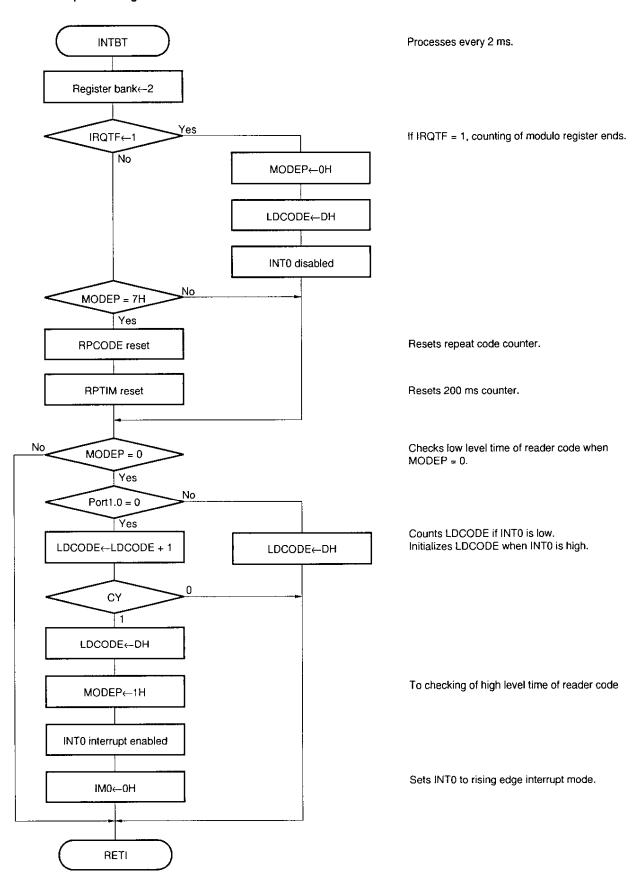

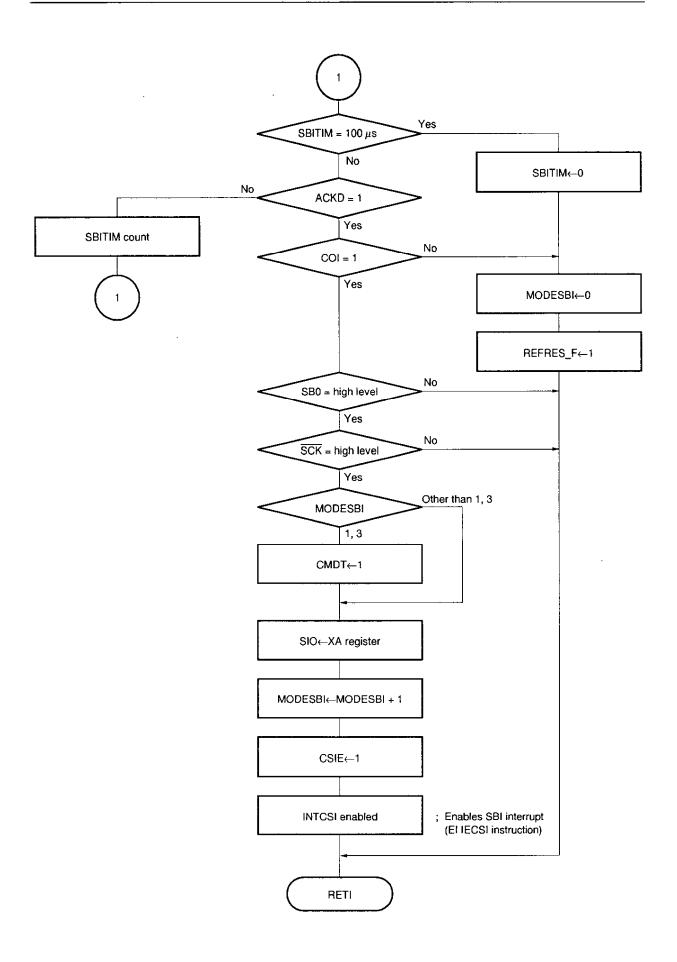

# **INTBT** processing

# **INTO processing**