Renesas Synergy™ Platform

# S3A7 MCU Safety Application Note

r11an0191eu0100 Rev.1.00 June 29, 2017

# Introduction

IEC 61508 is an international standard governing a range of electrical, electromechanical, and electronic safety related systems. It defines the requirements needed to ensure that systems are designed, implemented, operated, and maintained at the required Safety Integrity Level (SIL). Four SIL levels have been defined to indicate the risks involved in any particular system, with SIL4 being the highest risk level.

At the heart of the majority of safety related systems nowadays is a sophisticated and often highly integrated Microcontroller (MCU). An integral part of meeting the requirements of IEC61508 is the ability to verify the correct operation of critical areas of the MCU.

The purpose of this document is to provide guidelines to use the Renesas S3A7 Series MCUs within a safety context.

# **Target Device**

S3A7 MCUs

### Contents

| 1. | Comm   | on Terminology                                     | 5  |

|----|--------|----------------------------------------------------|----|

|    | 1.1 A  | kcronyms                                           | 5  |

|    | 1.2 C  | Document References                                | 6  |

| 2. | Consid | erations of External Protections                   | 7  |

|    | 2.1 E  | xternal Watchdog                                   | 7  |

| 3. | Hardwa | are (HW) Module Recommended Settings/ Usage        | 8  |

|    | 3.1 F  | Processing Module                                  | 8  |

|    | 3.1.1  | CPU                                                | 8  |

|    | 3.2 C  | Data I/O Modules                                   | 9  |

|    | 3.2.1  | I/O Ports                                          | 9  |

|    | 3.2.2  | 14-Bit A/D Converter (ADC14)                       | 10 |

|    | 3.2.3  | 12-Bit D/A Converter (DAC12)                       | 12 |

|    | 3.2.4  | Temperature Sensor (TSN)                           | 14 |

|    | 3.2.5  | High-Speed Analog Comparator (ACMPHS)              | 16 |

|    | 3.2.6  | Operational Amplifier (OPAMP)                      | 17 |

|    | 3.2.7  | Low-Power Analog Comparator (ACMPLP)               | 17 |

|    | 3.3 F  | Protection against HW faults                       | 19 |

|    | 3.3.1  | Low Voltage Detection Circuit (LVD)                | 19 |

|    | 3.3.2  | Clock Frequency Accuracy Measurement Circuit (CAC) | 20 |

|    | 3.3.3  | Port Output Enable Module for GPT (POEG)           | 21 |

|    | 3.3.4  | Independent Watchdog Timer (IWDT)                  | 22 |

|    | 3.3.5  | Battery Backup Function                            | 23 |

|    | 3.3.6  | Parity check                                       | 24 |

|    | 3.3.7  | ECC                                                | 24 |

| 3.4 Pi | otections against SW faults                  | . 26 |

|--------|----------------------------------------------|------|

| 3.4.1  | Memory Protection Unit (MPU)                 | . 26 |

| 3.4.2  | Watchdog Timer (WDT)                         | . 29 |

| 3.5 C  | ommunication Module(s)                       | . 31 |

| 3.5.1  | Buses                                        | . 31 |

| 3.5.2  | USB 2.0 Full-Speed Module (USBFS)            | . 33 |

| 3.5.3  | Serial Communication Interface (SCI)         | . 34 |

| 3.5.4  | IrDA Interface                               | . 35 |

| 3.5.5  | I <sup>2</sup> C Bus Interface (IIC)         | . 36 |

| 3.5.6  | Control Area Network Module (CAN)            | . 38 |

| 3.5.7  | Serial Peripheral Interface (SPI)            | . 39 |

| 3.5.8  | Quad Serial Peripheral Interface (QSPI)      | . 40 |

| 3.5.9  | Serial Sound Interface (SSI)                 | . 41 |

| 3.5.10 | Secure Digital Host Interface (SDHI)         | . 42 |

| 3.5.11 | Multi Media Card (MMC)                       | . 43 |

| 3.6 In | ternal interaction module(s)                 | . 44 |

| 3.6.1  | Interrupt Controller (ICU)                   | . 44 |

| 3.6.2  | Event Link Controller (ELC)                  | . 45 |

| 3.7 S  | ync module(s)                                | . 46 |

| 3.7.1  | General PWM Timer (GPT)                      | . 46 |

| 3.7.2  | Asynchronous General Purpose Timer (AGT)     | . 49 |

| 3.7.3  | Realtime Clock (RTC)                         | . 51 |

| 3.8 D  | ata management module(s)                     | . 52 |

| 3.8.1  | DMA Controller (DMAC)                        | . 52 |

| 3.8.2  | Data Transfer Controller (DTC)               | . 53 |

| 3.8.3  | CRC Calculator (CRC)                         | . 55 |

| 3.8.4  | Data Operation Circuit (DOC)                 | . 55 |

| 3.9 M  | emory                                        | . 57 |

| 3.9.1  | SRAM                                         | . 57 |

| 3.9.2  | Flash Memory                                 | . 59 |

| 3.9.3  | Memory Mirror Function (MMF)                 | . 60 |

| 3.10 S | ystem Support Module(s)                      | . 61 |

| 3.10.1 | Resets                                       | . 61 |

| 3.10.2 | Option-Setting Memory and Information Memory | . 62 |

| 3.10.3 | Clock Generation Circuit                     | . 63 |

| 3.10.4 | Low Power Mode                               | . 65 |

| 3.10.5 | Register Write Protection                    | . 67 |

| 3.10.6 | Boundary Scan                                | . 67 |

| 3.10.7 | Linear Regulator (LDO)                       | . 68 |

| 3.11 H | uman Machine Interface                       | . 69 |

| 3.11.1 | Key Interrupt Function (KINT)                | . 69 |

|    | 3.11.2 | Segment LCD Controller/Driver (SLCDC) | . 70 |

|----|--------|---------------------------------------|------|

|    | 3.11.3 | Capacitive Touch Sensing Unit (CTSU)  | . 70 |

| 4. | Safety | Mechanisms Description                | .71  |

|    | 4.1 C  | hip level Safety Mechanisms           | .71  |

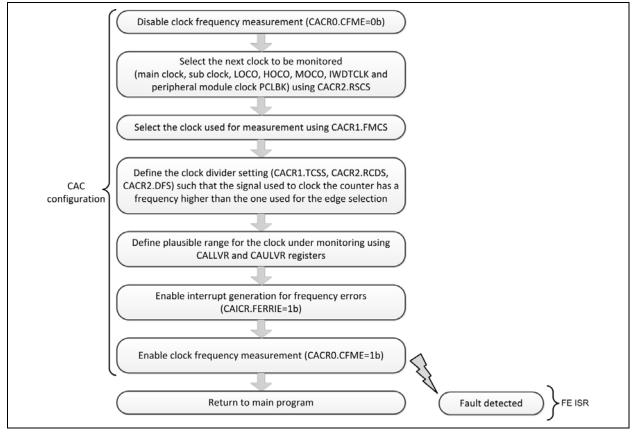

|    | 4.1.1  | CAC_self_test                         | .71  |

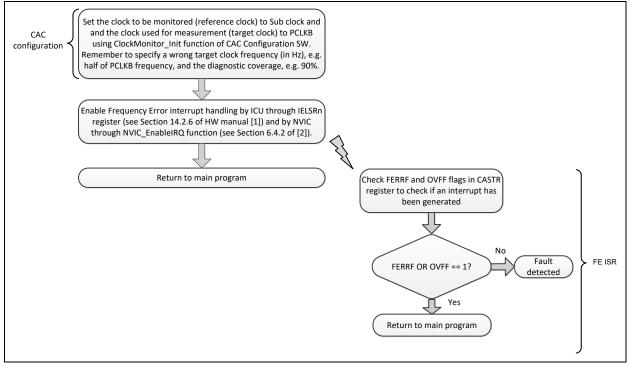

|    | 4.1.2  | CGC_clk_monitor                       | . 72 |

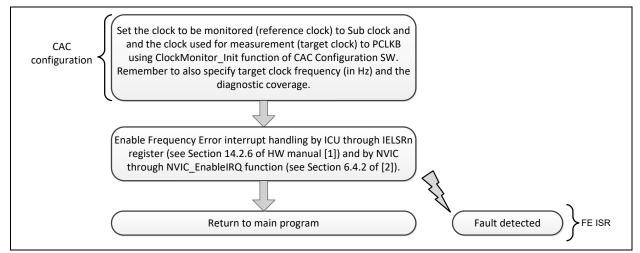

|    | 4.1.3  | CGC_clk_monitor_run_time              | . 73 |

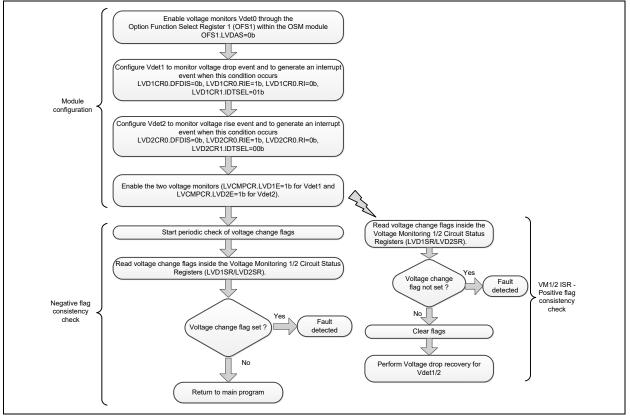

|    | 4.1.4  | LVD_Monitoring                        | . 74 |

|    | 4.1.5  | CGC_ClkStop                           | . 75 |

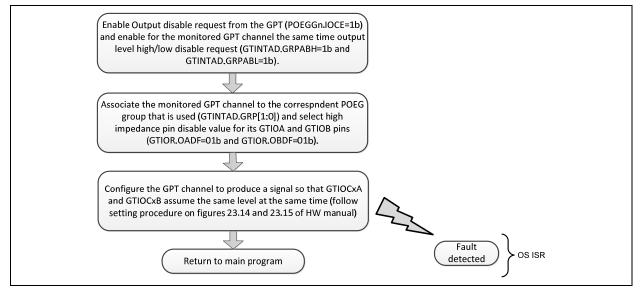

|    | 4.1.6  | PWM_short_monitor                     | . 75 |

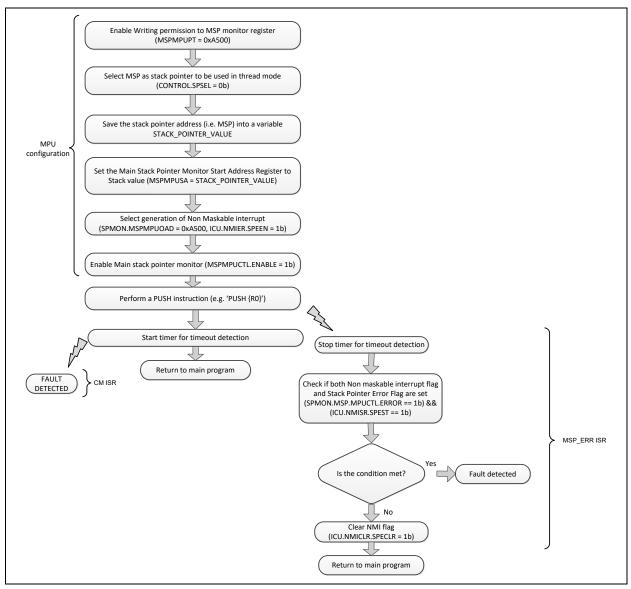

|    | 4.1.7  | MSPMPU_monitor                        | . 76 |

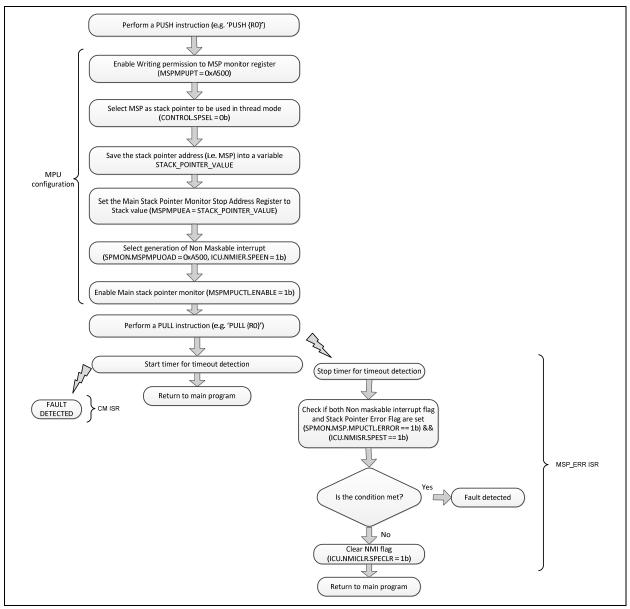

|    | 4.1.8  | PSPMPU_monitor                        | . 77 |

|    | 4.2 N  | lodule level Safety Mechanisms        | . 78 |

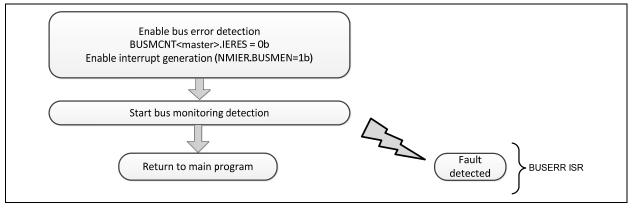

|    | 4.2.1  | BSC_Monitoring                        | . 78 |

|    | 4.3 S  | W level Safety Mechanisms             | . 78 |

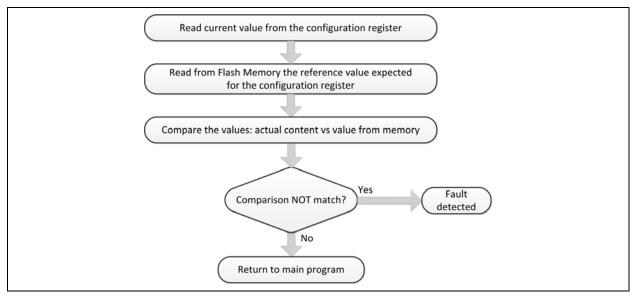

|    | 4.3.1  | Config_reg_read_back                  | . 78 |

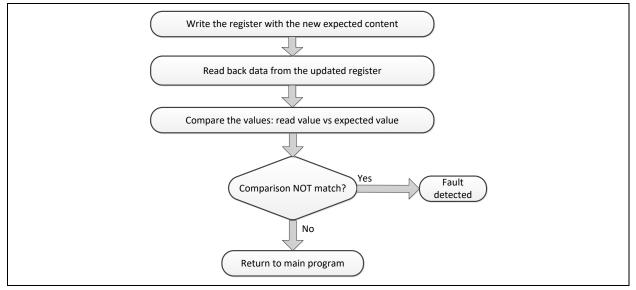

|    | 4.3.2  | Write_verify                          | . 79 |

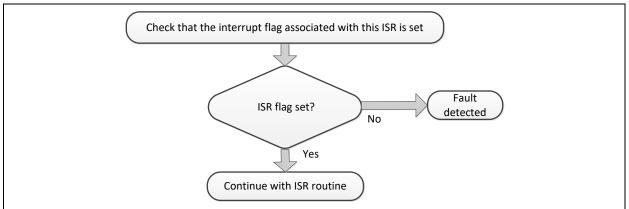

|    | 4.3.3  | ICU_int_source_check                  | . 79 |

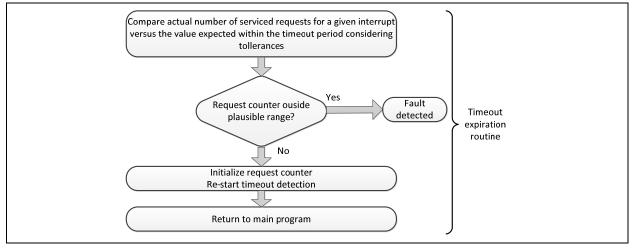

|    | 4.3.4  | ICU_int_count                         | . 80 |

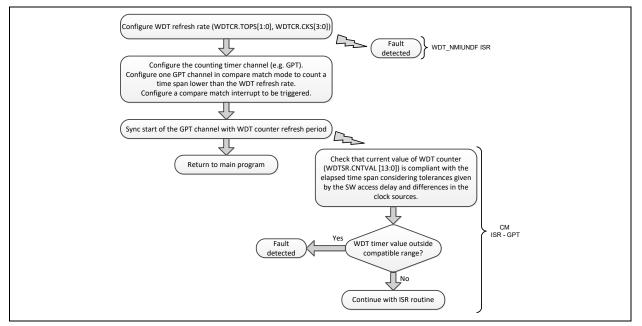

|    | 4.3.5  | WDT_Counter_Monitoring                | . 81 |

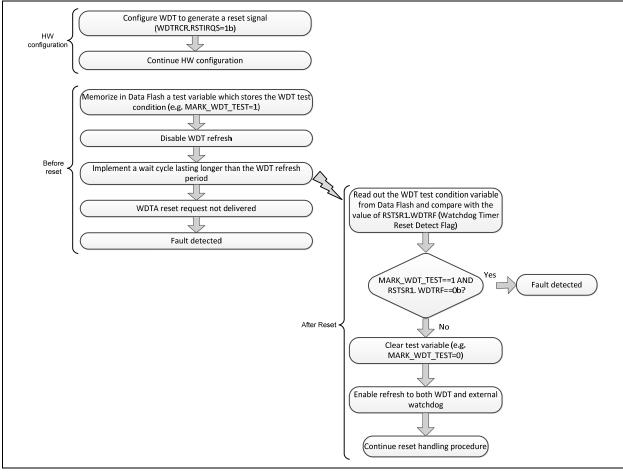

|    | 4.3.6  | WDT_Expire                            | . 82 |

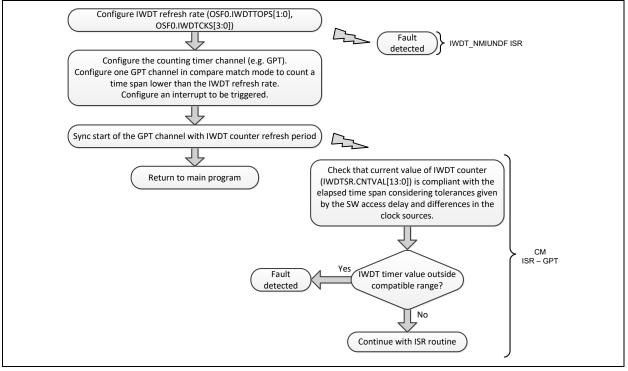

|    | 4.3.7  | IWDT_Clock_Monitoring                 | . 83 |

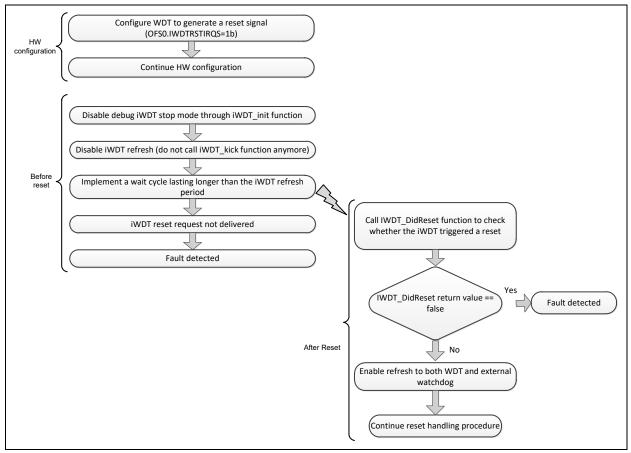

|    | 4.3.8  | IWDT_Expire                           | . 84 |

|    | 4.3.9  | CPU_SW_Test                           | . 84 |

|    | 4.3.10 | SRAM_SWTest                           | . 84 |

|    | 4.3.11 | FlashMemory_Crc                       | . 85 |

|    | 4.3.12 | MMF_Crc                               | . 85 |

|    | 4.3.13 | SW_reset_check                        | . 85 |

|    | 4.3.14 | CRC_SwCrc                             | . 86 |

|    | 4.3.15 | ADC14_TriggerDMA                      | . 87 |

|    | 4.3.16 | ADC14_Comparator_SW                   | . 88 |

|    | 4.3.17 | ADC14_TempSens                        | . 89 |

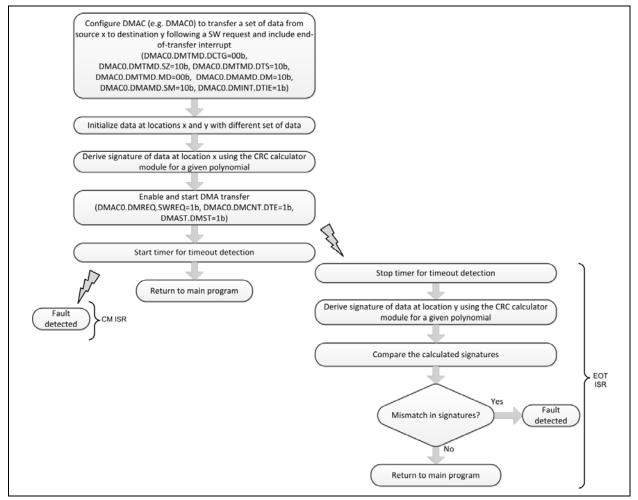

|    | 4.3.18 | GPT_DMAC_connection                   | . 91 |

|    | 4.3.19 | GPT_DTC_connection                    | . 92 |

|    | 4.3.20 | GPT_INT_generation                    | . 92 |

|    | 4.3.21 | GPT_sync_chan                         | . 93 |

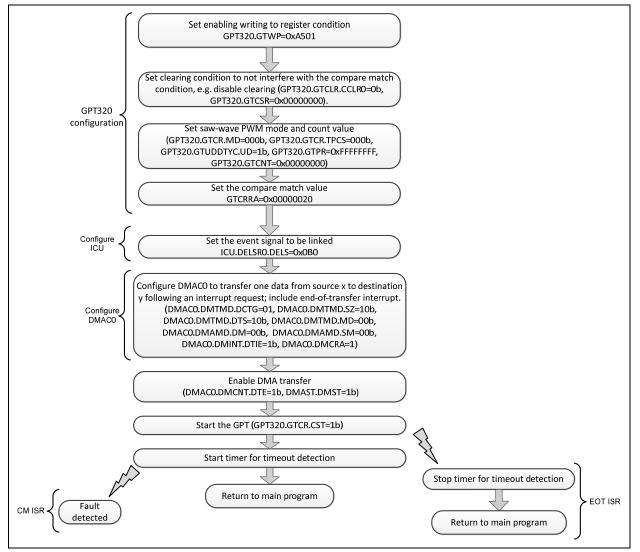

|    | 4.3.22 | AGT_GPT_freq_check                    | . 94 |

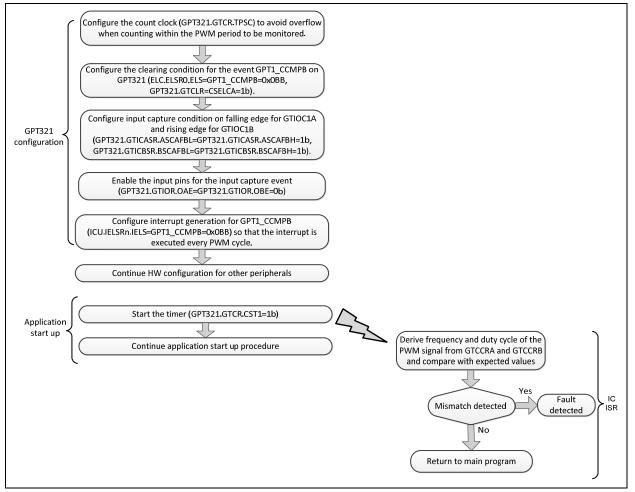

|    | 4.3.23 | GPT_redund_chan_input_capt            | . 96 |

|    | 4.3.24 | AGT_TriggerDTC                        | . 96 |

|    | 4.3.25 | AGT_TriggerDMAC                       | . 96 |

| 4.3.26 | AGT_TriggerADC                | 96  |

|--------|-------------------------------|-----|

| 4.3.27 | AGT_sync_chan                 | 96  |

| 4.3.28 | AGT_INT_generation            | 96  |

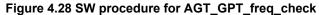

| 4.3.29 | DMAC_Crc                      | 97  |

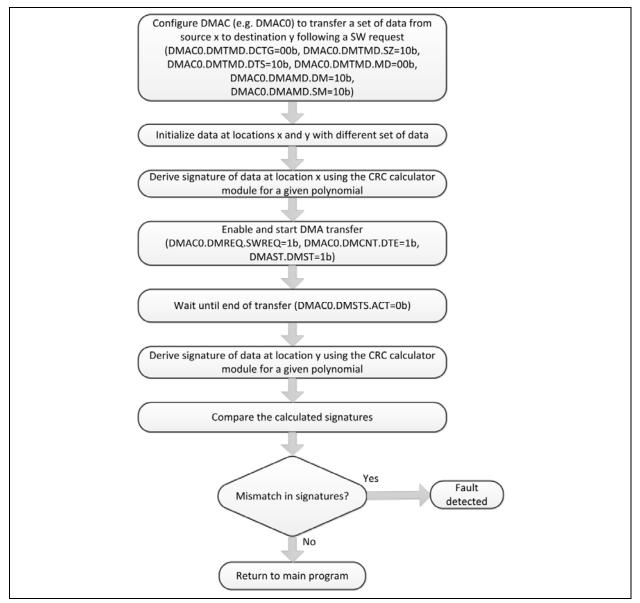

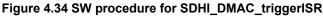

| 4.3.30 | DMAC_TriggerISR               | 99  |

| 4.3.31 | DTC_Crc                       | 100 |

| 4.3.32 | DTC_TriggerISR                | 100 |

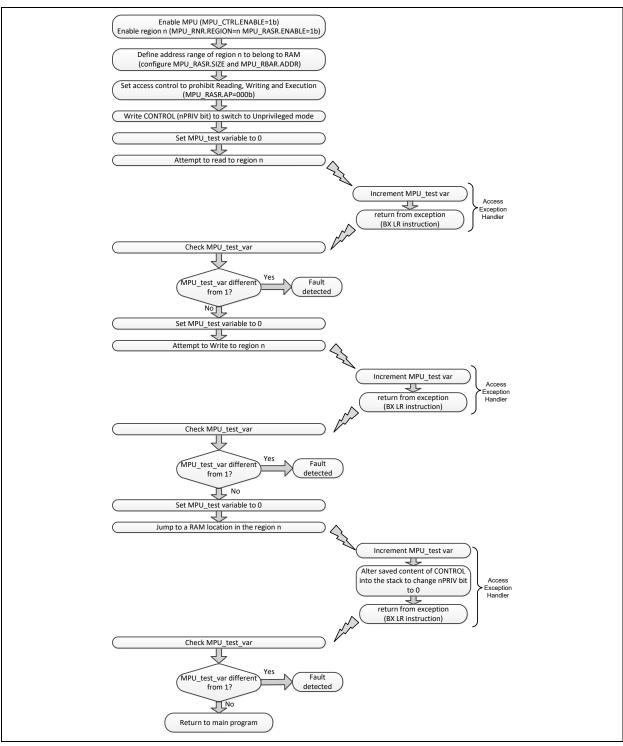

| 4.3.33 | MPU_region_check              | 100 |

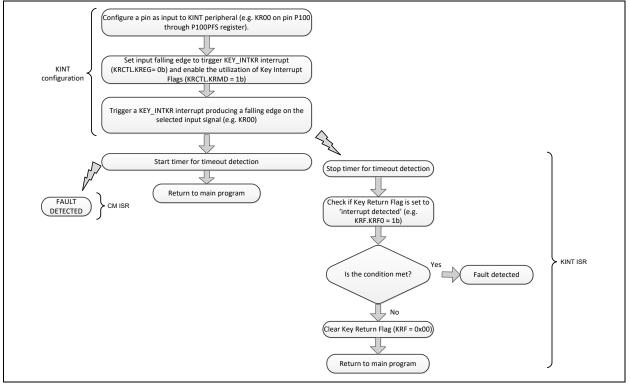

| 4.3.34 | KINT_triggerISR               | 102 |

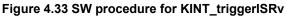

| 4.3.35 | SDHI_DMAC_triggerISR          | 103 |

| 4.3.36 | ACMPHS_triggerISR             | 104 |

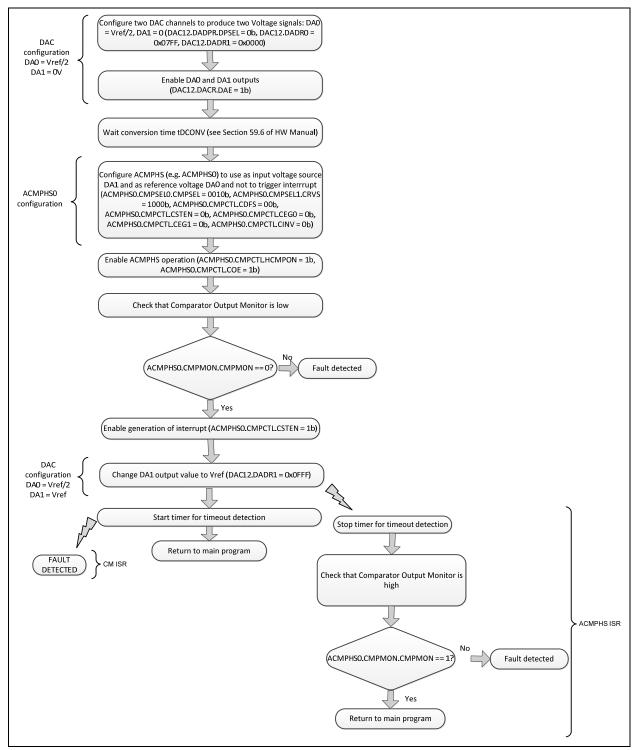

| 4.3.37 | DOC_check                     | 105 |

| 4.4 Sy | ystem Level Safety Mechanisms | 108 |

| 4.4.1  | BatteryBckp_check             | 108 |

| 4.4.2  | GPIO_in_redundancy            | 108 |

| 4.4.3  | GPIO_out_redundancy           | 108 |

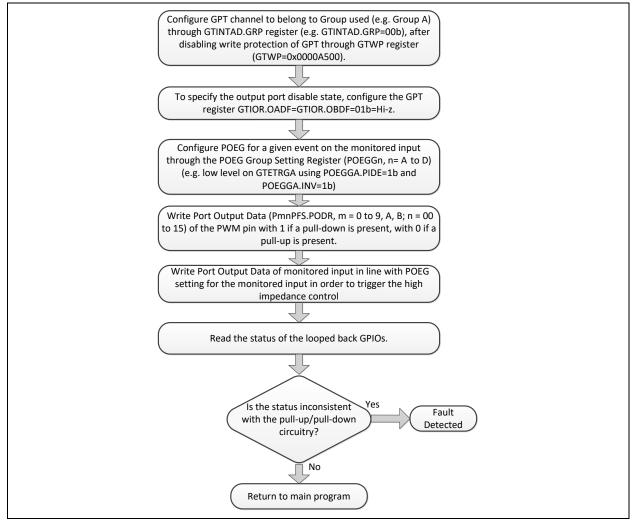

| 4.4.4  | POEG_ExtLoop                  | 109 |

| 4.4.5  | EndToEnd                      | 110 |

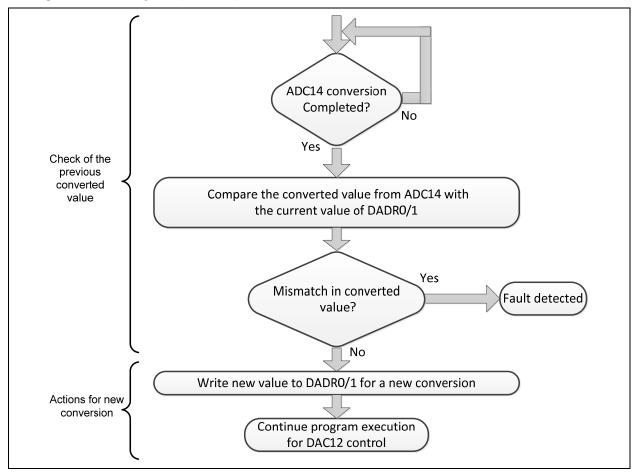

| 4.4.6  | DAC12_Loop_ADC14              | 111 |

| 4.4.7  | DAC12_system_redundancy       | 111 |

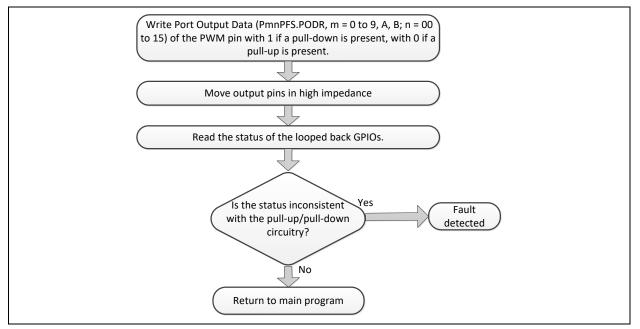

| 4.4.8  | GPT_chan_loop_back            | 112 |

| 4.4.9  | GPT_loop_back_AGT             | 112 |

| 4.4.10 | DMAC_ExtTrigger               | 113 |

| 4.4.11 | Ext_TempSens                  | 113 |

| 4.4.12 | LVD_check                     | 113 |

| 4.4.13 | SSI_check                     | 115 |

| 4.4.14 | SDHI_information_redundancy   | 115 |

| 4.4.15 | LDO_ext_monitoring            | 115 |

| 4.4.16 | ACMPLP_triggerISR             | 115 |

| 4.4.17 | ACMPLP_win_triggerISR         | 116 |

# 1. Common Terminology

This section defines some common terms and acronyms used throughout the rest of the document and provides references to other Renesas complementary documents.

### 1.1 Acronyms

# Table 1.1 Terminology and acronyms

| ADC       Analog to Digital Converter         BUSERR       Bus Error         CAN       Control Area Network         CRC       Cyclic Redundancy Check         CM       Compare Match         DAC       Digital to Analog Converter         DRW       Drawing Engine         E2E       End To End         ECC       Error Correction Code         EOC       End of Conversion         EOT       End of Conversion         GPT       General PWM Timer         HOCO       High speed On Chip Oscillator         IC       Input Capture         IrDA       Infrared Data Association         ISR       Interrupt Service Routine         IWDT       Independent Watchdog Timer         KINT       Key Interrupt Function         LOCO       Low-speed On-chip Oscillator         MMC       Multi Media Card         MOCO       Middle-speed On-chip Oscillator         MPU       Memory Protection Unit         NSR       Non Safety Relevant         OS       Output Short         PST       Process Safety Time         PTP       Precision Time Protocol         PWM       Pulse Width Modulation         Q&A<                            | Acronym | Description                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------|

| BUSERR       Bus Error         CAN       Control Area Network         CRC       Cyclic Redundancy Check         CM       Compare Match         DAC       Digital to Analog Converter         DRW       Drawing Engine         E2E       End To End         ECC       Error Correction Code         EOC       End of Conversion         EOT       End of Transfer         GPT       General PWM Timer         HOCO       High speed On Chip Oscillator         IC       Input Capture         IVDA       Infrared Data Association         ISR       Interrupt Service Routine         IWDT       Independent Watchdog Timer         KINT       Key Interrupt Function         LOCO       Low-speed On-chip Oscillator         MMC       Multi Media Card         MMCC       Midle-speed On-chip Oscillator         MPU       Memory Protection Unit         NSR       Non Safety Relevant         OS       Output Short         PST       Process Safety Time         PTP       Precision Time Protocol         PWM       Pulse Width Modulation         Q&A       Question and Answer         QSCI                                       |         |                                      |

| CAN       Control Area Network         CRC       Cyclic Redundancy Check         CM       Compare Match         DAC       Digital to Analog Converter         DRW       Drawing Engine         E2E       End To End         ECC       Error Correction Code         EOC       End of Conversion         EOT       End of Transfer         GPT       General PWM Timer         HOCO       High speed On Chip Oscillator         IC       Input Capture         IrDA       Infrared Data Association         ISR       Interrupt Service Routine         IWDT       Independent Watchdog Timer         KINT       Key Interrupt Function         LOCO       Low-speed On-chip Oscillator         MCCO       Mudtl Media Card         MOCO       Middle-speed On-chip Oscillator         MPU       Memory Protection Unit         NSR       Non Safety Relevant         OS       Output Short         PST       Process Safety Time         PTP       Precision Time Protocol         PWM       Pulse Width Modulation         Q&A       Question and Answer         QSCI       Quad Serial Communication Interface                          |         |                                      |

| CRC       Cyclic Redundancy Check         CM       Compare Match         DAC       Digital to Analog Converter         DRW       Drawing Engine         E2E       End To End         ECC       Error Correction Code         EOC       End of Conversion         EOT       End of Conversion         GPT       General PWM Timer         HOCO       High speed On Chip Oscillator         IC       Input Capture         IrDA       Infrared Data Association         ISR       Interrupt Service Routine         IWDT       Independent Watchdog Timer         KINT       Key Interrupt Function         LOCO       Low-speed On-chip Oscillator         MMC       Multi Media Card         MOCO       Middle-speed On-chip Oscillator         MPU       Memory Protection Unit         NSR       Non Safety Relevant         OS       Output Short         PST       Process Safety Time         PTP       Precision Time Protocol         PWM       Pulse Width Modulation         Q&A       Question and Answer         QSCI       Quad Serial Communication Interface         SIL       Safety Integrity Level      <                |         |                                      |

| CM       Compare Match         DAC       Digital to Analog Converter         DRW       Drawing Engine         E2E       End To End         ECC       Error Correction Code         EOC       End of Conversion         EOT       General PWM Timer         HOCO       High speed On Chip Oscillator         IC       Input Capture         IrDA       Infrared Data Association         ISR       Interrupt Service Routine         IWDT       Independent Watchdog Timer         KINT       Key Interrupt Function         LOCO       Low-speed On-chip Oscillator         MMC       Multi Media Card         MOCO       Middle-speed On-chip Oscillator         MPU       Memory Protection Unit         NSR       Non Safety Relevant         OS       Output Short         PST       Process Safety Time         PTP       Precision Time Protocol         PWM       Pulse Width Modulation         Q&A       Question and Answer         QSCI                                        |         |                                      |

| DACDigital to Analog ConverterDRWDrawing EngineE2EEnd To EndECCError Correction CodeEOCEnd of ConversionEOTEnd of TransferGPTGeneral PWM TimerHOCOHigh speed On Chip OscillatorICInput CaptureIrDAInfrared Data AssociationISRInterrupt Service RoutineIWDTIndependent Watchdog TimerKINTKey Interrupt FunctionLOCOLow-speed On-chip OscillatorMCCMulti Media CardMOCOMiddle-speed On-chip OscillatorMPUMemory Protection UnitNSRNon Safety RelevantOSOutput ShortPSTProcess Safety TimePTPPrecision Time ProtocolPWMPulse Width ModulationQ&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Peripheral InterfaceSILSafety MechanismSPISerial Communication InterfaceSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                            |         |                                      |

| DRW       Drawing Engine         E2E       End To End         ECC       Error Correction Code         EOC       End of Conversion         EOT       End of Transfer         GPT       General PWM Timer         HOCO       High speed On Chip Oscillator         IC       Input Capture         IrDA       Infrared Data Association         ISR       Interrupt Service Routine         IWDT       Independent Watchdog Timer         KINT       Key Interrupt Function         LOCO       Low-speed On-chip Oscillator         MMC       Multi Media Card         MMCCO       Middle-speed On-chip Oscillator         MPU       Memory Protection Unit         NSR       Non Safety Relevant         OS       Output Short         PST       Process Safety Time         PTP       Precision Time Protocol         PWM       Pulse Width Modulation         Q&A       Question and Answer         QSCI       Quad Serial Communication Interface         SIL       Safety Integrity Level         SM       Safety Mechanism         SPI       Serial Communication Interface         SRAM       Static Random Access Memory     <       |         |                                      |

| E2EEnd To EndECCError Correction CodeEOCEnd of ConversionEOTEnd of TransferGPTGeneral PVM TimerHOCOHigh speed On Chip OscillatorICInput CaptureIrDAInfrared Data AssociationISRInterrupt Service RoutineIWDTIndependent Watchdog TimerKINTKey Interrupt FunctionLOCOLow-speed On-chip OscillatorMMCMulti Media CardMOCOMiddle-speed On-chip OscillatorMPUMemory Protection UnitNSRNon Safety RelevantOSOutput ShortPSTProcess Safety TimePTPPrecision Time ProtocolPWMPulse Width ModulationQ&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSRSafety RelevantSMSafety RelevantSRAMStatic Random Access MemorySRAMStatic Random Access MemorySRCSampling Rate ConverterS                                                                                              |         |                                      |

| ECC       Error Correction Code         EOC       End of Conversion         EOT       End of Transfer         GPT       General PWM Timer         HOCO       High speed On Chip Oscillator         IC       Input Capture         IrDA       Infrared Data Association         ISR       Interrupt Service Routine         IWDT       Independent Watchdog Timer         KINT       Key Interrupt Function         LOCO       Low-speed On-chip Oscillator         MMC       Multi Media Card         MOCO       Middle-speed On-chip Oscillator         MPU       Memory Protection Unit         NSR       Non Safety Relevant         OS       Output Short         PST       Process Safety Time         PTP       Precision Time Protocol         PWM       Pulse Width Modulation         Q&A       Question and Answer         QSCI       Quad Serial Communication Interface         SM       Safety Integrity Level         SM       Safety Integrity Level         SM       Safety Relevant         SRAM       Static Random Access Memory         SRAM       Static Random Access Memory         SRC       Sampling Rate Conve  |         |                                      |

| EOC       End of Conversion         EOT       End of Transfer         GPT       General PWM Timer         HOCO       High speed On Chip Oscillator         IC       Input Capture         IDA       Infrared Data Association         ISR       Interrupt Capture         IWDT       Independent Watchdog Timer         KINT       Key Interrupt Function         LOCO       Low-speed On-chip Oscillator         MMC       Multi Media Card         MOCO       Middle-speed On-chip Oscillator         MPU       Memory Protection Unit         NSR       Non Safety Relevant         OS       Output Short         PST       Process Safety Time         PTP       Precision Time Protocol         PWM       Pulse Width Modulation         Q&A       Question and Answer         QSCI       Quad Serial Communication Interface         SIL       Safety Integrity Level         SM       Safety Mechanism         SPI       Serial Peripheral Interface         SR       Safety Relevant         SRC       Sampling Rate Converter         SSI       Serial Serial Bus         VM12       Voltage Monitoring 1/2                      |         |                                      |

| EOT       End of Transfer         GPT       General PWM Timer         HOCO       High speed On Chip Oscillator         IC       Input Capture         IrDA       Infrared Data Association         ISR       Interrupt Capture         IWDT       Independent Watchdog Timer         KINT       Key Interrupt Function         LOCO       Low-speed On-chip Oscillator         MMC       Multi Media Card         MOCO       Middle-speed On-chip Oscillator         MPU       Memory Protection Unit         NSR       Non Safety Relevant         OS       Output Short         PST       Process Safety Time         PTP       Precision Time Protocol         PWM       Pulse Width Modulation         Q&A       Question and Answer         QSCI       Quad Serial Communication Interface         RAM       Random Access Memory         SDHI       Secure Digital Host Interface (SDHI)         SCI       Serial Peripheral Interface         SR       Safety Mechanism         SPI       Serial Peripheral Interface         SR       Safety Relevant         SRC       Sampling Rate Converter         SSI       Serial Sound I  |         |                                      |

| GPT       General PWM Timer         HOCO       High speed On Chip Oscillator         IC       Input Capture         IrDA       Infrared Data Association         ISR       Interrupt Service Routine         IWDT       Independent Watchdog Timer         KINT       Key Interrupt Function         LOCO       Low-speed On-chip Oscillator         MMC       Multi Media Card         MOCO       Middle-speed On-chip Oscillator         MPU       Memory Protection Unit         NSR       Non Safety Relevant         OS       Output Short         PST       Process Safety Time         PTP       Precision Time Protocol         PWM       Pulse Width Modulation         Q&A       Question and Answer         QSCI       Quad Serial Communication Interface         RAM       Random Access Memory         SDHI       Secure Digital Host Interface (SDHI)         SCI       Serial Communication Interface         SR       Safety Integrity Level         SM       Safety Mechanism         SPI       Serial Peripheral Interface         SR       Safety Relevant         SRAM       Static Random Access Memory         SRC |         |                                      |

| HOCOHigh speed On Chip OscillatorICInput CaptureIrDAInfrared Data AssociationISRInterrupt Service RoutineIWDTIndependent Watchdog TimerKINTKey Interrupt FunctionLOCOLow-speed On-chip OscillatorMMCMulti Media CardMOCOMiddle-speed On-chip OscillatorMPUMemory Protection UnitNSRNon Safety RelevantOSOutput ShortPSTProcess Safety TimePTPPrecision Time ProtocolPWMPulse Width ModulationQ&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                     |         |                                      |

| IC       Input Capture         IrDA       Infrared Data Association         ISR       Interrupt Service Routine         IWDT       Independent Watchdog Timer         KINT       Key Interrupt Function         LOCO       Low-speed On-chip Oscillator         MMC       Multi Media Card         MOCO       Middle-speed On-chip Oscillator         MPU       Memory Protection Unit         NSR       Non Safety Relevant         OS       Output Short         PST       Process Safety Time         PTP       Precision Time Protocol         PWM       Pulse Width Modulation         Q&A       Question and Answer         QSCI       Quad Serial Communication Interface         RAM       Random Access Memory         SDHI       Secure Digital Host Interface (SDHI)         SCI       Serial Communication Interface         SIL       Safety Mechanism         SPI       Serial Peripheral Interface         SR       Safety Relevant         SRAM       Static Random Access Memory         SRC       Sampling Rate Converter         SR       Safety Relevant         SRAM       Static Random Access Memory         SRC   |         | High speed On Chip Oscillator        |

| IrDAInfrared Data AssociationISRInterrupt Service RoutineIWDTIndependent Watchdog TimerKINTKey Interrupt FunctionLOCOLow-speed On-chip OscillatorMMCMulti Media CardMOCOMiddle-speed On-chip OscillatorMPUMemory Protection UnitNSRNon Safety RelevantOSOutput ShortPSTProcess Safety TimePTPPrecision Time ProtocolPWMPulse Width ModulationQ&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety Integrity LevelSMSafety RelevantSRAMStatic Random Access MemorySPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                   |         |                                      |

| IWDT       Independent Watchdog Timer         KINT       Key Interrupt Function         LOCO       Low-speed On-chip Oscillator         MMC       Multi Media Card         MOCO       Middle-speed On-chip Oscillator         MPU       Memory Protection Unit         NSR       Non Safety Relevant         OS       Output Short         PST       Process Safety Time         PTP       Precision Time Protocol         PWM       Pulse Width Modulation         Q&A       Question and Answer         QSCI       Quad Serial Communication Interface         RAM       Random Access Memory         SDHI       Secure Digital Host Interface (SDHI)         SCI       Serial Communication Interface         SIL       Safety Integrity Level         SM       Safety Mechanism         SPI       Serial Peripheral Interface         SRAM       Static Random Access Memory         SRC       Sampling Rate Converter         SSI       Serial Sound Interface         USB       Universal Serial Bus         VM12       Voltage Monitoring 1/2         WDT       Watch Dog Timer                                                    | IrDA    |                                      |

| IWDT       Independent Watchdog Timer         KINT       Key Interrupt Function         LOCO       Low-speed On-chip Oscillator         MMC       Multi Media Card         MOCO       Middle-speed On-chip Oscillator         MPU       Memory Protection Unit         NSR       Non Safety Relevant         OS       Output Short         PST       Process Safety Time         PTP       Precision Time Protocol         PWM       Pulse Width Modulation         Q&A       Question and Answer         QSCI       Quad Serial Communication Interface         RAM       Random Access Memory         SDHI       Secure Digital Host Interface (SDHI)         SCI       Serial Communication Interface         SIL       Safety Integrity Level         SM       Safety Mechanism         SPI       Serial Peripheral Interface         SRAM       Static Random Access Memory         SRC       Sampling Rate Converter         SSI       Serial Sound Interface         USB       Universal Serial Bus         VM12       Voltage Monitoring 1/2         WDT       Watch Dog Timer                                                    | ISR     | Interrupt Service Routine            |

| KINTKey Interrupt FunctionLOCOLow-speed On-chip OscillatorMMCMulti Media CardMOCOMiddle-speed On-chip OscillatorMPUMemory Protection UnitNSRNon Safety RelevantOSOutput ShortPSTProcess Safety TimePTPPrecision Time ProtocolPWMPulse Width ModulationQ&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety MechanismSPISerial Peripheral InterfaceSRAMStatic Random Access MemorySBLSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                | IWDT    |                                      |

| LOCOLow-speed On-chip OscillatorMMCMulti Media CardMOCOMiddle-speed On-chip OscillatorMPUMemory Protection UnitNSRNon Safety RelevantOSOutput ShortPSTProcess Safety TimePTPPrecision Time ProtocolPWMPulse Width ModulationQ&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                                      |

| MMCMulti Media CardMOCOMiddle-speed On-chip OscillatorMPUMemory Protection UnitNSRNon Safety RelevantOSOutput ShortPSTProcess Safety TimePTPPrecision Time ProtocolPWMPulse Width ModulationQ&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety Integrity LevelSMSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                                      |

| MOCOMiddle-speed On-chip OscillatorMPUMemory Protection UnitNSRNon Safety RelevantOSOutput ShortPSTProcess Safety TimePTPPrecision Time ProtocolPWMPulse Width ModulationQ&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety Integrity LevelSMSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                                      |

| MPUMemory Protection UnitNSRNon Safety RelevantOSOutput ShortPSTProcess Safety TimePTPPrecision Time ProtocolPWMPulse Width ModulationQ&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety Integrity LevelSMSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                      |

| NSRNon Safety RelevantOSOutput ShortPSTProcess Safety TimePTPPrecision Time ProtocolPWMPulse Width ModulationQ&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety Integrity LevelSMSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                                      |

| OSOutput ShortPSTProcess Safety TimePTPPrecision Time ProtocolPWMPulse Width ModulationQ&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety Integrity LevelSMSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NSR     |                                      |

| PSTProcess Safety TimePTPPrecision Time ProtocolPWMPulse Width ModulationQ&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety Integrity LevelSMSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OS      |                                      |

| PTPPrecision Time ProtocolPWMPulse Width ModulationQ&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety Integrity LevelSMSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PST     |                                      |

| Q&AQuestion and AnswerQSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety Integrity LevelSMSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |                                      |

| QSCIQuad Serial Communication InterfaceRAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety Integrity LevelSMSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PWM     | Pulse Width Modulation               |

| RAMRandom Access MemorySDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety Integrity LevelSMSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q&A     | Question and Answer                  |

| SDHISecure Digital Host Interface (SDHI)SCISerial Communication InterfaceSILSafety Integrity LevelSMSafety MechanismSPISerial Peripheral InterfaceSRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | QSCI    | Quad Serial Communication Interface  |

| SCI       Serial Communication Interface         SIL       Safety Integrity Level         SM       Safety Mechanism         SPI       Serial Peripheral Interface         SR       Safety Relevant         SRAM       Static Random Access Memory         SRC       Sampling Rate Converter         SSI       Serial Sound Interface         USB       Universal Serial Bus         VM12       Voltage Monitoring 1/2         WDT       Watch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RAM     | Random Access Memory                 |

| SIL       Safety Integrity Level         SM       Safety Mechanism         SPI       Serial Peripheral Interface         SR       Safety Relevant         SRAM       Static Random Access Memory         SRC       Sampling Rate Converter         SSI       Serial Sound Interface         USB       Universal Serial Bus         VM12       Voltage Monitoring 1/2         WDT       Watch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SDHI    | Secure Digital Host Interface (SDHI) |

| SIL       Safety Integrity Level         SM       Safety Mechanism         SPI       Serial Peripheral Interface         SR       Safety Relevant         SRAM       Static Random Access Memory         SRC       Sampling Rate Converter         SSI       Serial Sound Interface         USB       Universal Serial Bus         VM12       Voltage Monitoring 1/2         WDT       Watch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SCI     |                                      |

| SPI       Serial Peripheral Interface         SR       Safety Relevant         SRAM       Static Random Access Memory         SRC       Sampling Rate Converter         SSI       Serial Sound Interface         USB       Universal Serial Bus         VM12       Voltage Monitoring 1/2         WDT       Watch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SIL     |                                      |

| SRSafety RelevantSRAMStatic Random Access MemorySRCSampling Rate ConverterSSISerial Sound InterfaceUSBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SM      | Safety Mechanism                     |

| SRAM       Static Random Access Memory         SRC       Sampling Rate Converter         SSI       Serial Sound Interface         USB       Universal Serial Bus         VM12       Voltage Monitoring 1/2         WDT       Watch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SPI     |                                      |

| SRAM       Static Random Access Memory         SRC       Sampling Rate Converter         SSI       Serial Sound Interface         USB       Universal Serial Bus         VM12       Voltage Monitoring 1/2         WDT       Watch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SR      |                                      |

| SSI       Serial Sound Interface         USB       Universal Serial Bus         VM12       Voltage Monitoring 1/2         WDT       Watch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SRAM    |                                      |

| SSI     Serial Sound Interface       USB     Universal Serial Bus       VM12     Voltage Monitoring 1/2       WDT     Watch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SRC     | Sampling Rate Converter              |

| USBUniversal Serial BusVM12Voltage Monitoring 1/2WDTWatch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                      |

| WDT Watch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                      |

| WDT Watch Dog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VM12    | Voltage Monitoring 1/2               |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | WDT     |                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |                                      |

# 1.2 Document References

- [1] User's Manual: Microcontrollers Renesas Synergy<sup>TM</sup> Family/S3 Series, Rev.1.2.

- [2] ARM<sup>®</sup> Cortex<sup>®</sup>-M4 Devices Generic User Guide, revision 16 December 2010.

- [3] S3 Series MCU Diagnostic Software User Guide, ID = r11an0188eu0100.

- [4] Diagnostic Software Safety Manual, ID= r11um0066eu0100.

# 2. Considerations of External Protections

Table 2.1 describes recommendations related to elements external to the MCU.

#### Table 2.1 Considerations for external protection

| ID    | Description                                                                                                                                                                                                                                   | Limitation/ Comment |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Ext_1 | It is recommended to use an external Watch Dog Timer (WDT). See section 2.1 for more information.                                                                                                                                             | None                |

| Ext_2 | The user shall follow the Electrical Characteristics specified in section 51 of [1].                                                                                                                                                          | None                |

| Ext_3 | It is recommended to use external measures to protect the power<br>supply to the MCU pins. See section 51 of [1] for a safe power supply<br>range. These measures shall be used in conjunction with the internal<br>LVD_Monitoring mechanism. | None                |

| Ext_4 | When using the ADC (ADC140 module), it is recommended to externally monitor the conversion reference voltage applied to pins VREFH0 and VREFL0.                                                                                               | None                |

# 2.1 External Watchdog

When designing the monitoring provided by an external Watch Dog, consider the following recommendations:

- Allow refresh only if all monitored tasks are executed, and in the proper order

- Allow refresh only if the expected time window for each task is followed

- Implement a Q&A-based exchange of messages before the refresh can take place (if supported by the external component).

- Note: Two internal Watch Dog Timers (WDTs) IWDT and WDT, are provided as MCU internal modules. If the internal WDTs are in use, the design of the external Watch Dog Timer can be simplified because the software (SW) control flow monitoring is also performed by the internal module(s).

- Note: When complementing the external WDT with the internal one, consider that both IWDT and WDT are not able to send an external error notification when the MCU status cannot be recovered through a SW routine (IRQ) or a reset procedure. This has to be considered during system design. The external WDT can effectively compensate for this issue.

# 3. Hardware (HW) Module Recommended Settings/ Usage

# 3.1 **Processing Module**

### 3.1.1 CPU

This module is the core used to run the safety application.

#### (1) **Recommended settings**

Table 3.1 describes the recommended settings for the CPU module.

#### Table 3.1 Recommended settings/usage for the CPU module

| ID  | Description | Limitation/ Comment |

|-----|-------------|---------------------|

| N/A | N/A         | N/A                 |

#### (2) Recommended protection against permanent faults

Table 3.2 describes the safety mechanism to protect the safety application from permanent failure of the CPU.

#### Table 3.2 Recommended protection from permanent failure of CPU

| ID  | Estimated<br>Coverage Level | Suggested Safety<br>Mechanisms | Suggested<br>Protection Type | Limitation/ Comment                                                                  |

|-----|-----------------------------|--------------------------------|------------------------------|--------------------------------------------------------------------------------------|

| N/A | Medium                      | CPU_SW_Test                    | Run-time                     | To be used in combination with<br>External WDT, see section 2.1<br>for more details. |

#### (3) Consideration for transient faults

It is recommended to protect the CPU from transient failures. In order to do this, consider the following information.

When protection CPU\_prot\_1 is used:

- a. Coverage is decreased to a low level since the effectiveness of CPU\_SW\_Test is affected by the test frequency.

- b. To improve the coverage level, adoption of application level mitigations is suggested for multiple operation processing, where elaboration of tasks is duplicated and the results of the redundant elaborations are compared to look for mismatches that indicate the presence of faults.

#### (4) Support of system level functional redundancy

# 3.2 Data I/O Modules

### 3.2.1 I/O Ports

#### (1) **Recommended settings**

Table 3.3 to Table 3.5 describe the recommended settings for the I/O Ports module.

#### Table 3.3 Recommended settings/usage for the I/O Ports module

| ID  | Description | Limitation/ Comment |

|-----|-------------|---------------------|

| N/A | N/A         | N/A                 |

#### Table 3.4 Recommended settings/usage for interference minimization of the I/O Ports module

| ID                                                                               | Description                                                                                                    | Limitation/ Comment |  |  |  |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------|--|--|--|

| IOPorts_sett_I1Follow recommendation for unused pins given in section20.4 of [1] |                                                                                                                | N/A                 |  |  |  |

| Table 3.5 Recom                                                                  | Table 3.5 Recommended settings/usage for protection against systematic System/SW faults                        |                     |  |  |  |

| ID                                                                               | Description                                                                                                    | Limitation/ Comment |  |  |  |

| IOPorts_recc_S1                                                                  | If pins belonging to the same General Purpose IO group are used for both SR and NSR functions, then a suitable | N/A                 |  |  |  |

#### (2) Recommended protection against permanent faults

Table 3.6 describes the safety mechanisms to protect the safety application from permanent failures of the I/O Ports.

Note: The coverage information reported is only valid for General Purpose I/O. For other usage purposes, refer to the module specific sections.

#### Table 3.6 Recommended protection from permanent failure of I/O Ports

| ID             | Estimated<br>Coverage<br>Level | Suggested Safety<br>Mechanisms                                      | Suggested<br>Protection Type | Limitation/Comment |

|----------------|--------------------------------|---------------------------------------------------------------------|------------------------------|--------------------|

| IOPorts_prot_1 | Medium                         | Config_reg_read_back,<br>GPIO_out_redundancy,<br>GPIO_in_redundancy | Run-time                     | N/A                |

#### (3) Consideration for transient faults

It is recommended to protect the I/O Ports from transient failures. In order to do this, see the following information.

When protection IOPorts\_prot\_1 is used:

a. Overall coverage is still kept High because the GPIO\_out\_redundancy and GPIO\_in\_redundancy mechanisms are always active and also effective for transient faults.

#### (4) Support for system level functional redundancy

Considerations are already provided in section 3.2.1.2. In particular, see GPIO\_in\_redundancy.

- Note: When using GPIO to achieve redundancy, special considerations need to be taken to mitigate possible dependencies. In particular, the following measures are recommended:

- Use pins belonging to different port groups

- Use pins that are not adjacent on the package

- Use pins whose data is located in different bits of the data bus.

# 3.2.2 14-Bit A/D Converter (ADC14)

This module can be used by the safety application when acquisition of analogue signals is necessary.

#### (1) **Recommended settings**

Table 3.7 to Table 3.9 describe the recommended settings for the 14-Bit ADC.

#### Table 3.7 Recommended settings/usage for the ADC14 module

| ID            | Description                                              | Limitation/ Comment |

|---------------|----------------------------------------------------------|---------------------|

| ADC14_sett_U1 | Enable the automatic clearing of A/D registers (ADDRy,   | N/A                 |

|               | ADRD, ADDBLDR, ADDBLDRA, ADDBLDRB, ADTSDR, or            |                     |

|               | ADOCDR) after any of these registers is read by the CPU, |                     |

|               | DTC, or DMAC.                                            |                     |

|               | ADCER.ACE = 1b.                                          |                     |

### Table 3.8 Recommended settings/usage for interference minimization for the ADC14 module

| ID            | Description                                                                         | Limitation/ Comment |

|---------------|-------------------------------------------------------------------------------------|---------------------|

| ADC14_sett_I1 | Enable Module-Stop state, when the peripheral is not used by setting the following: | N/A                 |

|               | setting the following.                                                              |                     |

#### MSTPCRD.MSTPD16 = 1b (ADC140).

# Table 3.9 Recommended settings/usage for protection against systematic System/SW faults for the ADC14 module

| ID            | Description                                                                                                                                                                                           | Limitation/ Comment |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| ADC14_recc_S1 | If at least one ADC channel is used for NSR functions while<br>the other channels are used for SR functions, then a suitable<br>SW handling is required to avoid compromising the safety<br>functions | N/A                 |

| ADC14_recc_S2 | The A/D conversion cannot be selected as ACMPHS input for targets listed in section 39.8.13 of [1] during A/D conversion because these pins are multiplexed with the A/D converter and ACMPHS         | N/A                 |

#### (2) Recommended protection against permanent faults

Table 3.10 describes the safety mechanisms to protect the safety application from permanent failures of the 14-Bit A/D Converter module.

| ID            | Estimated<br>Coverage<br>Length | Suggested Safety<br>Mechanism                                                                                 | Suggested<br>Protection<br>Type | Limitation/ Comment                                                                                                                                                                                                                                                                                                 |

|---------------|---------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC14_prot_1a | Medium                          | Error! Reference source<br>not<br>found.ADC14_Comparat<br>or_SW,<br>Config_reg_read_back                      | Run-time                        | If DMA is used in connection<br>with the ADC, then the self-test<br>provided by<br>ADC14_TriggerDMA shall be<br>adopted, as described in<br>ADC14_prot_1b.<br>When using <b>Error! Reference</b><br><b>source not found.</b> , take care<br>to mitigate dependency issues<br>between the sources of<br>information. |

| ADC14_prot_1b | Medium                          | Error! Reference source<br>not<br>found.ADC14_Comparat<br>or_SW,<br>ADC14_TriggerDMA,<br>Config_reg_read_back | Self-test                       | When using <b>Error! Reference</b><br><b>source not found.</b> , take care<br>to mitigate dependency issues<br>between the sources of<br>information                                                                                                                                                                |

#### Table 3.10 Recommended protection from permanent failure of ADC14

#### (3) **Consideration for transient faults**

It is recommended to protect the ADC14 from transient failures. In order to do this, see the following information.

When protection ADC14\_prot\_1a is used:

a. Overall coverage can be kept at a medium level despite the negative impact of the test frequency on ADC14 Comparator SW and Config reg read back.

#### (4) Support of system level functional redundancy

The MCU allows the possibility of using multiple channels belonging to the same unit to support system level redundancy. Usage of ADC14\_Comparator\_SW is highly recommended in the latter case to mitigate dependency issues related to the common analogue comparator.

## 3.2.3 12-Bit D/A Converter (DAC12)

This module can be used by the safety application when Digital to Analogue conversion is necessary.

#### (1) **Recommended settings**

Table 3.11 to Table 3.13 describe the recommended settings for the D/A Converter module.

#### Table 3.11 Recommended settings/usage for the DAC12 module

| ID  | Description | Limitation/ Comment |

|-----|-------------|---------------------|

| N/A | N/A         | N/A                 |

#### Table 3.12 Recommended settings/usage for interference minimization for the DAC12 module

| ID            | Description                                                                                                                                                    | Limitation/ Comment |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| DAC12_sett_I1 | As a measure against interference between D/A and A/D conversion, write DAADSCR.DAADST = 1b while ADCSR.ADST = 0b. See section 40.3.1 of [1] for more details. | N/A                 |

| DAC12_sett_I2 | Enable Module-Stop State when the peripheral is not<br>used, by setting MSTPCRD.MSTPD20 =1b                                                                    | N/A                 |

# Table 3.13 Recommended settings/usage for protection against systematic System/SW faults for the DAC12 module

| DAC12_recc_S1 If one channel (for example, DA0) is used for SR N/A<br>functions while the other (for example, DA1) is used for<br>NSR functions, then, suitable SW handling is required to<br>avoid compromising the safety functions | ID            | Description                                                                                                       | Limitation/ Comment |

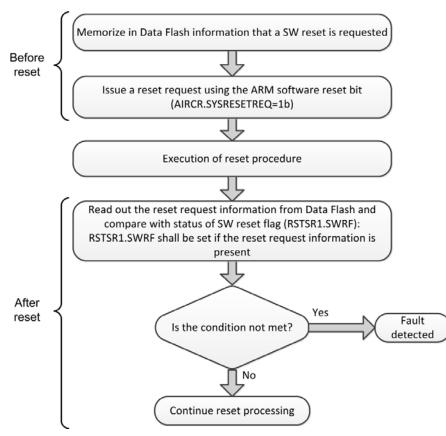

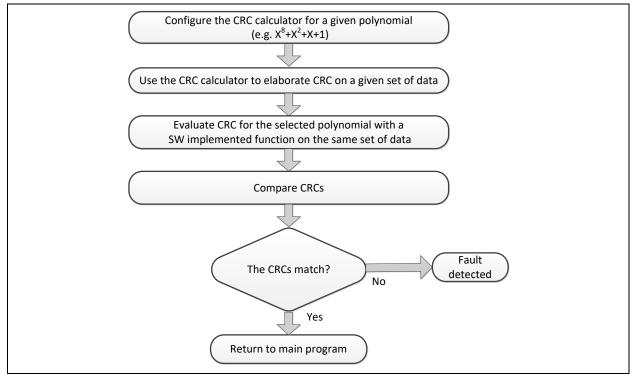

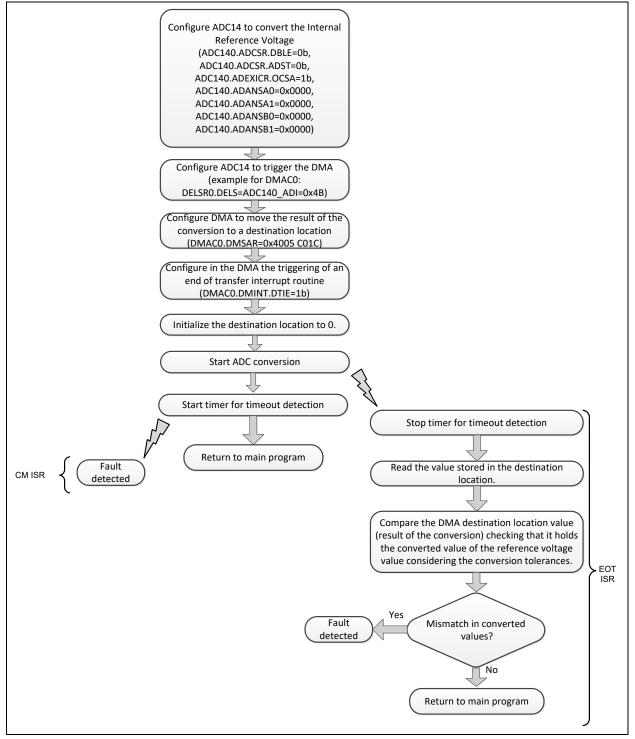

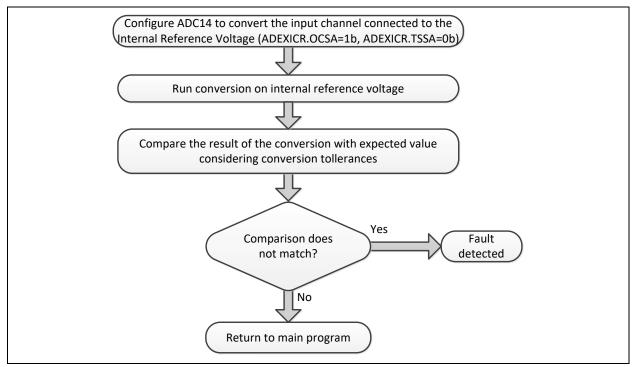

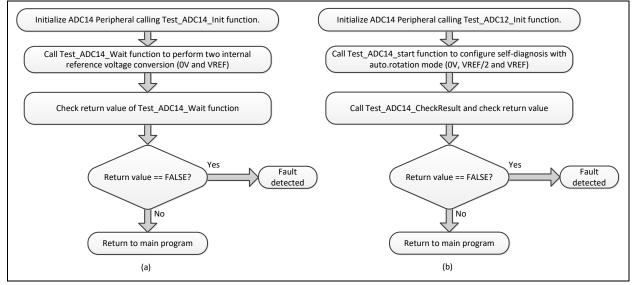

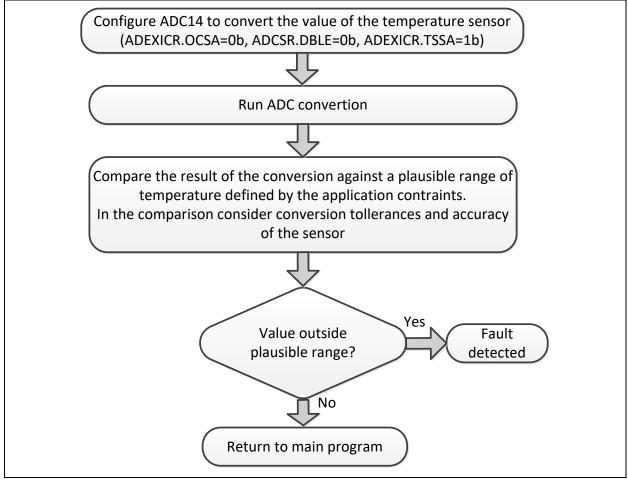

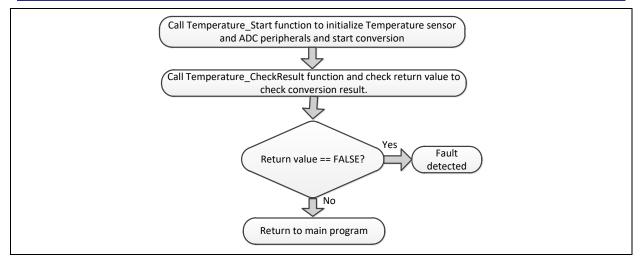

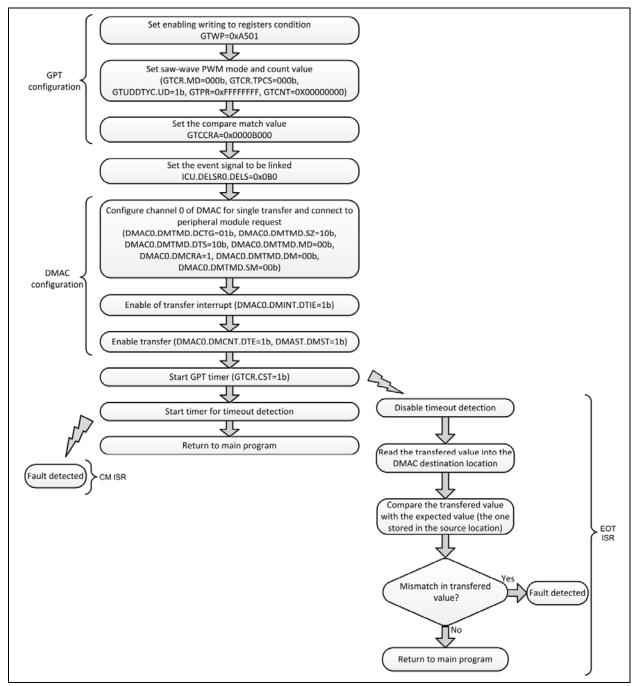

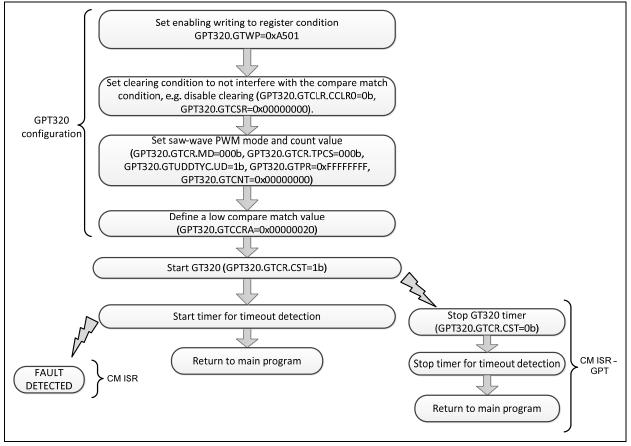

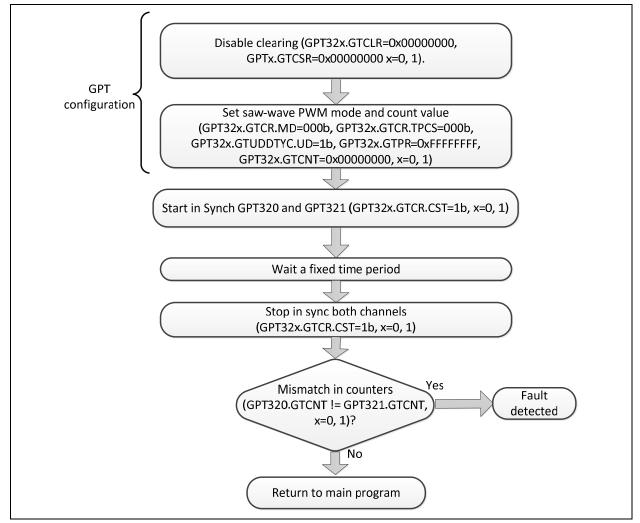

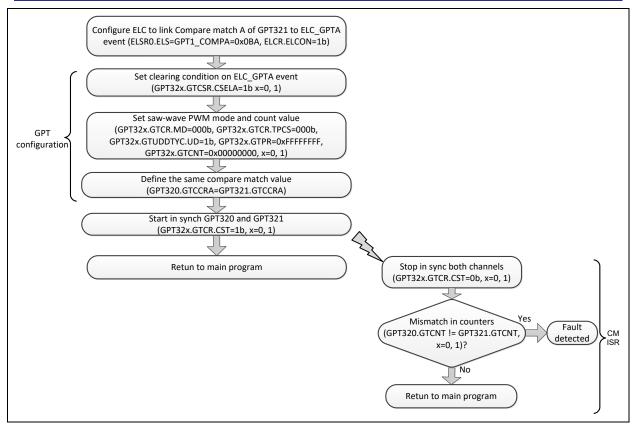

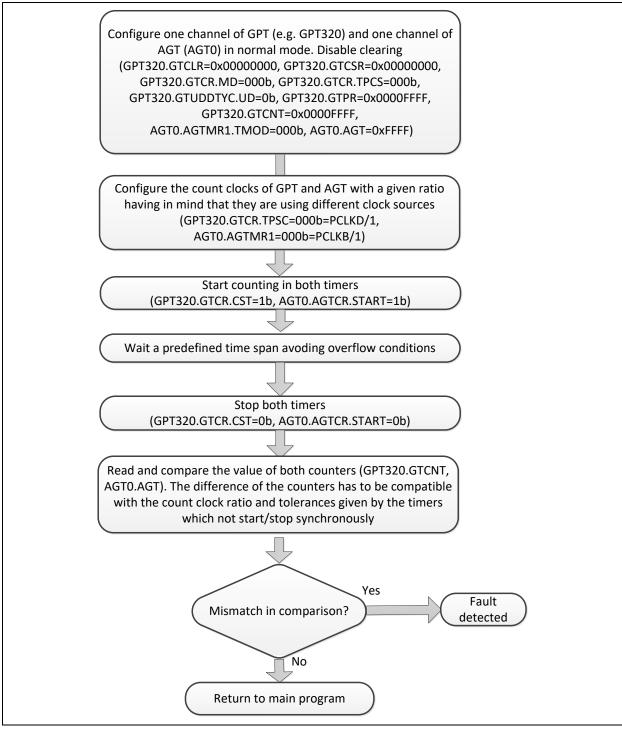

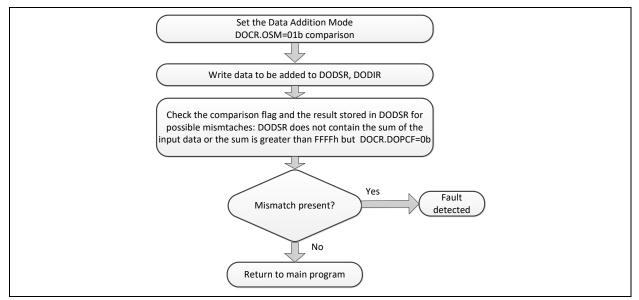

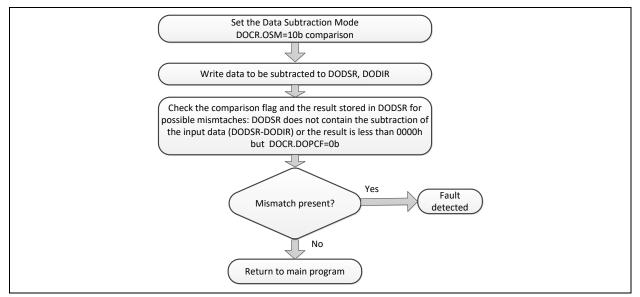

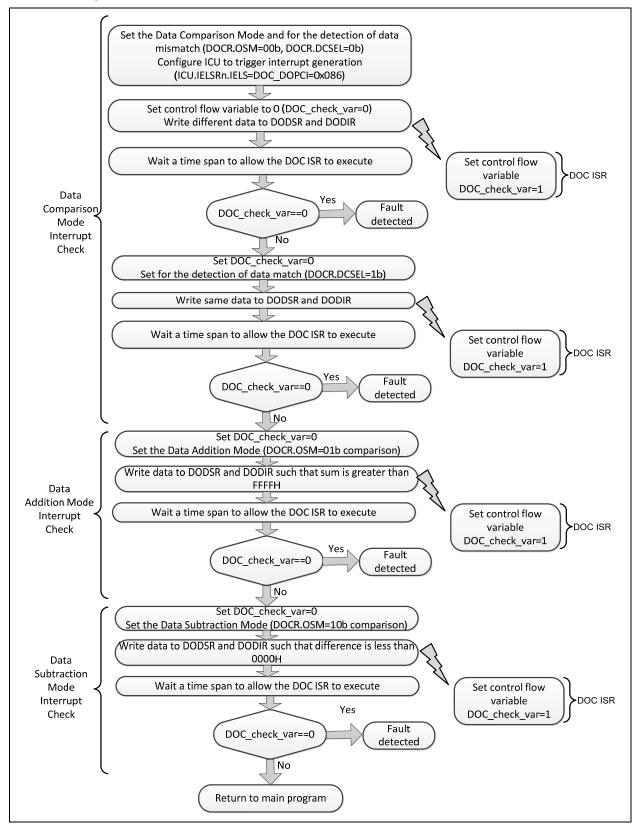

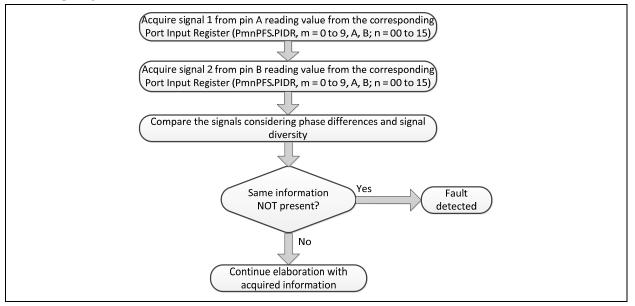

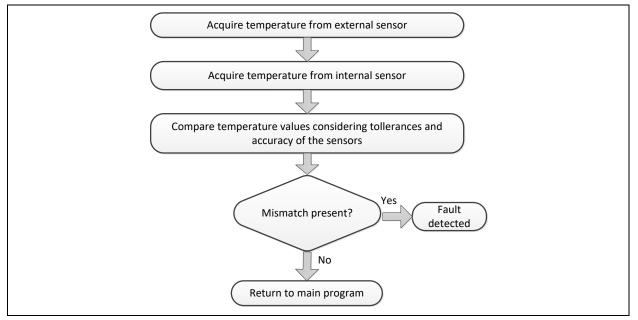

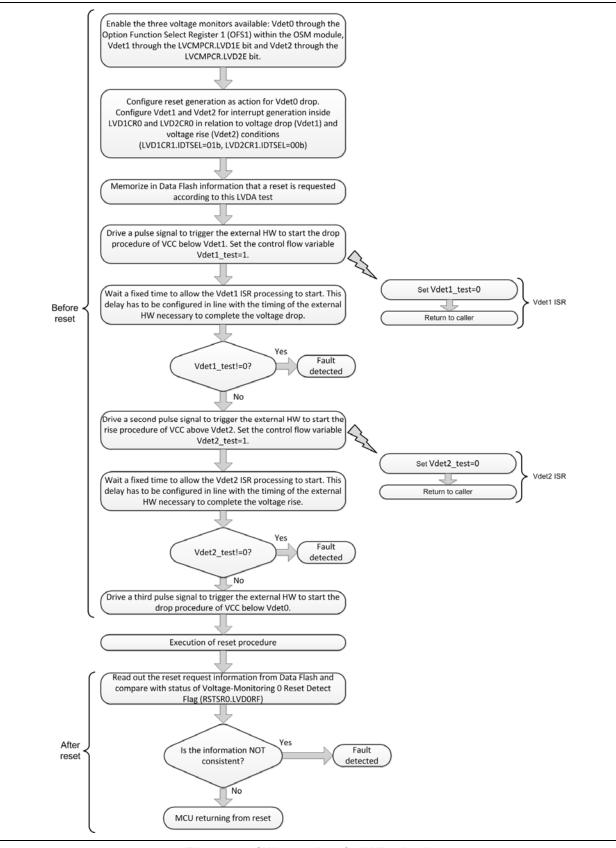

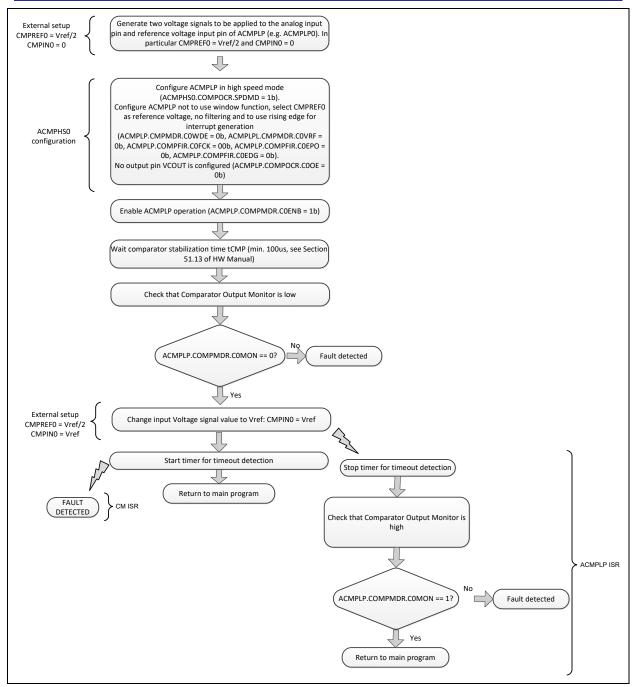

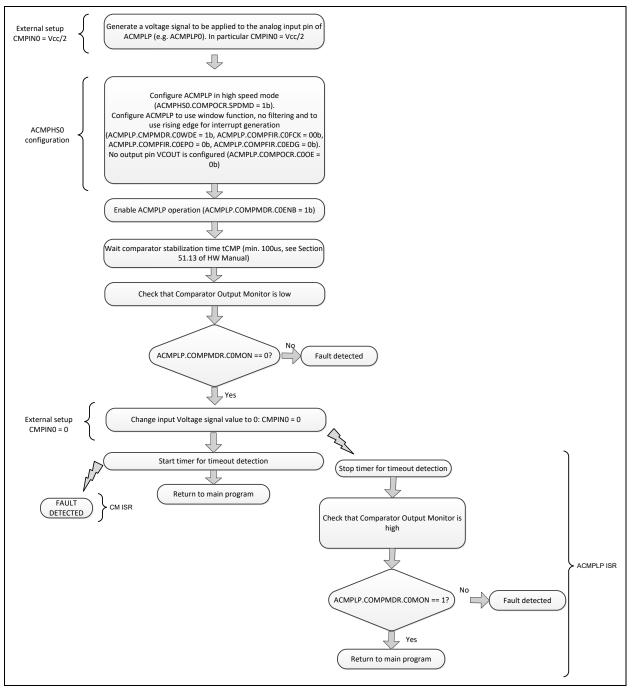

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------|---------------------|