# RH850/U2B

# Using eMMC Storage

# Introduction

RH850/U2B series provide a Multimedia Card Interface (MMCA) for external eMMC memory.

This document provides a general introduction of the eMMC standards, MMCA configuration flows and the sample software.

# **Target Device**

This document is intended to describe the MMCA sample SW on RH850/U2B series.

In this document, the RH850/U2B device R7F702Z21\* is employed to implement the example application. Still, the concept described in this document applies also to other members of the RH850/U2B series.

### Disclaimer

Renesas Electronics does not warrant the information included in this document. You are fully responsible for incorporation of these circuits, software, and information in the design of your equipment and system. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

# Contents

| Introduction1                                               |  |  |  |  |  |  |  |

|-------------------------------------------------------------|--|--|--|--|--|--|--|

| Target Device1                                              |  |  |  |  |  |  |  |

| Disclaimer1                                                 |  |  |  |  |  |  |  |

| Contents2                                                   |  |  |  |  |  |  |  |

| 1. Background4                                              |  |  |  |  |  |  |  |

| 2. Reference Documents                                      |  |  |  |  |  |  |  |

| 2.1 RH850/U2B Group User's Manual: Hardware5                |  |  |  |  |  |  |  |

| 2.2 RH850/X2X User's Manual: Main Board                     |  |  |  |  |  |  |  |

| 2.3 eMMC standards5                                         |  |  |  |  |  |  |  |

| 3. Definitions and Abbreviations                            |  |  |  |  |  |  |  |

| 4. Software and Hardware Tools                              |  |  |  |  |  |  |  |

| 4.1 Development Tools                                       |  |  |  |  |  |  |  |

| 4.2 Emulator E2                                             |  |  |  |  |  |  |  |

| 4.3 RH850/U2B Evaluation Boards                             |  |  |  |  |  |  |  |

| 4.3.1 PiggyBack Board                                       |  |  |  |  |  |  |  |

| 4.3.2 Main Board                                            |  |  |  |  |  |  |  |

| 4.3.3 Extension eMMC Board                                  |  |  |  |  |  |  |  |

| 5. eMMC Standards9                                          |  |  |  |  |  |  |  |

| 5.1 System Overview                                         |  |  |  |  |  |  |  |

| 5.2 Operation Modes                                         |  |  |  |  |  |  |  |

| 5.3 Bus Protocol and Speed Mode10                           |  |  |  |  |  |  |  |

| 5.4 State Machines                                          |  |  |  |  |  |  |  |

| 5.4.1 Boot Mode                                             |  |  |  |  |  |  |  |

| 5.4.2 Card-Identification Mode                              |  |  |  |  |  |  |  |

| 5.4.3 Interrupt Mode                                        |  |  |  |  |  |  |  |

| 5.4.4 Data Transfer Mode                                    |  |  |  |  |  |  |  |

| 5.5 Commands and response                                   |  |  |  |  |  |  |  |

| 5.5.1 Commands                                              |  |  |  |  |  |  |  |

| 5.5.2 Response                                              |  |  |  |  |  |  |  |

| 5.6 The JEDEC Standard Comparation (eMMC 4.41 vs. eMMC 5.0) |  |  |  |  |  |  |  |

| 5.7 eMMC registers                                          |  |  |  |  |  |  |  |

| 6. Port Setup for MMCA Module                               |  |  |  |  |  |  |  |

| 6.1 External Input / Output                                 |  |  |  |  |  |  |  |

| 6.2 Port Output Buffer Drive Strength                       |  |  |  |  |  |  |  |

| 6.3 Port Write Protection                                   |  |  |  |  |  |  |  |

# RH850/U2B

| 7.    | Clock Setup for MMCA Module                               | 28 |

|-------|-----------------------------------------------------------|----|

| 8.    | SW Procedure and Module Setup for Typical eMMC Operations | 29 |

| 8.1   | Card Reset                                                | 29 |

| 8.2   | Card Identification                                       | 29 |

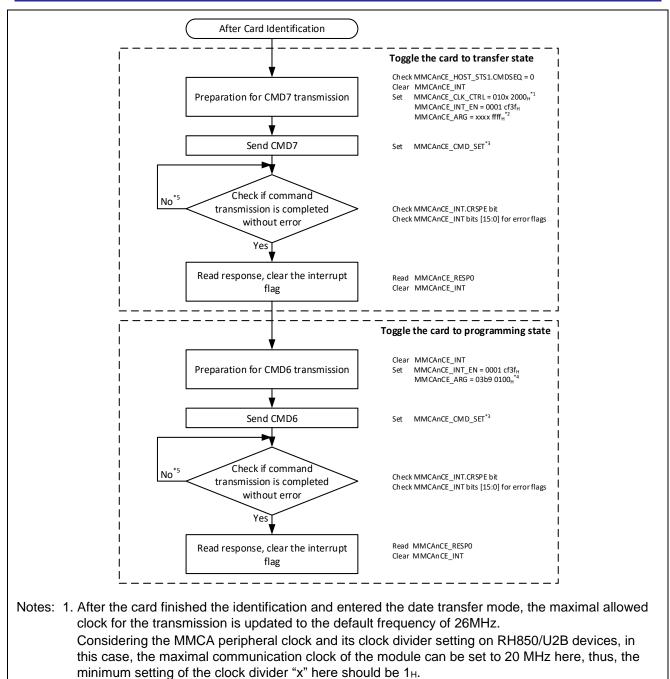

| 8.3   | Configuration Card Register and Basic Settings            | 31 |

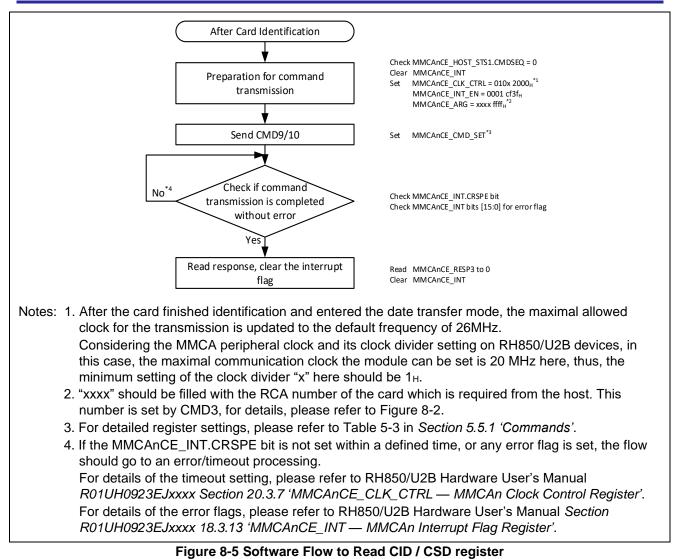

| 8.4   | Read Card Register                                        |    |

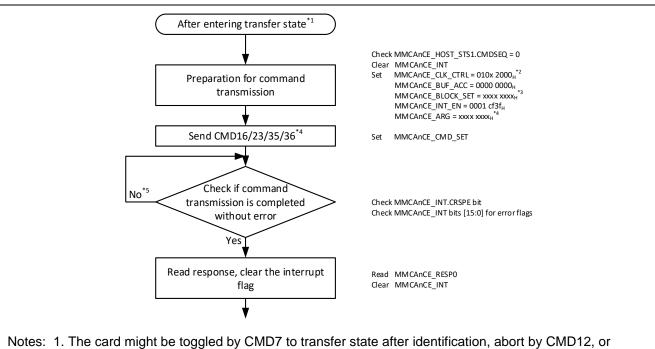

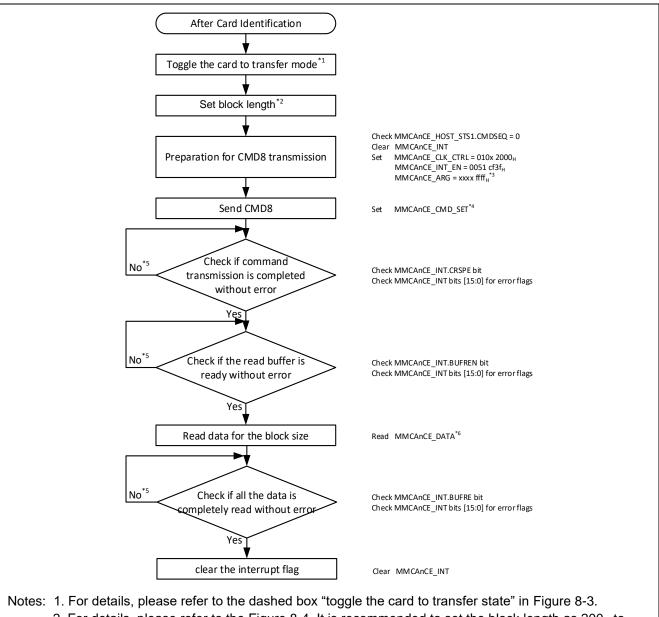

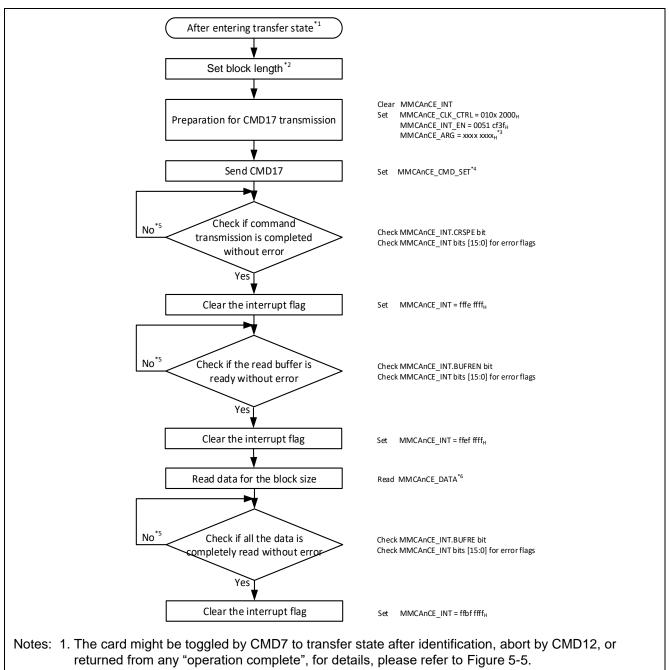

| 8.5   | Single-Block Read                                         |    |

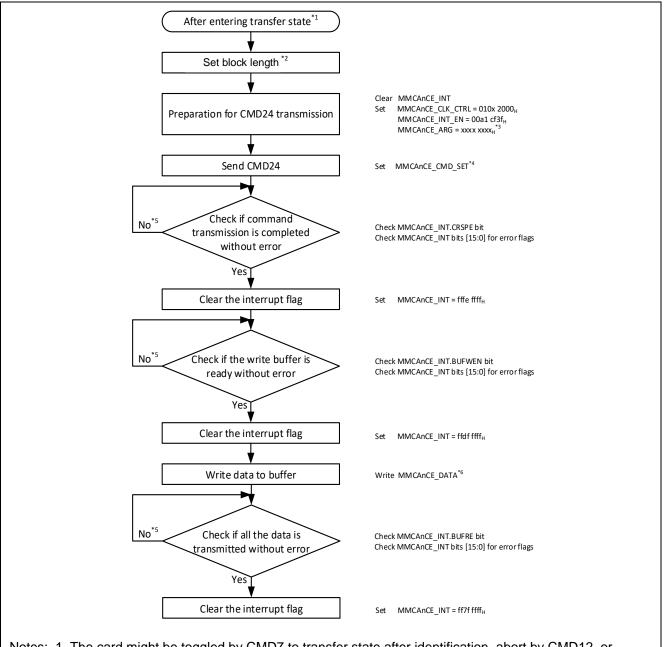

| 8.6   | Single-Block Write                                        |    |

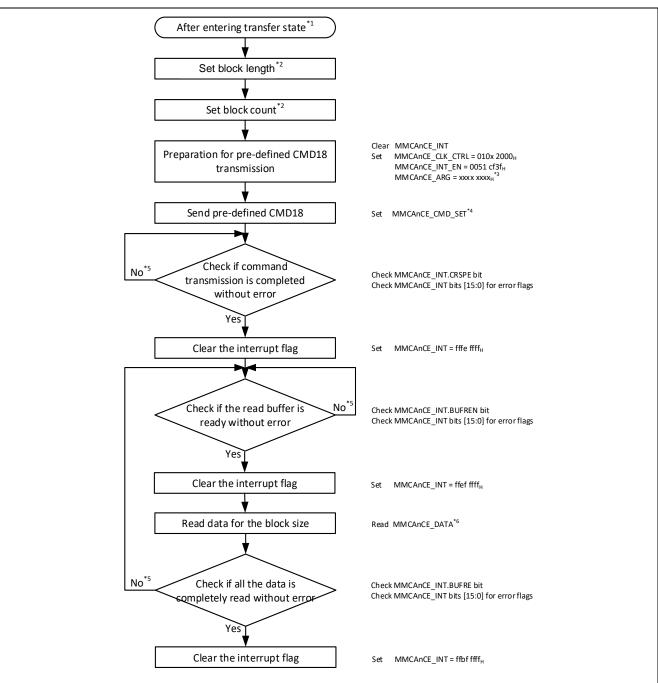

| 8.7   | Multi-Block Read                                          |    |

| 8.7.1 | 1 Pre-defined                                             |    |

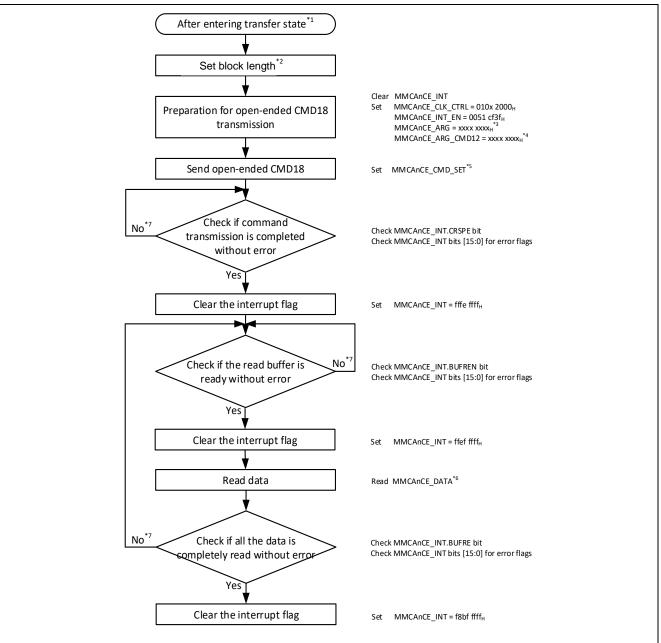

| 8.7.2 | 2 Open-ended                                              | 40 |

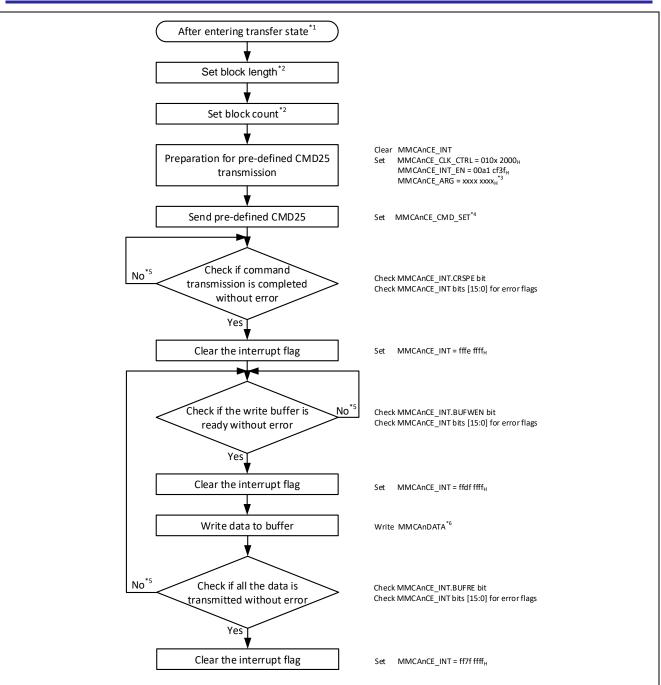

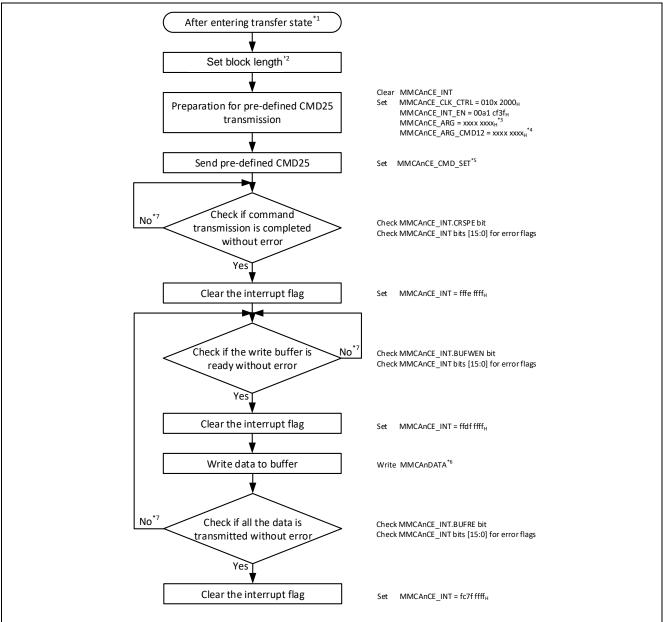

| 8.8   | Multi-Block Write                                         | 41 |

| 8.8.1 | 1 Pre-defined                                             | 41 |

| 8.8.2 | 2 Open-ended                                              | 43 |

| 8.9   | Erase                                                     | 44 |

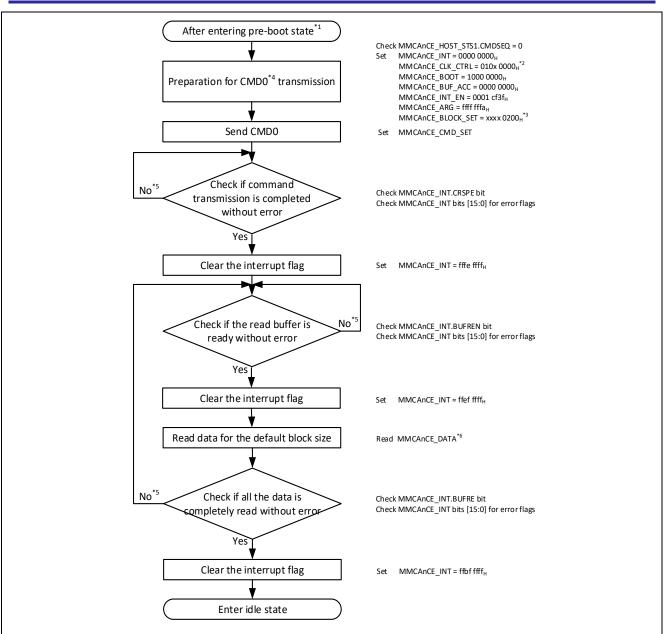

| 8.10  | Boot                                                      | 44 |

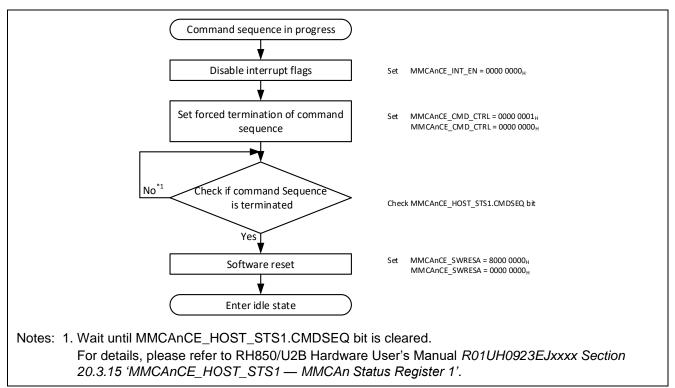

| 8.11  | Forcible Termination                                      |    |

| 9.    | Description of Sample Software                            | 47 |

| 9.1   | main_pe0.c                                                | 47 |

| 9.2   | MMCA.c and MMCA.h                                         | 47 |

| 9.3   | port_init.c                                               | 47 |

| Rev   | ision History                                             | 48 |

# 1. Background

Since much more complicated automotive applications and the corresponding memory extension are required for the future, RH850/U2B devices provide a Multimedia Card Interface for external eMMC memory.

This application note contains a general description of the eMMC standards, typical eMMC operations, related software procedures, MMCA module settings etc., and introduces the sample software and its software / hardware setups.

In this document, Section 2 includes the reference documents. For some detailed information or special use cases, please use this application note in combination with the references.

Section 3 lists of the register abbreviations in this document.

Section 4 provides a description about the hardware setups and software environment for the MCU applications with eMMC storage.

Section 5 introduces the eMMC standards with which the MCU is compliant. This section contains the operation modes, bus configuration, state machines, commands and response, card registers etc.

Section 6 and Section 7 describe individually the port and clock setups for the eMMC interface (MMCA) on MCU.

Section 8 provides the details of software flows and the related MCU register settings for the applications using eMMC storage.

Section 9 explains the structure of the related sample software.

# 2. Reference Documents

# 2.1 RH850/U2B Group User's Manual: Hardware

The Hardware User's Manual provides information about the functional and electrical behavior of the device.

At the release time of this document the following manual version is available:

• RH850/U2B User's Manual (Rev.1.00): R01UH0923EJ0100

# 2.2 RH850/X2X User's Manual: Main Board

The Main Board User's Manual provides information about the X2X main board and peripheral circuits.

At the release time of this document the following manual version is available:

RH850/X2X User's Manual: Main Board (Rev.1.00): R20UT4459ED0100

# 2.3 eMMC standards

The MMCA module in target device is compliant with JEDEC Standard JESD84-A441 and the JEDEC Standards with later versions.

Renesas provides also an extension board Y-RH850-EMMC-SFMA-EXT-BRD with eMMC. The eMMC device on this application board is the Swissbit SFEM4096B1EA1TO-I-GE-111-E02 device of the EM-26 Series, or the SFEM032GB1EA1TO-I-LF-111-STD device of the EM-20 Series. Both of the eMMC devices are compliant with JEDEC Standard JESD84-B50.

Therefore, the application note and sample code are based on the following documents:

- JESD84-A441, JEDEC Standard Embedded Multi-Media Card (e•MMC) Electrical Standard (4.41)

- JESD84-B50, JEDEC Standard Embedded Multi-Media Card (e•MMC) Electrical Standard (5.0)

Section 5.6 provides a comparation between these two standard versions.

### 3. Definitions and Abbreviations

For the purposes of this publication, the following abbreviations for common terms apply:

- **eMMC:** embedded multimedia card

- MMCA: multimedia card interface A

- Host: the MCU device with multimedia card interface

- Slave: the multimedia card

- Block: basic data transfer unit

- Stuff bit: fill 0 bits to ensure fixed length frames for commands and responses

- Erase: group erase operation which does not require actual physical NAND erase

- TRIM: erase operation to write blocks instead of erase groups

- Sanitize: physically remove data from the unmapped user address space

Additionally, the abbreviation of registers, which are mentioned in this application note is listed in Table 3-1.

|                                   | Register Name                                             | Symbol            |

|-----------------------------------|-----------------------------------------------------------|-------------------|

| eMMC Card Registers <sup>*1</sup> | Card Identification Number Register                       | CID               |

|                                   | Relative Card Address Register                            | RCA               |

|                                   | Driver Stage Register                                     | DSR               |

|                                   | Card Specific Data Register                               | CSD               |

|                                   | Operation Conditions Register                             | OCR               |

|                                   | Extended Card Specific Data Register                      | EXT_CSD           |

| MCU Port Registers*2              | Port Mode Register                                        | PMn               |

|                                   | Port Mode Control Register                                | PMCn              |

|                                   | Port Mode Control Register                                | PIPCn             |

|                                   | Port Function Control Register                            | PFCn              |

|                                   | Port Function Control Expansion Register                  | PFCEn             |

|                                   | Port Function Control Additional Expansion<br>Register    | PFACEn            |

|                                   | Port Universal Characteristic Control Register            | PUCCn             |

|                                   | Port Drive Strength Control Register                      | PDSCn             |

|                                   | Port Keycode Protection                                   | PKCPROT           |

|                                   | Port Write Enable Register                                | PWE               |

| MCU Clock Registers*2             | Module Standby Register for MMCA                          | MSR_MMCA          |

|                                   | Module Standby Register Key Code<br>Protection Register   | MSRKCPROT         |

| MCU MMCA Module                   | MMCAn Command Setting Register                            | MMCAnCE_CMD_SET   |

| Registers*2                       | MMCAn Argument Register                                   | MMCAnCE_ARG       |

|                                   | MMCAn Argument Register for<br>Automatically-Issued CMD12 | MMCAnCE_ARG_CMD12 |

|                                   | MMCAn Command Control Register                            | MMCAnCE_CMD_CTRL  |

|                                   | MMCAn Transfer Block Setting Register                     | MMCAnCE_BLOCK_SET |

|                                   | MMCAn Clock Control Register                              | MMCAnCE_CLK_CTRL  |

|                                   | MMCAn Buffer Access Configuration<br>Register             | MMCAnCE_BUF_ACC   |

|                                   | MMCAn Response Register 3                                 | MMCAnCE_RESP3     |

|                                   | MMCAn Response Register 2                                 | MMCAnCE RESP2     |

#### Table 3-1 Symbols of Registers

| MMCAn Response Register 1                                 | MMCAnCE_RESP1      |

|-----------------------------------------------------------|--------------------|

| MMCAn Response Register 0                                 | MMCAnCE_RESP0      |

| MMCAn Response Register for<br>Automatically-Issued CMD12 | MMCAnCE_RESP_CMD12 |

| MMCAn Data Register                                       | MMCAnCE_DATA       |

| MMCAn Boot Operation Setting<br>Register                  | MMCAnCE_BOOT       |

| MMCAn Interrupt Flag Register                             | MMCAnCE_INT        |

| MMCAn Interrupt Enable Register                           | MMCAnCE_INT_EN     |

| MMCAn Status Register 1                                   | MMCAnCE_HOST_STS1  |

| MMCAn Status Register 2                                   | MMCAnCE_HOST_STS2  |

| MMCAn Software Reset Register                             | MMCAnCE_SWRESA     |

Notes: 1. For details of the eMMC card registers, please refer to Section 5.7.

The general MCU register configurations are mentioned in Section 6 to 8. For further information, please refer to the Hardware User's Manual *R01UH0923EJxxxx* of the device.

### 4. Software and Hardware Tools

This section contains the information about tools which are used to implement the MMCA application.

### 4.1 Development Tools

The compiler used for the sample code is Renesas Electronics CS+.

The required version of the CS+ compiler for U2B devices is V8.09.00 or later versions.

### 4.2 Emulator E2

The Renesas E2 Emulator is required for the debugging.

### 4.3 RH850/U2B Evaluation Boards

The following evaluation boards are used to implement the MMCA application.

#### 4.3.1 PiggyBack Board

The PiggyBack Board Y-RH850-U2B-292PIN-PB-T1-V1 D018567\_06\_V02 carries the target device. The SW in this document is performed on the RH850/U2B device R7F702Z21\* within this piggyback board.

### 4.3.2 Main Board

Renesas provides the main board RH850-X2X-MB-T1-V1 for the RH850/X2X microcontrollers as easy to use platform to evaluate the devices. This main board should be used in conjunction with a piggyback board.

#### 4.3.3 Extension eMMC Board

Renesas provides also the extension board Y-RH850-EMMC-SFMA-EXT-BRD with eMMC.

This board is described in the RH850/X2X Main Board User's Manual *R20UT4459EDxxxx Section 4.9 'eMMC/SFMA Module'*.

### 5. eMMC Standards

The MMCA module in the target device is compliant with the JEDEC Standard JESD84-A441<sup>\*Note</sup> and the JEDEC Standards with later versions.

The description in this section is based on the eMMC standard version 4.41 and version 5.0.

# 5.1 System Overview

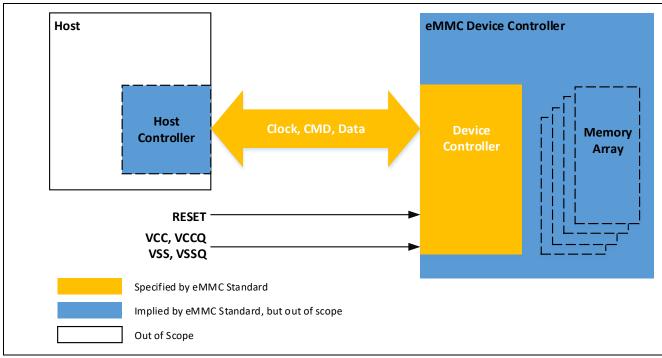

Figure 5-1 shows the general eMMC system overview. The eMMC specification covers the behavior of the interface and the device controller.

Figure 5-1 eMMC System Overview

The eMMC device supports the following features:

- For read-only, read/write and I/O cards.

- Maintains card support for three different data bus width modes: 1-bit (default), 4-bit, and 8-bit.

- Includes definition for a higher than 2GB density of memories.

- Includes password protection of data.

- Supports basic file formats for high data interchangeability.

- Includes application specific commands.

- Enables correction of memory field errors.

- Has built-in write protection features for the boot and user areas, which may be permanent, power-on, or temporary.

- Includes a simple erase mechanism.

- Maintains full backward compatibility with previous MultiMediaCard systems.

- Supports multiple command sets.

- Provides a possibility for the host to make sudden power failure safe-update operations for the data content.

- Enhanced power saving method by introducing a sleep functionality.

- Introduces Boot Operation Mode to provide a simple boot sequence method.

- Introduces Secure Erase & Trim to enhance data security.

- Signed access to a Replay Protected Memory Block.

# 5.2 Operation Modes

The eMMC devices has several operation modes:

Inactive mode

The device will enter inactive mode if either the device operating voltage range or access mode is not valid. The device can also enter inactive mode with the GO\_INACTIVE\_STATE command (CMD15). The device will reset to *Pre-idle* state with each power cycle.

Boot mode

The device will be in boot mode after a power cycle, the reception of CMD0 with an argument of 0xF0F0F0F0 or the assertion of a hardware reset signal.

• Card-identification mode

The device will be in card-identification mode after the boot operation mode is finished or if the host and /or the device does not support the boot operation mode. The device will remain in this mode until the SET\_RCA command (CMD3) is received.

- Data transfer mode The device will enter the data transfer mode once an RCA is assigned to it. The host will enter the data transfer mode after identifying the device on the bus.

- Interrupt mode

The host and the device enter and exit the interrupt mode simultaneously. In interrupt mode there is no data transfer. The only message allowed is an interrupt service request from the device or the host.

# 5.3 Bus Protocol and Speed Mode

After a power-on reset, the host must initialize the device by a special message-based eMMC bus protocol. The eMMC bus operations always contain a command token and a response token, some operations have a data token. For the detailed coding scheme of the tokens, please refer to the corresponding eMMC standards.

The default eMMC transfer frequency is up to 26MHz, with the maximal transfer speed of 26MB/s.

If the maximal MMCA clock frequency for RH850/U2B series of 40 MHz is required, the eMMC device should be switched to high speed mode for this higher eMMC clock frequency.

To switch the device into high speed mode, the host should use CMD6 to set the bytes [185] HS\_TIMING from register EXT\_CSD register to  $1_B$ .

# 5.4 State Machines

Table 5-1 shows the dependencies between bus modes, operation modes and device states. Each device state is associated with one bus mode and one operation mode.

| Device State         | Operation Mode             | Bus Mode   |

|----------------------|----------------------------|------------|

| Inactive State       | Inactive mode              | Open drain |

| Pre-Idle State       | Boot mode                  |            |

| Pre-Boot State       |                            |            |

| Idle State           | Device identification mode |            |

| Ready State          |                            |            |

| Identification State |                            |            |

| Stand-by State       | Data transfer mode         | Push-pull  |

| Sleep State          |                            |            |

| Transfer State       |                            |            |

| Bus-Test State       |                            |            |

#### Table 5-1 Overview of Device States and Bus modes

| Sending-data State |                |            |

|--------------------|----------------|------------|

| Receive-data State |                |            |

| Programming State  |                |            |

| Disconnect State   |                |            |

| Boot State         | Boot mode      |            |

| Wait-IRQ State     | Interrupt mode | Open drain |

### 5.4.1 Boot Mode

### 5.4.1.1 Alternative Boot Operation

The boot function described in this section is for devices with JEDEC Standard 4.4 and later. The compliant devices for the RH850/U2B MMCA module must show "1" on bit 0 in the Extended CSD byte [228].

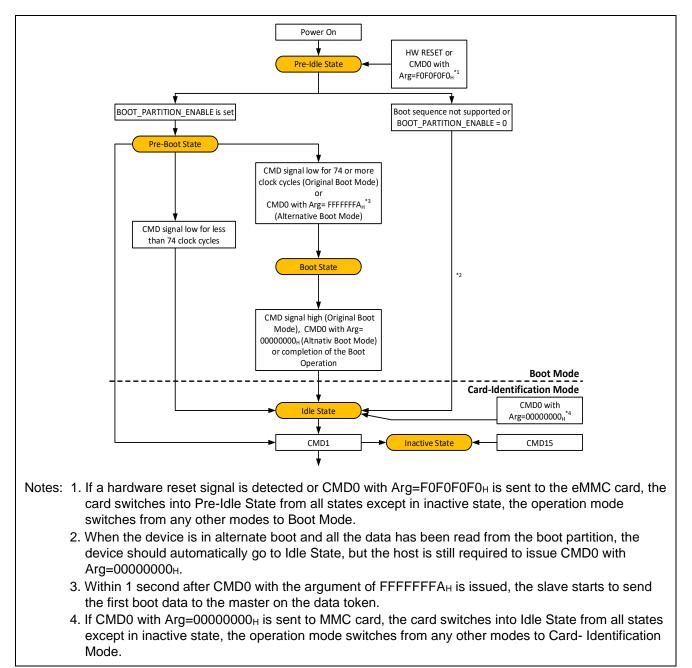

Figure 5-2 shows the state diagram of the boot mode.

Figure 5-2 Boot Mode

RENESAS

If boot acknowledge is enabled<sup>\*1</sup>, the slave must send the acknowledge pattern  $010_B$  to the master within 50ms after the CMD0 with the argument of 0xFFFFFFA is received, so that the master can recognize that the slave is operating. If boot acknowledge is disabled, the slave will not send out the acknowledge pattern  $010_B$ . The master can terminate the boot mode by issuing CMD0. If the master issues CMD0 in the middle of a data transfer, the slave must terminate the data transfer or the acknowledge pattern within 2 clock cycles<sup>\*2</sup>.

If the master terminates boot mode between consecutive blocks, the slave must release the data line(s) within 2 clock cycles. Boot operation will be terminated when all contents of the enabled boot data are sent to the master. After boot operation is executed, the slave shall be ready for CMD1 operation and the master needs to start a normal MMC initialization sequence by sending CMD1.

If the CMD line is held LOW for less than 74 clock cycles after power-up before CMD1 is issued, or the master sends any normal MMC command other than CMD1 and CMD0 with argument 0xFFFFFFA before initiating boot mode, the slave does not respond and will be locked out of boot mode until the next power cycle and the Idle State is entered. When BOOT\_PARTITION\_ENABLE bits are set and the master sends CMD1, the slave must enter Card-Identification Mode and respond to the command.

If the slave does not support boot operation mode, or the BOOT\_PARTITION \_ENABLE bit is cleared, the slave automatically enters the Idle State after power-on.

Notes: 1. Set BOOT\_ACK bit, referring to Table 5-2.

2. One data cycle and end bit cycle, for detailed information, please refer to JESD84-A441.

### 5.4.1.2 Configuration of Boot Partition, Bus Width and Data Access

The boot partition, bus width and data access can be configured in the EXT\_CSD register. The host can set the eMMC register by sending CMD6.

There are two partition regions. The minimum size of each boot partition is 128KB. The boot partition size is calculated as follows, with BOOT\_SIZE\_MULT from Extended CSD register byte [226]:

Maximum boot partition size = 128K byte x BOOT\_SIZE\_MULT

To configure the boot partition and data width, the protection of the boot configuration should be disabled by the EXT\_CSD register byte [178]. The boot partition and data access can be individually selected in the byte [179] PARTITION\_CONFIG bit [5:3] and bit [2:0]. The bus width can be selected in byte [177] bit [1:0].

Table 5-2 lists the boot mode configuration and corresponding bytes in the EXT\_CSD register.

| EXT_CSD<br>Field | Slice | Bit Name     | Bit Position | Cell Type | Description                                 | Set Value*1      |

|------------------|-------|--------------|--------------|-----------|---------------------------------------------|------------------|

| PARTITION_CO     | [179] | BOOT_ACK     | 6            | R/W/E     | No boot acknowledge sent                    | 0 <sub>B</sub>   |

| NFIG             |       |              |              |           | Boot acknowledge sent during boot operation | 1в               |

|                  |       | BOOT_PARTITI | 5 to         | R/W/E     | Boot not enabled                            | 000 <sub>B</sub> |

|                  |       | ON_ENABLE    | 3            |           | Boot partition 1 enabled for boot           | 001в             |

|                  |       |              |              |           | Boot partition 2 enabled for boot           | 010в             |

|                  |       |              |              |           | User area enabled for boot                  | 111в             |

|                  |       | PARTITON_AC  | 2 to         | R/W/E     | No access to boot partition                 | 000 <sub>B</sub> |

|                  |       | CESS         | 0            | _P        | R/W boot partition 1                        | 001 <sub>B</sub> |

|                  |       |              |              |           | R/W boot partition 2                        | 010в             |

|                  |       |              |              |           | R/W Replay Protected Memory                 | 011в             |

|                  |       |              |              |           | Block                                       |                  |

|                  |       |              |              |           | Access to General Purpose partition 1       | 100в             |

#### Table 5-2 Details of Boot Mode Configuration in EXT\_CSD Register

|                         |       |                                 |           |                          | Access to General Purpose partition 2                                                                                                                                       | 101в             |                                                                                                       |                |

|-------------------------|-------|---------------------------------|-----------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------|----------------|

|                         |       |                                 |           |                          | Access to General Purpose<br>partition 3                                                                                                                                    | 110в             |                                                                                                       |                |

|                         |       |                                 |           |                          | Access to General Purpose partition 4                                                                                                                                       | 111 <sub>в</sub> |                                                                                                       |                |

| BOOT_CONFIG             | [178] | PERM_BOOT_                      | 4         | R/W                      | Protection disabled                                                                                                                                                         | <b>0</b> B       |                                                                                                       |                |

| _PROT                   |       | CONFIG_PROT                     |           |                          | Protection of boot configuration<br>(PARTITION_CONFIG and<br>BOOT_BUS_CONDITIONS) is<br>permanently enabled                                                                 | 1 <sub>B</sub>   |                                                                                                       |                |

|                         |       | PWR_BOOT_                       | 0         | R/W/C                    | Protection disabled                                                                                                                                                         | <b>0</b> B       |                                                                                                       |                |

|                         |       | CONFIG_PROT                     |           | _P                       | Protection of boot configuration<br>(PARTITION_CONFIG and<br>BOOT_BUS_CONDITIONS)<br>from at this point until next<br>power cycle or next H/W reset<br>operation is enabled | 1 <sub>B</sub>   |                                                                                                       |                |

| BOOT_BUS_C<br>ONDITIONS | [177] | BOOT_MODE                       | 4 to<br>3 | R/W/E                    | Use single data rate + backward<br>compatible timings in boot<br>operation                                                                                                  | 00 <sub>B</sub>  |                                                                                                       |                |

|                         |       |                                 |           |                          | Use single data rate + high<br>speed timings <sup>*2</sup> in boot<br>operation mode                                                                                        | 01в              |                                                                                                       |                |

|                         |       |                                 |           |                          | Use dual data rate in boot operation                                                                                                                                        | 10 <sub>в</sub>  |                                                                                                       |                |

|                         |       |                                 |           | RESET_BOOT_<br>BUS_WIDTH | 2                                                                                                                                                                           | R/W/E            | Reset bus width to x1, single<br>data rate and backward<br>compatible timings after boot<br>operation | 0 <sub>B</sub> |

|                         |       |                                 |           |                          | Retain BOOT_BUS_WIDTH and<br>BOOT_MODE values after boot<br>operation                                                                                                       | 1в               |                                                                                                       |                |

|                         |       | BOOT_BUS_WI<br>DTH              | 1 to<br>0 | R/W/E                    | ×1 (sdr) or ×4 (ddr) bus width in boot operation mode                                                                                                                       | 00 <sub>B</sub>  |                                                                                                       |                |

|                         |       |                                 |           |                          | ×4 (sdr/ddr) bus width in boot operation mode                                                                                                                               | 01в              |                                                                                                       |                |

|                         |       |                                 |           |                          | ×8 (sdr/ddr) bus width in boot<br>operation mode                                                                                                                            | 10 <sub>в</sub>  |                                                                                                       |                |

| BOOT_WP                 | [173] | B_PWR_WP_DI<br>S <sup>*3</sup>  | 6         | R/W/C<br>_P              | Master is permitted to set<br>B_PWR_WP_EN                                                                                                                                   | Ов               |                                                                                                       |                |

|                         |       |                                 |           |                          | Disable B_PWR_WP_EN                                                                                                                                                         | 1 <sub>B</sub>   |                                                                                                       |                |

|                         |       | B_PREM_WP_<br>DIS <sup>∗4</sup> | 4         | R/W                      | Master is permitted to set<br>B_PREM_WP_EN                                                                                                                                  | 0в               |                                                                                                       |                |

|                         |       |                                 |           |                          | Disable B_PREM_WP_EN                                                                                                                                                        | 1 <sub>B</sub>   |                                                                                                       |                |

|                         |       | B_PREM_WP_<br>EN <sup>*5</sup>  | 2         | R/W                      | Boot region is not permanently write protected                                                                                                                              | 0в               |                                                                                                       |                |

|                         |       |                                 |           |                          | Boot region is permanently write protected                                                                                                                                  | 1в               |                                                                                                       |                |

|                         |       | B_PWR_WP_E<br>N <sup>*6</sup>   | 0         | R/W/C<br>_P              | Boot region is not power-on<br>write protected                                                                                                                              | 0в               |                                                                                                       |                |

|                         |       |                                 | ttings    |                          | Enable Power-On Period write<br>protection to the boot area                                                                                                                 | 1в               |                                                                                                       |                |

Notes: 1. The bolded values are the default settings after reset.

- 2. EXT\_CSD register byte [228] bit 2 tells the master if the high-speed timing during boot is supported by the device.

- 3. This bit must be zero if B\_PWR\_WP\_EN is set.

- 4. This bit must be zero if B\_PERM\_WP\_EN is set. This bit has no impact on the setting of CSD register byte [13].

- 5. This bit must be zero if B\_PERM\_WP\_DIS is set. This bit only indicates if permanent protection has been set specifically for the boot region. This bit may be zero if the whole card is permanently protected using CSD register byte [13].

- 6. This bit must be zero if B\_PWR\_WP\_DIS (bit 6) is set.

### 5.4.2 Card-Identification Mode

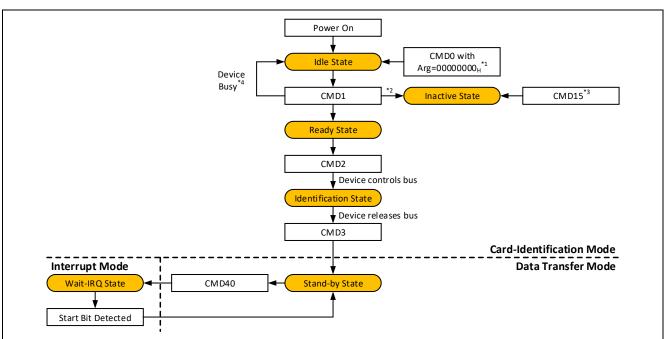

In card identification mode, the host resets the card, validates the operation voltage range and access mode, identifies the card and assigns a Relative Card Address (RCA) to the card on the bus. All data communication in the Card Identification Mode uses the command line (CMD) only.

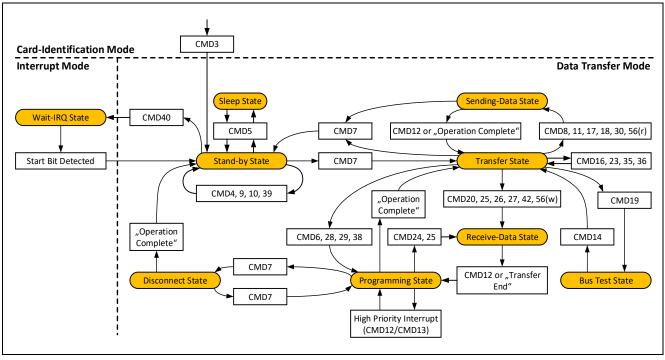

Figure 5-3 shows the state machine for card-identification mode.

- Notes: 1. If CMD0 with Arg=00000000H is sent to the MMC card, the card switches into Idle State from all states except from inactive state, and the operation mode switches from any other modes to Card-Identification Mode.

- 2. If the host cannot use a sector access mode (>2GB) in card, or the voltage range is not compatible, the card switches into Inactive State.

- If CMD15 is sent to the MMC card, the card switches into Inactive State from all states except in inactive state, the operation mode switches from any other modes to Card-Identification Mode. The CMD15 is used when the host explicitly wants to deactivate a device.

To access a device already in Inactive State, a hard reset must be done by switching the power supply off and back on.

4. If the slave is still working on its power-up/reset procedure and is not ready for communication, the host can get the state by reading the card power up status bit in the response of CMD1. In this case the host must repeat CMD1 until the card power up status bit is cleared. During the initialization procedure, the host is not allowed to change the operating voltage range or access mode setting. Such changes shall be ignored by the device. If there is a real change in the operating conditions, the host must reset the device and restart the initialization procedure.

#### Figure 5-3 Card-Identification Mode

The device moves into idle state within the following cases:

- After receiving a CMD0 with Arg=00000000<sub>H</sub> GO\_IDLE\_STATE.

- After completing the boot operation.

- After a CMD line low for less than 74 clocks in pre-boot state.

- After power up if the device is not boot enabled.

After the bus is activated, the host will request the eMMC card to send its valid operation conditions. The response to CMD1 is the wired-and operation on the condition restrictions of all slaves in the system. Incompatible devices are sent into inactive state.

The host then issues the broadcast command CMD2, asking all devices for its unique CID numbers to identify the device. All unidentified devices, which are ready, simultaneously start sending their CID numbers serially, while bit-wise monitoring their outgoing bit stream. The devices which successfully sends its full CID number to the host goes into identification state.

Then the host issues CMD3 to assign to this device a relative device address, which is shorter than CID and which will be used to address the device in the future data transfer mode. Once the RCA is received, the device state changes to the stand-by state, and the device does not react to further identification cycles.

The host repeats the identification process, until it receives a response to its identification command. The time-out condition to recognize completion of the identification process is the absence of a start bit for more than 5 clock cycles after sending CMD2.

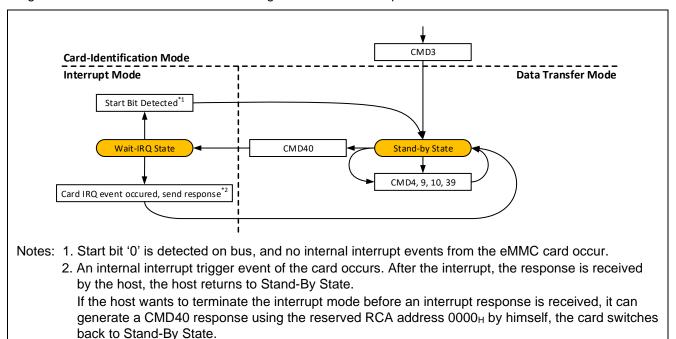

### 5.4.3 Interrupt Mode

The interrupt mode enables the host to grant the transmission allowance to the slaves simultaneously. This mode reduces the polling load for the host and hence, the power consumption of the system, while maintaining adequate responsiveness of the host to a card request for service.

Figure 5-4 shows the transformation among the states in interrupt mode.

Figure 5-4 Interrupt Mode

# 5.4.4 Data Transfer Mode

# 5.4.4.1 Data Transfer Mode

The card specific data, e.g. block length, storage capacity, clock rate, etc., can be issued in data transfer mode; and the communication between the host and slave is also included in this mode.

Figure 5-5 shows the state machine of data transfer mode.

Figure 5-5 Data Transfer Mode

### 5.4.4.2 Command sets and extended settings

The eMMC card operates in a given command set, by default, after a power cycle, a reset by CMD0 with an argument of 0x00000000 or after a boot operation, using a single data line DAT0. The host can change the active command set by issuing the SWITCH command CMD6 with a certain access mode<sup>\*Note</sup>. The supported command sets are defined in the EXT\_CSD register.

The EXT\_CSD register is divided into two segments, a properties segment and a modes segment. The properties segment contains information about the device capabilities, the modes segment reflects the current selected mode of the device.

The host reads the EXT\_CSD register by issuing the CMD8, SEND\_EXT\_CSD command. The device sends the EXT\_CSD register as a block of data, 512 bytes long. Any reserved, or write-only field, reads as '0'. The host can write the Modes segment of the EXT\_CSD register by issuing a SWITCH command and setting one of the access modes. All three modes access and modify one of the EXT\_CSD bytes, pointed to by the Index field.

The commands, their corresponding argument settings and responses are described in Section 5.5.

Note: In the Command set mode, the details of the access mode settings can be found in Table 5-3.

# 5.5 Commands and response

The MMCA module of the RH850/U2B devices are compliant with the JEDEC Standard JESD84-A441. All the commands are compliant also with the later JEDEC Standards, e.g. JESD84-B50.

### 5.5.1 Commands

All commands and responses are sent over the CMD line of the eMMC bus. The command transmission always starts with the left bit corresponding to the command codeword.

All commands have a fixed code length of 48 bits, including a start bit "0", a transmission bit "1", a command index, an argument, a CRC7 and an end bit "1". On RH850/U2B devices (host), the command sequence is configured in the register MMCAnCE\_CMD\_SET.

Table 5-3 lists the commands with the corresponding argument, response and register settings in the MCU.

| CMD  | Setting Value of<br>MMCAnCE_CMD_<br>SET Register | Response | Argument                                                                       | Abbreviation          | Command<br>Description                                                                                                               |

|------|--------------------------------------------------|----------|--------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                  | _        | [31:0] 00000000H                                                               | GO_IDLE_STATE         | Reset the card to idle state.                                                                                                        |

| CMD0 | 0000000н                                         | _        | [31:0] F0F0F0F0н                                                               | GO_PRE_IDLE_<br>STATE | Reset the card to pre-idle state.                                                                                                    |

|      | 400A0X0Y <sub>H</sub> *1                         |          | [31:0]<br>FFFFFFFA <sub>H</sub>                                                | BOOT_INITIATIO<br>N   | Initiate alternative boot operation.                                                                                                 |

| CMD1 | 01405000 <sub>H</sub>                            | R3       | [31] Set to 0<br>[30:0] OCR bit 30<br>to 0                                     | SEND_OP_CON<br>D      | Ask the card, in idle state, to<br>send its Operating Conditions<br>Register contained in the<br>response on the CMD line.           |

| CMD2 | 02806000 <sub>Н</sub>                            | R2       | [31:0] stuff bits                                                              | ALL_SEND_CID          | Ask the card to send its CID number on the CMD line.                                                                                 |

| CMD3 | 03400000н                                        | R1       | [31:16] RCA<br>[15:0] stuff bits                                               | SET_RELATIVE_<br>ADDR | Assign relative address RCA to the card.                                                                                             |

| CMD4 | 04000000 <sub>H</sub>                            | _        | [31:16] DSR<br>[15:0] stuff bits                                               | SET_DSR               | Program the DSR of the card.                                                                                                         |

| CMD5 | 05600000н                                        | R1b      | [31:16] RCA<br>[15] Sleep/Awake<br>[14:0] stuff bits                           | SLEEP_AWAKE           | Toggle the card between Sleep state and Standby state.                                                                               |

|      | 06400000н                                        | R1       | [31:26] Set to 0<br>[25:24] Access <sup>*4</sup>                               |                       | Switch the mode of operation of                                                                                                      |

| CMD6 | 06600000н                                        | R1b      | [23:16] Index <sup>*4</sup><br>[15:8] Value<br>[7:3] Set to 0<br>[2:0] CMD Set | SWITCH                | the selected card or modifies the EXT_CSD registers.                                                                                 |

| CMD7 | 07400000 <sub>Н</sub>                            | R1       | [31:16] RCA                                                                    | SELECT/DESELE         | Toggle a card between the<br>stand-by and transfer states or<br>between the programming and<br>disconnect states. In both cases      |

|      | 07600000H                                        | R1b      | [15:0] stuff bits                                                              | CT_CARD*5             | the card is selected by its own<br>relative address and gets<br>deselected by any other<br>address; address 0 deselects<br>the card. |

### Table 5-3 Commands Settings for RH850/U2B Device

# RH850/U2B

# Outline of eMMC Standards

| r        |                          |             |                                                                                                 |                                                                                                      | The cord cords its EVT COD                                                                                                          |

|----------|--------------------------|-------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| CMD8     | 0848000XH <sup>*2</sup>  | R1          | [31:0] stuff bits                                                                               | SEND_EXT_CSD                                                                                         | The card sends its EXT_CSD register as a block of data.                                                                             |

| CMD9     | 09806000н                | R2          | [31:16] RCA<br>[15:0] stuff bits                                                                | SEND_CSD                                                                                             | Addressed card sends its card-<br>specific data CSD on the CMD<br>line.                                                             |

| CMD10    | 0А806000н                | R2          | [31:16] RCA<br>[15:0] stuff bits                                                                | SEND_CID                                                                                             | Addressed card sends its card identification CID on CMD the line.                                                                   |

| CMD12    | 0С400000н                | R1          | [31:16] RCA3<br>[15:1] stuff bits                                                               | STOP_TRANSMI                                                                                         | Force the card to stop<br>transmission. If HPI flag is set,<br>the device shall interrupt its                                       |

| CIVID 12 | 0С600000н                | R1b         | [0] HPI                                                                                         | SSION                                                                                                | internal operations in a well-<br>defined timing.                                                                                   |

| CMD13    | 0D400000н                | R1          | [31:16] RCA<br>[15:1] stuff bits                                                                | SEND_STATUS                                                                                          | Addressed card sends its status<br>register. If HPI flag is set the<br>device shall interrupt its internal                          |

|          | 0D600000 <sub>H</sub>    | R1b         | [0] HPI                                                                                         | SEND_STATUS                                                                                          | operations in a well-defined timing.                                                                                                |

| CMD14    | 0E48040X <sub>H</sub> *3 | R1          | [31:0] stuff bits                                                                               | BUSTEST_R*6*7                                                                                        | A host reads the reversed bus testing data pat tern from a card.                                                                    |

| CMD15    | 0F000000н                | _           | [31:16] RCA<br>[15:0] stuff bits                                                                | GO_INACTIVE_S<br>TATE                                                                                | Set the card to inactive state.                                                                                                     |

| CMD16    | 10400000н                | R1          | [31:0] block length                                                                             | SET_BLOCKLEN<br>*7*10                                                                                | Set the block length (in bytes)<br>for all following block read/write<br>commands. Default block length<br>is specified in the CSD. |

| CMD17    | 1148000X <sub>H</sub> *2 | R1          | [31:0] data<br>address                                                                          | READ_SINGLE_<br>BLOCK <sup>*8</sup>                                                                  | Read a block of the size<br>selected by the<br>SET_BLOCKLEN command.                                                                |

| CMD18    | 124A000XH <sup>*2</sup>  | - R1        | [31:0] data                                                                                     | READ_MULTIPL                                                                                         | <b>Pre-Defined:</b> Continuously transfer data blocks from card to host until the requested number of data blocks is transmitted.   |

|          | 124B000XH <sup>*2</sup>  |             |                                                                                                 | address                                                                                              | E_BLOCK*8                                                                                                                           |

| CMD19    | 134C010X <sub>H</sub> *2 | R1          | [31:0] stuff bits                                                                               | BUSTEST_W*6*7                                                                                        | A host sends the bus test data pattern to a card.                                                                                   |

| CMD23    | 17400000н                | R1          | [31] Reliable<br>Write Request <sup>*11</sup><br>[30:16] set to 0<br>[15:0] number of<br>blocks | SET_BLOCK_CO<br>UNT                                                                                  | Define the number of read/write<br>blocks and the reliable write<br>parameter.                                                      |

| CMD24    | 184C000XH*2              | R1          | [31:0] data<br>address                                                                          | WRITE_SINGLE_<br>BLOCK <sup>*9</sup>                                                                 | Write a block of the size<br>selected by the<br>SET_BLOCKLEN command.                                                               |

| CMD25    | 194E000X <sub>H</sub> *2 | [31:0] data |                                                                                                 | <b>Pre-Defined:</b> Continuously write blocks of data until the requested number of blocks received. |                                                                                                                                     |

|          | 194F000Xн <sup>*2</sup>  |             | address                                                                                         | E_BLOCK <sup>*9</sup>                                                                                | <b>Open-ended:</b> Continuously<br>write blocks of data until a<br>STOP_TRANSMISSION follows.                                       |

| CMD26 | 1A4C000XH*2              | R1  | [31:0] stuff bits                                                                                                                                                                                                      | PROGRAM_CID'9                        | Programming of the card<br>identification register. This<br>command shall be issued only<br>once. The card contains<br>hardware to prevent this<br>operation after the first<br>programming. Normally this<br>command is reserved for the<br>manufacturer. |

|-------|--------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD27 | 1B4C000X <sub>H</sub> *2 | R1  | [31:0] stuff bits                                                                                                                                                                                                      | PROGRAM_CSD                          | Programming of the programmable bits of the CSD.                                                                                                                                                                                                           |

| CMD28 | 1С600000н                | R1b | [31:0] data<br>address                                                                                                                                                                                                 | SET_WRITE_PR<br>OT                   | If write protection feature is<br>provided, this command sets the<br>write protection bit of the<br>addressed group. The properties<br>of write protection are coded in<br>the CSD register.                                                               |

| CMD29 | 1D600000н                | R1b | [31:0] data<br>address                                                                                                                                                                                                 | CLR_WRITE_PR<br>OT                   | If the card provides write<br>protection features, this<br>command clears the write<br>protection bit of the addressed<br>group.                                                                                                                           |

| CMD30 | 1E48000Xн*²              | R1  | [31:0] write<br>protect data<br>address                                                                                                                                                                                | SEND_WRITE_P<br>ROT <sup>*8</sup>    | If the card provides write<br>protection features, this<br>command asks the card to send<br>the status of the write protection<br>bits.                                                                                                                    |

| CMD31 | 1F48000XH <sup>*2</sup>  | R1  | [31:0] write<br>protect data<br>address                                                                                                                                                                                | SEND_WRITE_P<br>ROT_TYPE             | Send the type of write protection<br>that is set for the different write<br>protection groups.                                                                                                                                                             |

| CMD35 | 23400000н                | R1  | [31:0] data<br>address                                                                                                                                                                                                 | ERASE_GROUP<br>_START <sup>*10</sup> | Set the address of the first erase<br>group within a range to be<br>selected for erase.                                                                                                                                                                    |

| CMD36 | 24400000н                | R1  | [31:0] data<br>address                                                                                                                                                                                                 | ERASE_GROUP<br>_END <sup>*10</sup>   | Set the address of the last erase<br>group within a continuous range<br>to be selected for erase.                                                                                                                                                          |

| CMD38 | 26600000 <sub>H</sub>    | R1b | <ul> <li>[31] Secure</li> <li>request</li> <li>[30:16] set to 0</li> <li>[15] Force</li> <li>garbage collect</li> <li>request</li> <li>[14:1] set to 0</li> <li>[0] Identify write</li> <li>block for erase</li> </ul> | ERASE                                | Erase all previously selected<br>write blocks according to<br>argument bits.                                                                                                                                                                               |

Outline of eMMC Standards

| CMD39 | 27400000 <sub>H</sub>   | R4                                  | [31:16] RCA<br>[15:15] register<br>write flag<br>[14:8] register<br>address<br>[7:0] register data | FAST_IO                                                                                                    | Used to write and read 8-bit<br>register data fields. The<br>command addresses a card and<br>a register and provides the data<br>for writing if the write flag is set.<br>The R4 response contains data<br>read from the addressed register<br>if the write flag is cleared to 0.<br>This command accesses<br>application dependent registers<br>which are not defined in the<br>Multimedia Card standard. |

|-------|-------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD40 | 28400000н               | Ps                                  | R5 [31:0] stuff bits                                                                               | GO_IRQ_STATE                                                                                               | Set the system into interrupt<br>mode. No IRQ defined for the<br>device, the device returns<br>standby state when start bit "0"<br>is detected.                                                                                                                                                                                                                                                            |

| CMD40 | 284000C0н               |                                     |                                                                                                    |                                                                                                            | Set the system into interrupt<br>mode. IRQ defined for the<br>device, the device returns<br>standby state by card IRQ<br>event.                                                                                                                                                                                                                                                                            |

| CMD42 | 2A4C000XH*2             | R1                                  | [31:0] stuff bits.                                                                                 | LOCK_UNLOCK'7                                                                                              | Used to set/reset the password<br>or lock/unlock the card. The size<br>of the data block is set by the<br>SET_BLOCK_LEN command.                                                                                                                                                                                                                                                                           |

| CMD55 | 37400000н               | R1                                  | [31:16] RCA<br>[15:0] stuff bits                                                                   | APP_CMD                                                                                                    | Indicate to the card that the next<br>command is an application<br>specific command rather than a<br>standard command.                                                                                                                                                                                                                                                                                     |

| CMD56 | 3848000XH <sup>*2</sup> | R1 [31:1] stuff bits.<br>[0]: RD/WR |                                                                                                    | Used to get a data block <sup>*12</sup> from the card for general purpose / application specific commands. |                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 384C000XH*2             |                                     |                                                                                                    | GEN_CMD                                                                                                    | Used to transfer a data block <sup>*12</sup> to the card the card for general purpose / application specific commands.                                                                                                                                                                                                                                                                                     |

Notes: 1. This command is used for alternative boot operation. In this table, it is ordered by CMD0 because of the command number; In RH850/U2B Hardware User's Manual *R01UH0923EJxxxx*, this command is called "Boot operation" in *Table 18.30 'Setting Values of MMCAnCE\_CMD\_SET'*. X=00X0<sub>B</sub>, the bit "X" enable/disables the boot acknowledge on host. If the boot acknowledge is enabled, the corresponding configuration to the card register EXT\_CSD should be done. For details, please refer to *Section 5.4.1.2 'Configuration of Boot Partition, Bus Width and Data Access'*.

$Y=00XX_B$ , the last 2 bits select the data bus width.

- X=00XX<sub>B</sub>, the last 2 bits select the data bus width. If the non-default bus width is selected, the connected eMMC device should also be configured to the same bus width in the extended CSD register.

- 3. X=10XX<sub>B</sub>, the last 2 bits select the data bus width. If the non-default bus width is selected, the connected eMMC device should also be configured to the same bus width in the extended CSD register.

- 4. The EXT\_CSD register access mode can be selected in bits [25:24] Access with the following values:

- 00<sub>B</sub>, Command Set Mode, the command set is changed according to the argument [2:0] CMD Set field.

- 01<sub>B</sub>, Set Bits Mode, the bits in the pointed byte are set according to "1" in Value field.

- 10<sub>B</sub>, Clear Bits Mode, the bits in the pointed byte are cleared according to "1" in Value field.

- 11<sub>B</sub>, Write Byte Mode, the Value field is written into the pointed byte.

- The bits [23:16] Index specify the pointed byte.

- 5. If the host switches another device from stand-by state to transfer state, using CMD7, the programming operation will be not terminated. The device will switch to disconnect state and release the DAT0 line.

A device can be reselected while in the disconnect state, using CMD7. In this case the device will move to the programming state and reactivate the busy indication.

- 6. To get a true result for the bus testing procedure, it is recommended to set up the clock frequency used for data transfer.

- 7. These commands are not allowed once the device is configured to operate in dual data rate mode and shall not be executed but regarded as illegal commands.

- 8. All data read commands can be aborted any time by the stop command CMD12. The data transfer will be terminated, and the device will return to the transfer state.

- No read commands are allowed while the device is programming.

- 9. All data write commands can be aborted any time by the stop command CMD12. The write commands must be stopped prior to deselecting the device by CMD7.

- 10. Parameter set commands are not allowed while the device is programming.

- 11. If reliable write is enabled for the pre-defined multi-block write, the old data pointed to by a logical address must remain unchanged until the new data written to same logical address has been successfully programmed. The data addressed by operation will never contain undefined data, even if unexpected reset or power loss occurs during the programming.

- 12. The size of the data block shall be set by the SET\_BLOCK\_LEN command.

### 5.5.2 Response

All responses are sent via the command line CMD. The response transmission always starts with the left bit corresponding to the response codeword.

The code length depends on the response type. A response always starts with a start bit "0", followed by the transmission bit "0". The responses except for the type R3 are protected by a CRC7. Every response codeword is terminated by the end bit "1".

At the RH850/U2B series, the information bits of the responses can be read from the registers MMCAnCE\_RESP3 to 0.

There are five types of responses, which is mentioned in Table 5-3:

• R1/R1b, Normal response command.

The code length is 48 bits, in which the bit 39 to 8 contains the card status after the corresponding commands. This 32-bit status can be read in the MMCAnCE\_RESP0 register.

R1b is identical to R1 with an optional busy signal transmitted on the data DAT0. For details of the card status please refer to Table 5-4.

• R2, CID/CSD register.

The code length is 136 bits. Bit 127 to 1 includes the CID or CSD register value including internal CRC7. These values are stored in the registers MMCAnCE\_RESP3 to 0.

• R3, OCR register.

The code length is 48 bits. The content of the OCR register is sent in bit 39 to 8, this 32-bit value is transmitted after the OCR related commands and stored in the MMCAnCE\_RESP0 register.

• R4, Fast I/O.

The code length is 48 bits. The bits 39 to 8 is the argument field, which contains the RCA number, status bit, as well as the register configuration. This field is stored in the MMCAnCE\_RESP0 register.

• R5, Interrupt request.

The code length is 48 bits. The bits 39 to 8 is the argument field, which includes the RCA number. This field can be stored in the MMCAnCE\_RESP0 register.

### Table 5-4 Card Status

| Bit Name             | Bit Position | Description                                                      | Value             |

|----------------------|--------------|------------------------------------------------------------------|-------------------|

| ADDRESS_OUT_OF_RANGE | 31           | No address range error occurs.                                   | 0в                |

|                      |              | Invalid address range is configured or                           |                   |

|                      |              | accessed by read/write.                                          | Ов                |

| ADDRESS_MISALIGN     | 30           | No address misalign error occurs.                                |                   |

|                      |              | Address misalign is configured or accessed by                    | 1в                |

|                      |              | read/write.                                                      |                   |

| BLOCK_LEN_ERROR      | 29           | No block length error occurs.                                    | 0 <sub>B</sub>    |

|                      |              | The argument of CMD6 or the pre-defined block length is invalid. | 1 <sub>B</sub>    |

| ERASE_SEQ_ERROR      | 28           | No sequence error of erase command occurs.                       | 0в                |

|                      |              | Error occurs in sequence of erase command.                       | 1 <sub>B</sub>    |

| ERASE_PARAM          | 27           | No erase parameter error occurs.                                 | 0в                |

|                      |              | Invalid selection of erase parameters is done.                   | 1 <sub>B</sub>    |

| WP_VIOLATION         | 26           | No write protection violation error occurs.                      | 0в                |

|                      |              | Error occurs by programing protected block.                      | 1 <sub>B</sub>    |

| CARD_IS_LOCKED       | 25           | Card is unlocked.                                                | 0в                |

|                      |              | Card is locked.                                                  | 1 <sub>B</sub>    |

| LOCK UNLOCK FAILED   | 24           | No lock/unlock error occurs.                                     | 0в                |

|                      |              | A sequence or password error is detected by                      | 1 <sub>B</sub>    |

|                      |              | lock/unlock card command.                                        |                   |

| COM CRC ERROR        | 23           | No CRC error occurs.                                             | 0в                |

|                      | -            | The CRC check of previous command failed.                        | 1 <sub>B</sub>    |

| ILLEGAL_COMMAND      | 22           | No illegal commands are discovered.                              | 0в                |

|                      |              | Illegal command sent for the card state.                         | 1 <sub>B</sub>    |

| CARD_ECC_FAILED      | 21           | No card ECC error occurs.                                        | 0в                |

| •····                |              | Card internal ECC was applied but failed to                      | 1 <sub>в</sub>    |

|                      |              | correct the data.                                                |                   |

| CC_ERROR             | 20           | No error occurs.                                                 | 0в                |

| _                    |              | A card error NOT related to the host command occurs.             | 1в                |

| ERROR                | 19           | No error occurs.                                                 | 0в                |

| 2111.011             | 10           | A generic error related to execution of the last                 | <u>1</u> в        |

|                      |              | host command occurs.                                             | 10                |

| CID/CSD OVERWRITE    | 16           | No error occurs.                                                 | 0в                |

|                      | -            | The CID register has been already written                        | 1в                |

|                      |              | and cannot be overwritten.                                       |                   |

|                      |              | • Or the read only section of the CSD does                       |                   |

|                      |              | not match the card content.                                      |                   |

|                      |              | Or an attempt to reverse the copy or                             |                   |

|                      |              | permanent write protection bits was made.                        |                   |

| WP_ERASE_SKIP        | 15           | No error occurs.                                                 | 0 <sub>B</sub>    |

|                      |              | Only partial address space was erased due to                     | 1в                |

|                      |              | existing write protected blocks.                                 |                   |

| ERASE_RESET          | 13           | No error occurs.                                                 | 0в                |

|                      |              | Erase sequence was cleared before executing                      | 1в                |

|                      |              | because a no-erase-sequence command was                          |                   |

|                      |              | received.                                                        |                   |

| CURRENT_STATE        | 12 to 9      | Idle State                                                       | 0000 <sub>B</sub> |

|                      |              | Ready State                                                      | 0001 <sub>B</sub> |

|                |   |                                                                                  | 0040              |

|----------------|---|----------------------------------------------------------------------------------|-------------------|

|                |   | Identification State                                                             | 0010в             |

|                |   | Stand-by State                                                                   | <b>0011</b> в     |

|                |   | Transfer State                                                                   | 0100в             |

|                |   | Sending-data State                                                               | 0101в             |

|                |   | Receive-data State                                                               | 0110в             |

|                |   | Programming State                                                                | 0111в             |