# RH850/F1Kx, RH850/F1K Series

# Hardware Design Guide

R01AN3841ED0120 Rev. 1.20 February 03, 2021

#### Introduction

This application note is intended to provide RH850/F1Kx, RH850/F1K series specific information and recommendations on the device usage. It should be used in conjunction with the corresponding RH850/F1Kx, RH850/F1K series user manual (includes the electrical characteristics).

## **Target Device**

RH850/F1Kx Series

- RH850/F1KM Group

- o RH850/F1KM-S1

- 100pin

- 80pin

- 64pin

- 48pin

- o RH850/F1KM-S2

- 176pin

- 144pin

- 100pin

- o RH850/F1KM-S4

- 272pin

- 233pin

- 176pin

- 144pin

- 100pin

- RH850/F1KH Group

- RH850/F1KH-D8

- 324pin

- 233pin

- 176pin

- RH850/F1K Series

- RH850/F1K Group

- 176pin

- 144pin

- 100pin

## Disclaimer:

Renesas Electronics does not warrant the information included in this document. You are fully responsible for incorporation of these circuits, software, and information in the design of your

equipment and system. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

# **Table of Contents**

| 1.    | Power Supply                                                            | 11 |

|-------|-------------------------------------------------------------------------|----|

| 1.1   | Power Supply Overview of RH850/F1KM-S1                                  | 11 |

| 1.1.1 | Power Supply Pin Overview of RH850/F1KM-S1                              | 11 |

| 1.1.2 | Power Supply Pin Configuration of RH850/F1KM-S1                         | 12 |

| 1.1.3 | Power Supply Pin Architecture of RH850/F1KM-S1                          | 12 |

| 1.1.4 | Power Supply Timing of RH850/F1KM-S1                                    | 15 |

| 1.2   | Power Supply Overview of RH850/F1KM-S2                                  | 17 |

| 1.2.1 | Power Supply Pin Overview of RH850/F1KM-S2                              | 17 |

| 1.2.2 | Power Supply Pin Configuration of RH850/F1KM-S2                         | 18 |

| 1.2.3 | Power Supply Pin Architecture of RH850/F1KM-S2                          | 18 |

| 1.2.4 | Power Supply Timing of RH850/F1KM-S2                                    | 29 |

| 1.3   | Power Supply Overview of RH850/F1KM-S4                                  | 31 |

| 1.3.1 | Power Supply Pin Overview of RH850/F1KM-S4                              | 31 |

| 1.3.2 | Power Supply Pin Configuration of RH850/F1KM-S4                         | 32 |

| 1.3.3 | Power Supply Pin Architecture of RH850/F1KM-S4                          | 32 |

| 1.3.4 | Power Supply Timing of RH850/F1KM-S4                                    | 43 |

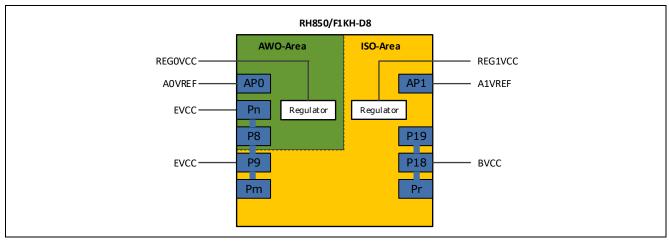

| 1.4   | Power Supply Overview of RH850/F1KH-D8                                  | 45 |

| 1.4.1 | Power Supply Pin Overview of RH850/F1KH-D8                              | 45 |

| 1.4.2 | Power Supply Pin Configuration of RH850/F1KH-D8                         | 46 |

| 1.4.3 | Power Supply Pin Architecture of RH850/F1KH-D8                          | 46 |

| 1.4.4 | Power Supply Timing of RH850/F1KH-D8                                    | 57 |

| 1.5   | Power Supply Overview of RH850/F1K                                      | 60 |

| 1.5.1 | Power Supply Pin Overview of RH850/F1K                                  | 60 |

| 1.5.2 | Power Supply Pin Configuration of RH850/F1K                             | 61 |

| 1.5.3 | Power Supply Pin Architecture of RH850/F1K                              | 61 |

| 1.5.4 | Power Supply Timing of RH850/F1K                                        | 67 |

| 1.6   | Principle Capacitor Placement at REGVCC of RH850/F1Kx, RH850/F1K Series | 69 |

| 2.    | Minimum External Components                                             | 70 |

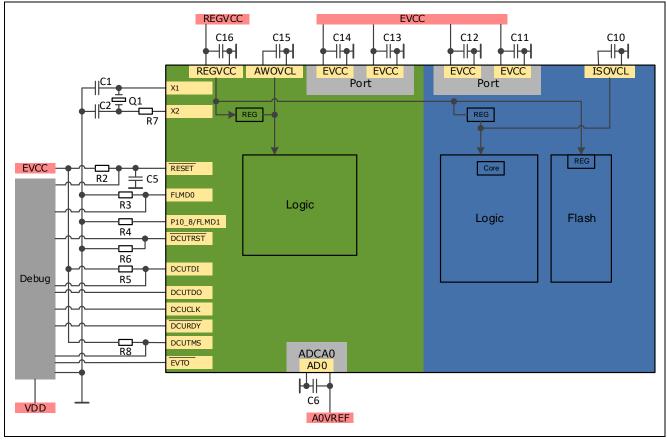

| 2.1   | Minimum External Components of RH850/F1KM-S1                            | 70 |

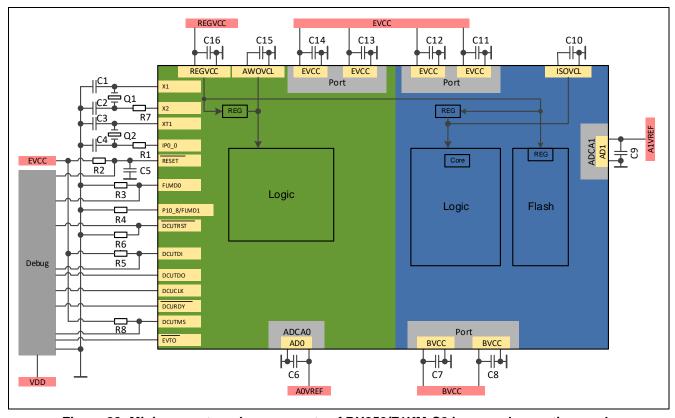

| 2.2   | Minimum External Components of RH850/F1KM-S2                            | 73 |

| 2.3   | Minimum External Components of RH850/F1KM-S4                            | 76 |

| 2.4   | Minimum External Components of RH850/F1KH-D8                            | 79 |

| 2.5   | Minimum External Components of RH850/F1K                                | 82 |

| 3.    | Oscillator                                                              | 85 |

| 3.1   | Recommended Oscillator Circuit                                          | 85 |

| 3.1.1 | Main Oscillator                                                         | 85 |

| 3.1.2 | Sub Oscillator                                                          | 86 |

| 3.2   | Recommended Oscillator Layout                                           | 87 |

| 4.    | Device Pins                                               | 88  |

|-------|-----------------------------------------------------------|-----|

| 4.1   | X1                                                        | 88  |

| 4.1.1 | 1 Direct Clock Supply to X1                               | 88  |

| 4.2   | RESET                                                     | 89  |

| 4.2.1 | 1 Minimum RESET Circuit                                   | 89  |

| 4.2.2 | 2 RESET Input Characteristics                             | 90  |

| 4.3   | General Purpose I/O                                       | 91  |

| 4.3.1 | 1 RESET State of General Purpose I/P                      | 91  |

| 4.3.2 | 2 JP0_4/ <u>DCUTRST</u>                                   | 91  |

| 4.3.3 | B P8_6/ RESETOUT                                          | 91  |

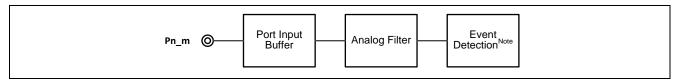

| 4.3.4 | 4 Analog Filter Function                                  | 92  |

| 4.3.5 | 5 Port and Pin Behavior during Low Power Mode             | 93  |

| 4.4   | Recommended Connection of Unused Pins                     | 94  |

| 4.4.1 | Recommended Connection of Unused Pins for RH850/F1KM-S1   | 94  |

| 4.4.2 | Recommended Connection of Unused Pins for RH850/F1KM-S2   | 96  |

| 4.4.3 | Recommended Connection of Unused Pins for RH850/F1KM-S4   | 98  |

| 4.4.4 | Recommended Connection of Unused Pins for RH850/F1KH-D8   | 100 |

| 4.4.5 | Recommended Connection of Unused Pins for RH850/F1K       | 102 |

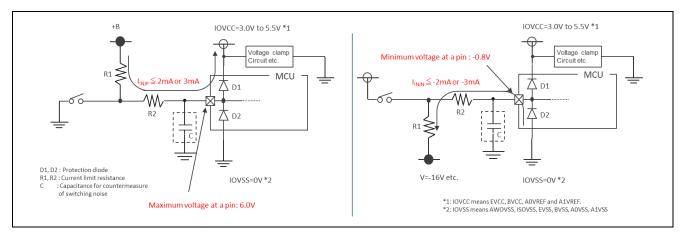

| 4.5   | Injected Current                                          | 104 |

| 5.    | SENT Interface (RH850/F1Kx Series only)                   | 105 |

| 6.    | AD-Converter                                              | 106 |

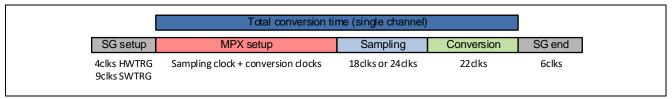

| 6.1   | Conversion time                                           | 106 |

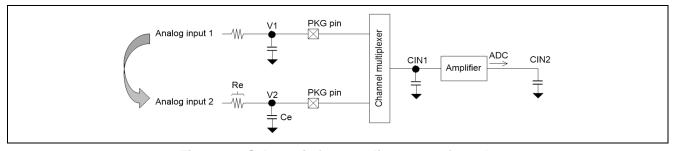

| 6.2   | External Multiplexer Wait Time                            | 107 |

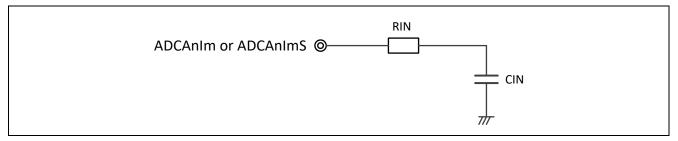

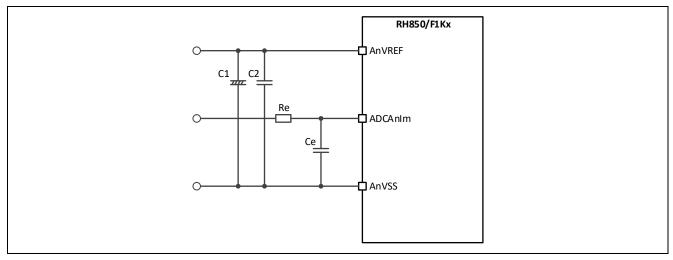

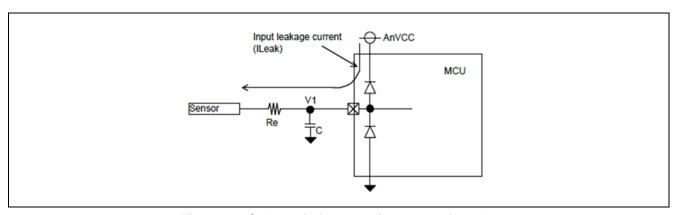

| 6.3   | Equivalent Input Circuit                                  | 107 |

| 6.4   | External Circuit on ADC Input                             | 108 |

| 6.5   | Formulas for sampling error                               | 109 |

| 7.    | Device Operation Modes                                    | 111 |

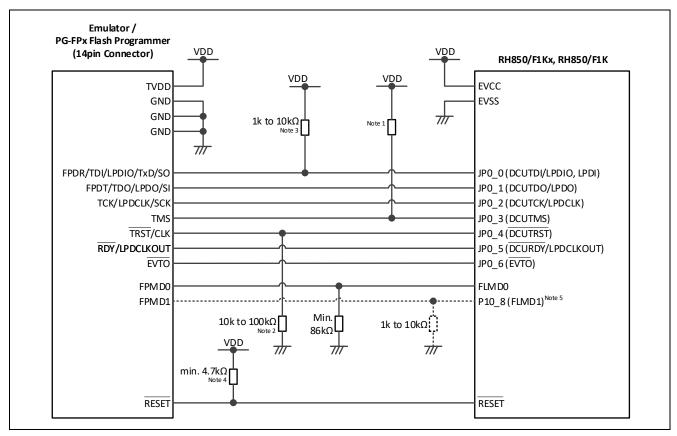

| 8.    | Development Tool Interface                                | 112 |

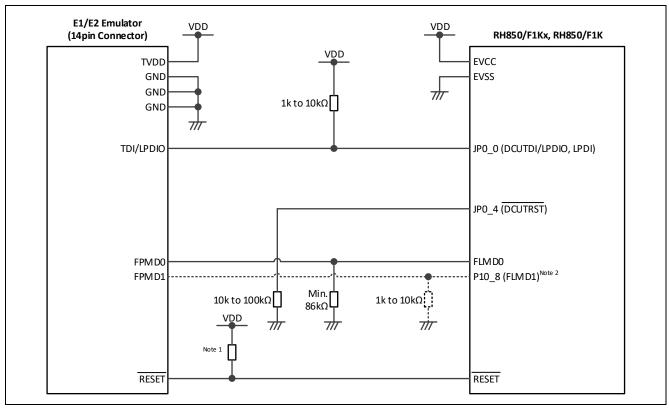

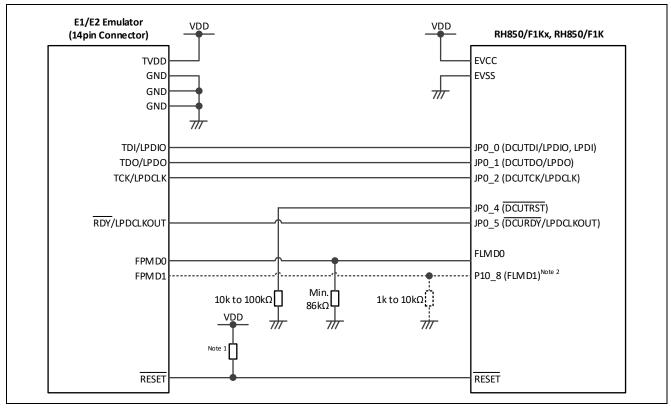

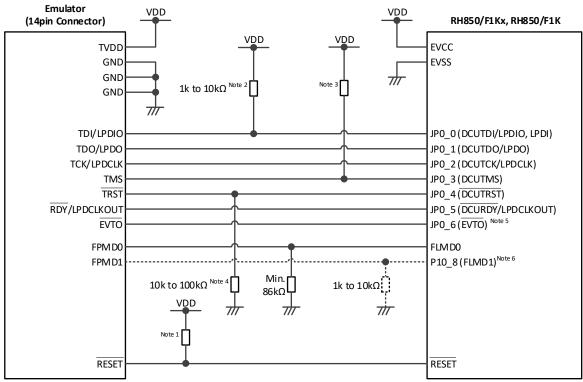

| 8.1   | Debug Interface Connection                                | 112 |

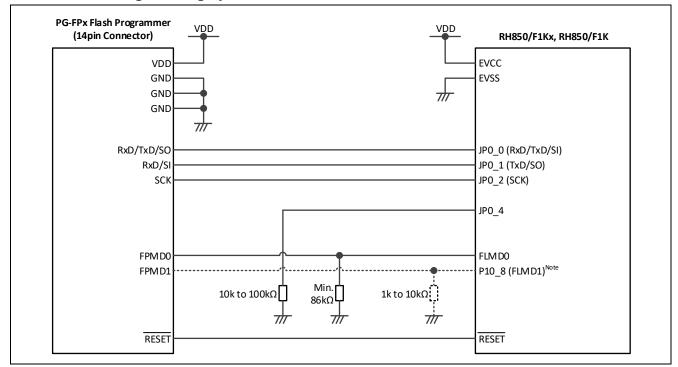

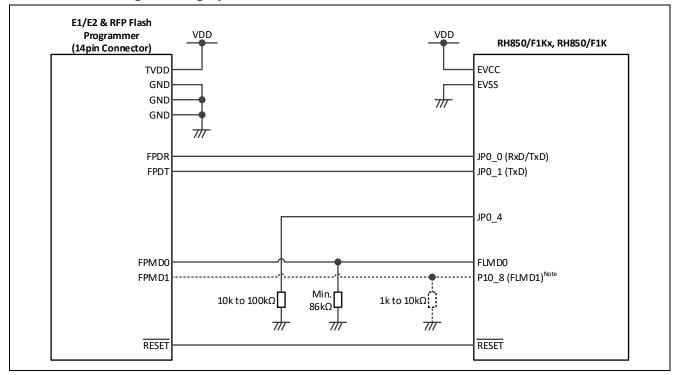

| 8.2   | Flash Programming Interface                               | 117 |

| 8.2.1 | 1 Flash Programming by PG-FPx                             | 118 |

| 8.2.2 | 2 Flash Programming by E1/E2 Emulator and RFP             | 119 |

| 8.3   | Combined Debug and Flash Programming Interface Connection | 120 |

| 8.4   | Debug Considerations when Hot Plug-in is used             | 122 |

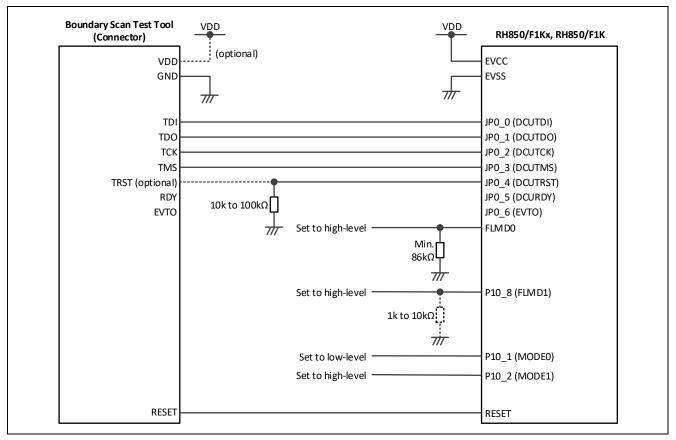

| 9.    | Test Tool Interface                                       | 123 |

| 10.   | Differences to RH850/F1L/M/H, RH850/F1Kx and RH850/F1K    | 124 |

| 11    | Reference Documents                                       | 125 |

# **Table of Figures**

| Figure 1: RH850/F1KM-S1 Power supply architecture                                 | 12  |

|-----------------------------------------------------------------------------------|-----|

| Figure 2: Recommended REGVCC power configuration for RH850/F1KM-S1                | 15  |

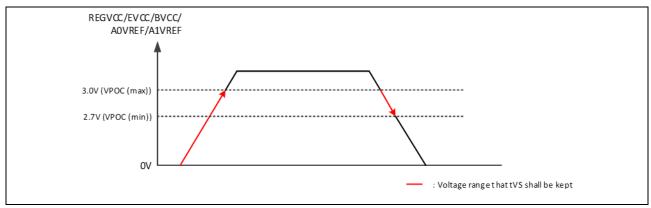

| Figure 3: The voltage range which has to be kept voltage slope for RH850/F1KM-S1  | 15  |

| Figure 4: RH850/F1KM-S1 Power up/down timing                                      | 16  |

| Figure 5: RH850/F1KM-S1 Power up/down timing                                      | 16  |

| Figure 6: RH850/F1KM-S2 Power supply architecture                                 | 18  |

| Figure 7: Recommended REGVCC power configuration for RH850/F1KM-S2                | 29  |

| Figure 8: The voltage range which has to be kept voltage slope for RH850/F1KM-S2  | 29  |

| Figure 9: RH850/F1KM-S2 Power up/down timing                                      | 30  |

| Figure 10: RH850/F1KM-S2 Power up/down timing                                     | 30  |

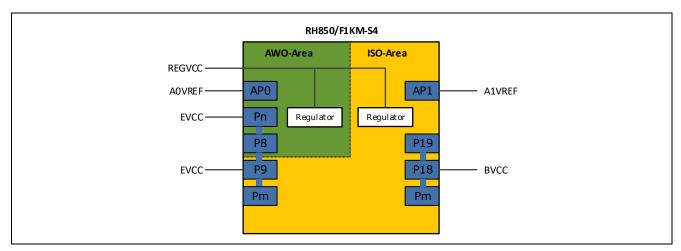

| Figure 11: RH850/F1KM-S4 Power supply architecture                                | 32  |

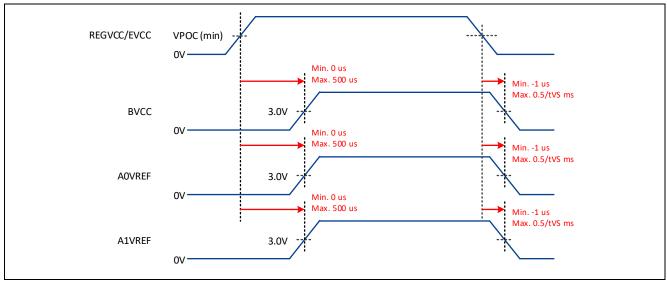

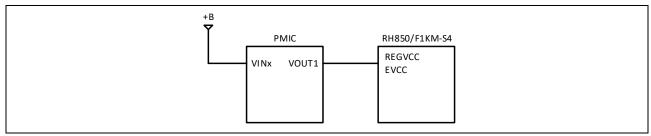

| Figure 12: Recommended REGVCC power configuration for RH850/F1KM-S4               | 43  |

| Figure 13: The voltage range which has to be kept voltage slope for RH850/F1KM-S4 | 43  |

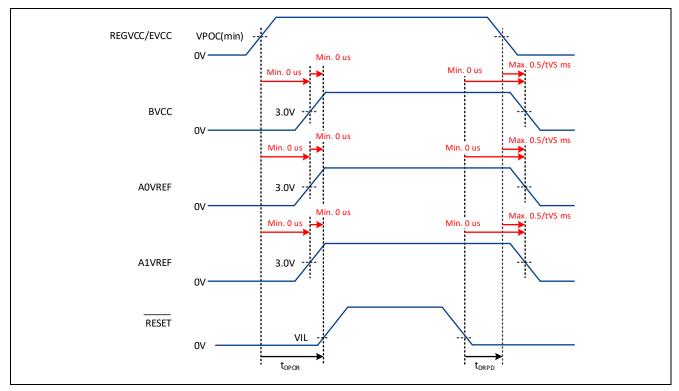

| Figure 14: RH850/F1KM-S4 Power up/down timing                                     | 44  |

| Figure 15: RH850/F1KM-S4 Power up/down timing                                     | 44  |

| Figure 16: RH850/F1KH-D8 Power supply architecture                                | 46  |

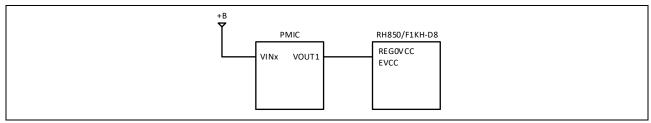

| Figure 17: Recommended REG0VCC power configuration for RH850/F1KH-D8              | 57  |

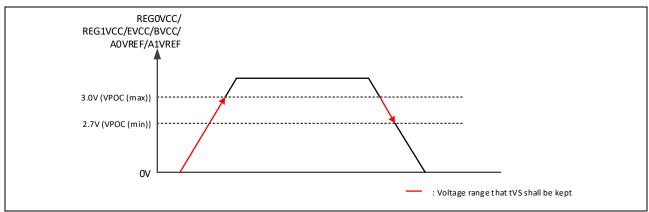

| Figure 18: The voltage range which has to be kept voltage slope for RH850/F1KH-D8 | 57  |

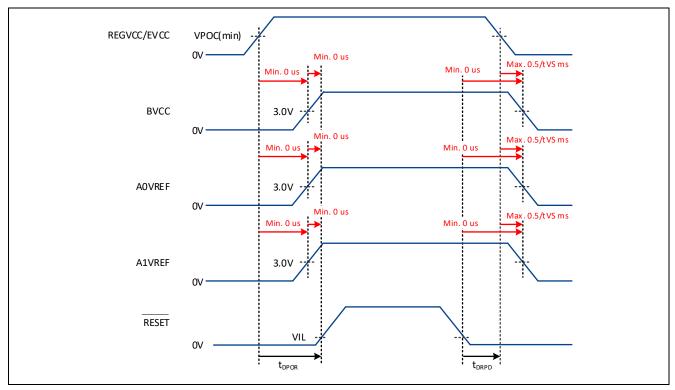

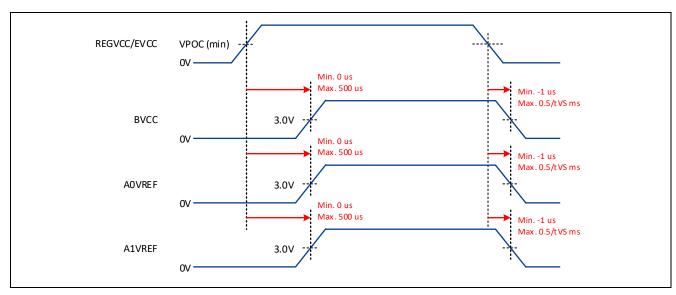

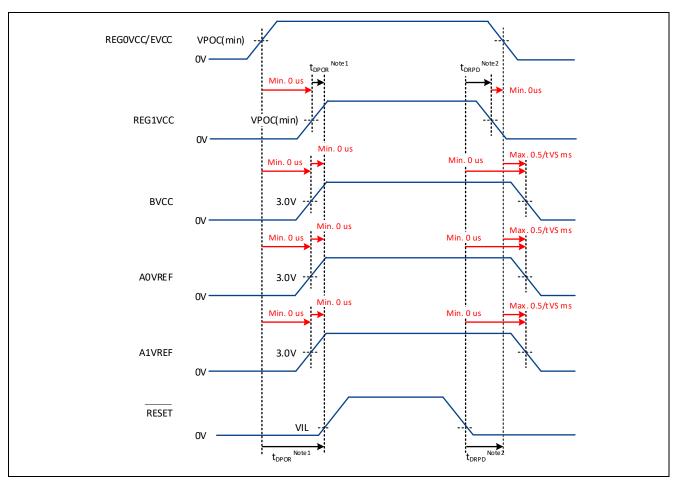

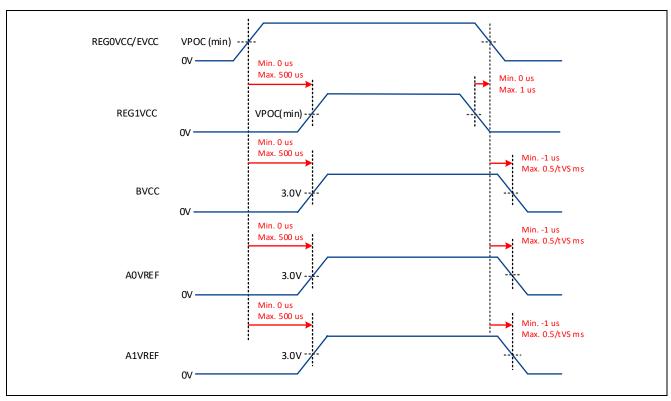

| Figure 19: RH850/F1KH-D8 Power up/down timing                                     | 58  |

| Figure 20: RH850/F1KH-D8 Power up/down timing                                     | 59  |

| Figure 21: RH850/F1K Power supply architecture                                    | 61  |

| Figure 22: Recommended REGVCC power configuration for RH850/F1K                   | 67  |

| Figure 23: The voltage range which has to be kept voltage slope for RH850/F1K     | 67  |

| Figure 24: RH850/F1K Power up/down timing                                         | 68  |

| Figure 25: RH850/F1K Power up/down timing                                         | 68  |

| Figure 26: Principle capacitor placement at REGVCC for EMI                        | 69  |

| Figure 27: Minimum external components of RH850/F1KM-S1 in normal operating mode  | 70  |

| Figure 28: Minimum external components of RH850/F1KM-S2 in normal operating mode  | 73  |

| Figure 29: Minimum external components of RH850/F1KM-S4 in normal operating mode  | 76  |

| Figure 30: Minimum external components of RH850/F1KH-D8 in normal operating mode  | 79  |

| Figure 31: Minimum external components of RH850/F1K in normal operating mode      | 82  |

| Figure 32: Recommended main oscillator circuit                                    | 85  |

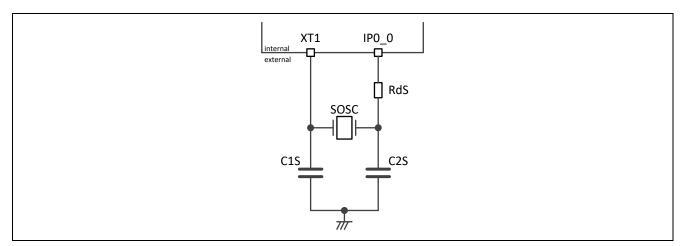

| Figure 33: Recommended sub oscillator circuit                                     | 86  |

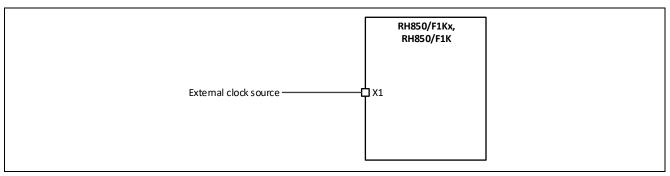

| Figure 34: Direct clock supply to X1 (MOSC)                                       | 88  |

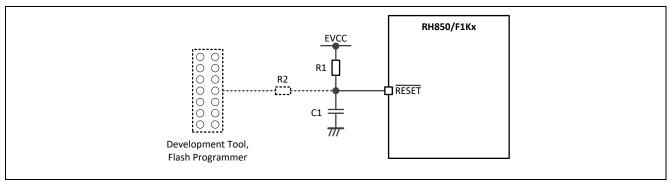

| Figure 35: Minimum RESET circuit                                                  | 89  |

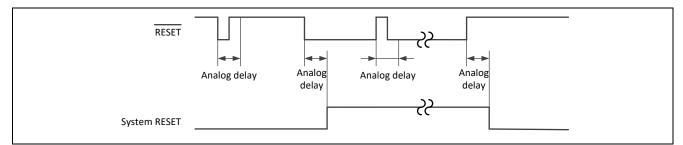

| Figure 36: External RESET timing                                                  | 90  |

| Figure 37: Analog filter function                                                 | 92  |

| Figure 38: Mechanism of injection current                                         | 104 |

|                                                                                   |     |

| Figure 39: ADC conversion time                                         | 106   |

|------------------------------------------------------------------------|-------|

| Figure 40: ADC equivalent input circuit                                | . 107 |

| Figure 41: ADC external circuit on analog input                        | 108   |

| Figure 42: Schematic for sampling error 1 formula                      | . 109 |

| Figure 43: Schematic for sampling error 2 formula                      | . 110 |

| Figure 44: LPD (1 pin) connection                                      | . 112 |

| Figure 45: LPD (4 pins) connection                                     | . 114 |

| Figure 46: Nexus, LPD (4 pins) and LPD (1 pin) connection              | . 115 |

| Figure 47: PG-FPx flash programming interface connection               | . 118 |

| Figure 48: E1/E2 flash programming interface connection                | . 119 |

| Figure 49: Combined debug and flash programming interface connections  | . 120 |

| Figure 50: Circuit configuration for hot plug-in                       | 122   |

| Figure 51: Boundary scan connection of RH850/F1Kx and RH850/F1K series | . 123 |

# **Table of Tables**

| Table 1: RH850/F1KM-S1 Power supply pin overview                              | 11 |

|-------------------------------------------------------------------------------|----|

| Table 2: RH850/F1KM-S1 Overview of power supply architecture cases            | 13 |

| Table 3: RH850/F1KM-S1 Power supply architecture with single supply 5V        | 13 |

| Table 4: RH850/F1KM-S1 Power supply architecture with mixed supply 5V & 3.3V  | 13 |

| Table 5: RH850/F1KM-S1 Power supply architecture with mixed supply 5V & 3.3V  | 14 |

| Table 6: RH850/F1KM-S1 Power supply architecture with mixed supply 5V & 3.3V  | 14 |

| Table 7: RH850/F1KM-S1 Power supply architecture with single supply 3.3V      | 14 |

| Table 8: RH850/F1KM-S2 Power supply pin overview                              | 17 |

| Table 9: RH850/F1KM-S2 Overview of power supply architecture cases            | 19 |

| Table 10: RH850/F1KM-S2 Power supply architecture with single supply 5V       | 19 |

| Table 11: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V | 20 |

| Table 12: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V | 20 |

| Table 13: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V | 21 |

| Table 14: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V | 22 |

| Table 15: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V | 23 |

| Table 16: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V | 24 |

| Table 17: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V | 25 |

| Table 18: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V | 25 |

| Table 19: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V | 25 |

| Table 20: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V | 26 |

| Table 21: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V | 27 |

| Table 22: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V | 28 |

| Table 23: RH850/F1KM-S2 Power supply architecture with single supply 3.3V     | 28 |

| Table 24: RH850/F1KM-S4 Power supply pin overview                             | 31 |

| Table 25: RH850/F1KM-S4 Overview of power supply architecture cases           | 33 |

| Table 26: RH850/F1KM-S4 Power supply architecture with single supply 5V       | 33 |

| Table 27: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V | 34 |

| Table 28: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V | 34 |

| Table 29: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V | 35 |

| Table 30: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V | 36 |

| Table 31: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V | 37 |

| Table 32: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V | 38 |

| Table 33: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V | 39 |

| Table 34: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V | 39 |

| Table 35: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V | 39 |

| Table 36: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V | 40 |

| Table 37: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V | 41 |

| Table 38: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V | 42 |

|                                                                               |    |

| Table 39: RH850/F1KM-S4 Power supply architecture with single supply 3.3V     | 42 |

|-------------------------------------------------------------------------------|----|

| Table 40: RH850/F1HM-D8 Power supply pin overview                             | 45 |

| Table 41: RH850/F1KH-D8 Overview of power supply architecture cases           | 47 |

| Table 42: RH850/F1KH-D8 Power supply architecture with single supply 5V       | 47 |

| Table 43: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 48 |

| Table 44: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 48 |

| Table 45: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 49 |

| Table 46: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 49 |

| Table 47: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 50 |

| Table 48: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 50 |

| Table 49: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 51 |

| Table 50: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 52 |

| Table 51: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 52 |

| Table 52: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 52 |

| Table 53: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 53 |

| Table 54: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 53 |

| Table 55: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 54 |

| Table 56: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 55 |

| Table 57: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V | 56 |

| Table 58: RH850/F1KH-D8 Power supply architecture with single supply 3.3V     | 56 |

| Table 59: RH850/F1K Power supply pin overview                                 | 60 |

| Table 60: RH850/F1K Overview of power supply architecture cases               | 62 |

| Table 61: RH850/F1K Power supply architecture with single supply 5V           | 62 |

| Table 62: RH850/F1K Power supply architecture with mixed supply 5V & 3.3V     | 62 |

| Table 63: RH850/F1K Power supply architecture with mixed supply 5V & 3.3V     | 63 |

| Table 64: RH850/F1K Power supply architecture with mixed supply 5V & 3.3V     | 63 |

| Table 65: RH850/F1K Power supply architecture with mixed supply 5V & 3.3V     | 63 |

| Table 66: RH850/F1K Power supply architecture with mixed supply 5V & 3.3V     | 64 |

| Table 67: RH850/F1K Power supply architecture with mixed supply 5V & 3.3V     | 65 |

| Table 68: RH850/F1K Power supply architecture with mixed supply 5V & 3.3V     | 66 |

| Table 69: RH850/F1K Power supply architecture with single supply 3.3V         | 66 |

| Table 70: Minimum external components of RH850/F1KM-S1 (100pin)               | 71 |

| Table 71: Minimum external components for RH850/F1KM-S2 (176pin)              | 74 |

| Table 72: Minimum external components for RH850/F1KM-S4 (272pin)              | 77 |

| Table 73: Minimum external components for RH850/F1KH-D8 (324pin)              | 80 |

| Table 74: Minimum external components for RH850/F1K (176pin)                  | 83 |

| Table 75: Guidance values of the main oscillator circuit                      | 85 |

| Table 76: Guidance values of the sub oscillator circuit                       | 86 |

| Table 77: Guidance values for the minimum RESET circuit                       | 89 |

| Table 78: Port and pin behavior during low power mode                         | 93 |

| Table 79: Recommended connection of unused pins for RH850/F1KM-S1 | 94  |

|-------------------------------------------------------------------|-----|

| Table 80: Recommended connection of unused pins for RH850/F1KM-S2 | 96  |

| Table 81: Recommended connection of unused pins for RH850/F1KM-S4 | 98  |

| Table 82: Recommended connection of unused pins for RH850/F1KH-D8 | 100 |

| Table 83: Recommended connection of unused pins for RH850/F1K     | 102 |

| Table 84: ADC conversion time overview                            | 106 |

| Table 85: Basic external ADC input circuit                        | 108 |

| Table 86: Device operation mode overview                          | 111 |

| Table 87: Device operation mode description                       | 111 |

| Table 88: Debug interface signal connection                       | 116 |

| Table 89: Basic flash programming connection                      | 117 |

| Table 90: PG-FPx Flash programming signal connection              | 118 |

| Table 91: E1/E2 Flash programming signal connection               | 119 |

| Table 92: Basic component value for hot plug-in                   | 122 |

## 1. Power Supply

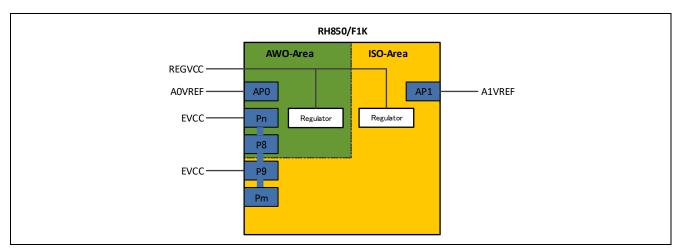

The internal circuits are separated into two independent power domains, the Always-On area (AWO area) and the Isolated area (ISO area). The power supply of the Always-On area (AWO area) is always on in all operating modes and stand-by modes. The power supply of the Isolated area (ISO area) can be turned off to reduce the overall power consumption depending on the type of stand-by mode. For each power domain, a dedicated on-chip voltage regulator generates the internal supply voltage.

## 1.1 Power Supply Overview of RH850/F1KM-S1

#### 1.1.1 Power Supply Pin Overview of RH850/F1KM-S1

The devices of the RH850/F1KM-S1 have the following power supply pins:

- Power supply voltage REGVCC for the on-chip voltage regulators. The output voltage of the voltage regulators is supplied to the digital circuits in each power domain.

- Power supply voltage EVCC for I/O ports.

- Power supply voltage A0VREF for the A/D converters and the separated I/O ports.

Table 1: RH850/F1KM-S1 Power supply pin overview

| Device                 | Power Supply Pins               |

|------------------------|---------------------------------|

| RH850/F1KM-S1 (100pin) | REGVCC                          |

|                        | AWOVCL <sup>Note</sup> , AWOVSS |

|                        | ISOVCL <sup>Note</sup> , ISOVSS |

|                        | EVCC, EVSS                      |

|                        | A0VREF, A0VSS                   |

| RH850/F1KM-S1 (64pin)  | REGVCC                          |

|                        | AWOVCL <sup>Note</sup> , AWOVSS |

|                        | ISOVCL <sup>Note</sup> , ISOVSS |

|                        | EVCC, EVSS                      |

|                        | A0VREF, A0VSS                   |

| RH850/F1KM-S1 (48pin)  | REGVCC                          |

|                        | AWOVCL <sup>Note</sup> , AWOVSS |

|                        | ISOVCL <sup>Note</sup> , ISOVSS |

|                        | EVCC, EVSS                      |

|                        | A0VREF, A0VSS                   |

Note: The pins AWOVCL and ISOVCL are available on all devices to connect external stabilization capacitors. Do not use AWOVCL and ISOVCL as power source of other devices.

RENESAS

#### 1.1.2 Power Supply Pin Configuration of RH850/F1KM-S1

The following shows power supply pin configuration. Do not open any power and GND terminals even if those are internally connected.

- The EVCC supply pins are internally connected.

- The EVSS pins are internally connected.

- AWOVSS and ISOVSS are internally connected.

- · Others are not internally connected.

#### 1.1.3 Power Supply Pin Architecture of RH850/F1KM-S1

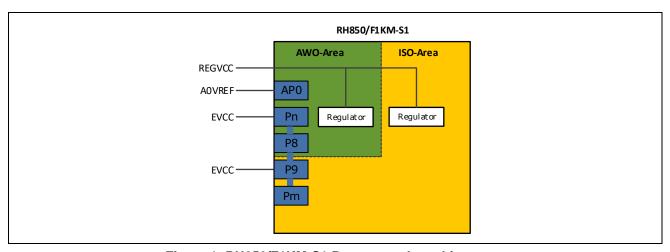

The RH850/F1KM-S1 supports different power supply architectures. The power supply architecture depends on the application requirements and the use case.

Some common conditions apply to the supply of the RH850/F1KM-S1:

- REGVCC = EVCC = VPOC to 5.5V

- A0VREF = 3.0V to 5.5V

- AWOVSS = ISOVSS = EVSS = A0VSS = 0V

The following figure and the different cases describe the impact to the ADC ports and the ports with analog/digital function depending on the power supply architecture. In addition, it describes the limitations to these ports.

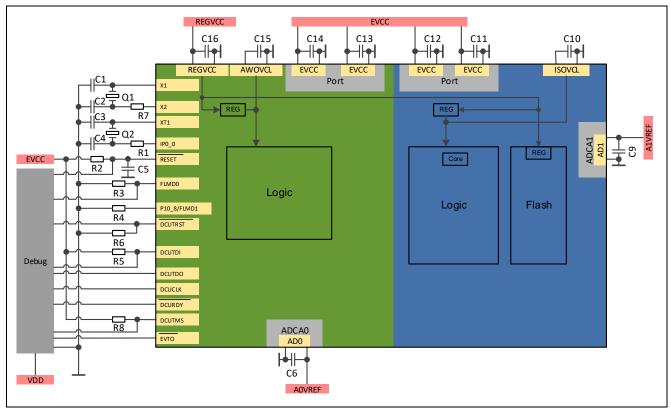

Figure 1: RH850/F1KM-S1 Power supply architecture

Table 2: RH850/F1KM-S1 Overview of power supply architecture cases

| Case   | Supply Voltage |      |        | Permission              |

|--------|----------------|------|--------|-------------------------|

| Case   | REGVCC         | EVCC | A0VREF | - Fermission            |

| Case 1 | 5V             | 5V   | 5V     | Operation permitted     |

| Case 2 | 5V             | 5V   | 3.3V   | Operation permitted     |

| Case 3 | 5V             | 3.3V | *      | Operation not permitted |

| Case 4 | 3.3V           | 5V   | *      | Operation not permitted |

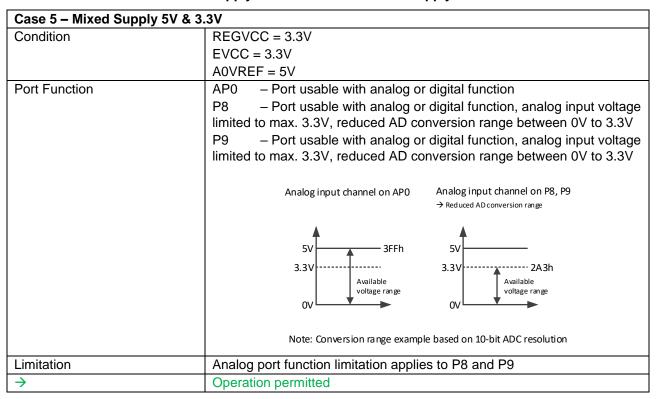

| Case 5 | 3.3V           | 3.3V | 5V     | Operation permitted     |

| Case 6 | 3.3V           | 3.3V | 3.3V   | Operation permitted     |

Note: \* means "don't care".

Table 3: RH850/F1KM-S1 Power supply architecture with single supply 5V

| Case 1 – Single Supply 5V |                                                   |  |  |

|---------------------------|---------------------------------------------------|--|--|

| Condition                 | REGVCC = 5V                                       |  |  |

|                           | EVCC = 5V                                         |  |  |

|                           | A0VREF = 5V                                       |  |  |

| Port Function             | AP0 – Port usable with analog or digital function |  |  |

|                           | P8 – Port usable with analog or digital function  |  |  |

|                           | P9 – Port usable with analog or digital function  |  |  |

| Limitation                | No limitation applies                             |  |  |

| $\rightarrow$             | Operation permitted                               |  |  |

Table 4: RH850/F1KM-S1 Power supply architecture with mixed supply 5V & 3.3V

| Case 2 – Mixed Supply 5V & 3.3V |                                                                        |  |  |

|---------------------------------|------------------------------------------------------------------------|--|--|

| Condition                       | REGVCC = 5V                                                            |  |  |

|                                 | EVCC = 5V                                                              |  |  |

|                                 | A0VREF = 3.3V                                                          |  |  |

| Port Function                   | AP0 – Port usable with analog or digital function                      |  |  |

|                                 | P8 – Port usable with analog or digital function, analog input         |  |  |

|                                 | voltage limited to max. 3.3V. When analog input terminal is over 3.3V, |  |  |

|                                 | do not include the input into an AD scan group                         |  |  |

|                                 | P9 – Port usable with analog or digital function, analog input         |  |  |

|                                 | voltage limited to max. 3.3V. When analog input terminal is over 3.3V, |  |  |

|                                 | do not include the input into an AD scan group                         |  |  |

| Limitation                      | Analog port function limitation applies to P8 and P9                   |  |  |

| $\rightarrow$                   | Operation permitted                                                    |  |  |

Table 5: RH850/F1KM-S1 Power supply architecture with mixed supply 5V & 3.3V

| Case 3 and Case 4 - Mixed Supply 5V & 3.3V |                                        |  |

|--------------------------------------------|----------------------------------------|--|

| Condition                                  | REGVCC ≠ EVCC                          |  |

|                                            | EVCC = 3.3V or 5V                      |  |

|                                            | A0VREF = Don't care                    |  |

| Port Function                              | _                                      |  |

| Limitation                                 | Common condition REGVCC = EVCC not met |  |

| <b>→</b>                                   | Operation not permitted                |  |

Table 6: RH850/F1KM-S1 Power supply architecture with mixed supply 5V & 3.3V

Table 7: RH850/F1KM-S1 Power supply architecture with single supply 3.3V

| Case 6 - Single Supply 3.3 | BV                                                |

|----------------------------|---------------------------------------------------|

| Condition                  | REGVCC = 3.3V                                     |

|                            | EVCC = 3.3V                                       |

|                            | A0VREF = 3.3V                                     |

| Port Function              | AP0 – Port usable with analog or digital function |

|                            | P8 – Port usable with analog or digital function  |

|                            | P9 – Port usable with analog or digital function  |

| Limitation                 | No limitation applies                             |

| <b>→</b>                   | Operation permitted                               |

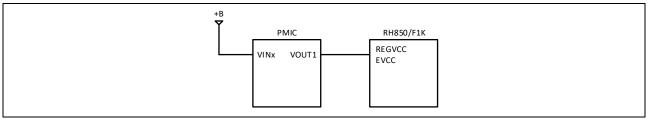

#### 1.1.4 Power Supply Timing of RH850/F1KM-S1

The RH850/F1KM-S1 has a recommended power supply timing.

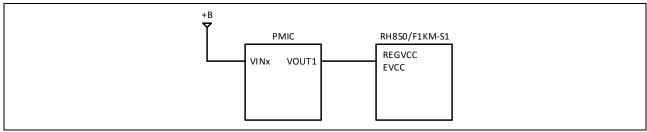

The voltage slope of the different power supply pins is defined with min. 0.02V/ms and max. 500V/ms. Satisfy the spec of voltage slope by using power IC with enable control or by using power IC which starts output over VPOC. The following shows an example of configuration between RH850/F1KM-S1 and PMIC.

Figure 2: Recommended REGVCC power configuration for RH850/F1KM-S1

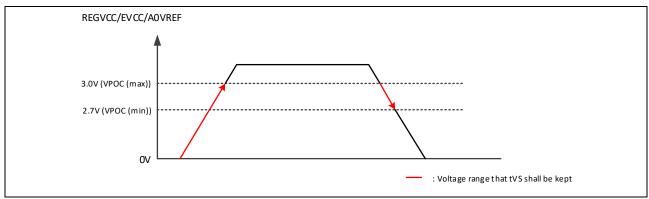

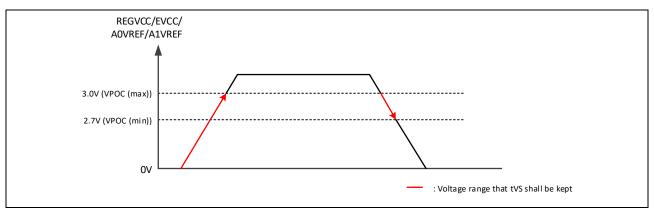

The voltage range which has to be kept voltage slope is as follows. There is no voltage slope limitation at the case other than below condition. For detail, see the following figure.

Figure 3: The voltage range which has to be kept voltage slope for RH850/F1KM-S1

Note: When the power source rises again, keep the spec of "REGVCC minimum width (tw\_Poc)", which is specified in the Section 47C.4.5.2, Voltage Detector (POC, LVI, VLVI, CVM) Characteristics of the RH850/F1KH, RH850/F1KM Hardware User's Manual.

For details on the electrical characteristics, please refer to Section 47C, Electrical Characteristics of RH850/F1KM-S1 of the RH850/F1KH, RH850/F1KM Hardware User's Manual.

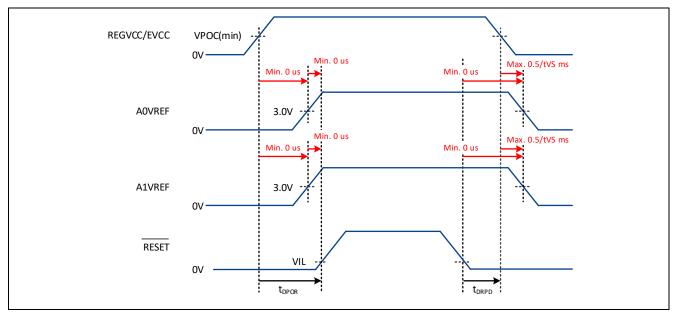

## a) When RESET terminal is used

Figure 4: RH850/F1KM-S1 Power up/down timing

## b) When RESET terminal is not used

Figure 5: RH850/F1KM-S1 Power up/down timing

Note. For the spec of t<sub>DPOR</sub>, t<sub>DRPD</sub> and t<sub>VS</sub>, please refer to Section 47C.4.5.3, Power Up/Down Timing of the RH850/F1KH, RH850/F1KM Hardware User's Manual.

## 1.2 Power Supply Overview of RH850/F1KM-S2

# 1.2.1 Power Supply Pin Overview of RH850/F1KM-S2

The devices of the RH850/F1KM-S2 have the following power supply pins:

- Power supply voltage REGVCC for the on-chip voltage regulators. The output voltage of the voltage regulators is supplied to the digital circuits in each power domain.

- Power supply voltages EVCC and BVCC (depending on device pin count) for the I/O ports.

- Power supply voltages A0VREF and A1VREF (depending on the device pin count) for the A/D converters and the separated I/O ports.

Table 8: RH850/F1KM-S2 Power supply pin overview

| Device                 | Power Supply Pins               |

|------------------------|---------------------------------|

| RH850/F1KM-S2 (176pin) | REGVCC                          |

|                        | AWOVCL <sup>Note</sup> , AWOVSS |

|                        | ISOVCLNote, ISOVSS              |

|                        | EVCC, EVSS                      |

|                        | BVCC, BVSS                      |

|                        | A0VREF, A0VSS                   |

|                        | A1VREF, A1VSS                   |

| RH850/F1KM-S2 (144pin) | REGVCC                          |

|                        | AWOVCL <sup>Note</sup> , AWOVSS |

|                        | ISOVCL <sup>Note</sup> , ISOVSS |

|                        | EVCC, EVSS                      |

|                        | BVCC, BVSS                      |

|                        | A0VREF, A0VSS                   |

|                        | A1VREF, A1VSS                   |

| RH850/F1KM-S2 (100pin) | REGVCC                          |

|                        | AWOVCL <sup>Note</sup> , AWOVSS |

|                        | ISOVCL <sup>Note</sup> , ISOVSS |

|                        | EVCC, EVSS                      |

|                        | A0VREF, A0VSS                   |

Note: The pins AWOVCL and ISOVCL are available on all devices to connect external stabilization capacitors. Do not use AWOVCL and ISOVCL as power source of other devices.

#### 1.2.2 Power Supply Pin Configuration of RH850/F1KM-S2

The following shows power supply pin configuration. Do not open any power and GND terminals even if those are internally connected.

- The EVCC supply pins are internally connected.

- The BVCC supply pins are internally connected (when available on the device).

- The EVSS pins are internally connected.

- The BVSS pins are internally connected (when available on the device).

- AWOVSS and ISOVSS are internally connected.

- · Others are not internally connected.

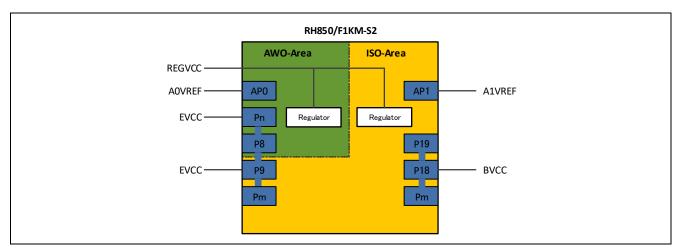

#### 1.2.3 Power Supply Pin Architecture of RH850/F1KM-S2

The RH850/F1KM-S2 supports different power supply architectures. The power supply architecture depends on the chosen RH850/F1KM-S2 device, application requirements and the use case.

Some common conditions apply to the supply of the RH850/F1KM-S2:

- REGVCC = EVCC = VPOC to 5.5V

- BVCC = VPOC to REGVCC (when available on the device)

- A0VREF = 3.0V to 5.5V

- A1VREF = 3.0V to 5.5V (when available on the device)

- AWOVSS = ISOVSS = EVSS = BVSS = A0VSS = A1VSS = 0V

The following figure and the different cases describe the impact to the ADC ports and the ports with analog/digital function depending on the power supply architecture. In addition, it describes the limitations to these ports.

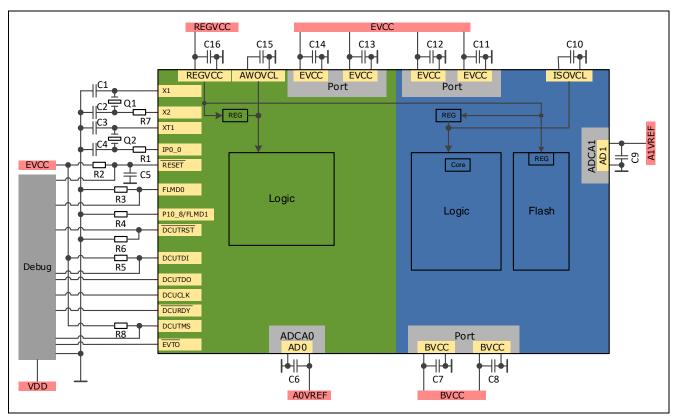

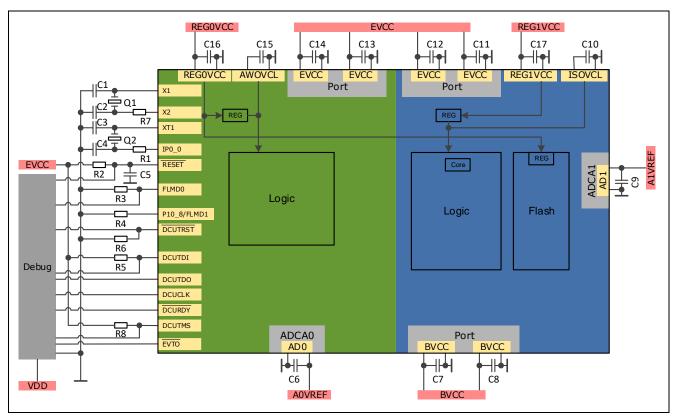

Figure 6: RH850/F1KM-S2 Power supply architecture

Note: The BVCC and A1VREF supply pin availability depends on the chosen device.

Table 9: RH850/F1KM-S2 Overview of power supply architecture cases

| Cooo    | Voltage |      |      |        | Parmiasian |                         |

|---------|---------|------|------|--------|------------|-------------------------|

| Case    | REGVCC  | EVCC | BVCC | A0VREF | A1VREF     | Permission              |

| Case 1  | 5V      | 5V   | 5V   | 5V     | 5V         | Operation permitted     |

| Case 2  | 5V      | 5V   | 5V   | 5V     | 3.3V       | Operation permitted     |

| Case 3  | 5V      | 5V   | 5V   | 3.3V   | 5V         | Operation permitted     |

| Case 4  | 5V      | 5V   | 5V   | 3.3V   | 3.3V       | Operation permitted     |

| Case 5  | 5V      | 5V   | 3.3V | 5V     | 5V         | Operation permitted     |

| Case 6  | 5V      | 5V   | 3.3V | 5V     | 3.3V       | Operation permitted     |

| Case 7  | 5V      | 5V   | 3.3V | 3.3V   | 5V         | Operation permitted     |

| Case 8  | 5V      | 5V   | 3.3V | 3.3V   | 3.3V       | Operation permitted     |

| Case 9  | 5V      | 3.3V | *    | *      | *          | Operation not permitted |

| Case 10 | 3.3V    | 5V   | *    | *      | *          | Operation not permitted |

| Case 11 | 3.3V    | 3.3V | 5V   | *      | *          | Operation not permitted |

| Case 12 | 3.3V    | 3.3V | 3.3V | 5V     | 5V         | Operation permitted     |

| Case 13 | 3.3V    | 3.3V | 3.3V | 5V     | 3.3V       | Operation permitted     |

| Case 14 | 3.3V    | 3.3V | 3.3V | 3.3V   | 5V         | Operation permitted     |

| Case 15 | 3.3V    | 3.3V | 3.3V | 3.3V   | 3.3V       | Operation permitted     |

Note: \* means "don't care".

Table 10: RH850/F1KM-S2 Power supply architecture with single supply 5V

| Case 1 - Single Supply 5V |                                                   |  |  |

|---------------------------|---------------------------------------------------|--|--|

| Condition                 | REGVCC = 5V                                       |  |  |

|                           | EVCC = 5V                                         |  |  |

|                           | BVCC = 5V                                         |  |  |

|                           | A0VREF = 5V                                       |  |  |

|                           | A1VREF = 5V                                       |  |  |

| Port Function             | AP0 – Port usable with analog or digital function |  |  |

|                           | P8 – Port usable with analog or digital function  |  |  |

|                           | P9 – Port usable with analog or digital function  |  |  |

|                           | AP1 – Port usable with analog or digital function |  |  |

|                           | P18 – Port usable with analog or digital function |  |  |

|                           | P19 – Port usable with analog or digital function |  |  |

| Limitation                | No limitation applies                             |  |  |

| $\rightarrow$             | Operation permitted                               |  |  |

Table 11: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V

| Case 2 – Mixed Supply 5V & 3.3V |                                                                        |  |  |

|---------------------------------|------------------------------------------------------------------------|--|--|

| Condition                       | REGVCC = 5V                                                            |  |  |

|                                 | EVCC = 5V                                                              |  |  |

|                                 | BVCC = 5V                                                              |  |  |

|                                 | A0VREF = 5V                                                            |  |  |

|                                 | A1VREF = 3.3V                                                          |  |  |

| Port Function                   | AP0 – Port usable with analog or digital function                      |  |  |

|                                 | P8 – Port usable with analog or digital function                       |  |  |

|                                 | P9 – Port usable with analog or digital function                       |  |  |

|                                 | AP1 – Port usable with analog or digital function                      |  |  |

|                                 | P18 – Port usable with analog or digital function, analog input        |  |  |

|                                 | voltage limited to max. 3.3V. When analog input terminal is over 3.3V, |  |  |

|                                 | do not include the input into an AD scan group.                        |  |  |

|                                 | P19 – Port usable with analog or digital function, analog input        |  |  |

|                                 | voltage limited to max. 3.3V. When analog input terminal is over 3.3V, |  |  |

|                                 | do not include the input into an AD scan group.                        |  |  |

| Limitation                      | Analog port function limitation applies to P18 and P19                 |  |  |

| $\rightarrow$                   | Operation permitted                                                    |  |  |

Table 12: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V

| Case 3 - Mixed Supply 5V & 3. | 3V                                                                     |  |  |

|-------------------------------|------------------------------------------------------------------------|--|--|

| Condition                     | REGVCC = 5V                                                            |  |  |

|                               | EVCC = 5V                                                              |  |  |

|                               | BVCC = 5V                                                              |  |  |

|                               | A0VREF = 3.3V                                                          |  |  |

|                               | A1VREF = 5V                                                            |  |  |

| Port Function                 | AP0 – Port usable with analog or digital function                      |  |  |

|                               | P8 – Port usable with analog or digital function, analog input         |  |  |

|                               | voltage limited to max. 3.3V. When analog input terminal is over 3.3V, |  |  |

|                               | do not include the input into an AD scan group.                        |  |  |

|                               | P9 – Port usable with analog or digital function, analog input         |  |  |

|                               | voltage limited to max. 3.3V. When analog input terminal is over 3.3V, |  |  |

|                               | do not include the input into an AD scan group.                        |  |  |

|                               | AP1 – Port usable with analog or digital function                      |  |  |

|                               | P18 – Port usable with analog or digital function                      |  |  |

|                               | P19 – Port usable with analog or digital function                      |  |  |

| Limitation                    | Analog port function limitation applies to P8 and P9                   |  |  |

| $\rightarrow$                 | Operation permitted                                                    |  |  |

Table 13: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V

| Case 4 – Mixed Supply 5V & 3.3V |                                                                        |  |

|---------------------------------|------------------------------------------------------------------------|--|

| Condition                       | REGVCC = 5V                                                            |  |

|                                 | EVCC = 5V                                                              |  |

|                                 | BVCC = 5V                                                              |  |

|                                 | A0VREF = 3.3V                                                          |  |

|                                 | A1VREF = 3.3V                                                          |  |

| Port Function                   | AP0 – Port usable with analog or digital function                      |  |

|                                 | P8 – Port usable with analog or digital function, analog input         |  |

|                                 | voltage limited to max. 3.3V. When analog input terminal is over 3.3V, |  |

|                                 | do not include the input into an AD scan group.                        |  |

|                                 | P9 – Port usable with analog or digital function, analog input         |  |

|                                 | voltage limited to max. 3.3V. When analog input terminal is over 3.3V, |  |

|                                 | do not include the input into an AD scan group.                        |  |

|                                 | AP1 – Port usable with analog or digital function                      |  |

|                                 | P18 – Port usable with analog or digital function, analog input        |  |

|                                 | voltage limited to max. 3.3V. When analog input terminal is over 3.3V, |  |

|                                 | do not include the input into an AD scan group.                        |  |

|                                 | P19 – Port usable with analog or digital function, analog input        |  |

|                                 | voltage limited to max. 3.3V. When analog input terminal is over 3.3V, |  |

|                                 | do not include the input into an AD scan group.                        |  |

| Limitation                      | Analog port function limitation applies to P8, P9, P18 and P19         |  |

| $\rightarrow$                   | Operation permitted                                                    |  |

Table 14: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V

| Case 5 - Mixed Supply 5 | SV & 3.3V                                                                                      |  |

|-------------------------|------------------------------------------------------------------------------------------------|--|

| Condition               | REGVCC = 5V                                                                                    |  |

|                         | EVCC = 5V                                                                                      |  |

|                         | BVCC = 3.3V                                                                                    |  |

|                         | A0VREF = 5V                                                                                    |  |

|                         | A1VREF = 5V                                                                                    |  |

| Port Function           | APO – Port usable with analog or digital function                                              |  |

|                         | P8 — Port usable with analog or digital function                                               |  |

|                         | P9 – Port usable with analog or digital function                                               |  |

|                         | AP1 — Port usable with analog or digital function                                              |  |

|                         | P18 — Port usable with analog or digital function, analog input                                |  |

|                         | voltage limited to max. 3.3V, reduced AD conversion range between 0V                           |  |

|                         | to 3.3V                                                                                        |  |

|                         | P19 – Port usable with analog or digital function, analog input                                |  |

|                         | voltage limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V                   |  |

|                         | Analog input channel on AP1 Analog input channel on P18 and P19  → Reduced AD conversion range |  |

|                         | 3.3V 3.3V 3.3V Available voltage range 0V 0V 2A3h Available voltage range                      |  |

|                         | Note: Conversion range example based on 10-bit ADC resolution                                  |  |

| Limitation              | Analog port function limitation applies to P18 and P19                                         |  |

| $\rightarrow$           | Operation permitted                                                                            |  |

Table 15: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V

| Case 6 – Mixed Supply 5V & 3.3V |                                                   |  |  |

|---------------------------------|---------------------------------------------------|--|--|

| Condition                       | REGVCC = 5V                                       |  |  |

|                                 | EVCC = 5V                                         |  |  |

|                                 | BVCC = 3.3V                                       |  |  |

|                                 | A0VREF = 5V                                       |  |  |

|                                 | A1VREF = 3.3V                                     |  |  |

| Port Function                   | AP0 – Port usable with analog or digital function |  |  |

|                                 | P8 – Port usable with analog or digital function  |  |  |

|                                 | P9 – Port usable with analog or digital function  |  |  |

|                                 | AP1 – Port usable with analog or digital function |  |  |

|                                 | P18 – Port usable with analog or digital function |  |  |

|                                 | P19 – Port usable with analog or digital function |  |  |

| Limitation                      | No limitation applies                             |  |  |

| $\rightarrow$                   | Operation permitted                               |  |  |

Table 16: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V

| Case 7 – Mixed Supply 5V & 3.3V |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Condition                       | REGVCC = 5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                 | EVCC = 5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                                 | BVCC = 3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                 | AOVREF = 3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                 | A1VREF = 5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Port Function                   | APO — Port usable with analog or digital function P8 — Port usable with analog or digital function, analog input voltage limited to max. 3.3V. When analog input terminal is over 3.3V, do not include the input into an AD scan group. P9 — Port usable with analog or digital function, analog input voltage limited to max. 3.3V. When analog input terminal is over 3.3V, do not include the input into an AD scan group. AP1 — Port usable with analog or digital function, analog input voltage limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V P18 — Port usable with analog or digital function, analog input voltage limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V P19 — Port usable with analog or digital function, analog input voltage limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V |  |

|                                 | Analog input channel on AP1  Analog input channel on P18 and P19  → Reduced AD conversion range   5V  3.3V  Available voltage range  0V  Available voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                 | Note: Conversion range example based on 10-bit ADC resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Limitation                      | Analog port function limitation applies to P8, P9, P18 and P19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| $\rightarrow$                   | Operation permitted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

Table 17: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V

| Case 8 – Mixed Supply 5V & 3.3V |                                                                        |  |  |

|---------------------------------|------------------------------------------------------------------------|--|--|

| Condition                       | REGVCC = 5V                                                            |  |  |

|                                 | EVCC = 5V                                                              |  |  |

|                                 | BVCC = 3.3V                                                            |  |  |

|                                 | A0VREF = 3.3V                                                          |  |  |

|                                 | A1VREF = 3.3V                                                          |  |  |

| Port Function                   | AP0 – Port usable with analog or digital function                      |  |  |

|                                 | P8 – Port usable with analog or digital function, analog input         |  |  |

|                                 | voltage limited to max. 3.3V. When analog input terminal is over 3.3V, |  |  |

|                                 | do not include the input into an AD scan group.                        |  |  |

|                                 | P9 – Port usable with analog or digital function, analog input         |  |  |

|                                 | voltage limited to max. 3.3V. When analog input terminal is over 3.3V, |  |  |

|                                 | do not include the input into an AD scan group.                        |  |  |

|                                 | AP1 – Port usable with analog or digital function                      |  |  |

|                                 | P18 – Port usable with analog or digital function                      |  |  |

|                                 | P19 – Port usable with analog or digital function                      |  |  |

| Limitation                      | Analog port function limitation applies to P8 and P9                   |  |  |

| $\rightarrow$                   | Operation permitted                                                    |  |  |

Table 18: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V

| Case 9, Case 10 – Mixed Supply 5V & 3.3V |                                        |  |  |

|------------------------------------------|----------------------------------------|--|--|

| Condition                                | REGVCC ≠ EVCC                          |  |  |

|                                          | EVCC = 3.3V or 5V                      |  |  |

|                                          | BVCC = Don't care                      |  |  |

|                                          | A0VREF = Don't care                    |  |  |

|                                          | A1VREF = Don't care                    |  |  |

| Port Function                            | -                                      |  |  |

| Limitation                               | Common condition REGVCC = EVCC not met |  |  |

| <b>→</b>                                 | Operation not permitted                |  |  |

Table 19: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V

| Case 11 – Mixed Supply 5V & 3.3V |                                        |  |

|----------------------------------|----------------------------------------|--|

| Condition REGVCC = 3.3V          |                                        |  |

|                                  | EVCC = 3.3V                            |  |

|                                  | BVCC = 5V                              |  |

|                                  | A0VREF = Don't care                    |  |

|                                  | A1VREF = Don't care                    |  |

| Port Function                    | -                                      |  |

| Limitation                       | Common condition REGVCC ≥ BVCC not met |  |

| <b>→</b>                         | Operation not permitted                |  |

Table 20: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V

| Case 12 - Mixed Supply 5V & 3.3V |                                                                                                             |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| Condition                        | REGVCC = 3.3V                                                                                               |  |

|                                  | EVCC = 3.3V                                                                                                 |  |

|                                  | BVCC = 3.3V                                                                                                 |  |

|                                  | A0VREF = 5V                                                                                                 |  |

|                                  | A1VREF = 5V                                                                                                 |  |

| Port Function                    | APO – Port usable with analog or digital function                                                           |  |

|                                  | P8 — Port usable with analog or digital function, analog input                                              |  |

|                                  | voltage limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V                                |  |

|                                  | P9 – Port usable with analog or digital function, analog input                                              |  |

|                                  | voltage limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V                                |  |

|                                  | AP1 – Port usable with analog or digital function                                                           |  |

|                                  | P18 — Port usable with analog or digital function, analog input                                             |  |

|                                  | voltage limited to max. 3.3V, reduced AD conversion range between 0V                                        |  |

|                                  | to 3.3V                                                                                                     |  |

|                                  | P19 — Port usable with analog or digital function, analog input                                             |  |

|                                  | voltage limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V                                |  |

|                                  | Analog input channel on APO, AP1 Analog input channel on P8, P9, P18 and P19  → Reduced AD conversion range |  |

|                                  | 3.3V 3.3V 2.43h Available voltage range 0V 0V 2A3h                                                          |  |

|                                  | Note: Conversion range example based on 10-bit ADC resolution                                               |  |

| Limitation                       | Analog port function limitation applies to P8, P9, P18 and P19                                              |  |

| $\rightarrow$                    | Operation permitted                                                                                         |  |

Table 21: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V

| Case 13 - Mixed Supp | ly 5V & 3.3V                                                                                  |

|----------------------|-----------------------------------------------------------------------------------------------|

| Condition            | REGVCC = 3.3V                                                                                 |

|                      | EVCC = 3.3V                                                                                   |

|                      | BVCC = 3.3V                                                                                   |

|                      | A0VREF = 5V                                                                                   |

|                      | A1VREF = 3.3V                                                                                 |

| Port Function        | AP0 – Port usable with analog or digital function                                             |

|                      | P8 — Port usable with analog or digital function, analog input                                |

|                      | voltage limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V                  |

|                      | P9 – Port usable with analog or digital function, analog input                                |

|                      | voltage limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V                  |

|                      | AP1 – Port usable with analog or digital function                                             |

|                      | P18 — Port usable with analog or digital function                                             |

|                      | P19 – Port usable with analog or digital function                                             |

|                      |                                                                                               |

|                      | Analog input channel on APO  Analog input channel on P8 and P9  → Reduced AD conversion range |

|                      | 3FFh 5V 3.3V Available voltage range 0V OV 2A3h Available voltage range                       |

|                      | Note: Conversion range example based on 10-bit ADC resolution                                 |

| Limitation           | Analog port function limitation applies to P8 and P9                                          |

| $\rightarrow$        | Operation permitted                                                                           |

Table 22: RH850/F1KM-S2 Power supply architecture with mixed supply 5V & 3.3V

| Case 14 - Mixed Supply 5V & 3.3V |                                                                                                |  |

|----------------------------------|------------------------------------------------------------------------------------------------|--|

| Condition                        | REGVCC = 3.3V                                                                                  |  |

|                                  | EVCC = 3.3V                                                                                    |  |

|                                  | BVCC = 3.3V                                                                                    |  |

|                                  | A0VREF = 3.3V                                                                                  |  |

|                                  | A1VREF = 5V                                                                                    |  |

| Port Function                    | AP0 – Port usable with analog or digital function                                              |  |

|                                  | P8 – Port usable with analog or digital function                                               |  |

|                                  | P9 – Port usable with analog or digital function                                               |  |

|                                  | AP1 – Port usable with analog or digital function                                              |  |

|                                  | P18 – Port usable with analog or digital function, analog input                                |  |

|                                  | voltage limited to max. 3.3V, reduced AD conversion range between 0V                           |  |

|                                  | to 3.3V                                                                                        |  |

|                                  | P19 – Port usable with analog or digital function, analog input                                |  |

|                                  | voltage limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V                   |  |

|                                  | Analog input channel on AP1 Analog input channel on P18 and P19  → Reduced AD conversion range |  |

|                                  | 3.3V 3.3V 2A3h Available voltage range OV OV                                                   |  |

|                                  | Note: Conversion range example based on 10-bit ADC resolution                                  |  |

| Limitation                       | Analog port function limitation applies to P18 and P19                                         |  |

| $\rightarrow$                    | Operation permitted                                                                            |  |

Table 23: RH850/F1KM-S2 Power supply architecture with single supply 3.3V

| Case 15 - Single Supply 3.3V |                                                   |  |  |

|------------------------------|---------------------------------------------------|--|--|

| Condition                    | REGVCC = 3.3V                                     |  |  |

|                              | EVCC = 3.3V                                       |  |  |

|                              | BVCC = 3.3V                                       |  |  |

|                              | A0VREF = 3.3V                                     |  |  |

|                              | A1VREF = 3.3V                                     |  |  |

| Port Function                | AP0 – Port usable with analog or digital function |  |  |

|                              | P8 – Port usable with analog or digital function  |  |  |

|                              | P9 – Port usable with analog or digital function  |  |  |

|                              | AP1 – Port usable with analog or digital function |  |  |

|                              | P18 – Port usable with analog or digital function |  |  |

| Limitation                   | No limitation applies                             |  |  |

| $\rightarrow$                | Operation permitted                               |  |  |

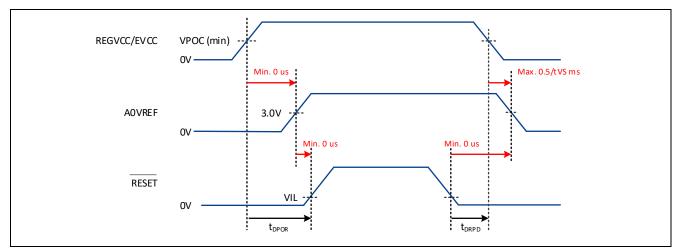

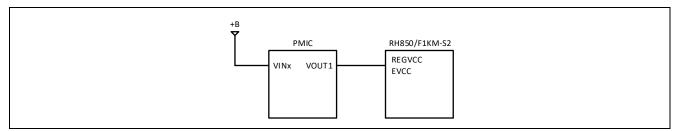

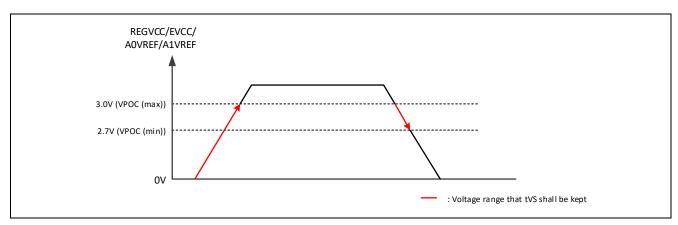

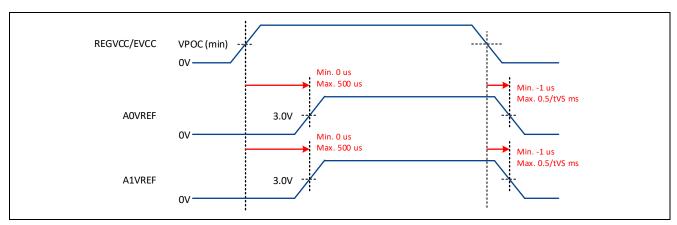

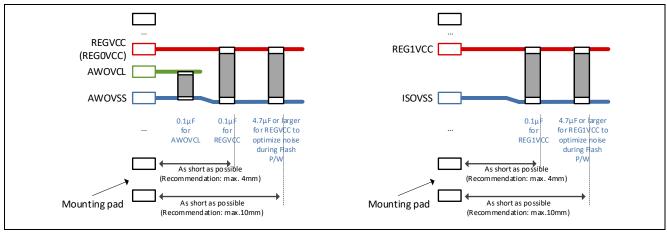

## 1.2.4 Power Supply Timing of RH850/F1KM-S2

The RH850/F1KM-S2 has a recommended power supply timing.

The voltage slope of the different power supply pins is defined with min. 0.02V/ms and max. 500V/ms. Satisfy the spec of voltage slope by using power IC with enable control or by using power IC which starts output over VPOC. The following shows an example of configuration between RH850/F1KM-S2 and PMIC.

Figure 7: Recommended REGVCC power configuration for RH850/F1KM-S2

The voltage range which has to be kept voltage slope is as follows. There is no voltage slope limitation at the case other than below condition. For detail, see the following figure.

Figure 8: The voltage range which has to be kept voltage slope for RH850/F1KM-S2

Note: When the power source rises again, keep the spec of "REGVCC minimum width (tw\_POC)", which is specified in the Section 47B.4.5.2, Voltage Detector (POC, LVI, VLVI, CVM) Characteristics of the RH850/F1KH, RH850/F1KM Hardware User's Manual.

For details on the electrical characteristics, please refer to Section 47B, Electrical Characteristics of RH850/F1KM-S4, RH850/F1KM-S2 of the RH850/F1KH, RH850/F1KM Hardware User's Manual.

## a) When RESET terminal is used

Figure 9: RH850/F1KM-S2 Power up/down timing

#### b) When RESET terminal is not used

Figure 10: RH850/F1KM-S2 Power up/down timing

Note: For the spec of t<sub>DPOR</sub>, t<sub>DRPD</sub> and t<sub>VS</sub>, please refer to Section 47B.4.5.3, Power Up/Down Timing of the RH850/F1KH, RH850/F1KM Hardware User's Manual.

## 1.3 Power Supply Overview of RH850/F1KM-S4

## 1.3.1 Power Supply Pin Overview of RH850/F1KM-S4

The devices of the RH850/F1KM-S4 have the following power supply pins:

- Power supply voltage REGVCC for the on-chip voltage regulators. The output voltage of the voltage regulators is supplied to the digital circuits in each power domain.

- Power supply voltages EVCC and BVCC (depending on device pin count) for the I/O ports.

- Power supply voltages A0VREF and A1VREF (depending on the device pin count) for the A/D converters and the separated I/O ports.

Table 24: RH850/F1KM-S4 Power supply pin overview

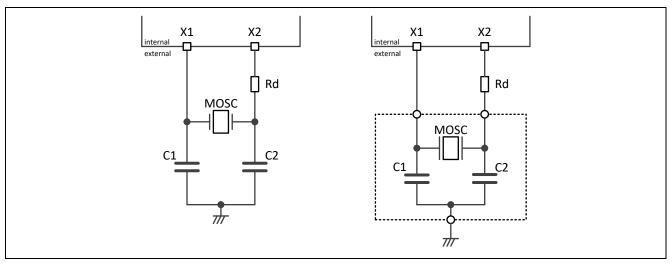

| Device                 | Power Supply Pins               |