### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

ADVANCED AND EVER ADVANCING SOCIO-TECH

# MITSUBISHI DIGITAL ASSP M66290A USB APPLICATION NOTE

Ver 1.0 Rev.C '00-11-20

**MITSUBISHI ELECTRIC CORPORATION**

MITSUBISHI ELECTRIC SEMICONDUCTOR SYSTEMS CORPORATION

#### Keep safety first in your circuit designs!

• Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Mitsubishi Electric Corporation by various means, including the Mitsubishi Semiconductor home page (http://www.mitsubishichips.com).

- When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.

| Contents - |  |

|------------|--|

|------------|--|

| 1. Ov        | erview of the Manual                                              |

|--------------|-------------------------------------------------------------------|

| 1.1.         | <b>Overview</b> 1                                                 |

| 1.2.         | Features of the Application Note    1                             |

| 1.3.         | Related Documents 1                                               |

| 2. Ov        | erview of USB                                                     |

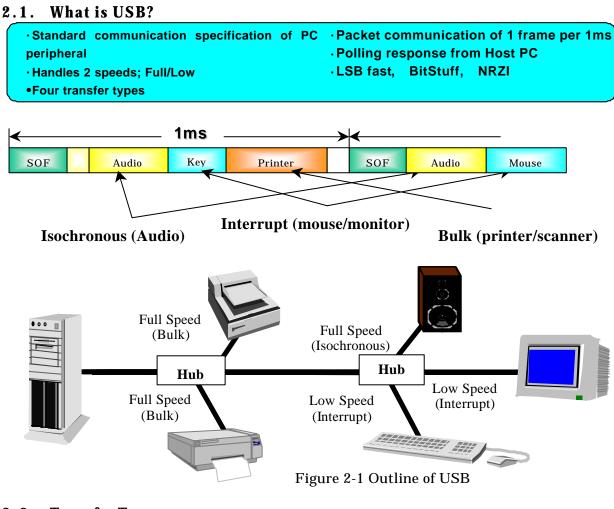

| 2.1.         | What is USB?                                                      |

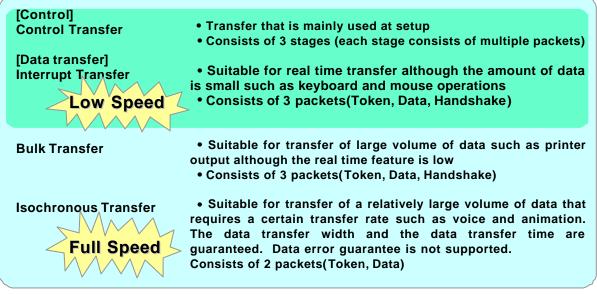

| 2.2.         | Transfer Type   2                                                 |

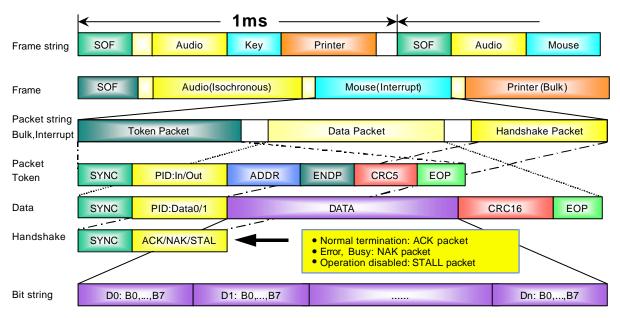

| 2.3.         | USB Protocol 3                                                    |

| 2.4.         | USB Packet 3                                                      |

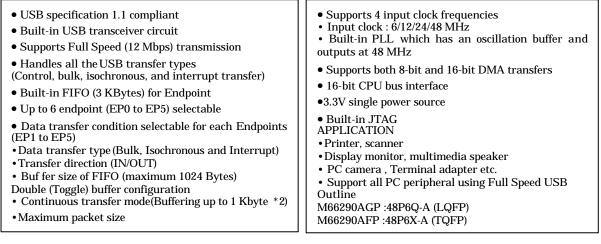

| 3. Ov        | erview of the M66290                                              |

| 3.1.         | Features of the M66290 4                                          |

| 3.2.         | Example of Connection with Control CPU 4                          |

| 3.3.         | Global Flow of Control Program                                    |

| 3.4.         | Interrupt Processing                                              |

| 3.5.         | Interrupt of Data Transfer                                        |

| 3.6.         | FIFO Control                                                      |

| 3.7.         | DMA Access                                                        |

| 4. Ini       | itialization                                                      |

| 4.1.         | Activating the M66290 11                                          |

| 4.2.         | Preparation for Control Transfers (Initialization of Endpoint0)12 |

| 4.3.         | USB Interrupt Enable                                              |

| 5. Co        | ntrol Transfers                                                   |

| 5.1.         | Outline of Control Transfers14                                    |

| 5.2.         | USB Device State Transition15                                     |

| 5.3.         | Device State Transition Processing16                              |

| 5.4.         | Control Transfer Stage Transition17                               |

| 5.5.         | Stage Transition Processing18                                     |

| 5.6.         | Setup Stage                                                       |

| 5.7.         | Control Read Transfer Processing (Data Stage)                     |

| <b>5.8</b> . | Control Write Transfer Processing (Data Stage)                    |

| 5.9.         | Control Write No Data Transfer Processing (Status Stage)          |

| 6. Da        | ta Transfers                                                      |

| 6.1.         | Outline of Data Transfers                                         |

| 6.2.         | Features of Data Transfers by the M6629024                        |

| 6.3.         | Data Transmit/Receive Interrupt                                   |

| 6.4.  | FIFO Access (Data Transmit: IN Direction)      |

|-------|------------------------------------------------|

| 6.5.  | FIFO Access (Data Receive: OUT Direction)27    |

| 7. U  | SB Special Signal Processing                   |

| 7.1.  | USB Bus Reset Signal                           |

| 7.2.  | Suspend Signal                                 |

| 7.3.  | Resume Detection (Bus Activity)   30           |

| 7.4.  | USB Bus Reset Detection of Suspend State       |

| 7.5.  | Remote Wakeup                                  |

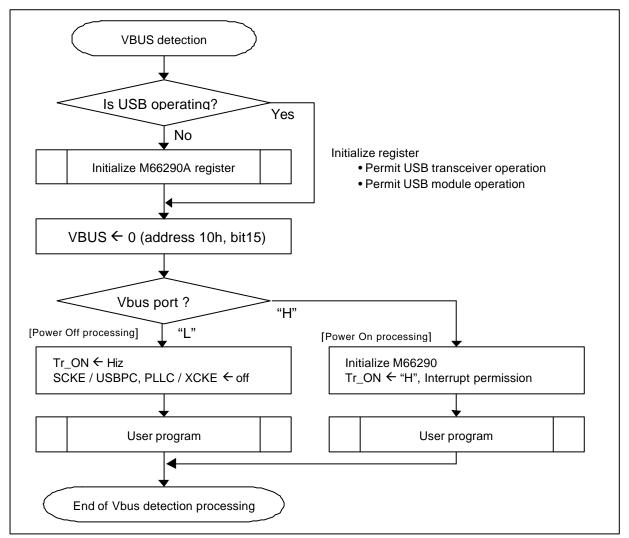

| 7.6.  | Vbus Detection                                 |

| 8. Aj | oplication Examples                            |

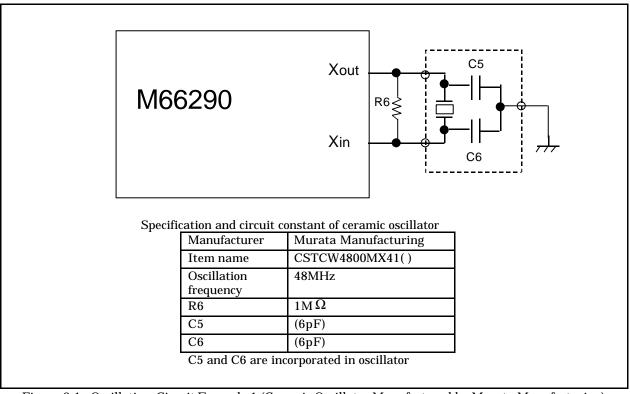

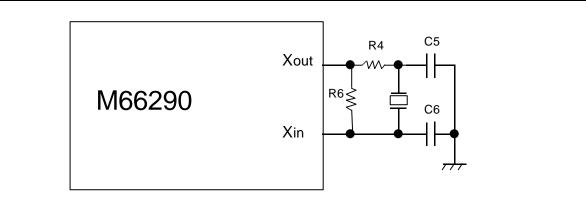

| 8.1.  | Oscillation Circuit                            |

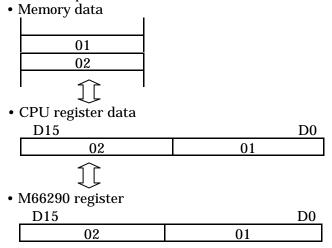

| 8.2.  | CPU Connection Method35                        |

| 9. Q  | & A                                            |

| 9.1.  | Q & A Relating to Substrate Design41           |

| 9.2.  | Q & A Relating to Control Transfer42           |

| 9.3.  | Q & A Related to Data Transfer46               |

| 9.4.  | Q & A Relating to DMA Transfer                 |

| 9.5.  | Q & A Relating to FIFO Control                 |

| 9.6.  | Q & A Relating to the Null Addition Function52 |

| 9.7.  | Q & A Relating to Communication Errors53       |

| 9.8.  | Q & A Relating to Other Functions              |

| 10.   | Revision History                               |

### 1. Overview of the Manual

#### 1.1. Overview

This manual (referred to as the Application Note henceforth) describes application technology manual for controlling the MITSUBISHI Digital ASSP general purpose USB device controller [M66290 Series] (referred to as M66290 henceforth) that is connected to the memory extension of the control CPU, and which does not specify any particular CPUs.

#### **1.2.** Features of the Application Note

The Application Note has the following features.

• Describes the techniques for M66290 control using actual coding examples.

• Describes notes on using the M66290.

• Links with M66290 control F/W.

• Describes abundant practical functional purposes.

The M66290 control F/W V.1.01 does not handle control of USB special signals. This manual simply shows examples of the M66290 control method. The actual method must be modified according to the customer's application.

#### **1.3. Related Documents**

[1] M66290AGP/FP data sheet

[http://www.mitsubishichips.com/data/datasheets/assps/index.html] [2] M66290A USB Firmware Ver1.01

[MESC Release '99.12.16]

[3] Base of USB (in Japanese) [http://www.infomicom.mesc.co.jp/usb/usbtop.htm] [4] USB Device Catalog [http://www.infomicom.mesc.co.jp/usb/usbmaine.htm] [5] USB Specification Version1.1

[http://www.usb.org/developers/docs.html]

## 2. Overview of USB

#### 2.2. Transfer Type

Figure 2-2 USB Transfer type

#### 2.3. USB Protocol

USB performs data communication in packet units. USB forms a communication unit called a transaction by grouping multiple packets. One transfer is formed by grouping multiple transactions.

Figure 2-3 USB Communication Protocol

#### 2.4. USB Packet

All bus transactions involve the transmission of up to three packets. Figure 2-4 shows the packet format. A packet consists of fields starting from the SYNC field followed by the PID field that indicates the packet type.

|                                                                          | at malates the packet type.                                       |                             |               |             |               |      |  |

|--------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------|---------------|-------------|---------------|------|--|

| Four types of packets                                                    | Four types of packets are used by USB.                            |                             |               |             |               |      |  |

| SOF Packet                                                               | SOF Packet Frame start packet that is used by the host every 1ms. |                             |               |             |               |      |  |

|                                                                          | SYNC                                                              | PID                         | Frame N       | umber       | CRC5          | EOP  |  |

|                                                                          | 8bit                                                              | 8bit                        | 11bi          | it          | 5bit          | 2bit |  |

| Token packet                                                             | Packet i                                                          | ssued by                    | the host at t | he start of | f a transacti | on   |  |

|                                                                          | SYNC                                                              | SYNC PID ADDR ENDP CRC5 EOP |               |             |               |      |  |

|                                                                          | 8bit 8bit 7bit 4bit 5bit 2bit                                     |                             |               |             |               |      |  |

| Data packet                                                              | cket Packet used at data transfer                                 |                             |               |             |               |      |  |

|                                                                          | SYNC                                                              | PID                         | DATA          | A           | CRC16         | EOP  |  |

|                                                                          | 8bit8bit0~1023 byte16bit2bit                                      |                             |               |             |               |      |  |

| Handshake packet Packet used by a transaction that performs flow control |                                                                   |                             |               |             |               |      |  |

| 8bit 8bit                                                                |                                                                   |                             |               |             |               |      |  |

Figure 2-4 Packet Format

### 3. Overview of the M66290

#### 3.1. Features of the M66290

See below for the features of the M66290. See the data sheet for details.

Figure 3-1 Features of M66290

#### 3.2. Example of Connection with Control CPU

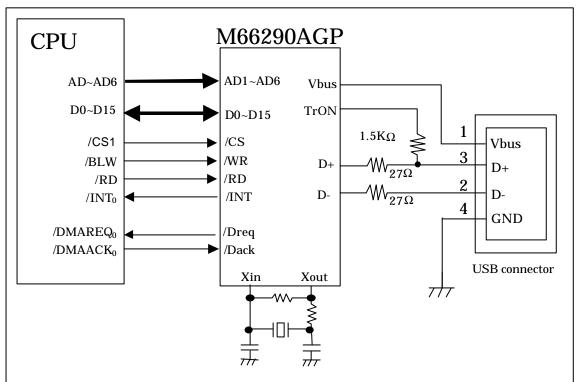

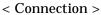

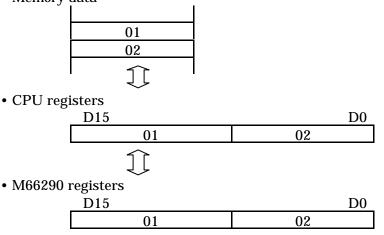

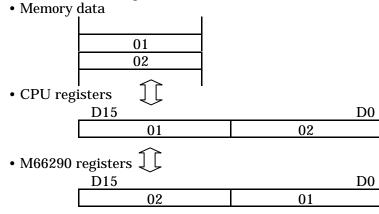

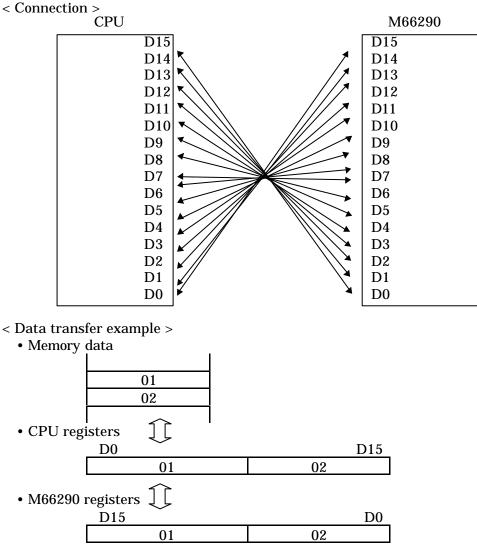

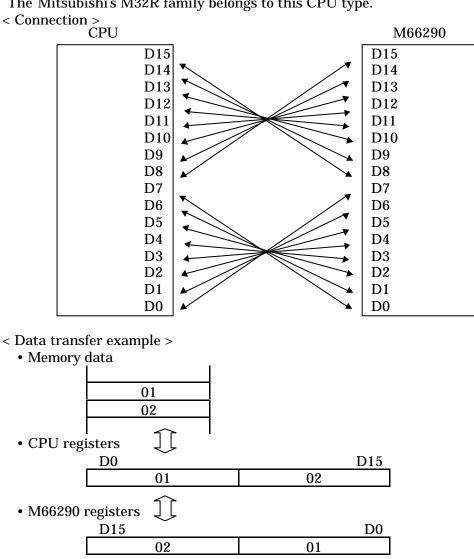

Figure 3-2 shows a connection example when 16-bit microcomputer is used as the CPU for controlling the M66290. Data bus D0 to D15 are set to an input state when /CS is not selected, so when the input level were indefinite, lead-through current would flow. Therefore, pull-up or pull-down resistance is required at the designing of hardware.

Figure 3-2 Connection Example for Main CPU

#### 3.3. Global Flow of Control Program

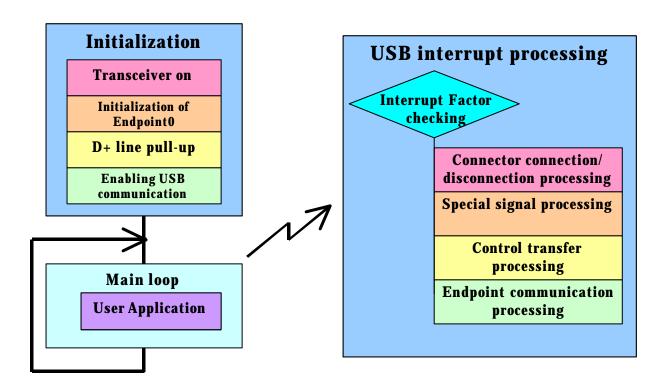

The M66290 notifies to CPU USB data transmit/receive processing and special signal processing using interrupt signals. Therefore, the control program consists of an initialization program and a USB interrupt processing program.

The control program checks interrupt factors using the external interrupt program and executes related processing.

(1) Special signal processing

Vbus interrupt, resume interrupt, SOF detection interrupt, and device state transition interrupt

(2) Control transfer processing

Control transfer stage transition interrupt and device state transition interrupt

(3) Endpoint transfer processing

Empty/size error interrupt, buffer/not ready interrupt, and buffer ready interrupt

The M66290 notifies various USB factors to the control CPU through interrupts. The following diagram shows the outline of the system flow when various USB factors that can be checked by the M66290 are posted by interrupt processing.

The main function requires initialization of the control CPU and registers that are related to the M66290.

Figure 3-3 Example of M66290 Control Program Configuration

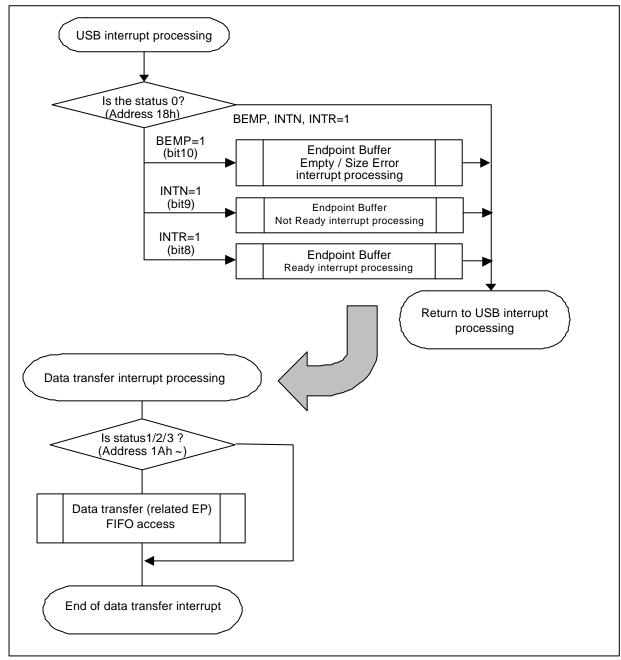

#### 3.4. Interrupt Processing

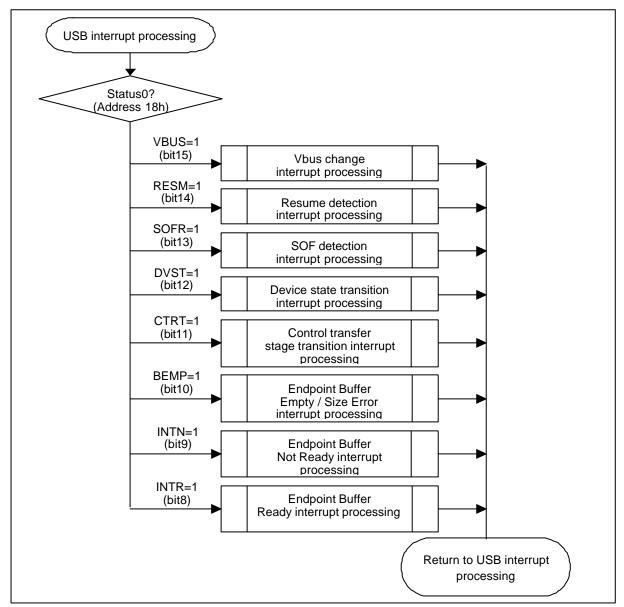

Control CPU identifies USB interrupts from the /INT signals from the M66290. Control CPU can identify factors from the contents of the following four types of interrupt status registers.

Interrupt status 0 register (Address 18h) Interrupt type identification

Interrupt status 1 register (Address 1Ah) Buffer ready identification

Interrupt status 2 register (Address 1Ch) Buffer not ready identification

Interrupt status 3 register (Address 1Eh) Buffer empty/size error identification

The interrupt status 0 register is used to identify a M66290 interrupt. The control program identifies the interrupt factor according to the bit status corresponding to each interrupt and performs related interrupt processing.

The interrupt status 1 register, interrupt status 2 register, and interrupt status 3 register are used to identify endpoint numbers that correspond to the endpoint buffer status interrupts.

See below for the flow of processing performed when a USB interrupt is detected.

Figure 3-4 Example of M66290 Interrupt Processing

#### 3.5. Interrupt of Data Transfer

The M66290 is equipped with three types of data transfer interrupts and users can select each data transfer interrupt type according to the purpose. The endpoint from which the interrupt factor of the interrupt occurred can be identified from one of the status registers 1 to 3. Note that the occurrence factor of a data transfer interrupt varies according to the transfer type, transfer direction, and access method.

See the M66290 data sheet [(2) Interrupts] for clearing each interrupt factor and the detail function.

| Features of M66290 interrupt functions |                                                                                      |                                 |                                              |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------|--|--|

| Transfer type                          | INTR interrupt                                                                       | INTN interrupt                  | BEMP interrupt                               |  |  |

| Outline of<br>interrupt factor         | Read/Write enable<br>(Level interrupt)Transmit/receive<br>unable<br>(Edge interrupt) |                                 | Buffer Empty<br>(Edge interrupt)             |  |  |

| Control<br>Read transfer               | Does not occur                                                                       | "NAK" response for<br>IN token  | Transmission<br>completion                   |  |  |

| Control<br>Write transfer              | Receive data Read<br>enable                                                          | "NAK" response for OUT token    | Exceeded packet size                         |  |  |

| Data transfer IN<br>(CPU access)       | Transmit data Write<br>enable                                                        | "NAK" response for<br>IN token  | Transmission<br>completion<br>(Buffer Empty) |  |  |

| Data transfer IN<br>(DMA access)       | Does not occur                                                                       | "NAK" response for<br>OUT token | Transmission<br>completion<br>(Buffer Empty) |  |  |

| Data transfer<br>OUT<br>(CPU access)   | Receive data Read<br>enable                                                          | "NAK" response for<br>IN token  | Exceeded packet<br>size                      |  |  |

| Data transfer<br>OUT<br>(DMA access)   | Received short<br>packet                                                             | "NAK" response for<br>OUT token | Exceeded packet<br>size                      |  |  |

Table 3-1 Interrupt Factors According to the Data Transfer Types

\* When the FIFO buffer is cleared while the endpoint is in the IN direction, the INTR interrupt occurs continuously.

\* Note that when FIFO is used by a double buffer, the BEMP interrupt occurs at transmission completion of opposite side of the double buffer while data is written.

(See 3.6, "FIFO Control" also.)

The following interrupt is recommended for each USB data transfer.

Table 3-2

Recommended Interrupt for Each Transfer

| Recommended interrupt        | Double buffer                                                                                                                                                                                                                                      | Continuous transfer                                                                                                                                                                                                                                                                                                                                                |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control transfer transition  |                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                  |

| BufferEmpty(non-continuous   |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                    |

| transfer)                    |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                    |

| Control transfer transition  | —                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                  |

| Buffer Ready (non-continuous |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                    |

| transfer)                    |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                    |

| Buffer Ready                 | 0                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                  |

| Buffer Ready                 | 0                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                  |

| Buffer Empty                 | —                                                                                                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                                                                                  |

| Buffer Ready                 | _                                                                                                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                                                                                  |

| Buffer Ready                 | 0                                                                                                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                                                                                  |

| Buffer Ready                 | 0                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                  |

|                              | Control transfer transition<br>BufferEmpty(non-continuous<br>transfer)<br>Control transfer transition<br>Buffer Ready (non-continuous<br>transfer)<br>Buffer Ready<br>Buffer Ready<br>Buffer Empty<br>Buffer Ready<br>Buffer Ready<br>Buffer Ready | Control transfer transition—BufferEmpty(non-continuous<br>transfer)—Control transfer transition—Buffer Ready (non-continuous<br>transfer)—Buffer ReadyOBuffer ReadyOBuffer ReadyOBuffer Ready—Buffer Ready—Buffer Ready—Buffer Ready—Buffer Ready—Buffer Ready—Buffer Ready—Buffer Ready—Buffer Ready—Buffer Ready—O—Buffer Ready—O—Buffer Ready—O—Buffer Ready—O— |

0 ----- Used

#### 3.6. FIFO Control

The M66290 is equipped with a large capacity FIFO buffer of 3K bytes and uses the buffer by allocating a separate buffer area to each of endpoints EP0 to EP5. The FIFO buffer consists of 64 bytes \* 48 blocks. Specify the first block number (EPi\_Buf\_Nmb) of EPi configuration register 0 (60h, 64h, 68h, 6Ch, 70h), buffer size (EPi\_Buf\_Siz), and the buffer mode (EPi\_DBLB) to allocate a FIFO buffer area to each endpoint. See the setting example that is described later for the method of allocating an area. An error does not occur even if the areas overlap. Note that the latest data written to the overlapped areas becomes valid.

Three FIFO registers are used to access each endpoint buffer. The FIFO registers include one EP0 dedicated FIFO register (CPU access) and two EP1~EP5 common FIFO data registers. The common FIFO data registers are classified into the register for CPU access and the register for DMA transfer according to the access method. The setting of the FIFO selection register determines the endpoint to be accessed among EP1 to EP5.

Do not specify the endpoint number with DMA transfer mode specified in the CPU\_FIFO selection register.

The three FIFO data registers have the following functions and perform options according to the setting of the "FIFO selection registor and FIFO control register".

(1) Short packet transmission function (IVAL: IN buffer status bit)

When sending a short packet, write IVAL after writing data in the FIFO register.

- (2) Transmit/receive buffer clear function (BCLR: Buffer clear bit)

When a double buffer is set, the side (half of buffer size) that can be access from the control CPU is cleared. When clearing the all of buffer, use EPi\_ACLR.

- (3) Null data (length 0 data) transmission function (IVAL & BCLR) By writing IVAL="1" and BCLR="1", a Null packet of length "0" can be sent.

- (4) Data length (8/16 bits) setting function (Octl: Register 8-bit mode bit) The mode can be changed from a 16-bit mode to an 8-bit mode during FIFO buffer Read/Write processing. During odd number byte access, data is read or written to the last byte of 16 bits, the mode is switched from the 16-bit mode to an 8-bit mode, and the last byte is read or written.

- (5) Receive data length count-down function (RCNT: Read count mode bit)

The receive data length count-down function is valid for CPU access only. When the FIFO selection is accessed for write processing while data is being written to or read

When the FIFO selection is accessed for write processing while data is being written to or read from the FIFO buffer, the FIFO buffer internal counter is initialized and the data that has been written (read) becomes invalid. Also, when this situation happens during FIFO data Write processing, the system assumes "FIFO Not Ready" (the host cannot respond to the IN token) and Empty interrupt and Null addition function (valid at continuous transfer setting) operate.

When FIFO Write processing is too slow, the above incident occurs. FIFO Write processing is terminated by the following processing.

(1) IVAL=1 was written and a short packet was specified.

(2) Data was written until the FIFO buffer becomes full.

\* At continuous transfer setting also, write processing is terminated by the processing indicated in (2) and the system cannot respond to the IN token even if data with the length between the maximum packet length and FIFO buffer length has been written. In this case, processing is terminated by writing IVAL=1.

See Chapter 6, "Data Transfers" for a FIFO buffer access example.

| Transfer type                                             | Bulk IN               | Interrupt IN   | Isochronous IN  |

|-----------------------------------------------------------|-----------------------|----------------|-----------------|

| Example of using endpor                                   | int                   |                |                 |

| Maximum packet size                                       | 64 bytes              | 32 bytes       | 100 bytes       |

| FIFO buffer size                                          | 512 bytes             | 64 bytes       | 256 bytes       |

| Double buffer structure                                   | 256*2                 | —              | 128*2           |

| FIFO number                                               | 08h~0Fh               | 20h~20h        | 22h~25h         |

| FIFO address                                              | 200h~3FFh             | 800h~83Fh      | 880h~97Fh       |

| Example of setting confi                                  | guration register 0/1 |                |                 |

| Transfer type                                             | 01                    | 10             | 11              |

| Transfer direction                                        | 1                     | 1              | 1               |

| Toggle mode                                               | 0                     | 0              | 0               |

| Buffer size                                               | 0011(256 bytes)       | 0000(64 bytes) | 0001(128 bytes) |

| Double buffer mode                                        | 1(256*2 bytes)        | 0              | 1(128*2 bytes)  |

| Continuous                                                | 1                     | 0              | 0               |

| transmit/receive mode                                     |                       |                |                 |

| First buffer number                                       | 08h                   | 20h            | 22h             |

| ResponsePID                                               |                       | _              |                 |

| DMA transfer mode                                         | 0                     | 0              | 0               |

| Null addition mode                                        | 1                     | 0              | 0               |

| Auto-clear mode                                           | 0                     | 0              | 0               |

| FIFO access mode                                          | 0                     | 0              | 0               |

| Maximum packet size                                       | 040h                  | 020h           | 064h            |

| Transfer type                                             | Bulk OUT              | Interrupt OUT  | Isochronous OUT |

| Example of using endpor                                   | int                   | · · · ·        |                 |

| Maximum packet size                                       | 64 bytes              | 32 bytes       | 100 bytes       |

| FIFO buffer size                                          | 1024 bytes            | 64 bytes       | 256 bytes       |

| Structure of double                                       | 512*2                 | <u> </u>       | 128*2           |

| buffer                                                    |                       |                |                 |

| FIFO number                                               | 10h~1Fh               | 21h~21h        | 26h~29h         |

| FIFO address                                              | 400h~7FFh             | 840h~87Fh      | 980h~A7Fh       |

| Example of setting config                                 | guration register 0/1 | -              |                 |

| Transfer type                                             | 01                    | 10             | 11              |

| Transfer direction                                        | 0                     | 0              | 0               |

| Toggle mode                                               | 0                     | 0              | 0               |

| Buffer size                                               | 0111(1024 bytes)      | 0000(64 bytes) | 0001(128 bytes) |

| Double buffer mode                                        | 1(1024*2 bytes)       | 0              | 1(128*2 bytes)  |

| Continuous                                                | 1                     | 0              | 0               |

| transmit/receive mode                                     |                       |                |                 |

| First buffer number                                       | 10h                   | 21h            | 26h             |

| Response PID                                              | —                     | _              |                 |

| DMA transfer mode                                         | 0                     | 0              | 0               |

|                                                           |                       | 0              | 0               |

| Null addition mode                                        | 0                     | U              |                 |

| Null addition mode<br>Auto-clear mode                     | 0                     | 0              | 0               |

| Null addition mode<br>Auto-clear mode<br>FIFO access mode |                       |                |                 |

Table 3-3 Example of Setting Each Endpoint Configuration Register

\* Notes on using a Null data transmit mode

When a double FIFO buffer is set and data is still being written from control CPU to one buffer after transmission of data in the other buffer to PC is completed, the M66290 assumes a buffer empty state and sends a NULL packet autoamtically. Therefore, a Null addition transmit mode must be set after the entire transmission data has been written to the FIFO buffer.

See Section 9.6, "Q & A Relating to the Null Addition Function.

#### 3.7. DMA Access

The M66290 can transfer data to FIFO buffers of endpoints EP1 to EP5 through DMA access. By DMA access, DMA FIFO data registers are accessed with a 16-bit width or an 8-bit width. In DMA access, the M66290 allocates buffer areas using endpoint configuration registers, specifies DMA transfer, and transfers data using DMA access FIFO data registers in the same way as for CPU access.

In DMA transfer by the M66290, data is transferred by handshaking between external DMAC, /Dreq, and /Dack signals, and the /Dreq signal is asserted when the buffer of the endpoint that is set to the DMA transfer mode is set to a Ready state. The Buffer Ready state enables indicates a Read Enable state if the endpoint transfer direction is set to OUT (receiving data from the host) and a Write Enable state if the transfer direction of the endpoint is set to IN (transmitting data to the host). The /Dack signal is handled in the same way as for the specification of the /CS signal and DMA FIFO data register address. The Read operation/Write operation is specified in the /RD signal or the /WR signal.

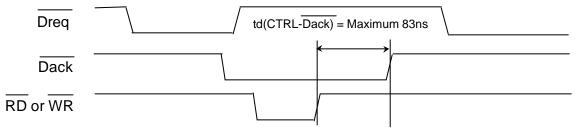

The M66290 negates /Dreq when detecting the /Dack signal ("L" level) by external DMAC after asserting the /Dreq signal. For assertion of the /Dreq signal for sending the next data, rising of the /RD or /WR signal (high-speed transfer mode) and rising of the /Dack signal (one-word transfer mode) can be selected. DMA transfer corresponds to only the single transfer that performs single-word transfer (16 or 18 bits) by one /Dreq activation.

\* The M66290 sets the data bus to an output state regardless of the access method when the /RD signal is input while the /Dack signal is asserted (data of the DMA FIFO register is output). Caution on the hardware design is necessary to avoid data collision. Since the M66290 is in an input state in other states, pull-up or pull-down processing must be performed externally to avoid internal lead-through current.

\* Note that the M66290 may stop the /Dreq signal according to the timing of /Dack in single-word transfer operation mode. In single-word transfer mode, the hardware must be designed so that the maximum period from rising of /RD or /WR to rising of Dack will be within 83ns. (See Figure 3-4..)

Figure 3-4 M66290 DMA Transfer Timing (Single-word mode)

In DMA transfer, an endpoint Buffer Not Ready interrupt and an Endpoint Buffer Empty interrupt occur according to the endpoint buffer state in the same way as for CPU access. However, there are the following differences with the CPU access for the Endpoint Buffer Ready interrupt.

(1) An Endpoint Buffer Ready interrupt does not occur when the transfer direction is IN.

(2) When the transfer direction is OUT, the M66290 receives a short data packet and an endpoint buffer ready interrupt occurs when transfer of the entire data that was received by DMA transfer has been transferred.

Reception of a short data packet can be recognized by the occurrence of an endpoint buffer ready interrupt and by referencing DMA\_DTLN (DMA FIFO receive data length register). DMA\_DTLN (DMA FIFO receive data length register) indicates the number of bytes of a short data packet or the number of bytes of received data up to the short data packet in continuous receive mode.

### 4. Initialization

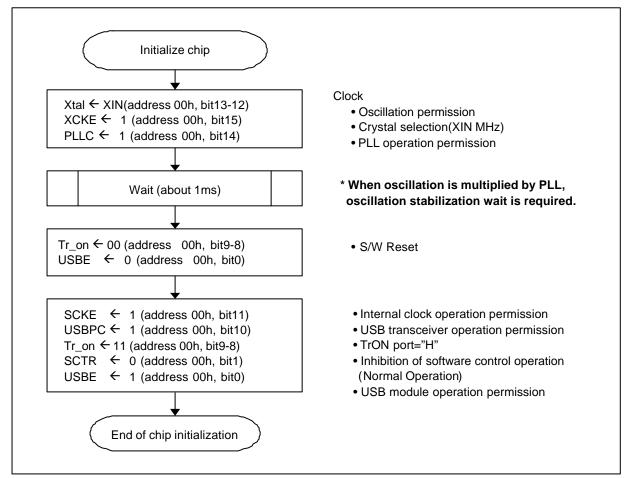

#### 4.1. Activating the M66290

Perform initialization processing after oscillation of the M66290 is stabilized. After PLL operation permission is set, a wait time (within 1ms) is required to avoid unstable operation by the clock. The host (upstream side) detects device connection when "H" is output from the Tr-On port.

See the "Table of registers" of the M66290 Datasheet for the status of each register at execution of software reset (USBE="0").

M66290 activation example

•The activation example shows the case where oscillation is supplied from a crystal oscillator.

•The software reset after a wait period also functions as notification of non-connection to the host for receiving the USB bus reset signal.

•This setting example shows activation of the M66290 (initialization) performed when Vbus is supplied from the host.

(Tr\_on and USBE bit setting : See Section 7.6, "Vbus Detection" for details of Vbus.) See below for the initialization flow of the M66290.

Figure 4-1 Example of M66290 Initialization

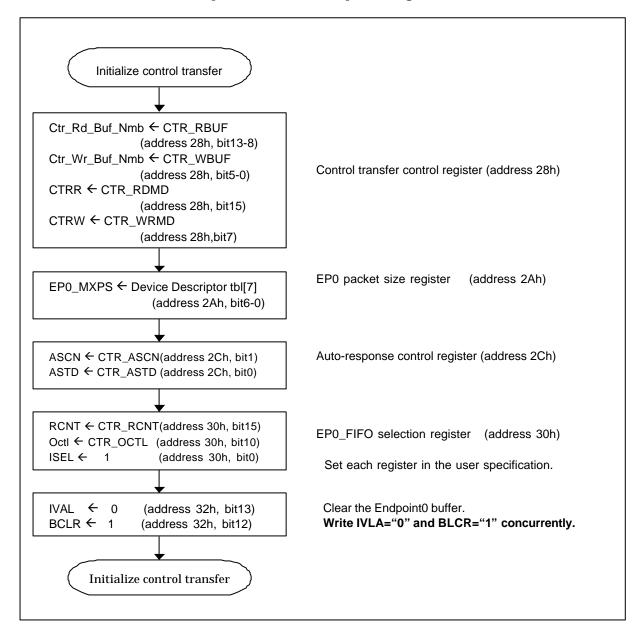

#### 4.2. Preparation for Control Transfers (Initialization of Endpoint0)

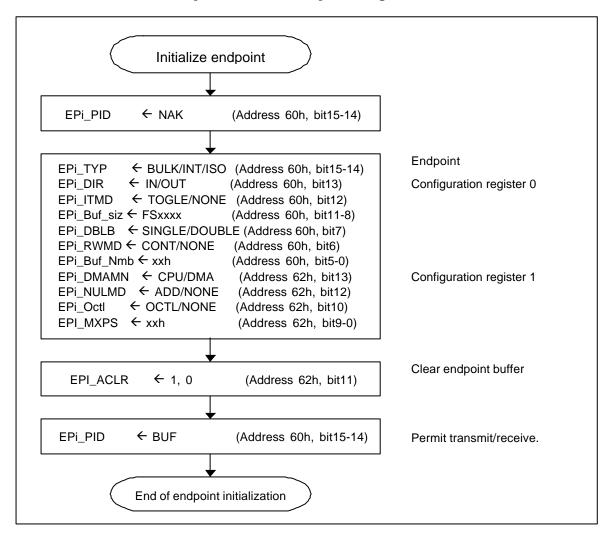

When the length of the data to be transmitted or received at the data stage is 256 bytes or more, continuous transfer cannot be used.

See Chapter 5, "Control Transfers" for the status transition for which auto-response is effective.

Specify the address so that the transmit/receive FIFO buffers do not overlap.

Initialize Endpoint0 after starting the M66290.

To clear the FIFO buffer, write IVLA = "0" and BLCR = "1" concurrently. In control transfer, the data packet in the Data stage uses the FIFO buffer. The reception of the data packet of the Setup stage is stored in a dedicated register. A size of "8 bytes" is recommended as the maximum packet size to correspond to the host controllers of the old type and the host OS of the old type.

Example of Endpoint0 initialization

•Each setting of Endpoint0 indicates the case where the macros are defined.

See below for the flow of Endpoint0 initialization processing.

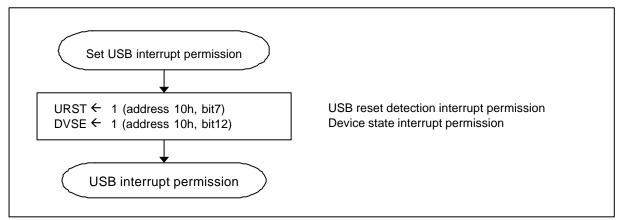

#### 4.3. USB Interrupt Enable

Set M66290 interrupt permission after starting the M66290 and initializing Endpoint0.

Set the timing of the M66290 interrupt permission taking into consideration the timing of the control CPU and other chips according to the system configuration and the purposes.

A device state transition interrupt, control transfer, and a control transfer stage transition interrupt other than USB bus reset and suspend detection are performed after detection of the USB bus reset signal.

Endpoint buffer interrupts (BEMPE, INTNE, INTRE) are issued after reception of a Set Configuration request.

Example of interrupt permission when Vbus is supplied (USB device has already been connected to the PC)

• A VBUS interrupt is not used in this setting example.

• A SUSP interrupt is not used in this setting example.

$\bullet$  This example shows the setting at activation of the M66290 (initialization) when Vbus is supplied from the host.

(Tr\_on and USBE bit setting : See Section 7.6, "Vbus Detection" for details.) See below for the flow of USB interrupt permission processing.

Figure 4-3 Example of USB Interrupt Permission Setting

## 5. Control Transfers

#### 5.1. Outline of Control Transfers

Control transfer is mainly bi-directional transfer that is used at setup and consists of at least two transaction stages (setup stage and status stage).

A data stage can be inserted between the two stages as optional.

In USB communication, control transfer by Endpoint0 and responses to a number of requests that are transmitted from a host to a device by control transfer of Endpoint0 are mandatory functions.

The M66290 is equipped with the following four functions to facilitate control transfer by Endpoint0 and the coding of a setup processing (bus enumeration) control program.

(1) Device state transition management function [See Sections 5.2 and 5.3 of this manual]

- (2) Data stage transition management function

- (3) Continuous transmit/receive function

[See Sections 5.4 and 5.5 of this manual] [See Sections 5.7 and 5.8 of this manual]

(4) Auto-response function

[See Section 5.9 of this manual]

The following transaction types are available for control transfer. Setup stage :

| Secup stuge .                                                                                  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Consists of setup, data (DATA0) and Handshake Packet.                                          |  |  |  |  |  |

| SETUP token                                                                                    |  |  |  |  |  |

| This series of transactions is expressed as <u>SETUP(DATA0)</u>                                |  |  |  |  |  |

| Data stage :                                                                                   |  |  |  |  |  |

| A data transaction is repeated as many times as required in the same way as for bulk transfer. |  |  |  |  |  |

| IN token → DATA(1/0) DATA(0/1) ··· DATA(0/1) → ACK                                             |  |  |  |  |  |

| OUT token $\longrightarrow$ DATA(1/0)DATA(0/1) $\cdots$ DATA(0/1) $\longrightarrow$ ACK        |  |  |  |  |  |

| This series of transactions is expressed as IN/OUT(DATA)                                       |  |  |  |  |  |

| Status stage :                                                                                 |  |  |  |  |  |

| Consists of the reverse tokens of the data stage and data packet of length "0" ("DATA1")       |  |  |  |  |  |

| OUT token                                                                                      |  |  |  |  |  |

| IN token — DATA1 (data of length 0) — ACK                                                      |  |  |  |  |  |

| This series of transactions is expressed as <u>IN/OUT(DATA1 : HS)</u>                          |  |  |  |  |  |

| The following types of control transfers are available.                                        |  |  |  |  |  |

| Control read transfer :                                                                        |  |  |  |  |  |

| SETUP(DATA0)IN(DATA1)IN(DATA0)IN(DATA0/1)OUT(DATA1 : HS)                                       |  |  |  |  |  |

| Setup Data stage Status                                                                        |  |  |  |  |  |

| Control write transfer :                                                                       |  |  |  |  |  |

| SETUP(DATA0)OUT(DATA1)OUT(DATA0)IN(DATA1 : HS)                                                 |  |  |  |  |  |

| Setup Data stage Status                                                                        |  |  |  |  |  |

| Control write no data transfer :                                                               |  |  |  |  |  |

| SETUP(DATA0) IN(DATA1 : HS)                                                                    |  |  |  |  |  |

| Setup Status                                                                                   |  |  |  |  |  |

|                                                                                                |  |  |  |  |  |

The M66290 is equipped with a stage management function and notifies stage transition through a control transfer transition interrupt. CPU performs stage processing related to the control transfer according to the interrupt factor. The contents of the data acquired at the setup stage clearly indicate to the device request type that is required by the host, and the device can perform related control transfer processing.

The M66290 is equipped with a continuous transmit/receive function. The continuous transmit/receive function in control transfer sends and receive data continuously up to 255 bytes without issuing an interrupt. By using the continuous transmit/receive function, the data stage no longer requires FIFO access for each transaction, thereby enhancing the CPU performance.

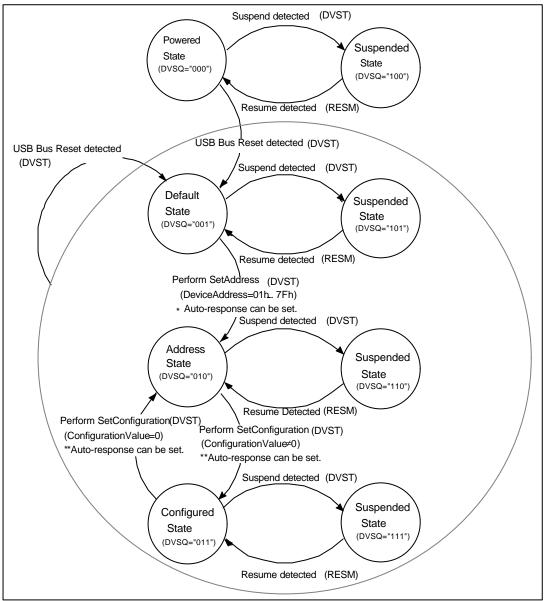

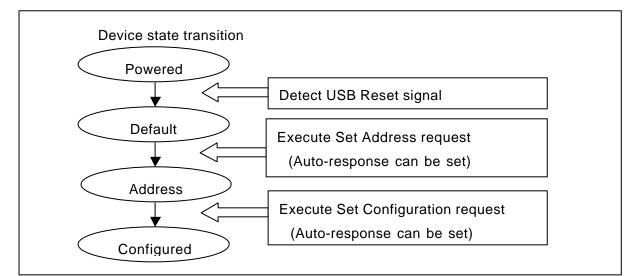

#### 5.2. USB Device State Transition

The M66290 manages device state transition of USB device states, which are Powered, Default, Address, Configured, Suspended, with hardware. Device state transition is notified to the CPU by a device state transition interrupt (DVST). When an auto-response is set, transfer of Set Address and Set Configuration requests can be completed without issuing an interrupt to the CPU.

Figure 5-1 Device State Transition

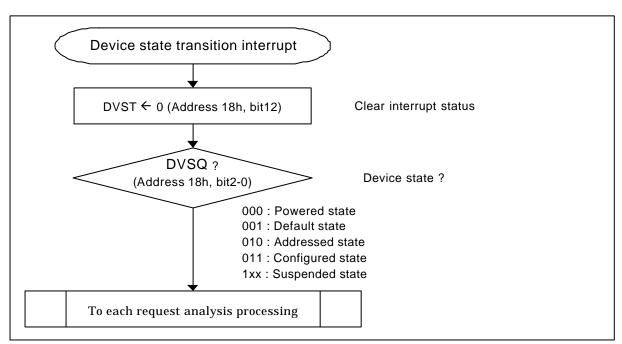

#### 5.3. Device State Transition Processing

When device state transition is executed normally, the M66290 generates a device state transition interrupt (DVST). However, the device state transition interrupt (DVST) will not occur, unless the bit corresponding to Interrupt Enable Register0 (address 10h) of the Detect USB Reset Interrupt, Set Address Interrupt, Set Configuration interrupt, and Suspend Detection Interrupt is set. In this case, the related value is set in the device state bit (DVSQ) of Interrupt Status Register0(address 18h) by the device state management function. Processing of the device state that was changed is performed and the user program is executed according to the state transition.

The M66290 changes states by detecting the USB reset signal, suspend signal, or Set Address/Set Configuration request. Note that the device state bit (DVSQ) has been changed at the occurrence of an interrupt.

(1) Power state software Reset

No processing required

(2) Default state USB bus reset detection processing

Control transfer enable

(3) Address state (4) Configured state

(5) Suspend state Suspend signal detection

Set Address request detection

Address retention, etc. Set Configuration request detection Configuration number retention, etc. Suspend processing

Figure 5-2 Device State Transition

Figure 5-3 Example of a Setup Stage Control Procedure

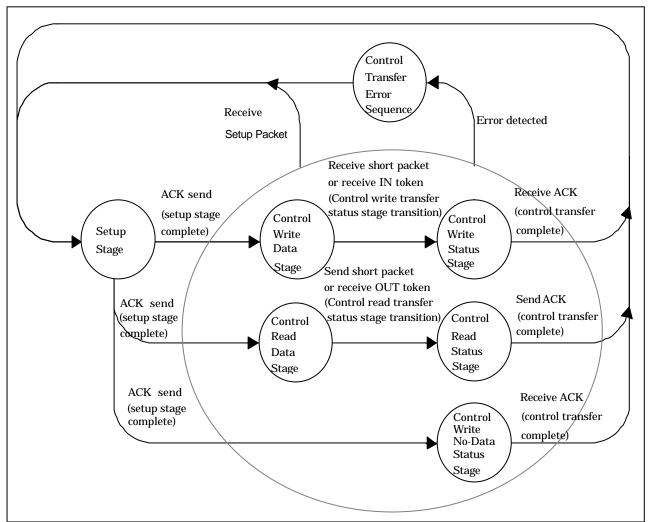

#### 5.4. Control Transfer Stage Transition

The M66290 manages transition of control transfer stages, namely a setup stage, a data stage, and a status stage through hardware. Control transfer stage transition is notified to the CPU by a control transfer stage transition interrupt (CTRT). When auto-response is set, transfer can be completed without generating an interrupt to CPU for the Set Address and Set Configuration requests. There are five CTRT interrupt factors; setup stage completion, Control Write transfer status stage transition, Control Read transfer status stage transition, Control Transfer completion, and control transfer sequence error. The following seven Control Transfer sequence errors can be detected by hardware.

When hardware detects a control transfer sequence error, the response PID is automatically set to STALL("1x") and the contents are retained until the next setup packet is received.

- 1. Receiving the IN token packet at the Control Write data stage (Receiving the IN token packet when no ACK response has been issued for the OUT token packet of the data stage)

- 2. Receiving the OUT token packet at the Control Write status stage

- 3. Receiving the OUT token packet at the Control Read data stage (Receiving the OUT token packet when no data has been transferred to the IN token packet of the data stage)

- 4. Receiving the IN token packet at the Control Read status stage

- 5. Receiving a Data Packet other than Null data at the Control Read status stage

- 6. Receiving the OUT token packet at the Control Write no data status stage

- 7. Receiving data that exceeds the maximum packet size

When a data packet exceeding the wLength value of the request is received in the control data stage, the M66290 cannot recognize the event as a sequence error.

Figure 5-4 Control Transfer State Transition

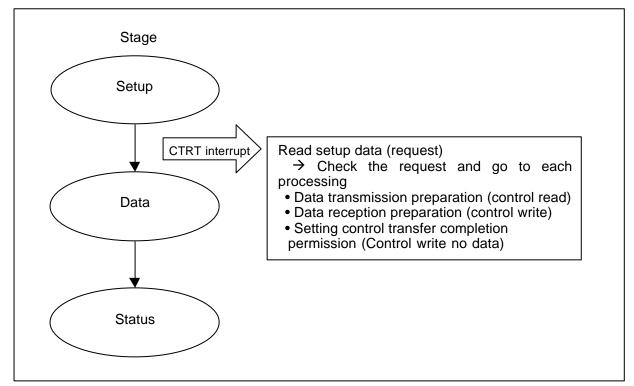

#### 5.5. Stage Transition Processing

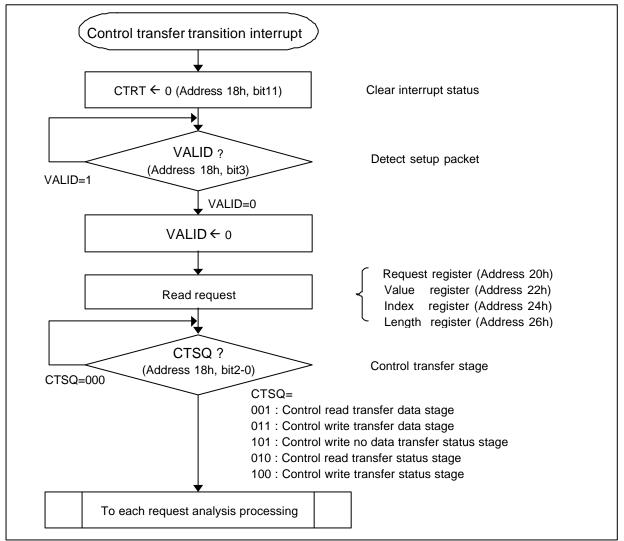

The CPU that detected control stage transition of the M66290 through a CTRT interrupt checks the transfer stage and performs related processing. The M66290 stores the data packet (request from the host PC) of the setup stage in the dedicated register. The data packet of the data stage uses Endpoint0 FIFO.

Note that the stage of 66290 control transfer stage bit (CTSQ) has been shifted at the occurrence of a CTRT interrupt.

- (1) Idle or setup stage

- (2) Control read transfer data stage transmission

- No processing is required

- Data (Request) analysis and preparation for data

- (3) Control write transfer data stage reception

- Data (Request) analysis and preparation for data

- (4) Control write no data transfer status stage

- (5) Control read transfer status stage

- (6) Control write transfer status stage

- No processing is required Data analysis

Data (Request) analysis

- (7) Control transfer sequence error

- Preparation for setup re-reception

Figure 5-5 Status Stage Transition Processing

#### 5.6. Setup Stage

A setup transaction transfers a request composed 8bytes(data packet of the setup stage) from the host and stores it in the following four registers.

| Table 5-1 Request Storage Register |         |      |              |  |  |  |  |

|------------------------------------|---------|------|--------------|--|--|--|--|

| Register name                      | Address | Bit  | Value stored |  |  |  |  |

| Poquest                            | 20h     | 15-8 | bRequest     |  |  |  |  |

| Request                            | 2011    | 7-0  | bmRequest    |  |  |  |  |

| Value                              | 22h     | 15-0 | wValue       |  |  |  |  |

| Index                              | 24h     | 15-0 | wIndex       |  |  |  |  |

| Length                             | 26h     | 15-0 | wLength      |  |  |  |  |

|                                    |         |      |              |  |  |  |  |

Table 5.1 Dequest Storage Degister

When the request is stored in the registers normally, the M66290 generates a control transfer stage transition interrupt (CTRT). In this case, the setup packet detect bit (VALID) of the interrupt status register 0 is set to "1". The control transfer stage management function sets a related value in the control transfer stage bit (CTSQ) in the register. After sets "0" in the setup packet detect bit (VALID), reads the request from the registers, checks any errors, performs request analysis processing, and prepares for the data stage.

When receiving a setup transaction normally, the M66290 sends an "ACK" response. After receiving a setup packet, the M66290 automatically sets PID of Endpoint0 to NAK.

See below for the flow of control transfer transition processing.

Figure 5-6 Example of Control Transfer Transition Interrupt

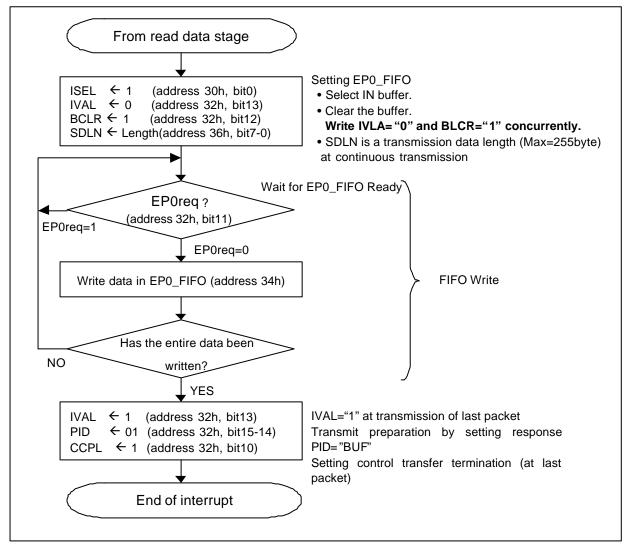

#### 5.7. Control Read Transfer Processing (Data Stage)

When the request that was received at the setup stage is a Control Read request, the data that was requested to the host PC in the data stage is transmitted.

The M66290 is equipped with a continuous transfer function and can transmit multiple packets continuously at data transmission (data stage) in control read. The maximum length of continuous transmission data in control transfer is 255 bytes. Set non-continuous transmission, when transmitting data exceeding 255 bytes. When sending a short packet in the data stage, the M66290 automatically changes the stage to a status stage. When the length of the data to be sent is an exact multiple of the maximum packet size, the M6290 automatically adds a Null packet (handled as a short packet), as specified in the USB Specification after sending the entire data and changes the stage. For transmission of data with a size less than the FIFO size, send a short packet by setting "IVAL=1" after writing the last data.

See below for the flow of Control Read transfer processing.0.

Figure 5-7 Example of Control Read Transfer Processing

\* When CCPL is set at a status stage, NAK packet for the OUT token is inserted.

\* When the ISEL bit is accessed during FIFO write processing, the processing becomes invalid.

\* When writing data of odd number bytes, use FIFO access 8bit mode bit (Octl) function. The mode can be changed to "Octl" when the last byte is written.

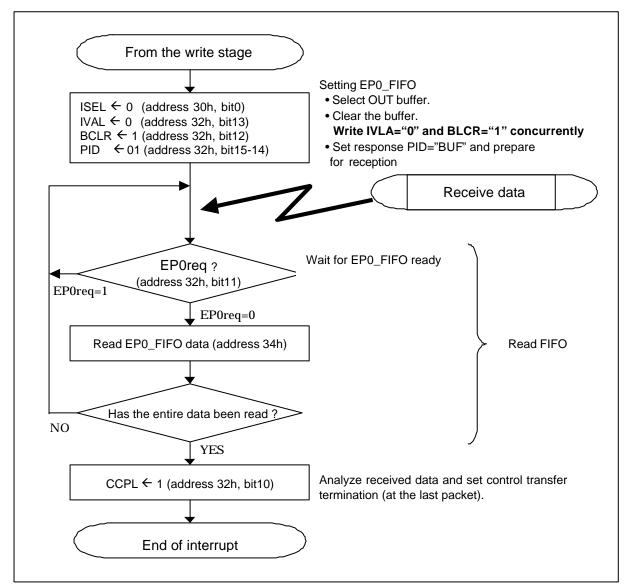

#### 5.8. Control Write Transfer Processing (Data Stage)

When the request that was received at the setup stage is a Control Write request, the data that was requested to the host PC is received at the data stage.

The M66290 is equipped with a continuous transfer function at data reception (data stage) in Control Write and can receive multiple packets continuously. The maximum length of continuous reception data in control transfer is 255 bytes. Set a non-continuous mode when receiving data more than 256 bytes.

When receiving a short packet in data stage, the M66290 automatically changes the stage to a status stage. The M66290 also changes the stage when receiving a Null packet (handled as a short packet) as specified in the USB specification.

See below for the flow of Control Write transfer processing.

Figure 5-8 Example of Control Write Transfer Processing

- \* Set CCPL after analyzing the data that was received at the status data stage.

- \* When the ISEL bit is accessed during FIFO read processing, the read counter becomes invalid.

- \* When reading data of odd number of bytes, use FIFO access 8bit mode bit (Octl) function. The mode can be changed to "Octl" when the last byte is read.

- \* When the last packet is received in non-continuous control receive mode, an INTR interrupt occurs after a stage transition interrupt. Therefore, data must be read by checking the INTR status during status stage transition interrupt processing.

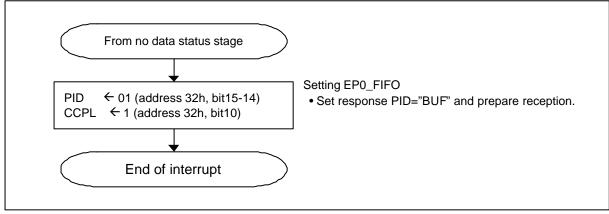

#### 5.9. Control Write No Data Transfer Processing (Status Stage)

When the request that was received at a setup stage is a Control Write No Data request, the data does not transmit and receive at a data stage.

When receiving a Control Write No Data request, the M66290 automatically changes the stage to a status stage. The bmRequestType and wLength field are used for checking a Control Write No Data request.

The M66290 can complete transfer without generating an interrupt in the CPU for the Set Address and Set Configuration standard requests in Control Write No Data transfer.

- In Address auto-response mode, the M66290 sends automatically responses for the Set Address Request (DeviceAddress=01h~7Fh)in the Default state, but it dose not response when the device state is another state or DeviceAddress 01h~7Fh for the Set Address Request.

- In Configuration auto-response mode, the M66290 sends automatically a response for the Set Configuration request (ConfigurationValue 0) when the device state is the Address state and for the Set Configuration request (Configuration Value=0) in the Configured state. The M66290 does not response automatically for requests in other states and for the Set Configuration requests with values different from the value indicated above.

See below for the flow of data transfer stage processing.

Figure 5-9 Example of Control No Data Transfer Processing

### 6. Data Transfers

#### 6.1. Outline of Data Transfers

Data transfer is single-direction transfer and consists of at least two packets (token packet and data packet). In the transfer that guarantees data transfer between a host and a device by the retransmit function, a handshake packet is added following the data packet, involving 3 packets. Three transfer types are available; isochronous transfer consisting of 2 packets that does not detect communication errors between a host and a device and guarantees a transfer rate, bulk transfer and interrupt transfer consisting of 3 packets that detects communication errors, but does not guarantee a transfer rate.

See below for the features of each data transfer type.

| Transfer type                     | Bulk transfer                  | Interrupt transfer | Isochronous transfer |

|-----------------------------------|--------------------------------|--------------------|----------------------|

| Real time feature                 | Low                            | Real time          | High                 |

| Transfer rate                     | Not guaranteed                 | Not guaranteed     | Guaranteed           |

| Volume of transfer data           | Large                          | Small              | Small – large        |

| Number of packets                 | 3                              | 3                  | 2                    |

| Data packet                       | Data0/Data1                    | Data0/Data1        | Data0                |

| Handshake                         | Yes                            | Yes                | No                   |

| Maximum packet size 8, 16, 32, 64 |                                | 0~64               | 0~1023               |

| Features of M66290 fu             | inction                        |                    |                      |

| Continuous transmit<br>function   | Valid                          | Invalid            | Invalid              |

| Double buffer function            | Valid                          | Valid              | Valid                |

| Null addition function            | Valid (at continuous transfer) | Invalid            | Invalid              |

| DMA access                        | Valid                          | Valid              | Valid                |

Table 6-1

List of Data Transfer Types

A data transfer transaction is specified as follows.

Bulk IN and interrupt IN :

Consists of IN token, data (DATA0/1), and handshake packets.

Isochronous IN :

Consists of IN token and data (DATA0).

IN token → DATA(0) Bulk OUT and interrupt OUT :

Consists of OUT token, data (DATA0/1) and handshake packets.

| OUT token         | DATA(0/1) | <br>ACK |  |

|-------------------|-----------|---------|--|

| Isochronous OUT : |           |         |  |

Consists of OUT token and data (DATA0).

OUT token ---> DATA(0)

This series of transactions is expressed as IN(DATA0) OUT(DATA0)

Communication of each data transfer is performed in the following transaction structure. Bulk IN transfers and interrupt IN transfer :

| IN(DATA0)                  | IN(DATA1)                                      | IN(DATA0)  | IN(DATA1)  | ••• IN(DATA0/1)  |  |  |  |

|----------------------------|------------------------------------------------|------------|------------|------------------|--|--|--|

| Isochronous IN tra         | nsf <u>er :</u>                                |            |            |                  |  |  |  |

| IN(DATA0)                  | IN(DATA0)                                      | IN(DATA0)  | IN(DATA0)  | ••• IN(DATA0)    |  |  |  |

| Bulk OUT transfer          | Bulk OUT transfer and interrupt OUT transfer : |            |            |                  |  |  |  |

| OUT(DATA0)                 | OUT(DATA1)                                     | OUT(DATA0) | OUT(DATA1) | ••• OUT(DATA0/1) |  |  |  |

| Isochronous OUT transfer : |                                                |            |            |                  |  |  |  |

| OUT(DATA0)                 | OUT(DATA0)                                     | OUT(DATA0) | OUT(DATA0) | ••• OUT(DATA0)   |  |  |  |

#### 6.2. Features of Data Transfers by the M66290

The M66290 can transfer data of all types that are specified in USB communication. The M66290 is equipped with the following functions to facilitate the coding of data transfer programs.

(1) Abundant endpoint interrupts

[See 3.5 and 6.3 of this manual]

(2) FIFO buffer of a total of 3K bytes

[See 3.6, 6.4, and 6.5 of this manual]

(3) Continuous transmit/receive function (bulk transfer only) [See 3.6]

(4) Enables transfer conditions for each endpoint [See 3.6 of this manual]

The M66290 is equipped with a double buffer function. Therefore, buffers can be accessed without having to wait for a free FIFO buffer while the device is communicating with the host. By using the double buffer function, data transfer of high USB bus efficiency can be achieved.

The M66290 is also equipped with a continuous transmit/receive function for bulk transfer only. In data transfer, the M66290 has a function that transmits and receives data continuously up to 1K bytes without issuing an interrupt. In bulk transfer, if the continuous transmit/receive function is used, FIFO access is not required for each transfer, enhancing the CPU performance.

\*The M66290 automatically issues a "NAK" response when receiving a Token packet from the host if the FIFO buffer cannot be accessed due to Full/Empty.

See below for the flow of endpoint initialization processing.

#### 6.3. Data Transmit/Receive Interrupt

The M66290 is equipped with three types of data transfer interrupt functions; they are Buffer Ready, Buffer Not Ready, and Buffer Empty. For each interrupt, the endpoint from which the interrupt factor occurred can be recognized from status registers 1 to 3. Note that the occurrence factor of a data transfer interrupt varies according to the transfer type, transfer direction, and access method. (For the difference of factors, see [3.5. Data Transfer Interrupt].) See below for the flow of data transmit/receive processing.

Figure 6-2 Example of Data Transmit/Receive Control Procedure

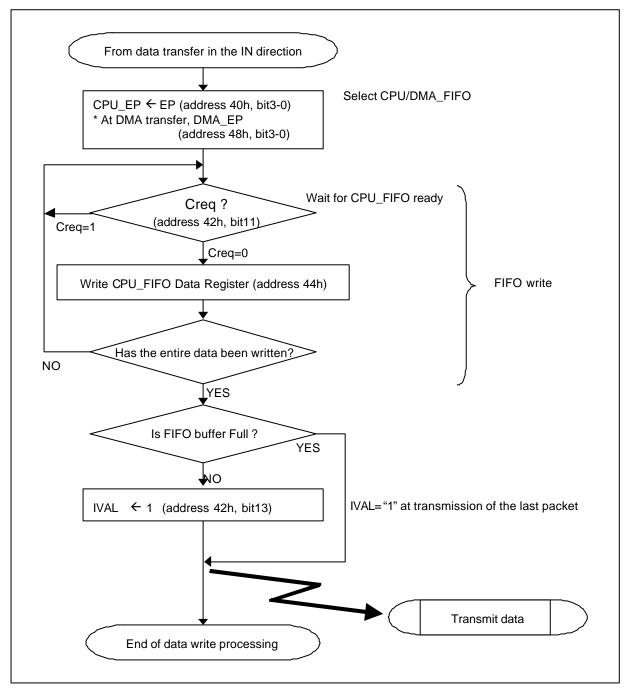

#### 6.4. FIFO Access (Data Transmit: IN Direction)

When there is data to be transmitted to the device side, the data is transferred to the host by the IN transaction. In USB communication, data is transferred by host PC sampling. Therefore, the device writes data to be transmitted to the FIFO buffer of the M66290 in advance and waits for the IN token from the host. The M66290 notifies that the write processing to the FIFO buffer is enabled by termination of data transfer, by generating an interrupt. (For details of the factor, see [3.5. Data Transfer Interrupt].)

See below for the flow of data write processing.

Figure 6-3 Example of Data Transmission Setting Control Procedure

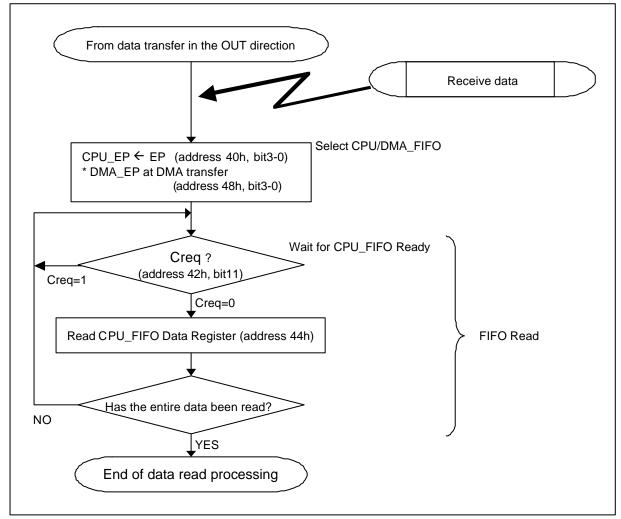

#### 6.5. FIFO Access (Data Receive: OUT Direction)

When a device receives data from a host PC, data is transferred by the OUT transaction. In USB communication, data is transferred by host PC sampling. Therefore, the device waits for an OUT token from the host by emptying the FIFO buffer of the M66290. The M66290 notifies that the FIFO buffer contents can be read by termination of data transfer. (For details of factors, see [3.5 Data Transfer Interrupt]. )

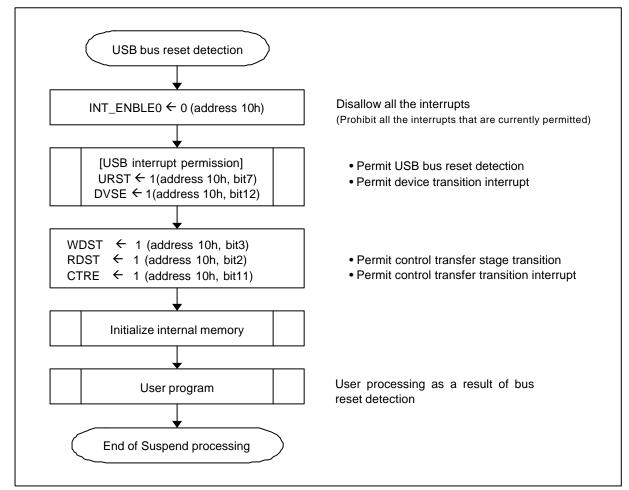

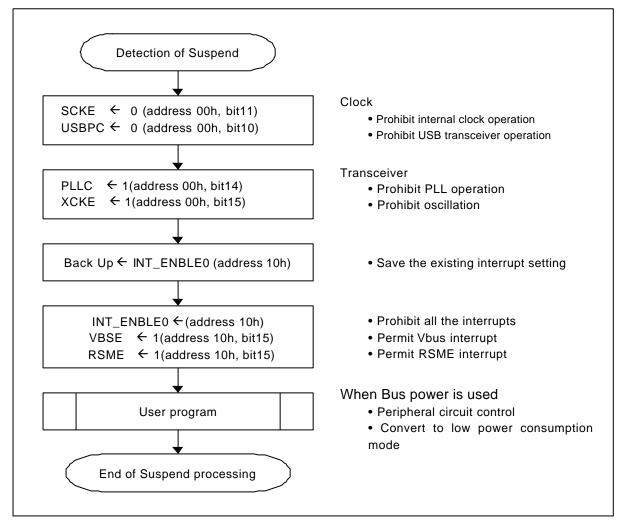

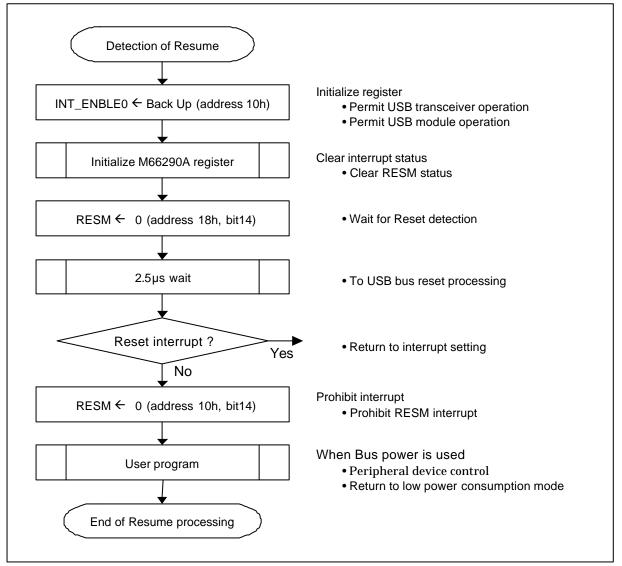

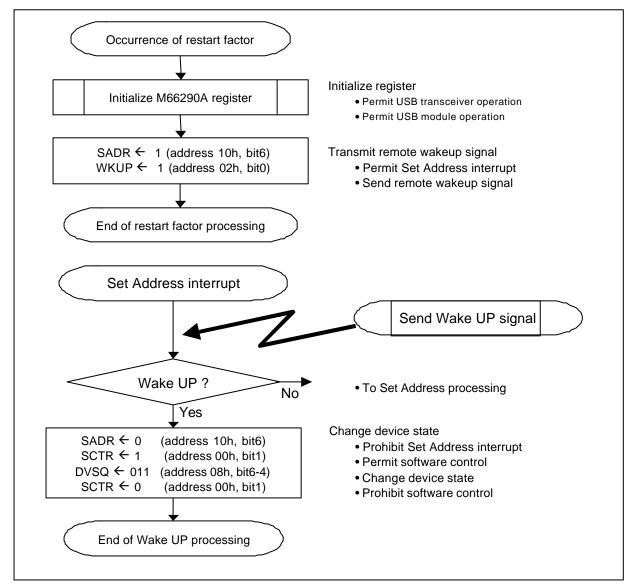

See below for the flow of data read processing.