### Designing an Idle-Bus Failsafe Network for the HS-26Cxx32 Family

## Introduction

This application note describes the design of an idle-bus failsafe network when using the HS-26Cxx32 family of Radiation Hardened RS-422 Receivers.

This family includes HS-26C32EH, HS-26C32RH, HS-26C32RH-T, HS-26CT32EH, HS-26CT32RH, HS-26CLV32EH, and HS-26CLV32RH.

In RS-422 data transmission, there are instances where a receiver might not receive data due to certain bus faults. In such instances, a receiver is required to indicate the fault by turning its output high. This is known as a failsafe feature.

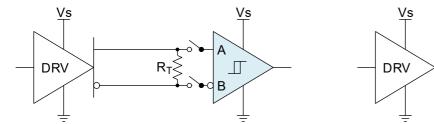

If the connection between the bus and the receiver is broken or open, the receiver inputs float (Figure 1). To indicate this fault, the receiver inputs are internally biased, creating a differential input voltage large enough to turn the receiver output high. This is known as an open-bus failsafe.

Figure 1. Open Bus: Inputs are Floating

Figure 2. Idle Bus: Inputs are Shorted

Another fault is, when a receiver is connected to a terminated bus and the transmitter at the opposite end of the bus is disabled (Figure 2). In this case, the bus is not actively driven or idle, and the low-impedance termination resistor reduces the differential bus voltage to zero. This is below the input sensitivity of the receiver, making its output state undetermined. Some receiver outputs might turn high, while others turn low or even oscillate.

To ensure the receiver output state is high during an idle bus condition, an external resistor network is required to create the necessary input voltage that turns the output high. This is known as an idle-bus failsafe.

While the open-bus failsafe feature is incorporated in the receiver design, the idle-bus failsafe feature must be added.

# Contents

| 1. | Design Equations            | 2 |

|----|-----------------------------|---|

| 2. | Receiver Input Structure    | 3 |

| 3. | Idle-Bus Failsafe Network   | 4 |

| 4. | Other Design Considerations | 5 |

| 5. | Conclusion                  | 6 |

| 6. | Revision History            | 6 |

## 1. Design Equations

This section provides design equations for an idle-bus failsafe biasing network.

Table 1 lists the recommended resistor values for  $R_B$  and  $R_T$  when using the HS-26Cxx32 receivers.

### Table 1. Recommended Resistor Values for $V_{FS}$ = 0.5V, RIN(min) = 6k $\Omega$ , Z0 = 100 $\Omega$

| Parameter                 | Symbol              | Values |     |     | UNIT |   |

|---------------------------|---------------------|--------|-----|-----|------|---|

| Minimum Supply Voltage    | V <sub>S(min)</sub> | 3.0    |     | 4.5 |      | V |

| # Bus Receiver            | n                   | 1      | 10  | 1   | 10   | - |

| Failsafe Biasing Resistor | R <sub>B</sub>      | 300    | 300 | 448 | 448  | Ω |

| Termination Resistor      | R <sub>T</sub>      | 121    | 133 | 114 | 124  | Ω |

## 2. Receiver Input Structure

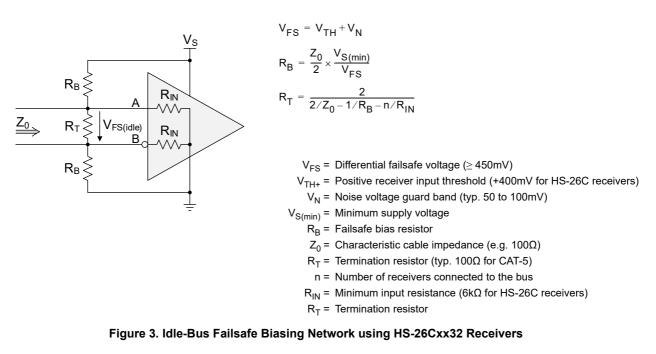

The RS-422 Standard specifies the minimum impedance between a receiver input and receiver ground with 4000 $\Omega$ . The input impedance is defined as the ratio of an applied input voltage difference to the corresponding difference in measured input current:  $R_{IN} = \Delta V_i / \Delta I_i$ . These measurements apply with the receiver power supply in both power-on and power-off conditions (Figure 4).

Figure 4. Receiver Input Current-Voltage Measurement

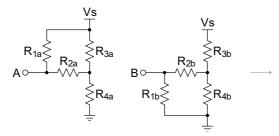

Figure 5 shows the simplified input structure of a HS-26Cxx32 receiver. Both inputs, here denoted as A and B, have identical voltage dividers. The differential failsafe voltage for a bus-open condition,  $V_{FS(open)}$ , is generated by connecting  $R_{1a}$  to the receiver supply and  $R_{1b}$  to receiver ground.

Figure 5. Receiver Input Structure

Applying simple but tedious voltage divider calculations results in the open-circuit input voltages:

$$V_{A} = V_{S} \times \left( \frac{R_{2}}{R_{1} + R_{2}} + \frac{R_{4}}{R_{4} + R_{3} \parallel (R_{1} + R_{2})} \times \frac{R_{1}}{R_{1} + R_{2}} \right) \qquad \text{and} \qquad V_{B} = V_{S} \times \frac{R_{4} \parallel (R_{1} + R_{2})}{R_{3} + R_{4} \parallel (R_{1} + R_{2})} \times \frac{R_{1}}{R_{1} + R_{2}} \times \frac{R_{1}}{R_{1} + R_{2}} + \frac{R_{2} \parallel (R_{1} + R_{2})}{R_{1} + R_{2}} \times \frac{R_{1} \parallel (R_{1} + R_{2})}{R_{1} + R_{2} + R_{2} + R_{1} + R_{2} + R_{2$$

Then, calculating their difference yields the open-bus failsafe voltage:

(EQ. 1)

$$V_{FS(open)} = \frac{V_S}{1 + R_1 / (R_2 + R_3 || R_4)}$$

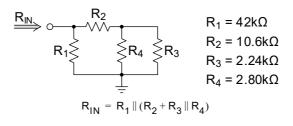

In the worst-case condition, when the receiver supply is powered off, both resistors  $R_{3a}$  and  $R_{3b}$  are parallel to  $R_{4a}$  and  $R_{4b}$ , respectively. Also,  $R_{1a}$  is parallel to the remaining resistor network for input A. This results in an input impedance structure that is common to both inputs (Figure 6).

intersil

Therefore, the impedance is calculated with:

(EQ. 2)  $R_{1N} = R_1 \| (R_2 + R_3 \| R_4)$

*Note*: The HS-26Cxx32 internal resistor values in Figure 6 are nominal, therefore, yielding an R<sub>IN</sub> of  $9k\Omega$ . However, across temperature, the minimum input impedance temperature has been determined by  $R_{IN(min)} = 6k\Omega$ , and therefore 50% higher than the  $4k\Omega$  required by the RS-422 Standard.

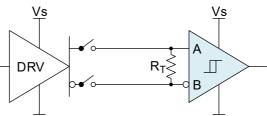

### 3. Idle-Bus Failsafe Network

The input sensitivity of a HS-26Cxx32 receiver is specified with  $\pm$ 400mV. A differential input voltage of >+400mV forces the receiver output high, while a V<sub>ID</sub> <-400mV turns the output low. Voltages between these thresholds cause the output to be undetermined. This condition can occur when a bus driver is disabled, and its outputs become high impedance. In this case, the low-impedance termination resistor reduces the bus voltage to zero and

the bus assumes an idle state.

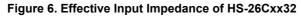

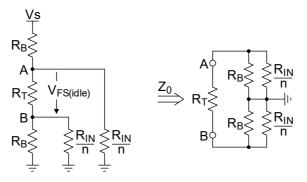

To ensure the receiver output turns high when the bus idles, a resistive failsafe biasing network is implemented to provide a differential voltage across  $R_T$  greater than +400mV (Figure 7).

Figure 7. Idle-Bus Failsafe Biasing

Designing a robust failsafe biasing network requires that the idle-bus failsafe voltage includes a noise guard band above the positive receiver input threshold,  $V_{FS(idle)} = V_{TH+} + V_N$ .  $V_{TH+} = +400$ mV and  $V_N$  is the expected peak-to-peak noise.

To find an equation for the failsafe voltage, the circuit in Figure 7 is converted into the lumped equivalent circuit of Figure 8, where  $R_{IN}/n$  represents the combined input impedance of n receivers.

Figure 8. Lumped Equivalent Circuits

Then, establishing the node currents and voltages gives:

Node A

$$\frac{V_S - V_A}{R_B} = \frac{V_A - V_B}{R_T} + \frac{V_A}{R_{IN}/n} \Rightarrow V_A = \frac{V_S / R_B + V_B / R_T}{1/R_B + n/R_{IN} + 1/R_T}$$

Node B

$$\frac{V_A - V_B}{R_T} = \frac{V_B}{R_B} + \frac{V_B}{R_{IN}/n} \Rightarrow V_B = \frac{V_A/R_T}{1/R_B + n/R_{IN} + 1/R_T}$$

Deriving the failsafe voltage  $V_{FS(idle)} = V_A - V_B$  yields:

(EQ. 3)

$$V_{FS(idle)} = \frac{V_S}{1/R_B(2/R_T + n/R_{IN})}$$

And solving for R<sub>T</sub> gives:

(EQ. 4)

$$R_{T} = \frac{2}{(V_{S}/V_{FS(idle)} - 1)/R_{B} - n/R_{IN}}$$

The second design requirement in Figure 8 is that the impedance of the resistor network (including  $R_T$ ) must match the characteristic cable impedance  $Z_0$ :

(EQ. 5)  $Z_0 = R_T \| 2(R_{IN} / n \| R_B)$

Solving this equation for RT gives:

(EQ. 6)

$$R_{T} = \frac{2}{2/Z_{0} - 1/R_{B} - n/R_{IN}}$$

Then, equating both  $R_T$  equations (Equation 4 = Equation 6) and solving for  $R_B$  provides the bias resistor value:

(EQ. 7)

$$R_B = \frac{Z_0}{2} \times \frac{V_S}{V_{FS(idle)}}$$

Having established R<sub>B</sub>, use Equation 6 to calculate R<sub>T</sub>.

### 4. Other Design Considerations

At high data rates, the capacitance of the transmission cable can round the edges of the bus signal significantly. Counteract this effect by making  $R_{IN}$  slightly smaller than  $Z_0$ . This results in an underdamped termination that maintains the crisp edges of fast signal transitions.

Also, try minimizing the ground potential difference (GDP) between driver and receiver. The RS-422 Standard demands high common-mode capability for the receiver but none for the driver. However, in an idle bus condition, the GPD adds to the receiver common-mode input voltage, which can quickly exceed the absolute maximum voltage ratings of the driver's bus and supply terminals.

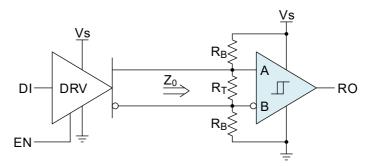

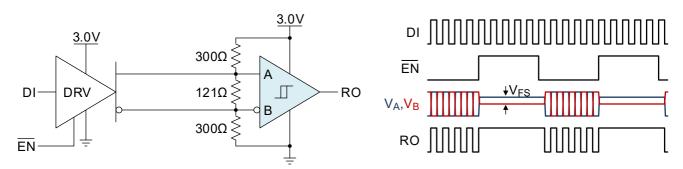

Figure 9. Idle-Bus Failsafe in Action with HS-26CLV31 Driver and HS-26CLV32 Receiver

# 5. Conclusion

The design methodology for implementing an idle-bus failsafe network using the HS-26Cxx32 family of RS-422 receivers is outlined in this application note. While these devices include internal mechanisms for open-bus fault detection, idle-bus conditions require an external biasing network to ensure predictable receiver behavior. Detailed design equations and resistor selection guidelines are provided to achieve the required differential input voltage and impedance matching. By following these recommendations and accounting for factors such as ground potential differences and signal integrity at high data rates, designers can ensure robust and reliable system performance in demanding environments.

# 6. Revision History

| Revision | Date        | Description      |  |  |

|----------|-------------|------------------|--|--|

| 1.00     | Jun 2, 2025 | Initial release. |  |  |

### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.