# Capacitive Load Compensation of Voltage Followers using the ISL7xx44 Amplifiers

## Introduction

The voltage follower is the most demanding configuration for an operational amplifier as the device operates at its phase margin. Loading the follower output capacitively reduces this phase margin, which can lead to instability. This manifests itself in output signal overshoot, ringing, and at worst in self-sustaining oscillations.

To help engineers design stable buffer amplifiers despite capacitive loading, this application note describes the two most popular phase compensation techniques, which are passive and active cap-load compensation.

The ISL7xx44 family of wideband amplifiers includes the ISL70244SEH, ISL73244SEH, ISL70444SEH, ISL73444SEH, and ISL71444M devices.

## **Contents**

| 1. | Desig                        | gn Equations                            | 2 |  |  |

|----|------------------------------|-----------------------------------------|---|--|--|

| 2. | Stabi                        | lity Analysis using Rate-of-Closure     | 2 |  |  |

|    |                              | ive Cap-Load Compensation               |   |  |  |

|    |                              | Determining the Value of R <sub>S</sub> |   |  |  |

| 4. | Active Cap-Load Compensation |                                         |   |  |  |

|    |                              | Calculating Component Values            |   |  |  |

| 5. | Conc                         | lusion                                  | 5 |  |  |

| 6. | Revis                        | sion History                            | 6 |  |  |

## 1. Design Equations

This section provides a summary of the design equations for both compensation techniques. Both circuits use a series resistor  $R_S$  that isolates the load capacitance  $C_I$  from the op-amp output.

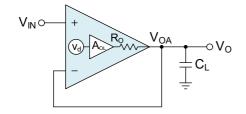

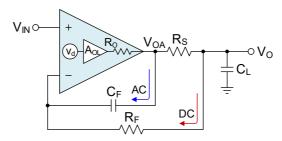

The simpler and more widespread *passive* cap-load compensation (Figure 1) applies direct feedback from output to inverting input and relies on  $R_S$  to provide the necessary phase compensation. Its main disadvantage is the loss of DC accuracy at the circuit output due to the voltage drop across  $R_S$ .

Figure 1. Passive Cap-Load Compensation with R<sub>S</sub> and Single Feedback Path

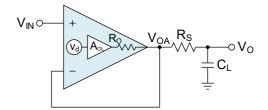

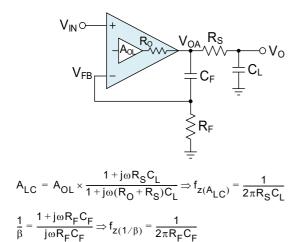

The more complex active cap-load compensation (Figure 2) uses two feedback loops around  $R_S$ . The feedback path using  $R_F$  restores DC accuracy at the output while the feedback through  $C_F$  maintains stability at high frequencies.

Figure 2. Active Cap-Load Compensation with R<sub>S</sub> and Dual Feedback

Table 1 lists the key parameters to use in the design equations for the ISL7xx44 op-amp family of wideband amplifiers recommended for this application.

Table 1. ISL70244 Parameters

| Parameter                  | Symbol         | Value |     |      | Unit |

|----------------------------|----------------|-------|-----|------|------|

| Supply Voltage Range       | V <sub>S</sub> | ±18   | ±5  | ±1.5 | V    |

| Minimum Gain Bandwidth     | GBW            | 17    | 15  | 10   | MHz  |

| Open-Loop Output Impedance | R <sub>O</sub> |       | 100 |      | Ω    |

# 2. Stability Analysis using Rate-of-Closure

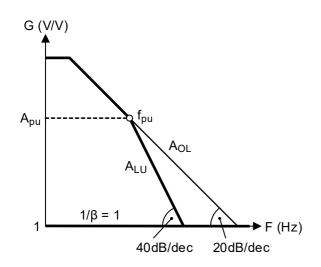

Stability analysis uses the rate-of-closure (ROC) between the circuit's open-loop gain A and the noise-gain  $1/\beta$  (reciprocal of the feedback factor  $\beta$ ) as criteria to determine whether a circuit is stable (ROC = 20dB/dec) or instable (ROC = 40dB/dec).

# 3. Passive Cap-Load Compensation

In the unloaded case, the op-amp's  $A_{OL}$  crosses the 1/ $\beta$  line at an ROC of 20dB/decade, meaning the circuit is stable. In the loaded case, the load capacitance ( $C_L$ ) forms a low-pass filter with the op-amp output impedance ( $R_O$ ). This adds phase lag to  $A_{OL}$ , resulting in the loaded, uncompensated open-loop gain response,  $A_{LU}$ .  $A_{LU}$  has a roll-off of 40dB/decade, starting at the pole frequency  $f_{pu}$  = 1/( $2\pi R_O C_L$ ). It crosses 1/ $\beta$  at an ROC of 40dB/dec, indicating instability.

Figure 3. Loading Op-amp with  $C_L$  makes ROC = 40dB/dec and the Circuit unstable

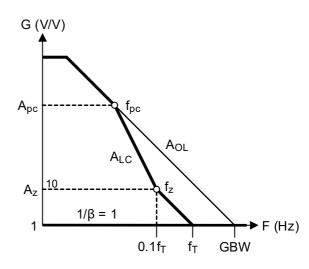

Figure 4. Inserting R<sub>S</sub> reduces ROC to 20dB/dec and restores Stability

To restore circuit stability, place a series resistor,  $R_S$ , between  $C_L$  and the op-amp output (Figure 4).  $R_S$  and  $C_L$  introduce a phase-lead at the zero frequency  $f_z = 1/(2\pi R_S C_L)$  that neutralizes the phase lag from  $R_O$  and  $C_L$ , resulting in the loaded but compensated open-loop gain,  $A_{LC}$  (Figure 4). As  $A_{LC}$  crosses the  $1/\beta$  line at an ROC of 20dB/decade, circuit stability has been restored.

Note: The use of  $R_S$  also reduces the pole frequency from  $f_{pu} = 1/(2\pi R_O C_L)$  to  $f_{pc} = 1/[2\pi (R_O + R_S) C_L]$ .

# 3.1 Determining the Value of R<sub>S</sub>

To find an equation for calculating R<sub>S</sub> the location of f<sub>7</sub> must be derived by completing the following steps.

- 1. Set the gain at  $f_Z$  to  $A_Z$  = 10. This places  $f_Z$  one decade below  $f_T$ , allowing the phase lead to fully develop and  $A_{LC}$  to achieve maximum phase margin.

- 2. Along the 40dB/dec slope, the ratio of pole-gain to zero-gain is:

(EQ. 1)

$$\frac{A_{pc}}{A_z} = \frac{f_z^2}{f_{pc}^2}$$

3. As  $f_{pc}$  lies on the op-amp's open-loop gain slope of constant gain-bandwidth, the pole-gain is:

$$A_{pc} = GBW/f_{pc}$$

4. Then, substituting all variables in Equation 1 with their pre-established values and time constants:

$$\frac{\text{GBW/f}_{pc}}{10} = \frac{1/(2\pi R_S C_L)^2}{1/[2\pi (R_O + R_S) C_L]^2}$$

5. Solve for R<sub>S</sub> and receive a quadratic equation, whose solution is:

(EQ. 2)

$$R_S \ge \frac{1 + \sqrt{1 + 0.8\pi C_L \times GBW \times R_O}}{0.4\pi C_L \times GBW}$$

# 4. Active Cap-Load Compensation

This compensation circuit adds dual feedback around  $R_S$ . The feedback path using  $R_F$  restores the DC accuracy that would be lost because of the voltage drop across  $R_S$ . The feedback path using  $C_F$  provides access to the op-amp output at high frequencies to act like passive cap-load compensation (Figure 5).

Figure 5. Phase Compensation with Dual Feedback Restores DC-Accuracy and Circuit Stability

Therefore,  $C_F$  and  $R_F$  operate as a frequency-dependent switch or high-pass that gradually directs feedback from the circuit output  $V_O$  to the op-amp output  $V_{OA}$ . As stability analysis focuses on  $A_{LC}$  phase margin at  $f_T$ ,  $C_L$  presents a short, allowing  $R_F$  to be grounded (Figure 6).

Figure 6. Making  $R_F \cdot C_F = 10 \cdot R_S \cdot C_L$  ensures Circuit Stability

As previously mentioned, the open-loop gain response A<sub>LC</sub> is the same as for passive compensation:

$$A_{LC} = A_{OL} \times \frac{1 + j\omega R_S C_L}{1 + j\omega (R_O + R_S) C_L} \text{ with a zero frequency at } f_{z(A_{LC})} = \frac{1}{2\pi R_S C_L}$$

Deriving the noise gain or 1/β response yields:

$$\frac{1}{\beta} = \frac{1 + j\omega R_F C_F}{j\omega R_F C_F} \text{with a zero frequency at } f_{Z(1/\beta)} = \frac{1}{2\pi R_F C_F}$$

For maximum phase margin of  $A_{LC}$  at  $f_T$ , the phase lead due to  $C_F$ - $R_F$  must be fully developed at  $f_{z(A_{LC})}$ , which requires that  $f_{z(1/\beta)} = 0.1 f_{z(A_{LC})}$ . Expressing this relation in terms of time constants gives:

(EQ. 3)

$$R_FC_F = 10 \times R_SC_L$$

## 4.1 Calculating Component Values

To design a stable active cap-load compensation, complete the following steps.

1. Calculate RS the same way as for passive compensation, using Equation 2:

$$R_S \ge \frac{1 + \sqrt{1 + 0.8\pi C_L \times GBW \times R_O}}{0.4\pi C_L \times GBW}$$

2. To minimize the loading effects of the feedback path, make

$$R_F \ge 100R_S$$

3. Solving Equation 3 for C<sub>F</sub>, calculate:

$$C_F = C_L \times \frac{10R_S}{R_F}$$

## 5. Conclusion

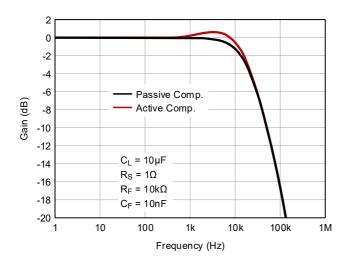

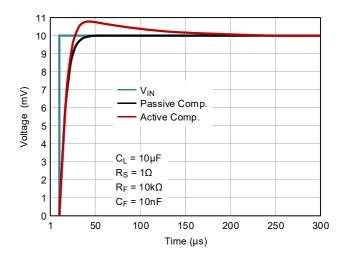

Both passive and active cap-load compensation circuits have the same -3dB signal bandwidth.

Passive cap-load compensation is simple in both design and implementation. It can achieve fast settling times while minimizing overshoot and generally remains stable with reasonable variation in the transient response over a wide range of capacitive loads.

Its main disadvantage is that the voltage drop across  $R_S$  is dependent on the output current, which can make this compensation impractical for precision applications.

Figure 7. Bandwidth and Overshoot Comparison

Active cap-load compensation solves the DC accuracy issue of passive compensation. However, its dual feedback must be aligned with the capacitive load and isolation resistor. This makes it less tolerant to changes in the output capacitance, allowing it to quickly become unstable. Thus, active cap-load compensation is best applied in situations where the output capacitance is known and does not vary significantly.

Also, this compensation technique has longer settling times and higher overshoot than passive compensation. While smaller C<sub>F</sub> values reduce settling time, they usually produce higher overshoot.

# 6. Revision History

| Revision | Date         | Description      |

|----------|--------------|------------------|

| 1.00     | May 19, 2025 | Initial release. |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.