RZ/G2L, RZ/G2LC, RZ/V2L, RZ/G2UL, RZ/Five, RZ/A3UL, RZ/G3S, and RZ/A3M PCB Design Checklist

R01AN6021EJ0210 Rev.2.10 Apr. 25, 2025

### Introduction

This document summarizes hardware design knowledge required to design PCBs with target devices, along with design examples and a design checklist. It also describes the restrictions and recommendations described in its hardware manuals, as well as includes some hints to reduce troubles in hardware development.

### **Target Device**

- RZ/G2L

- RZ/G2LC

- RZ/V2L

- RZ/G2UL

- RZ/Five

- RZ/A3UL

- RZ/G3S

- RZ/A3M

#### **NOTE**

The design of evaluation board kits might not meet items in the checklist due to internal evaluation and realizing multiplexed functions, however, we strongly recommend to design along with the checklist.

In figures in this document, No marks indicate prohibited items, and imarks indicate items to notice.

Please also refer to the following documents.

- User's Manual: Hardware

- Design Data of EV Kit

- Other Application Notes for Hardware Design

# **Table of Contents**

| 1. | . Reset                                 |                                                             |    |  |

|----|-----------------------------------------|-------------------------------------------------------------|----|--|

|    | 1.1                                     | Circuits for PRST# Input                                    | 6  |  |

|    | 1.2                                     | Note for the Reset Signal with Open-Drain                   | 12 |  |

|    | 1.3                                     | Reset Timing                                                | 13 |  |

|    | 1.4                                     | Oscillator Stabilization Time                               | 14 |  |

|    | 1.5                                     | Resetting Peripheral Devices                                | 15 |  |

|    | 1.6                                     | Mode Pins                                                   | 16 |  |

| 2. | CI                                      | lock                                                        | 17 |  |

|    | 2.1                                     | Input and Output Clock                                      | 17 |  |

|    | 2.2                                     | Accuracy and Deviation                                      | 18 |  |

|    | 2.3                                     | Crystal Oscillator Circuits                                 | 19 |  |

|    | 2.4                                     | Terminal Handling of External Clock Input                   | 21 |  |

|    | 2.5                                     | Oscillator Drive Strength                                   | 22 |  |

|    | 2.6                                     | Clock Input for Peripheral Devices                          | 23 |  |

|    | 2.7                                     | General Notes on the Clock Circuit and Wiring               | 24 |  |

| 3. | B. Power Supplies                       |                                                             | 25 |  |

|    | 3.1                                     | Capacity for MPU and Peripherals                            | 25 |  |

|    | 3.2                                     | Capacity for VDD                                            | 26 |  |

|    | 3.3                                     | Supply Voltage and Power Sequence                           | 27 |  |

|    | 3.4                                     | Noise Filter                                                | 28 |  |

|    | 3.5                                     | Impedance Design                                            | 29 |  |

|    | 3.6                                     | Bypass Capacitors                                           | 30 |  |

|    | 3.7                                     | 7 Selecting Ceramic Capacitors                              |    |  |

|    | 3.8                                     | Design of the Power Supply IC Circuit                       | 32 |  |

|    | 3.9                                     | Remote Sensing of the Output Voltage by the Power Supply IC |    |  |

|    | 3.10 Supplying Power through Connectors |                                                             |    |  |

|    | 3.11                                    | 1 SD                                                        | 35 |  |

|    |                                         | 3.11.1 Power Supply Circuit for the SD card Interface       | 35 |  |

|    |                                         | 3.11.2 Switching the IO Power Supply Voltage                | 36 |  |

| 4. | High-Speed Interfaces                   |                                                             | 37 |  |

|    | 4.1                                     | Other Guidelines and Documents                              | 37 |  |

|    | 4.2                                     | DDR                                                         | 38 |  |

|    |                                         | 4.2.1 Supported DRAM Interface                              | 38 |  |

|    |                                         | 4.2.2 PCB Verification Guide                                | 39 |  |

|    |                                         | 4.2.3 Model Number of a DRAM for Simulation                 | 39 |  |

|    |      | 4.2.4    | Topology for Connecting with the DRAM                 | 40 |

|----|------|----------|-------------------------------------------------------|----|

|    |      | 4.2.5    | DRAM Interface Circuits                               |    |

|    |      | 4.2.6    | VREF Circuit for DDR3L                                |    |

|    |      | 4.2.7    | VREF Circuit for DDR4                                 |    |

|    |      | 4.2.8    | ZQ Resistor (Value and Tolerance)                     | 44 |

|    |      | 4.2.9    | Pin Swapping for DDR3L                                |    |

|    |      | 4.2.10   | Pin Swapping for DDR4                                 | 47 |

|    |      | 4.2.11   | Pin Swapping for LPDDR4                               | 49 |

|    |      | 4.2.12   | Power-on Sequence for DDR3L                           | 50 |

|    |      | 4.2.13   | Power-on Sequence for DDR4                            | 50 |

|    |      | 4.2.14   | Power-on Sequence for LPDDR4                          | 50 |

|    |      | 4.2.15   | VREF, DDR_CALIBRATION, ZQ, CS, and CLK for A3M        | 51 |

|    | 4.3  | Resisto  | r and Capacitor                                       | 52 |

|    | 4.4  | Clock    |                                                       | 53 |

|    | 4.5  | PCIe     |                                                       | 54 |

|    |      | 4.5.1    | AC Coupling Capacitor                                 | 54 |

|    |      | 4.5.2    | Clock                                                 | 54 |

|    | 4.6  | Instruct | ons in schematic for PCB Layout                       | 55 |

|    | 4.7  |          |                                                       |    |

|    | 4.8  | Disturba | ance Noises and Static Electricity                    | 57 |

|    | 4.9  | USB      | ·                                                     | 58 |

|    |      | 4.9.1    | Overcurrent or VBUS Input                             | 58 |

|    |      | 4.9.2    | VBUS Enable                                           | 59 |

| 5. | 0    | thers    |                                                       | 60 |

|    | 5.1  | Unused   | Pins                                                  | 60 |

|    | 5.2  | NC pins  | ·                                                     | 61 |

|    | 5.3  | Counter  | measures against Overshoots and Undershoots           | 62 |

|    | 5.4  |          | hifting                                               |    |

|    | 5.5  |          | racteristics between MPU and Connected Devices        |    |

|    | 5.6  |          | age Level Restriction for the PVDD182533 Power Domain |    |

|    | 5.7  |          | between Pull-Up and Pull-Down                         |    |

|    | 5.8  |          | ely High-Speed Interfaces (about 10 to 100 MHz)       |    |

|    |      |          |                                                       |    |

|    | 5.9  |          |                                                       |    |

|    |      | •        | t Signals                                             |    |

|    | 5.11 |          |                                                       |    |

|    |      | 5.11.1   | Connection with eMMC                                  |    |

|    |      | 5.11.2   | eMMC Interface Circuit                                |    |

|    |      |          | emory Controller                                      |    |

|    | 5.13 | 3 SPI    |                                                       | 72 |

|    | 5.13.1     | SPI Multi I/O Interface                           | 72  |

|----|------------|---------------------------------------------------|-----|

|    | 5.13.2     | 2 eXpanded Serial Peripheral Interface (xSPI)     | 74  |

|    | 5.13.3     | 3 Master and Slave                                | 76  |

|    | 5.13.4     | Selection of QSPI flash memory                    | 77  |

|    | 5.14 SDHI  |                                                   | 78  |

|    | 5.14.1     | 1 CD and WP Signals                               | 78  |

|    | 5.14.2     | 2 SDHI Circuit                                    | 79  |

|    | 5.15 Conn  | ecting Ethernet PHY                               | 80  |

|    | 5.16 JTAG  | S                                                 | 81  |

|    | 5.16.1     | 1 Mode Setting                                    | 81  |

|    | 5.16.2     | 2 TRST# pin                                       | 82  |

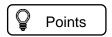

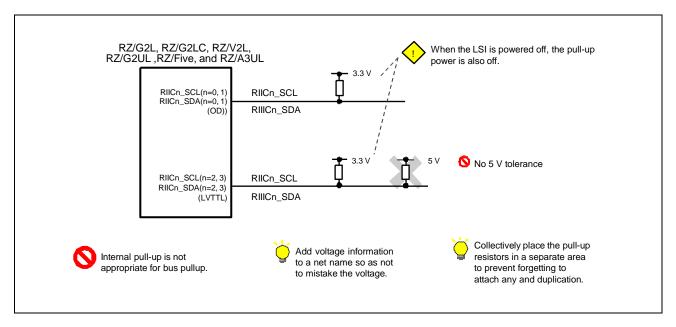

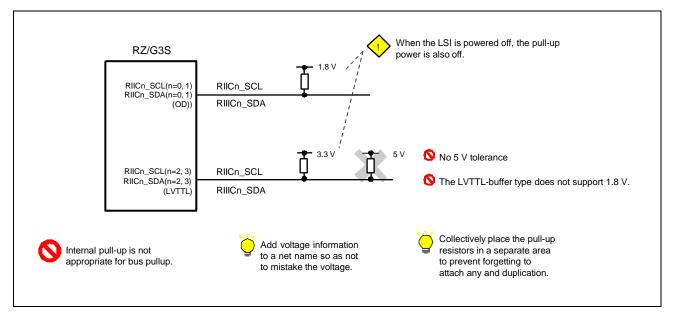

|    | 5.17 I2C   |                                                   | 83  |

|    | 5.17.1     | 1 IO Voltage and Buffer Type                      | 83  |

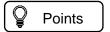

|    | 5.17.2     | 2 Slave Address                                   | 86  |

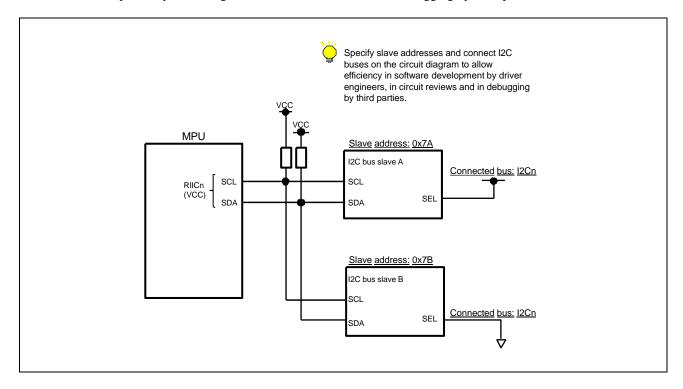

|    | 5.18 SCIF  |                                                   | 87  |

|    | 5.18.1     | 1 External Input Clock                            | 87  |

|    | 5.18.2     | 2 SCIF0 for Debug                                 | 88  |

|    | 5.19 Audio | )                                                 | 89  |

|    | 5.19.1     | Coupling Capacitors for Audio Output Circuits     | 89  |

|    | 5.20 Polar | ity of Electrolytic Capacitors                    | 90  |

|    | 5.21 Progr | ramming On-Board EEPROM                           | 91  |

|    | 5.22 Board | d to Board Connector                              | 92  |

|    | 5.23 Confi | rm Part Number of MPU                             | 93  |

|    | 5.24 Reco  | nfirm Operations of Re-used Circuits              | 94  |

|    | 5.25 Watc  | hdog Timer (WDT)                                  | 95  |

| 6. | PCB La     | ayout Design                                      | 96  |

|    | 6.1 Powe   | er Supply                                         | 96  |

|    | 6.1.1      | Target Impedance                                  | 96  |

|    | 6.1.2      | Trace Width                                       | 97  |

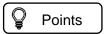

|    | 6.2 Expo   | sed Pad                                           | 99  |

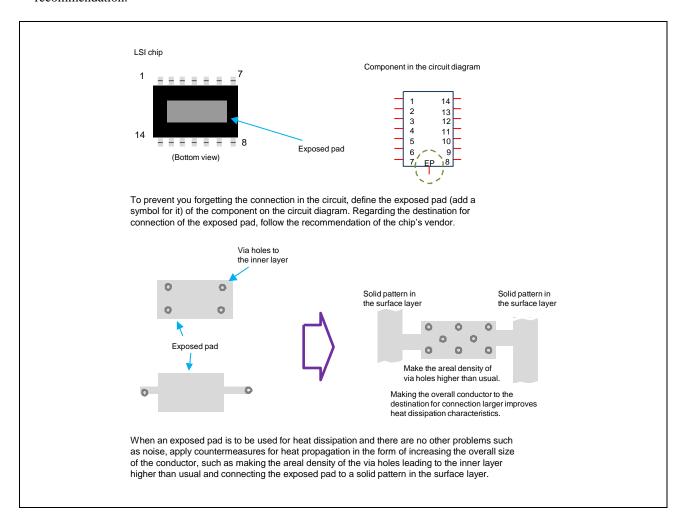

|    | 6.3 Digita | al and Analog Ground                              | 100 |

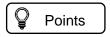

|    | 6.4 Grou   | nd Shields/Guards                                 | 102 |

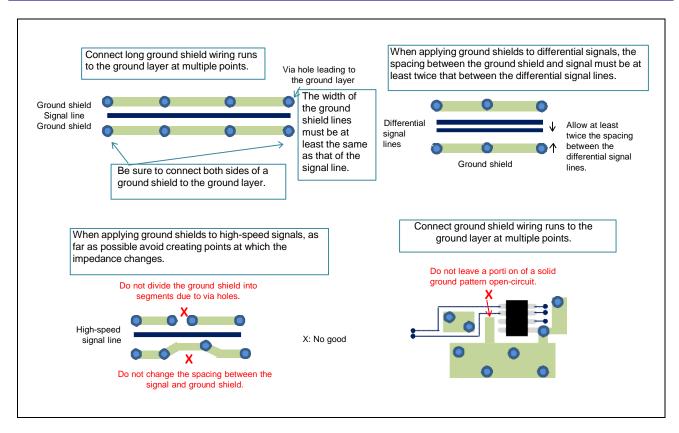

|    | 6.5 Retur  | rn Path                                           | 104 |

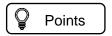

|    | 6.6 3-Ter  | minal Capacitor with "Non-feedthrough" Connection | 106 |

|    | 6.7 High-  | Speed Interfaces                                  | 107 |

|    | 6.7.1      | Differential Signals                              |     |

|    | 6.7.2      | Crosstalk                                         | 110 |

|    | 6.7.3      | Pads for Monitoring Signals                       | 112 |

|    | 6.8 Gene   | eral Notes                                        | 113 |

|    |            |                                                   |     |

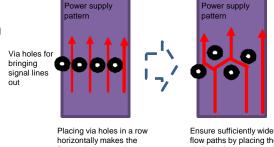

|    | .9 Countermeasures for Noise | 114 |

|----|------------------------------|-----|

| 7. | Check List                   | 115 |

| RE | /ISION HISTORY               | 126 |

### 1. Reset

### 1.1 Circuits for PRST# Input

ALL

• Check the IO voltage of the PRST#.

The PRST# is a reset input with Schmitt trigger, and it is on the 1.8V power domain only for RZ/G3S and the 3.3V power domain for others.

• Do not set PRST# high when the MPU is powered off.

High level input for the PRST# is not supported while the power supply is turned off.

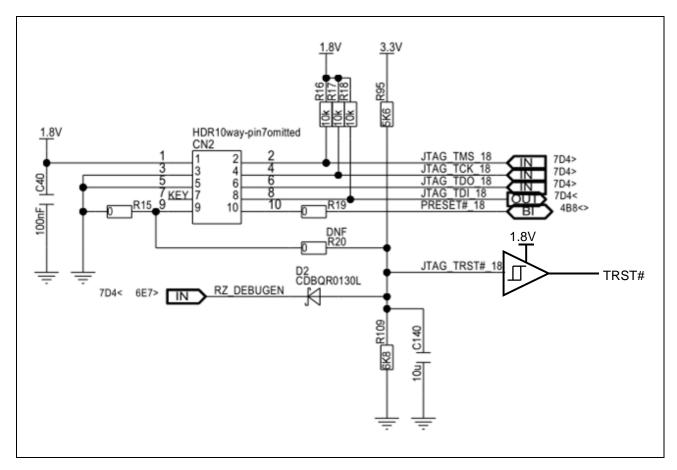

• Make sure that the connection to TRST# is OK.

The TRST# signal from a JTAG ICE should be considered in terms of its connection to the PRST# signal, and the voltages of each signal should be confirmed.

- Make sure the PRST# signal is pulled up.

- $\bullet$  We recommend that the pull-up resistor is no greater than  $10k\Omega$

The IO on the PRST# pin is Schmitt-triggered and does not have an internal pull-up; a signal generated by an open drain source must be input to PRST#.

• Also check the reset signals of peripheral devices.

Some peripheral devices may require a reset at the same time as the MPU reset. In such cases, make sure that there is no problem with the voltage of the reset signal of the peripheral device. Also, if an open drain is used to generate the PRST# signal, make sure that the waveform of the PRST# signal is stable.

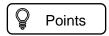

Figure 1.1(a) Example of the Configuration of PRST# for RZ/G2L and RZ/V2L EVKIT Discrete Edition

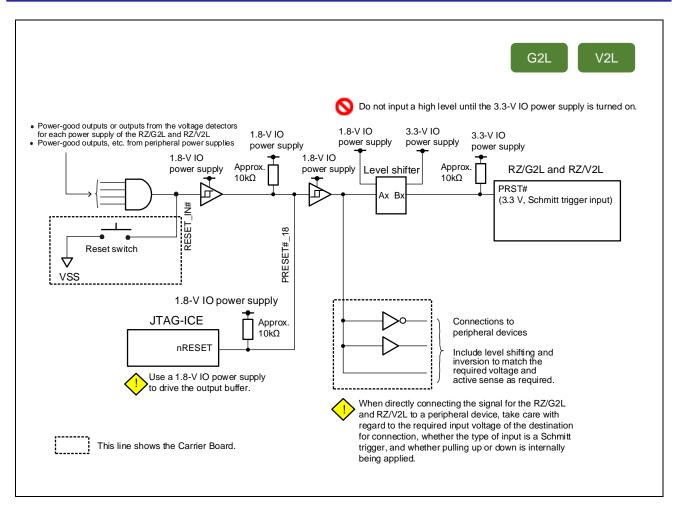

Figure 1.1(b) Example of the Configuration of PRST# for RZ/G2L, RZ/G2LC, and RZ/V2L EVKIT PMIC Edition

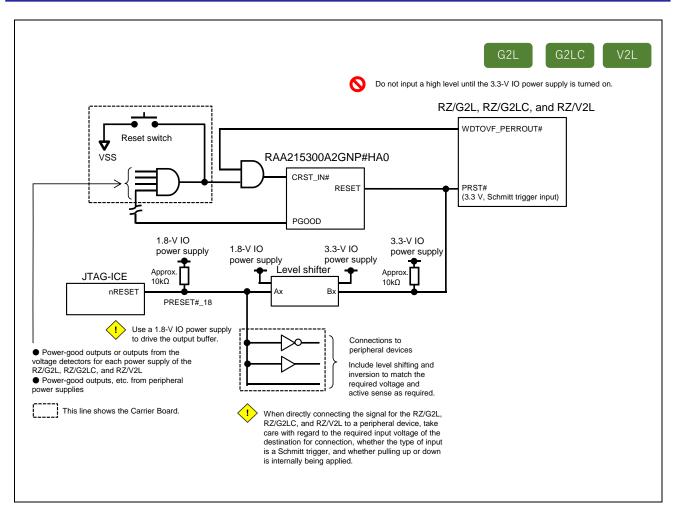

Figure 1.1(c) Example of the Configuration of PRST# for RZ/G2UL, RZ/Five, and RZ/A3UL EVKIT

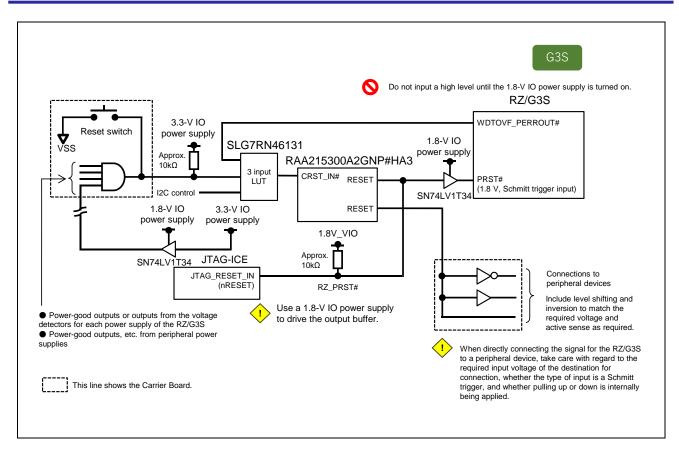

Figure 1.1(d) Example of the Configuration of PRST# for RZ/G3S EVKIT

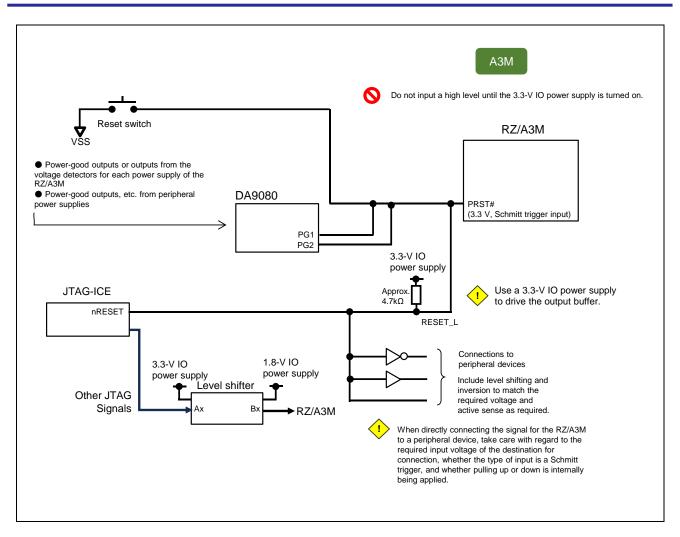

Figure 1.1(e) Example of the Configuration of PRST# for RZ/A3M EVKIT

## 1.2 Note for the Reset Signal with Open-Drain

ALL

When an open-drain output, wired OR, and voltage level shifter are used in the circuits for generating the reset signals, take care on the following points.

- Peripherals with a reset terminal with Schmitt trigger IO are recommended.

- Take care of the noise.

The effect of noise such as crosstalk is very likely to lead to the incorrect behavior of reset signals. Therefore, apply countermeasures for noise such as separating the reset signal from other signals and applying a grounded guard.

• Determine the pull-up resistor to account for stray capacitance.

The overall wiring length tends to be long because the reset signal branches to other devices and connectors at the edge of the board. As a result, the signal waveform is likely to be dulled by stray capacitance. Consider this when determining the value of the pull-up resistor to be used for the open-drain output.

• Note the pull-up/pulldown resistors scattered throughout the schematic.

If pull-up or pull-down resistors for the reset signal are scattered across multiple pages of the schematic, they may be overlooked and cause unintended operation. For schematic readability, it is recommended that pull-up and pull-down resistors be placed in a single location.

• To clarify the wait time for software initialization to start after reset release, it is recommended to take into account the slow rise of the reset signal.

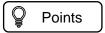

Figure 1.2 Note for the Reset Signal with Open-Drain

## 1.3 Reset Timing

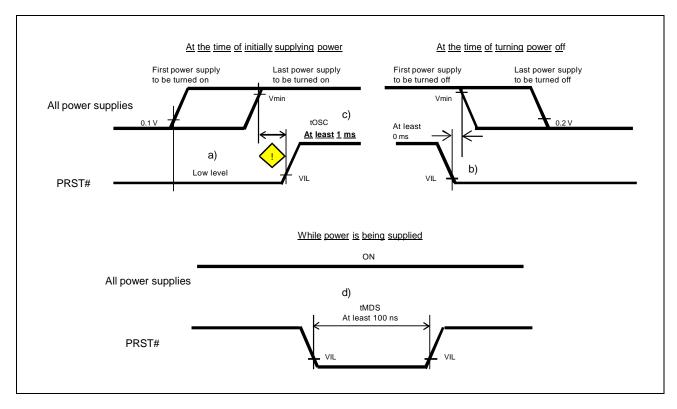

- Make sure the following constraints are met for the reset timing.

- a. During the power-on sequence, the PRST# signal should remain at the low level until all power supplies have been turned on.

- b. During the power-off sequence, the PRST# signal should be at the low level before any power supply is turned off

- c. During power-on sequence, the PRST# signal should be at the low level at least 1ms after the last power supply was turned on. Required 2ms for RZ/G3S.

- d. When using the PRST# signal to reset the target devices while power is being supplied, hold the signal low for at least 100 ns. RZ/G3S is 0 ms.

Figure 1.3 Timing of PRST# Input

### 1.4 Oscillator Stabilization Time

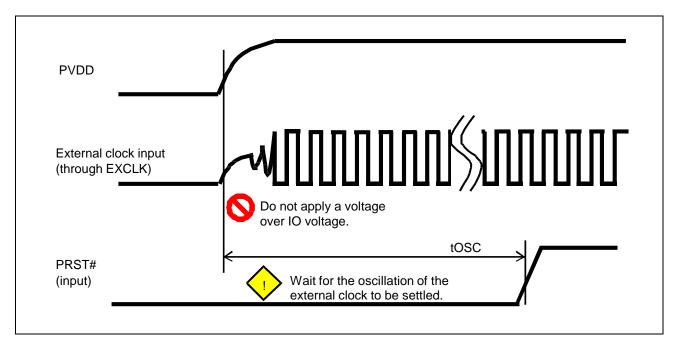

• When using an external clock through the EXCLK pin, de-assert the PRST# signal after the oscillation is settled. Please refer to the AC characteristics on the User's Manual.

Figure 1.4 Timing between External Clock Input (through EXCLK) and De-assertion of PRST#

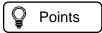

## 1.5 Resetting Peripheral Devices

- When using the main reset signals PRST# to reset a peripheral device, take care on the following points.

- Is power to the peripheral device turned on?

- Are you observing the correct reset sequence for the peripheral device?

- Is the active sense of the reset signal for peripheral devices correct?

- When multiple peripheral devices are connected, are you sure that pull-up or pull-down resistors within the individual devices will not cause the voltage of the reset signal to be at an intermediate level?

- Is the driving ability of the reset signals sufficient?

- When the target devices have reset pins for exclusive use with specific modules such as the DDR\_RESET# pin for DRAM and the QSPI\_RESET# pin for the SPI Multi I/O interface the SD0\_RST# pin for the SD/MMC host interface, use these pins instead of the PRST# pin.

Figure 1.5 Resetting Peripheral Devices

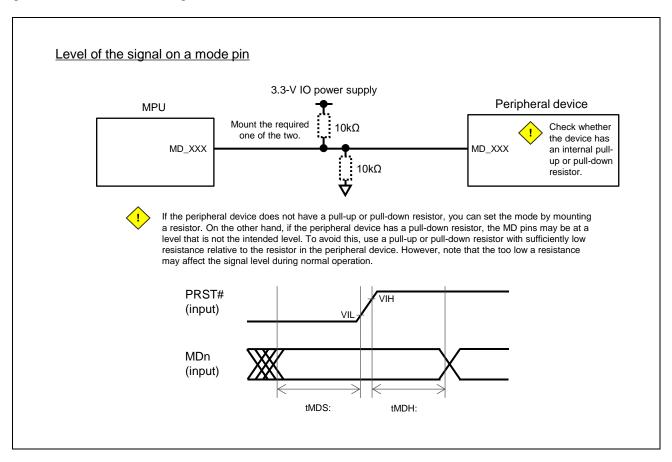

### 1.6 Mode Pins

The mode pins (MDn) are used to set the initial operating mode. They are implemented with pull-up or pull-down resistors and are captured only one time after the PRST# is released, not after a software reset. The level of the mode pins should be held for a time specified as tMDH.

Figure 1.6 Handling the Mode Pins

### 2. Clock

## 2.1 Input and Output Clock

ALL

• The voltage of the clock should conform to the voltage of its power domain.

For example of the RZ/G2L, the system clock (EXCLK or XIN) and AUDIO\_CLKn are in the 3.3-V IO power domain, but CSI\_CLKN/P and DSI\_CLKN/P are in the 1.8-V IO power domain. Using a clock input with an incorrect voltage may damage the MPU. Please refer to the "Power" column of the pin function list of the target devices.

- The spread spectrum clock generator (SSCG) cannot be used as the input clock unless specifically stated otherwise in the hardware manual.

- Make sure that the input clock is accurate enough.

The system clock is frequency-multiplied to obtain each kind of clock. Deviation of the oscillation frequency (center frequency) of the input clock (the system clock) affects the center frequency and deviation of the DDR\_CK.

• Make sure that whether the output clock of the MPU satisfies with the requirement of the input clock of the external peripheral devices. Refer to the CPG section of the hardware manual.

## 2.2 Accuracy and Deviation

- In general, the specifications of crystal resonators are based on the temperature characteristics, the degree to which oscillation may deviate from the oscillation frequency (center frequency), and so on.

- As with crystal resonators, the specifications of crystal oscillators and clock synthesizers are also based on the degree to which oscillation may deviate from the oscillation frequency (center frequency).

- When using the clock generated inside the target devices as the clock source of external peripheral devices or modules, you should be more careful for the deviation of the input clock of the MPU.

- The system clock provides the source of each kind of clock through frequency-multiplication. Any deviation in the frequency of the input clock (the system clock) thus produces deviation in the frequency of clock after multiplication.

- To design a system such that the maximum frequency of the DDR\_CK does not exceed the maximum frequency specified for the DRAM, you must select the center frequency of the system clock input in consideration of possible deviation.

- When using MIPI DSI, or USB, the jitter of the external clock should be less than the values in **Table 2.1**. On the other hand, when not using any of MIPI DSI, and USB, the jitter of the external clock should be less than 80 ps.

- We recommend using clocks with less than 50 ppm frequency deviation. Since the RZ/A3M has no RGMII interface, less than 100 ppm is acceptable.

Table 2.1 Maximum Value of EXCLK Jitter

| High-Speed Signal Interfaces | Maximum Value of External Clock Jitter (p-p) [ps] |  |  |

|------------------------------|---------------------------------------------------|--|--|

| MIPI DSI, USB2               | 40                                                |  |  |

| Others                       | 80                                                |  |  |

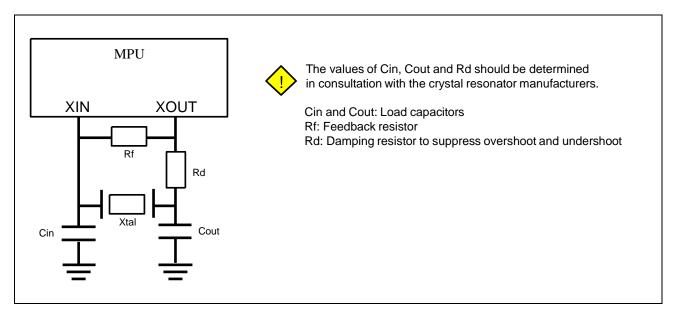

## 2.3 Crystal Oscillator Circuits

- For the load capacitance, damping resistance and feedback resistance of the crystal oscillator circuit, determine appropriate values based on the evaluation of oscillation by the selected crystal resonator manufacturer.

- For the provisional value of the load capacitance before evaluating the oscillation, select a value that meets the characteristics of the resonator.

- A feedback resistor can be removed, but it depends on the characteristics of a crystal oscillator and circuit configuration and layout. Please make your decision based on the oscillation evaluation.

- In evaluating the oscillation, adding a feedback resistance is relatively easy, but adding a damping resistance is difficult. Select the value of the damping resistor in consideration of adjustment in evaluating the oscillation.

- Observe the following notes for the crystal oscillator circuit, even though they are not stated in the hardware manual:

- Bypass Capacitors

Insert laminated ceramic capacitors as bypass capacitors for each VSS/VCC pair. Mount the bypass capacitor near

the power supply pins of the LSI. Use components with a frequency characteristic suitable for the operating

frequency of the LSI, as well as a suitable capacitance value.

- Notes on Using a PLL Oscillation Circuit Keep the wiring from the PLL VDD and VSS connection pattern to the power supply pins short, and make the pattern width large, to minimize the inductance component. The analog power supply system of the PLL circuits is sensitive to noise. Therefore, system malfunction may occur by the intervention with another power supply. Do not supply the analog power supply with the same resource as the digital power supply of VDD and VCC.

- When Using an External Crystal Resonator

Place the crystal resonator, capacitors Cin and Cout, and damping resistor Rd as close to the XIN and XOUT pins as possible. To minimize induction and thus obtain oscillation at the correct frequency, the capacitors to be attached to the resonator must be grounded to the same ground. Do not bring wiring patterns close to these components.

- Observe the following other notes for the crystal oscillator circuit:

- Do not cross the circuit with other signal lines.

- Keep the circuit away from lines that carry large currents.

- Do not ground the circuit to ground patterns that carry large currents.

- Do not bring signals out from the oscillator circuit.

- The result of our crystal marching evaluation is shown below as a reference example. In our case, a feedback resistance is implemented after evaluation. Please check the specification of the crystal oscillator to be used, and implement the appropriate load capacitance, damping resistor and feedback resistor.

Figure 2.1 Crystal Oscillator Circuit on the EVK

Table 2.2 Characteristics by Recommended Constants (CL = 8 pF)

| MPU            | Xtal            | Rf  | Rd | Cin  | Cout |

|----------------|-----------------|-----|----|------|------|

| G2L, G2LC, V2L | CX1612DB 24 MHz | 1ΜΩ | 0Ω | 6 pF | 6 pF |

| G3S            | CX2016SA 24 MHz | DNF | 0Ω | 6 pF | 6 pF |

## 2.4 Terminal Handling of External Clock Input

- The MPUs have the XIN and EXCLK pins for crystal clock input and external clock input respectively. Only RZ/G3S has the XIN only for common clock input.

- Check the way to connect a clock source is correct.

- Check the terminal treatments for selecting a clock source, either a crystal resonator or an external clock. Some MPUs require a mode pin setting.

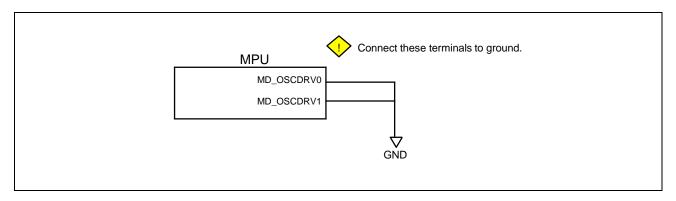

# 2.5 Oscillator Drive Strength

The MD\_OSCDRV pins are for setting the drive strength of crystal oscillators; however, only one setting is supported. Make sure that these pins are connected to ground.

Figure 2.2 Handling of the MD\_OSCDRV Pins

## 2.6 Clock Input for Peripheral Devices

- It is also necessary to pay attention to the clock input and clock oscillator circuit of peripheral devices. Read the data sheets and manuals of the individual peripheral devices carefully to avoid improper design.

- If you intend to use the output clock of the MPU as the input clock for a peripheral device, pay attention to the voltage of the clock output (the power domain to which the clock pin belongs and the interface level), and the clock frequency and accuracy.

- Please refer to the datasheet of the peripheral devices to be used.

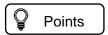

## 2.7 General Notes on the Clock Circuit and Wiring

- Pay attention to the following general notes when designing the clock input and clock output circuits. In addition, important points to be considered in PCB pattern design, such as the GND shield, are helpful in circuit diagram review and evaluation after the board is completed. State the important points as notes on the circuit diagram as far as possible.

- Properly reduce the load on the clock line to prevent malfunctions due to rounding of the clock signals on rising or falling edges. When the load is too large, take measures such as inserting a clock buffer.

- Avoid unnecessary branches and stubs as much as possible to avoid degradation of the signal quality caused by reflection. Use continuous patterns for branching as much as possible. When the wiring requires a T branch, take measures such as inserting a clock buffer.

- When inserting a clock buffer, be sure to consider the effect of clock delay. When delay is a problem, take

measures such as using a zero-delay buffer.

- Prepare circuits and pads in consideration of adjustment of the clock quality after the board is completed.

- Insert a damping resistor such that the resistor is near to the outputting terminal of the clock signal

- Placing a termination circuit such as a Thevenin termination near to the receiving terminal of the clock signal

- Use routes that minimize variations in characteristic impedance. Measures for this include keeping routes in the same PCB wiring layer and minimizing the use of via holes in clock wiring.

- Prevent the wiring for the clock and other signals from running side by side to avoid crosstalk noise and take measures such as applying a ground shield where appropriate.

- Consider the layout in terms of avoiding excessive noise from switched-mode power circuits and so on.

- In the case of circuits for selecting from among two or more clock signals, use chip jumper blocks with  $0\Omega$  resistors and use a pattern that minimizes the number of stubs.

Figure 2.3 General Notes on the Clock Circuit and Wiring

## 3. Power Supplies

## 3.1 Capacity for MPU and Peripherals

- In general, the system with the MPU including lots of peripherals such as SD cards, USB, memory devices like DRAMs, and communications devices, etc., requires a wide variety of power supplies. Then its power system is likely to be complex.

- The logic power supply has to be able to provide particularly large currents, so its capacity to supply power should be designed with a margin that allows for increases above the estimate of current drawn.

- For a power supply that is to be the source of multiple power supply voltages, take measures in consideration of the efficiency of each power supply IC, such as stepping down voltages in two stages.

- In order to "visualize" the possibility of power capacity being insufficient, we recommend that you create a calculation sheet, such as a power tree.

- Please refer to the datasheet for the electrical characteristics of the power supply IC and peripheral devices to be used.

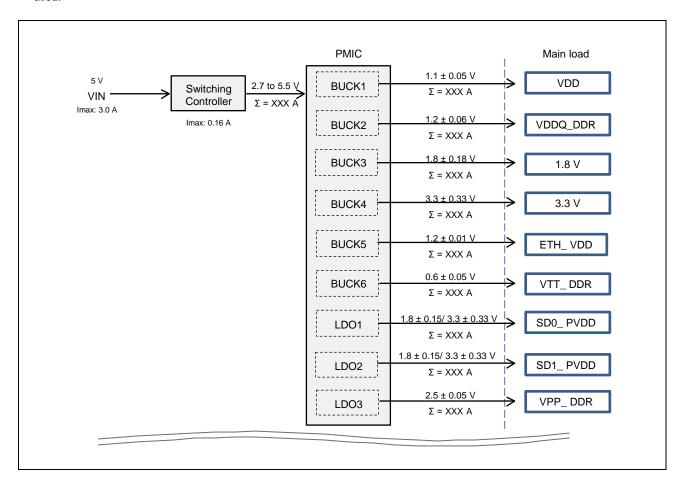

Figure 3.1 Example of a Power Tree

## 3.2 Capacity for VDD

- When selecting a power supply IC for the logic power supply, make sure that its specifications satisfy the requirement of all the power supply of the MPU, where the specification includes such as the load regulation and load response. For example, the load regulation ability for the power supply IC should satisfy the VDD specification of the MPU.

- Simply calculating, on a desk, the maximum current drawn from the electrical characteristics, and designing the power supply capacity with a margin based on the results of calculation is desirable. However, designing a power supply that allows a margin of two or three times for the maximum current is not easy without significantly increasing costs. The following methods can be used to reduce the cost of the power supply by estimating the details of the standard power consumption.

- Setting the power supply voltage to TYP +  $\alpha$  (allowing for the accuracy of the power supply voltage) to be set for the power supply IC, rather than to the maximum value in the specification

- Excluding (from the estimate) modules that are not to be used among the internal modules

- Using duty ratios based on anticipated use cases rather than current drawn during full operation

- Implementing a margin based on addition rather than multiplication (for example, using +1 A or 2 A instead of two to three times the maximum value)

- If the margin is reduced, the instantaneous peak of the current drawn might exceed the power supply capacity. The following methods can be used to compensate for this.

- Using several capacitors with large capacitances, such as 10 to 100 μF, to absorb sudden increases in load current

- Increasing the response of the power supply IC, by increasing the switching frequency of the power supply IC by a value of the order of several MHz, and implementing a multi-channel power supply IC configuration

- Limiting the overcurrent protection of the power supply IC to the original maximum current + α to prevent unexpected shutdowns

- Finally, if you have not secured adequate margins on your desk, perform sufficient evaluation with the actual machine and software by increasing the number of boards to be evaluated and verify whether power supply integrity is maintained. In addition, you must consider advance measures for shortages of power capacity.

- Please refer to the datasheet of the power supply IC to be used.

## 3.3 Supply Voltage and Power Sequence

- Check that the power up and down sequence described in the electrical characteristics of the user's manual.

- We strongly recommend drawing a timing chart of the power up and down sequences of all the power supplies including the reset system of the MPU and peripheral devices.

- Regarding the sequence of switching power off, the before-and-after relations of items in the sequence might change depending on whether a discharge circuit is present. Therefore, also consider the effect of a discharge circuit on the sequence.

- Make sure that the rising or falling of the supply voltage is not excessively long. Although the slope (mV/s) of the rising or falling of the power supply voltages is not specified, a monotonic increase or decrease is assumed.

- In the power supply sequence, the condition for the next power-on is that the power supply voltage must have dropped below the rated value when the power supply was turned off last time. Therefore, it should be noted that turning the power supply back on when the power supply voltage has not sufficiently dropped due to insufficient discharge is strictly a violation of the rated value.

- For the evaluation phase, we recommend configuring the initial hardware to allow adjustment for the defect in the power supply sequence. For example, use a PMIC and a MCU which change the control program of the PMIC, and prepare a pattern for a discharge circuit.

- Note the voltage tolerance of the signal pins with pull-up. Not only pins on the MPU, but also the ones on peripheral devices.

### 3.4 Noise Filter

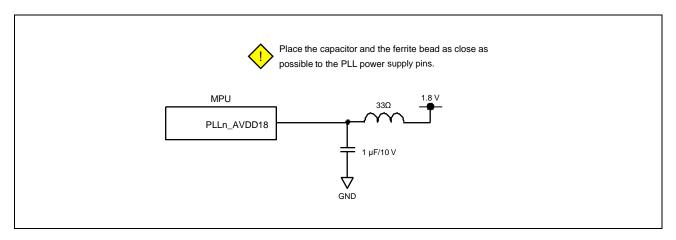

- Make sure to place noise filters for dedicated power rails such as the PLL. It is not recommended merging multiple power rails and filtering with one filter. Refer to the guidelines for each interface.

- The noise filter circuit of the PLL power supply on the EVK has a proven track record, so we recommend reusing the filter circuit.

Figure 3.2 Example of the Filter Circuit for the PLL Power Supply

## 3.5 Impedance Design

Power supplies that require high current, such as VDD, which is a logic power supply, and power supplies for noise-sensitive high-speed signal interfaces such as DDR require a PCB design that takes signal impedance into account.

We provide the following guidelines. Please refer to them. We strongly recommend that the target value be in accordance with these guidelines to reduce the risk of malfunction.

#### [VDD]

- PCB verification guide for Core VDD

### [DDR]

- PCB verification guide for DDR4/DDR3L

- PCB design guideline for DDR4/DDR3L

- PCB verification guide for LPDDR4/DDR4 (for RZ/G3S)

- PCB design guideline for LPDDR4/DDR4 (for RZ/G3S)

[High speed signal interface]

- PCB design guidelines for High-Speed Signal Interfaces

## 3.6 Bypass Capacitors

- There are no recommended capacities for bypass capacitors for the general-purpose digital IO power supplies of the target devices; however, use the evaluation board kit as a reference to determine the appropriate number and capacity of bypass capacitors.

- It is desirable to use a single ceramic 0.1-μF capacitor per pin of the IO power supply as a bypass capacitor. However, arrange the appropriate number of capacitors in consideration of the signal operating frequencies, the number of operations that will simultaneously be in progress, and the priority of other power bypass capacitors and filter circuits.

- If many signals are operating simultaneously, place a capacitor with a relatively large value of about 10  $\mu$ F at the end of the PCB IO power supply pattern.

- Confirm that the bypass capacitors for peripheral devices are appropriate, as well as the MPU. The recommended

capacities and PCB wiring patterns might be stated in the provided data sheets and technical documents of some

devices.

- Coordinate with the PCB pattern designer with regard to obtaining the best implementation of bypass capacitors, such as their placement near the target power supply pins and the capacitance values, by stating them in notes. For example, bypass capacitors for the BGA parts should be  $0.1~\mu F$  or less when located within the area on the other side of the board under the LSI, and at least  $1~\mu F$  when not located within the area on the other side of the board under the LSI.

- Please refer to the datasheet of the peripheral devices to be used.

## 3.7 Selecting Ceramic Capacitors

- When a multilayer ceramic capacitor is used as a bypass capacitor, the effective capacitance decreases depending on the DC bias characteristics and temperature characteristics.

- For details, check the characteristics provided by the manufacturer of a capacitor. However, the trends are as follows:

- The rate of decrease of the effective capacitance depends on the dielectric of the capacitor in use.

- The effective capacitance tends to decrease with the working voltage margin for withstand voltage.

- For capacitors with relatively high capacitance (10  $\mu$ F or higher), the effective capacitance decreases significantly with the body size.

- Note that when a capacitor with a large capacitance is used to support sudden changes in the load current, the desired effect might not be fully obtained due to a decrease in the effective capacitance.

- Make sure that the withstand voltage of the capacitor is at least three times the working voltage.

- If the decrease in the effective capacitance is a problem, also consider the capacitor characteristics: F, X5R (= the dielectric in use).

- When you select a capacitor with a small body, pay attention to the decrease in the effective capacitance. In terms of the effective capacitance, the effective capacitance of two small capacitors can correspond to that of a single larger capacitor.

- Please refer to the datasheet for the electrical characteristics of the multilayer ceramic capacitor to be used.

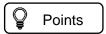

## 3.8 Design of the Power Supply IC Circuit

- The datasheets and technical documents for power supply ICs usually cover the reference circuits useful for configuring power supply circuits.

- Especially for switching regulators, the power supply quality might be significantly degraded depending on the circuit constants, or oscillation might occur. Therefore, the manufacturer and model number of the components used in the provided reference circuits are amply stated in many cases.

- Verifying the selection of specific components and the margins (for phase and gain) by using a simulation tool might be possible.

- When you design power supply circuits, use the technical information and reference circuits provided by the power supply IC manufacturers to make sure that the recommended circuits and constants are observed.

- The recommended designs for PCB wiring patterns and heat dissipation might also be stated, follow the recommendations.

- Carefully confirm the specifications of the coils, FETs, diodes, and other components that need to be selected

according to the current drawn in the actual use cases so that they do not violate the ratings. We also recommend

writing comments regarding the confirmed characteristics on the circuit diagram to help in component selection at

design reviews and in response to changes of specifications.

- Pay attention to the allowable losses (W) when inserting a shunt resistor into the power supply line for current measurement.

- Please refer to the datasheet of the power supply IC or peripheral device to be used for the electrical characteristics.

- Please refer to the datasheet for the electrical characteristics of the components used in power supply circuits and power supply IC to be used.

Figure 3.3 Example of Stating the Characteristics of Peripheral Power Supply Components

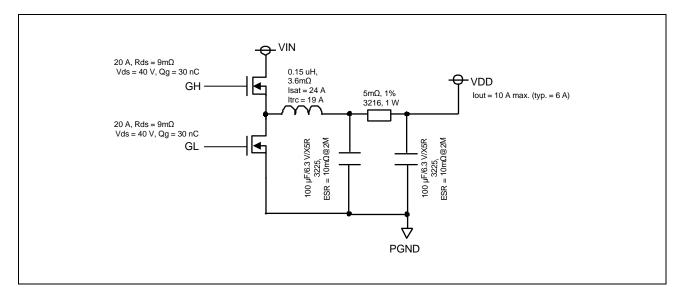

## 3.9 Remote Sensing of the Output Voltage by the Power Supply IC

ALL

Recently, current for the logic power supply has increased and the power supply voltage has gotten lower. So the power supply ICs that have a function sensing the output voltage to improve the quality of a power supply have been appearing. The quality of supplying power can be maintained by placing a remote sensing pin near the load (the LSI) and canceling out IR drops in the power supply line. We provide some general notes here.

- Sense the voltage at the point as close to the power supplies as possible. Sensing the voltage at the pin of the power supply on the MPU is preferable; however, this is often difficult.

- As with other noise-sensitive signals, take countermeasures to avoid noise, such as avoiding parallel runs of remote sensing and other signal wiring, and using ground shields.

- If a paired GND signal is provided, wire the GND signal and the remote sensing signal in a pair, and take the above precautions against noise as well.

Figure 3.4 Remote Sensing Input of a Power Supply IC

## 3.10 Supplying Power through Connectors

- When supplying power through a connector, be sure to provide sufficient power supply pins and GND pins for the maximum current value.

- Calculate the amount of current per pin from the allowable current and contact resistance of the connector pin.

- According to the amount of current near the connector, place a capacitor with a relatively large capacitance and

generally consider the design in terms of making sure that changes in the power supply voltage due to changes in the

current drawn will not become a problem.

- Please refer to the datasheet of the connectors to be used.

### 3.11 SD

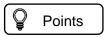

### 3.11.1 Power Supply Circuit for the SD card Interface

- When power is applied to an SD card, the inrush current may place a heavy load on the source power supply and

make the system unstable.

- Depending on the card in use, the current may have large fluctuations. Determine the capacitance of a bypass capacitor for the card power supply based on actual evaluation.

- If the inrush current when the power is turned on is excessively large, you can reduce it by using a high-side switch with a soft start function.

- If the bypass capacitor placed adjacent to the SD card and SD card power connector needs to be discharged quickly when power to the SD card is switched off due to removal of the card, use a high-side switch with a discharge function. If quickly discharging the capacitor is not necessary, discharge it through a resistor with a value of about  $1k\Omega$ .

- Please refer to the datasheet of the peripheral devices to be used.

Figure 3.5 Example of a Power Supply Configuration for an SD Card Slot

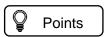

### 3.11.2 Switching the IO Power Supply Voltage

The MPU supports the 1.8 V and 3.3 V IO power supply voltage for SDHI.

- When dynamically switching the IO power supply voltage, make sure that the voltage does not exceed the specifications.

- In particular, when using a two-input high-side switch, be careful not to have a guard band that prevents the switches from being turned on at the same time during switching.

Figure 3.6 Switching the IO Power Supply Voltage of the SDHI

# 4. High-Speed Interfaces

## 4.1 Other Guidelines and Documents

We are providing the design guidelines for high-speed signal interfaces except for DDR interface. Be sure to follow the guidelines to verify the design.

Table 4.1 Guidelines Related to the PCB Design of High-Speed Serial Interfaces

| Guideline/External Guideline Documentation Referred to by the Renesas Guidelines                                                                                                                             |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <ul> <li>PCB design guidelines for High Speed Signal Interfaces</li> <li>High Speed USB Platform Design Guidelines Rev1.0<br/>Download from https://www.usb.org/</li> </ul>                                  |  |  |

| PCB design guidelines for High Speed Signal Interfaces                                                                                                                                                       |  |  |

| PCB design guidelines for High Speed Signal Interfaces                                                                                                                                                       |  |  |

| <ul> <li>PCB design guidelines for High Speed Signal Interfaces</li> <li>Board Design Guidelines for PCI Express<sup>TM</sup> Architecture         Download from https://members.pcisig.com/     </li> </ul> |  |  |

|                                                                                                                                                                                                              |  |  |

### 4.2 DDR

This chapter describes the points to note regarding DDR design. For detailed design methods, please refer to the following guidelines.

### **Reference Documents:**

- PCB design guideline for DDR4/DDR3L

- PCB design guideline for LPDDR4/DDR4

- PCB verification guide for DDR4/DDR3L

- PCB verification guide for LPDDR4/DDR4

- DDR board config structure generation tools for individual target devices

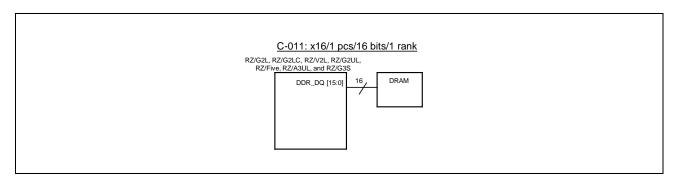

### 4.2.1 Supported DRAM Interface

ALL

The following tables show the DRAM interfaces supported by the target MPU.

Table 4.2 Supported DRAM

| MPU     | Туре   | Maximum Memory Size | Speed (Mbps) | Maximum Number of Ranks |

|---------|--------|---------------------|--------------|-------------------------|

| RZ/G2L  | DDR4   | 4 GB                | 1333 to 1600 | 2                       |

| RZ/G2LC | DDR3L  |                     | 800 to 1333  |                         |

| RZ/V2L  |        |                     |              |                         |

| RZ/G2UL |        |                     |              |                         |

| RZ/Five |        |                     |              |                         |

| RZ/A3UL |        |                     |              |                         |

| RZ/G3S  | LPDDR4 | 1 GB                | 1600         | 2                       |

|         | DDR4   | 4 GB                |              |                         |

| RZ/A3M  | DDR3L  | 128 MB (internal)   | 1600         | 1                       |

#### 4.2.2 PCB Verification Guide

The target devices have guidelines for performing SI verification, timing verification, and PI verification for DDR circuit and pattern design. The PCB design guidelines describe design examples of evaluation board kits.

Table 4.3 PCB Verification Guidelines for DRAM Interface Design

| MPU                                                | Guideline                                                  |  |

|----------------------------------------------------|------------------------------------------------------------|--|

| RZ/G2L, RZ/G2LC, RZ/V2L, RZ/G2UL, RZ/Five, RZ/A3UL | PCB verification guide for DDR4/DDR3L                      |  |

|                                                    | <ul> <li>PCB design guideline for DDR4/DDR3L</li> </ul>    |  |

| RZ/G3S                                             | <ul> <li>PCB verification guide for LPDDR4/DDR4</li> </ul> |  |

|                                                    | <ul> <li>PCB design guideline for LPDDR4/DDR4</li> </ul>   |  |

#### 4.2.3 Model Number of a DRAM for Simulation

• Make sure the DRAM model number is correct.

Please make sure that the model number of the DRAM you are installing matches the model number of the DRAM you are using as a model in the pre-design simulation. If the model numbers do not match, the DRAM may not operate properly.

When installing multiple types of DRAMs with different capacities or from different manufacturers on the same PCB, please verify by simulation with all model numbers of DRAMs to be used according to the PCB verification guide. In addition, due to shrinking of silicon dies and changes in internal structure, model parameters may differ if the model number is different even for DRAMs of the same capacity from the same vendor. There is a risk in judging that there is no problem only by observing the waveform on the current PCB. Be sure to obtain a new model from the DRAM vendor and check the compatibility according to the PCB verification guide.

### 4.2.4 Topology for Connecting with the DRAM

• Make sure the topology you are using is correct.

The command and address connection between the MPU and the DRAM is only supported point-to-point on our reference board. It is shown in the figure below.

If you design with a different topology than our reference board, please refer to the PCB verification guide and run the simulation yourself. Even if you design with the same topology as our reference board, we strongly recommend that you run the simulation because the PCB structure, materials, and target DRAM are not exactly the same.

Figure 4.1 Topology Example of RZ/G2L, RZ/G2UL, RZ/V2L, RZ/G2UL, RZ/Five, RZ/A3UZ, and RZ/G3S

#### 4.2.5 DRAM Interface Circuits

• Make sure the DRAM interface circuit constants are correct.

The DRAM interface circuit constants are listed in our PCB verification guide, so please refer to the latest guidelines to make sure the circuit constants are correct. The following is a general guideline for the example constants, but please note that the corrective action may differ depending on the board.

#### **Constant examples**

- Differential signal (CLK, DQS) termination handling

- Address/command signal termination handling (Rs resistor)

- Address/command signal VTT termination handling

- RESET signal termination handling (Rs resistor, pull-up resistor)

- VREF generation circuit

- ZQ pin handling

and so on

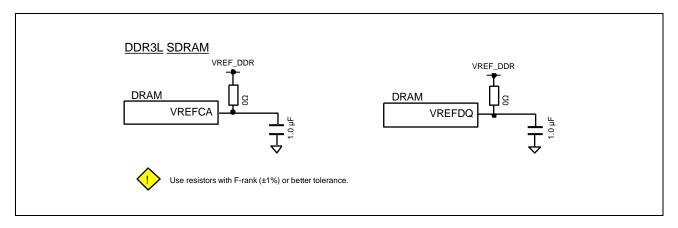

#### 4.2.6 VREF Circuit for DDR3L

You should refer to the datasheet of the DRAM or contact its vendor for the appropriate VREF circuit for the DDR3L SDRAM side; however, we describe an example of the implementation for the evaluation board kits.

The VREF implementation has two ways, dividing resistors or dedicated power supply. The later way is implemented on our evaluation board kits. A 1.0- $\mu$ F capacitors connected between the power supply and GND for stable voltage as shown in the following figure.

Figure 4.2 VREF Circuit for DDR3L

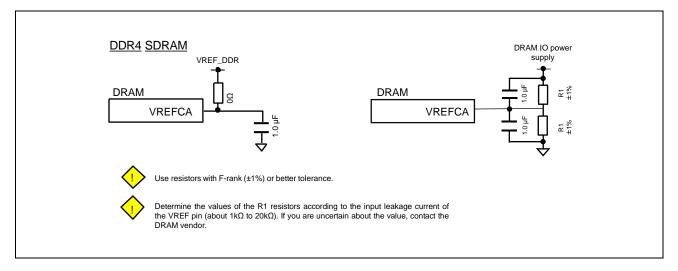

#### 4.2.7 VREF Circuit for DDR4

• For the VREF circuit on the DDR4 SDRAM side, contact the DRAM vendor and use an appropriate circuit configuration. On the evaluation board kits for the target devices except for G3S, each VREF are generated by the dedicated power supply, with 1.0-μF capacitors connected between the power supply and GND. For the evaluation board kit for G3S, each VREF are generated by resistor dividers with 1.0-μF capacitors connected in parallel between the power supply and GND for stabilization.

#### VREF generation by resistive division

- To generate VREF input from the VDD/GND pin nearest to each VREF input pin, the VREF voltages can be generated by using the VDD/GND in the presence of noise. The VREF generated by a VREF power supply IC, etc. near the DRAM power supply may be inferior in precision to VREF independently generated by resistive division in terms of the reference VDD/GND being near a DRAM power supply IC and at a distance from each VREF input pin and of the effect of the application of noise to the VREF wiring.

- The VREF generation circuit must be placed as close as possible to the DRAM VREF pin.

- Input leakage current on the VREF pin leads to a voltage shift that depends on the dividing resistor values.

- Current flows through the resistor during backup.

Figure 4.3 VREF Circuit for DDR4

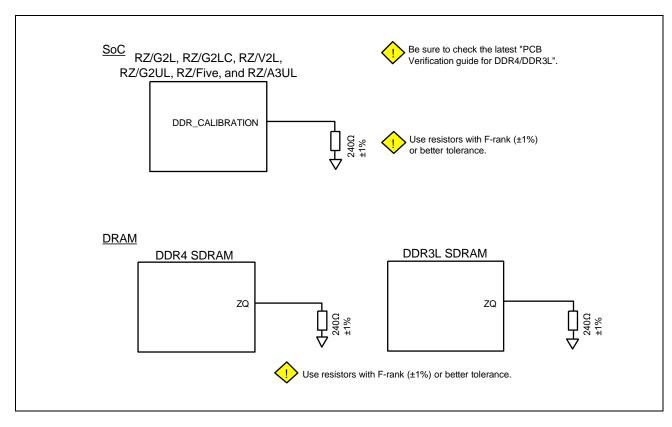

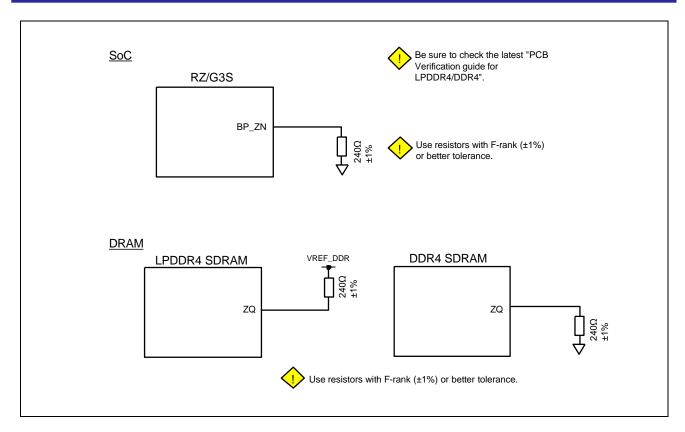

## 4.2.8 ZQ Resistor (Value and Tolerance)

- Install ZQ resistors with the value specified in the PCB verification guide both on the SoC side and DRAM side.

- Select a resistor with a tolerance of  $\pm 1\%$  or better and place it as close as possible to the pin.

Figure 4.4(a) ZQ Resistor for DDR4 and DDR3L

Figure 4.4(b) ZQ Resistor for DDR4 and LPDDR4

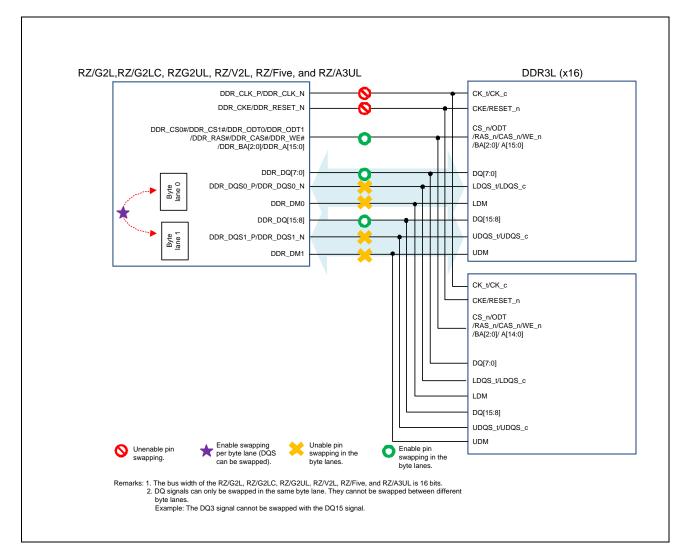

### 4.2.9 Pin Swapping for DDR3L

The MPU's DDR interface has a signal pin swapping function and has some restrictions.

- Make sure that the following restrictions are met:

- Signals of DDR\_A[15:0], DDR\_BA[2:0], DDR\_ODT[1:0], DDR\_CS[1:0]#, DDR\_RAS#, DDR\_CAS#,

DDR\_WE# can be swapped.

- During write leveling, the SoC side monitors changes in all DQ signals. Designers can switch DQ signals in the same byte lane at their own discretion.

- The DQS/DQS#[1:0] signals can be swapped per differential pair. The positive or negative logic of the DQS signals cannot be swapped.

- DM signals cannot be swapped with DQ signals.

- The initialization software must contain information about pin swapping (a generation tool is provided).

Figure 4.5 Pin Swapping between the MPU and DDR3L Interface

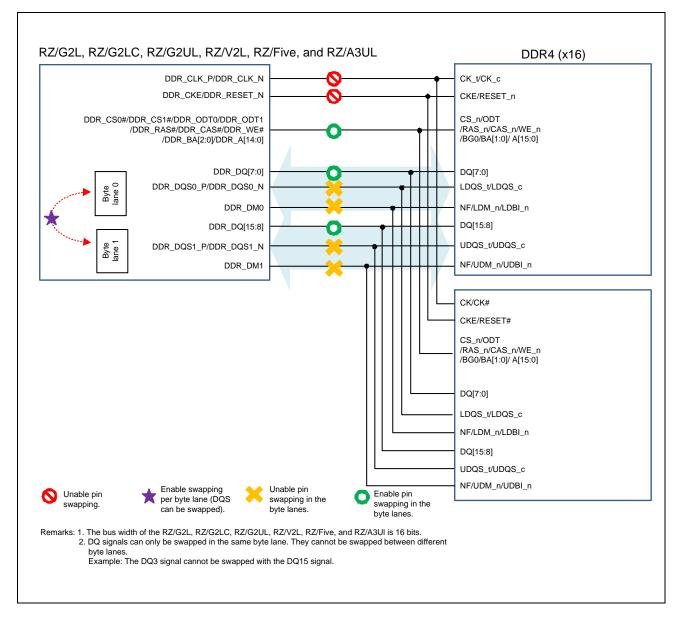

### 4.2.10 Pin Swapping for DDR4

The MPU's DDR interface has a signal pin swapping function and has some restrictions.

- Make sure that the following restrictions are met:

- Address/command signals can be swapped.

- During write leveling, the SoC side monitors changes in all DQ signals. Designers can switch DQ signals in the same byte lane at their own discretion.

- DM signals cannot be swapped with DQ signals.

- The initialization software must contain information about pin swapping (a generation tool is provided).

Figure 4.6(a) Pin Swapping between the MPU and Two DDR4 DRAMs

Figure 4.6(b) Pin Swapping between the RZ/G3S and the Single DDR4 DRAM

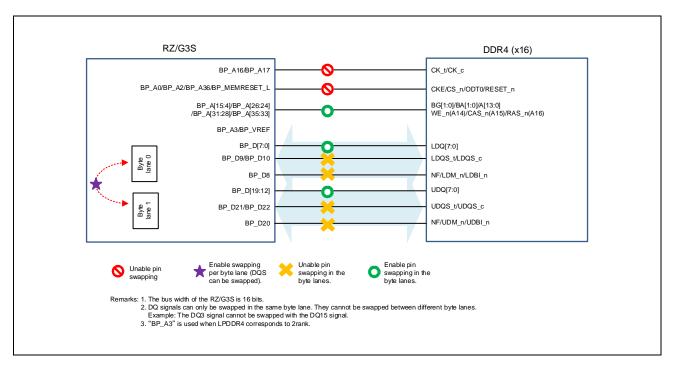

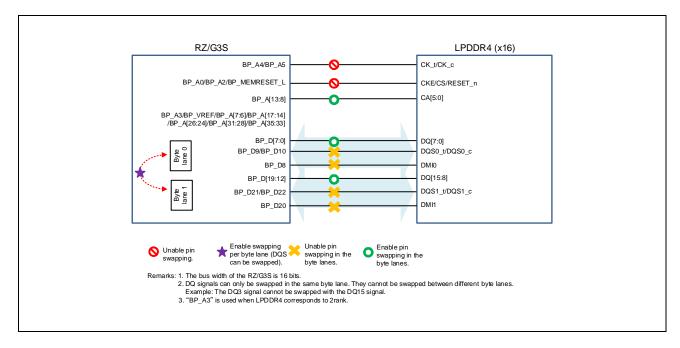

### 4.2.11 Pin Swapping for LPDDR4

G3S

The MPU's DDR interface has a signal pin swapping function and has some restrictions.

- Make sure that the following restrictions are met:

- Address signals CA[5:0] can be swapped within that range.

- Control signals cannot be swapped.

- The positive or negative logic of the DQS signals cannot be swapped.

- DMI signals cannot be swapped with DQ signals.

- The initialization software must contain information about pin swapping.

Figure 4.7 Pin Swapping between in the MPU and the LPDDR4 DRAM

### 4.2.12 Power-on Sequence for DDR3L

- DDR3L SDRAM has VDDn (n = 0 to 9, typ.1.2 V) and VDDQn (n = 0 to 9, typ.1.2 V) as power supply pins. Please supply VDDn (n = 0 to 9) and VDDQn (n = 0 to 9) for DDR4 and DDR3L from the same power supply system.

- When DDR3L is connected to the target devices and both the power supplies are shared with the target devices, the power supply should be adjusted for the power supply interface of the DDR3L SDRAM.

- Please refer to JEDEC (JESSD79-3F and JESD79-3-1A.01) for more information on power-on order restrictions.

### 4.2.13 Power-on Sequence for DDR4

- DDR4 SDRAM has VDDn (n = 0 to 9, typ.1.2 V) and VDDQn (n = 0 to 9, typ.1.2 V) as power supply pins. Please supply VDDn (n = 0 to 9) and VDDQn (n = 0 to 9) for DDR4 and DDR3L from the same power supply system.

- When DDR4 is connected to the target devices and both the power supplies are shared with the target devices, the power supply should be adjusted for the power supply interface of the DDR4 SDRAM.

- Please refer to JEDEC (JESD79-4-1B and JESD79-4D) for more information on power-on order restrictions.

### 4.2.14 Power-on Sequence for LPDDR4

- LPDDR4 SDRAM has VDD1 (typ.1.8 V), VDDQ (typ.1.1 V) and VDD2 (typ.1.1 V) as power supply pins.

- The power-on sequence is defined for each power supply of LPDDR4.

- When LPDDR4 SDRAM is connected to the target device, and both the power supplies are shared with the target device, the power supply must be adjusted for the power supply interface of the LPDDR4 SDRAM.

- Please refer to JEDEC (JESD209-4) for more information on power-on order restrictions.

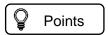

### 4.2.15 VREF, DDR\_CALIBRATION, ZQ, CS, and CLK for A3M

АЗМ

- To generate VREF input from the VDD/GND pin nearest to each VREF input pin, the VREF voltages can be generated by using the VDD/GND in the presence of noise.

- The VREF generation circuit must be placed as close as possible to the VREF pin.

- Input leakage current on the VREF pin leads to a voltage shift that depends on the dividing resistor values.

- Install the DDR\_CALIBRATION and ZQ resistors with the values specified in the PCB verification guide to the pins.

- Select a resistor with a tolerance of  $\pm$  1% or better and place it as close as possible to the DDR\_CALIBRATION and ZQ pins.

- The CS pins of A3M, DDR\_CS\_SOC and DDR\_CS\_DRAM, are not for external DDR3L but for external resistor. The DDR\_CS\_SOC and DDR\_CS\_DRAM implementation is as follows.

- The CLK pins of A3M, DDR\_CLK\_P and DDR\_CLK\_N, are also not for external DDR3L but for external capacitor and resistor. The DDR\_CLK\_P and DDR\_CLK\_N implementation is as follows.

Figure 4.8 DDR VREF, CS, and CLK Circuit for A3M

## 4.3 Resistor and Capacitor

- Follow the guidelines for selecting bypass capacitors. High-speed interfaces have dedicated power pins, and the High-Speed Interface Design Guidelines provide recommended capacitance values for bypass capacitors for power pins.

- As with power supply decoupling, place small-capacity bypass capacitors close to the MPU's power supply pins.

- Resistors used as current references may specify not only resistance values but also accuracy and temperature coefficients, so follow the design guidelines.

### 4.4 Clock

- The guidelines provide requirements for external clock input, so follow the guidelines for designing. A spread-spectrum clock (SSC) cannot be connected as the external clock.

- Make sure that a clock is not input before the power of the MPU is turned on.

## 4.5 PCIe

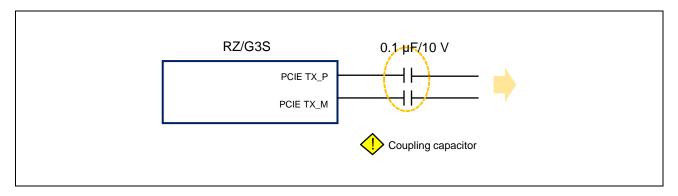

## 4.5.1 AC Coupling Capacitor

• Make sure the transmitter has a coupling capacitor installed.

Figure 4.9 Coupling Capacitor at the Transmitting End for the PCIE

### 4.5.2 Clock

• Make sure you provide an external clock for PCIe. PCIe requires an external clock.

## 4.6 Instructions in schematic for PCB Layout

The guideline provides recommendations and restrictions for wiring patterns. We recommend including indications in the circuit diagram to give pattern designers a secure understanding of how recommendations and restrictions in the guidelines have been applied.

For general reference information on PCB pattern design, see **section 6**, **PCB Layout Design** in this guideline.

## 4.7 Observing High-Speed Serial Interface Signals

- Note that installation of an observation pad on high-speed serial signal wiring may cause degradation in the signal quality.

- Unnecessary stubs are constructed to set observation points.

- Wiring runs that can only be arranged in the inner layer are brought out to the surface layer to set observation points on the surface layer.

- Setting observation points for differential signals may lead to the symmetry of the differential wiring collapsing.

- The possibility of signal degradation increases with the signal speed, due to the addition of observation circuits. In order to improve the design quality, avoiding the unjustifiable setting of observation points is also necessary.

- High-speed signals might be distorted due to ISI or reflection deriving from observation points. In such cases, ideal waveforms such as are shown in the documents for reference might not be observed.

- In cases such as the above, you must proceed with advanced simulation of the intended observation points and the input circuits of the observation equipment by using the S parameter of the wiring and confirm the suitability by using the observation point movement function of the observation equipment.

## 4.8 Disturbance Noises and Static Electricity

ALL

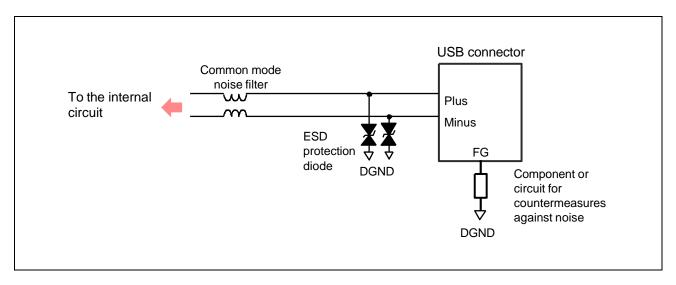

- For interfaces such as USB2.0, that can be hot-plugged or connected to external devices, insert components for countermeasures against static electricity and external common mode noise.

- Dedicated components that can handle the signal level and signal frequency of each of the interfaces and components with noise filters having an ESD protection function are also available. Select components by reference to the circuit diagram of the evaluation board kits.

Figure 4.10 Example of Measures Against Disturbance Noises and Static Electricity

### 4.9 USB

### 4.9.1 Overcurrent or VBUS Input

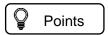

ALL

- When the overcurrent inputs are used, the input signal level should be 3.3 V. On the other hand, when a USB host is used but the overcurrent inputs are not used, these pins should be pulled up as the overcurrent interrupt from the VBUS controller may not be disabled.

- While the power supply to the MPU is turned off, the overcurrent input should not be the high level.

- When the VBUS input is used, connect it to the MPU through external dividing resistors with a value of  $1k\Omega \pm 1\%$  and  $1.8k\Omega \pm 1\%$ .

The following figure shows a design example on the EVK; however, please refer to the datasheet of the USB VBUS control IC to be used.

Figure 4.11 Overcurrent or VBUS Input

#### 4.9.2 VBUS Enable

ALL

• Select an USB VBUS controller IC with an active-high EN input.

The VBUS enable signal of the USB interface is assumed as active high. And during a hardware reset (PRST# is low), the VBUS enable pin is high impedance. Examples of implementation are seen on our EVK. Please refer to their schematics and also refer to the datasheet of the USB VBUS controller IC.

### 5. Others

### 5.1 Unused Pins

- If there are unused function pins, handle these pins in accord with the statements on the handling of unused pins in the hardware manual.

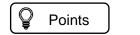

- Please connect to GND via 1-µF capacitor about the terminal processing of ABG NCP OUT.

- Even if you do not use all the functions, be sure to turn on the relevant power supplies.

Figure 5.1 Terminal Processing of ABG\_NCP\_OUT

- RZ/G2L Group, RZ/G2LC Group User's Manual: Hardware

- RZ/V2L Group User's Manual: Hardware

- Lists of pin functions for RZ/G2L, RZ/G2LC, and RZ/V2L

## 5.2 NC pins

G2UL Five

• Check how to treat NC pins. Please refer to the pin function list of the MPU.

In general, a pin being labeled non-connection (NC) means that the pin is not connected to the silicon die inside the MPU. NC pins do not generally need to be connected to anything, but some products may specify recommended pin treatments, such as connecting to GND or a power supply. Therefore, even if a pin is marked NC, be sure to check whether the recommended pin treatment is listed in the technical documentation for each IC. If the treatment method is not listed, we recommend that you contact the chip vendor. Similarly, be careful with LSI test pins and internal regulator output terminals.

## 5.3 Countermeasures against Overshoots and Undershoots

- Larger than expected signal overshoots and undershoots must be prevented from causing the device ratings to be exceeded.

- A common method of doing so is to insert damping resistors near the signal outputting ends before determining the

necessity and, if one is required, value of the resistor through evaluation. However, in such cases, you must pay

attention to the following points.

- The placement of damping resistors increases the number of parts near the MPU and peripheral devices, significantly affecting the placement of other important parts.

- The connection of damping resistors necessitates the movement of signals to the surface layer. As a result, via holes and through holes significantly affect the properties of the wiring.

- When inserting a damping resistor to prevent overshooting and undershooting, carefully determine their necessity rather than inserting them unnecessarily.

- Obtain IBIS models of the buffers, simulate typical transmission paths such as the longest one and shortest one,

and estimate the possible amounts of overshoot and undershoot in advance.

- Reduce the amounts of overshoot and undershoot by bringing the wiring layer (surface layer/inner layer) and wiring width close to the output impedance of the buffer.

- Check if the driving ability of the output buffers is adjustable or can be set.

- Apply impedance matching with parallel termination at the receiving ends instead of inserting damping resistors.

- Hardware user's manuals for individual target devices

- Lists of pin functions for individual target devices

## 5.4 Level Shifting

- Some types of IO of the target device such as SD/MMC and QSPI allow two power supply voltages. The IO type of Gigabit Ethernet allows three power supply voltages.

- When the signal voltage differs between the MPU and a peripheral device, level shifters should be used and pay attention to the following points.

- Is the IC to be used voltage tolerant?

- Does the high-level voltage of signals and the VIH of the IC raise a problem?

- Does the IC operate at a speed sufficient for the operating frequency of the signals?

- Pay attention to the power supply and output enable of the IC used for level shifting so that the signals do not go to the high level while power for the target device is cut off.

- In order to prevent misuse and misconnection of signals before and after level shifting, we recommend using net names that include signal voltages on the circuit diagram.

- Hardware user's manuals for individual target devices

- Lists of pin functions for individual target devices

### 5.5 IO Characteristics between MPU and Connected Devices

- When connecting the target device and a peripheral device, there will generally be no problem if the CMOS inputs and outputs have the same power supply voltage, even if the connections are direct at the DC level. If the AC timing also raises no problems, the connection will be problem-free. However, the DC specifications might differ slightly from device to device, so we recommended checking the AC and DC margins of both sides.

- The main external factors that may reduce the AC and DC level margins are as follows.

- Minor differences in power supply voltage, such as where different power supply sources are used, or an FET switch is used

- Superimposition of ground bounce and signal reflections due to simultaneous switching output (SSO) on rising and falling of the signals

- Signal rounding due to excessive wiring length or load capacitance

- Under-driving of the output buffers due to excessive resistive loads

- Degradation in the signal quality due to crosstalk or ISI

- If there is a possibility that the AC and DC margins for the connected device are insufficient, consider measures such as inserting a pull-up resistor or buffer in the circuit design stage.

- Hardware user's manuals for individual target devices

- Circuit diagrams of individual evaluation board kits

## 5.6 IO Voltage Level Restriction for the PVDD182533 Power Domain

The IO voltage of the pins belonging to the PVDD182533\_0 or the PVDD182533\_1 power domains are selectable from 1.8 V, 2.5 V, and 3.3 V when used as Ethernet function; however, when used as other than Ethernet, the IO voltage should be 3.3 V. Please also refer to the pin function list.

Table 5.1 Supported IO Voltage Levels for the PVDD182533 Power Domain

|                   | As Ethernet         | As other than Ethernet |

|-------------------|---------------------|------------------------|

| IO voltage usable | 1.8 V, 2.5 V, 3.3 V | 3.3 V                  |

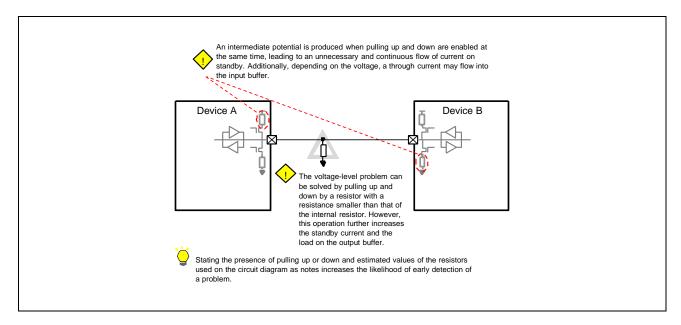

## 5.7 Conflict between Pull-Up and Pull-Down

ALL

- Many devices including the target devices might have pull-up and down resistors. Although internal pulling up and

down help to reduce the number of parts, conflicts may occur when devices are connected to each other, leading to

unexpected problems.

- The following is a common case. Device A has a pull-up resistor and device B has a pull-down resistor. Connecting A and B leads to the signal potential becoming intermediate.

#### Cases

- An intermediate potential is produced because the internal pulling up and down compete against each other.

- The internal pulling up or down competes with the pulling down or up in an external circuit.

- When a device is turned off, pulling up in another device may apply a voltage exceeding the standard, and the

power that should have been turned off does not become 0 V because of external pulling up or a device-protection

diode.

- In particular, pay attention to pulling up and down for use in setting the mode of the target device.

- Check the data sheets and technical documentation of each device for details to avoid conflicts.

- The presence of internal pulling up or down, values of the resistors used, and method of control (such as in terms of always being on, and pin and register settings)

- Interface equivalent circuit including pulling up or down

- Behavior in special cases such as during and immediately after a reset, etc.

- The pin function table of the target device describes the information and control of the internal pulling up and down, and the pull-up or -down resistor values are described in the electrical characteristics.

Figure 5.2 Conflict between Internal Pulling Up and Down

## 5.8 Relatively High-Speed Interfaces (about 10 to 100 MHz)

We provide design guidelines for high-speed signal interfaces such as MIPI-CSI, MIPI DSI, and USB, but it does not specially provide those for relatively high-speed synchronous parallel interfaces (such as Parallel Input/Output, Ether MII, SD/MMC, and QSPI).

- When designing a relatively high-speed interface, we recommend that you observe the following general precautions:

- Include wiring instructions, such as equal-length wiring, in the schematic diagram to avoid problems in the layout design.

- Route all wiring on a single layer to prevent delay differences between layers. If possible, calculate the delay from a transmission simulation in advance and instruct the designer to design an equal delay pattern.

- Leave sufficient wiring spacing to prevent crosstalk. If possible, the wiring spacing should be three times the distance to the reference layer.

- When using a flexible cable to connect to a peripheral device, be sure to provide a return path and provide a sufficient number of ground wiring to prevent crosstalk and unnecessary radiation.

## 5.9 Notes on Signal Connection

ALL

- Make sure that the CMOS input ports are not left open-circuit (Hi-Z).

- If they are left open-circuit, a through current may continue to flow, leading to deterioration and destruction of elements.

- Also pay attention to hidden open-circuit states of input ports, such as when a part or IC that is a destination for connection is not mounted.

- Confirm that output signals do not conflict between devices including the MPU.

- If such conflict continues for a long time, elements may deteriorate or be destroyed.

- Also, pay attention to hidden conflicts arising from special situations such as during a reset.

- Be careful when connecting ICs that operate under special conditions, such as ICs that operate with the power of an external USB bus even if the main power of the board is not on.

- Do not drive high or pull up pins that do not have tolerance.

- In the Renesas evaluation board kits, the USB-UART bridge IC is an LSI chip that partially operates with USB bus power.

- Be careful when using WDTOVR\_PERROUT# terminal of RZ/G3S. When PRST# signal level is low, the pin condition of WDTOVR\_PERROUT# terminal is Hi-Z, not the high level. So, an external pull-up resistor is required.

#### Remarks:

Technically, the pins of the target device that are capable of pulling up and down control remain open-circuit from the time the power is turned on until reset is released or until pulling up or down is enabled by the PFC settings, if there is no external component or IC that determines the signal level.

If the reset period is short and the PFC settings proceed quickly after startup, deterioration and destruction due to heat generated by the IO through current will not occur. If you do not need the LSI to perform any processing, we consider turning off the power to be normal. However, if there is a special circumstance, such as when it is necessary to leave the power on or have a longer reset period, use an external device for additional pin handling, although this will increase the number of components.

## 5.10 Interrupt Signals

- The MPU has interrupt inputs like the NMI and IRQs. Note that these interrupt inputs differ in the IO power supply they are supplied with, whether the IO buffer is a Schmitt trigger, and whether there is a built-in pull-up/pull-down or not.

- Also, the RZ/G2LC has IRQ0 to IRQ7, but IRQ2 and IRQ3 cannot be used, so be careful.

### 5.11 eMMC

#### 5.11.1 Connection with eMMC

- Since the eMMC interface is a relatively high-speed parallel interface, we recommend that you perform SI simulation with the IBIS model.

- If you are concerned about overshooting or undershooting during eMMC boot, add a series damping resistor to the interface.

- When using an eMMC as a boot device, the output impedance should be  $50\Omega$ . So please design the capacitive load according to the electrical specification in the user's manual and the transmission line of the board to be  $50\Omega$ .

#### 5.11.2 eMMC Interface Circuit

- Determine the pull-up resistor values for the CMD and DAT signals according to the operating voltage in reference to the recommended values provided in the eMMC standard documentation.

- Insert a series termination resistor (series resistor) for the CLK signal as necessary.

- We recommend that you confirm that the signal quality is free of problems by simulating transmission.

- When booting from an eMMC is used, eMMC must be reset before the start of booting up the CPU.

Note 1. Some eMMC devices may not activate reset pin function just after the factory shipping.

• Please refer to JEDEC(JESD84-B51) for more information.

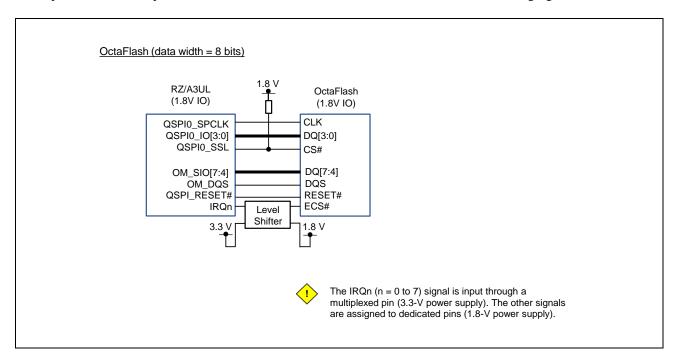

## 5.12 Octa Memory Controller

• When using an OctaFlash as boot memory, connect the QSPI\_RESET# pin to the OctaFlash RESET# pin. An OctaFlash can be only connected to the Octa Memory Controller, not to the SPI Multi I/O Bus Controller.

An implementation example of an OctaFlash and controller connection is illustrated in following figure.

Figure 5.3 Connection to the OctaFlash

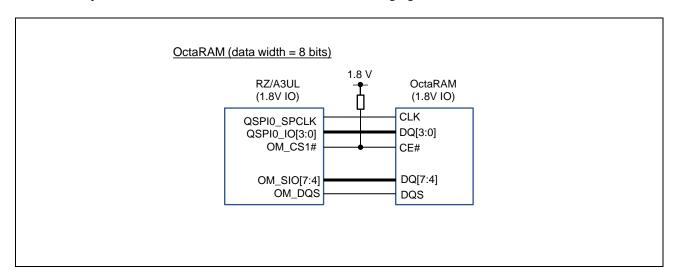

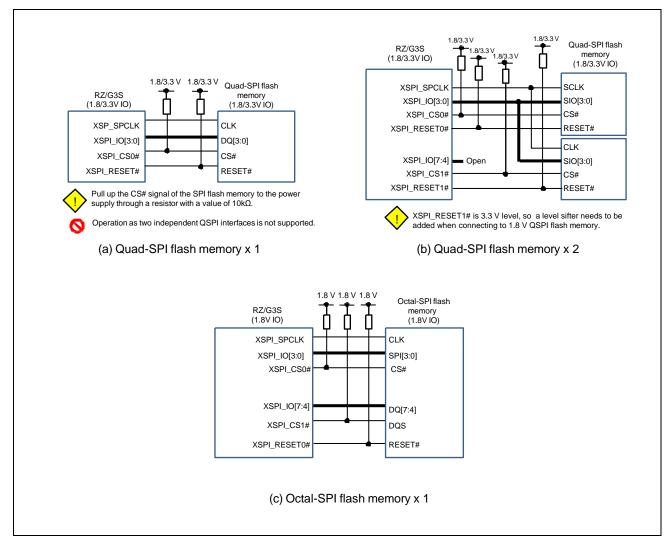

Also an example of an OctaRAM connection is illustrated in following figure.

Figure 5.4 Connection to the OctaRAM

### 5.13 SPI

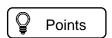

#### 5.13.1 SPI Multi I/O Interface

The SPI multi I/O interface consists of two internal QSPI interfaces; however, these two interfaces do not support independent operation.

When QSPI0 is used as the Single-SPI or Quad-SPI interface, QSPI1 cannot be used. Although connecting two units of Quad-SPI flash memory to QSPI0 and QSPI1 in parallel and using them as 8-bit width is possible, QSPI0 and QSPI1 cannot be used as two independent interfaces for Quad-SPI flash memory.

- The QSPI boot mode only supports QSPI0 interface. In order to use Octal SPI interface by combination of QSPI0 and 1, software should change configuration after boot.

- The SPI multi-I/O interface is a relatively high-speed interface. Although we do not have a specific guide, we recommend that you use equal-length wiring and perform a transmission simulation in advance to check that there are no problems with the signal timing or quality.

Figure 5.5 Connection of SPI Flash Memory

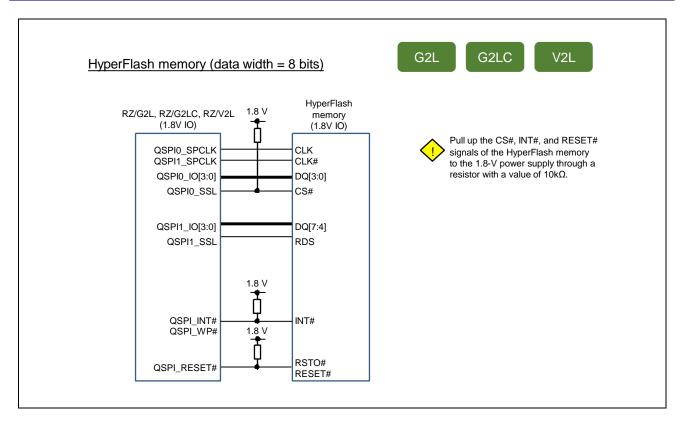

Figure 5.6 Connection of HyperFlash Memory

## 5.13.2 eXpanded Serial Peripheral Interface (xSPI)

G3S

- The xSPI enables the direct connection of Quad/Octal-SPI flash memory and OctaRAM to the MPU.

- When two Quad-SPI flash memories are connected to the MPU, the two Quad-SPI flash memories operate exclusively of each other.

- By default, CS1 does not have an address space. The address space of CS0 and CS1 can be set by registers in the SYSC section. When setting the address spaces of CS0 and CS1, overlapping addresses is prohibited.

- The xSPI is a relatively high-speed interface. Although we do not provide any guide in particular, we recommend that you confirm that the signal timing and quality are free of problems by providing instructions about equal-delay (equal-length) wiring or simulating transmission in advance.

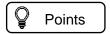

Figure 5.7 Connection of SPI Flash Memory

Figure 5.8 Connection of OctaRAM

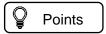

### 5.13.3 Master and Slave

ALL

- The SPI Multi I/O interface supports only master mode and the Renesas Serial Peripheral interface, RSPI, supports master and slave modes.

- When the RSPI is used in master mode, the SSL signal is fixed to the low level.

- When the RSPI is used in slave mode, the SCK input is not a Schmitt-trigger input. Therefore, pay attention to glitches and rounding of the clock waveform due to pin capacitances and wiring branches.

- When the RSPI is used in both master and slave modes, such as on a multi-master SPI bus, make sure that the two

outputs do not become short-circuited.

Figure 5.9 Connection of SPI and RSPI

Documents for Reference

- Hardware user's manuals for individual target devices

- Lists of pin functions for individual target devices

- Datasheets or technical documents for the individual peripheral devices

## 5.13.4 Selection of QSPI flash memory

ALL

Using a QPSI flash memory with RESET pin is recommended.

When accessing over 16MB memory area, the following changes are needed.

- (1) change from 3-byte address access to 4-byte address access (enter 4-byte addressing, Address: B7h)

- (2) switch to a BANK other than the first 16MB (read extended address register, Address: C8h)

When a reset occurs after these changes, the SoC will be reset, but the flash memory will not be reset. Then changes on the flash memory will remain. The boot ROM code on the SoC will try to read the first 16MB of the flash memory with "3-byte address"; however, the flash memory cannot accept that request. Therefore, the SoC will fail to reboot.

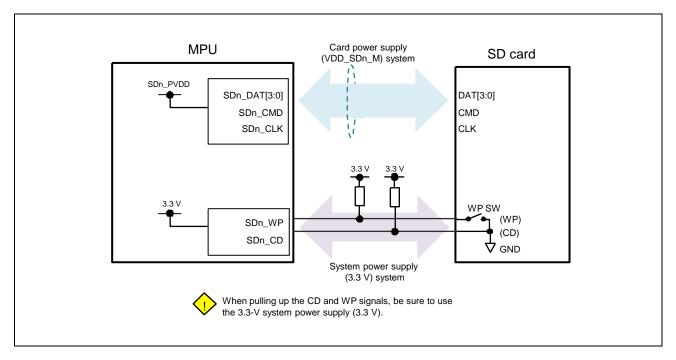

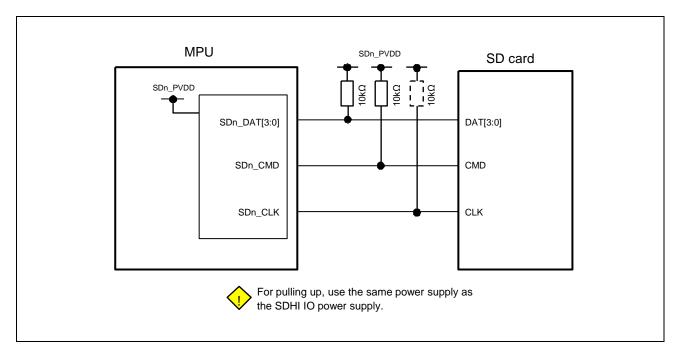

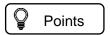

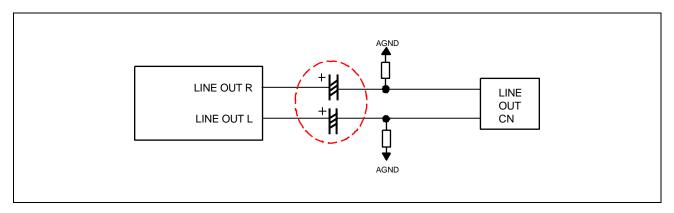

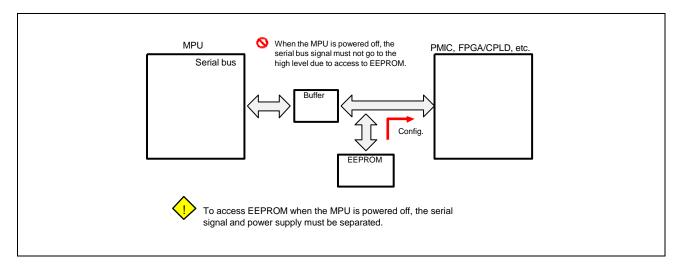

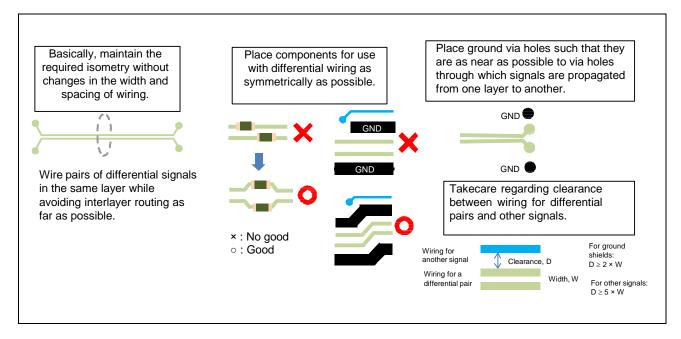

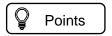

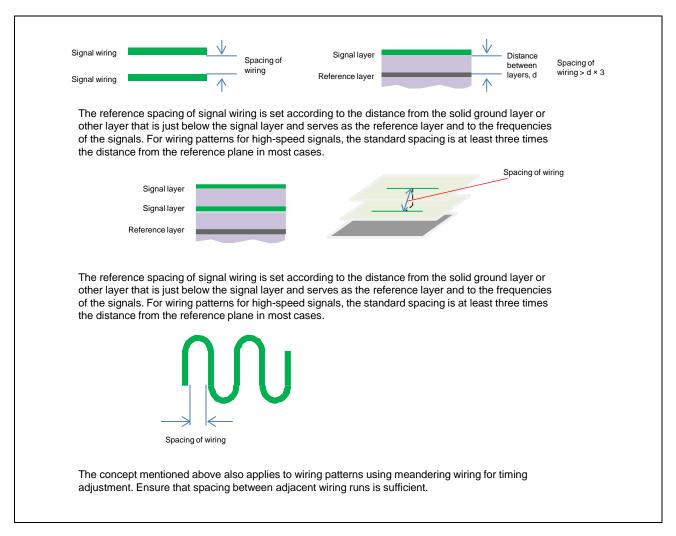

With a QSPI flash memory less than 16MB capacity, this issue will not occur because the changes (1) and (2) for 4-byte address read are not needed.