## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **Application Note**

**Multimedia Processor for Mobile Applications**

**EMMC** Interface

-----

**EMMA Mobile1**

Document No.S19904EJ1V0AN00Date PublishedAug. 2009

© NEC Electronics Corporation 2009 Printed in Japan

### PREFACE

| Purpose      | The purpose<br>EMMC (SDM                                     | of this document is to specify the usage of EMMA Mobile1<br>I) interface.                                                                                                        |

|--------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Organization | <ul><li>Introduct</li><li>Usage of</li><li>Example</li></ul> | nt includes the following:<br>ion<br>f EMMC(SDM) Interface<br>of EMMC Operation<br>Driver Function                                                                               |

| Notation     | Here explain<br>Note<br>Caution<br>Remark                    | s the meaning of following words in text:<br>Explanation of item indicated in the text<br>Information to which user should afford special attention<br>Supplementary information |

**Related document** The following tables list related documents.

#### **Reference Document**

| Document Name                                           | Version/date | Author      | Description                 |

|---------------------------------------------------------|--------------|-------------|-----------------------------|

| S19265EJ1V0UM00_ASMUGIO.pdf                             | 1st Edition  | NECEL       | SMU&GPIO user's manual      |

| S19268EJ1V0UM00_1chip.pdf                               | 1st Edition  | NECEL       | 1 chip user's manual        |

| S19361JJ2V0UM00_SDI.pdf                                 | 2nd Edition  | NECEL       | SDM interface user's manual |

| S19907EJ1V0AN00_GD.pdf                                  | 1st Edition  | NECEC       | GD Spec                     |

| KMCEG0000A-S9980(4GB<br>moviNAND_8Gb MLC Based)_0.0.pdf | V0.0         | SAMAUN<br>G | EMMC chip user's manual     |

|                                                         |              |             |                             |

#### Disclaimers

- The information contained in this document is subject to change without prior notice in the future. Refer to the latest applicable data sheet(s) and user manual when designing a product for mass production.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this documents or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customers' equipment shall be done under the full responsibility of the customer. NEC Electronics assume no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

#### Note)

- 1. "NEC Electronics" as used in this document means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- 2. "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above)

## CONTENTS

| Chapter 1 Introduction                      | 7  |

|---------------------------------------------|----|

| 1.1 Outline                                 | 7  |

| 1.2 Development Environment                 |    |

| Chapter 2 Usage of EMMC(SDM) Interface      | 8  |

| 2.1 Initialization                          | 9  |

| 2.2 Data Transfer                           | 11 |

| 2.3 Erase                                   | 14 |

| 2.4 Write Protect Management                | 15 |

| 2.5 Lock/Unlock Operation                   | 16 |

| Chapter 3 Example of EMMC Operation         | 17 |

| 3.1 Outline of EMMC Operation               | 17 |

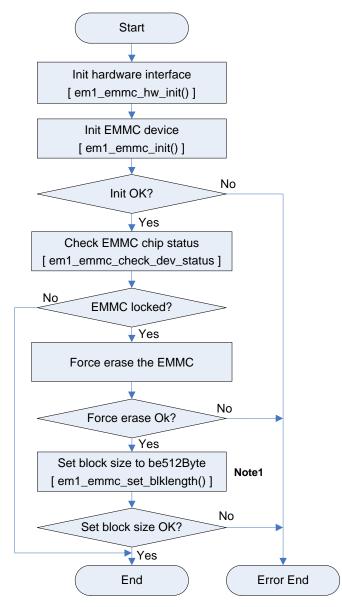

| 3.2 Initialization                          | 18 |

| 3.2.1 Operation Flow                        | 18 |

| 3.2.2 Operation Detail                      | 19 |

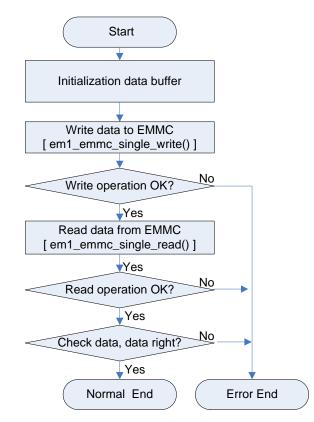

| 3.3 Example of EMMC Single Block Read/Write | 24 |

| 3.3.1 Operation Flow                        | 24 |

| 3.3.2 Operation Detail                      | 25 |

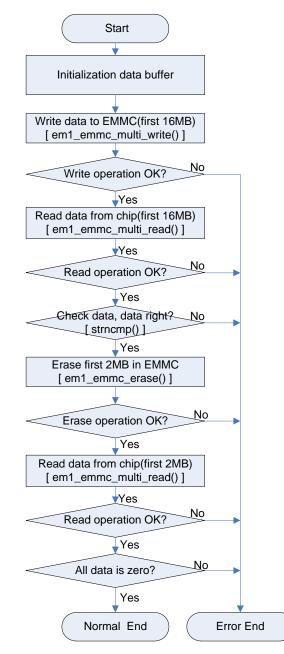

| 3.4 Example of EMMC Multi Block Operation   | 27 |

| 3.4.1 Operation Flow                        | 27 |

| 3.4.2 Operation Detail                      | 28 |

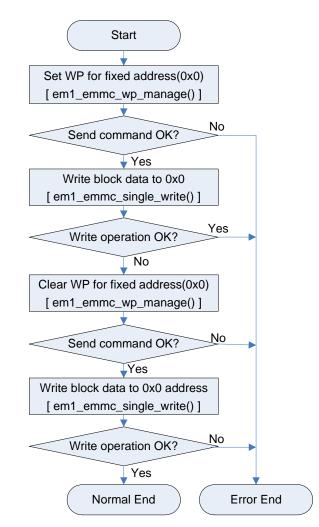

| 3.5 Example of EMMC Write Protect Operation | 29 |

| 3.5.1 Operation Flow                        | 29 |

| 3.5.2 Operation Detail                      | 30 |

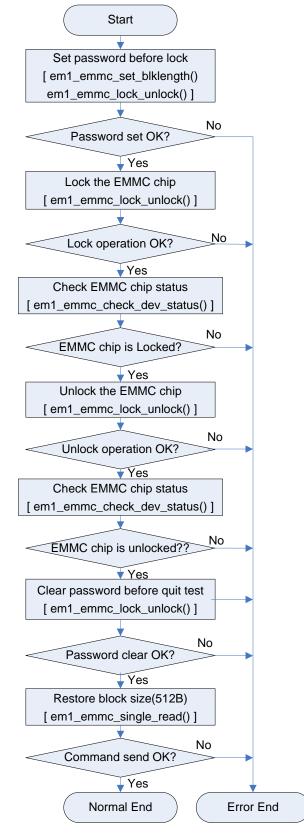

| 3.6 Example of EMMC Lock/Unlock Operation   | 31 |

| 3.6.1 Operation Flow                        | 32 |

| 3.6.2 Operation Detail                      | 33 |

| APPENDIX A EMMC Driver Function             | 35 |

| A.1 Function List                           | 35 |

| A.2 Global Variable Define                  | 35 |

| A.3 Structure Define                        | 36 |

| A.3.1 mmc_csd                               | 36 |

| A.4 Function Details                        | 37 |

| A.4.1 Hardware Initialization Function      | 37 |

| A.4.2 EMMC Init Operation                   | 38 |

| A.4.3 Sector Setting                        | 40 |

| A.4.4 Send Command                          | 41 |

| A.4.5 Set Clock                             | 43 |

| A.4.6 Set Block Length                      | 44 |

| A.4.7 Select Card                           | 45 |

| ANN | EX Modification History        | 65 |

|-----|--------------------------------|----|

| APP | ENDIX B COMMANDS               | 62 |

|     | A.4.19 Check Response Status   | 61 |

|     | A.4.18 Decode CSD              |    |

|     | A.4.17 Transfer Prepare        | 59 |

|     | A.4.16 Write Protect Manage    |    |

|     | A.4.15 Lock/Unlock Function    | 56 |

|     | A.4.14 Multiple Block Write    | 55 |

|     | A.4.13 Multiple Block Read     | 54 |

|     | A.4.12 Single Block Write      | 52 |

|     | A.4.11 Single Block Read       | 50 |

|     | A.4.10 Erase Function          | 49 |

|     | A.4.9 Check Device Status      | 48 |

|     | A.4.8 Configuration Extend CSD | 46 |

## LIST OF TABLES

| Table 1-1 Hardware Environment            | 7  |

|-------------------------------------------|----|

| Table 1-2 Software Environment            | 7  |

| Table 2-1 Lock/Unlock EMMC Data Structure | 16 |

| Table A-1 EMMC Driver Function List       | 35 |

| Table A-2 Global Variable Define          | 35 |

| Table A-3 Structure Define                |    |

| Table A-4 Structure of mmc_csd            |    |

| Table B-1 Command Description List        | 62 |

## **LIST OF FIGURES**

| Figure 2-1 EMMA Mobile 1 EMMC Initialization               | 9  |

|------------------------------------------------------------|----|

| Figure 2-2 EMMA Mobile 1 EMMC Data Transfer in DMA Mode    | 11 |

| Figure 2-3 EMMA Mobile 1 EMMC Erase Operation              | 14 |

| Figure 2-4 EMMA Mobile 1 EMMC Lock/Unlock Operation        | 16 |

| Figure 3-1 Connection between EMMA Mobile 1 and KMCEG0000A | 17 |

| Figure 3-2 Initialization before Test                      | 18 |

| Figure 3-3 EMMC Single Read/Write Operation Flow           | 24 |

| Figure 3-4 EMMC Multi block Operation Flow                 | 27 |

| Figure 3-5 EMMC Write Protect Operation Flow               | 29 |

| Figure 3-6 EMMC Lock/Unlock Operation Flow                 | 32 |

| Figure A-1 SDM Hardware Initialization Flow                | 37 |

| Figure A-2 EMMC Chip Initialization Flow                   | 39 |

| Figure A-3 Sector Setting Flow                             | 40 |

| Figure A-4 Send Command                                    | 42 |

| Figure A-5 Set Block Length                                | 44 |

| Figure A-6 Select Card                                     | 45 |

| Figure A-7 Configure Extend CSD                            | 46 |

| Figure A-8 Check EMMC Chip Stauts                          | 48 |

| Figure A-9 Single Block Read in CPU mode                   | 51 |

| Figure A-10 Single Block Write in CPU mode                 | 53 |

| Figure A-11 Lock/Unlock Progress                           | 57 |

| Figure A-12 Write Protect Management                       | 58 |

| Figure A-13 Register Prepare before Data transfer          | 59 |

| Figure A-14 Check Response Status                          | 61 |

## **Chapter 1 Introduction**

### 1.1 Outline

This document will show users how to operate EMMC chip on EMMA Mobile1 evaluation board. The EMMC operation will use SDM interface. More details about EMMC feature please refer to" **KMCEG0000A-S9980 (4GB moviNAND\_8Gb MLC Based)\_0.0.pdf**" (EMMC chip user's manual), please contact "Samsung Electronics " to get the EMMC chip user's manual.

### **1.2 Development Environment**

• Hardware environment of this project is listed as below.

#### Table 1-1 Hardware Environment

| Name                                     | Version | Maker                       |

|------------------------------------------|---------|-----------------------------|

| EMMA Mobile 1 evaluation board (PSKCH2Y- | -       | NEC Electronics             |

| S-0016-01)                               |         |                             |

| PARTNER-Jet ICE ARM                      | M20     | Kyoto Microcomputer Co. Ltd |

• Software used in this project is listed as below.

#### Table 1-2 Software Environment

| Name             | Version | Maker                       |

|------------------|---------|-----------------------------|

| GNUARM Toolchain | V4.3.2  | GNU                         |

| WJETSET-ARM      | V5.10a  | Kyoto Microcomputer Co. Ltd |

## Chapter 2 Usage of EMMC(SDM) Interface

According to the hardware feature, the EMMA Mobile 1 EMMC (SDM) interface has the following main function:

- 1. Initialization

- 2. Data Transfer

- 3. Erase

- 4. Write Protect Management

- 5. Lock/Unlock Operation

#### 2.1 Initialization

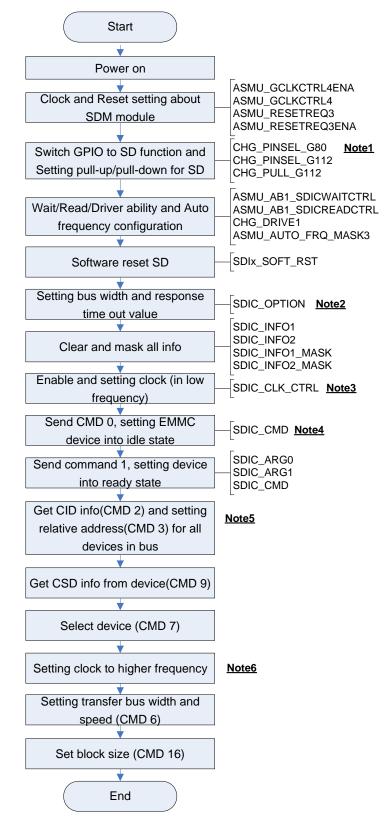

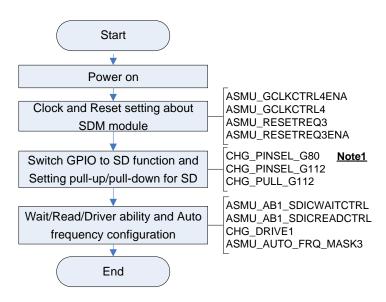

Following figure shows EMMA Mobile 1 EMMC initialize progress:

Figure 2-1 EMMA Mobile 1 EMMC Initialization

Application Note S19904EJ1V0AN00

#### Note:

1) Switch pins to SD function, in this document, use SD2 as the EMMC interface, users should operate this step according the actual hardware connection, for example: if users connect the EMMC with SD1 interface, please switch the related GPIO to SD1 function.

2) Before the initialization of EMMC device, set the bus width to be 1bit and the response time out value to be maximum, reason is: in EMMC identification progress, bus width will use 1bit and the clock frequency should in 10-400 KHz range.

3) After setting the clock for SDM transfer, please wait 1ms for stability.

4) After send command, user should check the command response, if error occurred (except when response time out for CMD 2), the initialization will be ended abnormally.

Commands simple description please refers to the "APPENDIX B COMMANDS".

More details about the commands format and function please refer to "**Chapter4.6 Commands**" of the EMMC chip user's manual.

5) CID: Card Identification

CSD: Card Specific Data

More details about CID and CSD information please refer to "Chapter 5.0 REGISTERS" of the EMMC chip user's manual

6) After initialization, users can configure the bus width and clock frequency for transfer speed according the CSD parameter of EMMC chip, the transfer speed defines in CSD register just clock frequency not in high speed mode, so the actual transfer speed is related to EMMC chip specification version.

7) More details about SDM registers and related bits please refer to SDM interface user's manual of EMMA Mobile 1.

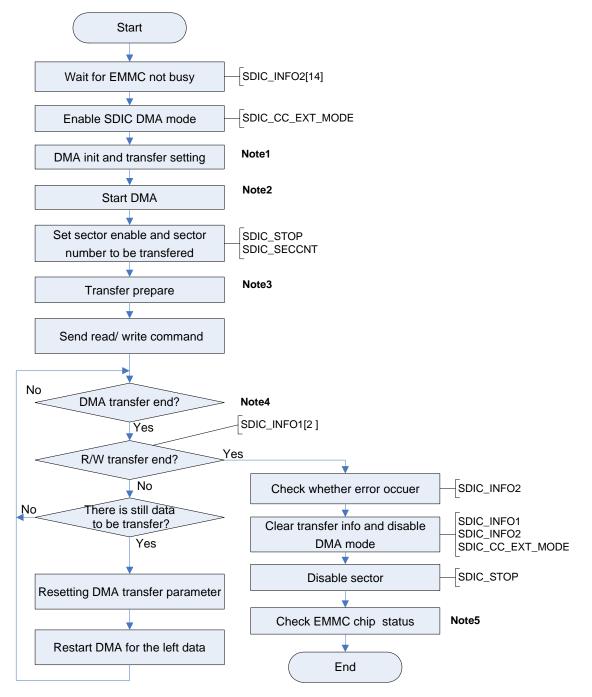

## 2.2 Data Transfer

EMMC has two kinds of data transfer mode: DMA mode and CPU mode. In realize operation, mainly use DMA mode to transfer data, so in this chapter, introduce the DMA mode operation, about EMMC single block read/write in CPU mode; please refer to **"APPENDIX A EMMC Driver Function".** Following figure shows EMMA Mobile 1 EMMC DMA read/write progress:

Figure 2-2 EMMA Mobile 1 EMMC Data Transfer in DMA Mode

#### Note:

1) In DMA init and transfer setting step, user should reset DMA channel, open DMA clock, clear DMA interrupt source, set transfer parameter for DMA.

DMA reset setting related register: ASMU\_RESETREQ0ENA ASMU\_RESETREQ0 DMA clock setting related register: ASMU\_GCLKCTRL0 ASMU\_GCLKCTRL0ENA

P2M Clear DMA interrupt source related register: DMA\_P2M\_PE0\_LCH4LCH7\_INT\_REQ\_CL DMA\_P2M\_DSP\_LCH4LCH7\_INT\_REQ\_CL

M2P Clear DMA interrupt source related register: DMA\_M2P\_PE0\_LCH4LCH7\_INT\_REQ\_CL DMA\_M2P\_DSP\_LCH4LCH7\_INT\_REQ\_CL

P2M DMA transfer setting related register: DMA\_P2M\_LCH5\_AADD DMA\_P2M\_LCH5\_BADD DMA\_P2M\_LCH5\_BOFF DMA\_P2M\_LCH5\_BSIZE DMA\_P2M\_LCH5\_BSIZE\_COUNT DMA\_P2M\_LCH5\_LENG DMA\_P2M\_LCH5\_MODE

M2P DMA transfer setting related register: DMA\_M2P\_LCH5\_BADD DMA\_M2P\_LCH5\_AADD DMA\_M2P\_LCH5\_AOFF DMA\_M2P\_LCH5\_ASIZE DMA\_M2P\_LCH5\_ASIZE\_COUNT DMA\_M2P\_LCH5\_LENG DMA\_M2P\_LCH5\_MODE

Start DMA transfer.

P2M start register

DMA\_P2M\_CONT

M2P start register DMA\_M2P\_CONT 3) Before data transfer, clear all information register, make sure data transfer end, enable the related interrupt.

Related register: SDIC\_INFO1 SDIC\_INFO2 SDIC\_INFO1\_MASK SDIC\_INFO2\_MASK SDIC\_STOP

4) Check whether DMA transfer has endedP2M transfer related register:

DMA\_P2M\_CONTSTATUS

M2P transfer related register: DMA\_M2P\_CONTSTATUS

5) After data transfer, send CMD 13(SEND\_STATUS) to read EMMC status register info, check whether error occurred.

Related register: SDIC\_ARG0 SDIC\_ARG1 SDIC\_CMD SDIC\_RSP0 SDIC\_RSP1 SDIC\_INFO1 SDIC\_INFO2 SDIC\_INFO1\_MASK SDIC\_INFO2\_MASK

More details about EMMC status register information please refer to "**Chapter 4.9 moviNAND Status**" of the EMMC chip user's manual.

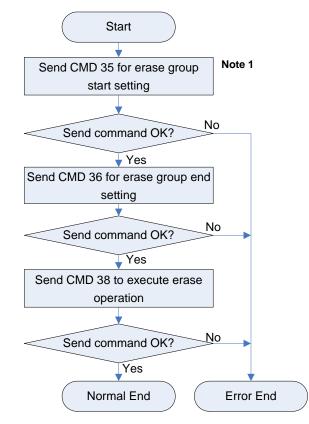

## 2.3 Erase

Following figure shows EMMA Mobile 1 EMMC erase progress:

Figure 2-3 EMMA Mobile 1 EMMC Erase Operation

#### Note:

1) Parameter about CMD 35, CMD36 will be the address to start and end, and the address will be in Group erase unit, more details about erase operation and meaning of erase group unit please refer to "Chapter 4.2.9 Erase" and "Chapter 4.10 Memory Array Partitioning" of EMMC chip user's manual.

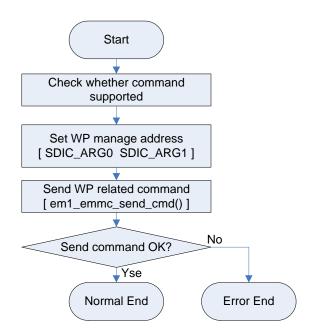

### 2.4 Write Protect Management

Write protect (WP) management including there command: set write protect (CMD 28), clear write protect (CMD 29) and send write protect info (CMD30). To realize these functions, users just need to send command to EMMC device.

The write protect argument is WP address, it based on unit of WP\_GRP\_SIZE, which is defined in CSD register.

More details about write protect function and meaning of WP\_GRP\_SIZE please refer to "Chapter 4.2.10 Write Protect Management" and "Chapter 4.10 Memory Array Partitioning" of EMMC chip user's manual.

## 2.5 Lock/Unlock Operation

Lock/Unlock operation including password setting and cancel lock/unlock EMMC device and enforce erase. To complete these function, please follow the fixed data structure format as followed.

| Byte #              | Bit 7         | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit2        | Bit 1   | Bit 0   |

|---------------------|---------------|---------|-------|-------|-------|-------------|---------|---------|

| 0                   |               | Rese    | rved  |       | ERASE | LOCK_UNLOCK | CLR_PWD | SET_PWD |

| 1                   |               | PWD_LEN |       |       |       |             |         |         |

| 2                   |               |         |       |       |       |             |         |         |

| <br>PWD_LE<br>N + 1 | Password data |         |       |       |       |             |         |         |

Table 2-1 Lock/Unlock EMMC Data Structure

**ERASE**: '1' = Forced Erase Operation (all other bits shall be '0') and only command byte is sent. **LOCK/UNLOCK**: '1' = Locks the EMMC. '0' = Unlock the EMMC (note that it is valid to set this bit together with SET\_PWD but it is not allowed to set it together with CLR\_PWD).

CLR\_PWD: '1' = Clears password (PWD).

SET\_PWD: '1' = Set new password to PWD

**PWD\_LEN**: Defines the following password length (in bytes). Valid password length is 1 to 16 bytes. **PWD**: The password (new or currently used depending on the command).

Following figure shows the lock/unlock operation flow:

Figure 2-4 EMMA Mobile 1 EMMC Lock/Unlock Operation

More details about lock/unlock operation and fixed data structure please refer to "**Chapter 4.2.11 moviNAND Lock/Unlock Operation**" of EMMC chip user's manual.

Application Note S19904EJ1V0AN00

## **Chapter 3 Example of EMMC Operation**

## 3.1 Outline of EMMC Operation

This chapter will show users how to operate EMMC chip using SDM interface.

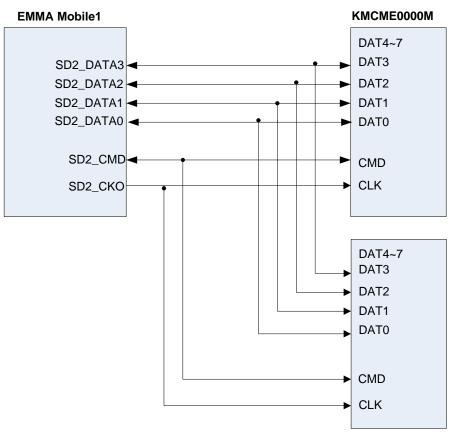

On EMMA Mobile 1 evaluation board (PSKCH2Y-S-0016-01), the external EMMC chip is KMCEG0000M (Manufacture: Samsung). Its capacity is 4GB, and it has multimedia card system specification Ver4.2 compatible feature. More details about the KMCEG0000A please refer to its user's manual.

Figure 3-1 shows the connection of EMMA Mobile 1 EMMC interface and KMCEG0000M.

KMCME0000M

Figure 3-1 Connection between EMMA Mobile 1 and KMCEG0000A

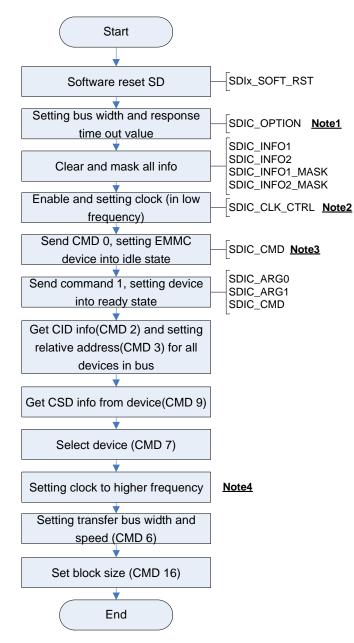

### 3.2 Initialization

Before EMMC operation, initialization should be executed at first.

#### 3.2.1 Operation Flow

Figure 3-2 Initialization before Test

More details about the functions used in initialization please refer to "APPENDIX A EMMC Driver Function"

#### 3.2.2 Operation Detail

#### (1) Init SDM module hardware

Init SDM module (function: em1\_emmc\_hw\_init() ). Following steps shows the hardware initialization (em1\_emmc\_hw\_init()) progress:

| Step1: | Reset | setting |

|--------|-------|---------|

|--------|-------|---------|

| ASMU_RESETREQ3[4]     | (0: reset; 1: cancel reset)             |

|-----------------------|-----------------------------------------|

| ASMU_RESETREQ3ENA [4] | (0: disable setting; 1: enable setting) |

Step2: Clock setting ASMU\_GCLKCTRL

ASMU\_GCLKCTRL4[7] (0: close clock; 1: open clock) ASMU\_GCLKCTRL4ENA[7] (0: disable setting; 1: enable setting)

Step3: Switch pins to SD function: CHG\_PINSEL\_G80 = 0x04000000 (GIO\_P93 -> SD2\_CKI) CHG\_PINSEL\_G112 = 0x00000555 (GIO\_P112-117 -> SD2\_CKO/CMD/DATA0-3 )

Step4: Pull-up/down setting CHG\_PULL\_G112 = 0x00666661

(SD2\_CKO: Pull-up/down Disable, SD2\_CMD and DATA0-3: Input Enable, Pull-up enable)

Step5: Drive capability setting CHG\_DRIVE1 = 0x05000000

(SD2\_CK and SD2 pins : 4mA, default value)

Setp6: Read and wait control register setting ASMU\_AB1\_SDICWAITCTRL = 0x00000300 ASMU\_AB1\_SDICREADCTRL = 0x00000000 (default value)

Setp7: Auto frequency control setting ASMU\_AUTO\_FRQ\_MASK3 = 0x07 (default value)

#### (2) Init EMMC device

EMMC device initialization (em1\_emmc \_init()) including following steps:

Step1: Power on EMMC device

Step2: Soft reset SD SDIC\_SOFT\_RST = 0x0000 (module reset) SDIC\_SOFT\_RST = 0x0007 (release reset)

Step3: Set bus width and time out value for response, card detect stable time SDIC\_OPTION = 0x80EE (bus width: 1bit; biggest time value for response time

20/65

out and card detection stable time )

Step4: Clear and mask all information and interrupt SDIC INFO1 = 0x0000

> SDIC\_INFO2 = 0x0000 SDIC\_INFO1\_MASK = 0xFFFF SDIC\_INFO2\_MASK = 0xFFFF

Step5: Set clock

SDIC\_CLK\_CTRL = 0x0140 (divide factor: 256, about 325KHz; Use the lower frequency when init EMMC) Delay 1ms after setting the clock frequency

Step6: Send CMD0, make EMMC chip to idle state, including following steps: Clear all error and information (SDIC\_INFO1, SDIC\_INFO2) Enable response end interrupt occur (SDIC\_INFO1\_MASK) Enable all error occur (SDIC\_INFO2\_MASK) Send command (SDIC\_CMD) Wait for command send end or error occur (SDIC\_INFO1, SDIC\_INFO2) Check whether error occur (SDIC\_INFO2, SDIC\_RSP0, SDIC\_RSP1) Note: If command has argument, setting the argument at first (SDIC\_ARG0, SDIC\_ARG1)

Step7: Send CMD1 with argument 0x40FF8080, make EMMC chip to ready state.

SDIC\_ARG0 = 0x8080 SDIC\_ARG1 = 0x40FF

Check whether power up is ready? (SDIC\_RSP1[15]). If not ready, send CMD1 again; if in ready state, run to next step. Details about send command please refer to step6.

Step8: All EMMC chip send CID to host, and get RCA (relative card address) information from host, including following steps:

Send CMD2(ALL\_SEND\_CID) with argument 0x00000000

Send CMD3 (SNED\_RELATIVE\_ADDR) with argument RCA (RCA init value is 1) Increase RCA value and circle Step8 until all the EMMC chip on the SD bus has get a RCA from host, at this time, response time out error will occur, run to next step. Details about send command please refer to step6.

Step9: Get CSD information, including following steps:

Send CMD9 (SNED\_CSD) with argument RCA (the one that need to send CSD information to host). Details about send command please refer to step6. Get CSD information from the command response (SDIC\_RSP0~SDIC\_RSP7)

Step10: Select EMMC chip

Send CMD7 (SELECT) with argument RCA(which selected to communicate). Details about send command please refer to step6.

Step11: Re-setting clock

SDIC\_CLK\_CTRL = 0x0301 (divide factor: 4, about 20.8MHz; Use higher frequency after init EMMC)

Delay 1ms after setting the clock frequency

Step12: Setting extends CSD register, including following steps:

Send CMD6 (SWITCH) with argument 0x03B70100 (bus width: 4 bits) to configure extends CSD register.

Change bus width in SDIC\_OPTION register

Send CMD6 (SWITCH) with argument 0x03B90100 (high speed) to configure extends CSD register. Details about send command please refer to step6.

Step13: Set block length, including following steps: Send CMD16 (SET\_BLOCKLEN) with argument "block length". Details about send command please refer to step6. Changing block size values in SDIC\_SIZE register.

More details about the initialization progress please refer to "**APPENDIX A EMMC Driver Function**".

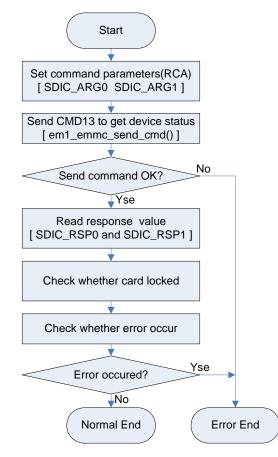

#### (3) Check EMMC Device Status

According to the EMMC chip feature (if chip has password, the chip will be locked automatically after power on), in order to make sure read/write operation success after power on, check the device status at first (function: em1\_emmc\_check\_dev\_status()). If EMMC is locked, enforce erase the whole chip by lock/unlock command. If enforce erase OK, set block size to be 512 byte, then the read and right operation followed can works normally.

Check device status (em1\_emmc\_check\_dev\_status()) including following steps:

Step1: Send CMD13 (SEND\_STATUS) with argument RCA. Details about send command please refer to step 6 of "(2) Init EMMC device" in "Chapter 3.2.2 Operation Details"

Step2: Read response value (SDIC\_RSP0, SDIC\_RSP1)

Step3: Check whether EMMC locked and error occurred according the EMMC status structure. More details about the EMMC status structure please refer to "**Chapter 4.9 moviNAND Status**" of EMMC chip user's manual.

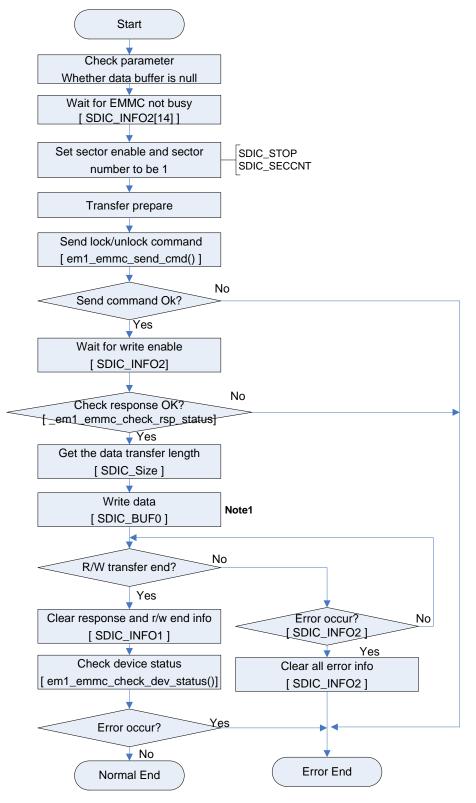

#### (4) Enforce Erase If EMMC Device Locked

If EMMC is locked, enforce erase the whole chip by lock/unlock command (function: em1\_emmc\_set\_blklength() and em1\_emmc\_lock\_unlock()).

a) Set block length to be 1.

Details about block length setting (em1\_emmc\_set\_blklength()) please refer to step13 of "(2) Init EMMC device" in "Chapter 3.2.2 Operation Details".

b) Set lock/unlock data structure, make sure the bit3 "ERASE" of the lock/unlock data structure to be 1, and execute lock/unlock function. More details about lock/unlock operation and fixed data structure please refer to "**Chapter 4.2.11 moviNAND Lock/Unlock Operation**" of EMMC chip user's manual,

Lock/unlock function (em1\_emmc\_lock\_unlock()) including following steps: Step1: Ensure EMMC interface is not busy, check bit 14 of SDIC\_INFO register

Step2: Enable sector setting and set sector number to 1 (SDIC\_STOP, SDIC\_SECCNT)

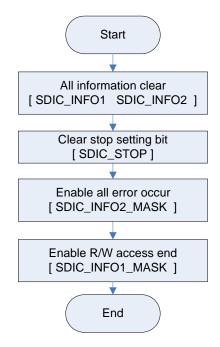

Step3: Prepare for data transfer, including following steps: Clear interrupt information in SDIC\_INFO1 register Clear all error information in SDIC\_INFO2 register Set transfer none stop (SDIC\_STOP[0] = 0) Enable all error interrupt in SDIC\_INFO2\_MASK register Enable read/write access interrupt occur in SDIC\_INFO1\_MASK register

Step4: Send CMD42 (LOCK\_UNLOCK) without argument. Details about send command please refer to step 6 of "(2) Init EMMC device" in "Chapter 3.2.2 Operation Details"

Step5: Wait for write enable (SDIC\_INFO2) and check whether error occur (SDIC\_RSP0, SDIC\_RSP1)

Step6: Write data

If no errors occur, write data (lock/unlock data structure) to EMMC chip (SDIC\_BUF0 = data)

Step7: Wait for data transfer end or error occur (SDIC\_INFO1, SDIC\_INFO2)

Step8: Send CMD13 (SEND\_STATUS) with argument RCA to check device status. Detail steps about check EMMC device status please refer to "(3) Check EMMC Device Status" in "Chapter 3.2.2 Operation Details".

#### Note:

Details about send command please refer to step 6 of "(2) Init EMMC device" in "Chapter

#### 3.2.2 Operation Details".

#### (5) Set Block Size after Enforce Erase

After enforce erase, in order to make sure the read and right operation followed can works normally, set block size to be 512 byte (function: em1\_emmc\_set\_blklength() ).

Details about block length setting (em1\_emmc\_set\_blklength()) please refer to step13 of "(2) Init EMMC device" in "Chapter 3.2.2 Operation Details".

#### Note:

The EMMA Mobile 1 SDM interface can support 512 byte as the maximum block size.

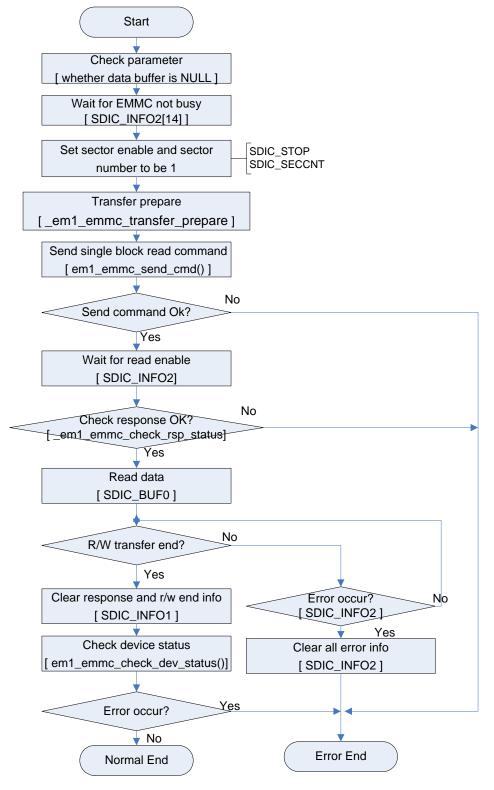

## 3.3 Example of EMMC Single Block Read/Write

In this example, we will write fixed data to EMMC chip, then read out and compare whether the data is right, both read and write operation will use single CPU operation mode.

#### 3.3.1 Operation Flow

Figure 3-3 EMMC Single Read/Write Operation Flow

More details about the functions used in this example please refer to "APPENDIX A EMMC Driver Function"

#### 3.3.2 Operation Detail

#### (1) Initialization Data Buffer

Initialize the write data buffer, set fixed value (as the following code segment shows) to write data buffer which will be wrote to EMMC chip. At the same time, initialize the read data buffer with 0, it will read out data from EMMC chip.

```

for (i =0; i<SDM_BLOCKLEN_VAL; i++ )

{

g_write_buff[i] = (i&0xFF);

}</pre>

```

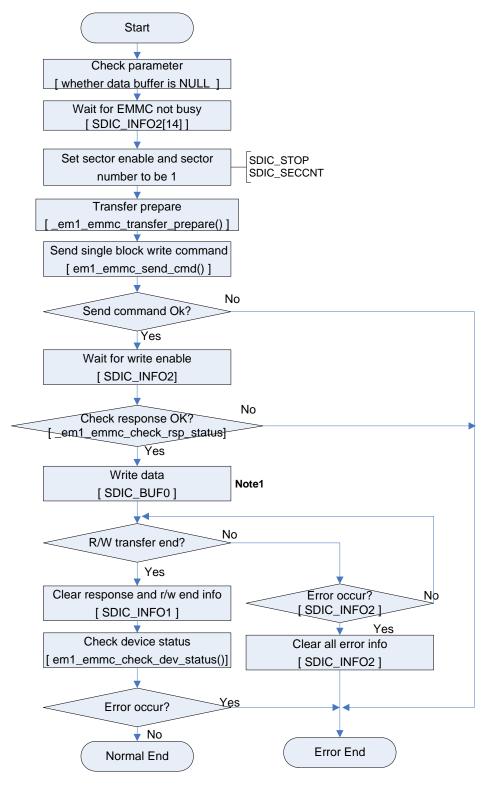

#### (2) Write Data to EMMC

Call the "em1\_emmc\_single\_write()" function to write data into EMMC chip. If write operation failed (error occur during data transfer), end the operation and print error information; if write operation works OK, continue the test program.

Following steps shows the write operation progress:

Step1: Ensure EMMC interface is not busy, check bit 14 of SDIC\_INFO register

Step2: Enable sector setting and set sector number (SDIC\_STOP, SDIC\_SECCNT)

Step3: Prepare for data transfer, including following steps: Clear interrupt information in SDIC\_INFO1 register Clear all error information in SDIC\_INFO2 register Set transfer none stop (SDIC\_STOP[0] = 0) Enable all error interrupt in SDIC\_INFO2\_MASK register Enable read/write access interrupt occur in SDIC\_INFO1\_MASK register

Step4: Send CMD24 (WRITE\_SINGLE\_BLOCK) with argument "write address". Detail steps about send command please refer to step 6 of "(2) Init EMMC device" in "Chapter 3.2.2 Operation Details".

Step5: Wait for write enable (SDIC\_INFO2) and check whether error occur (SDIC\_RSP0, SDIC\_RSP1)

Step6: Write data

If no errors occur after send CMD24 (WRITE\_SINGLE\_BLOCK), write data to EMMC chip (SDIC\_BUF0 = data)

Step7: Wait for data transfer end or error occur (SDIC\_INFO1, SDIC\_INFO2)

Step8: Send CMD13 (SEND\_STATUS) with argument RCA to check device status. Detail

steps about check EMMC device status please refer to "(3) Check EMMC Device Status" in "Chapter 3.2.2 Operation Details".

More details about single block write operation please refer to "chapter A.4.12 Single Block Write".

#### (3) Read Data

Call "em1\_emmc\_single\_read()" function to read out the written data by step (2) from EMMC. If read failed, end the operation and print error; if read OK, continue the test program. Following steps shows the read operation progress and registers configurations:

Step1: Ensure EMMC interface is not busy, check bit 14 of SDIC\_INFO register

Step2: Enable sector setting and set sector number (SDIC\_STOP, SDIC\_SECCNT)

Step3: Prepare for data transfer, including following steps: Clear interrupt information in SDIC\_INFO1 register Clear all error information in SDIC\_INFO2 register Set transfer none stop (SDIC\_STOP[0] = 0) Enable all error interrupt in SDIC\_INFO2\_MASK register Enable read/write access interrupt occur in SDIC\_INFO1\_MASK register

Step4: Send CMD17 (READ\_SINGLE\_BLOCK) with argument "read address". Detail steps about send command please refer to step 6 of "(2) Init EMMC device" in "Chapter 3.2.2 Operation Details".

Step5: Wait for write enable (SDIC\_INFO2) and check whether error occur (SDIC\_RSP0, SDIC\_RSP1)

Step6: Read data If no errors occur after send CMD17 (READ\_SINGLE\_BLOCK), read data from EMMC chip (data = SDIC\_BUF0)

Step7: Wait for data transfer end or error occur (SDIC\_INFO1, SDIC\_INFO2)

Step8: Send CMD13 (SEND\_STATUS) with argument RCA to check device status. Detail steps about check EMMC device status please refer to "(3) Check EMMC Device Status" in "Chapter 3.2.2 Operation Details".

#### (4) Compare Data

Compare the read out data with the written data. If same, print OK; otherwise, print error end.

#### 3.4 Example of EMMC Multi Block Operation

In this example, we will write fixed data (0x5A) to EMMC chip (first 16MB data area), then read out and compare whether the data is right. When read/write works OK, erase the first 2MB data area in EMMC chip, then read out and check whether data in first 2MB is zero or not. Both read and write operation will use multi block DMA operation mode.

#### 3.4.1 Operation Flow

Figure 3-4 EMMC Multi block Operation Flow

More details about the functions used in this example please refer to "APPENDIX A EMMC Driver Function"

#### Application Note S19904EJ1V0AN00

#### 3.4.2 Operation Detail

#### (1) Initialization Data Buffer

Initialize the write data buffer, set fixed value (0x5A) to write data buffer which will be wrote to EMMC chip. At the same time, initialize the read data buffer with 0, it will read out data from EMMC chip.

#### (2) Write Data to EMMC

Setting parameters about the data transfer, call the "em1\_emmc\_multi\_write()" function to write data into EMMC chip. Check the write operation, if failed, end the operation and print error information; if OK, continue the test program.

Details about multiple blocks write operation please refer to "figure2-2 EMMA Mobile 1 EMMC Data Transfer in DMA Mode ".

#### (3) Read Data from EMMC

Call "em1\_emmc\_multi\_read()" function to read out the written data by step (2) from EMMC. Check the read operation, if read failed, end the operation and print error; if read OK, continue the test program.

Details about multiple blocks read operation please refer to "figure2-2 EMMA Mobile 1 EMMC Data Transfer in DMA Mode ".

#### (4) Compare Data

Compare the read out data with the written data. If same, print OK; otherwise, print error and end the test.

#### (5) Erase first 2MB in EMMC

Call "em1\_emmc\_erase()" function to erase the first 2MB data area in EMMC. If failed, end the operation and print error; if OK, continue the test program.

Details about EMMC erase operation please refer to "figure2-3 EMMA Mobile 1 EMMC Erase Operation ".

#### (6) Read Data from EMMC

Call "em1\_emmc\_multi\_read()" function to read out the first 2MB data from EMMC. If read failed, end the operation and print error; if read OK, continue the test program.

#### (7) Compare Data

Compare the read out data. If 2MB data are all zero, test operation works OK; otherwise, error end.

#### 3.5 Example of EMMC Write Protect Operation

In write protect operation example, set write protect(WP) to fixed address, then write data, if write operation works normally, it means the WP operation failed, otherwise, the WP operation works OK, then clear the write protect for fixed address, and write operation followed will works normally.

#### 3.5.1 Operation Flow

Figure 3-5 EMMC Write Protect Operation Flow

More details about the functions used in this example please refer to "APPENDIX A EMMC Driver Function"

#### 3.5.2 Operation Detail

#### (1) Set WP to 0x0 Address

Send CMD28(SET\_WRITE\_PROT) to EMMC(function: em1\_emmc\_wp\_manage()), with address 0x0, if command send failed, print error and end test, otherwise, continue the test. Write protect management (m1\_emmc\_wp\_manage()) including following steps:

Step1: Check whether the command is supported

Step2: Send command CMD28/CMD29 (SET\_WRITE\_PROT/ CLR\_WRITE\_PROT) with the argument "write protect unit" (based on unit of WP\_GRP\_SIZE). Detail steps about send command please refer to step 6 of "(2) Init EMMC device" in "Chapter 3.2.2 Operation Details".

#### (2) Write Data to EMMC

Setting parameters about the data transfer, call the "em1\_emmc\_single\_write()" function to write block data into 0x0 in EMMC chip. Check the write operation, if OK, means WP operation failed, end the operation and print error information; if OK, continue the test program.

Details about EMMC single write operation please refer to "(2) Write Data to EMMC" of "Chapter 3.3.2 Operation Detail".

#### (3) Clear WP for 0x0 Address

Send CMD28 (CLR\_WRITE\_PROT) to EMMC(function: em1\_emmc\_wp\_manage()), with address 0x0, if command send failed, print error and end test, otherwise, continue the test. Details about Write protect management please refer to "(1) Set WP to 0x0 Address".

#### (4) Write Data to EMMC

Setting parameters about the data transfer, call the "em1\_emmc\_single\_write()" function to write block data into 0x0 in EMMC chip. Check the write operation, if OK, means WP test operation works OK, otherwise, the WP test failed.

### 3.6 Example of EMMC Lock/Unlock Operation

In lock/unlock example, set password for EMMC at first, then lock the device, check EMMC status, if EMMC is not locked, means lock operation failed, otherwise, lock works OK; then unlock the device, and read the EMMC status again to check the unlock operation.

#### Note:

In this test, use "123" as the password, and before end the lock/unlock test, in order not to affect other tests, should clear the password, and restore the block size (512 byte).

#### 3.6.1 Operation Flow

Figure 3-6 EMMC Lock/Unlock Operation Flow

Application Note S19904EJ1V0AN00

#### 3.6.2 Operation Detail

#### (1) Set Password before Lock

Call function "em1\_emmc\_set\_blklength()" and "em1\_emmc\_lock\_unlock()" to set password before lock the chip, before send command to EMMC, setting the lock/unlock data structure, and make sure the bit0(SET\_PWD) in lock/unlock data structure set to 1. If failed, end the operation and print error information; if OK, continue the test program.

In this test, use "123" as the password contact.

#### Note:

Details about execution of lock/unlock function please refer to "(4) Enforce Erase If EMMC Device Locked" of "Chapter 3.2.2 Operation Details".

#### (2) Lock EMMC

Call function "em1\_emmc\_lock\_unlock()" to lock the EMMC chip, make sure the bit2(Lock/Unlock) in lock/unlock data structure set to 1. If failed, end the operation and print error information; if OK, continue the test program.

#### (3) Check EMMC Chip Status

Call "em1\_emmc\_check\_dev\_status ()" function to check EMMC status. if card is not locked, means lock function failed, end the operation and print error; otherwise, continue the test program.

Detail steps about check EMMC device status please refer to "(3) Check EMMC Device Status" in "Chapter 3.2.2 Operation Details".

#### (4) Unlock EMMC

Call function "em1\_emmc\_lock\_unlock()" to unlock the EMMC chip, make sure the bit2(Lock/Unlock) in lock/unlock data structure set to 0. If failed, end the operation and print error information; if OK, continue the test program.

#### (5) Check EMMC Chip Status

Call "em1\_emmc\_check\_dev\_status ()" function to check EMMC status. if card is still locked, means unlock function failed, end the operation and print error; otherwise, continue the test program.

#### (6) Clear Password

Call function "em1\_emmc\_lock\_unlock()" to clear password, make sure the bit1(CLR\_PWD) in lock/unlock data structure set to 1, "123" as the password contact. If failed, end the operation and print error information; if OK, continue the test program.

#### (7) Set block length to be 512 byte

Before end the lock/unlock test, call function "em1\_emmc\_set\_blklength()" to set block size as 512 byte, if command works OK, end the test normally.

Details about block length setting (em1\_emmc\_set\_blklength()) please refer to step13 of "(2) Init EMMC device" in "Chapter 3.2.2 Operation Details".

#### Note:

More details about lock/unlock data structure and its operation; please refer to "Chapter 4.2.11 moviNAND Lock/Unlock Operation" of EMMC chip user's manual.

More details about the functions used in this example please refer to "APPENDIX A EMMC Driver Function"

# **APPENDIX A EMMC Driver Function**

# A.1 Function List

The following table shows the EMMC driver interface functions:

| Class    | Function Name              | Function Detail                             |

|----------|----------------------------|---------------------------------------------|

|          | em1_emmc_hw_init           | Init the SDM module setting                 |

|          | em1_emmc_init              | EMMC device initialization                  |

|          | em1_emmc_set_seccnt        | Enable/disable sector and set sector number |

|          | em1_emmc_send_cmd          | Send comand                                 |

|          | em1_emmc_set_clk           | Set SDM output clock value                  |

|          | em1_emmc_set_blklength     | Set block length                            |

|          | em1_emmc_select_card       | Select card                                 |

| External | em1_emmc_set_ext_csd       | Set extend CSD register                     |

| function | em1_emmc_check_dev_status  | Check EMMC chip status                      |

|          | em1_emmc_erase             | Erase function                              |

|          | em1_emmc_single_read       | Single block read operation in CPU mode     |

|          | em1_emmc_signle_write      | Single block write operation in CPU mode    |

|          | em1_emmc_multi_read        | Multi block read operation in DMA mode      |

|          | em1_emmc_multi_write       | Multi block write operation in DMA mode     |

|          | em1_emmc_lock_unlock       | Lock/unlolck operation                      |

|          | em1_emmc_wp_manage         | Write protect management                    |

| Internal | _em1_emmc_tranf_prepare    | Prepare before data transfer                |

| function | _em1_emmc_decode_csd       | Decode CSD structure                        |

| TUTICUUT | _em1_emmc_check_rsp_status | Check response status                       |

#### Table A-1 EMMC Driver Function List

# A.2 Global Variable Define

# Table A-2 Global Variable Define

| Name            | Туре   | Detail                           |  |

|-----------------|--------|----------------------------------|--|

| g_RCA_VAL       | ushort | Globle flag for relative address |  |

| g_password_buff | uchar  | Password data structure buffer   |  |

| g_read_buff[]   | uchar  | Read buffer                      |  |

| g_write_buff[]  | uchar  | Write buffer                     |  |

# A.3 Structure Define

#### Table A-3 Structure Define

| Structure Name | Detail                 |

|----------------|------------------------|

| mmc_csd        | CSD register sturcture |

## A.3.1 mmc\_csd

| Member              | Detail                                          |  |  |

|---------------------|-------------------------------------------------|--|--|

|                     | MMC structure version                           |  |  |

| uchar mmca_vsn      |                                                 |  |  |

| ushort cmdclass     | Command classes                                 |  |  |

| ushort tacc_clks    | Read access time in clocks                      |  |  |

| uint tacc_ns        | Read access time in ns                          |  |  |

| uint max_dtr        | Maximum data transfer speed                     |  |  |

| uint read_blkbits   | Read block bits                                 |  |  |

| uint read_blkbits   | Write block bits                                |  |  |

| uint capacity       | Device capacity                                 |  |  |

| uint erase_grp_size | Erase group base size                           |  |  |

| uint erase_grp_mult | Erase group size multipile factor               |  |  |

| uint wp_grp_size    | Write protect froup size                        |  |  |

| uint read_partial   | Whether enable read in partial block            |  |  |

| uint read_misalign  | Whether enable read block cross physical block  |  |  |

|                     | boundaries                                      |  |  |

| uint write_partial  | Whether enable write in partial block           |  |  |

| uint write_misalign | Whether enable write block cross physical block |  |  |

|                     | boundaries                                      |  |  |

#### Table A-4 Structure of mmc\_csd

#### A.4 Function Details

## A.4.1 Hardware Initialization Function

#### [Function Name]

em1\_emmc\_hw\_init

#### [Format]

void em1\_emmc\_hw\_init (void);

#### [Argument]

None

#### [Function Return]

None

## [Flow Chart]

Figure A-1 SDM Hardware Initialization Flow

#### [Note]

1) Switch GPIO which used for EMMC to SD function, users should operate this step according the actual hardware connection.

## A.4.2 EMMC Init Operation

# [Function Name]

em1\_emmc\_init

## [Format]

int em1\_emmc\_init( void ) ;

# [Argument]

None.

## [Function Return]

DRV\_OK

Others: error end

## [Flow Chart]

Figure A-2 EMMC Chip Initialization Flow

#### [Note]

1) Before the initialization of EMMC device, set the bus width to be 1bit and the response time out value to be maximum, reason is: in EMMC identification progress, bus width will use 1bit and the clock frequency should in 10-400 KHz.

2) After setting the clock for SDM transfer, please wait 1ms for stability.

3) After send command, user should check the command response, if error occurred (except when response time out for CMD 2), the initialization will be ended abnormally.

4) After initialization, users can configure the bus width and clock frequency for transfer speed according the CSD parameter of EMMC chip, the transfer speed defines in CSD register just clock frequency not in high speed mode, so the actual transfer speed is related to EMMC chip specification version.

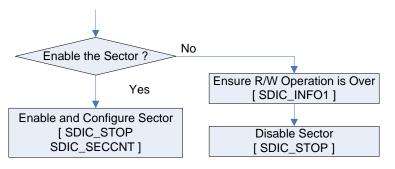

## A.4.3 Sector Setting

## [Function Name]

em1\_emmc\_set\_seccnt

## [Format]

void em1\_emmc\_set\_seccnt(BOOL bEnable, uint sec\_num);

## [Argument]

| Parameter | Туре | I/O | Detail                |

|-----------|------|-----|-----------------------|

| bEnable   | BOOL | Ι   | Enable/disable sector |

| sec_num   | uint | Ι   | Sector number         |

## [Function Return]

None

## [Flow Chart]

Figure A-3 Sector Setting Flow

## [Note]

None

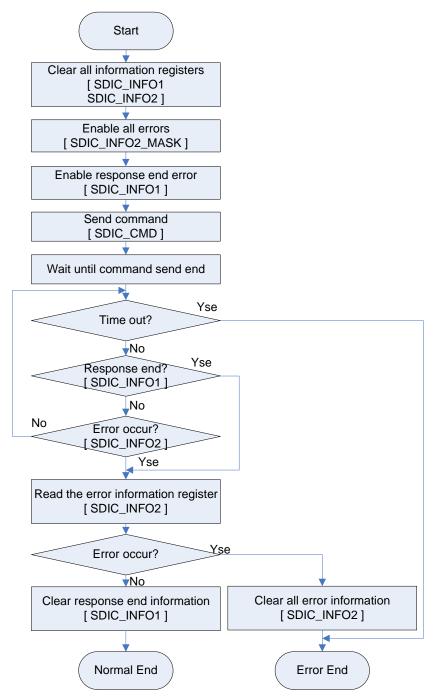

#### A.4.4 Send Command

# [Function Name]

em1\_emmc\_send\_cmd

## [Format]

int em1\_emmc\_send\_cmd (int cmd) ;

## [Argument]

| Parameter | Туре | I/O | Detail                             |

|-----------|------|-----|------------------------------------|

| cmd       | int  | I   | Command index that need to be send |

## [Function Return]

DRV\_OK

Others: error end

Figure A-4 Send Command

#### [Note]

Send command to EMMC chip

#### A.4.5 Set Clock

# [Function Name]

em1\_emmc\_set\_clk

#### [Format]

void em1\_emmc\_set\_clk( ushort value );

## [Argument]

| Parameter | Туре   | I/O | Detail              |

|-----------|--------|-----|---------------------|

| value     | ushort | I   | Clock setting value |

## [Function Return]

None

#### [Flow Chart]

None

#### [Note]

Set SDIx\_CLK\_CTRL register.

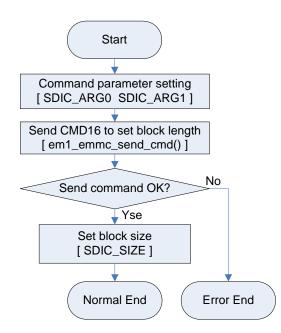

#### A.4.6 Set Block Length

#### [Function Name]

em1\_emmc\_set\_blklength

#### [Format]

int em1\_emmc\_set\_blklength(ushort length);

## [Argument]

| Parameter | Туре   | I/O | Detail                     |

|-----------|--------|-----|----------------------------|

| length    | ushort | I   | Block length setting value |

#### [Function Return]

DRV\_OK

Others: error end

#### [Flow Chart]

Figure A-5 Set Block Length

#### [Note]

Data transfer block length setting.

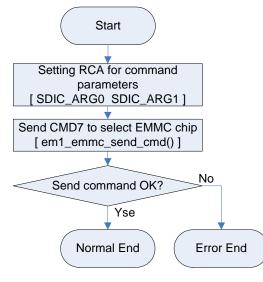

#### A.4.7 Select Card

## [Function Name]

em1\_emmc\_select\_card

## [Format]

int em1\_emmc\_select\_card(uint RCA);

## [Argument]

| Parameter | Туре | I/O | Detail                                       |

|-----------|------|-----|----------------------------------------------|

| RCA       | uint | I   | Relative card address that need to be select |

#### [Function Return]

DRV\_OK

Others: error end

#### [Flow Chart]

Figure A-6 Select Card

## [Note]

None.

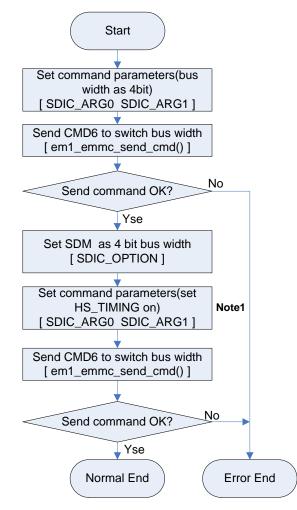

#### A.4.8 Configuration Extend CSD

#### [Function Name]

em1\_emmc\_set\_ext\_csd

## [Format]

int em1\_emmc\_set\_ext\_csd( void ) ;

## [Argument]

None

#### [Function Return]

DRV\_OK

Others: error end

#### [Flow Chart]

Figure A-7 Configure Extend CSD

#### [Note]

Change bus width and other operation mode.

1) Details about extend CSD information, please refer to "Chapter 5.5 Extended CSD

Register" of EMMC chip user's manual

#### A.4.9 Check Device Status

## [Function Name]

em1\_emmc\_check\_dev\_status

## [Format]

int em1\_emmc\_check\_dev\_status ( void );

## [Argument]

None

#### [Function Return]

DRV\_EMMC\_LOCKED

#### DRV\_EMMC\_UNLOCKED

DRV\_ERR\_STATE

#### [Flow Chart]

Figure A-8 Check EMMC Chip Stauts

#### [Note]

Check EMMC chip status register.

#### A.4.10 Erase Function

# [Function Name]

$em1\_emmc\_erase$

# [Format]

int em1\_emmc\_erase(uint str\_addr, uint end\_addr) ;

## [Argument]

| Parameter | Туре | I/O | Detail                          |

|-----------|------|-----|---------------------------------|

| str_addr  | uint | Ι   | Start erase group unit address  |

| end_addr  | uint | I   | End of erase group unit address |

## [Function Return]

DRV\_OK

Others: error end

## [Flow Chart]

Please refer to "figure2-3 EMMA Mobile 1 Erase Operation" in "chapter 2.3 Erase".

## [Note]

None

## A.4.11 Single Block Read

# [Function Name]

em1\_emmc\_single\_read

#### [Format]

int em1\_emmc\_single\_read( uint address, uchar \*data );

# [Argument]

| Parameter | Туре    | I/O | Detail                   |

|-----------|---------|-----|--------------------------|

| address   | uint    | I   | block address to be read |

| data      | uchar * | I/O | read out data buffer     |

## [Function Return]

DRV\_OK

Others: error end

#### [Flow Chart]

Figure A-9 Single Block Read in CPU mode

#### [Note]

None

## A.4.12 Single Block Write

# [Function Name]

em1\_emmc\_single\_write

#### [Format]

int em1\_emmc\_single\_write( uint address, uchar \*data );

# [Argument]

| Parameter | Туре    | I/O | Detail                    |

|-----------|---------|-----|---------------------------|

| address   | uint    | I   | block address to be write |

| data      | uchar * | I/O | Write source data buffer  |

## [Function Return]

DRV\_OK

Others: error end

#### [Flow Chart]

Figure A-10 Single Block Write in CPU mode

#### [Note]

1) During write operation, check SDIC\_INFO2, if buffer write access error occur, end the write operation and return with error information.

#### A.4.13 Multiple Block Read

#### [Function Name]

em1\_emmc\_multi\_read

## [Format]

int em1\_emmc\_multi\_read ( uint address, uchar \*read\_buf, uint blk\_num);

## [Argument]

| Parameter | Туре    | I/O | Detail                   |

|-----------|---------|-----|--------------------------|

| address   | uint    | I   | block address to be read |

| read_buf  | uchar * | I/O | read out data buffer     |

| blk_num   | uint    | I   | block number to be read  |

## [Function Return]

DRV\_OK

Others: error end

## [Flow Chart]

Please refer to "figure2-2 EMMA Mobile 1 EMMC Data Transfer in DMA Mode" in "chapter 2.2

Data Transfer".

## [Note]

None.

#### A.4.14 Multiple Block Write

#### [Function Name]

em1\_emmc\_multi\_write

## [Format]

int em1\_emmc\_multi\_write ( uint address, uchar \* write\_buf, uint blk\_num);

## [Argument]

| Parameter | Туре    | I/O | Detail                    |

|-----------|---------|-----|---------------------------|

| address   | uint    | I   | block address to be write |

| write_buf | uchar * | I/O | write source data buffer  |

| blk_num   | uint    |     | block number to be write  |

## [Function Return]

DRV\_OK

Others: error end

## [Flow Chart]

Please refer to "figure2-2 EMMA Mobile 1 EMMC Data Transfer in DMA Mode" in "chapter 2.2

Data Transfer".

## [Note]

None.

## A.4.15 Lock/Unlock Function

# [Function Name]

em1\_emmc\_lock\_unlock

## [Format]

int em1\_emmc\_lock\_unlock( uchar \*data );

# [Argument]

| Parameter | Туре   | I/O | Detail                     |

|-----------|--------|-----|----------------------------|

| data      | uchar* | Ι   | Lock data structure buffer |

## [Function Return]

DRV\_OK

Others: error end

#### [Flow Chart]

Figure A-11 Lock/Unlock Progress

#### [Note]

1) During write operation, check SDIC\_INFO2, if buffer write access error occur, end the write operation and return with error information.

#### A.4.16 Write Protect Manage

#### [Function Name]

em1\_emmc\_wp\_manage

#### [Format]

int em1\_emmc\_wp\_manage(int cmd, uint addr);

## [Argument]

| Parameter | Туре | I/O | Detail                          |

|-----------|------|-----|---------------------------------|

| cmd       | int  | I   | Write protect command           |

| addr      | uint | I   | Address to be set write protect |

#### [Function Return]

DRV\_OK

Others: error end

#### [Flow Chart]

Figure A-12 Write Protect Management

#### [Note]

None.

#### A.4.17 Transfer Prepare

#### [Function Name]

\_em1\_emmc\_transfer\_prepare

#### [Format]

void \_em1\_emmc\_transfer\_prepare(void);

#### [Argument]

None

#### [Function Return]

None

## [Flow Chart]

Figure A-13 Register Prepare before Data transfer

## [Note]

None.

#### A.4.18 Decode CSD

## [Function Name]

\_em1\_emmc\_decode\_csd

## [Format]

void \_em1\_emmc\_decode\_csd(uint \*raw\_csd);

## [Argument]

| Parameter | Туре | I/O | Detail               |

|-----------|------|-----|----------------------|

| raw_csd   | uint | I   | Raw CSD value buffer |

## [Function Return]

None

#### [Flow Chart]

None

## [Note]

This function will decode the response of SEND\_CSD command; get CSD members that useful for data transfer.

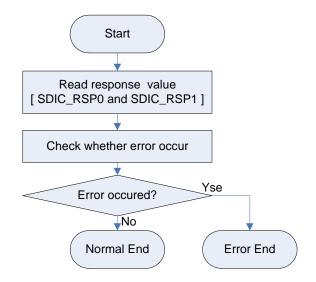

## A.4.19 Check Response Status

## [Function Name]

\_em1\_emmc\_check\_rsp\_status

## [Format]

int \_em1\_emmc\_check\_rsp\_status(void);

## [Argument]

None

## [Function Return]

DRV\_OK

DRV\_ERR\_STATE

#### [Flow Chart]

Figure A-14 Check Response Status

#### [Note]

None

# **APPENDIX B COMMANDS**

Following table shows the simple function of the EMMC chip command which used in this document.

More details about the commands format and function please refer to "**Chapter4.6 Commands**" of the EMMC chip user's manual.

| CMD<br>INDEX | Argument                                                                                               | Abbreviation             | Command Description                                                                                                        |  |

|--------------|--------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| CMD0         | [31:0] stuff bits                                                                                      | GO_IDLE_STATE            | Resets the EMMC chip to idle state                                                                                         |  |

| CMD1         | [31:0] OCR<br>without busy                                                                             | SEND_OP_COND             | Ask chip send its Operating Conditions Register contents.                                                                  |  |

| CMD2         | [31:0] stuff bits                                                                                      | ALL_SEND_CID             | Asks the EMMC chip to send its CID number<br>on the CMD line                                                               |  |

| CMD3         | [31:16] RCA<br>[15:0] stuff bits                                                                       | SET_RELATIVE_A<br>DDR    | Assigns relative address to the EMMC chip                                                                                  |  |

| CMD4         |                                                                                                        | Not                      | Supported                                                                                                                  |  |

| CMD5         |                                                                                                        | R                        | eserved                                                                                                                    |  |

| CMD6         | [31:26] Set to 0<br>[25:24] Access<br>[23:16] Index<br>[15:8] Value<br>[7:3] Set to 0<br>[2:0] Cmd Set | SWITCH                   | Switches operation mode of the selected EMMC chip or modifies the EXT_CSD registers.                                       |  |

| CMD7         | [31:16] RCA<br>[15:0] stuff bits                                                                       | SELECT/DESELEC<br>T_CARD | Select device by its own relative addres<br>and gets deselected by any other address<br>address 0 deselects the EMMC chip. |  |

| CMD8         | [31:0] stuff bits                                                                                      | SEND_EXT_CSD             | The EMMC chip sends its EXT_CSD register as a block of data.                                                               |  |

| CMD9         | [31:16] RCA<br>[15:0] stuff bits                                                                       | SEND_CSD                 | Addressed EMMC chip sends its Card-<br>Specific Data (CSD) on the CMD line.                                                |  |

| CMD10        | [31:16] RCA<br>[15:0] stuff bits                                                                       | SEND_CID                 | Addressed EMMC chip sends its Card Identification (CID) on CMD the line.                                                   |  |

| CMD11        |                                                                                                        | Not                      | Supported                                                                                                                  |  |

| CMD12        | [31:0] stuff bits                                                                                      | STOP_TRANSMIS<br>SION    | Forces the EMMC chip to stop transmission                                                                                  |  |

| CMD13        | [31:16] RCA<br>[15:0] stuff bits                                                                       | SEND_STATUS              | Addressed EMMC chip sends its status register.                                                                             |  |

| CMD14        | [31:0] stuff bits                                                                                      | BUSTEST_R                | A host reads the reversed bus testing data pattern from a EMMC chip.                                                       |  |

| CMD15        | [31:16] RCA<br>[15:0] stuff bits                                                                       | GO_INACTIVE_ST<br>ATE    | Sets the EMMC chip to inactive state                                                                                       |  |

| CMD16        | [31:0] block                                                                                           | SET_BLOCKLEN             | Sets the block length (in bytes) for all                                                                                   |  |

## **Table B-1 Command Description List**

|                | length                                                                                       |                          | following block commands (read and write).                                                                                                  |  |

|----------------|----------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| (              | [31:0] data                                                                                  | READ_SINGLE_BL           | Reads a block of the size selected by the                                                                                                   |  |

| CMD17          | address                                                                                      | OCK                      | SET_BLOCKLEN command                                                                                                                        |  |

| CMD18          | [31:0] data<br>address                                                                       | READ_MULTIPLE_<br>BLOCK  | Multipile block read command                                                                                                                |  |

|                | audress                                                                                      | BLUCK                    | A host sends the bus test data pattern to a                                                                                                 |  |

| CMD19          | [31:0] stuff bits                                                                            | BUSTEST_W                | EMMC chip                                                                                                                                   |  |

| CMD20          |                                                                                              | Not                      | supported                                                                                                                                   |  |

| CMD21<br>CMD22 |                                                                                              | R                        | eserved                                                                                                                                     |  |

|                | [31:16] set to 0<br>[15:0] number<br>of blocks                                               | SET_BLOCK_COU<br>NT      | Defines the number of blocks which are<br>going to be transferred in the immediately<br>succeeding multiple block read or write<br>command. |  |

| CMD24          | [31:0] data<br>address                                                                       | WRITE_BLOCK              | Writes a block of the size selected by the SET_BLOCKLEN command.                                                                            |  |

| CMD25          | [31:0] data<br>address                                                                       | WRITE_MULTIPLE<br>_BLOCK | Continuously writes blocks of data until a STOP_TRANSMISSION follows or the requested number of block received                              |  |

| CMD26          | Not applicable                                                                               |                          |                                                                                                                                             |  |

|                | [31:0] stuff bits                                                                            | PROGRAM_CSD              | Programming of the programmable bits of the CSD                                                                                             |  |

| CMD28          | [31:0] data<br>address                                                                       | SET_WRITE_PROT           | Sets the write protection bit of the addressed group.                                                                                       |  |

| CMD29          | [31:0] data<br>address                                                                       | CLR_WRITE_PRO<br>T       | Clears the write protection bit of the addressed group                                                                                      |  |

| CMD30          | [31:0] write<br>protect data<br>address                                                      | SEND_WRITE_PR<br>OT      | Asks the EMMC chip to send the status of the write protection bits.                                                                         |  |

| CMD31          | Reserved                                                                                     |                          |                                                                                                                                             |  |

| CMD34          |                                                                                              |                          |                                                                                                                                             |  |

| CMD35          | [31:0] data<br>address                                                                       | ERASE_GROUP_S<br>TART    | Sets the address of the first erase group within a range to be selected for erase                                                           |  |

| CMD36          | [31:0] data<br>address                                                                       | ERASE_GROUP_E<br>ND      | Sets the address of the last erase group<br>within a continuous range to be selected for<br>erase                                           |  |

| CMD37          |                                                                                              | R                        | eserved                                                                                                                                     |  |

| CMD38          | [31:0] stuff bits                                                                            | ERASE                    | Erases all previously selected write blocks                                                                                                 |  |

|                | [31:16] RCA<br>[15:15]register<br>write Flag<br>[14:8] register<br>address<br>[7:0] register | FAST_IO                  | Used to write and read 8 bit (register) data fields.                                                                                        |  |

|                | data                                                                                         |                          |                                                                                                                                             |  |

| CMD40          | data<br>[31:0] stuff bits                                                                    | GO_IRQ_STATE             | Sets the system into interrupt mode                                                                                                         |  |

| CMD42 | [31:0] stuff bits. | LOCK_UNLOCK        | Used to set/reset the password or lock/unlock the EMMC chip. The size of the data block is set by the SET_BLOCK_LEN command. |  |

|-------|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| CMD43 |                    |                    |                                                                                                                              |  |

|       | Reserved           |                    |                                                                                                                              |  |

| CMD54 |                    |                    |                                                                                                                              |  |

| CMD55 |                    | MMCA Optional Comm | nand, currently not supported.                                                                                               |  |

| CMD56 |                    |                    |                                                                                                                              |  |

|       |                    | R                  | eserved                                                                                                                      |  |

| CMD59 |                    |                    |                                                                                                                              |  |

# **ANNEX Modification History**

| Number   | Modification Contents | Author | Date       |

|----------|-----------------------|--------|------------|

| Ver 1.00 | New version           |        | Aug,4.2009 |

|          |                       |        |            |

|          |                       |        |            |

|          |                       |        |            |

|          |                       |        |            |

|          |                       |        |            |

|          |                       |        |            |

|          |                       |        |            |

|          |                       |        |            |

|          |                       |        |            |

|          |                       |        |            |