# RA Family IEC 60730/60335 Self Test Library for RA2 MCU (CM23 Class-C)

R01AN7507EJ0100 Rev.1.00 May. 31. 25

# Introduction

Today, as automatic electronic controls systems continue to expand into many diverse applications, the requirement of reliability and safety are becoming an ever-increasing factor in system design.

For example, the introduction of the IEC60730 safety standard for household appliances requires manufactures to design automatic electronic controls that ensure safe and reliable operation of their products.

The IEC60730 standard covers all aspects of product design but Annex H is of key importance for design of Microcontroller based control systems. This provides three software classifications for automatic electronic controls:

- 1. Class A: Control functions, which are not intended to be relied upon for the safety of the equipment. Examples: Room thermostats, humidity controls, lighting controls, timers, and switches.

- 2. Class B: Control functions, which are intended to prevent unsafe operation of the controlled equipment. Examples: Thermal cut-offs and door locks for laundry equipment.

- 3. Class C: Control functions, which are intended to prevent special hazards

Examples: Automatic burner controls and thermal cut-outs for closed.

This Application Note provides guidelines of how to use flexible sample software routines to assist with compliance with IEC60730 class C safety standards. These routines have been certified by VDE Test and Certification Institute GmbH and a copy of the Test Certificate is available in the download package for this Application Note.

The software routines provided are to be used after reset and also during the program execution. This document and the accompanying sample code provide an example of how to do this.

# Target

- Device:

- Renesas RA Family (Arm<sup>®</sup> Cortex<sup>®</sup>-M23) \* See **Table a** for series and groups.

- Development environment:

- GNU-GCC ARM Embedded Toolchain12.2.1.arm-12-mpacbti-34 / Renesas e2 studio 2023-10 (23.10.0)

The term "RA MCU" used in this document refers to the following products.

| Table a: RA | MCU | Self-Test | <b>Function List</b> |

|-------------|-----|-----------|----------------------|

|-------------|-----|-----------|----------------------|

|          | CPU Core                          | Arm <sup>®</sup> Cortex®-M23 |

|----------|-----------------------------------|------------------------------|

|          | Series                            | RA2                          |

|          | Group                             | RA2E1/RA2L1*                 |

| L        | CPU                               | 0                            |

| Function | ROM                               | 0                            |

| Fun      | RAM                               | 0                            |

| Test     | Clock                             | 0                            |

| Т        | Independent Watchdog Timer (IWDT) | 0                            |

\*: the difference between RA2E1 and RA2L1 is the size of ROM/RAM.

# Self-test library overview

The self-test library consists of instruction decoding, CPU registers, internal memory, watchdog timer, and monitoring functions for the system clock.

As described below, the anomaly monitoring process provides an application program interface (API) for each module that monitors. Use each function according to the purpose.

The self-test library functions are divided into modules according to IEC60730Class-C. The anomaly monitoring process can be performed standalone by selecting each test function in turn.

The RA2 series (with Arm® Cortex®-M23) self-test library implement functions of the following main self-testing.

• Instruction decoding

Verify that the corresponding instruction of Arm Cortex-M23 works properly according to the specifications.

See "IEC 60730-1:2013+A1:2015+A2:2020 Annex H - H2.18.5 equivalence class test".

CPU Register

Test the CPU registers listed in "**Table 1.1** CPU Test target (Overview) ". The internal data path is verified during the normal operation test of the above registers. See "IEC 60730-1:2013+A1:2015+A2:2020 Annex H - Table H.11.12.7 1.CPU".

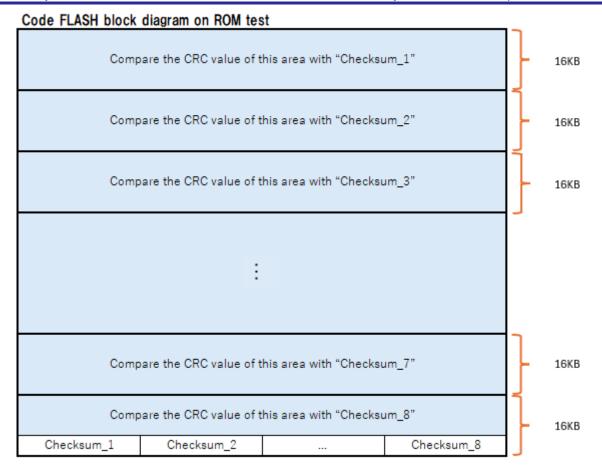

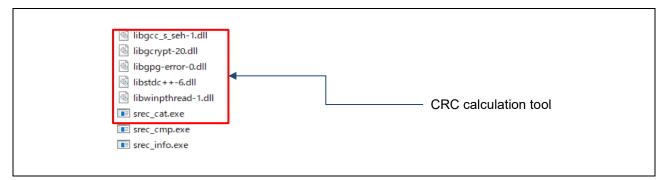

• Invariable memory

Test the internal Flash memory of the MCU. See "IEC 60730-1:2013+A1:2015+A2:2020 Annex H - H2.19.4.2 CRC – double word".

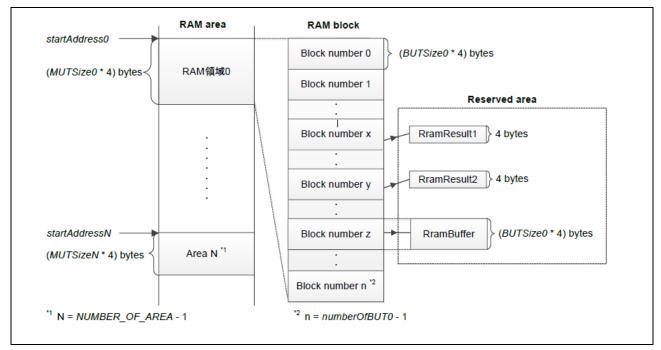

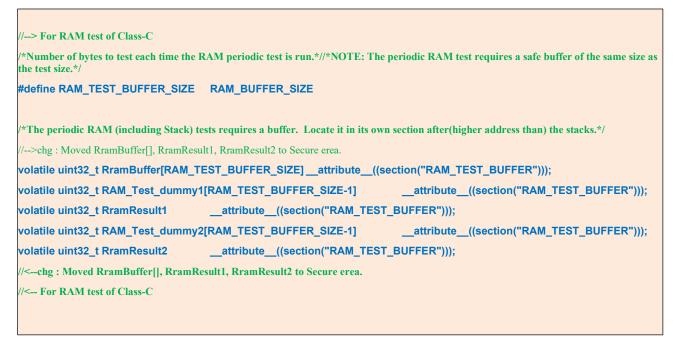

• Variable memory

Test Internal SRAM The RAM test uses the Word-oriented Memory Test and the Extended March C-algorithm. See "IEC 60730-1:2013+A1:2015+A2:2020 Annex H - H.2.19.7 walkpat memory test".

System Clock

Test the operation and frequency of the system clock based on the reference clock source (this test requires an independent internal or external reference clock). See "IEC Reference - IEC 60730-1:2013+A1:2015+A2:2020 Annex H - H2.18.10.1 Frequency monitoring".

• CPU / Program Counter(PC)

To confirm that the program is executing the sequence within the specified time, it is confirmed using the built-in watchdog timer that operates with a clock independent of the CPU. See "IEC 60730-1:2013+A1:2015+A2:2020 Annex H – H2.18.10.3 independent time-slot and logical monitoring".

# **Table of Contents**

| Intro | duction                           | 1  |

|-------|-----------------------------------|----|

| Tab   | le of Contents                    | 5  |

| 1.    | Tests                             | 6  |

| 1.1   | CPU                               | 6  |

| 1.2   | ROM                               | 38 |

| 1.3   | RAM                               | 43 |

| 1.4   | Clock                             | 53 |

| 1.5   | Independent Watchdog Timer (IWDT) | 56 |

| 2.    | Example Usage                     | 59 |

| 2.1   | CPU                               | 60 |

| 2.2   | ROM                               | 62 |

| 2.3   | RAM                               | 71 |

| 2.4   | Clock                             | 72 |

| 2.5   | Independent Watchdog Timer (IWDT) | 74 |

| Web   | osite and Support                 | 78 |

| Refe  | erence Documents                  | 78 |

| Rev   | ision History                     | 79 |

# 1. Tests

# 1.1 CPU

The objective of the CPU test is to detect random permanent faults from CPU core. Main functions of CPU Test are described below.

- CPU instruction test

- CPU register test

# 1.1.1 CPU instruction test and CPU register test

**Table 1.16** describes the outline of each test of the CPU test performed by this self-test library. The related registers and instruction codes are tested by executing each test, and by checking the execution results, CPU fault can be detected.

Test target (Overview) are CPU instructions and registers listed in Table 1.1.

Table 1.1 CPU Test target(Overview)

|             | Test target                               |          | Arm <sup>®</sup> Cortex <sup>®</sup> -M23(CM23) |

|-------------|-------------------------------------------|----------|-------------------------------------------------|

| Instruction | Profile                                   |          | ARMv8-M                                         |

|             |                                           | Baseline |                                                 |

|             | Instruction set                           |          | Cortex-M23                                      |

|             |                                           |          | Instruction Set                                 |

|             | DSP                                       |          | N/A*                                            |

|             | FSP                                       | N/A      |                                                 |

| Register    | General purpose registers                 | R0 – R12 | √                                               |

|             | Stack Pointer                             | SP(R13)  | $\checkmark$                                    |

|             | Link Register                             | LR(R14)  | $\checkmark$                                    |

|             | Program Counter                           | PC(R15)  | $\checkmark$                                    |

|             | Single-precision Floating-point Registers | S0 - S31 | N/A                                             |

|             | Floating-point Status Control Register    | FPSCR    | N/A                                             |

|             | Application Program Status Register       | APSR     | $\checkmark$                                    |

\* N/A: not available.

**RA** Family

The list of the Armv8-M registers and their test support status is listed in the below "**Table 1.2** - **Table 1.3**". See the "Arm®v8-M Architecture Reference Manual" (<u>Reference Document [2]</u>) for detailed information on each register.

[Notation]

| 1       | : To be tested     |

|---------|--------------------|

| (blank) | : Not to be tested |

N/A : Not applicable

# Table 1.2 Armv8-M Registers Tested/Not Tested by CPU Test (1 of 2)

| No. | Component       | Register       | Description                                       | Tested by<br>CPU test |

|-----|-----------------|----------------|---------------------------------------------------|-----------------------|

| 1   | Special and     | APSR           | Application Program Status Register               | 1                     |

|     | general-purpose | BASEPRI        | Base Priority Mask Register                       | N/A                   |

|     | registers       | CONTROL        | Control Register                                  |                       |

|     |                 | EPSR           | Execution Program Status Register                 |                       |

|     |                 | FAULTMASK      | Fault Mask Register                               | N/A                   |

|     |                 | FPSCR          | Floating-point Status and Control Register        | N/A                   |

|     |                 | IPSR           | Interrupt Program Status Register                 |                       |

|     |                 | LO_BRANCH_INFO | Loop and branch tracking information              | N/A                   |

|     |                 | LR(R14)        | Link Register                                     | 1                     |

|     |                 | MSPLIM         | Main Stack Pointer Limit Register                 |                       |

|     |                 | PC(R15)        | Program Counter                                   | 1                     |

|     |                 | PRIMASK        | Exception Mask Register                           |                       |

|     |                 | PSPLIM         | Process Stack Pointer Limit Register              |                       |

|     |                 | Rn (R0 - R12)  | General-Purpose Register n                        | 1                     |

|     |                 | SP (R13)       | Current Stack Pointer Register                    | 1                     |

|     |                 | SP             | Stack Pointer (Non-secure)                        |                       |

|     |                 | S0 – S31       | Single-precision Floating-point<br>Registers      | 1                     |

|     |                 | VPR            | Vector Predication Status and<br>Control Register | N/A                   |

|     |                 | XPSR           | Combined Program Status Registers                 |                       |

| No. | Component                                                                                                               | Register      | Tested by |

|-----|-------------------------------------------------------------------------------------------------------------------------|---------------|-----------|

| NO. | Component                                                                                                               | rtegister     | CPU test  |

| 2   | Payloads                                                                                                                | All registers |           |

| 3   | Instrumentation Macrocell                                                                                               | All registers |           |

| 4   | Data Watchpoint and Trace                                                                                               | All registers |           |

| 5   | Flash Patch and Breakpoint                                                                                              | All registers |           |

| 6   | Performance Monitoring Unit                                                                                             | All registers | N/A       |

| 7   | Reliability, Availability and Serviceability Extension Fault Status Register (Registers starting at address 0xE0005000) | All registers | N/A       |

| 8   | Implementation Control Block                                                                                            | All registers |           |

| 9   | SysTick Timer                                                                                                           | All registers |           |

| 10  | Nested Vectored Interrupt Controller                                                                                    | All registers |           |

| 11  | System Control Block                                                                                                    | All registers |           |

| 12  | Memory Protection Unit                                                                                                  | All registers |           |

| 13  | Security Attribution Unit                                                                                               | All registers |           |

| 14  | Debug Control Block                                                                                                     | All registers |           |

| 15  | Software Interrupt Generation                                                                                           | All registers |           |

| 16  | Reliability, Availability and Serviceability Extension Fault Status Register (Registers starting at address 0xE000EF04) | All registers |           |

| 17  | Floating-Point Extension                                                                                                | All registers |           |

| 18  | Cache Maintenance Operations                                                                                            | All registers |           |

| 19  | Debug Identification Block                                                                                              | All registers |           |

| 20  | Implementation Control Block (NS alias)                                                                                 | All registers |           |

| 21  | SysTick Timer (NS alias)                                                                                                | All registers |           |

| 22  | Nested Vectored Interrupt Controller (NS alias)                                                                         | All registers |           |

| 23  | System Control Block (NS alias)                                                                                         | All registers |           |

| 24  | Memory Protection Unit (NS alias)                                                                                       | All registers |           |

| 25  | Debug Control Block (NS alias)                                                                                          | All registers |           |

| 26  | Software Interrupt Generation (NS alias)                                                                                | All registers |           |

| 27  | Reliability, Availability and Serviceability Extension Fault Status Register (NS Alias)                                 | All registers |           |

| 28  | Floating-Point Extension (NS alias)                                                                                     | All registers |           |

| 29  | Cache Maintenance Operations (NS alias)                                                                                 | All registers |           |

| 30  | Debug Identification Block (NS alias)                                                                                   | All registers |           |

| 31  | Trace Port Interface Unit                                                                                               | All registers |           |

# Table 1.3 Armv8-M Registers Tested/Not Tested by CPU Test (2 of 2)

**RA** Family

The list of the Armv8-M instructions and their test support status is listed in the below "**Table 1.4 - Table 1.13**"<sup>1</sup>.

See the "Arm® Cortex®-M23 Devices Generic User Guide " (<u>Reference Document [1]</u>) for detailed information on each instruction.

Note that the main purpose is not to test individual instructions, but to detect random permanent failure of the CPU core.

#### [Notation]

✓ : To be tested

(blank) : Not to be tested

N/A : Not applicable

: Not tested but fault is detected in conjunction with the other instruction (The mnemonic of target instruction is tested by the other instruction encoding (see "Arm®v8-M Architecture Reference Manual") and instruction encoding of the target instruction is tested by the other instruction)

Please note the primary aim is not to test individual instructions but to detect random permanent failure of the CPU core.

| No. | Instruction                | Tested by<br>CPU test | No. | Instruction     | Tested by<br>CPU test |

|-----|----------------------------|-----------------------|-----|-----------------|-----------------------|

| 1   | ADC (immediate)            | N/A                   | 21  | BFC             | N/A                   |

| 2   | ADC (register)             | $\checkmark$          | 22  | BFI             | N/A                   |

| 3   | ADD (SP plus immediate)    | $\checkmark$          | 23  | BIC (immediate) | N/A                   |

| 4   | ADD (SP plus register)     | *                     | 24  | BIC (register)  | $\checkmark$          |

| 5   | ADD (immediate)            | *                     | 25  | ВКРТ            |                       |

| 6   | ADD (immediate, to PC)     | *                     | 26  | BL              | $\checkmark$          |

| 7   | ADD (register)             | $\checkmark$          | 27  | BLX, BLXNS      | $\checkmark$          |

| 8   | ADR                        | $\checkmark$          | 28  | BTI             | N/A                   |

| 9   | AND (immediate)            | N/A                   | 29  | BX, BXNS        | $\checkmark$          |

| 10  | AND (register)             | $\checkmark$          | 30  | BXAUT           | N/A                   |

| 11  | ASR (immediate)            | N/A                   | 31  | CBNZ, CBZ       | $\checkmark$          |

| 12  | ASR (register)             | N/A                   | 32  | CDP, CDP2       | N/A                   |

| 13  | ASRL (immediate)           | N/A                   | 33  | CINC            | N/A                   |

| 14  | ASRL (register)            | N/A                   | 34  | CINV            | N/A                   |

| 15  | ASRS (immediate)           | *                     | 35  | CLREX           | $\checkmark$          |

| 16  | ASRS (register)            | $\checkmark$          | 36  | CLRM            | N/A                   |

| 17  | AUT                        | N/A                   | 37  | CLZ             | N/A                   |

| 18  | AUTG                       | N/A                   | 38  | CMN (immediate) | N/A                   |

| 19  | В                          | $\checkmark$          | 39  | CMN (register)  | $\checkmark$          |

| 20  | BF, BFX, BFL, BFLX, BFCSEL | N/A                   | 40  | CMP (immediate) | *                     |

Table 1.4 Armv8-M Instructions Tested/Not Tested by CPU Test (1 of 10)

# Table 1.5 Armv8-M Instructions Tested/Not Tested by CPU Test (2 of 10)

| No. | Instruction      | Tested by<br>CPU test | No. | Instruction           | Tested by<br>CPU test |

|-----|------------------|-----------------------|-----|-----------------------|-----------------------|

| 41  | CMP (register)   | $\checkmark$          | 71  | LDAEXB                | $\checkmark$          |

| 42  | CNEG             | N/A                   | 72  | LDAEXH                | $\checkmark$          |

| 43  | CPS              |                       | 73  | LDAH                  | $\checkmark$          |

| 44  | CSDB             | N/A                   | 74  | LDC, LDC2 (immediate) | N/A                   |

| 45  | CSEL             | N/A                   | 75  | LDC, LDC2 (literal)   | N/A                   |

| 46  | CSET             | N/A                   | 76  | LDM, LDMIA, LDMFD     | $\checkmark$          |

| 47  | CSETM            | N/A                   | 77  | LDMDB, LDMEA          | N/A                   |

| 48  | CSINC            | N/A                   | 78  | LDR (immediate)       | $\checkmark$          |

| 49  | CSINV            | N/A                   | 79  | LDR (literal)         | *                     |

| 50  | CSNEG            | N/A                   | 80  | LDR (register)        | $\checkmark$          |

| 51  | CX1              | N/A                   | 81  | LDRB (immediate)      | $\checkmark$          |

| 52  | CX1D             | N/A                   | 82  | LDRB (literal)        | N/A                   |

| 53  | CX2              | N/A                   | 83  | LDRB (register)       | *                     |

| 54  | CX2D             | N/A                   | 84  | LDRBT                 | N/A                   |

| 55  | CX3              | N/A                   | 85  | LDRD (immediate)      | N/A                   |

| 56  | CX3D             | N/A                   | 86  | LDRD (literal)        | N/A                   |

| 57  | DBG              | N/A                   | 87  | LDREX                 | $\checkmark$          |

| 58  | DMB              |                       | 88  | LDREXB                | $\checkmark$          |

| 59  | DSB              |                       | 89  | LDREXH                | $\checkmark$          |

| 60  | EOR (immediate)  | N/A                   | 90  | LDRH (immediate)      | $\checkmark$          |

| 61  | EOR (register)   | $\checkmark$          | 91  | LDRH (literal)        | N/A                   |

| 62  | ESB              | N/A                   | 92  | LDRH (register)       | *                     |

| 63  | FLDMDBX, FLDMIAX | N/A                   | 93  | LDRHT                 | N/A                   |

| 64  | FSTMDBX, FSTMIAX | N/A                   | 94  | LDRSB (immediate)     | N/A                   |

| 65  | ISB              |                       | 95  | LDRSB (literal)       | N/A                   |

| 66  | IT               | N/A                   | 96  | LDRSB (register)      | $\checkmark$          |

| 67  | LCTP             | N/A                   | 97  | LDRSBT                | N/A                   |

| 68  | LDA              | $\checkmark$          | 98  | LDRSH (immediate)     | N/A                   |

| 69  | LDAB             | $\checkmark$          | 99  | LDRSH (literal)       | N/A                   |

| 70  | LDAEX            | $\checkmark$          | 100 | LDRSH (register)      | √                     |

# Table 1.6 Armv8-M Instructions Tested/Not Tested by CPU Test (3 of 10)

| No. | Instruction                           | Tested by<br>CPU test | No. | Instruction               | Tested by<br>CPU test |

|-----|---------------------------------------|-----------------------|-----|---------------------------|-----------------------|

| 101 | LDRSHT                                | N/A                   | 131 | ORN (immediate)           | N/A                   |

| 102 | LDRT                                  | N/A                   | 132 | ORN (register)            | N/A                   |

| 103 | LE, LETP                              | N/A                   | 133 | ORR (immediate)           | N/A                   |

| 104 | LSL (immediate)                       | N/A                   | 134 | ORR (register)            | $\checkmark$          |

| 105 | LSL (register)                        | N/A                   | 135 | PAC                       | N/A                   |

| 106 | LSLL (immediate)                      | N/A                   | 136 | PACBTI                    | N/A                   |

| 107 | LSLL (register)                       | N/A                   | 137 | PACG                      | N/A                   |

| 108 | LSLS (immediate)                      | *                     | 138 | PKHBT, PKHTB              | N/A                   |

| 109 | LSLS (register)                       | $\checkmark$          | 139 | PLD (literal)             | N/A                   |

| 110 | LSR (immediate)                       | N/A                   | 140 | PLD, PLDW (immediate)     | N/A                   |

| 111 | LSR (register)                        | N/A                   | 141 | PLD, PLDW (register)      | N/A                   |

| 112 | LSRL (immediate)                      | N/A                   | 142 | PLI (immediate, literal)  | N/A                   |

| 113 | LSRS (immediate)                      | *                     | 143 | PLI (register)            | N/A                   |

| 114 | LSRS (register)                       | $\checkmark$          | 144 | POP (multiple registers)  | $\checkmark$          |

| 115 | MCR, MCR2                             | N/A                   | 145 | POP (single register)     | N/A                   |

| 116 | MCRR, MCRR2                           | N/A                   | 146 | PSSBB                     | N/A                   |

| 117 | MLA                                   | N/A                   | 147 | PUSH (multiple registers) | $\checkmark$          |

| 118 | MLS                                   | N/A                   | 148 | PUSH (single register)    | N/A                   |

| 119 | MOV (immediate)                       | $\checkmark$          | 149 | QADD                      | N/A                   |

| 120 | MOV (register)                        | *                     | 150 | QADD16                    | N/A                   |

| 121 | MOV, MOVS (register-shifted register) | *                     | 151 | QADD8                     | N/A                   |

| 122 | MOVT                                  | $\checkmark$          | 152 | QASX                      | N/A                   |

| 123 | MRC, MRC2                             | N/A                   | 153 | QDADD                     | N/A                   |

| 124 | MRRC, MRRC2                           | N/A                   | 154 | QDSUB                     | N/A                   |

| 125 | MRS                                   | $\checkmark$          | 155 | QSAX                      | N/A                   |

| 126 | MSR (register)                        | $\checkmark$          | 156 | QSUB                      | N/A                   |

| 127 | MUL                                   | √                     | 157 | QSUB16                    | N/A                   |

| 128 | MVN (immediate)                       | N/A                   | 158 | QSUB8                     | N/A                   |

| 129 | MVN (register)                        | √                     | 159 | RBIT                      | N/A                   |

| 130 | NOP                                   |                       | 160 | REV                       | √                     |

# Table 1.7 Armv8-M Instructions Tested/Not Tested by CPU Test (4 of 10)

| No. | Instruction                           | Tested by<br>CPU test | No. | Instruction                       | Tested by<br>CPU test |

|-----|---------------------------------------|-----------------------|-----|-----------------------------------|-----------------------|

| 161 | REV16                                 | $\checkmark$          | 191 | SMLALD, SMLALDX                   | N/A                   |

| 162 | REVSH                                 | $\checkmark$          | 192 | SMLAWB, SMLAWT                    | N/A                   |

| 163 | ROR (immediate)                       | N/A                   | 193 | SMLSD, SMLSDX                     | N/A                   |

| 164 | ROR (register)                        | N/A                   | 194 | SMLSLD, SMLSLDX                   | N/A                   |

| 165 | RORS (immediate)                      | N/A                   | 195 | SMMLA, SMMLAR                     | N/A                   |

| 166 | RORS (register)                       | $\checkmark$          | 196 | SMMLS, SMMLSR                     | N/A                   |

| 167 | RRX                                   | N/A                   | 197 | SMMUL, SMMULR                     | N/A                   |

| 168 | RRXS                                  | N/A                   | 198 | SMUAD, SMUADX                     | N/A                   |

| 169 | RSB (immediate)                       | $\checkmark$          | 199 | SMULBB, SMULBT, SMULTB,<br>SMULTT | N/A                   |

| 170 | RSB (register)                        | N/A                   | 200 | SMULL                             | N/A                   |

| 171 | SADD16                                | N/A                   | 201 | SMULWB, SMULWT                    | N/A                   |

| 172 | SADD8                                 | N/A                   | 202 | SMUSD, SMUSDX                     | N/A                   |

| 173 | SASX                                  | N/A                   | 203 | SQRSHR (register)                 | N/A                   |

| 174 | SBC (immediate)                       | N/A                   | 204 | SQRSHRL (register)                | N/A                   |

| 175 | SBC (register)                        | $\checkmark$          | 205 | SQSHL (immediate)                 | N/A                   |

| 176 | SBFX                                  | N/A                   | 206 | SQSHLL (immediate)                | N/A                   |

| 177 | SDIV                                  | $\checkmark$          | 207 | SRSHR (immediate)                 | N/A                   |

| 178 | SEL                                   | N/A                   | 208 | SRSHRL (immediate)                | N/A                   |

| 179 | SEV                                   |                       | 209 | SSAT                              | N/A                   |

| 180 | SG                                    |                       | 210 | SSAT16                            | N/A                   |

| 181 | SHADD16                               | N/A                   | 211 | SSAX                              | N/A                   |

| 182 | SHADD8                                | N/A                   | 212 | SSBB                              | N/A                   |

| 183 | SHASX                                 | N/A                   | 213 | SSUB16                            | N/A                   |

| 184 | SHSAX                                 | N/A                   | 214 | SSUB8                             | N/A                   |

| 185 | SHSUB16                               | N/A                   | 215 | STC, STC2                         | N/A                   |

| 186 | SHSUB8                                | N/A                   | 216 | STL                               | $\checkmark$          |

| 187 | SMLABB, SMLABT, SMLATB,<br>SMLATT     | N/A                   | 217 | STLB                              | ~                     |

| 188 | SMLAD, SMLADX                         | N/A                   | 218 | STLEX                             | $\checkmark$          |

| 189 | SMLAL                                 | N/A                   | 219 | STLEXB                            | $\checkmark$          |

| 190 | SMLALBB, SMLALBT, SMLALTB,<br>SMLALTT | N/A                   | 220 | STLEXH                            | √                     |

# Table 1.8 Armv8-M Instructions Tested/Not Tested by CPU Test (5 of 10)

| No. | Instruction              | Tested by<br>CPU test | No. | Instruction        | Tested by<br>CPU test |

|-----|--------------------------|-----------------------|-----|--------------------|-----------------------|

| 221 | STLH                     | $\checkmark$          | 251 | TEQ (register)     | N/A                   |

| 222 | STM, STMIA, STMEA        | $\checkmark$          | 252 | TST (immediate)    | N/A                   |

| 223 | STMDB, STMFD             | N/A                   | 253 | TST (register)     | $\checkmark$          |

| 224 | STR (immediate)          | $\checkmark$          | 254 | TT, TTT, TTA, TTAT |                       |

| 225 | STR (register)           | *                     | 255 | UADD16             | N/A                   |

| 226 | STRB (immediate)         | $\checkmark$          | 256 | UADD8              | N/A                   |

| 227 | STRB (register)          | $\checkmark$          | 257 | UASX               | N/A                   |

| 228 | STRBT                    | N/A                   | 258 | UBFX               | N/A                   |

| 229 | STRD (immediate)         | N/A                   | 259 | UDF                |                       |

| 230 | STREX                    | $\checkmark$          | 260 | UDIV               | $\checkmark$          |

| 231 | STREXB                   | $\checkmark$          | 261 | UHADD16            | N/A                   |

| 232 | STREXH                   | $\checkmark$          | 262 | UHADD8             | N/A                   |

| 233 | STRH (immediate)         | $\checkmark$          | 263 | UHASX              | N/A                   |

| 234 | STRH (register)          | $\checkmark$          | 264 | UHSAX              | N/A                   |

| 235 | STRHT                    | N/A                   | 265 | UHSUB16            | N/A                   |

| 236 | STRT                     | N/A                   | 266 | UHSUB8             | N/A                   |

| 237 | SUB (SP minus immediate) | $\checkmark$          | 267 | UMAAL              | N/A                   |

| 238 | SUB (SP minus register)  | N/A                   | 268 | UMLAL              | N/A                   |

| 239 | SUB (immediate)          | $\checkmark$          | 269 | UMULL              | N/A                   |

| 240 | SUB (immediate, from PC) | N/A                   | 270 | UQADD16            | N/A                   |

| 241 | SUB (register)           | *                     | 271 | UQADD8             | N/A                   |

| 242 | SVC                      |                       | 272 | UQASX              | N/A                   |

| 243 | SXTAB                    | N/A                   | 273 | UQRSHL (register)  | N/A                   |

| 244 | SXTAB16                  | N/A                   | 274 | UQRSHLL (register) | N/A                   |

| 245 | SXTAH                    | N/A                   | 275 | UQSAX              | N/A                   |

| 246 | SXTB                     | $\checkmark$          | 276 | UQSHL (immediate)  | N/A                   |

| 247 | SXTB16                   | N/A                   | 277 | UQSHLL (immediate) | N/A                   |

| 248 | SXTH                     | $\checkmark$          | 278 | UQSUB16            | N/A                   |

| 249 | TBB, TBH                 | N/A                   | 279 | UQSUB8             | N/A                   |

| 250 | TEQ (immediate)          | N/A                   | 280 | URSHR (immediate)  | N/A                   |

| No. | Instruction           | Tested by<br>CPU test | No. | Instruction           | Tested by<br>CPU test |

|-----|-----------------------|-----------------------|-----|-----------------------|-----------------------|

| 281 | URSHRL (immediate)    | N/A                   | 301 | VADC                  | N/A                   |

| 282 | USAD8                 | N/A                   | 302 | VADD (floating-point) | N/A                   |

| 283 | USADA8                | N/A                   | 303 | VADD (vector)         | N/A                   |

| 284 | USAT                  | N/A                   | 304 | VADD                  | N/A                   |

| 285 | USAT16                | N/A                   | 305 | VADDLV                | N/A                   |

| 286 | USAX                  | N/A                   | 306 | VADDV                 | N/A                   |

| 287 | USUB16                | N/A                   | 307 | VAND (immediate)      | N/A                   |

| 288 | USUB8                 | N/A                   | 308 | VAND                  | N/A                   |

| 289 | UXTAB                 | N/A                   | 309 | VBIC (immediate)      | N/A                   |

| 290 | UXTAB16               | N/A                   | 310 | VBIC (register)       | N/A                   |

| 291 | UXTAH                 | N/A                   | 311 | URSHRL (immediate)    | N/A                   |

| 292 | UXTB                  | $\checkmark$          | 312 | USAD8                 | N/A                   |

| 293 | UXTB16                | N/A                   | 313 | USADA8                | N/A                   |

| 294 | UXTH                  | $\checkmark$          | 314 | USAT                  | N/A                   |

| 295 | VABAV                 | N/A                   | 315 | USAT16                | N/A                   |

| 296 | VABD (floating-point) | N/A                   | 316 | USAX                  | N/A                   |

| 297 | VABD                  | N/A                   | 317 | USUB16                | N/A                   |

| 298 | VABS (floating-point) | N/A                   | 318 | USUB8                 | N/A                   |

| 299 | VABS (vector)         | N/A                   | 319 | UXTAB                 | N/A                   |

| 300 | VABS                  | N/A                   | 320 | UXTAB16               | N/A                   |

# Table 1.9 Armv8-M Instructions Tested/Not Tested by CPU Test (6 of 10)

# Table 1.10 Armv8-M Instructions Tested/Not Tested by CPU Test (7 of 10)

| No. | Instruction           | Tested by<br>CPU test | No. | Instruction                                             | Tested by<br>CPU test |

|-----|-----------------------|-----------------------|-----|---------------------------------------------------------|-----------------------|

| 321 | UXTAH                 | N/A                   | 346 | VDUP                                                    | N/A                   |

| 322 | UXTB                  | √                     | 347 | VEOR                                                    | N/A                   |

| 323 | UXTB16                | N/A                   | 348 | VFMA (vector by scalar plus vector, floating-point)     | N/A                   |

| 324 | UXTH                  | $\checkmark$          | 349 | VFMA                                                    | N/A                   |

| 325 | VABAV                 | N/A                   | 350 | VFMA, VFMS (floating-point)                             | N/A                   |

| 326 | VABD (floating-point) | N/A                   | 351 | VFMAS (vector by vector plus<br>scalar, floating-point) | N/A                   |

| 327 | VABD                  | N/A                   | 352 | VFMS                                                    | N/A                   |

| 328 | VABS (floating-point) | N/A                   | 353 | VFNMA                                                   | N/A                   |

| 329 | VABS (vector)         | N/A                   | 354 | VFNMS                                                   | N/A                   |

| 330 | VABS                  | N/A                   | 355 | VHADD                                                   | N/A                   |

| 331 | VADC                  | N/A                   | 356 | VHCADD                                                  | N/A                   |

| 332 | VADD (floating-point) | N/A                   | 357 | VHSUB                                                   | N/A                   |

| 333 | VADD (vector)         | N/A                   | 358 | VIDUP, VIWDUP                                           | N/A                   |

| 334 | VADD                  | N/A                   | 359 | VINS                                                    | N/A                   |

| 335 | VADDLV                | N/A                   | 360 | VLD2                                                    | N/A                   |

| 336 | VADDV                 | N/A                   | 361 | VLD4                                                    | N/A                   |

| 337 | VAND (immediate)      | N/A                   | 362 | VLDM                                                    | N/A                   |

| 338 | VAND                  | N/A                   | 363 | VLDR (System Register)                                  | N/A                   |

| 339 | VBIC (immediate)      | N/A                   | 364 | VLDR                                                    | N/A                   |

| 340 | VBIC (register)       | N/A                   | 365 | VLDRB, VLDRH, VLDRW                                     | N/A                   |

| 341 | VCX2 (vector)         | N/A                   | 366 | VLDRB, VLDRH, VLDRW, VLDRD<br>(vector)                  | N/A                   |

| 342 | VCX3                  | N/A                   | 367 | VLLDM                                                   | N/A                   |

| 343 | VCX3 (vector)         | N/A                   | 368 | VLSTM                                                   | N/A                   |

| 344 | VDDUP, VDWDUP         | N/A                   | 369 | VMAX, VMAXA                                             | N/A                   |

| 345 | VDIV                  | N/A                   | 370 | VMAXNM                                                  | N/A                   |

# Table 1.11 Armv8-M Instructions Tested/Not Tested by CPU Test (8 of 10)

| No. | Instruction                            | Tested by<br>CPU test | No. | Instruction                                                                             | Tested by<br>CPU test |

|-----|----------------------------------------|-----------------------|-----|-----------------------------------------------------------------------------------------|-----------------------|

| 371 | VMAXNM, VMAXNMA (floating-<br>point)   | N/A                   | 386 | VMLS                                                                                    | N/A                   |

| 372 | VMAXNMV, VMAXNMAV (floating-<br>point) | N/A                   | 387 | VMLSDAV                                                                                 | N/A                   |

| 373 | VMAXV, VMAXAV                          | N/A                   | 388 | VMLSLDAV                                                                                | N/A                   |

| 374 | VMIN, VMINA                            | N/A                   | 389 | VMOV (between general-purpose register and half-precision register)                     | N/A                   |

| 375 | VMINNM                                 | N/A                   | 390 | VMOV (between general-purpose<br>register and single-precision<br>register)             | N/A                   |

| 376 | VMINNM, VMINNMA (floating-<br>point)   | N/A                   | 391 | VMOV (between two general-<br>purpose registers and a<br>doubleword register)           | N/A                   |

| 377 | VMINNMV, VMINNMAV (floating-<br>point) | N/A                   | 392 | VMOV (between two general-<br>purpose registers and two single-<br>precision registers) | N/A                   |

| 378 | VMINV, VMINAV                          | N/A                   | 393 | VMOV (general-purpose register to vector lane)                                          | N/A                   |

| 379 | VMLA (vector by scalar plus vector)    | N/A                   | 394 | VMOV (half of doubleword register to single general-purpose register)                   | N/A                   |

| 380 | VMLA                                   | N/A                   | 395 | VMOV (immediate) (vector)                                                               | N/A                   |

| 381 | VMLADAV                                | N/A                   | 396 | VMOV (immediate)                                                                        | N/A                   |

| 382 | VMLALDAV                               | N/A                   | 397 | VMOV (register) (vector)                                                                | N/A                   |

| 383 | VMLALV                                 | N/A                   | 398 | VMOV (register)                                                                         | N/A                   |

| 384 | VMLAS (vector by vector plus scalar)   | N/A                   | 399 | VMOV (single general-purpose<br>register to half of doubleword<br>register)             | N/A                   |

| 385 | VMLAV                                  | N/A                   | 400 | VMOV (two 32-bit vector lanes to two general-purpose registers)                         | N/A                   |

# Table 1.12 Armv8-M Instructions Tested/Not Tested by CPU Test (9 of 10)

| No. | Instruction                                                     | Tested by<br>CPU test | No. | Instruction                                           | Tested by<br>CPU test |

|-----|-----------------------------------------------------------------|-----------------------|-----|-------------------------------------------------------|-----------------------|

| 401 | VMOV (two general-purpose registers to two 32-bit vector lanes) | N/A                   | 431 | VPT                                                   | N/A                   |

| 402 | VMOV (vector lane to general-<br>purpose register)              | N/A                   | 432 | VPUSH                                                 | N/A                   |

| 403 | VMOVL                                                           | N/A                   | 433 | VQABS                                                 | N/A                   |

| 404 | VMOVN                                                           | N/A                   | 434 | VQADD                                                 | N/A                   |

| 405 | VMOVX                                                           | N/A                   | 435 | VQDMLADH, VQRDMLADH                                   | N/A                   |

| 406 | VMRS                                                            | N/A                   | 436 | VQDMLAH, VQRDMLAH<br>(vector by scalar plus vector)   | N/A                   |

| 407 | VMSR                                                            | N/A                   | 437 | VQDMLASH, VQRDMLASH<br>(vector by vector plus scalar) | N/A                   |

| 408 | VMUL (floating-point)                                           | N/A                   | 438 | VQDMLSDH, VQRDMLSDH                                   | N/A                   |

| 409 | VMUL (vector)                                                   | N/A                   | 439 | VQDMULH, VQRDMULH                                     | N/A                   |

| 410 | VMUL                                                            | N/A                   | 440 | VQDMULL                                               | N/A                   |

| 411 | VMULH, VRMULH                                                   | N/A                   | 441 | VQMOVN                                                | N/A                   |

| 412 | VMULL (integer)                                                 | N/A                   | 442 | VQMOVUN                                               | N/A                   |

| 413 | VMULL (polynomial)                                              | N/A                   | 443 | VQNEG                                                 | N/A                   |

| 414 | VMVN (immediate)                                                | N/A                   | 444 | VQRSHL                                                | N/A                   |

| 415 | VMVN (register)                                                 | N/A                   | 445 | VQRSHRN                                               | N/A                   |

| 416 | VNEG (floating-point)                                           | N/A                   | 446 | VQRSHRUN                                              | N/A                   |

| 417 | VNEG (vector)                                                   | N/A                   | 447 | VQSHL, VQSHLU                                         | N/A                   |

| 418 | VNEG                                                            | N/A                   | 448 | VQSHRN                                                | N/A                   |

| 419 | VNMLA                                                           | N/A                   | 449 | VQSHRUN                                               | N/A                   |

| 420 | VNMLS                                                           | N/A                   | 450 | VQSUB                                                 | N/A                   |

| 421 | VNMUL                                                           | N/A                   | 451 | VREV16                                                | N/A                   |

| 422 | VORN (immediate)                                                | N/A                   | 452 | VREV32                                                | N/A                   |

| 423 | VORN                                                            | N/A                   | 453 | VREV64                                                | N/A                   |

| 424 | VORR (immediate)                                                | N/A                   | 454 | VRHADD                                                | N/A                   |

| 425 | VORR                                                            | N/A                   | 455 | VRINT (floating-point)                                | N/A                   |

| 426 | VPNOT                                                           | N/A                   | 456 | VRINTA                                                | N/A                   |

| 427 | VPOP                                                            | N/A                   | 457 | VRINTM                                                | N/A                   |

| 428 | VPSEL                                                           | N/A                   | 458 | VRINTN                                                | N/A                   |

| 429 | VPST                                                            | N/A                   | 459 | VRINTP                                                | N/A                   |

| 430 | VPT (floating-point)                                            | N/A                   | 460 | VRINTR                                                | N/A                   |

| No. | Instruction | Tested by<br>CPU test | No. | Instruction                            | Tested by<br>CPU test |

|-----|-------------|-----------------------|-----|----------------------------------------|-----------------------|

| 461 | VRINTX      | N/A                   | 478 | VSQRT                                  | N/A                   |

| 462 | VRINTZ      | N/A                   | 479 | VSRI                                   | N/A                   |

| 463 | VRMLALDAVH  | N/A                   | 480 | VST2                                   | N/A                   |

| 464 | VRMLALVH    | N/A                   | 481 | VST4                                   | N/A                   |

| 465 | VRMLSLDAVH  | N/A                   | 482 | VSTM                                   | N/A                   |

| 466 | VRSHL       | N/A                   | 483 | VSTR (System Register)                 | N/A                   |

| 467 | VRSHR       | N/A                   | 484 | VSTR                                   | N/A                   |

| 468 | VRSHRN      | N/A                   | 485 | VSTRB, VSTRH, VSTRW                    | N/A                   |

| 469 | VSBC        | N/A                   | 486 | VSTRB, VSTRH, VSTRW, VSTRD<br>(vector) | N/A                   |

| 470 | VSCCLRM     | N/A                   | 487 | VSUB (floating-point)                  | N/A                   |

| 471 | VSEL        | N/A                   | 488 | VSUB (vector)                          | N/A                   |

| 472 | VSHL        | N/A                   | 489 | VSUB                                   | N/A                   |

| 473 | VSHLC       | N/A                   | 490 | WFE                                    |                       |

| 474 | VSHLL       | N/A                   | 491 | WFI                                    |                       |

| 475 | VSHR        | N/A                   | 492 | WLS, DLS, WLSTP, DLSTP                 | N/A                   |

| 476 | VSHRN       | N/A                   | 493 | YIELD                                  |                       |

| 477 | VSLI        | N/A                   |     |                                        |                       |

# Table 1.13 Armv8-M Instructions Tested/Not Tested by CPU Test (10 of 10)

# 1.1.2 Test Error

The CPU test will jump to this function if an error is detected.

This error handling function is the structure of closed loop and should not return.

All the test functions follow the rules of register preservation following a C function call. Therefore, the user can call these functions like any normal C function without any additional responsibilities for saving register values beforehand.

extern void CPU\_Test\_ErrorHandler(void);

# 1.1.3 CPU Software API

The software API source files related to CPU testing are shown in **Table 1.14**.

When the CPU Test API is executed, the related CPU registers and instructions codes are tested.

A CPU fault can be detected by checking the execution result output to the argument.

It needs to set the configuration of CPU tests before compiling your code. The CPU test configuration directive and each CPU test is shown in **Table 1.15** and **Table 1.16**.

For details, refer to "2.1.3 Preparation for CPU testing".

#### Table 1.14 Source files of CPU Software API

| File Name           | Remarks                                 |

|---------------------|-----------------------------------------|

| r_cpu_diag_config.h | Definition of CPU Test Directive.       |

| cpu_test.c          | CPU test implementation part            |

| r_cpu_diag_0.asm    | Definition of CPU Test core function.   |

| r_cpu_diag_1.asm    | Note:                                   |

| r_cpu_diag_2.asm    | Please note that some tests consist of  |

| r_cpu_diag_3.asm    | multiple files like r_cpu_diag_7_1.asm, |

| r_cpu_diag_4.asm    | r_cpu_diag_7_2.asm.                     |

| r_cpu_diag_5.asm    |                                         |

| r_cpu_diag_6.asm    |                                         |

| r_cpu_diag_7_1.asm  |                                         |

| r_cpu_diag_7_2.asm  |                                         |

| r_cpu_diag_7_3.asm  |                                         |

| r_cpu_diag_8.asm    |                                         |

| r_cpu_diag_0.h      | Declaration of CPU Test core function.  |

| r_cpu_diag_1.h      |                                         |

| r_cpu_diag_2.h      |                                         |

| r_cpu_diag_3.h      |                                         |

| r_cpu_diag_4.h      |                                         |

| r_cpu_diag_5.h      |                                         |

| r_cpu_diag_6.h      |                                         |

| r_cpu_diag_7_1.h    |                                         |

| r_cpu_diag_7_2.h    |                                         |

| r_cpu_diag_7_3.h    |                                         |

| r_cpu_diag_8.h      |                                         |

| r_cpu_diag.c        | Definition of CPU Test API function.    |

| r_cpu_diag.h        | Declaration of CPU Test API function.   |

| r_cpu_diag.inc      | Definition of Assembler macro.          |

Table 1.15 Directives for Software Configuration for CPU Test

| File Name               | Description                                                              |

|-------------------------|--------------------------------------------------------------------------|

| BUILD_R_CPU_DIAG_0      | When set to "1", the CPU test function:<br>R_CPU_Diag0 is constructed.   |

| BUILD_R_CPU_DIAG_1      | When set to "1", the CPU test function:<br>R_CPU_Diag1 is constructed.   |

| BUILD_R_CPU_DIAG_2      | When set to "1", the CPU test function:<br>R_CPU_Diag2 is constructed.   |

| BUILD_R_CPU_DIAG_3      | When set to "1", the CPU test function:<br>R CPU Diag3 is constructed.   |

| BUILD_R_CPU_DIAG_4_1 *1 | When set to "1", the CPU test function:<br>R_CPU_Diag4_1 is constructed. |

| BUILD_R_CPU_DIAG_4_2 *1 | When set to "1", the CPU test function:<br>R_CPU_Diag4_2 is constructed. |

| BUILD_R_CPU_DIAG_5      | When set to "1", the CPU test function:<br>R_CPU_Diag5 is constructed.   |

| BUILD_R_CPU_DIAG_6      | When set to "1", the CPU test function:<br>R_CPU_Diag6 is constructed.   |

| BUILD_R_CPU_DIAG_7_1 *1 | When set to "1", the CPU test function:<br>R_CPU_Diag7_1 is constructed. |

| BUILD_R_CPU_DIAG_7_2 *1 | When set to "1", the CPU test function:<br>R_CPU_Diag7_2 is constructed. |

| BUILD_R_CPU_DIAG_7_3 *1 | When set to "1", the CPU test function:<br>R_CPU_Diag7_3 is constructed. |

| BUILD_R_CPU_DIAG_8      | When set to "1", the CPU test function:<br>R_CPU_Diag8 is constructed.   |

Notes: 1. See Table 1.16.

Please note that some tests have multiple directives like BUILD\_R\_CPU\_DIAG\_7\_1, BUILD\_R\_CPU\_DIAG\_7\_2.

# IEC 60730/60335 Self Test Library for RA2 MCU (CM23 Class-C)

# RA Family

# Table 1.16 CPU Test Target

| Test<br>No | index *1 | Function name *2 | Objective of the Test                                               |

|------------|----------|------------------|---------------------------------------------------------------------|

| 0          | 0        | R_CPU_Diag0      | Four basic arithmetic operations (add, sub, mul and div)            |

| 1          | 1        | R_CPU_Diag1      | Sign/Zero extension operations                                      |

| 2          | 2        | R_CPU_Diag2      | Branch, logical, comparison and conditional operations              |

| 3          | 3        | R_CPU_Diag3      | Bit manipulation and data transfer operations                       |

| 4          | 4        | R_CPU_Diag4      | Memory access (Load/Store) without exclusive operations             |

| 5          | 5        | R_CPU_Diag5      | Memory access (Load/Store) with exclusive and privileged operations |

| 6          | 6        | R_CPU_Diag6      | System related operations                                           |

| 7          | 7        | R_CPU_Diag7_1    | Registers R0 - R12, MSP(R13), LR(R14), and APSR                     |

|            | 8        | R_CPU_Diag7_2    | diagnostic operation                                                |

|            | 9        | R_CPU_Diag7_3    |                                                                     |

| 8          | 10       | R_CPU_Diag8      | CPU register test using WALKPAT algorithm                           |

Notes: 1. Test is required for all indexes when the test spans over multiple indexes.

2. See **Table 1.15** for software configuration directives for code generation of each function.

# ■ cpu\_test.c File

| Syntax                                     |                                                                                                                                                                                                                                                                            |  |  |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| <pre>void CPU_Test_ClassC(void)</pre>      |                                                                                                                                                                                                                                                                            |  |  |  |

| Description                                |                                                                                                                                                                                                                                                                            |  |  |  |

| Perform the CPU test                       | s in the following order:                                                                                                                                                                                                                                                  |  |  |  |

| SaveSPmo<br>2. Disable the CPU<br>set_spmo | SaveSPmonitor = get_spmonitor_status();<br>Disable the CPU stack pointer monitor function.<br>set_spmonitor_status(0);                                                                                                                                                     |  |  |  |

| •                                          | of the argument "result".                                                                                                                                                                                                                                                  |  |  |  |

| When all the CP<br>If an error is dete     | If the result is OK, return to step 3. above. (perform the next test)<br>When all the CPU tests are completed, go to step 6 below.<br>If an error is detected, the external function CPU_Test_ErrorHandler will be called.<br>Check Individual Tests for more information. |  |  |  |

| 6. Restore the stac                        | k pointer monitor access control register saved in step 1.                                                                                                                                                                                                                 |  |  |  |

| 7. CPU_Test_PC                             |                                                                                                                                                                                                                                                                            |  |  |  |

|                                            | Function is finished when all tests have been performed.<br>If all tests were not performed, the external function CPU_Test_ErrorHandler is called.                                                                                                                        |  |  |  |

| Input Parameters                           |                                                                                                                                                                                                                                                                            |  |  |  |

| NONE                                       | N/A                                                                                                                                                                                                                                                                        |  |  |  |

| Output Parameters                          |                                                                                                                                                                                                                                                                            |  |  |  |

| const uint32_t<br>forceFail                | Forced FAIL Option<br>The default value is fixed at "1" (N/A).<br>* If you want to test the forced FAIL, change the value to fixed at "0".                                                                                                                                 |  |  |  |

| Return Values                              |                                                                                                                                                                                                                                                                            |  |  |  |

| NONE                                       | N/A                                                                                                                                                                                                                                                                        |  |  |  |

# Syntax

void CPU\_Test\_PC(void)

#### Description

This function tests the program counter (PC) register.

This checks that the PC is working reliably.

The function returns the inverted value of the specified parameter so that it can verify that the function was executed actually. This return value is checked for correctness.

If an error is detected, the external function CPU\_Test\_ErrorHandler is called.

| Input Parameters  |     |  |

|-------------------|-----|--|

| NONE              | N/A |  |

| Output Parameters |     |  |

| NONE              | N/A |  |

| Return Values     |     |  |

| NONE              | N/A |  |

# ■ r\_cpu\_diag.c File

#### Syntax

void R\_CPU\_Diag(uint32\_t index, const uint32\_t forceFail, int32\_t \*result)

#### Description

Use the index argument to execute the test function that corresponds to the CPU test number. See **Table 1.16** for the argument index, test number, and test function.

- Set "resultTemp" to the initial value. When the test function is performed, the test result is saved in "resultTemp".

- Check if the value of the argument "Index" is valid.

If it is invalid, it exits the process after setting "FAIL(=0)" in the test result.

- 3. Perform the function of the corresponding CPU test according to the value of the argument "index".

- 4. Set the test result to "\* result" and exit the function.

#### Input Parameters

| uint32_t index                               | CPU Test No (Refer to <b>Table 1.16</b> )<br>Returns FAIL when argument value is invalid.             |  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

| const uint32_t<br>forceFail                  | Forced FAIL Option<br>When set to 0, the function fails forcibly.<br>0 : Enabled<br>Others : Disabled |  |

| int32_t *result Pointer to store Test result |                                                                                                       |  |

| Output Parameters                            |                                                                                                       |  |

| int32_t *result                              | Test result (0: FAIL / 1: PASS)                                                                       |  |

| Return Values                                |                                                                                                       |  |

| NONE                                         | N/A                                                                                                   |  |

# Syntax

static void norm\_null(const uint32\_t forceFail, int32\_t \*result)

#### Description

This function is a dummy function of the CPU test function excluded from compilation by the directive. Set the test result to PASS.

# Input Parameters

| • • • • • • • • • •         |                                                                                                       |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------|--|--|

| const uint32_t<br>forceFail | Forced FAIL Option<br>When set to 0, the function fails forcibly.<br>0 : Enabled<br>Others : Disabled |  |  |

| int32_t *result             | Pointer to store Test result                                                                          |  |  |

| Output Parameters           |                                                                                                       |  |  |

| int32_t *result             | Test result (1: PASS)                                                                                 |  |  |

| Return Values               |                                                                                                       |  |  |

| NONE                        | N/A                                                                                                   |  |  |

## ■ r\_cpu\_diag\_0.asm File

# Syntax void R\_CPU\_Diag0(const uint32\_t forceFail, int32\_t \*result)

## Description

#### 1. Addition instructions test Execute each instruction of ADCS (register), ADDS (register), and check the match with the expected value of local signature and global signature.

#### 2. Subtraction instructions test

Execute each instruction of SBCS (register), SUBS (immediate), RSBS (immediate), and check the match with the expected value of local signature and global signature.

3. Multiplication instructions test

Execute each instruction of MULS and check the match with the expected value of local signature and global signature.

#### 4. Division instructions test

Execute each instruction of SDIV, UDIV and check the match with the expected value of local signature and global signature.

#### 5. Addition and subtraction for stack pointer test

Execute each instruction of SUB (SP minus immediate), ADD (SP plus immediate), and check the match with the expected value of local signature and global signature.

| Input Parameters            |                                                                                                       |

|-----------------------------|-------------------------------------------------------------------------------------------------------|

| const uint32_t<br>forceFail | Forced FAIL Option<br>When set to 0, the function fails forcibly.<br>0 : Enabled<br>Others : Disabled |

| int32_t *result             | Pointer to store Test result                                                                          |

| Output Parameters           |                                                                                                       |

| int32_t *result             | Test result (0: FAIL / 1: PASS)                                                                       |

| Return Values               |                                                                                                       |

| NONE                        | N/A                                                                                                   |

# ■ r\_cpu\_diag\_1.asm File

### Syntax

void R\_CPU\_Diag1(const uint32\_t forceFail, int32\_t \*result)

#### Description

#### 1. Sign extension

Execute each instruction of SXTB T1, SXTH T1 and check the match with the expected value of local signature and global signature.

#### 2. Zero extension

Execute each instruction of UXTB T1, UXTH T1 and check the match with the expected value of local signature and global signature.

| Input Parameters            |                                                                                                       |

|-----------------------------|-------------------------------------------------------------------------------------------------------|

| const uint32_t<br>forceFail | Forced FAIL Option<br>When set to 0, the function fails forcibly.<br>0 : Enabled<br>Others : Disabled |

| int32_t *result             | Pointer to store Test result                                                                          |

| Output Parameters           |                                                                                                       |

| int32_t *result             | Test result (0: FAIL / 1: PASS)                                                                       |

| Return Values               |                                                                                                       |

| NONE                        | N/A                                                                                                   |

# ■ r\_cpu\_diag\_2.asm File

| Syntax                                                                                                                                                                                            |                                                                                                       |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

| void R CPU Diag2(const uint32 t forceFail, int32 t *result)                                                                                                                                       |                                                                                                       |  |

| Description                                                                                                                                                                                       |                                                                                                       |  |

| 1. Branch<br>Execute each instruct                                                                                                                                                                | -                                                                                                     |  |

| Logical test<br>Execute each instruction of TST T1 and check the match with the expected value of local signature<br>and global signature.                                                        |                                                                                                       |  |

| <ul> <li>Logical operation<br/>Execute each instruction of ANDS T1, ORRS T1, EORS T1, MVNS T1 and check the match with the<br/>expected value of local signature and global signature.</li> </ul> |                                                                                                       |  |

| <ol> <li>Comparison<br/>Execute each instruction of CMN T1, CMP T1 and check the match with the expected value of local<br/>signature and global signature.</li> </ol>                            |                                                                                                       |  |

| If it matches the expected value, set PASS (0x0001) to "resultTemp", and if it does not match the expected value, set FAIL (0x0000) to "resultTemp".                                              |                                                                                                       |  |