## I3C/I<sup>2</sup>C Bus Multiplexer, IO Expander

The I<sup>2</sup>C bus is a standard bidirectional interface between master and slave devices. The I3C interface improves upon the features of the I<sup>2</sup>C interface, while maintaining backward compatibility. It is a two-wire bidirectional serial bus, optimized for multiple slave devices and is controlled by only one I3C master device at a time.

In most I3C/I<sup>2</sup>C applications, there is the potential need to access I3C/I<sup>2</sup>C slave devices that share two masters, to isolate slave devices that have similar addresses, or to provide more external I/O ports. Renesas provides an I3C/I<sup>2</sup>C Bus Multiplexer and I/O Expander to meet these different application requirements.

## Contents

|                                                             |   |

|-------------------------------------------------------------|---|

| 1. Features .....                                           | 1 |

| 2. I3C/I <sup>2</sup> C Multiplexer Applications .....      | 2 |

| 2.1 IMX3102 – 2:1 Bus Multiplexer .....                     | 2 |

| 2.2 IMX3112 – 1:2 Bus Multiplexer .....                     | 3 |

| 2.3 IO Level Support .....                                  | 4 |

| 2.4 IMX3102 Active Master Selection .....                   | 4 |

| 2.5 IMX3112 Local Channel Selection .....                   | 4 |

| 2.6 I3C/I <sup>2</sup> C Address .....                      | 4 |

| 2.7 I3C/I <sup>2</sup> C Mode Switch .....                  | 5 |

| 2.8 Temperature Sensor .....                                | 5 |

| 2.9 Comparison between I <sup>2</sup> C and I3C Basic ..... | 6 |

| 3. Revision History .....                                   | 7 |

## 1. Features

- Supports I3C basic spec and backward compatible with I<sup>2</sup>C

- Two-wire programmable I3C/I<sup>2</sup>C bus serial interface

- Single device load on the host bus

- Single 1.8V power supply

- Up to 12.5MHz I3C transfer rate

- Integrated on-die LDO, 1.0V VLDO output at VIO pin

- Support Internal pull-up with internal VLDO

- Supports 1.0V, 1.1V, and 1.2 V push-pull IO levels

- Supports 1.0V, 1.2V, 1.8V, 2.5V, and 3.3V open-drain IO levels

- Integrated Temperature Sensor; 0.5°C accuracy with 0.25°C resolution

- Bus reset function

- Packet Error Check (PEC) function

- Parity Error Check function

- Up to 8 unique addressing (except IMX3102 which has a static address)

- Programmable I3C, I<sup>2</sup>C Bus Addressing Scheme

- 9-pin thermally enhanced 2 × 3 × 0.75mm DFN package

- Temperature: Industrial range of -40° to 125°C

## 2. I3C/I<sup>2</sup>C Multiplexer Applications

Table 1. I3C Multiplexer Part Numbers and Feature Summary

| Part Number | Bus Multiplexer | Internal Thermal Sensor | I3C/I <sup>2</sup> C Address<br>(xxx = HID, 000 to 111) |

|-------------|-----------------|-------------------------|---------------------------------------------------------|

| IMX3102     | 2:1             | Yes                     | 0001 111                                                |

| IMX3112     | 1:2             | Yes                     | 1110 xxx                                                |

### 2.1 IMX3102 – 2:1 Bus Multiplexer

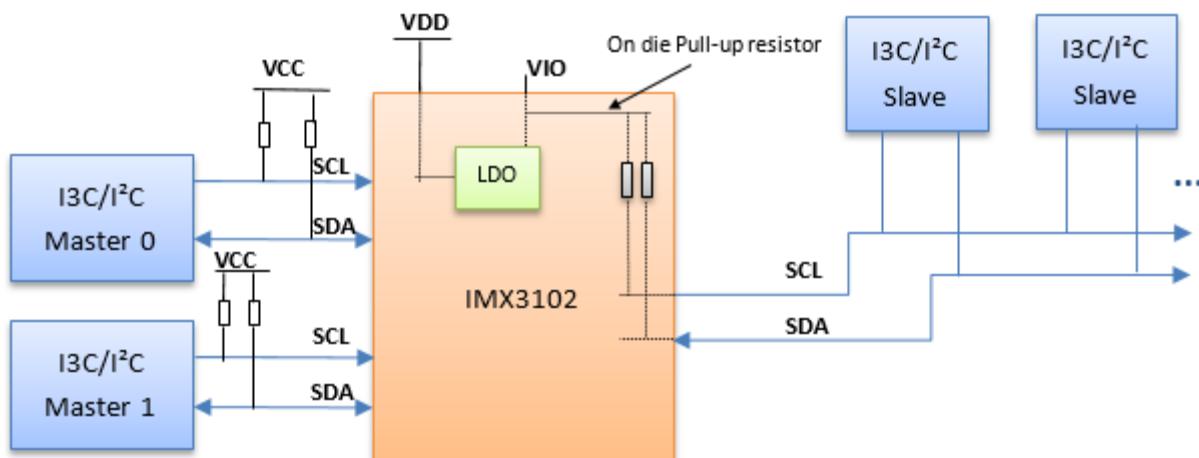

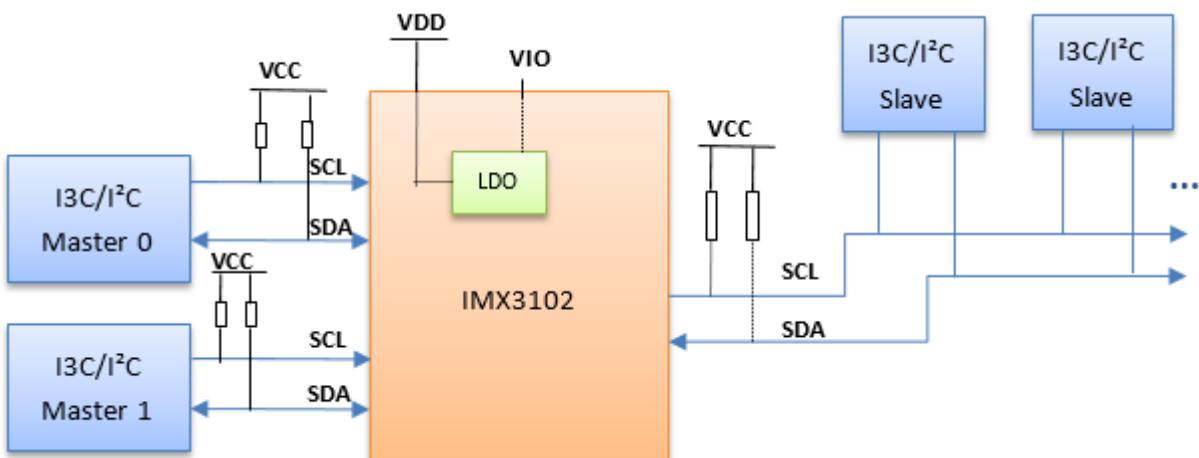

The IMX3102 is a 2-to-1 I3C basic bus multiplexer switch with integrated Temperature Sensor. It is designed to be used for various motherboard applications. There are two master ports (Master port 0 and Master port 1) and one slave port. Either master port can be selected as active Master, which has the control of the slave port as well as the IMX3102. By default, at power on, the master port 0 is selected as active master and it can hand over the control to master port 1 at any time by setting bit 7 in MR65.

Figure 1. I3C/I<sup>2</sup>C Bus 2:1 Multiplexer with Slave Devices (Using Internal On-die Pull-up Resistor)Figure 2. I3C/I<sup>2</sup>C Bus 2:1 Multiplexer with Slave Devices (Using External Pull-up Resistor)

## 2.2 IMX3112 – 1:2 Bus Multiplexer

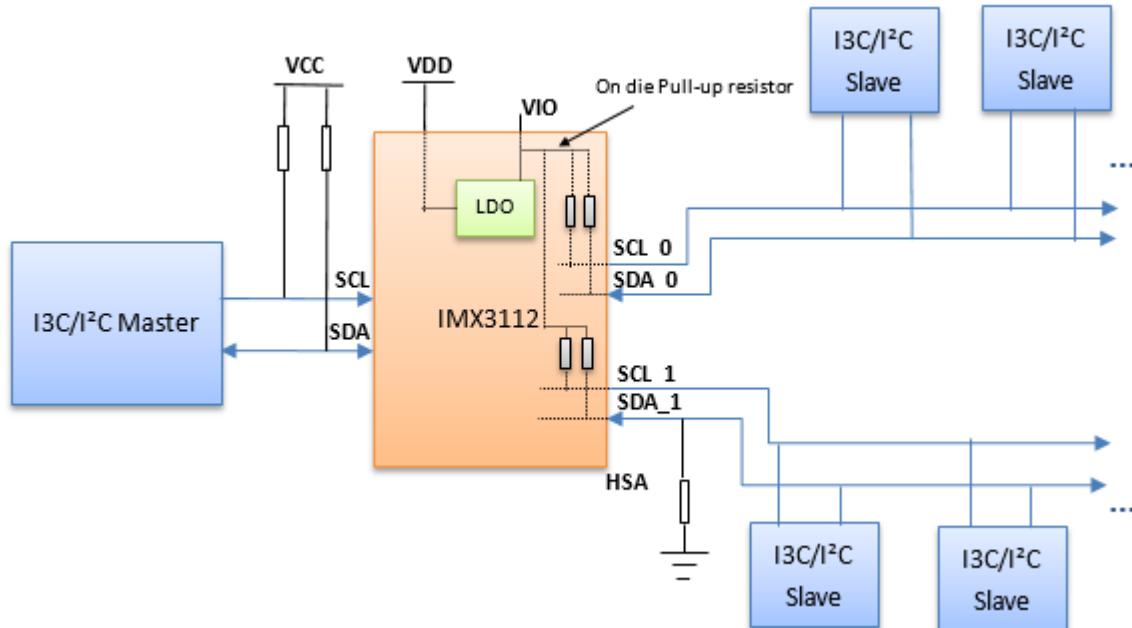

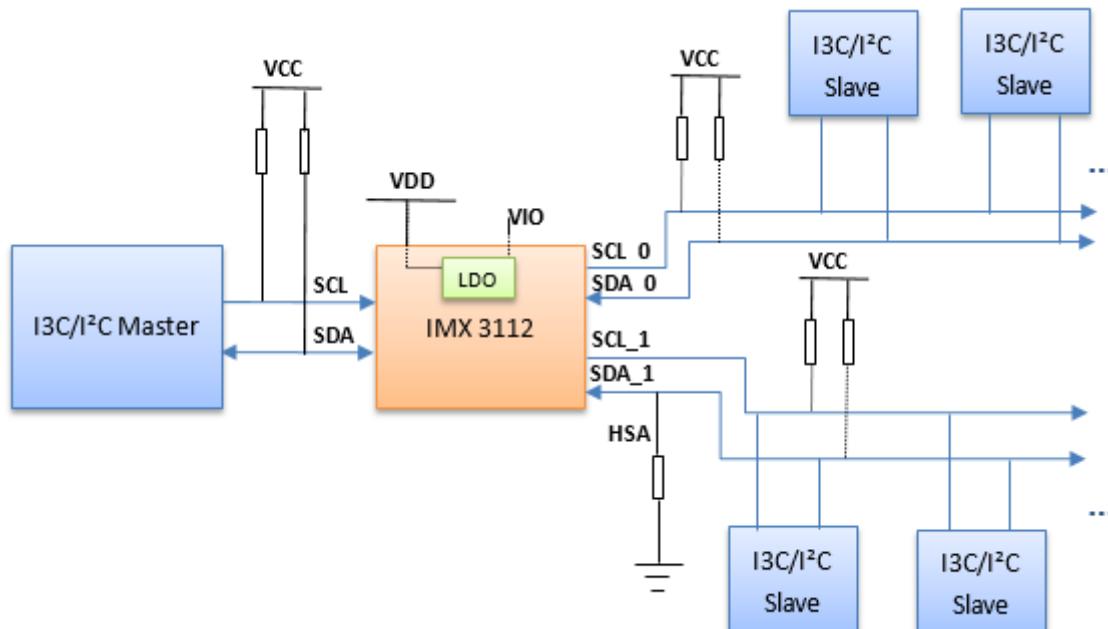

The IMX3112 is a dual bidirectional 1-to-2 translating multiplexer for the I3C/I<sup>2</sup>C bus. The input SDA/SCL pair can fan out to two output pairs (or channels), and either individual output channel can be selected. Applications with slave devices that share the same address can use the multiplexer to prevent slave address conflicts. By selecting the proper output channel, the I3C/I<sup>2</sup>C master can communicate with more slave devices.

Figure 3. I3C/I<sup>2</sup>C Bus 1:2 Multiplexer with Slave Devices (Using Internal On-die Pull-up Resistor)

Figure 4. I3C/I<sup>2</sup>C Bus 1:2 Multiplexer with Slave Devices (Using External Pull-up Resistor)

## 2.3 IO Level Support

On the master side, the IMX3112/3102 can support open-drain IO levels from 1.0V to 3.3V depending on the supply rail master that pulled up the resistor. On output side, the IMX3112/3102 can support open-drain IO levels from 1.0V to 3.3V with an external pull-up resistor or support push-pull IO levels from 1.0V to 1.2V with an internal pull-up resistor. The IO voltage level is configurable through register MR14 [4:2].

|                    | Open Drain   | Push Pull          |

|--------------------|--------------|--------------------|

| Support IO Voltage | 1.0V to 3.3V | 1.0V, 1.1V or 1.2V |

## 2.4 IMX3102 Active Master Selection

The IMX3102 (2:1 multiplexer) has two registers, MR64 and MR65, that are used to select the active master port and enable the slave port. These registers can be written and read via the I3C/I<sup>2</sup>C bus. For more information, see the *IMX3102 Datasheet*.

## 2.5 IMX3112 Local Channel Selection

The IMX3112 (1:2 multiplexer) provides two control registers for the master to select one of the downstream channels as an output local channel – MR64 (IO port switch configuration) and MR65 (bus mux selection). These registers can be written and read via the I3C/I<sup>2</sup>C bus. For more information, see the *IMX3112 Datasheet*.

## 2.6 I3C/I<sup>2</sup>C Address

The 7-bit device I3C/I<sup>2</sup>C address of the IMX3102 is static 0001 111b, which can be any unique address and be programmed by Renesas before shipping. However, the IMX3112 always samples the status of the HSA (Host Address) pin on power-up (the HSA pin is used in conjunction with SDA\_1, and is tied to GND via a resistor value). The status of the HSA pin determines the unique host ID (HID) of the device. The host identifier value is merged with the device type **1110 xxxb** to establish the 7-bit address for this device on the I<sup>2</sup>C or I3C bus as shown in Table 3. For example, if the value sensed on HSA pin identifier 2 (010 binary), then the unique address for this device is 1110 010b.

Table 2. 7-bit Address of the IMX3112/3102 Device

| Bit 7                      | Bit 6 | Bit 5 | Bit 4 | Bit 3         | Bit 2 | Bit 1 | Bit 0      |

|----------------------------|-------|-------|-------|---------------|-------|-------|------------|

| 1                          | 1     | 1     | 0     | HID2          | HID1  | HID0  | R/W        |

| Multiplexer Device Type ID |       |       |       | Host ID (HID) |       |       | Read/Write |

Table 3. HSA Pin Resistor Value and ID

| HSA Pin Connection <sup>[1]</sup> | Device ID | Comment     |

|-----------------------------------|-----------|-------------|

| 10.0KΩ to GND                     | HID = 000 | 1% Resistor |

| 15.4KΩ to GND                     | HID = 001 |             |

| 23.2KΩ to GND                     | HID = 010 |             |

| 35.7KΩ to GND                     | HID = 011 |             |

| 54.9KΩ to GND                     | HID = 100 |             |

| 84.5KΩ to GND                     | HID = 101 |             |

| HSA Pin Connection <sup>[1]</sup> | Device ID | Comment |

|-----------------------------------|-----------|---------|

| 127KΩ to GND                      | HID = 110 |         |

| 196KΩ to GND                      | HID = 111 |         |

1. If there is no resistor between the HSA pin and GND, the IMX3112 will sense a device HID of 111.

## 2.7 I3C/I<sup>2</sup>C Mode Switch

By default when the IMX3112/3102 first powers on, it operates in I<sup>2</sup>C mode. The IMX3112/3102 can operate in I<sup>2</sup>C mode indefinitely. The host puts the IMX3112/3102 in I3C mode by issuing *SETAASA* CCC. The host can put the IMX3112/3102 back in I<sup>2</sup>C mode at any time by issuing *RSTDAA* CCC.

Table 4. *SETAASA* CCC – Broadcast

| Start   | Bit 7            | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | A/N/T | Stop |

|---------|------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| S or Sr | 1                | 1     | 1     | 1     | 1     | 1     | 0     | W = 0 | A     |      |

|         | 0x29 (Broadcast) |       |       |       |       |       |       |       |       | T P  |

Table 5. *RSTDAA* CCC – Broadcast

| Start   | Bit 7            | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | A/N/T | Stop      |

|---------|------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------|

| S or Sr | 1                | 1     | 1     | 1     | 1     | 1     | 0     | W = 0 | A     |           |

|         | 0x06 (Broadcast) |       |       |       |       |       |       |       |       | T Sr or P |

## 2.8 Temperature Sensor

The IMX3112/3102 has an integrated temperature sensor that provides thermal capability of 0.5°C accuracy with 0.25°C resolution. All thermal registers are 16-bit quantities stored in two consecutive registers – low byte and high byte. The device always returns 0 in Reserved (RSVD) bits when the host reads from the low and high byte. Units for all thermal registers are °C. The format of the thermal registers is displayed in the following tables.

Table 6. Thermal Register - Low Byte and High Byte

| Register |           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|

| MR49     | Low Byte  | 8     | 4     | 2     | 1     | 0.5   | 0.25  | RSVD  | RSVD  |

| MR50     | High Byte | RSVD  | RSVD  | RSVD  | Sign  | 128   | 64    | 32    | 16    |

Table 7. Thermal Register Examples

| High Byte  | Low Byte   | Value  | Unit |

|------------|------------|--------|------|

| 000 0 0101 | 1111 00 00 | +95.00 | °C   |

| 000 0 0101 | 0101 00 00 | +85.00 | °C   |

| 000 0 0100 | 1011 00 00 | +75.00 | °C   |

| 000 0 0000 | 0001 00 00 | + 1.00 | °C   |

| High Byte  | Low Byte   | Value  | Unit |

|------------|------------|--------|------|

| 000 0 0000 | 0000 11 00 | + 0.75 | °C   |

| 000 0 0000 | 0000 10 00 | + 0.50 | °C   |

| 000 0 0000 | 0000 01 00 | + 0.25 | °C   |

| 000 0 0000 | 000 0 0000 | 0.00   | °C   |

| 000 1 1111 | 1111 11 00 | -0.25  | °C   |

| 000 1 1111 | 1111 10 00 | -0.50  | °C   |

| 000 1 1111 | 1111 01 00 | -0.75  | °C   |

| 000 1 1111 | 1111 00 00 | -1.00  | °C   |

| 000 1 1111 | 1101 10 00 | -40.00 | °C   |

## 2.9 Comparison between I<sup>2</sup>C and I3C Basic

The following table compared the key feature differences between I<sup>2</sup>C and I3C basic.

Table 8. Comparison between I<sup>2</sup>C and I3C

| Parameter                                        | I <sup>2</sup> C                                             | I3C                                                                                          |

|--------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| <b>Number of wires</b>                           | 2-wire                                                       | 2-wire                                                                                       |

| <b>Data Rate</b>                                 | 3.4MHz (Hs) / 1MHz (Fm+) / 400KHz (Fm)                       | Up to 12.5MHz                                                                                |

| <b>IO Voltage</b>                                | 1.0V ~ 3.3V                                                  | 1.0V, 1.1V, or 1.2V                                                                          |

| <b>In-Band Interrupt</b>                         | No<br>(An additional wire is required for interrupt support) | Yes<br>(No additional signal required)                                                       |

| <b>Packet Error Check (PEC)</b>                  | No                                                           | Yes                                                                                          |

| <b>Parity Error Check</b>                        | No                                                           | Yes                                                                                          |

| <b>In-band Integrated Commands (CCC) Support</b> | No                                                           | Yes                                                                                          |

| <b>Slave Address</b>                             | 7 bit, Static                                                | 7 bit, Dynamic<br>(Assigned during initialization, static I <sup>2</sup> C address at start) |

| <b>Data Signal</b>                               | Open Drain                                                   | Open Drain or Push-pull<br>(Changed dynamically)                                             |

| <b>Clock Signal</b>                              | Open Drain                                                   | Push-pull                                                                                    |

### 3. Revision History

| Revision | Date         | Description      |

|----------|--------------|------------------|

| 1.0      | Sep 17, 2021 | Initial release. |

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).