# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **H8S Family**

## Sample Firmware for the M66592 USB ASSP

### Introduction

This Application Note consists of two parts: Part I, Connection of the H8S/2218 and the M66592, and Part II, Sample Firmware for the M66592.

This Application Note describes how to use the Renesas generally applicable sample firmware for the M66592 ASSP (hereafter called USB firmware), a sample program for controlling the USB interface of the M66592.

The H8S/2218 is used for control.

## **Target Device**

H8S/2218

#### **Contents**

#### Connection of the H8S/2218 and the M66592

|     | 1.   | Overview                                 | 2   |

|-----|------|------------------------------------------|-----|

|     | 2.   | Development Tools for the USB Firmware   | 4   |

|     | 3.   | Programming the Internal Flash Memory    | 12  |

|     | 4.   | Restrictions                             | 14  |

| Sar | nple | Firmware for the M66592                  |     |

|     | 1.   | Overview                                 | 15  |

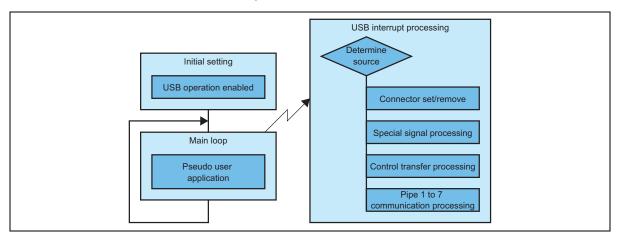

|     | 2.   | Executing the USB Firmware               | 17  |

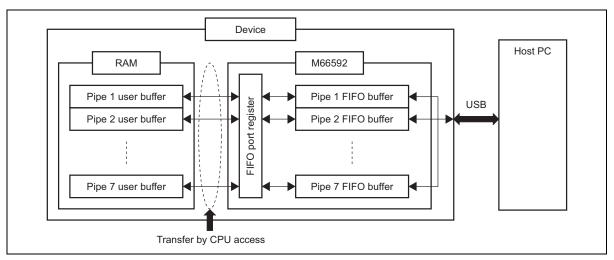

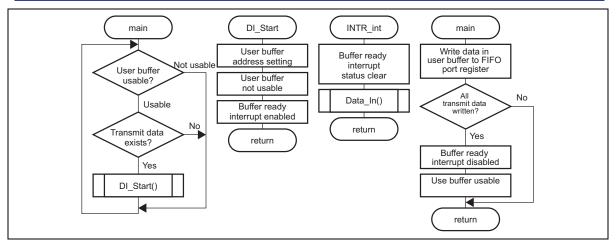

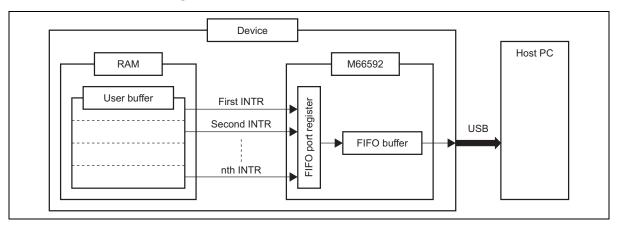

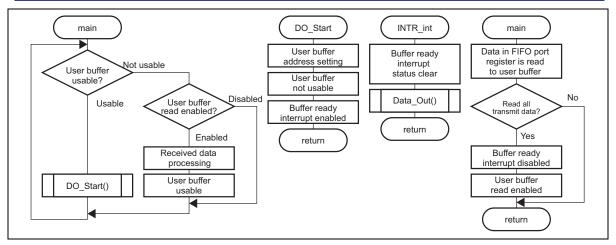

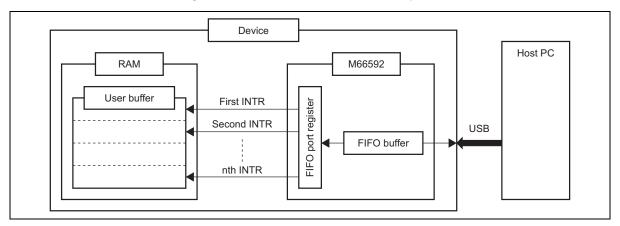

|     | 3.   | Data Transfer                            | 18  |

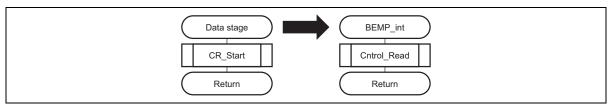

|     | 4.   | Class/Vendor Requests                    | 23  |

|     | 5.   | User-Defined Information                 | 24  |

|     | 6.   | User-Defined Macro Directives (macusr.h) | 26  |

|     | 7.   | Pipe Definition (def_ep.h)               | 28  |

|     | 8.   | Descriptor Definitions (descrip.h)       | 31  |

|     | 9.   | Low Power Sleep Function (PCUT)          | 33  |

|     | 40   | Destrictions                             | 0.4 |

#### Connection of the H8S/2218 and the M66592

#### 1. Overview

#### **Related Documents:**

- 1. H8S, H8/300 Series High-performance Embedded Workshop 3 User's Manual

- 2. H8S, H8/300 Series High-performance Embedded Workshop 3 Tutorial Manual

- 3. H8S, H8/300 Series C/C++ Compiler Package Application Note

- 4. Solution Engine<sup>TM</sup> H8S/2218 CPU Board Overview

- 5. Universal Serial Bus Revision 2.0 specification

#### 1.1 Features of the USB Firmware for the H8S/2218

The USB firmware for the H8S/2218 (hereafter referred to as the USB firmware) has the following features:

- Configuration does not include specification of the peripherals; so the user can define them individually.

- The connection can be checked by using the USBCommandVerifier.exe (hereafter called USBCV; it can be downloaded from: http://www.usb.org/developers/developers/tools/).

- Sample programs for bulk and interrupt-driven input and output data transfer.

- Files are divided into functional groups (refer to the list under section 1.4, File Configuration).

- The USB firmware runs on the H8S/2218, and evaluation can be conducted by connecting the M66592 to the H8S/2218 CPU board (M2218CP01 Solution Engine® manufactured by Hitachi ULSI Systems, Co., Ltd.) via a signal connection board (created by the user), or the H8S/2218 E10A-USB emulator.

Note: Solution Engine® is a registered trademark of Hitachi ULSI Systems Co., Ltd.

#### 1.2 Objectives of the USB Firmware

The USB firmware was developed with the following objectives:

- to facilitate the development of USB communications programs for the M66592; and

- to give a specific example of M66592 control as a supplementary description.

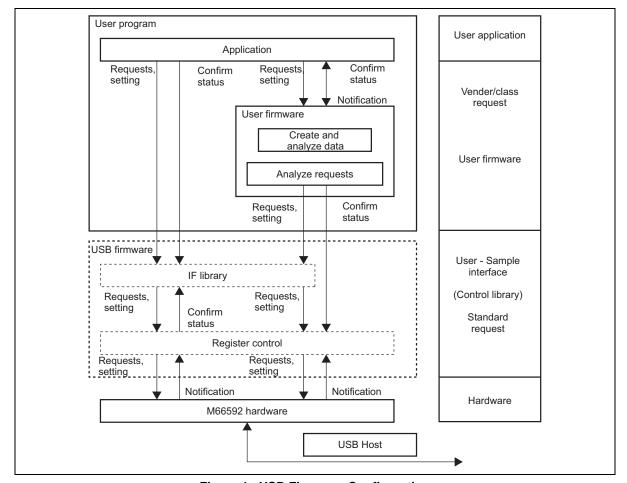

#### 1.3 Services Provided by the USB Firmware

The services provided by the USB firmware to the upper layer (user-program layer) are:

- initialization of the M66592 (reset, oscillation control, pipe initialization, etc.);

- response to requests (standard requests defined in the USB Revision 2.0 specification);

- handling of data transfer (bulk, interrupt-driven, CPU access);

- status notification (status notification function); and

- request notification (request notification function).

## 1.4 File Configuration

Files for the USB firmware for the H8S/2218 can be categorized as main files, modified or added files, and the workspace files for the H8S/2218 (generated by using High-performance Embedded Workshop 3, or HEW).

**Table 1 File Configuration List**

| Category       | File Name                    | Description                                               |

|----------------|------------------------------|-----------------------------------------------------------|

| Main files     | changeep.c                   | User application processing                               |

|                | classvender.c                | Processing of class/vendor requests                       |

|                | controlrw.c                  | Control of reading and writing                            |

|                | dataio.c                     | Processing to read or write data                          |

|                | datable.h                    | Definition of the user buffer for use in transmission and |

|                |                              | reception                                                 |

|                | def592.h                     | Definitions of M66592 register addresses and bits         |

|                | def_ep.h                     | Data definition for pipe setting                          |

|                | descrip.h                    | Descriptor data definition                                |

|                | extern.h                     | Definitions of external references                        |

|                | global.c                     | Processing of global variables                            |

|                | Intrn.c                      | Handlers for the INTR, INTN, and BEMP interrupts          |

|                | usbsig.c                     | USB signal processing                                     |

|                | libassp.c                    | Processing of USB ASSP register manipulation              |

|                | lib592.c                     | Processing of USB ASSP register manipulation              |

|                | libassp.h                    | Definitions of USB ASSP register manipulation             |

|                | macurs.h                     | Definitions of user macros                                |

|                | status.c                     | Processing to manipulate the internal state               |

|                | stdreqget.c                  | Processing of standard requests                           |

|                | stdreqset.c                  | Processing of standard requests                           |

|                | typedef.h                    | Definitions of variable types                             |

|                | version.h                    | Definition of the version information                     |

| Modified files | usbint.c                     | Handler for USB interrupts                                |

|                | Main.c                       | Pseudo user application                                   |

|                | defusr.h                     | Definitions of user settings                              |

| Added file     | 2218S.H                      | Definitions of H8S/2218 registers                         |

| HEW3           | dbsct.c                      | Settings of sections B and R                              |

| workspace      | resetprg.c                   | Reset program                                             |

| files for the  | Sbrk.c                       | Program of sbrk                                           |

| H8S/2218       | Sbrk.h                       | Header file for sbrk                                      |

|                | stacksct.h                   | Setting of stack area                                     |

|                | Fw592_H8S2218.hws(.hbp/.tws) | Workspace file                                            |

|                | Fw592_H8S2218.hwp(.pgs/.tps) | HEW project file                                          |

|                | defaultSession.hsf           | Session file                                              |

|                | \debug, \relase              | Absolute file generation folders                          |

## 2. Development Tools for the USB Firmware

The USB firmware for the H8S/2218 was developed and evaluated with the development tools below.

Table 2 Tools Used in Developing the USB Firmware for the H8S/2218

| Category | Type No.      | Name                                                      | Remark         |

|----------|---------------|-----------------------------------------------------------|----------------|

| Hardware | M3A-0038G01   | M66592 utility board                                      | _              |

|          | MS2218CP01    | H8S/2218 Solution Engine® (CPU board)                     | _              |

|          | _             | Signal connection board                                   | Created by the |

|          |               |                                                           | user           |

|          | HS0005KCU01H  | E10A-USB                                                  | Emulator       |

| Software | _             | High-performance Embedded Workshop ver.3.0.06 (release 2) | Development    |

|          |               |                                                           | tool           |

|          | _             | H8S, H8/300H Standard Toolchain (V.6.0.3.0)               | Toolchain      |

|          | HS0005KCU01SR | HDI                                                       | Emulator       |

|          |               |                                                           | software       |

## 2.1 Hardware Configuration

## 2.1.1 CPU Board and Utility Board

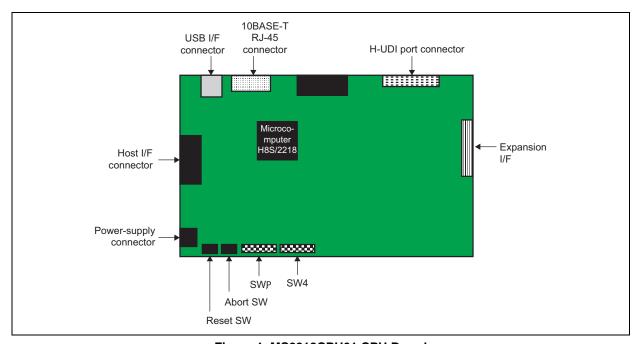

Figure 1 MS2218CPU01 CPU Board

Note: Set the switches only after turning the power supply OFF.

Table 3 MS2218CPU01 SW1 Setting Contents

| SW    | Name | Function                          | Setting |

|-------|------|-----------------------------------|---------|

| SW1-1 | MD0  | MCU mode switchover (MCU mode: 6) | On      |

| SW1-2 | MD1  |                                   | Off     |

| SW1-3 | MD2  |                                   | Off     |

| SW1-4 | FEW  | Flash write enable                | Off     |

| SW1-5 | EMLE | H-UDI function enable             | Off     |

| SW1-6 | _    | Not used                          | Off     |

| SW1-7 |      | Not used                          | Off     |

| SW1-8 | _    | Not used                          | Off     |

Note: Refer to the Solution Engine® H8S/2218 CPU Board Overview.

Table 4 Pin Assignment of Expansion Slot CN12 on the MS2218CP01 CPU Board

| 1         GND         —         2         φ         89           3         GND         —         4         D0         64           5         D1         65         6         D2         66           7         D3         67         8         GND         —           9         D4         68         10         D5         69           11         D6         70         12         D7         71           13         GND         —         14         D8         72           15         D9         73         16         D10         74           17         D11         75         18         GND         —           19         D12         76         20         D13         77           21         D14         78         22         D15         79           23         GND         —         24         3.3 V         —           24         3.3 V         —         26         GND         —           27         A0         10         28         A1         11           29         A2         12         30                                                                                    | Pin | Signal Name | Terminal No. | Pin | Signal Name | Terminal No. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|--------------|-----|-------------|--------------|

| 5         D1         65         6         D2         66           7         D3         67         8         GND         —           9         D4         68         10         D5         69           11         D6         70         12         D7         71           13         GND         —         14         D8         72           15         D9         73         16         D10         74           17         D11         75         18         GND         —           19         D12         76         20         D13         77           21         D14         78         22         D15         79           23         GND         —         24         3.3 V         —           24         3.3 V         —         26         GND         —           27         A0         10         28         A1         11           29         A2         12         30         A3         13           31         GND         —         32         A4         17           33         A5         18         34                                                                               | 1   | GND         | _            | 2   | ф           | 89           |

| 7         D3         67         8         GND         —           9         D4         68         10         D5         69           11         D6         70         12         D7         71           13         GND         —         14         D8         72           15         D9         73         16         D10         74           17         D11         75         18         GND         —           19         D12         76         20         D13         77           21         D14         78         22         D15         79           23         GND         —         24         3.3 V         —           24         3.3 V         —         26         GND         —           24         3.3 V         —         26         GND         —           27         A0         10         28         A1         11           29         A2         12         30         A3         13           31         GND         —         32         A4         17           33         A5         18         34                                                                           | 3   | GND         | _            | 4   | D0          | 64           |

| 9         D4         68         10         D5         69           11         D6         70         12         D7         71           13         GND         —         14         D8         72           15         D9         73         16         D10         74           17         D11         75         18         GND         —           19         D12         76         20         D13         77           21         D14         78         22         D15         79           23         GND         —         24         3.3 V         —           24         3.3 V         —         26         GND         —           27         A0         10         28         A1         11           29         A2         12         30         A3         13           31         GND         —         32         A4         17           33         A5         18         34         A6         19           35         A7         20         36         GND         —           41         GND         —         42                                                                           | 5   | D1          | 65           | 6   | D2          | 66           |

| 11         D6         70         12         D7         71           13         GND         —         14         D8         72           15         D9         73         16         D10         74           17         D11         75         18         GND         —           19         D12         76         20         D13         77           21         D14         78         22         D15         79           23         GND         —         24         3.3 V         —           24         3.3 V         —         26         GND         —           24         3.3 V         —         26         GND         —           27         A0         10         28         A1         11           29         A2         12         30         A3         13           31         GND         —         32         A4         17           33         A5         18         34         A6         19           35         A7         20         36         GND         —           37         A8         37         38 <td>7</td> <td>D3</td> <td>67</td> <td>8</td> <td>GND</td> <td>_</td>  | 7   | D3          | 67           | 8   | GND         | _            |

| 13         GND         —         14         D8         72           15         D9         73         16         D10         74           17         D11         75         18         GND         —           19         D12         76         20         D13         77           21         D14         78         22         D15         79           23         GND         —         24         3.3 V         —           24         3.3 V         —         26         GND         —           27         A0         10         28         A1         11           29         A2         12         30         A3         13           31         GND         —         32         A4         17           33         A5         18         34         A6         19           35         A7         20         36         GND         —           37         A8         37         38         A9         38           39         A10         39         40         A11         40           41         GND         —         42 <td>9</td> <td>D4</td> <td>68</td> <td>10</td> <td>D5</td> <td>69</td> | 9   | D4          | 68           | 10  | D5          | 69           |

| 15         D9         73         16         D10         74           17         D11         75         18         GND         —           19         D12         76         20         D13         77           21         D14         78         22         D15         79           23         GND         —         24         3.3 V         —           24         3.3 V         —         26         GND         —           27         A0         10         28         A1         11           29         A2         12         30         A3         13           31         GND         —         32         A4         17           33         A5         18         34         A6         19           35         A7         20         36         GND         —           37         A8         37         38         A9         38           39         A10         39         40         A11         40           41         GND         —         42         A12         49           43         A13         50         44<                                                                     | 11  | D6          | 70           | 12  | D7          | 71           |

| 17         D11         75         18         GND         —           19         D12         76         20         D13         77           21         D14         78         22         D15         79           23         GND         —         24         3.3 V         —           24         3.3 V         —         26         GND         —           27         A0         10         28         A1         11           29         A2         12         30         A3         13           31         GND         —         32         A4         17           33         A5         18         34         A6         19           35         A7         20         36         GND         —           37         A8         37         38         A9         38           39         A10         39         40         A11         40           41         GND         —         42         A12         49           43         A13         50         44         A14         51           45         A15         52         46                                                                     | 13  | GND         | _            | 14  | D8          | 72           |

| 19         D12         76         20         D13         77           21         D14         78         22         D15         79           23         GND         —         24         3.3 V         —           24         3.3 V         —         26         GND         —           27         A0         10         28         A1         11           29         A2         12         30         A3         13           31         GND         —         32         A4         17           33         A5         18         34         A6         19           35         A7         20         36         GND         —           37         A8         37         38         A9         38           39         A10         39         40         A11         40           41         GND         —         42         A12         49           43         A13         50         44         A14         51           45         A15         52         46         GND         —           47         A16         1         48<                                                                     | 15  | D9          | 73           | 16  | D10         | 74           |

| 21     D14     78     22     D15     79       23     GND     —     24     3.3 V     —       24     3.3 V     —     26     GND     —       27     A0     10     28     A1     11       29     A2     12     30     A3     13       31     GND     —     32     A4     17       33     A5     18     34     A6     19       35     A7     20     36     GND     —       37     A8     37     38     A9     38       39     A10     39     40     A11     40       41     GND     —     42     A12     49       43     A13     50     44     A14     51       45     A15     52     46     GND     —       47     A16     1     48     A17     100       49     nCS1     27     50     nCS3     25       51     GND     —     52     nWAIT     95       53     3.3 V     —     54     nRD     92       55     nIRQ0     6     56     nIRQ1     8       59<                                                                                                                                                                                                                                                        | 17  | D11         | 75           | 18  | GND         | _            |

| 23         GND         —         24         3.3 V         —           24         3.3 V         —         26         GND         —           27         A0         10         28         A1         11           29         A2         12         30         A3         13           31         GND         —         32         A4         17           33         A5         18         34         A6         19           35         A7         20         36         GND         —           37         A8         37         38         A9         38           39         A10         39         40         A11         40           41         GND         —         42         A12         49           43         A13         50         44         A14         51           45         A15         52         46         GND         —           47         A16         1         48         A17         100           49         nCS1         27         50         nCS3         25           51         GND         —         5                                                                     | 19  | D12         | 76           | 20  | D13         | 77           |

| 24       3.3 V       —       26       GND       —         27       A0       10       28       A1       11         29       A2       12       30       A3       13         31       GND       —       32       A4       17         33       A5       18       34       A6       19         35       A7       20       36       GND       —         37       A8       37       38       A9       38         39       A10       39       40       A11       40         41       GND       —       42       A12       49         43       A13       50       44       A14       51         45       A15       52       46       GND       —         47       A16       1       48       A17       100         49       nCS1       27       50       nCS3       25         51       GND       —       52       nWAIT       95         53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1                                                                                                                                                                        | 21  | D14         | 78           | 22  | D15         | 79           |

| 27       A0       10       28       A1       11         29       A2       12       30       A3       13         31       GND       —       32       A4       17         33       A5       18       34       A6       19         35       A7       20       36       GND       —         37       A8       37       38       A9       38         39       A10       39       40       A11       40         41       GND       —       42       A12       49         43       A13       50       44       A14       51         45       A15       52       46       GND       —         47       A16       1       48       A17       100         49       nCS1       27       50       nCS3       25         51       GND       —       52       nWAIT       95         53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1       8         57       nIRQ2       97       58       nRES                                                                                                                                                                      | 23  | GND         | _            | 24  | 3.3 V       | _            |

| 29       A2       12       30       A3       13         31       GND       —       32       A4       17         33       A5       18       34       A6       19         35       A7       20       36       GND       —         37       A8       37       38       A9       38         39       A10       39       40       A11       40         41       GND       —       42       A12       49         43       A13       50       44       A14       51         45       A15       52       46       GND       —         47       A16       1       48       A17       100         49       nCS1       27       50       nCS3       25         51       GND       —       52       nWAIT       95         53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1       8         57       nIRQ2       97       58       nRES       58         59       GND       —       60       nHWR                                                                                                                                                                    | 24  | 3.3 V       | _            | 26  | GND         | _            |

| 31       GND       —       32       A4       17         33       A5       18       34       A6       19         35       A7       20       36       GND       —         37       A8       37       38       A9       38         39       A10       39       40       A11       40         41       GND       —       42       A12       49         43       A13       50       44       A14       51         45       A15       52       46       GND       —         47       A16       1       48       A17       100         49       nCS1       27       50       nCS3       25         51       GND       —       52       nWAIT       95         53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1       8         57       nIRQ2       97       58       nRES       58         59       GND       —       60       nHWR       93         61       nLWR       94       62       nAS <td>27</td> <td>A0</td> <td>10</td> <td>28</td> <td>A1</td> <td>11</td>                                                                                         | 27  | A0          | 10           | 28  | A1          | 11           |

| 33       A5       18       34       A6       19         35       A7       20       36       GND       —         37       A8       37       38       A9       38         39       A10       39       40       A11       40         41       GND       —       42       A12       49         43       A13       50       44       A14       51         45       A15       52       46       GND       —         47       A16       1       48       A17       100         49       nCS1       27       50       nCS3       25         51       GND       —       52       nWAIT       95         53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1       8         57       nIRQ2       97       58       nRES       58         59       GND       —       60       nHWR       93         61       nLWR       94       62       nAS       91                                                                                                                                                                                                                | 29  | A2          | 12           | 30  | A3          | 13           |

| 35       A7       20       36       GND       —         37       A8       37       38       A9       38         39       A10       39       40       A11       40         41       GND       —       42       A12       49         43       A13       50       44       A14       51         45       A15       52       46       GND       —         47       A16       1       48       A17       100         49       nCS1       27       50       nCS3       25         51       GND       —       52       nWAIT       95         53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1       8         57       nIRQ2       97       58       nRES       58         59       GND       —       60       nHWR       93         61       nLWR       94       62       nAS       91                                                                                                                                                                                                                                                                        | 31  | GND         | _            | 32  | A4          | 17           |

| 37       A8       37       38       A9       38         39       A10       39       40       A11       40         41       GND       —       42       A12       49         43       A13       50       44       A14       51         45       A15       52       46       GND       —         47       A16       1       48       A17       100         49       nCS1       27       50       nCS3       25         51       GND       —       52       nWAIT       95         53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1       8         57       nIRQ2       97       58       nRES       58         59       GND       —       60       nHWR       93         61       nLWR       94       62       nAS       91                                                                                                                                                                                                                                                                                                                                | 33  | A5          | 18           | 34  | A6          | 19           |

| 39       A10       39       40       A11       40         41       GND       —       42       A12       49         43       A13       50       44       A14       51         45       A15       52       46       GND       —         47       A16       1       48       A17       100         49       nCS1       27       50       nCS3       25         51       GND       —       52       nWAIT       95         53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1       8         57       nIRQ2       97       58       nRES       58         59       GND       —       60       nHWR       93         61       nLWR       94       62       nAS       91                                                                                                                                                                                                                                                                                                                                                                                        | 35  | A7          | 20           | 36  | GND         | _            |

| 41       GND       —       42       A12       49         43       A13       50       44       A14       51         45       A15       52       46       GND       —         47       A16       1       48       A17       100         49       nCS1       27       50       nCS3       25         51       GND       —       52       nWAIT       95         53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1       8         57       nIRQ2       97       58       nRES       58         59       GND       —       60       nHWR       93         61       nLWR       94       62       nAS       91                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37  | A8          | 37           | 38  | A9          | 38           |

| 43       A13       50       44       A14       51         45       A15       52       46       GND       —         47       A16       1       48       A17       100         49       nCS1       27       50       nCS3       25         51       GND       —       52       nWAIT       95         53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1       8         57       nIRQ2       97       58       nRES       58         59       GND       —       60       nHWR       93         61       nLWR       94       62       nAS       91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39  | A10         | 39           | 40  | A11         | 40           |

| 45       A15       52       46       GND       —         47       A16       1       48       A17       100         49       nCS1       27       50       nCS3       25         51       GND       —       52       nWAIT       95         53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1       8         57       nIRQ2       97       58       nRES       58         59       GND       —       60       nHWR       93         61       nLWR       94       62       nAS       91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41  | GND         | _            | 42  | A12         | 49           |

| 47       A16       1       48       A17       100         49       nCS1       27       50       nCS3       25         51       GND       —       52       nWAIT       95         53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1       8         57       nIRQ2       97       58       nRES       58         59       GND       —       60       nHWR       93         61       nLWR       94       62       nAS       91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43  | A13         | 50           | 44  | A14         | 51           |

| 49     nCS1     27     50     nCS3     25       51     GND     —     52     nWAIT     95       53     3.3 V     —     54     nRD     92       55     nIRQ0     6     56     nIRQ1     8       57     nIRQ2     97     58     nRES     58       59     GND     —     60     nHWR     93       61     nLWR     94     62     nAS     91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45  | A15         | 52           | 46  | GND         | _            |

| 51       GND       —       52       nWAIT       95         53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1       8         57       nIRQ2       97       58       nRES       58         59       GND       —       60       nHWR       93         61       nLWR       94       62       nAS       91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47  | A16         | 1            | 48  | A17         | 100          |

| 53       3.3 V       —       54       nRD       92         55       nIRQ0       6       56       nIRQ1       8         57       nIRQ2       97       58       nRES       58         59       GND       —       60       nHWR       93         61       nLWR       94       62       nAS       91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49  | nCS1        | 27           | 50  | nCS3        | 25           |

| 55     nIRQ0     6     56     nIRQ1     8       57     nIRQ2     97     58     nRES     58       59     GND     —     60     nHWR     93       61     nLWR     94     62     nAS     91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51  | GND         | _            | 52  | nWAIT       | 95           |

| 57     nIRQ2     97     58     nRES     58       59     GND     —     60     nHWR     93       61     nLWR     94     62     nAS     91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53  | 3.3 V       | <del>_</del> | 54  | nRD         | 92           |

| 59         GND         —         60         nHWR         93           61         nLWR         94         62         nAS         91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55  | nIRQ0       | 6            | 56  | nIRQ1       | 8            |

| 61 nLWR 94 62 nAS 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57  | nIRQ2       | 97           | 58  | nRES        | 58           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59  | GND         | <del></del>  | 60  | nHWR        | 93           |

| 63 GND — 64 3.3 V —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61  | nLWR        | 94           | 62  | nAS         | 91           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63  | GND         | _            | 64  | 3.3 V       | _            |

Note: Type No.: 14-5014-064-102-861 (female type) manufactured by Kyocera Elco Ltd.

## 2.1.2 Utility Board to be Used

Figure 2 M3A-0038G01 Utility Board

Table 5 Pin Assignment of CN2 on the M3A-0038G01 Utility Board

| Pin | 16-bit sep.*1 | 16-bit mult.*2 | Pin | 16-bit sep.* <sup>1</sup> | 16-bit mult.*2 |

|-----|---------------|----------------|-----|---------------------------|----------------|

| 1   | GND           | GND            | 2   | D15                       | D15            |

| 3   | D14           | D14            | 4   | D13                       | D13            |

| 5   | D12           | D12            | 6   | D11                       | D11            |

| 7   | D10           | D10            | 8   | D9                        | D9             |

| 9   | D8            | D8             | 10  | GND                       | GND            |

| 11  | D7            | D7             | 12  | D6                        | D6/AD6         |

| 13  | D5            | D5/AD5         | 14  | D4                        | D4/AD4         |

| 15  | D3            | D3/AD3         | 16  | D2                        | D2/AD2         |

| 17  | D1            | D1/AD1         | 18  | D0                        | D0             |

| 19  | GND           | GND            | 20  | GND                       | GND            |

| 21  | Not used      | Not used       | 22  | Not used                  | Not used       |

| 23  | WR1_N         | WR1_N          | 24  | VBUS                      | VBUS           |

| 24  | EXIOVcc       | EXIOVcc        | 26  | EXIOVcc                   | EXIOVcc        |

| 27  | _             | _              | 28  | _                         | _              |

| 29  | GND           | GND            | 30  | GND                       | GND            |

| 31  | _             | _              | 32  | _                         | _              |

| 33  | _             | _              | 34  | _                         | _              |

| 35  | _             | _              | 36  | _                         | _              |

| 37  | _             | _              | 38  | _                         | _              |

| 39  |               | <del></del>    | 40  |                           |                |

| 41  | SD7           | SD7            | 42  | SD6                       | SD6            |

| 43  | SD5           | SD5            | 44  | SD4                       | SD4            |

| 45  | SD3           | SD3            | 46  | SD2                       | SD2            |

| 47  | SD1           | SD1            | 48  | SD0                       | SD0            |

| 49  | GND           | GND            | 50  | GND                       | GND            |

Note: 16-bit sep.\*1: When a separate 16-bit bus is in use. 16bit-mult.\*2: When a 16-bit multiplexed bus is in use.

| Pin | 16-bit sep.*1                      | 16-bit mult.*2                     | Pin | 16-bit sep.*1 | 16-bit mult.*2 |

|-----|------------------------------------|------------------------------------|-----|---------------|----------------|

| 1   | WR0_N                              | WR0_N                              | 2   | GND           | GND            |

| 3   | RD_N                               | RD_N                               | 4   | GND           | GND            |

| 5   | CS_N                               | CS_N                               | 6   | RST_N         | RST_N          |

| 7   | DREQ_0                             | DREQ_0                             | 8   | DACK0_N       | DACK0_N        |

| 9   | INT_N                              | INT_N                              | 10  | GND           | GND            |

| 11  | GND                                | GND                                | 12  | A1            | Not used       |

| 13  | A2                                 | Not used                           | 14  | A3            | Not used       |

| 15  | A4                                 | Not used                           | 16  | A5            | Not used       |

| 17  | A6                                 | ALE                                | 18  | GND           | GND            |

| 19  | EXVcc                              | EXVcc                              | 20  | EXVcc         | EXVcc          |

| 21  | Not used                           | (JP7-ALE)                          | 22  | _             | _              |

| 23  | _                                  | _                                  | 24  | SOF_N         | SOF_N          |

| 24  | DACK1_N/DSTB0_N                    | DACK1_N/DSTB0_N                    | 26  | DREQ1_N       | DREQ1_N        |

| 27  | _                                  | _                                  | 28  | _             | _              |

| 29  | GND                                | GND                                | 30  | GND           | GND            |

| 31  | JP6-EXT (external 1.5-<br>V input) | JP6-EXT (external 1.5-<br>V input) | 32  | _             | _              |

| 33  | _                                  | _                                  | 34  | _             | _              |

| 35  | DACK1_N/DSTB0_N                    | DACK1_N/DSTB0_N                    | 36  | DEND0_N       | DEND0_N        |

| 37  | _                                  | _                                  | 38  | _             | _              |

| 39  | _                                  | _                                  | 40  | DEND1_N       | DEND1_N        |

| 41  | _                                  | _                                  | 42  | _             | _              |

| 43  | _                                  | _                                  | 44  | _             | _              |

| 45  | _                                  | _                                  | 46  | _             | _              |

| 47  | _                                  | _                                  | 48  | _             | _              |

| 49  | GND                                | GND                                | 50  | GND           | GND            |

|     |                                    |                                    |     |               |                |

Note: 16-bit sep.\*1: When a separate 16-bit bus is in use. 16bit-mult.\*2: When a 16-bit multiplexed bus is in use.

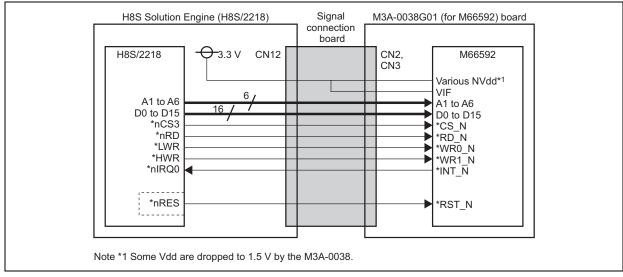

#### 2.1.3 Connecting the Utility Board with the CPU Board

The first step towards developing with and evaluating the USB firmware for the H8S/2218 is to connect the CPU board with the utility board via the signal connection board.

Figure 3 Wiring Connections

#### 2.1.4 Configuring the System

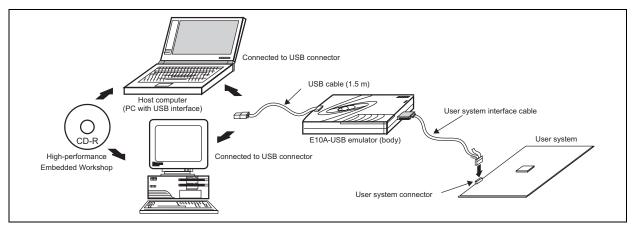

The user system (target system) is connected to the host computer via the E10A-USB emulator.

Figure 4 System Configuration

## 2.2 Software Configuration

The next step towards developing with and evaluating the USB firmware is to create a project with the following settings in the High-performance Embedded Workshop 3.

#### 2.2.1 Settings in the High-performance Embedded Workshop 3

1. Setting the workspace file for the H8S/2218

Generate a workspace file for the H8S/2218 by specifying "Create a new project workspace" in the Highperformance Embedded Workshop 3 and make the settings shown below on the displayed input screens to.

Table 7 High-performance Embedded Workshop 3 Settings

| Input Screen | Item                                          | Setting                                       | Remarks                                                                                                                                             |

|--------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|              | "Application" selected                        | Application                                   |                                                                                                                                                     |

|              | Workspace Name                                | Fw592_H8S2218                                 | Input                                                                                                                                               |

|              | Project Name                                  | Fw592_H8S2218                                 | Input                                                                                                                                               |

|              | CPU Family                                    | H8S, H8/300                                   |                                                                                                                                                     |

|              | Toolchain                                     | Hitachi H8S, H8/300 Standard                  |                                                                                                                                                     |

| 1/9          | Toolchain version                             | 6.0.3.0                                       | H8S, H8/300 C/C++ library generator (V.2.00.01)                                                                                                     |

|              |                                               |                                               | H8S, H8/300 C/C++ compiler (V. 6.00.03)                                                                                                             |

|              |                                               |                                               | H8S, H8/300 assembler (V.6.01.00)                                                                                                                   |

|              |                                               |                                               | Optimizing linkage editor (V.8.00.07)                                                                                                               |

|              | CPU Series                                    | 2000                                          |                                                                                                                                                     |

|              | CPU Type                                      | Other                                         | 2218 is not selectable (when Other is specified for CPU Type, files containing information on the CPU and I/O register definitions must be created) |

| 2/9          | Operating Mode                                | Advanced                                      |                                                                                                                                                     |

|              | Address Space                                 | 16 Mbyte                                      |                                                                                                                                                     |

|              | Merit of Library                              | Code Size                                     |                                                                                                                                                     |

|              | Stack calculation                             | Medium (2 bytes)                              |                                                                                                                                                     |

| 3/9          | Use I/O Library                               | Not checked                                   |                                                                                                                                                     |

|              | Use Heap Memory                               | Checked                                       |                                                                                                                                                     |

|              | [Heap Size]                                   | H'420                                         |                                                                                                                                                     |

|              | [Generate main( ) Function]                   | None                                          |                                                                                                                                                     |

|              | I/O Register Definition<br>Files              | Not checked                                   |                                                                                                                                                     |

| 4/9          | Library                                       | [Disable all] is checked                      |                                                                                                                                                     |

| 5/9          | Stack Pointer Address                         | H'00FFE800                                    |                                                                                                                                                     |

|              | Stack Size                                    | H'200                                         |                                                                                                                                                     |

| 6/9          | Vector Definition Files                       | Checked                                       |                                                                                                                                                     |

| 7/9          | Targets                                       | All unchecked                                 |                                                                                                                                                     |

| 8/9          | Target name                                   | H8S/2218F E10A-USB System (CPU2000)           |                                                                                                                                                     |

|              | Configuration name                            | Debug_H8S_2218F_E10A-<br>USB System (CPU2000) |                                                                                                                                                     |

| 9/9          | The following source files will be generated. |                                               | Pressing the Finish button ends the settings.                                                                                                       |

#### 2. Section settings

Section settings required for developing and evaluating the USB firmware for the H8S/2218 are shown below. Select HEW-[Tools]-[Options]-[H8S, H8/300 Standard Toolchain]-[Optimizing Linkage Editor]-Category: Section.

### Table 8 Section Settings

| Address    | Section Name | Description                    |

|------------|--------------|--------------------------------|

| 0x00000400 | PResetPRG    | Reset function                 |

|            | PIntPRG      | Exception processing function  |

| 0x00001000 | Р            | Program area                   |

|            | С            | Constants area                 |

|            | C\$BSEC      | For the _INITSCT function      |

|            | C\$DSEC      | For the _INITSCT function      |

|            | CIntPRG      | For exception processing       |

|            | D            | Initialization data area (ROM) |

| 0x00FFC000 | В            | Non-initialization data area   |

|            | R            | Initialization data area (RAM) |

| 0x00FFE800 | S            | Stack area                     |

#### 3. CPU information creation

The CPU information has to be created for use in debugging. Select HEW-[Tools]-[Options]-[H8S, H8/300 Standard Toolchain]-[Optimizing Linkage Editor]-Category: Verification Creation.

#### Table 9 CPU Information

| Device | Start      | End        |  |

|--------|------------|------------|--|

| ROM    | 0x00000000 | 0x001FFFFF |  |

| RAM    | 0x00FFC000 | 0x00FFFFFF |  |

For details, please refer to the H8S, H8/300 Series C/C++ Compiler Package Application Note. The USB firmware for the H8S/2218 should be set as shown above since it is to be used with the H8S/2218 Solution Engine.

http://documentation.renesas.com/eng/products/tool/apn/rej05b0464\_h8s.pdf

#### 2.2.2 H8S/2218 Settings

Changes have been made to certain files of the Renesas generally applicable. Sample firmware for the M66592 USB ASSP (Version 1.00) and one file has been added to make the set usable with the H8S/2218 Solution Engine by the USB firmware.

Table 10 Additions and Changes to Renesas Generally Applicable Sample Firmware for the M66592 USB ASSP

| File Name | Additions and Changes                                                                                       | Remarks                                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| main.c    | delay_1ms(), delay_10us() are changed.                                                                      | Time adjustment. Bus and software interrupt                                             |

|           | CPU_init() is set to be used for the H8S/2218.                                                              | settings.                                                                               |

| Defusr.h  | Changed according to the contents                                                                           | Details are given in section 2.2.3.                                                     |

| Usbint.c  | Method of function declaration was changed.  #pragma section IntPRG _interrupt (vect=16) void usbint (void) | Interrupt function is declared together with the vector (set by the compiler function). |

| 2218S.H   | H8S/2218 register definition file was added.                                                                |                                                                                         |

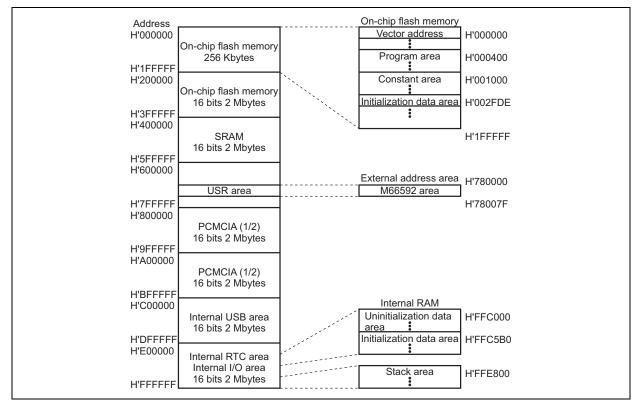

#### 1. Address map

The address map used by the USB firmware for the H8S/2218 is from address H'000000 to H'1FFFFF, H'780000 to H'78007F, and H'C00000 to H'FFFFFF.

Figure 5 H8S/2218 Solution Engine Address Map

2. Bus width and inserted wait-state settings

Bus width and inserted wait-state settings of the USB firmware for the H8S/2218 for controller MCU is as follows (set in the main.c: CPU\_init()).

Table 11 Bus Width and the Number of Wait States

| Area No.                   | Area Name       | <b>Bus Width</b> | Access State | Wait State |

|----------------------------|-----------------|------------------|--------------|------------|

| CS3 (H'780000 to H'78007F) | The M66592 area | 16 bits          | 3 states     | 1 state    |

## 2.2.3 User Defined Items in the USB Firmware for the H8S/2218

The USB firmware for the H8S/2218 includes the following settings for the H8S/2218 Solution Engine.

Table 12 User Defined Items in the USB Firmware for the H8S/2218

| Settings                          | Remarks                                                                                                                                                                                                  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #define PCUT_MODE PCUT_USE        | Brings the low-power sleep function into use                                                                                                                                                             |

| #define ATCKM_MODE<br>ATCKM_USE   | -                                                                                                                                                                                                        |