## Renesas RA8P1 Series

# Getting Started with RA8P1 Memory Architecture, Configurations and Topologies

#### Introduction

This application note is designed to provide guidance on effectively utilizing the memory resources of the RA8P1 Dual core family of devices, with a focus on optimizing performance for dual-core applications. As MCUs advance in complexity, on-chip memory may not always be sufficient to support demanding requirements, making the use of off-chip memory essential for fully realizing the potential of advanced dual-core applications. The RA8P1 MCU offer extensive on-chip memory along with support for off-chip memory interfaces, ensuring efficient memory management in dual-core environments.

## This application note covers:

- Overview of internal MRAM, SRAM and Cache architectures in RA8P1 MCU, for dual-core operation.

- Overview of External memory such as OSPI flash/RAM, SDRAM and Chip selectable external interface

for additional memories and guidelines on interfacing with OSPI and SDRAM/memory bus to efficiently

manage memory in a dual-core system.

- Instructions on connecting external memory devices such as OSPI, SDRAM and Chip select addressable memory space for seamless dual-core execution.

- Steps to enable and allocate TCM for optimized execution on each core.

- Explanation of ECC and parity memory on RA8P1 devices, including configuration for dual-core applications.

- Essential steps to maximize memory efficiency, ensuring smooth and high-performance execution in dual-core RA8P1 based designs.

## **Required Resources**

Flexible Software Package (FSP) v6.0.0

#### Target devices

• RA8P1 (Dual core and Single Core version)

## Contents

| 1. Dual-Core MCU Architecture                                  | 4  |

|----------------------------------------------------------------|----|

| 1.1 Overview of Dual-Core Architecture                         | 4  |

| 1.2 RA Dual-Core Bus Architecture                              | 4  |

| 1.3 System Bus and Data Path                                   | 5  |

| 1.4 Core Communication and Synchronization                     | 6  |

| 2. Memory Architecture of RA Dual-Core MCU                     | 6  |

| 2.1 Internal Memory                                            | 8  |

| 2.1.1 MRAM Code Memory                                         | g  |

| 2.1.2 Option Setting Memory                                    | 13 |

| 2.1.2.1 Option Setting Memory Registers                        | 15 |

| 2.1.3 On-Chip ROM                                              | 17 |

| 2.1.4 SRAM                                                     | 18 |

| 2.1.5 TCM (Tightly Coupled Memory)                             | 19 |

| 2.1.6 Cache                                                    | 22 |

| 2.1.6.1 Data Cache                                             | 22 |

| 2.1.6.2 Instruction Cache                                      | 23 |

| 2.1.6.3 How to Enable / Disable Cache Memory                   | 23 |

| 2.1.6.4 Cache Memory and Performance Impact on the System      | 24 |

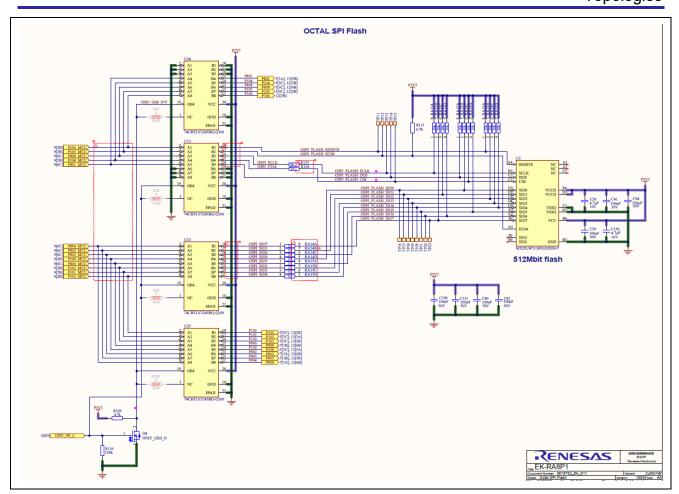

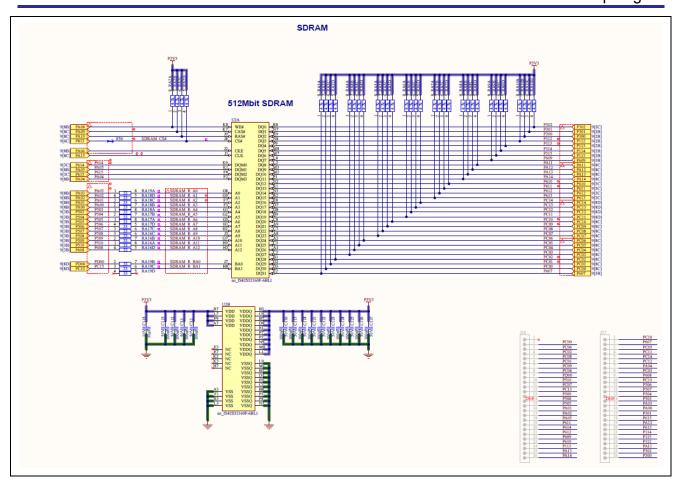

| 2.2 External Memory                                            | 24 |

| 2.2.1 SDRAM                                                    | 25 |

| 2.2.2 Octal SPI Memory                                         | 27 |

| 2.2.3 CS Addressable Memory Space                              | 29 |

| 2.3 External Memory Bus Interface                              | 32 |

| 2.4 How to Interface External Memory                           | 36 |

| 2.5 Supported External Memory types on RA8P1                   | 40 |

| Memory Considerations in System Design                         | 41 |

| 3.1 Internal Memory Selection in System Design                 | 41 |

| 3.2 External Memory Selection in System Design                 | 42 |

| 4. TrustZone and Secure Memory Management                      | 43 |

| 5. Low Power Mode and Memory Management                        | 45 |

| 5.1 Operating State of Memory Modules in Low Power Mode        | 45 |

| 5.2 Operating State of Processor Low Power Mode                | 46 |

| 5.3 Power Gating and Clock Gating for Memory Modules           | 46 |

| 5.4 Low Power modes and SDRAM                                  | 46 |

| 6. Configuring the Dual-Core MCU Memory Using FSP Configurator | 47 |

| 6.1 FSP based Memory Configuration for RA Dual-Core MCU        | 47 |

| 6.2 SDRAM Memory Startup Configuration and Initialization      | 49 |

#### Renesas RA8 Series Getting Started with RA8 Memory Architecture, Configurations and **Topologies**

| 6.3 | Dual core Memory Selection and its Configuration                   | 50 |

|-----|--------------------------------------------------------------------|----|

| 6.4 | Ensuring Data Coherency in a RA8P1                                 | 50 |

| 7.  | Inter-processor communication (IPC) and Shared memory              | 51 |

| 7.1 | Communication Mechanisms Between Cores                             | 51 |

| 7.2 | Shared Memory Settings and Limitations                             | 51 |

| 8.  | How to interpret the electrical characteristic of RA8P1 MCU        | 51 |

| 8.1 | How to read the Electrical Characteristics specified in the MCU UM | 52 |

| 9.  | Example Projects, Reference Applications, and Application Notes    | 62 |

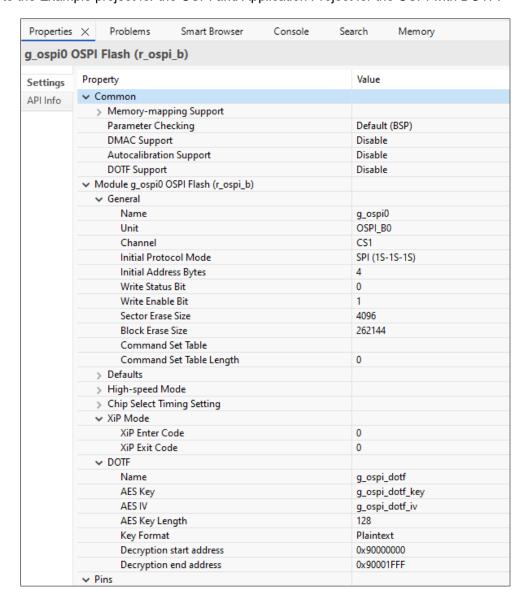

| 9.1 | Reference Example for OSPI                                         | 62 |

| 9.2 | Reference Application project for Decryption on the fly for OSPI   | 62 |

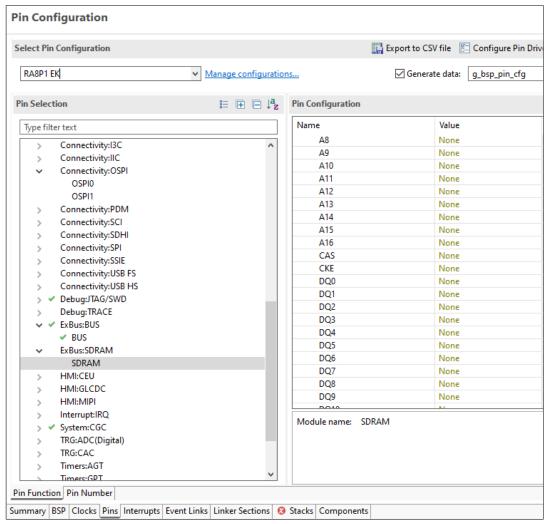

| 9.3 | Reference Example for SDRAM                                        | 63 |

| 9.4 | Reference Example for MRAM                                         | 63 |

| 10. | References                                                         | 63 |

| 11. | Website and Support                                                | 64 |

| Rev | /ision History                                                     | 65 |

Jun.30.25

#### 1.1 Overview of Dual-Core Architecture

Dual-core MCUs integrate two processing cores within a single chip to enhance performance, parallel processing, and power efficiency. These MCUs are commonly used in real-time applications, IoT devices, industrial automation, and automotive control systems. The architecture can be categorized into:

**Homogeneous Dual-Core MCUs:** Both cores are identical, often executing similar tasks in parallel or load balancing computational processes.

**Heterogeneous Dual-Core MCUs:** Each core is different in architecture or instruction set, enabling distinct tasks such as one core handling real-time operations while the other manages general-purpose computations.

Renesas RA dual core MCU RA8P1 architecture falls into heterogeneous Dual core MCU, with Cortex-M85 (CM85) is designated as Core 0/CPU0, serving as the high-performance processing unit, while Cortex-M33 (CM33) is designated as Core 1/CPU1, handling additional real-time control and system management tasks.

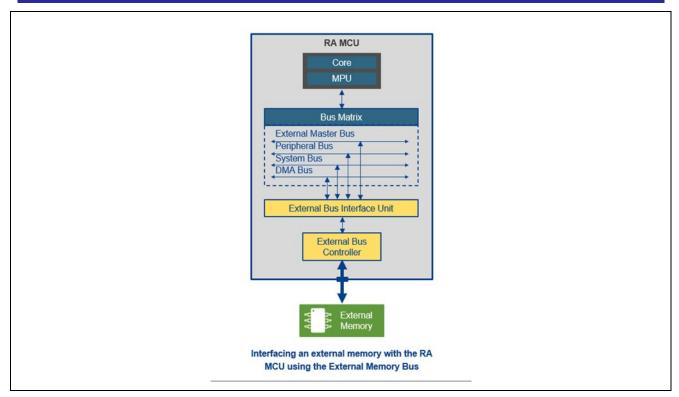

#### 1.2 RA Dual-Core Bus Architecture

The bus architecture in RA dual-core MCUs is engineered to support efficient communication and data exchange between the cores and peripherals. These devices primarily use a shared bus architecture, where both cores access a common system bus that connects to memory and peripheral components. To maintain smooth operation, arbitration mechanisms are employed to prevent conflicts and ensure fair access to shared resources. In addition, a dedicated bus is provided for accessing ITCM and DTCM, further enhancing performance and reducing contention.

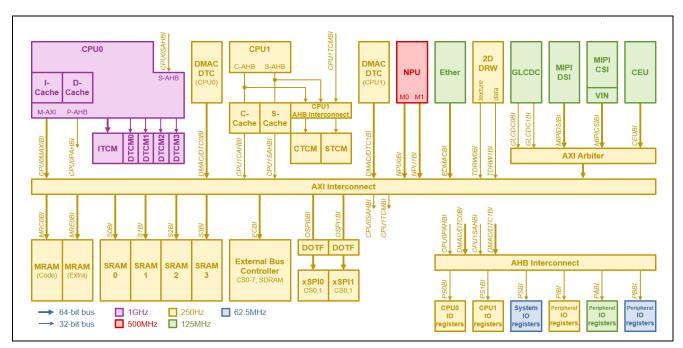

Figure 1. RA8P1 Dual Core Bus Architecture Overview

Key components of the RA8P1 dual-core bus architecture include System Bus AXI, AHB, APB, which facilitates communication between CM85, CM33, memory, and peripherals.

These buses collectively form an interconnected matrix that enables efficient routing of data and control signals across the RA8P1 dual-core system. Both the CM85 and CM33 cores, which can act as independent bus masters, communicate seamlessly with various on-chip memory blocks such as ITCM, DTCM, SRAM, and MRAM. In addition, the architecture supports smooth access to peripherals via the APB and connects to external interfaces through AXI or AHB expansions. By intelligently distributing traffic across buses with different performance characteristics and access priorities, the RA8P1 ensures that real-time tasks, background processing, and peripheral operations can run concurrently without contention, essential for

high-performance dual-core applications requiring parallelism and synchronized inter-core interaction.

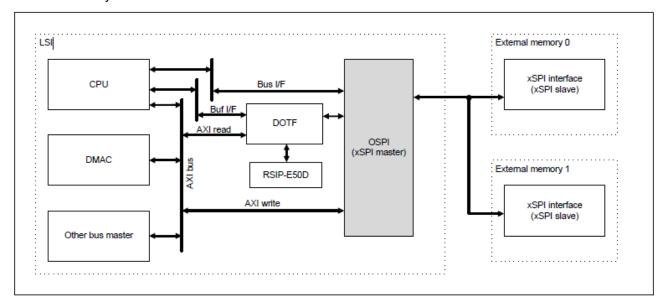

## 1.3 System Bus and Data Path

The system consists of multiple bus interfaces that connect processing units and peripherals. The CPU0, based on the Arm® Cortex®-M85, connects to the Master-AXI (M-AXI) and Peripheral AHB (P-AHB) bus interfaces, while the CPU1, featuring the Arm® Cortex®-M33, connects to C-AHB and S-AHB Interface. There are Neural Processing Unit (NPU) connected to interfaces NPU0 and NPU1 bus interfaces. The Direct Memory Access bus (DMAC/DTC1BI/EDMACBI) includes interfaces for DMAC,DTC0, DTC1, and EDMAC. The system also contains dedicated bus(GRAPHBI/TDRWBI) for image and display processing through the Camera Engine Unit (CEU), Graphics LCD Controller (GLCDC0 and GLCDC1), and Drawing Engine (DRW0 and DRW1). For multimedia applications, the MIPI-DSI interface is used for display, while the MIPI-CSI interface supports video input via VIN.

It includes connections to various memory units, such as Code MRAM and Extra MRAM (read-only), along with multiple SRAM modules (SRAM0, SRAM1, SRAM2, and SRAM3) for high-speed data storage. The CPU0 and CPU1 each have dedicated system AHB connections (CPU0 S-AHB and CPU1 S-AHB) to ensure smooth data flow. External memory interfaces include OSPI connections for SPI-Flash, SDRAM and CSC for general external device support.

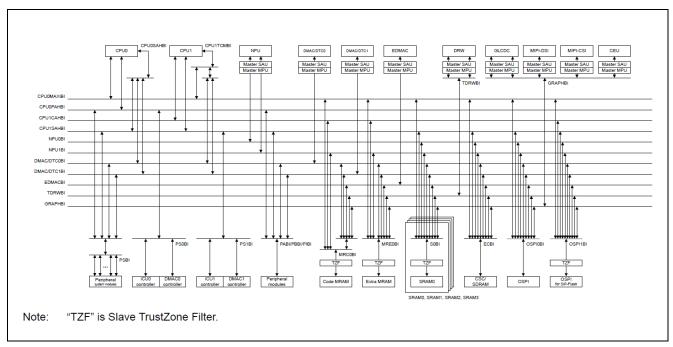

Peripheral synchronization is achieved through modules linked to different clock domains, including PCLKA, PCLKB, and ICLK, ensuring coordinated operation. The ICU controllers (ICU0 and ICU1) are integrated with CPU0 and CPU1 to manage efficient interrupt handling. Additionally, the peripheral system module manages multiple controllers, including cache, memory protection, debug, security, and bus control, ensuring robust system operation. Figure 2 shows the RA8P1 Dual core system Bus connection.

Figure 2. RA8P1 Dual Core System Bus Connection

Figure 3 shows the RA8P1 Dual core System Bus Access mapping table for Bus Master and Slave.

Figure 3. RA8P1 Dual Core System Bus Access Path

## 1.4 Core Communication and Synchronization

Core communication and synchronization are essential for efficient interaction between the CM85 and CM33 cores within the CPUs. Inter-Processor Communication (IPC) enables hardware sharing, data exchange, and co-ordination through interrupt events, ensuring seamless operation between the two cores.

To maintain proper synchronization and prevent resource conflicts, IPC employs multiple locks and semaphore mechanisms. CM85 and CM33 share memory regions, with mutual exclusion mechanisms to prevent race conditions.

Developers can choose between separate or shared hardware semaphores based on application requirements, ensuring mutually exclusive access to shared resources between CM85 and CM33.

Also for efficient data transfer, IPC integrates FIFO buffers:

- A write-only FIFO for CM85 and a read-only FIFO for CM33, allowing CM85 to send data to CM33.

- A write-only FIFO for CM33 and a read-only FIFO for CM85, enabling bidirectional communication.

These mechanisms ensure reliable and structured data exchange and shared memory access between the two cores, supporting seamless synchronization and coordination.

## 2. Memory Architecture of RA Dual-Core MCU

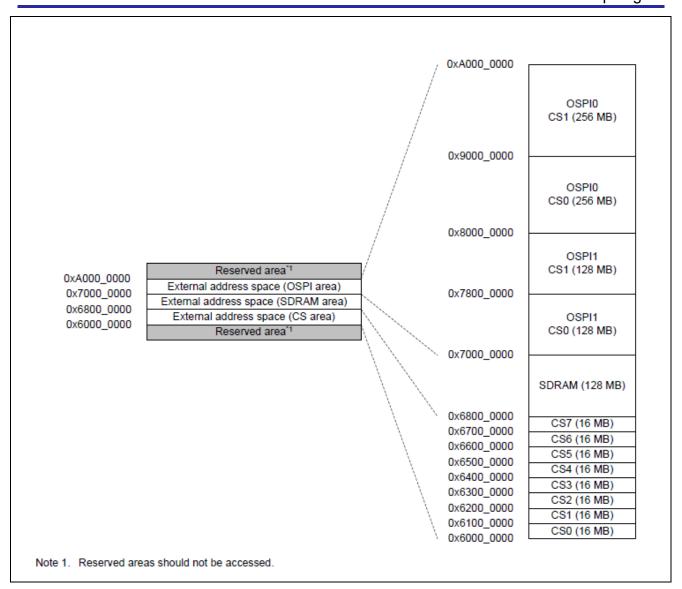

RA8P1 MCU has addressing capacity of 2^32-bits, making a 4 GB addressable space ranging from 0x0000\_0000 to 0XFFFF\_FFF. RA8P1 supports a variety of memories both internal and external to the MCU.

The different types of internal and external memory are shown in Table 1 below.

Table 1. RA8P1 Memory Example

| Up to Maximum 1 MB of MRAM memory(Non Volatile).                                                                                                                                                               |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2 MB (256 KB CM85 TCM RAM, 128 KB CM33 TCM RAM and 1664 KB of users SRAM) of on-chip high-speed SRAM with Error Correction Code (ECC).  Note: In Some of the RA8P1 Part numbers the SRAM is limited to 1792 KB |  |

| 128 KB (16 blocks $\times$ 8KB) with ECC for Tightly coupled Instruction Memory, 128 KB (16 blocks $\times$ 8KB) with ECC for Tightly coupled Data Memory for CM85.                                            |  |

| 64 KB with ECC for Tightly coupled Instruction memory and 64 KB with ECC for Tightly Coupled Data Memory for CM33.                                                                                             |  |

| Note: These are part of 2MB SRAM Memory.                                                                                                                                                                       |  |

| On-chip immutable ROM contains First Stage Bootloader (FSBL)                                                                                                                                                   |  |

| 16 KB of I-Cache with ECC and 16 KB of D-Cache with ECC for CM85.                                                                                                                                              |  |

| Code-bus Cache (C-Cache): 16 KB with ECC and System-bus Cache (S-Cache): 16 KB with ECC for CM33                                                                                                               |  |

| Note: In Some of the RA8P1 Part numbers the CPU1 doesn't contain C/S cache                                                                                                                                     |  |

| The option-setting memory which determines the state of the MCU after a reset.                                                                                                                                 |  |

| emory Support using OSPI or QSPI (2 slots of 256 MB)                                                                                                                                                           |  |

| 256 MB *2 external memory address space shared for CM85 and CM33                                                                                                                                               |  |

| 256 MB *2 external memory address space shared for CM85 and CM33                                                                                                                                               |  |

| 256 MB *2 external memory address space shared for CM85 and CM33                                                                                                                                               |  |

| RAM Memory Support 128 MB                                                                                                                                                                                      |  |

| 128 MB (SDRAM) external memory address space shared for CM85 and CM33                                                                                                                                          |  |

| t memory mapped addressable are for additional SRAM and peripherals                                                                                                                                            |  |

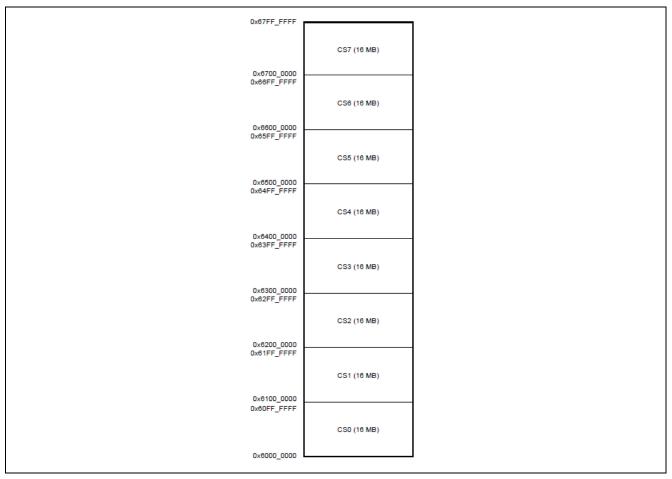

| 8 X 16 MB addressable memory regions for additional SRAM, and other memory mapped connections shared for CM85 and CM33.                                                                                        |  |

|                                                                                                                                                                                                                |  |

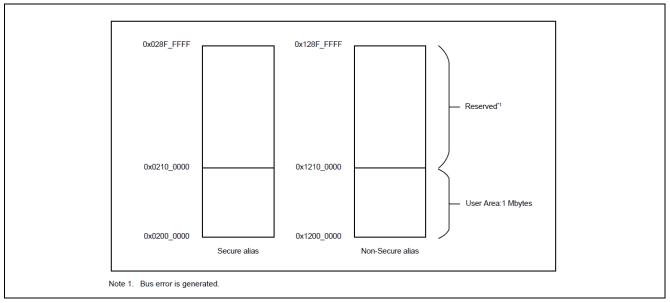

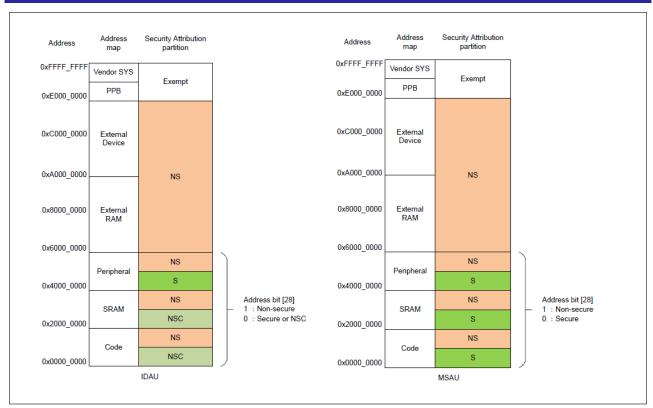

All these memories are not in a contiguous area. There are reserved areas for internal/future use. The memory layout can be mainly divided into 4 different categories. Internal code memory (MRAM), Internal data memory (SRAM), External memory address space interface, and Peripheral Registers. Another important feature with RA8P1 MCU is that the memory regions are aliased to Secure and Non secure areas.

For instance, the regions from 0x0000\_0000 to 0x0FFF\_FFFF are aliased to 0x1000\_0000 to 0x1FFF\_FFFF for Secure and Non secure access.

Details of the individual memory will be explained in detail in the following sections. Figure 4 shows the RA8P1 Memory Map in detail.

Figure 4. RA8P1 Dual-core Memory Map

## 2.1 Internal Memory

In RA8P1, On-chip memory plays a critical role in system performance by enabling fast data access, reducing latency, and ensuring data integrity. The memory architecture incorporates various performance

Internal memory can be mainly divided into Code MRAM, SRAM, TCM for Instruction and Data access. From Figure 4, you can see the MRAM placed at an address of (0x0200\_0000 - 0x0210\_0000) for secure access and (0x1200\_0000-0x1210\_0000) for non-secure access. Similarly, the SRAM is placed at an address of (0x2200\_0000 - 0x221A\_0000) for secure access and (0x3200\_0000 - 0x321A\_0000) for non-secure access. In addition, TCM for Instructions are placed at an address of (0x0000\_0000 - 0x0001\_1FFF) for secure access and (0x1000\_0000 - 0x1001\_1FFF) for non-secure access. TCM for data are placed at an address of (0x2000\_0000 - 0x2001\_1FFF) for secure access and (0x3000\_0000 - 0x3001\_1FFF) for non-secure access.

SiP-Flash area (OSPI1 CS1 area) which is (0x0800\_0000 – 0x1000\_0000) for secure, and SiP-Flash area (OSPI1 CS1 area) which is (0x1800\_0000 – 0x2000\_0000) for non-secure are selectively available on MCU devices where the OSPI flash is inside the MCU instead of having external OSPI as part of the board.

On-chip SRAM (SRAME) which is (0x221A\_0000 - 0x221D\_4000) for secure access and (0x221A\_0000 - 0x321D\_4000) for non-secure access are available in selective MCU devices where additional SRAM for large data storage are placed inside the MCU.

Internal memory also has Extra MRAM sections. This is not used for storing the program but for internal use. On-chip flash (option-setting memory) is placed at an address of (0x12E0\_0000 - 0x12D0\_0000, 0x12A0\_0000 - 0x1300\_0000) for secure access and (0x02E0\_0000 - 0x02D0\_0000, 0x02A0\_0000 - 0x0300\_0000) for non-secure access as part of the Extra MRAM.

#### 2.1.1 MRAM Code Memory

Magneto resistive Random Access Memory (MRAM) is a cutting edge non-volatile memory technology that brings together the speed of SRAM with the long-term data retention capabilities of flash memory. This hybrid advantage makes MRAM particularly suitable for embedded systems, where fast read/write access, low power consumption, and high endurance are critical. One of MRAM's standout features is its ability to retain data without power, contributing to improved energy efficiency, system reliability, and rapid recovery in the event of a power failure. These characteristics are especially beneficial in real-time and embedded applications, where consistent performance and resilience are essential. In systems with dual-core architectures, MRAM further enhances efficiency by minimizing memory requirements, supporting more compact and power-conscious designs.

A key differentiator of MRAM lies in its operational advantages over traditional memory types. Unlike flash memory, which necessitates time-consuming erase cycles before data can be rewritten, MRAM supports direct bit-level writing without prior erasure. This enables significantly faster and more efficient read/write operations. Furthermore, while flash memory degrades after a limited number of write/erase cycles, MRAM boasts a much higher endurance, capable of enduring millions of cycles with minimal wear. This exceptional durability makes MRAM ideal for applications demanding frequent data updates.

MRAM also excels in power efficiency. It requires less energy to operate and does not depend on high-voltage programming, which aligns well with the needs of modern low-power embedded systems. Additionally, MRAM demonstrates robust resistance to environmental challenges such as radiation and electromagnetic interference, ensuring stable operation in demanding sectors like automotive, aerospace, and industrial automation.

In conclusion, MRAM offers a compelling mix of speed, endurance, and non-volatility, integrating the strengths of SRAM, flash, and DRAM technologies. This makes it an ideal memory solution for microcontrollers and embedded systems that require a balance of performance, data integrity, and energy efficiency.

In the Renesas RA8P1 microcontroller, the code MRAM serves as storage for instructions and constant data, functioning similarly to flash memory. It offers up to 1 MB of user-accessible memory, segmented into code MRAM and option-setting memory. MRAM programming is performed through a page buffer and option setting memory in extra MRAM using MACI commands, and both code and option-setting memory support simultaneous read/write operations during background tasks. Programming granularity includes 1, 2, 4, or 8

bytes for general data, and 16 or 32 bytes for code MRAM. While it does not support dual-bank or block swap functionality, it provides a wide range of security features including tamper protection, startup area protection, permanent block protection, TrustZone support, and an anti-rollback counter. Additional safety features include software-based protection, ECC support for correcting double-bit errors and detecting triple-bit errors, and robust error detection for invalid operations. The boot area can be securely set to sizes of 8 KB, 16 KB, or 32 KB, ensuring safe firmware updates.

Table 2. RA8P1 MRAM Memory specification

| Item                         | Code MRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Option-setting memory in extra MRAM                                                                                   |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Memory capacity              | User area: 1 MB max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | See section 7, Option-Setting Memory.                                                                                 |

| Read cycle                   | See section 60.5.2. MRCFREQ : Code MRAM Frequency Notifications Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | See section 60.5.3. MREFREQ : Extra MRAM Frequency Notifications Register                                             |

| Programming method           | Write page buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MACI command                                                                                                          |

| Protection                   | Protects against erroneous rewriting of the MRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                     |

| Dual bank function           | Not available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Not available                                                                                                         |

| Block swap function          | Not available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Not available                                                                                                         |

| Background operations (BGOs) | The code MRAM can be read while option-se Option-setting memory can be read while the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                       |

| Units of programming         | Program data buffer: 1/2/4/8 bytes<br>Code MRAM: 32 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16 bytes                                                                                                              |

| MACI command                 | Not available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Program: 16 bytes Forced stop Status clear Configuration set: 16 bytes Increment counter: 1 bit Read counter: 8 bytes |

| Security function            | <ul> <li>Protect against illicit tampering with or readir</li> <li>OFS area protection</li> <li>Startup area select setting protection         <ul> <li>BTFLG, BTSIZE and MSUACR register</li> </ul> </li> <li>Permanent block protect setting protection         <ul> <li>User area is permanently protected fron function.</li> </ul> </li> <li>MRAM protection for TrustZone         <ul> <li>Protection for MRAM area (program)</li> <li>Protection for register</li> </ul> </li> <li>Extra MRAM program mode entry protection</li> <li>Anti-rollback counter</li> <li>HUK protection</li> </ul>         | s are protected by the FSPR bit.  In programming operation by permanent block protect                                 |

| Safety function              | Software protection  • MACI command protection by MENTRYR register  • User area protection by MRCP0 and MRCP1 registers  • User area protection by the block protection setting.  Error protection  • Error is detected when unintended commands or prohibited settings occur. The MACI command is not accepted after an error detection.  Boot area protection  • The startup area select function allows customer to safely update the boot firmware. The size of the startup area can be selected from 8 KB, 16 KB or 32 KB.  ECC support for double-bit error correction and triple-bit error detection. |                                                                                                                       |

| Interrupt request            | MRAM_MRCRD (Code MRAM read error)     Enabled by INTENBTC and INTENBDC bits.      MRAM_MRERD (Extra MRAM read error)     Enabled by INTENBTE and INTENBDE bits.      MRAM_MRCPR (Code MRAM sequencer error)     Enabled by MRCAEIE bits.      MRAM_MREPR (Extra MRAM sequencer error)     Enabled by CMDLKIEE and MREAEIE bits.      MRAM_ENDOFPE (Extra MRAM sequencer ready (processing end))     Enabled by MRDYIE bit.                                                                                                                                                                                   |                                                                                                                       |

Figure 5. RA8P1's Internal MRAM Memory specifications

Additionally, the code MRAM is designed to store user application code and constant data, with support for self-programming. This allows applications to update the code memory without requiring external programming tools, enabling seamless and efficient in-field firmware updates. To assist with this, the Renesas Flexible Software Package (FSP) provides HAL drivers for modifying both code and data flash memory.

In the RA8P1 MCU series, the MRAM code memory serves as non-volatile storage for the firmware executed by the MCU upon power-up. This memory holds the core instructions that drive the system's functionality. Programming or writing to the MRAM code memory is typically carried out using serial-based tools, such as the Renesas Flash Programmer or J-Link Flash Programmer.

The memory layout can be viewed in Figure 6, which illustrates the linear memory map of the MRAM code memory.

Figure 6. RA8P1 Map of the Code MRAM Memory in Linear Mode

#### 2.1.1.1 Prefetch Buffer

The MRAM prefetch buffer feature of RA8P1 accelerates CPU instruction fetches from the code MRAM by reducing latency between the bus master and memory access. Specifically implemented for the target memory region 0x0000\_0000 to 0x00FF\_FFFF (1 MB), it supports instruction fetches from both CPU0 and CPU1 in a dual-core configuration. Each CPU is equipped with a 64-byte prefetch buffer, which helps anticipate and preload instructions before they are requested by the processor.

The buffer is designed as a fully associative cache structure, which allows any incoming instruction address to map to any entry in the buffer, maximizing hit rates and minimizing fetch delays. Each entry holds 256 bits of aligned instruction data, and the prefetch buffer contains 2 such entries, enabling efficient lookahead and retrieval. This structure ensures that instruction streams are delivered quickly to the CPU cores, significantly improving execution speed when running code from MRAM, and maintaining system responsiveness even when accessing non-volatile memory.

| Function          | Implementation                                                                              |

|-------------------|---------------------------------------------------------------------------------------------|

| Target Region     | 0x000_0000 ~ 0x00F_FFFF (1 MB)                                                              |

| Target Bus Master | CPU0 and CPU1 instruction fetch                                                             |

| Capacity          | 64 Bytes/CPU                                                                                |

| Associativity     | Full associative                                                                            |

|                   | 256 bits/entry (256 bits aligned data), 2 entries                                           |

| Access Cycle      | Hit: 0 wait Miss: See section 60.5.2. MRCFREQ : Code MRAM Frequency Notifications Register. |

Figure 7. RA8P1 MRAM Prefetch buffer overview

## 2.1.1.2 Programming Procedure

Code MRAM programming is performed in 32-byte units via a program data buffer accessed through the system bus. To avoid bus stalls during programming, only one bus master should perform write access at a time, and data should not cross 32-byte boundaries. Before writing, the system must check that no other programming is in progress using the PRGBSYC and ABUFFULL flags in the MRCPS register. Data is written to the buffer and programmed into MRAM when one of the following occurs, 1)the buffer is full, the write crosses a 32-byte boundary, or 2)the MRCFL bit is set. Errors during programming can be detected via PRGERRC and ECCERRC bits. For extra MRAM programming procedures, refer to MACI commands in section 60.7 in the RA8P1's UM.

#### 2.1.1.3 Operating Mode - MRAM Read/Program Mode

Code MRAM and extra MRAM operate in separate read and program modes, with automatic transitions between them based on specific conditions. For code MRAM, programming mode is triggered when the program data buffer is full, a write crosses a 32-byte boundary, or the MRCFL bit is set. Once programming is completed, the system automatically returns to reading mode. For extra MRAM, mode transitions are manually controlled by modifying the MENTRYR register or through W-HUK zeroization. When MENTRYR = 0x0000 and no zeroization is active, the MRAM remains in read mode; changing these conditions switches it to program mode.

## 2.1.1.4 MACI Commands - Programmable Area with MACI commands

Extra MRAM includes programmable areas for security, safety, and system configuration, which can be accessed using the MACI command. These areas include One-Time Programmable (OTP) regions, with and without Error Correction Code (ECC). In OTP areas with ECC, each 16-byte unit can be programmed only once, and bits can only change from 1 to 0, reprogramming is not allowed due to ECC constraints. In OTP areas without ECC, 16-byte units can be programmed multiple times as long as no bits are changed from 0 to 1. Reliability in non-ECC areas is ensured through redundant data configurations.

| Address<br>(Offset address: BASE_MC) | Area name                                                                | Memory type | ECC       |

|--------------------------------------|--------------------------------------------------------------------------|-------------|-----------|

| 0x00C9_F020 ~ 0x00C9_F0AF            | Configuration                                                            | MRAM        | Use       |

| 0x00C9_F0C0 ~ 0x00C9_F7FF            | Configuration                                                            | MRAM        | Use       |

| 0x00E0_7400 ~ 0x00E0_74BF            | Hash of OEM_ROOT_PKn ( n = 0 to 3)                                       | ОТР         | Use       |

| 0x00E0_7600 ~ 0x00E0_760F            | FSBL setting                                                             | OTP         | Use       |

| 0x00E0_7610 ~ 0x00E0_769F            | Start address of measurement report<br>Start address of Code Certificate | OTP         | Use       |

| 0x00E0_76A0 ~ 0x00E0_76FF            | General purpose OTP                                                      | OTP         | Use       |

| 0x00E1_7700 ~ 0x00E1_777F            | Permanent Block Protect Setting for Secure                               | OTP         | Don't use |

| 0x00E1_7780 ~ 0x00E1_77FF            | Permanent Block Protect Setting                                          | ОТР         | Don't use |

| 0x00E1_7900 ~ 0x00E1_790F            | OFS Permanent Lock Setting                                               | OTP         | Don't use |

| 0x00E1_7910 ~ 0x00E1_791F            | REVOKE                                                                   | ОТР         | Don't use |

| 0x00E1_7920 ~ 0x00E1_792F            | Zeroization HUK in OTP Enable                                            | OTP         | Don't use |

| 0x00E1_7930 ~ 0x00E1_793F            | Anti-Rollback Counter Setting                                            | OTP         | Don't use |

| 0x00E1_7950 ~ 0x00E1_79FF            | Reserved                                                                 | ОТР         | Don't use |

| _                                    | Anti-Rollback Counter                                                    | OTP         | Don't use |

Figure 8. RA8P1 Programmable area with MACI commands

## 2.1.1.5 Security function

The extra MRAM sequencer in security-enabled products provides key security features, including permanent protection of Option Function Select (OFS) settings, startup area and size security flags, and permanent block protection. It also supports TrustZone-based MRAM protection, safeguards for the extra MRAM configuration area, an anti-rollback counter, and protection for critical keys such as the Hardware Unique Key (HUK) and OEM ROOT KEY.

The software protection function restricts MRAM programming operations based on specific register and configuration settings. It includes multiple layers of protection such as code MRAM programming protection, block-level protection, error detection, and startup program protection, enhancing system security and preventing unauthorized memory modifications.

#### 2.1.1.7 Boot Mode

There are two serial programming modes for boot operations: one using the SCI9 interface and the other using the USBFS interface. Each mode utilizes specific I/O pins and supports different communication interfaces, as detailed in Figure 9 and Figure 10.

| Pin Name       | I/O    | Mode to be Used                                                              | Use                                                     |

|----------------|--------|------------------------------------------------------------------------------|---------------------------------------------------------|

| MD             | Input  | Boot mode<br>(for the SCI interface)<br>Boot mode<br>(for the USB interface) | Selection of operating mode                             |

| P208/RXD9      | Input  | Boot mode                                                                    | For host communication (to receive data through SCI)    |

| P209/TXD9      | Output | (for the SCI interface)                                                      | For host communication (to transmit data through SCI)   |

| USB_DP, USB_DM | I/O    | Boot mode                                                                    | Data input/output of USB                                |

| USB_VBUS       | Input  | (for the USB interface)                                                      | Detection of connection and disconnection of USB cables |

Figure 9. RA8P1 I/O Pins Used in Boot Mode

| Main clock oscillator or external clock is connected | Yes            | No              | No              |

|------------------------------------------------------|----------------|-----------------|-----------------|

| Sub clock oscillator is connected*1                  | Yes or No      | Yes             | No              |

| Available interface                                  | SCI or USB     | SCI or USB      | SCI             |

| Tool connection time*2                               | Up to 1 second | Up to 2 seconds | Up to 3 seconds |

Figure 10. Available Communication Interface Used in Boot Mode

Note: For the detailed description of MRAM Programming, Operating Modes, Protection function, security function and Boot Mode please refer to the MRAM section of the RA8P1 User's Manual.

## 2.1.2 Option Setting Memory

The option-setting memory determines the state of the MCU after a reset. It is allocated to the configuration setting area and the program flash area of the MRAM memory. The available methods of setting are different for the two areas. Option setting memory may differ in size and layout for Cortex-M85 and Cortex-M33 based devices.

The registers are detailed in the "Option Setting Memory" chapter in the RA8P1 User's Hardware Manual.

Option-setting memory registers have a discontinuous address space layout in the code flash memory. Sometimes the registers may be located in a portion of the MRAM memory which is near reserved areas in the internal MRAM. It is possible that some customers may inadvertently store data in the registers of option-setting memory or write into the reserved area in internal MRAM. This may result in improper functionality. It is advised that the user check to ensure that no unwanted data is written to these locations prior to programming the internal MRAM by reviewing the map file or s-record files generated by the compiler upon creation of the binary. For instance, settings in the flash option registers can enable the Independent Watchdog Timer (IWDT) immediately after reset. If data stored in program ROM inadvertently overlaps the option setting memory register, it is possible to turn on the IWDT on without realizing it. This may cause the debugger to have communication problems with the board. Additionally, security attribution of code flash option-setting memory can impact which value is applied at runtime, so user must confirm that required values are programmed into the option-setting memory.

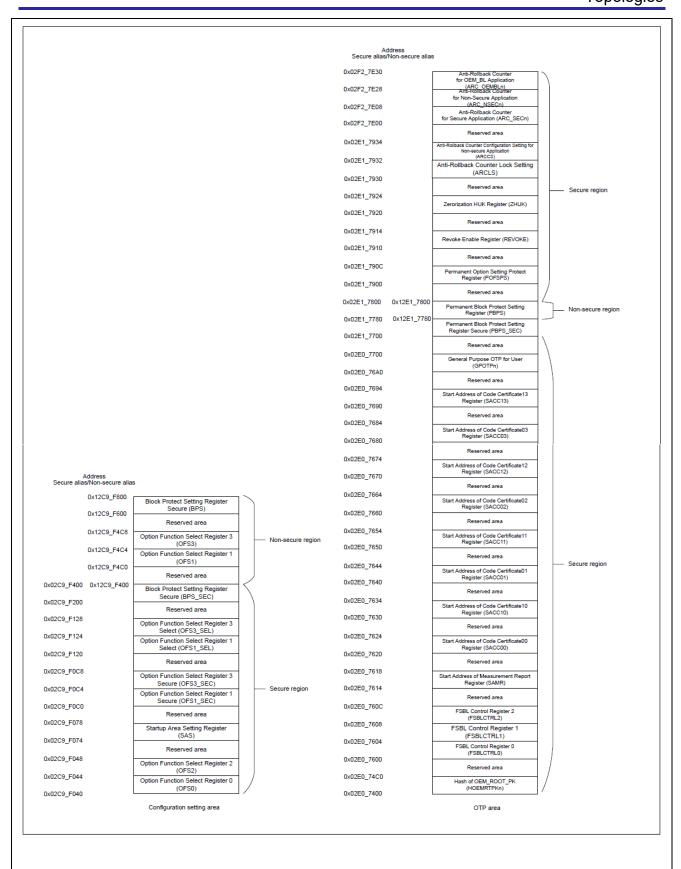

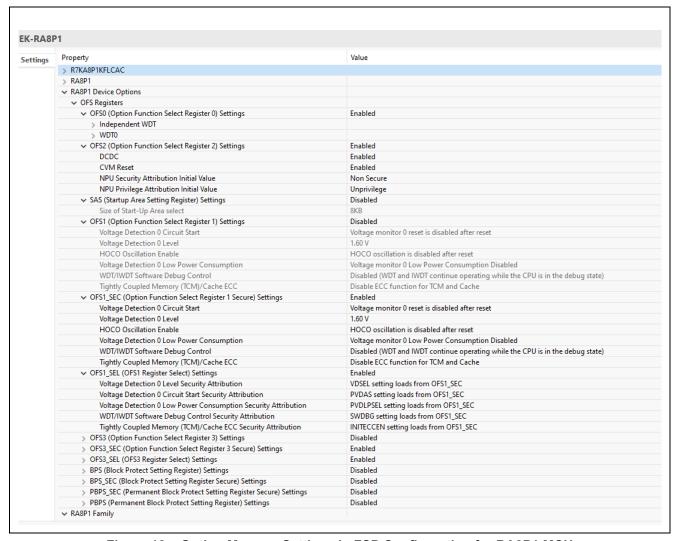

The image below shows the option setting memory, which consists of the option function select registers on RA8P1.

Figure 11. RA8P1 Option Settings Memory Map

## 2.1.2.1 Option Setting Memory Registers

Following is a summary of the option setting memory registers. Make sure that they are configured properly before first programming the MCU for startup. To check the configuration, review the map file, and output file (using hex or s-record format) to confirm the values programmed into the option setting memory registers.

Table 3. RA8P1 Memory

| OFC0 ===i=+==              | ntrol Settings                                                                        |

|----------------------------|---------------------------------------------------------------------------------------|

| OFS0 register              | Independent Watchdog Timer (IWDT) auto start                                          |

|                            | IWDT timeout, frequency, windowing, interrupt type, and low power mode                |

|                            | behavior                                                                              |

|                            | Watchdog Timer (WDT) auto start                                                       |

|                            | WDT timeout, frequency, windowing, interrupt type, and low power mode                 |

|                            | behavior                                                                              |

| OFS1 register              | PVD0 startup settings after reset                                                     |

|                            | HOCO startup settings after reset                                                     |

|                            | Software Debug Control                                                                |

|                            | Set ECC function of TCM and CACHE                                                     |

| OFS2 register              | DCDC enable at reset                                                                  |

| <b>Code Memory Setting</b> | I                                                                                     |

| SAS register               | Startup area selection                                                                |

| DUALSEL register           | Code Flash memory mode upon reset                                                     |

| BANKSEL registers          | Controls swapping banks at the next reset                                             |

| BPS, PBPS registers        | Turns off erasing and programming capability of selected blocks of code flash         |

| , 3                        | memory. Note that when PBPS are set to disable the flash erase and                    |

|                            | programming, it can never be reverted.                                                |

| Firmware Verification      | and Update Control Registers                                                          |

| FSBLCTRLx                  | Controls operation of the First Stage Boot Loader which verifies the integrity and    |

| registers                  | authenticity of an OEM boot loader (called OEM_BL) starting at the beginning of       |

| -                          | application executable memory.                                                        |

| SACCx register             | Identifies Locations in code flash memory where x.509 certificates are stored for     |

| -                          | validating the application when FSBL is operating in Secure Boot mode.                |

|                            | SACC0/1 is selected by the FSBL based on the MCU Start Area Selection and             |

|                            | the Bank mode. User can reference the "Secure Boot" section in the Hardware           |

|                            | User's Manual to understand this selection process.                                   |

| SAMR register              | FSBL stores the measurement report to the SRAM address specified by the SAMR register |

| HOEMRTPK register          | This register can be programmed only by the MCU boot firmware. It is                  |

| 3                          | programmed after a code image is validated. This register contains a processed        |

|                            | Hash value.                                                                           |

| CFGDxLOCK register         | Specify write protection for corresponding Lockable Configuration Data Areas in       |

|                            | Data Flash. Note that when the protection is enabled, it can never be reverted.       |

| ARCLS register             | Controls Anti Rollback Counter Lock functionality. Note that if this lock             |

|                            | functionality is enabled, it can never be reverted. This register can be set using    |

|                            | the Renesas Flash Programming (RFP) tool.                                             |

| ARCCS register             | Configures the Anti Rollback Counter operation for the non-secure application.        |

|                            | Note that when this configuration is disabled, the "Increment Counter" or Read        |

|                            | Counter" command cannot be issued anymore. This register can be set using the         |

|                            | Renesas Flash Programming (RFP) tool.                                                 |

| ARC_SECn registers         | Anti-Rollback Counter for Secure Application                                          |

| ARC_NSECn                  | Anti-Rollback Counter for Non-Secure Application                                      |

| registers                  |                                                                                       |

| ARC_OEMBLn                 | Anti-Rollback Counter for OEMBL                                                       |

| registers                  |                                                                                       |

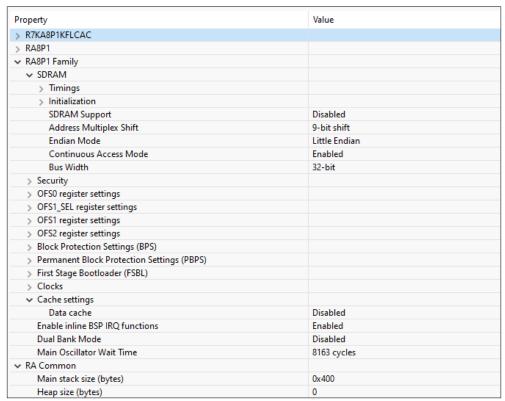

Renesas FSP Configurator supports setting of option memory in BSP settings, as shown in the following Figure 12 for RA8P1 MCU.

Figure 12. Option Memory Settings in FSP Configuration for RA8P1 MCU

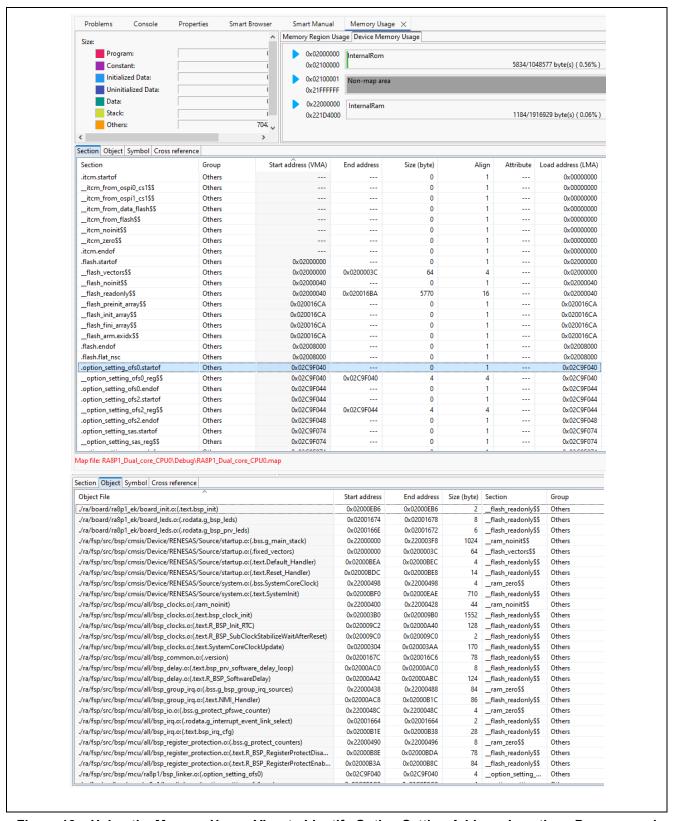

You can also use the objdump command to check the settings of the option setting memory. Following is an example for dumping the option setting registers:

Figure 13. Using the Memory Usage View to Identify Option Setting Address Locations Programmed

## 2.1.3 On-Chip ROM

RA8P1's On-chip immutable read-only memory (ROM) contains the First Stage Bootloader (FSBL) which is a bootloader that is permanently embedded in read-only memory, and it cannot be altered or modified. The primary purpose of such a bootloader is to provide the initial bootstrapping process for the MCU while

ensuring its security and integrity of the first application (typically, an OEM developed bootloader) executed. FSBL is programmed into the ROM during the manufacturing process. This cannot be altered without physically altering the hardware, making it immune to external tampering or unauthorized modifications. FSBL enhances the security of a device by preventing unauthorized or malicious code from being loaded during the boot process. This ensures that only trusted and verified code can execute.

The primary function of the FSBL is to initialize the hardware and load the second-stage bootloader or main firmware from a secure and trusted source, such as a secure storage medium or a secure boot mechanism. In RA8P1 MCU, the FSBL plays a critical role in implementing secure boot procedures. It verifies the authenticity and integrity of the second-stage bootloader or firmware before allowing it to execute. This helps protect against firmware-level attacks and unauthorized code execution. The FBSL can also facilitate firmware recovery in case of a system failure or corruption of the main firmware. It can be designed to have a minimal and stable codebase for restoring the system to a known good state.

The operation of the FSBL is managed by the Option-Setting Registers. The registers used during development phase can be configured using the BSP tab property setting. The FSBL when enabled can verify the integrity and authenticity of an OEM bootloader (OEM\_BL) or a normal application (with no bootloader capability) starting at the application executable memory. The OEM BL or a normal application is verified when it is initially programmed as well as prior to execution. For RA8P1 MCUs, user can use the FSP MCUboot module to establish the OEM\_BL or use their own custom bootloader.

For specifications on secure boot operations, user can reference the RA8P1 User's Manual: Hardware "section 52.7 Secure Boot". For examples on how to use the Secure Boot feature, user can reference the application project (OEM BL and Application Design Using the RA8 First Stage Bootloader).

#### 2.1.4 SRAM

RA8P1 contains on-chip 2MB (256 KB CM85 TCM RAM, 128 KB CM33 TCM RAM and 1664 KB of users SRAM) of on-chip high-speed SRAM with Error Correction Code (ECC).

#### **SRAM Specification**

| Parameter               |                  | SRAM0                                                                                                                                                                                                                      | SRAM1                                                                                                                                                                                                                                                                                                          | SRAM2                         | SRAM3                         |

|-------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|

| SRAM capacity           |                  | 512 KB                                                                                                                                                                                                                     | 512 KB                                                                                                                                                                                                                                                                                                         | 512 KB                        | 128 KB                        |

| SRAM address            | Secure alias     | 0x2200_0000 to<br>0x2207_FFFF                                                                                                                                                                                              | 0x2208_0000 to<br>0x220F_FFFF                                                                                                                                                                                                                                                                                  | 0x2210_0000 to<br>0x2217_FFFF | 0x2218_0000 to<br>0x2219_FFFF |

|                         | Non-secure alias | 0x3200_0000 to<br>0x3207_FFFF                                                                                                                                                                                              | 0x3208_0000 to<br>0x320F_FFFF                                                                                                                                                                                                                                                                                  | 0x3210_0000 to<br>0x3217_FFFF | 0x3218_0000 to<br>0x3219_FFFF |

| ECC region*1            | Secure alias     | 0x221A_0000 to<br>0x221A_FFFF                                                                                                                                                                                              | 0x221B_0000 to<br>0x221B_FFFF                                                                                                                                                                                                                                                                                  | 0x221C_0000 to<br>0x221C_FFFF | 0x221D_0000 to<br>0x221D_3FFF |

|                         | Non-secure alias | 0x321A_0000 to<br>0x321A_FFFF                                                                                                                                                                                              | 0x321B_0000 to<br>0x321B_FFFF                                                                                                                                                                                                                                                                                  | 0x321C_0000 to<br>0x321C_FFFF | 0x321D_0000 to<br>0x321D_3FFF |

| Access                  |                  | Wait states are not inserted into the access cycle by default. If the ICLK frequency is greater than 125 MHz, a wait state is required. If the ICLK frequency is less than or equal 125 MHz, a wait state is not required. |                                                                                                                                                                                                                                                                                                                |                               |                               |

| Data retention function |                  | Not available in Deep Software Standby mode                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                |                               |                               |

| Module-stop funct       | tion             | Module-stop state can be set to reduce power consumption                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                |                               |                               |

| Error checking          |                  | SEC-DED (Single-Error Correction and Double-Error Detection Code: 64-bit data with 8-bit ECC code)                                                                                                                         |                                                                                                                                                                                                                                                                                                                |                               |                               |

| Security                |                  | space is controlled by<br>(SFR) space is control                                                                                                                                                                           | TrustZone Filter is integrated for memory access and SFR access. Access to the memory space is controlled by setting the memory Security Attribution (SA). And access to I/O space (SFR) space is controlled by setting the register Security Attribution (SA). See section 59.3.5. TrustZone Filter function. |                               |                               |

Note 1. When ECC function is disabled, it is used as a data region and can be accessed directly. When ECC function is enabled, direct access is disabled. When bypass is enabled, direct access to ECC bit is possible

#### Figure 14. RA8P1 Internal SRAM Memory specification

ECC with SRAM: ECC (Error-Correcting Code) memory is used to detect and correct single-bit errors in SRAM. ECC memory is typically used in mission-critical applications where data integrity is of utmost importance.

There are some drawbacks to using ECC memory. ECC memory typically has higher latency compared to non-ECC memory. This is because ECC memory requires additional time to check and potentially correct errors in data. ECC memory modules are more expensive than non-ECC memory. This can be a significant drawback, especially for cost-sensitive applications like consumer products, where data integrity is not as critical. ECC memory requires additional hardware and logic to implement error checking and correction. This overhead can result in slightly lower memory bandwidth and increased power consumption, although the impact is generally minimal.

ECC for SRAM can be enabled or disabled via the ECCMOD[1:0] bits in the SRAMCRn register. When enabled, it uses SEC-DED (Single-Error Correction, Double-Error Detection) with 8-bit check bits for every 64-bit data. ECC supports correction of 1-bit errors and detection of 2-bit errors. Depending on whether error checking is enabled, corresponding status bits (ERRn0, ERRn1) may be updated. When ECC is disabled, neither error correction nor detection occurs. After power-on or exiting Deep Software Standby mode, SRAM contains undefined data, so it's recommended to initialize used areas with 64-bit writes and ECC enabled (with or without error checking) to prevent ECC errors.

The SRAM interrupt source includes an ECC error, and TrustZone® filter error. ECC error can choose non-maskable interrupt or reset by SRAMCR0.OAD or SRAMCR1.OAD bit. The SRAM interrupt occurs when one error status in the SRAMESR register is set to 1, the SRAM interrupt continues to occur until the SRAMESR register flag is cleared. When common memory errors occur (NMISR.CMST=1 or RSTSR1.CMSR=1), read SRAMESR and check SRAM interrupt source.

| Name   | Interrupt Source           | DTC Activation | DMAC Activation |

|--------|----------------------------|----------------|-----------------|

| ECCERR | ECC error (SRAMs with ECC) | Not possible   | Not possible    |

| TZFLT  | TrustZone filter error     | Not possible   | Not possible    |

Figure 15. RA8P1 SRAM Interrupt source

**SRAM Wait State:** When ICLK frequencies are higher than 125 MHz, do not set 0x00 in wait enable bit for the SRAMWTSC register, in order to insert a wait cycle. When the wait is not inserted, the operation is not guaranteed. Depending on the operating frequency of ICLK, the WAIT setting for SRAM access has the following conditions.

- 250 MHz ≥ ICLK > 125 MHz = 1 wait

- 125 MHz ≥ ICLK = No-wait

#### Instruction Fetch from SRAM:

When executing code from SRAM, it's important to properly initialize the SRAM area to ensure correct CPU instruction prefetching. If the CPU attempts to prefetch from uninitialized memory, ECC errors may occur. To prevent this, initialize an extra 12-byte region beyond the program's end address, aligned to an 8-byte boundary. Renesas recommends using NOP instructions for this initialization.

## **ECC Error Checking in SRAM:**

Since SRAM contents are undefined after power-on, reading uninitialized memory can trigger ECC errors. SRAM reads occur in 8-byte (64-bit) units, so all memory should be initialized in 8-byte aligned segments before access when ECC error checking is enabled.

#### 2.1.5 TCM (Tightly Coupled Memory)

TCM is a specialized, high-speed memory closely integrated with the CPU cores of the RA8P1 MCU. Strategically placed near the CPU core, TCM enables low-latency, deterministic access to critical program instructions and data, allowing for quick instruction and data fetch and execution. Its close physical proximity significantly reduces access delays and avoids contention that may occur with shared memory resources.

Note: To allocate and configure the TCM memory resources using FSP configurator, please refer to the application note "R01AN7881EU0100-developing-with-ra8-dual-core-mcu"

Figure 16. TCM Memory Architecture for M85 and M33 core in RA8P1

## 2.1.5.1 ITCM (Instruction Tightly Coupled Memory)

ITCM is a specialized, high-speed memory closely integrated with the CPU cores of the RA8P1 MCU. Strategically placed near the CPU core, ITCM enables low-latency, deterministic access to critical program instructions, allowing for quick instruction fetch and execution. Its close physical proximity significantly reduces access delays and avoids contention that may occur with shared memory resources.

ITCM is ideal for storing time-sensitive code, such as ISRs, control loops, and high-frequency functions that demand consistent execution speed. To further enhance performance, TCM encompassing both ITCM and DTCM, and cache memory can be used in tandem with Helium™ technology. TCM offers single-cycle, deterministic access, making it particularly effective for minimizing latency in real-time operations. Placing critical code and frequently accessed data in TCM ensures fast, predictable execution, which is essential for performance-driven embedded applications.

In the RA8P1 MCU, the CM85 core (CPU0) is equipped with a 128 KB ITCM, organized as 16 blocks of 8 KB each and includes Error Correction Code (ECC) support. ECC functionality can be enabled via the OFS1.INITECCEN setting, and the ITCM is activated by default through the ITCMCR.EN = 1 configuration. This ITCM is physically separate from the main Flash memory, reducing contention and ensuring faster, low-latency instruction access compared to the relatively slower Flash interface.

For CPU0, ITCM is memory-mapped to:

- 0x0000\_0000 0x0001\_FFFF for secure access

- 0x1000 0000 0x1001 FFFF for non-secure access

Similarly, the CM33 core (CPU1) features a 64 KB Code Tightly Coupled Memory (CTCM), structured as 8 blocks of 8 KB each, also with ECC support. Like CPU0, ECC is controlled via OFS1.INITECCEN, and the memory is enabled by default with ITCMCR.EN = 1. The separation of CTCM from Flash memory helps maintain consistent performance by avoiding Flash access delays.

For CPU1, the CTCM is mapped to:

- 0x0000\_0000 0x0000\_FFFF for secure access

- 0x1000 0000 0x1000 FFFF for non-secure access

This architecture ensures that both cores benefit from deterministic, high-speed instruction fetches without contention from shared Flash resources.

For MCU based RTOS systems, the micro kernel can be placed at the ITCM to improve the speed of the system. Motor control algorithms can be placed at the ITCM for improved(i.e. deterministic) execution.

ITCM instructions do not pass through the Cache and do not impose any restriction on wait states. This allows for direct and deterministic access to instructions from this tightly coupled memory, improving execution speed for critical or time-sensitive code. Accessing instructions from ITCM typically incurs fewer or zero wait states compared to accessing instructions from slower memory regions like Flash memory. This reduction in wait states enhances real-time performance and responsiveness of the MCU.

Note: TCM access is unavailable when the CPU is in Deep Sleep, Software Standby, or Deep Software Standby modes.

#### FSP Supplied ITCM initialization happens in

```

ra\fsp\src\bsp\cmsis\Device\RENESAS\Source\system.c, inside the SystemInit().

/* Initialize ITCM RAM from ROM image. */

#if BSP_FEATURE_BSP_HAS_ITCM

bsp_init_itcm();

#endif

```

The linker script has a section .itcm\_data for the ITCM, users can place the data in the ITCM using the sample code in your application

```

#define ITCM_CODE     __attribute__((section(".itcm_data"), long_call))

ITCM_CODE void itcmfn() {

// Place your code logic here

}

```

Users can refer to the *High Performance with RA8 MCU using CM85 core with Helium*™ application note and application project which showcases the performance improvement using the ITCM.

## 2.1.5.2 DTCM (Data Tightly Coupled Memory)

DTCM is another specialized memory on RA8P1 MCUs, closely integrated with the MCU's core processor, similar to ITCM. DTCM, however, is primarily used for storing critical data that requires fast and deterministic access.

In the RA8P1 MCU, the CM85 core (CPU0) features a 128 KB DTCM, organized as 16 blocks of 8 KB, with Error Correction Code (ECC) support. DTCM provides fast, deterministic access to critical program data, making it ideal for variables and buffers that require low-latency, high-frequency access, such as those used in real-time processing.

Like ITCM, DTCM is physically located near the CPU core, separate from the main system RAM. This separation reduces memory access latency and avoids contention with shared memory resources, ensuring quick and predictable read/write operations. The deterministic nature of DTCM access is essential for real-time applications, where consistent timing is critical.

Due to its limited 128 KB capacity, developers must strategically allocate performance-critical data, such as control variables, sensor inputs, computation intermediates, or communication buffers, to DTCM. It is especially valuable in motor control, digital signal processing (DSP), and industrial control systems.

In RA8P1, DTCM is enabled by default via DTCMCR.EN = 1, and ECC can be activated through the OFS1.INITECCEN setting. It is mapped to the following address ranges:

- 0x2000\_0000 0x2001\_FFFF for secure access

- 0x3000 0000 0x3001 FFFF for non-secure access

DTCM is connected to both the CPUSAHBI and DMAC/DTC buses, enabling efficient data exchange across the system without performance bottlenecks.

In contrast, the CM33 core (CPU1) includes a 64 KB Instruction TCM (ITCM), organized as 8 blocks of 8 KB, also with ECC support. Like the CM85's ITCM, it is separate from Flash memory to prevent access delays. ECC can be enabled via OFS1.INITECCEN, and it is active by default (ITCMCR.EN = 1). Its memory map is:

- 0x0000 0000 0x0000 FFFF for secure access

- 0x1000 0000 0x1000 FFFF for non-secure access

This architecture enables both cores to perform time-critical operations with reliable and consistent performance, owing to the use of dedicated, tightly integrated memory subsystems.

In Software Standby mode the Data of TCM data is retained. Whereas in the Deep software standby mode it is not retained.

DTCM data does not pass through the Cache and does not impose any restriction on wait states. This allows for direct and deterministic access to data from this tightly coupled memory, improving faster access to critical or time-sensitive data. Accessing Data from DTCM typically incurs fewer or zero wait states compared to accessing data from external memories. This reduction in wait states enhances real-time performance by fast and deterministic access.

FSP Supplied DTCM initialization happens in ra\fsp\src\bsp\cmsis\Device\RENESAS\Source\system.c, inside the **SystemInit()**.

```

/* Initialize DTCM RAM from ROM image and zero initialize DTCM RAM BSS section..*/

#if BSP_FEATURE_BSP_HAS_DTCM

bsp_init_dtcm();

#endif

```

The linker script has a section .dtcm\_data for the DTCM, users can place the data in the DTCM RAM using the sample code in your application.

```

__attribute__((section(".dtcm_data"))) uint32_t my_array[64];

```

Users can refer to the *High Performance with RA8 MCU using CM85 core with Helium*™ application note and application project which showcases the performance improvement using the DTCM.

#### 2.1.6 Cache

Cache memory on RA8P1 is a high-speed, volatile memory that stores frequently accessed data to reduce the time it takes to access that data from the slower main memory or storage. The primary purpose of RA8P1's cache is to improve the overall performance of the system by providing faster access to frequently used data.

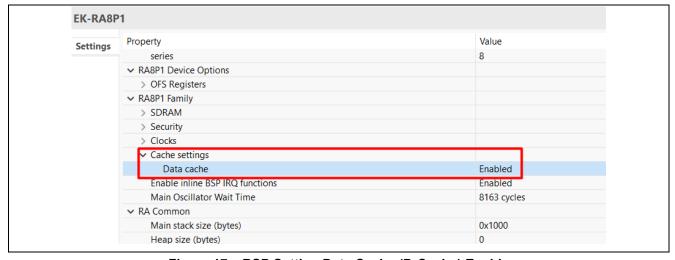

RA8P1 MCU provides 2 types of caches - Data Cache, and Instruction Cache to improve the processing speed and reduce latency. For CPU0(CM85 core) it is implemented by ARM and for CPU1(CM33 core) it is Renesas Implementation, and it is called C-cache which is for code/instruction and S-cache which is called system cache used for data

For CPU0 the Instruction cache: 16 KB with ECC and Data cache: 16 KB with ECC are inside the CPU0 core.

Whereas for the CPU1 Code-bus Cache (C-Cache): 16 KB with ECC on Cortex-M33 Code AHB interface (C-AHB) and another one is System-bus Cache (S-Cache): 16 KB with ECC on Cortex-M33 System AHB interface (S-AHB).

## 2.1.6.1 Data Cache

RA8P1 MCU's CPU0 and CPU1 provides 16 KB of Data L1 Cache with ECC. L1 cache on the CPU side is used to store frequently accessed data to reduce the time it takes for the CPU to retrieve information from the main memory (RAM). This helps in accelerating program execution and data processing. The Cortex®-M85 processor L1 Data cache has the following features.

- It is a four-way set-associative cache.

- It has a cache line size of 32 bytes.

- It supports the following inner memory attributes and allocation hints for Non-shareable memory:

- > Write-Back and Write-Through Cacheable.

- Read-Allocate and No Read-Allocate.

- Write-Allocate and No Write-Allocate.

- Transient and Non-transient. Clean cache lines that are associated with Transient memory are prioritized for eviction over lines that are associated with Non-transient memory.

Allocation into the L1 data cache depends on inner memory attributes only.

- The outer and inner memory attributes are exported on the Manager AXI (M-AXI) interface to support further system-level caching.

- The shareability attribute forces the region to be treated as non-cacheable, regardless of the inner memory attributes. This enables maintaining coherency at the system-level.

#### 2.1.6.2 Instruction Cache

RA8P1 MCU's CPU0 and CPU1 provides 16KB of L1 Instruction Cache with ECC. L1 cache on CPU side is used to store frequently accessed instructions to reduce the time it takes for the CPU to retrieve information from the slave memory device used for retrieving instructions(code memory). This helps in accelerating program execution and data processing. The Cortex®-M85 processor L1 Data cache has the following features.

- It is a two-way set-associative cache.

- It has a cache line size of 32 bytes.

- It does not allow writes to be performed, except for allocations.

- It only supports read-allocate for inner cacheable memory. Write-Allocate, Write-Back, Write-Through, and Transient attribute hints are ignored. Allocation into the L1 data cache depends on inner memory attributes only.

- Outer and inner memory attributes are exported on the Manager-AXI (M-AXI) interface to support further system-level caching.

- The shareability attribute is ignored for instruction side accesses.

- The inner cache ability attributes are always respected.

Debug accesses from the Debug AHB (D-AHB) subordinate interface on the processor cannot read information from the instruction cache.

Software or a debugger must use the direct cache access registers to read the contents of RAM arrays. The instruction cache is logically organized into two sets of RAM arrays. The dimensions of these RAM arrays vary with the cache size and the inclusion of Error Correcting Code (ECC) logic.

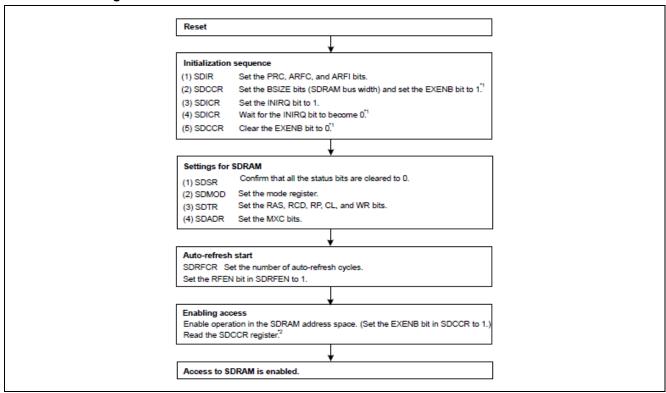

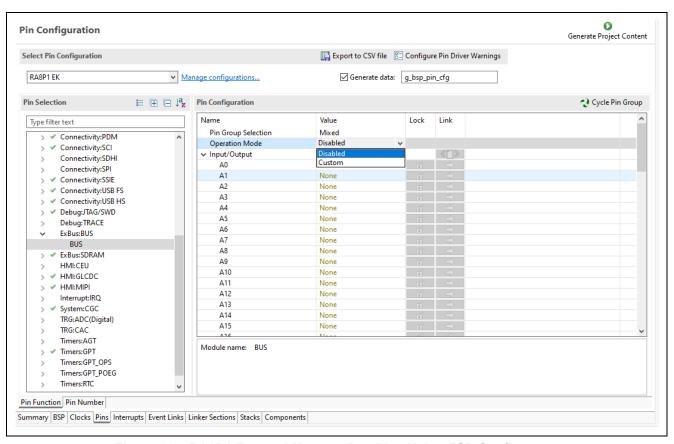

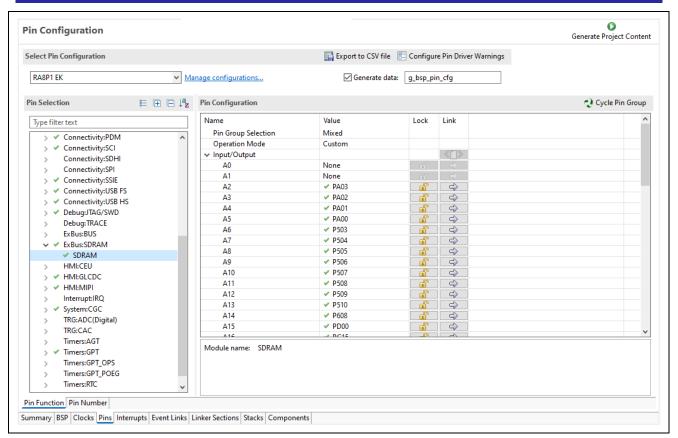

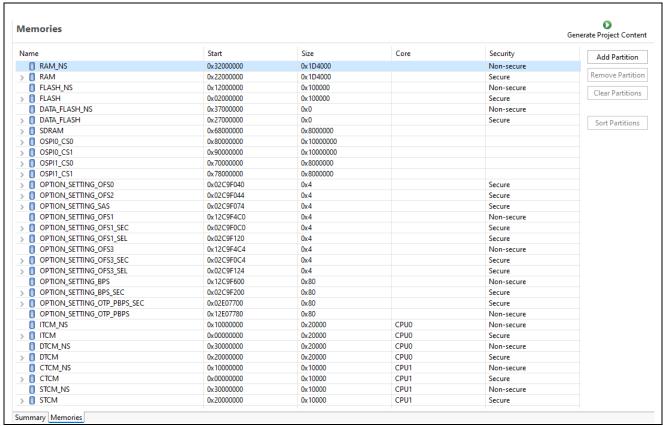

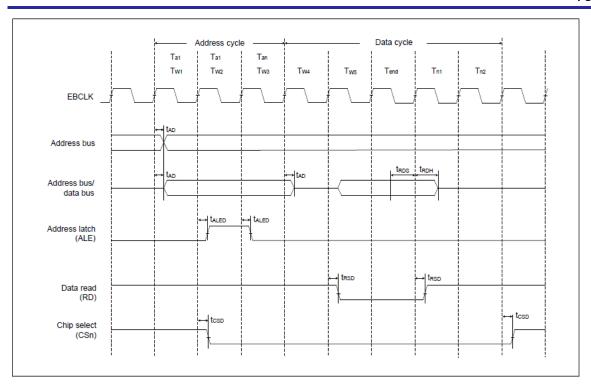

#### 2.1.6.3 How to Enable / Disable Cache Memory