# **DA14535 Hardware Guidelines**

This Application Note provides the minimal reference schematic, circuit explanation, and design guidelines for Bluetooth® LE applications based on the DA14535 SoCs.

# **Contents**

| Con  | ntents |            |            |                                     | 1  |  |  |  |

|------|--------|------------|------------|-------------------------------------|----|--|--|--|

| Figu | ures   |            |            |                                     | 2  |  |  |  |

| Tab  | les    |            |            |                                     | 2  |  |  |  |

| 1.   | Term   | s and D    | efinitions |                                     | 4  |  |  |  |

| 2.   | Refe   | References |            |                                     |    |  |  |  |

| 3.   | Intro  |            |            |                                     |    |  |  |  |

|      | 3.1    |            |            | mbering and Marking                 |    |  |  |  |

|      | 3.2    | The DA     | •          | em                                  |    |  |  |  |

|      |        | 3.2.1      | The Power  | Section of DA14535                  |    |  |  |  |

|      |        |            | 3.2.1.1    | The PMU of DA14535                  | 8  |  |  |  |

|      |        |            | 3.2.1.2    | Important Notices for PMU           | 9  |  |  |  |

|      |        |            | 3.2.1.3    | Supplying External Loads            | 10 |  |  |  |

|      |        |            | 3.2.1.4    | The Passive Components              | 10 |  |  |  |

|      |        | 3.2.2      |            | MHz (Y1)                            |    |  |  |  |

|      |        | 3.2.3      | •          | 768 kHz (Y2)                        |    |  |  |  |

|      |        | 3.2.4      |            |                                     |    |  |  |  |

|      | 3.3    | UART       |            |                                     |    |  |  |  |

|      |        | 3.3.1      |            | lash                                |    |  |  |  |

|      | 3.4    | RF Sec     |            |                                     |    |  |  |  |

|      |        | 3.4.1      |            |                                     |    |  |  |  |

|      |        | 3.4.2      |            | Performance                         |    |  |  |  |

|      |        |            | 3.4.2.1    | TX Measurements                     |    |  |  |  |

|      |        |            | 3.4.2.2    | RX Measurements                     |    |  |  |  |

|      |        |            | 3.4.2.3    | Antenna and Current Measurements    |    |  |  |  |

| 4.   |        | -          |            |                                     |    |  |  |  |

|      | 4.1    |            | -          | 4535                                |    |  |  |  |

|      |        | 4.1.1      | •          | stem PCB Layout                     |    |  |  |  |

| App  |        | -          |            | ations for Reset Functionality      |    |  |  |  |

|      | A.1    |            |            |                                     |    |  |  |  |

|      | A.2    | -          | •          | and P0_0                            |    |  |  |  |

|      | A.3    |            |            |                                     |    |  |  |  |

|      | A.4    | •          |            |                                     |    |  |  |  |

|      |        | A.4.1      | •          | : Booting from 2-wire UART          |    |  |  |  |

|      |        | A.4.2      | Example 2  | : RST/P0_0 signal shared with FLASH | 31 |  |  |  |

| Appendix B External filtering for Quadrature Decoder                                                                   | 33 |

|------------------------------------------------------------------------------------------------------------------------|----|

| 5. Revision History                                                                                                    | 35 |

| Figures                                                                                                                |    |

|                                                                                                                        |    |

| Figure 1. DA14535 block diagram                                                                                        |    |

| Figure 2. FCGQFN24 pin assignment (top view)                                                                           |    |

| Figure 4. DA14535 system configurations                                                                                |    |

| Figure 5. DA14535 SoC power management unit (PMU)                                                                      |    |

| Figure 6. Battery connection for buck (left), boost (middle) or bypass (right) configuration                           |    |

| Figure 9. Effective capacitance of a 2.2 µF ceramic capacitor                                                          |    |

| Figure 11. Buck configuration                                                                                          |    |

| Figure 12. Boost configuration                                                                                         |    |

| Figure 13. Bypass configuration                                                                                        |    |

| Figure 14. DCDC efficiency in buck configuration                                                                       |    |

| Figure 15. DCDC efficiency in boost configuration                                                                      |    |

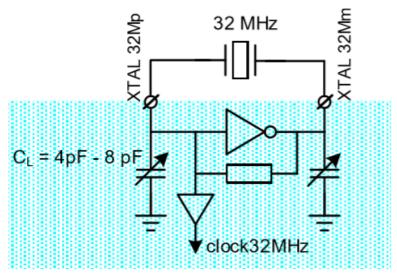

| Figure 18. The circuit of 32 MHz crystal oscillator                                                                    |    |

| Figure 19. 32 MHz XTAL oscillator capacitance value versus frequency                                                   |    |

| Figure 20. Debugger enabling                                                                                           | 17 |

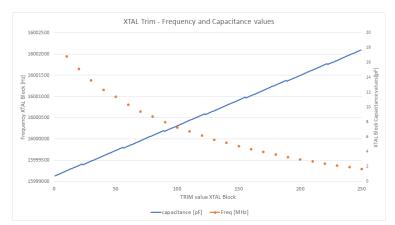

| Figure 21. Single UART hardware configuration                                                                          | 18 |

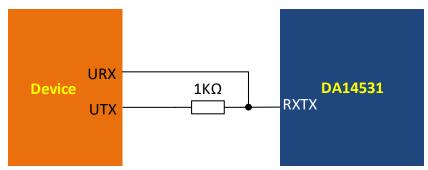

| Figure 22. SPI data flash hardware setup                                                                               |    |

| Figure 23. DA14535 RF section                                                                                          |    |

| Figure 24. Pi filter topology                                                                                          |    |

| Figure 25. S21 simulated parameters                                                                                    | 20 |

| Figure 26. DA14535 FCGQFN24 reference circuit                                                                          |    |

| Figure 27. PCB cross section                                                                                           |    |

| Figure 28. PCB placement and routing – top layerFigure 29. FCGQFN24 PCB placement and routing – GND plane - INT1 layer |    |

| Figure 30. FCGQFN24 PCB placement and routing – GND plane - INT1 layer                                                 |    |

| Figure 31. FCGQFN24 PCB placement and routing – IN12 layer                                                             |    |

| Figure 27. PCB occupied area for DA14535 system (the schematic)                                                        |    |

| Figure 32. PCB occupied area for DA14535 system (right the top layer and left, the INT1 layer)                         |    |

| Figure 40. Type B GPIO Pad-GPIO with Schmitt Trigger & RC filter                                                       |    |

| Figure 41. Reset block diagram                                                                                         |    |

| Figure 42. Booting sequence and booting pins for DA14535                                                               |    |

| Figure 43. P0_0 connected to SPI_MOSI                                                                                  |    |

| Figure 44. FTDI and DA14535 connection circuit for Reset                                                               | 31 |

| Figure 45. Example of connecting a sensor to the SPI BUS and an MCU to RST and UART of DA14535                         |    |

| SmartBond TINY™ module [376-25-C]                                                                                      | 32 |

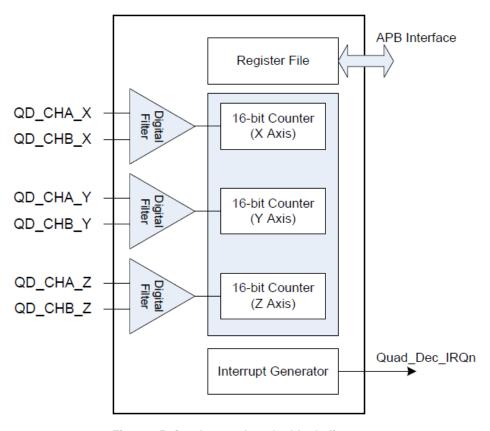

| Figure 46. Quadrature decoder block diagram                                                                            |    |

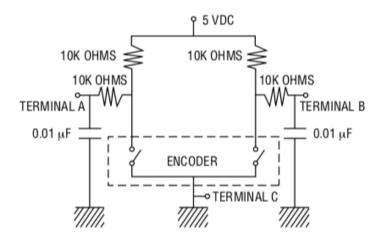

| Figure 47. Suggested filter for mechanical incremental encoder                                                         | 34 |

| T-11                                                                                                                   |    |

| Tables                                                                                                                 |    |

| Table 1. Ordering information                                                                                          | F  |

| Table 2. CHIP_REVISION_REG (0x50003214)                                                                                |    |

| Table 3. CHIP_TEST1_REG (0x500032F8)                                                                                   |    |

| Table 4. Chip revision numbering                                                                                       |    |

| Table 5. Typical rail voltages and their sources in the various PMU modes                                              | 9  |

| Table 6. DA14535 DCDC external load supply capability                                                                  | 10 |

| Table 7. DFE201610E-2R2M characteristics                                                                               |    |

| Table 9. Inductor peak current limit                                                                                   |    |

| Table 10. XTAL32 MHz oscillator - recommended operating conditions                                                     | 14 |

| Table 12. Selected main XTAL specification                                                                             |    |

| Table 13. XTAL oscillator 32 kHz - recommended operating conditions                                                    |    |

| Table 14. Selected main XTAL specification                                                                             |    |

| Table 15. P0_0 assignment during boot                                                                                  |    |

| Table 17. Fundamental power and harmonics, Conducted mode, PA in 3 dBm mode                                            | 20 |

|                                                                                                                        |    |

# **DA14535 Hardware Guidelines**

| Table 18. LO leakage, Conducted mode results | 21 |

|----------------------------------------------|----|

| Table 19. P0_0 assignment during boot        |    |

# 1. Terms and Definitions

BOM Bill Of Materials

CS Chip Select

DCR DC Resistance

GPIO General Purpose Input Output (pin)

IC Integrated Circuit

ILIM DCDC Inductor peak current limit

JTAG Joint Test Action Group

OTP One Time Programmable

PCB Printed Circuit Board

PCBA Printed Circuit Board Assembly

PMU Power Management Unit

PRO-Devkit DA14531 PRO Development kit

RF Radio Frequency

SDK Software Development Kit

SoC System on Chip

SPI Serial Peripheral Interface

SRAM Static Random-Access Memory

SWD Serial Wire Debug

UART Universal Asynchronous Receiver Transmitter

# 2. References

- [1] DA14535, Datasheet, Renesas Electronics.

- [2] UM-B-041, SmartBond Production Line Tool, Manual, Renesas Electronics.

- [3] UM-B-144, DA14531 Development Kit Pro Hardware, Manual, Renesas Electronics.

- [4] ETSI EN 300 328 and EN 300 440 Class 2 (Europe).

- [5] FCC CFR47 Part 15 (US).

- [6] ARIB STD-T66 (Japan).

- [7] AN-B-099, DA14535 Requirements for Spurious Reduction, Application Note, Renesas Electronics.

- [8] AN-B-072, DA14531 Booting Options, Application Note, Renesas Electronics.

- [9] AN-B-088, DA145xx Flash Selector Guide, Application Note, Renesas Electronics.

- [10] UM-B-119, SW Platform Reference, Manual, Renesas Electronics.

- [11] UM-B-083 SmartSnippets Toolbox, Manual, Renesas Electronics.

- [12] UM-B-159, DA14535-Module-getting-started-Guide, Renesas Electronics.

# 3. Introduction

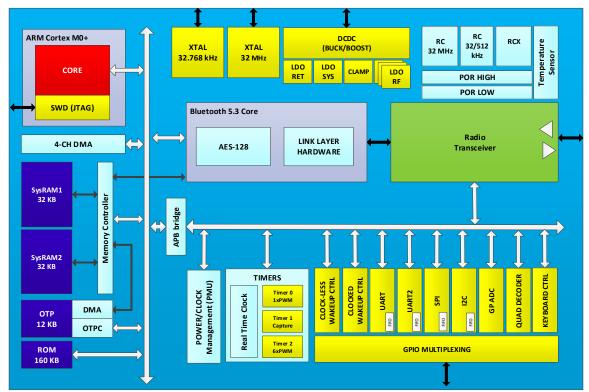

The DA14535 is an ultra-low power SoC integrating a 2.4 GHz transceiver and an Arm® Cortex®-M0+ microcontroller with a RAM of 64 kB and a One-Time Programmable (OTP) memory of 12 kB. It can be used as a standalone application processor or as a data pump in hosted systems.

# **Key characteristics:**

- Compatible with:

- Bluetooth V5.3

- ETSI EN 300 328 and EN 300 440 Class 2 (Europe)

- FCC CFR47 Part 15 (US)

- ARIB STD-T66 (Japan)

- Supports up to 3 Bluetooth<sup>®</sup> LE connections

- · Typical cold boot to radioactive 35 ms

- Memories:

- 12 kB One-Time-Programmable (OTP)

- 64 kB Retainable System RAM

- 160 kB ROM

- · Ram retainability configured in 2 blocks

- SysRAM1 (32 kB)

- SysRAM2 (32 kB)

- Integrated Buck/Boost DCDC converter

- Buck: 1.8 V ≤ VBAT\_HIGH ≤ 3.6 V

- Boost: 1.2 V ≤ VBAT LOW ≤ 1.65 V

- Clock-less hibernation mode: Buck <550 nA, Boost <550 nA

- Built-in temperature sensor for die temperature monitoring

- Digital interfaces:

- 12 x GPIOs

- 2× UARTs (one with flow control)

- SPI Master/Slave up to 32 MHz (Master)

- I2C bus at 100 kHz and 400 kHz

- 3-axis capable Quadrature Decoder

- Keyboard controller

- Analog interfaces:

- 4-channel, 10-bit ADC

- Radio transceiver:

- Fully integrated 2.4 GHz CMOS transceiver

- Single wire antenna

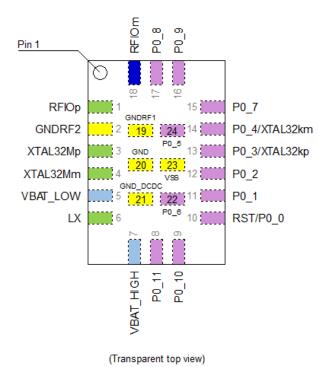

- Package: FCGQFN 24 pins, 2.2 × 3, 0.4 mm pitch

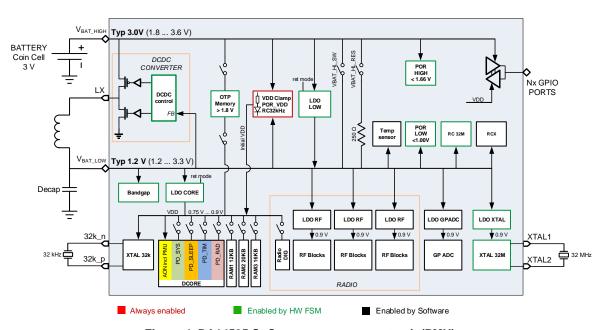

Figure 1. DA14535 block diagram

Figure 2. FCGQFN24 pin assignment (top view)

**Table 1. Ordering information**

| Part Number      | Package  | Pitch (mm) | Size (mm) |

|------------------|----------|------------|-----------|

| DA14535-00000FX2 | FCGQFN24 | 0.4        | 2.2 x 3.0 |

# 3.1 Device Revision Numbering and Marking

The revision number of the chip can be read from the device by reading the registers mentioned in Table 2 and Table 3. The result should be one of the options in Table 4.

Table 2. CHIP\_REVISION\_REG (0x50003214)

| Bit | Mode | Symbol        | Description                                         | Reset |

|-----|------|---------------|-----------------------------------------------------|-------|

| 7:0 | R    | CHIP_REVISION | Chip version, corresponds with type number in ASCII | 0x41  |

|     |      |               | 0x41 = 'A', 0x42 = 'B'.                             |       |

Table 3. CHIP\_TEST1\_REG (0x500032F8)

| Bit | Mode | Symbol               | Description                                                | Reset |

|-----|------|----------------------|------------------------------------------------------------|-------|

| 7:0 | R    | CHIP_LAYOUT_REVISION | Chip layout version, corresponds with type number in ASCII | 0x42  |

Table 4. Chip revision numbering

| Commercial number         | Package  | CHIP_REVISION_REG<br>(0x50003214) | CHIP_TEST1_REG<br>(0x500032F8) |

|---------------------------|----------|-----------------------------------|--------------------------------|

| DA14535- <b>00</b> 000FX2 | FCGQFN24 | 0x41 (A)                          | 0x42 (B)                       |

# 3.2 The DA14535 System

Only a few external components are required to have DA14535 operational. The necessary components are:

- Inductor, 2.2 μH for internal DCDC converter. Necessary for buck and boost configuration. In bypass configuration, the inductor can be removed.

- Capacitors on VBAT\_HIGH and VBAT\_LOW for internal DCDC converter. Their value depends on the DCDC configuration and the type of power source.

- XTAL 32 MHz, provides the main system and Bluetooth LE clock.

- XTAL 32 kHz, as the low-power clock in Sleep mode. When RCX (less accurate) is used, XTAL 32 kHz can be omitted.

- For some applications an RF low-pass filter is required to supress spurious emissions.

- Antenna. Is either printed or ceramic.

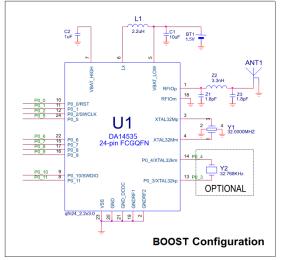

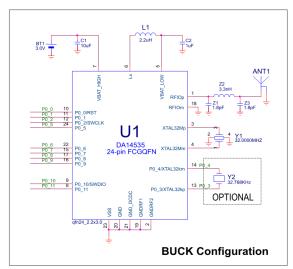

Figure 3. DA14535 system configurations

# 3.2.1 The Power Section of DA14535

The DA14535 has a flexible power setup and can operate in three different power configurations: Buck, Boost and Bypass. Depending on the available power source, Buck mode is intended for use with higher voltage batteries, such as lithium primary cells (3 V) or 2x alkaline combinations, while Boost mode can be used with

lower voltage Silver oxide cells. In Bypass mode, the DCDC converter is not used and because of that there is no need for an external inductor. This results in a cheaper BOM, but also in lower power efficiency.

The power management logic is fully integrated, and the user can select the desired mode with minor hardware modifications.

#### 3.2.1.1 The PMU of DA14535

The DA14535 has an integrated Power Management Unit (PMU), which consists of a VDD Clamp, Power on Reset (POR) circuitry, a DCDC converter and various LDOs.

The PMU integrates two main power rails VBAT\_HIGH, VBAT\_LOW and the internal VDD power rail.

- VBAT\_HIGH voltage is in the range of 1.8 V 3.6 V. This power rail is used for the blocks that require a higher supply voltage. The OTP and the GPIOs are connected to this power rail. The lowest voltage for OTP reading is 1.66 V whereas to write OTP this is 2.25 V.

- VBAT\_HIGH is protected by the power-on-reset circuit POR\_HIGH, which will generate a Power On Reset when the voltage drops below 1.66 V (VTH\_L) for more than 50 µs and will release the reset at typically 1.75V.

- VBAT\_LOW is the main system supply, with the lowest voltage equal to 1.2 V. The functional range is between 1.2 V - 3.3 V.

- When used in Boost mode, the default voltage range is **1.2 V 1.6 V**. Within this range the boost converter can provide a VBAT\_HIGH supply in the range of 1.8 V 3.0 V.

- As most internal blocks are powered from this power rail through LDOs (Figure 4), the most efficient voltage to apply is 1.2 V.

- Higher input voltage is allowed when additional settings are made to regulate DCDC boost behavior. VBAT\_LOW is protected with the power-on-reset circuit POR\_LOW, which will generate a hardware reset when the voltage drops below 1.1 V ( $V_{TH_L}$ ) for more than 50 µs and release the reset at typically 1.15 V. See Power On Reset section in datasheet of DA14535.

The internal VDD power rail supplies the digital power domains including RAM blocks. It is generated internally, and the voltage is between 0.7 V and 0.9 V, depending on the Power mode of the system (active, sleep, and so on).

Figure 4. DA14535 SoC power management unit (PMU)

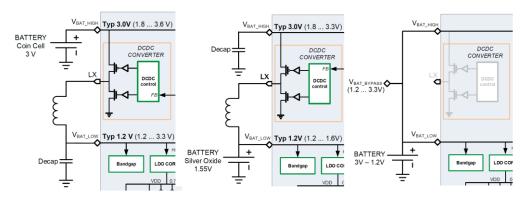

There are 3 setups for the DCDC converter of the PMU: Buck, Boost and Bypass mode. The difference of this setups is given by where the battery voltage is applied (Figure 5).

In Bypass mode, VBAT HIGH and VBAT LOW rails are tied together and the DCDC converter is not used.

Figure 5. Battery connection for buck (left), boost (middle) or bypass (right) configuration

Table 5. Typical rail voltages and their sources in the various PMU modes

|                                |                           | VBA                                                   | AT_HIGH                    | VBA             | AT_LOW                     |

|--------------------------------|---------------------------|-------------------------------------------------------|----------------------------|-----------------|----------------------------|

| Configuration                  | Mode                      | Voltage rang                                          | Supplied to/generated from | Voltage range   | Supplied to/generated from |

|                                | Active                    | 1.8 V to 3.6 V                                        | VBAT                       | 1.2 V           | DCDC out                   |

| BUCK Supply on VBAT HIGH       | Deep or<br>Extended Sleep | 1.8 V to 3.6 V                                        | VBAT                       | 1.2 V           | LDO_LOW                    |

| VBAT_ITIOIT                    | Hibernation               | 1.8 V to 3.6 V                                        | VBAT                       | 0 V             |                            |

|                                | Active                    | 1.8 V, 2.5 V or<br>3 V                                | DCDC out                   | 1.2 V to 1. 5 V | VBAT                       |

| BOOST<br>Supply on<br>VBAT_LOW | Deep or<br>Extended Sleep | Parasitic diodes<br>in DCDC or<br>clamp<br>(VBAT_LOW) |                            | 1.2 V to 1. 5 V | VBAT                       |

|                                | Hibernation               | Parasitic diodes<br>in DCDC or<br>clamp<br>(VBAT_LOW) |                            | 1.2 V to 1. 5 V | VBAT                       |

| Bypass                         | Active                    | 1.8 V to 3.3 V                                        | VBAT                       | 1.8 V to 3.3 V  | VBAT                       |

| Supply on<br>VBAT_HIGH,        | Deep or<br>Extended Sleep | 1.8 V to 3.3 V                                        | VBAT                       | 1.8 V to 3.3 V  | VBAT                       |

| VBAT_LOW                       | Hibernation               | 1.8 V to 3.3 V                                        | VBAT                       | 1.8 V to 3.3 V  | VBAT                       |

# 3.2.1.2 Important Notices for PMU

**Boost mode:** for a guaranteed startup, the load on VBAT\_HIGH must not exceed 0.85 mA during system startup/wake-up.

| Parameter                            | Description                                                                        | Conditions                         | Min | Тур | Max  | Unit |

|--------------------------------------|------------------------------------------------------------------------------------|------------------------------------|-----|-----|------|------|

| I <sub>L_VBAT_HIGH_</sub><br>BOOTING | Maximum DC load current on V <sub>BAT_HIGH</sub> rail during booting in boost mode | Boost mode booting sequence active |     |     | 0.85 | mA   |

Figure 6. Maximum DC load on VBAT\_HIGH rail during boot

Higher loads should be isolated from VBAT\_HIGH to avoid overloading the rail during boot. A dedicated GPIO pin can be used to provide power to an external device either directly, if the current requirements are within the current sourcing capabilities of the pin, or through a load switch/power management IC.

**Bypass mode**: VBAT\_HIGH and VBAT\_LOW are shorted on the PCB. This mode is detected by the chip as boost mode. The software should set the CFG\_POWER\_MODE\_BYPASS flag. Otherwise, the software would stop after booting, when the supply is below 3V.

As the DCDC converter cannot boost VBAT\_HIGH to 1.8 V (default), the initial voltage on VBAT\_HIGH must be above 1.75 V to release the POR\_HIGH and allow booting.

If the voltage in the system drops below 1.66 V after booting, POR\_HIGH must be masked or disabled to prevent a reset.

### 3.2.1.3 Supplying External Loads

The internal DCDC converter of the DA14535 can be used to supply external loads, in both buck and boost mode. Use the application software to select and trim the output voltage.

In Table 6, the external load driving capability of the DCDC converter is summarized.

Table 6. DA14535 DCDC external load supply capability

| Configuration | VBAT_HIGH   | VBAT_LOW    | Maximum load current |

|---------------|-------------|-------------|----------------------|

| BUCK          | 3.0 V (in)  | 1.1 V (out) | 20 mA                |

| BOOST         | 1.8 V (out) | 1.5 V (in)  | 20 mA                |

| BOOST         | 2.5 V (out) | 1.5 V (in)  | 10 mA                |

| BOOST         | 3.0 V (out) | 1.5 V (in)  | 10 mA                |

In Buck mode, VBAT\_LOW is the source for the load current, while in Boost mode, VBAT\_HIGH is the source for the load current.

From a system point of view, this is very interesting for Boost mode, where the DA14535 can replace the step-up DCDC converters needed to supply loads like SPI data flash or sensors, and so on, and consequently reduce the BOM cost considerably. Note that, as mentioned in Section 3.2.1.2, you must pay special attention to the load current during initialization, which in Boost mode must not exceed 0.85 mA.

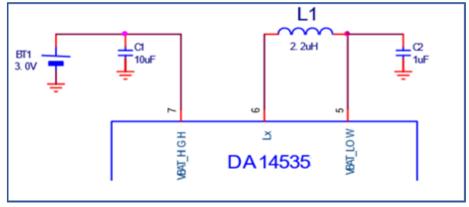

### 3.2.1.4 The Passive Components

The DCDC converter is internal to the SoC circuit and requires only three external components: two capacitors and one inductor. As the DCDC converter must meet the input and output voltage and load current specifications, proper selection of the external components is very important.

#### **Capacitors**

Two capacitors are required, C1 attached to the VBAT HIGH rail pin, and C2 attached to the VBAT LOW rail.

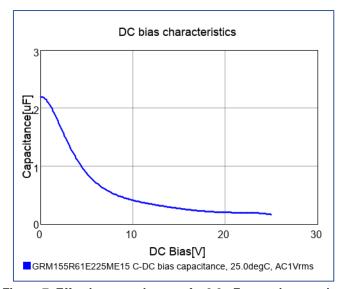

The capacitors are of the type Multi-Layer Ceramic Capacitor (MLCC). Note that in MLCC capacitors, the effective capacitance value depends on the DC voltage applied to the capacitor.

For example, GRM155R61E225ME15D is a 2.2  $\mu$ F capacitor with a rated voltage of 25 V. With 3 VDC applied on its pins, the effective capacitance drops to 1.39  $\mu$ F.

You must take this into account and select the parts carefully, because a poor capacitor value can degrade system performance.

Figure 7. Effective capacitance of a 2.2  $\mu F$  ceramic capacitor

### **Buck mode:**

- C1: 10 µF effective (input capacitor)

- C2: 1 µF effective (output filter capacitor)

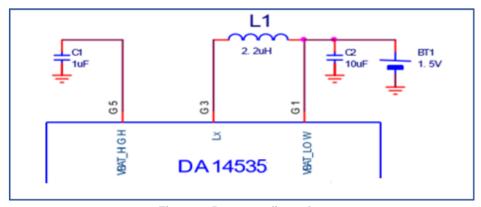

Figure 8. Buck configuration

# Boost mode:

- C1: 1 µF effective (output filter capacitor)

- C2: 10 µF effective (input capacitor)

Figure 9. Boost configuration

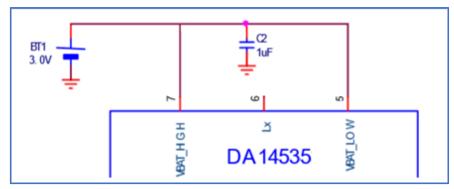

#### Bypass mode

In Bypass mode, the DCDC converter is not used and C1, C2 are used for decoupling. As the two power pins (VBAT\_HIGH and VBAT\_LOW) are located very close, a capacitor of 1  $\mu$ F is enough. See Figure 10.

Figure 10. Bypass configuration

#### Inductor

The DA14535 DCDC converter requires an external 2.2  $\mu$ H inductor. The choice of inductor will impact the DCDC converter efficiency. Generally, larger inductors with alloy/metal composite cores, low DC resistance and high resonance frequency will give better efficiency.

For optimal operation of the DCDC converter, use the general criteria below to select a suitable part:

- 40 MHz Self resonance or higher

- 500 mΩ ESR or lower (the lower the better)

- 2.2 µH with 20% or lower tolerance

- Shielded inductors preferred over unshielded types

The inductor used on DA14535 PRO-development kit is the DFE201610E-2R2M of Murata.

Table 7. DFE201610E-2R2M characteristics

| DCR      | 0.14 Ω |

|----------|--------|

| lmax     | 1.7 A  |

| Package  | 0806   |

| Shielded | yes    |

In cases where we need to reduce the size of the system, and the external load currents are negligible, it is possible to reduce the physical size of the power inductor. By doing so, the expectation is that some of the conversion efficiency is sacrificed. So, you must find the optimal tradeoff among power efficiency, size and cost, depending on the intended application.

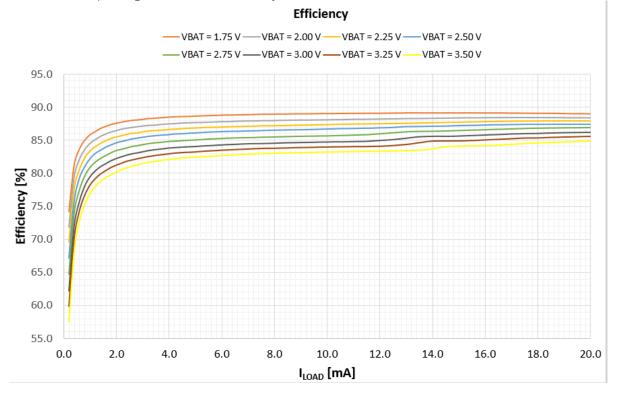

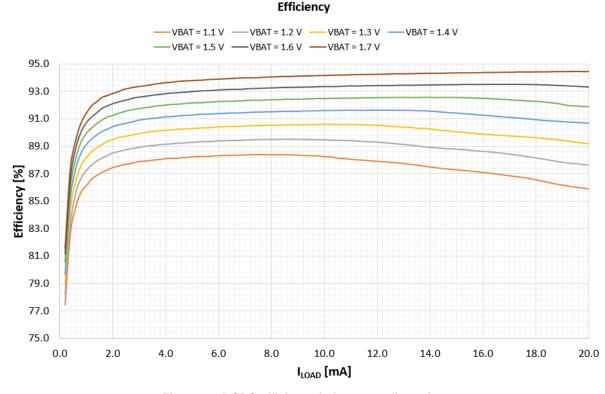

Figure 11 and Figure 12 show the performance (efficiency) of the DCDC converter for buck and boost (3 V, 2.5 Vand 1.8 V) configurations. The efficiency is measured for the load as described in Table 6.

Figure 11. DCDC efficiency in buck configuration

Figure 12. DCDC efficiency in boost configuration

**ILIM** defines the peak current of the Inductor of the DCDC converter (L1). The peak current varies between DCDC\_ILIM\_MAX (iLimH) and DCDC\_ILIM\_MIN (liLimL). DCCD\_ILIM\_MAX is the maximum peak current that can pass through the Inductor. For a peak current higher than this limit, the internal switch of the DCDC converter is deactivated.

DCDC\_ILIM\_MIN and DCDC\_ILIM\_MAX can be set between 6 mA and 96 mA, with a 6 mA step.

Table 8. Inductor peak current limit

| Inductor peak current | DCDC_CTRL_REG (0x50000080)P<br>bits | Default | Current |

|-----------------------|-------------------------------------|---------|---------|

| DCDC_ILIM_MAX         | 15:12                               | 0x8     | 54 mA   |

| DCDC_ILIM_MIN         | 11:8                                | 0x4     | 30 mA   |

The current limit values in Table 8 are set in the SDK and fits in most use cases. In general, the recommendation is to leave the current limit values as is, since the system performance is verified with these settings. In special cases, you can adjust the settings to fit the needs of the application. However, changes in these settings may affect system performance.

# 3.2.2 XTAL, 32 MHz (Y1)

The system clock of DA14535 is 16 MHz, which is generated from a 32 MHz crystal oscillator. The crystal oscillator consists of an external 32 MHz XTAL and the internal clock oscillator. The recommended operating conditions are given in Table 9.

Table 9. XTAL32 MHz oscillator - recommended operating conditions

| Symbol     | Parameter                    | Conditions                                                             | Min | Тур | Max | Unit |

|------------|------------------------------|------------------------------------------------------------------------|-----|-----|-----|------|

| fXTAL_32M  | Crystal oscillator frequency |                                                                        |     | 32  |     | MHz  |

| ΔfXTAL     | Crystal frequency tolerance  | After optional trimming; including aging and temperature drift. Note 1 | -20 |     | 20  | ppm  |

| ΔfXTAL_UNT | Crystal frequency tolerance  | Untrimmed; including aging and temperature drift. Note 2               | -40 |     | 40  | ppm  |

| ESR_1pF    | Equivalent series resistance | C <sub>0</sub> <1pF                                                    |     |     | 200 | Ω    |

| ESR_3pF    | Equivalent series resistance | C <sub>0</sub> <3pF                                                    |     |     | 80  | Ω    |

| ESR_5pF    | Equivalent series resistance | C <sub>0</sub> <5pF                                                    |     |     | 50  | Ω    |

| CL         | Load capacitance             | No external capacitors are required                                    | 4   | 6   | 8   | pF   |

Note 1 Using the internal varicaps a wide range of crystals can be trimmed to the required tolerance.

Note 2 Maximum allowed frequency tolerance for compensation by the internal varicap trimming mechanism.

If the specification of the crystal meets the requirements of the DA14535 oscillator, the crystal package does not affect the operation of the system.

The selected crystal for the DA14535 PRO-devkit is the XRCGB32M000F1SBAR0 of Murata. The XTAL specification is shown in Table 10.

Table 10. Selected main XTAL specification

| Parameter                    | Description | Min | Тур | Max | Unit |

|------------------------------|-------------|-----|-----|-----|------|

| Frequency                    | Fo          |     | 32  |     | MHz  |

| Operating Temperature Range  | Тор         | -40 |     | 105 | °C   |

| Load Capacitance             | CL          |     | 6   |     | pF   |

| Drive Level                  | DL          |     |     | 300 | μW   |

| Equivalent Series Resistance | ESR         |     |     | 50  | Ω    |

| Parameter                      | Description | Min | Тур | Max | Unit    |

|--------------------------------|-------------|-----|-----|-----|---------|

| Frequency Tolerance            | dF/Fo       | -10 |     | 10  | ppm     |

| Frequency shift by Temperature | dF/F25      | -20 |     | 20  | ppm     |

| Aging                          | dF/F25      | -2  |     | 2   | ppm     |

| Package                        | 2.0x1.6 mm  |     |     |     | mm × mm |

### 32 MHz XTAL Trimming

The 32 MHz (XTAL32M) crystal oscillator has trimming capability. The frequency is trimmed by two on-chip variable capacitor banks, see Figure 13. Both capacitor banks are controlled by the same 8-bit register, CLK FREQ TRIM REG.

Figure 13. The circuit of 32 MHz crystal oscillator

With CLK\_FREQ\_TRIM\_REG[XTAL32M\_TRIM] = 0x00, the minimum capacitance and thus the maximum frequency is selected.

With CLK\_FREQ\_TRIM\_REG[XTAL32M\_TRIM] = 0xFF, the maximum capacitance and thus the minimum frequency is selected, see Figure 14.

Figure 14. 32 MHz XTAL oscillator capacitance value versus frequency

The advice is to trim the crystal (XTAL) to achieve optimal RF performance and power consumption.

Not trimming the crystal might lead to out of spec RF, when taking frequency drift into account due to temperature and aging.

Crystal trimming is fully supported by the PLT, see Ref. [2], without the need for external equipment or can be performed manually.

Crystal Trimming is an iterative algorithm:

- 1. Set the TRIM-value.

- 2. Measure the resulting frequency.

- 3. Adapt the TRIM value until Delta < 5 ppm.

# 3.2.3 XTAL, 32.768 kHz (Y2)

You can put an external crystal of 32.768 kHz on pins P0\_3 and P0\_4 of DA14535 (external digital clock can also be applied on pin P0\_3).

This XTAL oscillator does not have varicap tuning, so the frequency accuracy of this clock depends on the selected component. Select a crystal that matches the specification given in Table 12, or matches the crystal with external load capacitance. The recommended operating conditions for the 32.768 kHz crystal oscillator are in Table 11.

Table 11. XTAL oscillator 32 kHz - recommended operating conditions

| Symbol        | Parameter                                     | Conditions                                                                          | Min  | Тур        | Max | Unit |

|---------------|-----------------------------------------------|-------------------------------------------------------------------------------------|------|------------|-----|------|

| fXTAL_3<br>2M | Crystal oscillator frequency                  |                                                                                     | 30   | 32.76<br>8 | 35  | kHz  |

| ESR           | Equivalent series resistance                  |                                                                                     |      |            | 100 | kΩ   |

| CL            | Load capacitance                              | No external capacitors are required for a 6pF or 7pF crystal                        | 6    | 7          | 9   | pF   |

| C0            | Shunt capacitance                             |                                                                                     |      | 1          | 2   | pF   |

| PDRV_M<br>AX  | Maximum drive power                           |                                                                                     | 0.1  |            |     | μW   |

| ΔfXTAL        | Crystal frequency tolerance (including aging) | Timing accuracy is dominated by crystal accuracy. A much smaller value is dominated | -250 |            | 250 | ppm  |

A crystal that can be used is the SC20S-7PF20PPM of SEIKO Instruments. The specification is in Table 12.

Table 12. Selected main XTAL specification

| Parameter                    | Description | Min | Тур    | Max | Unit |

|------------------------------|-------------|-----|--------|-----|------|

| Frequency                    | Fo          |     | 32.768 |     | kHz  |

| Operating Temperature Range  | Тор         | -40 |        | +85 | °C   |

| Load Capacitance             | CL          |     | 7      |     | pF   |

| Equivalent Series Resistance | ESR         |     |        | 90  | kΩ   |

| Shunt Capacitance            | Со          |     | 1.3    |     | pF   |

| Frequency Tolerance          | dF/Fo       | -20 |        | +20 | ppm  |

| Aging, per year              | dF/F25      |     | ±3     |     | ppm  |

| Drive Level                  | DL          |     | 0.1    | 1   | μW   |

| Package                      |             | mm  |        |     |      |

Note 1 There is no 32.768 kHz crystal used on the DA14535 PRO-development kit. An internal RCX oscillator is used instead.

In most applications the DA14535 can run with good accuracy with its internal RC oscillator (RCX) and therefore the XTAL32k is not needed. For applications with more demanding accuracy/drift characteristics, such as timekeeping, consider using the XTAL32k.

#### Reset

During power on and before booting, the reset pin is active high and is assigned on P0\_0. This is the HW reset. After booting, reset pin assignment and operation is handled by software.

At boot, P0\_0 is also assigned as output to UART and SPI for the time required from each booting step. At the end of each boot step, P0\_0 is assigned again to Reset.

Table 13. P0\_0 assignment during boot

| Pin  | Booting sequence | State                                                                   | Comments                                                                                                                |

|------|------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| P0_0 | Before boot      | RST                                                                     | Input with pull down                                                                                                    |

|      | During boot      | MISO, (Boot Step 1)<br>UTX, (Boot Step 4)<br>MOSI. (Boot Step 5)<br>RST | P0_0 is handled from Booting sequence. At the end of each step, and before next booting step, P0_0 is assigned to Reset |

|      | After boot       | RST/GPIO                                                                | Handled by the software.                                                                                                |

The RST functionality on P0\_0 can be disabled by setting the HWR\_CTRL\_REG[DISABLE\_HWR] bit.

Special consideration regarding Reset functionality and P0\_0 multiplexing, see Appendix A.

### 3.2.4 JTAG

JTAG consists of SWDIO and SWCLK. SWCLK is assigned to P0\_2 and SWDIO is assigned to P0\_10. But through software programming, SWDIO can also be assigned to P0\_1 or P0\_5.

During the booting sequence, JTAG is not enabled. If no bootable device is found on any of the serial interfaces, the booter can do two things depending on what was stored in the Configuration Script (CS). If the 'Debugger disable' (0x70000000) command is stored in the CS, the booter starts rescanning the peripherals. Otherwise, it enters an endless loop with the debugger (JTAG) being enabled.

To use the JTAG GPIOs as general-purpose pins, the JTAG function must be disabled by clearing the 'debugger enable' bits. See Figure 15. The same bits can be used to remap the JTAG pins.

| SYS_0 | SYS_CTRL_REG (0x50000012) |                     |                                                                                                                                                                        |  |  |  |  |

|-------|---------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit   | Mode                      | Symbol              | Description                                                                                                                                                            |  |  |  |  |

| 8:7   | R/W                       | DEBUGGER_ENAB<br>LE | Enable the debugger. This bit is set by the booter according to the OTP header. If not set, the SWDIO and SW_CLK can be used as gpio ports.  0x0: no debugger enabled. |  |  |  |  |

|       |                           |                     | 0x1: SW_CLK = P0[2], SW_DIO=P0[5]                                                                                                                                      |  |  |  |  |

|       |                           |                     | 0x2: SW_CLK = P0[2], SW_DIO=P0[1]                                                                                                                                      |  |  |  |  |

|       |                           |                     | 0x3: SW_CLK = P0[2], SW_DIO=P0[10]                                                                                                                                     |  |  |  |  |

Figure 15. Debugger enabling

### **3.3 UART**

There are three different UART configurations possible: 1-wire UART (or Single-wire is preferable due to low pin number), 2-wire UART and 4-wire UART.

**UART, Single-wire**: UTX and URX are multiplexed together on a single pin of DA14535. On board level, a 1 k $\Omega$  resistor separates the two signals. See Figure 16.

Figure 16. Single UART hardware configuration

In a regular UART bus, UTX and URX lines can be active simultaneously. In most use cases of the DA14535 (boot, HCI commands etc.), the traffic on the UART is half duplex and a single wire can be used for all UART transactions. On the DA14535 side, the SDK UART driver takes care of switching the pin direction.

On the host side, all data sent is echoed back since TX and RX are shorted. For successful communication, the software should be able to discard the echo. Smart Snippets Toolbox, see Ref. [11], implements such a feature and can be used with a 1-wire UART.

Single-wire UART is used on the booter. The DA14535 has two options to boot from single-wire UART: from P0\_5 in boot step #2 and from P0\_3 in boot step #3. After the boot sequence, the application software can redefine any GPIO as single-wire UART.

UART, 2-wires: UTX and URX.

Two-wire UART is used in boot step #4. P0\_0 and P0\_1 are used for UTX (output) and URX (input) respectively.

After booting, the software can reassign the UTX and URX to other pins by setting the Pxx\_MODE\_REG.

**UART, 4 wires**: This is the full UART with flow control. Set the Pxx\_MODE\_REG to assign GPIOs. Hardware flow control is mainly needed for external host applications.

### 3.3.1 SPI Data Flash

There are two available SPI modes on DA14535, Ext-SPI master and Ext-SPI slave. In the Ext-SPI master mode, an external processor (master) can download code to the DA14535. In the Ext-SPI slave, the DA14535 can download code from a slave device such as an external SPI data Flash.

In this case, the bootloader downloads the binary file to RAM and execute it. The default GPIOs during boot are given in Table 14.

Table 14. DA14535 pins assignment for SPI data slave on booting

| DA14535 signals | SPI data flash |

|-----------------|----------------|

| P0_0            | MOSI           |

| P0_1            | CS             |

| P0_3            | MISO           |

| P0_4            | SCK            |

Booting GPIOs can be changed by either a secondary bootloader, or by declaring them in the OTP header bootspecific mapping.

Data flashes tested successfully are listed in Ref. [9].

Figure 17. SPI data flash hardware setup

The SPI clock (SCK) frequency is configurable up to 32 MHz. The frequency depends on the physical connections between the DA14535 SoC and the SPI Data flash. On DA14535 DK-PRO, there is significant capacitive load on the SPI pins, due to signal multiplexing and long traces. On the software development kit (SDK), the frequency used is 2 MHz to boot and 4 MHz for SUOTA.

### **PCB Layout Notice**

The SPI data flash Read/Write frequency depends on the PCB layout. The suggestion is to put the data flash as close as possible to DA14535. In case that this is not feasible, consider adding termination resistors in the order of  $30~\Omega$  next to source pins. Add GND between routed traces to eliminate crosstalk.

### 3.4 RF Section

DA14535 provides a 50  $\Omega$  single RFIO port for TX and RX without requiring external balun or RF switch. The internal RF power amplifier provides TX RF power from -18 dBm to +4 dBm.

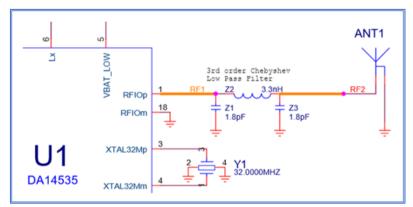

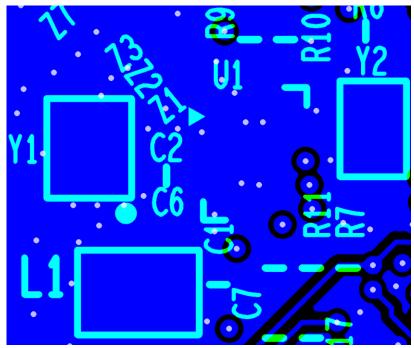

Figure 18. DA14535 RF section

The Pi filter for Renesas Electronics DA14535 System-on-Ship (SoC) in 2.4 GHz Bluetooth LE applications specifically addresses the conducted and radiated performance.

The objective of the Pi-filter is to suppress the local oscillator leakage, which violates the conducted performance requirements of ETSI, ARIB (Japanese standard) and KC (Korean certification) standards.

There is no violation of FCC regulations. Consequently, the user can omit the Pi-filter if only the FCC regulations must be adhered to.

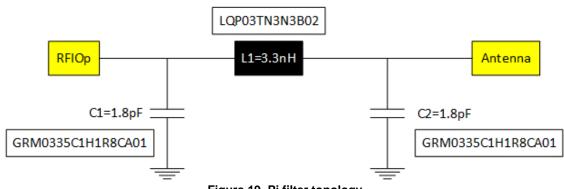

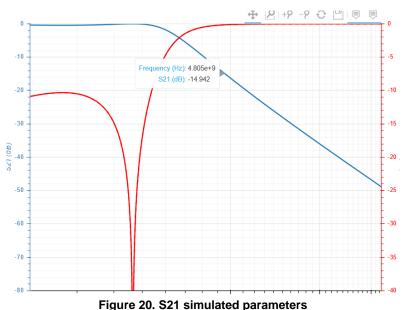

The Pi filter configuration is chosen, because it gives the best suppression with minimal power loss at fundamental frequencies. The filter is a third order Chebyshev Lowpass Filter with a cut-off frequency at 2600 MHz, and passband ripple of 0.4 dB, see Ref. [7].

#### 3.4.1 Pi Filter

Figure 19 shows the filter topology.

Figure 19. Pi filter topology

# Components used:

- Capacitors: 1.8 pF, 0201, Murata, PN: GRM0335C1H1R8CA01

- Inductor: 3.3 nH, 0201, Murata, PN: LQP03TN3N3B02

Measured S21 parameters give a minimum -15 dBm attenuation at 4.8 GHz. The filter gives a 0.7 dBm to 1.2 dBm loss in sensitivity and 0.2 to 0.7 dBm in TX power.

#### 3.4.2 **Conducted Performance**

The measurements are done with a calibrated spectrum analyzer and RF cables. The levels are measured at the SMA output with the DUT.

All measurements are calibrated for cable losses.

#### 3.4.2.1 **TX Measurements**

The test was done at ch19, room temperature, normal operating conditions. Measurements are done in burst mode, modulated signal.

Table 15. Fundamental power and harmonics, Conducted mode, PA in 3 dBm mode

|                     | Fundamental | 2nd harm | 3rd harm | 4th harm | 5th harm |

|---------------------|-------------|----------|----------|----------|----------|

| Without RFIO filter | 3.56        | -49.57   | -42.50   | -42.23   | -38.43   |

| With RFIO filter    | 2.83        | -57.50   | -62.27   | -62.17   | -63.30   |

All values are in dBm Note 2

Note 3 Measurement accuracy < ± 0.3 dB

#### 3.4.2.2 RX Measurements

The test was done at ch19, measurement frequency 2\*(2440+1 MHz) = 4882 MHz.

Table 16. LO leakage, Conducted mode results

|                  | Without RFIO filter | With RFIO filter |

|------------------|---------------------|------------------|

| LO leakage power | -42.18              | -61.26           |

Note 1 All values are in dBm

Note 2 Measurement accuracy < ± 0.3 dB

### 3.4.2.3 Antenna and Current Measurements

The antenna's transmit power is received from the RF circuitry through the TX line (matched to an impedance of 50  $\Omega$ ). Matching the input impedance of the antenna to 50  $\Omega$  is required, to ensure that the maximum power is transferred from the RF circuity to the antenna with only a negligible amount being reflected.

However, the matching circuits are not always perfect and the components present tolerances.

Also, if a printed antenna is in contact or close to other surfaces (especially conductive materials), it is detuned, and a lot of RF energy is not radiated, but reflected to the RF transmitter.

Peak current measurements depend on the antenna matching. A not perfectly matched antenna results in a higher power consumption during RF transmission.

The safest way to measure the peak power consumption of the system (hardware and software) is to have instead of the antenna a 50  $\Omega$  termination (dummy load).

# 4. PCB Layout Guidelines

PCB guidelines for the DA14535 are presented below, using the daughterboards of the PRO-Devkit as reference:

FCGQFN24: DA14531-00FXDB-P \_ [376-04-F]

# 4.1 PCB Layout of DA14535

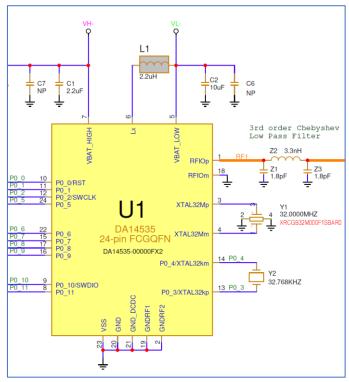

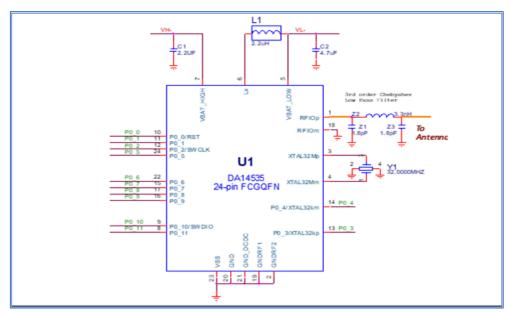

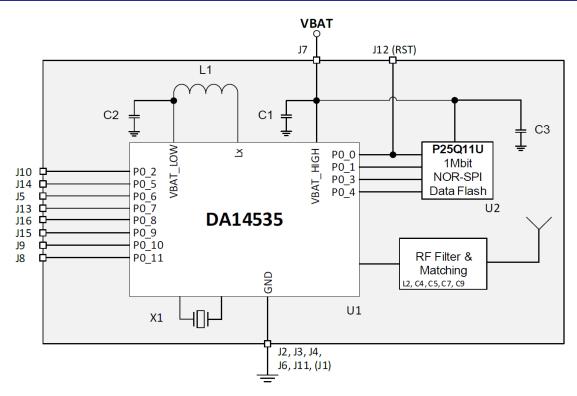

The implemented PCB layout is based on the schematic shown in Figure 21. The same layout can be used for buck, boost and bypass configurations (for bypass, L1 must be removed from the circuit).

A low-pass filter has been added on the RFIOp trace, which presents impedance on both sides, equal to 50 Ohm. The antenna is not shown in the schematic in Figure 21.

Finally, please notice that Y2, 32.768 kHz can be omitted.

Figure 21. DA14535 FCGQFN24 reference circuit

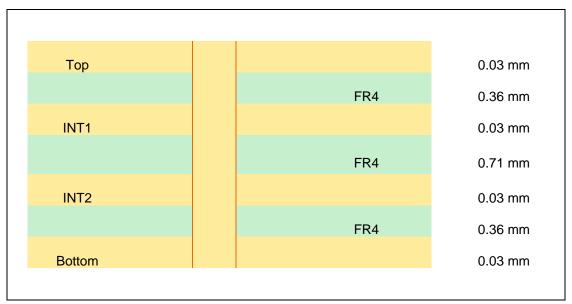

PCB rules applied on the PRO-Daughterboard:

- Number of layers: 4

- Material: FR-4 no microvias

- Vias: Mechanical

- Under chip: Diameter 0.45 mm/drill 0.15 mm

- Rest PCB areas: Diameter 0.5 mm/drill 0.15 mm

- Copper clearance: 0.1 mm

- Copper width: 0.1 mm

Figure 22. PCB cross section

### **PCB** Layout guidelines

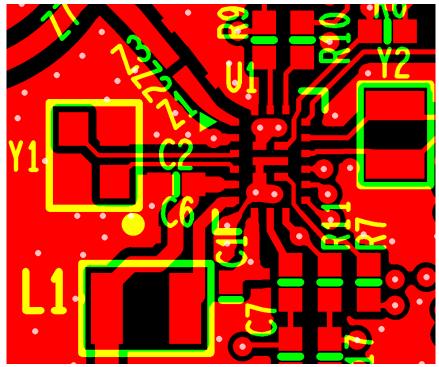

#### **Grounding:**

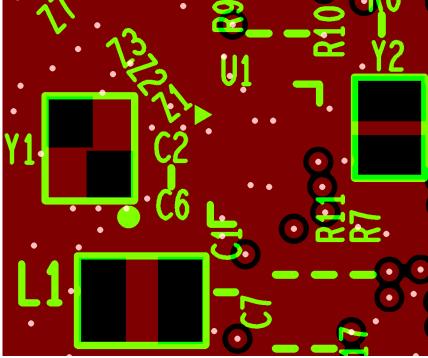

- Use INT1 layer free of routing and assign it as reference ground

- Separate RF ground pins of DA14535 from the rest ground pins

- Connect pin 19 to GND with vias as shown in Figure 23

- Short 20, 21, 23 GND pins together and use two GND vias, as shown in Figure 23

- Add GND stitching vias to increase the performance of the system

# Power management:

- Put capacitors C1 and C2 close to the pins of DA14535. Apply a GND per capacitor next to the GND pin

- Put L1 as close as possible to the chip. Remove grounding under the inductor to minimize any possible coupling from reference ground

### XTALs:

- Put XTALs close to the chip

- Try to have a ground shield around XTALs

- There is no need to route the two XTAL traces differentially

Remove the area on the INT1 ground layer under the pads of XTAL to reduce coupling as shown in Figure 24. Use the 3rd or 4th layer to shield the xtal pads.

### RF strip:

Calculate and route a 50 Ohm RF stripline between DA14535 RFIOp pin and antenna. A low-pass filter, consisting of three components (Z1, Z2, Z3) must be put as close as possible to the chip. Both capacitors must be grounded on the same side of the RF stripline preferably to RFIOm, which is the RF reference ground.

In case the antenna needs matching, put a matching circuit next to the antenna. Ground the components on the same side of RF trace, same as in the low-pass filter.

Figure 23. PCB placement and routing - top layer

Figure 24. FCGQFN24 PCB placement and routing – GND plane - INT1 layer

Figure 25. FCGQFN24 PCB placement and routing – INT2 layer

Figure 26. FCGQFN24 PCB placement and routing – GND bottom layer

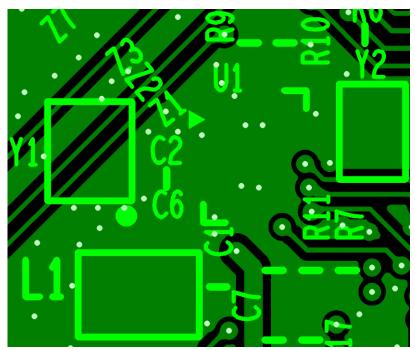

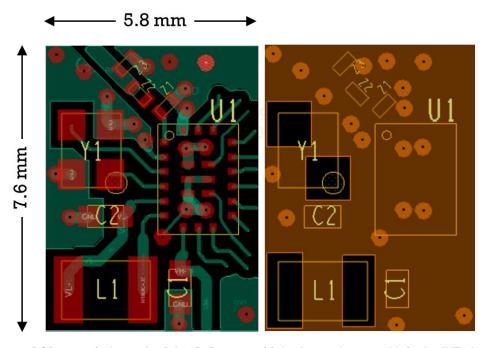

# 4.1.1 Minimal System PCB Layout

An example of the PCB layout occupied from the DA14535 system is given in Figure 28.

The implemented system uses the necessary components. Crystal 32 kHz is omitted. The inductor is the same as on the Pro-Devkit whereas all signals are fanned out. Component placement is much more efficient than the PRO-development kit, as there is no need for signals multiplexing. Dimensions of the area are 5.8 mm x 7.6 mm.

The PCB can be either 2 layers or 4 layers. For a two layer design, please close the openings under the XTAL pads on the second layer.

Figure 27. PCB occupied area for DA14535 system (the schematic)

Figure 28. PCB occupied area for DA14535 system (right the top layer and left, the INT1 layer)

# Appendix A Special considerations for Reset Functionality

There are three main reset signals in the DA14535:

- The hardware reset: it is optional triggered by the RST pad (P0\_0) when it becomes active for a short period

of time (less than the programmable delay for POR)

- The Power-On Reset (POR): it is optional triggered by a GPIO set as the POR source with a selectable polarity and/or the RST pad (P0\_0) after a programmable time delay

- The software reset: it is triggered by writing the SYS\_CTRL\_REG[SW\_RESET] bit For more detailed description see DA14535 Datasheet [1].

Special considerations should be taken when using reset functionality. The reason is the following:

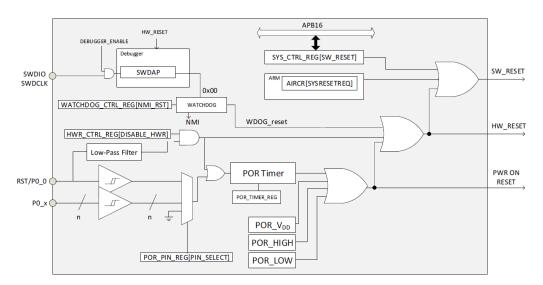

- RST pad is multiplexed with P0\_0 pin (Figure 30)

- P0\_0 is also used during boot sequence (Figure 31)

- P0\_0 is connected to SPI FLASH (as MOSI (SPI\_DO)) in many cases

We examine the above cases in more detail.

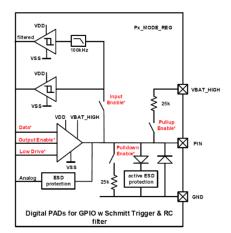

# A.1 Reset Pad (P0\_0)

The DA14535 comprises a reset (RST) pad which is active high. It contains an RC filter with a resistor of 465 k $\Omega$  and a capacitor of 3.5 pF to suppress spikes. It also contains a 25 k $\Omega$  pull-down resistor (see Figure 29). This pad should be driven externally by a field-effect transistor (FET) or a single button connected to VBAT. The typical latency of the RST pad is in the range of 2  $\mu$ s.

#### Features:

- RC spike filter on RST to suppress external spikes (465 kΩ, 3.5 pF)

- Three different reset lines (SW, HW, and POR)

- Latching the cause of a reset operation (RESET\_STAT\_REG)

- Configurable POR circuitry

This reset pad is multiplexed with P0\_0.

Figure 29. Type B GPIO Pad-GPIO with Schmitt Trigger & RC filter

Figure 30. Reset block diagram

# A.2 Booting Sequence and P0\_0

P0\_0 is used as booting pin in the steps described in Figure 31.

|          | Step 1                         | Step 2                                      | Step 3                                   | Step 4                      | Step 5                           | Step 6           |

|----------|--------------------------------|---------------------------------------------|------------------------------------------|-----------------------------|----------------------------------|------------------|

|          | Boot from<br>ext SPI<br>Master | Boot from<br>1 wire<br>UART<br>(1st option) | Boot from 1<br>wire UART<br>(2nd option) | Boot from<br>2 wire<br>UART | Boot<br>from ext<br>SPI<br>Slave | Boot from<br>I2C |

| P0_0/RST | MISO                           |                                             |                                          | Tx                          | MOSI                             |                  |

| P0_1     | MOSI                           |                                             |                                          | Rx                          | SCS                              |                  |

| P0_2     |                                |                                             |                                          |                             |                                  |                  |

| P0_3     | SCS                            |                                             | RxTx                                     |                             | MISO                             | SDA              |

| P0_4     | SCK                            |                                             |                                          |                             | SCK                              | SCL              |

| P0_5     |                                | RxTx                                        |                                          |                             |                                  |                  |

Note: The booter will try to boot from the above serial interfaces in the order from Step 1 to step 6.

Figure 31. Booting sequence and booting pins for DA14535

During power on and before booting, the reset pin is active high and is assigned on P0\_0. This is the hardware reset. After booting, reset assignment and operation is handled by software.

During boot, the reset functionality POR or hardware reset on P0\_0 is multiplexed with SPI Slave MISO (Boot Step 1), UART TX (Boot Step 4) and MOSI (Boot Step 5). During this time reset functionality is disabled. At the end of each boot step, the reset functionality on P0\_0 is restored.

Table 17. P0\_0 assignment during boot

| Pin  | Booting sequence | State                                                                   | Comments                                                                                                                |

|------|------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| P0_0 | Before boot      | RST                                                                     | Input with pull down                                                                                                    |

|      | During boot      | MISO, (Boot Step 1)<br>UTX, (Boot Step 4)<br>MOSI. (Boot Step 5)<br>RST | P0_0 is handled from Booting sequence. At the end of each step, and before next booting step, P0_0 is assigned to Reset |

|      | After boot       | RST/GPIO                                                                | Handled by the software.                                                                                                |

The RST functionality on P0 0 can be disabled by setting the HWR CTRL REG[DISABLE HWR] bit.

During start-up sequence the RST pin inputs with pull-down keeping the chip out of reset. After application initialization the RST pin can be switched into GPIO mode. In case an external microcontroller does not drive P0\_0, it is recommended to use it as an output in order to not permit external devices to interfere with the power up sequence of the chip.

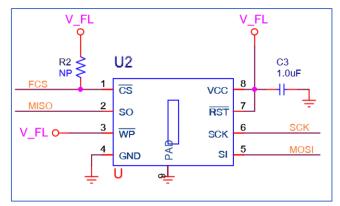

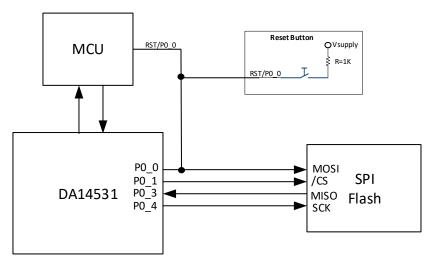

# A.3 SPI FLASH

P0\_0 in many cases is connected to SPI\_MOSI of SPI FLASH. In this case RST/P0\_0 pin should not be driven while the device is booting from the SPI Flash. Any external circuit that triggers hardware reset should not be used during this time.

Figure 32. P0\_0 connected to SPI\_MOSI

# A.4 Examples

# A.4.1 Example 1: Booting from 2-wire UART

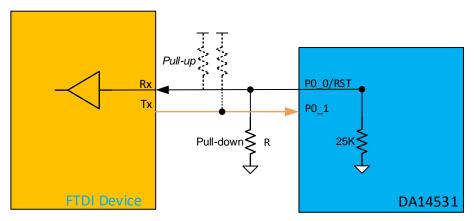

Since the idle state of the UART lines are default high, FTDI devices and microcontrollers tend to have a pull up resistor on their RX line in order to avoid continuous break. Since P0\_0 is used as a TX while booting and also as HW reset, connecting a device might continuously reset the DA14535 due to this external pull up.

When booting from 2-wire UART (Figure 31, Step 4), the TX is mapped to P0\_0 which is also used as Reset pin. The device starting its boot sequence detects UART on P0\_0/P0\_1. After the boot sequence is finished the P0\_0 is automatically restored to Reset mode. If a connected external microcontroller or FTDI USB to UART bridge pulls this port high, it triggers a continuous reset.

A valid solution would be to use a stronger R pull-down resistor connected to P0\_0 overriding the effect of the receiver's pull up, as shown in Figure 33. The value of R depends on the pull up on the receiver's side. This solution is acceptable if there is no constant voltage from an external device on P0\_0 to leak through the strong pull down.

In case that the application requires constant connection on the P0\_0/P0\_1 due to external interface the user must make sure that during booting process of DA14535, the external controller will not drive its RX pin to high state. If the external controller can handle continuous break conditions, due to low state because its RX line then the external pull down can be omitted.

Figure 33, FTDI and DA14535 connection circuit for Reset

Using permanently P0\_0 as TX means that reset function of P0\_0 is disabled. DA14535 can be reset from external controller by either enabling the reset again through a command or set a GPIO pin to act as a POR source. An alternative solution would be to burn a secondary booter in the OTP and boot from different pins and keep the P0\_0 as a reset.

# A.4.2 Example 2: RST/P0\_0 signal shared with FLASH

Special considerations should be taken when RST/P0\_0 is shared with a SPI Flash Memory. RST/P0\_0 pin should not be driven while the device is booting from the SPI Flash. When the Flash is in use the reset functionality is not available. To access the flash and have the reset functionality of reset pin, follow the steps:

- 1. Disable RST functionality on P0\_0 by setting HWR\_CTRL\_REG[DISABLE\_HWR] bit.

- 2. Set P0\_0 to SPI\_MOSI.

- 3. Access Flash.

- 4. Enable hardware reset.

Figure 34. Example of connecting a sensor to the SPI BUS and an MCU to RST and UART of DA14535 SmartBond TINY™ module [376-25-C]

### NOTE

DA14535 SmartBond TINY™ module comes with a preloaded demo. See Ref. [12].

# **Appendix B External filtering for Quadrature Decoder**

DA14535 has an integrated Quadrature decoder that can automatically decode the signals for the X, Y, Z axes of a HID input device, reporting step count and direction. For more information about the decoder, see Ref. [1].

Figure 35. Quadrature decoder block diagram

The decoder is equipped with digital filtering which eliminates the spikes shorter that three clock periods. This means that for sys\_clk=16 MHz and max time setting QDEC\_CLOCKDIV=0x3FF, the decoder can handle bounces in the order of 200 µs. However, bouncing in encoders is relevant and depends on the mechanical characteristics. It can be in the order of some hundreds µs up to a few ms. These long bounces require external filtering. Usually, relevant filtering information can be found in the encoder's manufacturer datasheet. It is suggested to follow manufacturer instructions or apply a generic RC filter like the one shown in Figure 36.

Figure 36. Suggested filter for mechanical incremental encoder

# 5. Revision History

| Revision | Date         | Description                      |

|----------|--------------|----------------------------------|

| 1.1      | Jan 17, 2025 | Converted into Renesas template. |

| 1.0      | Feb 9, 2024  | Initial version.                 |

# **STATUS DEFINITIONS**

| Status               | Definition                                                                                                                   |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| DRAFT                | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |  |

| APPROVED or unmarked | The content of this document has been approved for publication.                                                              |  |

# **ROHS COMPLIANCE**

Renesas Electronics' suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.