# Application Note Tracking ADC

# **AN-CM-309**

# Abstract

This application note describes the implementation of a simple tracking ADC based on digital rheostats of the SLG47004. No external components and no special tuning procedure are required for the proposed ADC structure. Also, the circuit has much better PSRR and temperature drift than a capacitor based counter type ADC.

The proposed ADC can be used for monitoring slow-changing signals like temperature, battery voltage, and others.

This application note comes complete with design files which can be found in the References section.

# **AN-CM-309**

# Contents

| Ab  | strac                                 | t                                                                |    |  |  |  |  |  |  |

|-----|---------------------------------------|------------------------------------------------------------------|----|--|--|--|--|--|--|

| Со  | ntent                                 | S                                                                | 2  |  |  |  |  |  |  |

| Fig | jures                                 |                                                                  | 2  |  |  |  |  |  |  |

| Та  | bles .                                |                                                                  | 2  |  |  |  |  |  |  |

| 1   | Tern                                  | ns and Definitions                                               | 3  |  |  |  |  |  |  |

| 2   | Refe                                  | rences                                                           |    |  |  |  |  |  |  |

| 3   | Intro                                 | oduction                                                         |    |  |  |  |  |  |  |

| 4   | Trac                                  | king ADC Principle                                               | 4  |  |  |  |  |  |  |

| 5   | Inter                                 | nal Blocks Configuration                                         | 6  |  |  |  |  |  |  |

|     | 5.1                                   | Chopper ACMP Configuration                                       | 6  |  |  |  |  |  |  |

|     | 5.2                                   | Oscillators Configurations                                       | 7  |  |  |  |  |  |  |

|     | 5.3                                   | Digital Rheostats Configurations                                 | 7  |  |  |  |  |  |  |

|     | 5.4                                   | LUTs Configurations                                              |    |  |  |  |  |  |  |

|     | 5.5                                   | DFFs Configurations                                              | 8  |  |  |  |  |  |  |

|     | 5.6                                   | Filter/Edge Detector Configuration                               | 9  |  |  |  |  |  |  |

|     | 5.7                                   | Vref0 Configuration                                              | 9  |  |  |  |  |  |  |

|     | 5.8                                   | IO Pins Configurations                                           | 9  |  |  |  |  |  |  |

|     | 5.9                                   | I <sup>2</sup> C Macrocell Configuration                         | 10 |  |  |  |  |  |  |

| 6   | Desi                                  | gn Verification Using Software Simulation and Hardware Prototype | 10 |  |  |  |  |  |  |

| 7   | Accuracy and Timing Characteristics12 |                                                                  |    |  |  |  |  |  |  |

| 8   | Conclusions                           |                                                                  |    |  |  |  |  |  |  |

| Re  | visio                                 | n History                                                        |    |  |  |  |  |  |  |

# **Figures**

| . 4 |

|-----|

| . 5 |

| . 6 |

| 6   |

| . 7 |

| . 7 |

| . 8 |

| 8   |

| . 9 |

| 9   |

| 9   |

| 10  |

| 11  |

| 11  |

|     |

# **Tables**

| Table 1: The Comparison of Tracking ADC and Capacitor Based (Wilkinson) ADC 13 |              |             |  |  |  |  |  |  |

|--------------------------------------------------------------------------------|--------------|-------------|--|--|--|--|--|--|

| Application Note                                                               | Revision 1.0 | 03-Nov-2020 |  |  |  |  |  |  |

## **1** Terms and Definitions

| ACMP  | Analog comparator           |

|-------|-----------------------------|

| ADC   | Analog to digital converter |

| DAC   | Digital to analog converter |

| IC    | Integrated circuit          |

| OpAmp | Operational amplifier       |

# 2 References

For related documents and software, please visit:

#### GreenPAK<sup>™</sup> Programmable Mixed-Signal Products | Renesas

Download our free GreenPAK Designer software [1] to open the .gp files [2] and view the proposed circuit design. Use the GreenPAK development tools [3] to freeze the design into your own customized IC in a matter of minutes. Find out more in a complete library of application notes [4] featuring design examples as well as explanations of features and blocks within the GreenPAK IC.

- [1] GreenPAK Designer Software, Software Download and User Guide

- [2] AN-CM-309 Tracking ADC.gp, GreenPAK Design File

- [3] GreenPAK Development Tools, GreenPAK Development Tools Webpage

- [4] GreenPAK Application Notes, GreenPAK Application Notes Webpage

- [5] SLG47004, Datasheet

Author: Vladyslav Kozlov

# 3 Introduction

The growing development of digital ICs like microcontrollers, microprocessors, FPGA, and others, allows using complex digital processing techniques instead of analog signal conditioning. This tendency made ADC a widely used component of mixed-signal circuits.

There are a lot of types of ADC: successive-approximation ADC, sigma-delta ADC, direct-conversion ADC, capacitor charge/discharge based ADC, ADC with voltage-to-frequency converters, and others. All these ADC types have different accuracy, frequency, and cost characteristics. The proposed structure of ADC is the tracking ADC.

# 4 Tracking ADC Principle

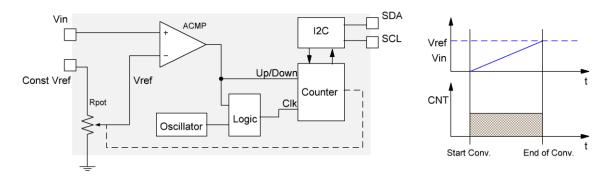

The main components of the tracking ADC are:

- DAC. Current project uses buffered voltage reference output and digital potentiometer as DAC.

- ACMP.

- Counter with Up/Down control input. In the SLG47004 this counter is embedded into the digital rheostats macrocells.

The operation principle of the tracking ADC is shown in Figure 1. When conversion starts, the counter begins to change the resistance of digital potentiometer depending on the level at Up/Down input. At each (Oscillator) step the voltage at the inverting input of ACMP increases (or decreases). The conversion ends when ACMP changes its output. After the end of the conversion it's possible to calculate sampled input voltage:

$$Vin = \frac{Vref}{Ntaps} \cdot N,$$

where Vin – input voltage at inverting input of ACMP; Vref – reference voltage; Ntaps – maximum number of potentiometer taps; N – the value of counter after the end of conversion.

•

#### Figure 1: Basic Structure and Operation Principle of the Tracking ADC

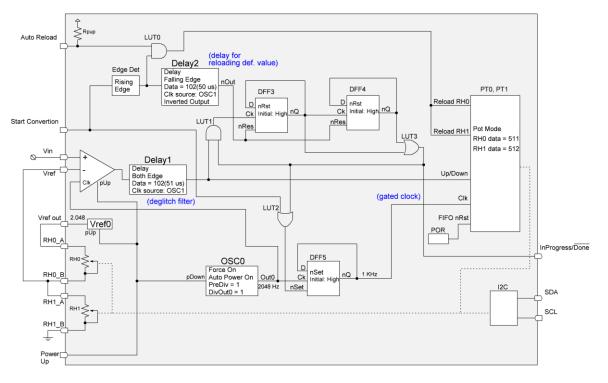

Figure 2 shows the internal design of the tracking ADC based on the SLG47004.

Pulse at "Start Conversion" input begins conversion process. There are two options for initial rheostats value:

- If "Auto-Reload" input is floating, every new conversion starts from the rheostats default value of 512. This default value corresponds to Vref/2 voltage at dividers output.

- If "Auto-Reload" input is connected to ground, every new conversion starts from the previous rheostat value. This option can speed up the conversion time for slow-changing processes.

#### **Application Note**

**Revision 1.0**

The stop condition occurs when ACMP changes its input from Low to High the 3<sup>rd</sup> time.

The User can hold a logic level High at "Start Conversion" input to track input voltage level. In this case the rheostat will keep on switching and changing Vref voltage near Vin voltage level. Note that "In Progress/Done" output will change its level to logic Low after ACMP changes its input from Low to High the 3<sup>rd</sup> time, even if logic level High is being kept at the "Start Conversion" input.

Figure 2: Internal Design of the Tracking ADC Based on SLG47004

## AN-CM-309

## **Tracking ADC**

# 5 Internal Blocks Configuration

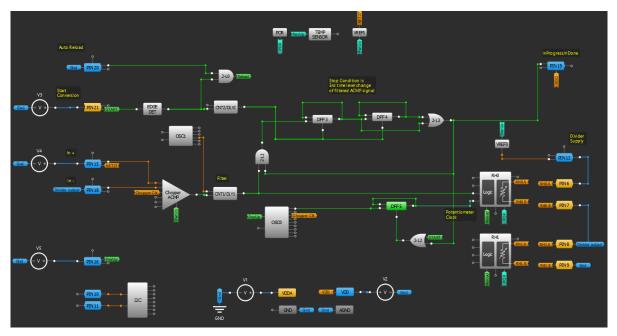

Figure 3 shows the design of the project in GreenPAK Designer Software.

Figure 3: Project Design in GreenPAK Designer Software

## 5.1 Chopper ACMP Configuration

| Chopper ACMP          |                        |  |  |  |  |  |  |  |

|-----------------------|------------------------|--|--|--|--|--|--|--|

| OUT polarity:         | Non-inverted (OU 🔻     |  |  |  |  |  |  |  |

|                       | Non-Inverted (00) +    |  |  |  |  |  |  |  |

| IN- Vref source:      | HD buffer 🔻            |  |  |  |  |  |  |  |

| Auto-Trim<br>Channel: | Channel0 💌             |  |  |  |  |  |  |  |

| Auto-Trim:            | Disable 👻              |  |  |  |  |  |  |  |

| Channel 0             |                        |  |  |  |  |  |  |  |

| IN+ CH0 source:       | Ext. Vref (PIN 15 (G 💌 |  |  |  |  |  |  |  |

| IN- CH0 source:       | Ext. Vref (PIN 18 (G 🔻 |  |  |  |  |  |  |  |

| CH0 clock:            | OSCO 💌                 |  |  |  |  |  |  |  |

| Ch                    | annel 1                |  |  |  |  |  |  |  |

| IN+ CH1 source:       | InAmp OUT              |  |  |  |  |  |  |  |

| IN- CH1 source:       | Ext. Vref (PIN 18 (G 👻 |  |  |  |  |  |  |  |

| CH1 clock:            | Ext. Clk. (From mat 🔻  |  |  |  |  |  |  |  |

Figure 4: Chopper ACMP Configuration

| Δn | nlice | ation | Note |

|----|-------|-------|------|

|    | piice | ation | NOLE |

**Revision 1.0**

## 5.2 Oscillators Configurations

|                                                              | OSC0                      | OSC1 |                                                              |                             |  |  |

|--------------------------------------------------------------|---------------------------|------|--------------------------------------------------------------|-----------------------------|--|--|

| Control pin<br>mode:<br>OSC power<br>mode:                   | Force on<br>Auto Power On | •    | Control pin<br>mode:<br>OSC power<br>mode:                   | Power down    Auto Power On |  |  |

| Clock selector:                                              | osc                       | •    | Clock selector:                                              | osc 🔹                       |  |  |

| 'OSC0' frequency:                                            | 2.048 kHz                 | -    | 'OSC1' frequency:                                            | 2.048 MHz 💌                 |  |  |

| 'CLK' predivider<br>by:                                      | 1                         | •    | 'CLK' predivider<br>by:                                      | 1 •                         |  |  |

| 'OUT0' second<br>divider by:<br>'OUT1' second<br>divider by: | 1                         | •    | 'OUT0' second<br>divider by:<br>'OUT1' second<br>divider by: | 1 <b>•</b><br>1 •           |  |  |

Figure 5: Oscillators Configurations

# 5.3 Digital Rheostats Configurations

| Digital                              | Rheostat0           | Digital Rheostat1 |                                      |                     |   |  |  |

|--------------------------------------|---------------------|-------------------|--------------------------------------|---------------------|---|--|--|

| Mode:                                | None                | •                 | Mode:                                | Potentiometer       | • |  |  |

| Charge Pump<br>Enable:               | Always On           | •                 | Charge Pump<br>Enable:               | Always On           | • |  |  |

| Charge Pump<br>Clock: <sup>(7)</sup> | LPBG chopper OS(    | •                 | Charge Pump<br>Clock: <sup>(7)</sup> | LPBG chopper OS(    | • |  |  |

| Auto-Trim:                           | Disable             | •                 | Auto-Trim:                           | Disable             | Ŧ |  |  |

| Active level for<br>UP/DOWN:         | Up when LOW         | •                 | Active level for<br>UP/DOWN:         | Up when HIGH        | - |  |  |

| Resistance (initial                  | 511                 | -                 | Resistance (initial                  | 512                 | ÷ |  |  |

| data):                               | (Range: 0 - 1023)   |                   | data):                               | (Range: 0 - 1023)   |   |  |  |

| Con                                  | nections            |                   | Con                                  | nections            |   |  |  |

| UP/DOWN<br>source:                   | Ext. (From matrix)  | •                 | UP/DOWN<br>source:                   | Ext. (From matrix)  | Ŧ |  |  |

| Clock:                               | Ext. Clk. (From mat | •                 | Clock:                               | Ext. Clk. (From mat | - |  |  |

Figure 6: Digital Rheostats Configurations

## 5.4 LUTs Configurations

| 2-bit LUT0/DFF/LATCH0   |           |         |                         |        |         | 2-bit LUT1/DFF/LATCH1 |     |        |                     |       | 2-bit LUT2/DFF/LATCH2 |          |          |      |               | 2-bit LUT3/PGEN |          |     |       |  |

|-------------------------|-----------|---------|-------------------------|--------|---------|-----------------------|-----|--------|---------------------|-------|-----------------------|----------|----------|------|---------------|-----------------|----------|-----|-------|--|

| Type:                   |           | LUT     |                         | •      | Type:   |                       | LUT |        | -                   | Type: |                       | LUT      |          | -    | Type:         |                 | LUT      |     | -     |  |

| IN3                     | IN2       | IN1     | INO                     | OUT    | IN3     | IN2                   | IN1 | INO    | OUT                 | IN3   | IN2                   | IN1      | INO      | OUT  | IN3           | IN2             | IN1      | INO | OUT   |  |

| 0                       | 0         | 0       | 0                       | 0      | 0       | 0                     | 0   | 0      | 0                   | 0     | 0                     | 0        | 0        | 0    | 0             | 0               | 0        | 0   | 0     |  |

| 0                       | 0         | 0       | 1                       | 0      | 0       | 0                     | 0   | 1      | 0                   | 0     | 0                     | 0        | 1        | 1    | 0             | 0               | 0        | 1   | 1     |  |

| 0                       | 0         | 1       | 0                       | 0      | 0       | 0                     | 1   | 0      | 0                   | 0     | 0                     | 1        | 0        | 1    | 0             | 0               | 1        | 0   | 1     |  |

| 0                       | 0         | 1       | 1                       | 1      | 0       | 0                     | 1   | 1      | 1                   | 0     | 0                     | 1        | 1        | 1    | 0             | 0               | 1        | 1   | 1     |  |

| 0                       | 1         | 0       | 0                       | 0      | 0       | 1                     | 0   | 0      | 0                   | 0     | 1                     | 0        | 0        | 0    | 0             | 1               | 0        | 0   | 0     |  |

| 0                       | 1         | 0       | 1                       | 0      | 0       | 1                     | 0   | 1      | 0                   | 0     | 1                     | 0        | 1        | 0    | 0             | 1               | 0        | 1   | 0     |  |

| 0                       | 1         | 1       | 0                       | 0      | 0       | 1                     | 1   | 0      | 0                   | 0     | 1                     | 1        | 0        | 0    | 0             | 1               | 1        | 0   | 0     |  |

| 0                       | 1         | 1       | 1                       | 0      | 0       | 1                     | 1   | 1      | 0                   | 0     | 1                     | 1        | 1        | 0    | 0             | 1               | 1        | 1   | 0     |  |

| 1                       | 0         | 0       | 0                       | 0      | 1       | 0                     | 0   | 0      | 0                   | 1     | 0                     | 0        | 0        | 0    | 1             | 0               | 0        | 0   | 0     |  |

| 1                       | 0         | 0       | 1                       | 0      | 1       | 0                     | 0   | 1      | 0                   | 1     | 0                     | 0        | 1        | 0    | 1             | 0               | 0        | 1   | 0     |  |

| 1                       | 0         | 1       | 0                       | 0      | 1       | 0                     | 1   | 0      | 0                   | 1     | 0                     | 1        | 0        | 0    | 1             | 0               | 1        | 0   | 0     |  |

| 1                       | 0         | 1       | 1                       | 0      | 1       | 0                     | 1   | 1      | 0                   | 1     | 0                     | 1        | 1        | 0    | 1             | 0               | 1        | 1   | 0     |  |

| 1                       | 1         | 0       | 0                       | 0      | 1       | 1                     | 0   | 0      | 0                   | 1     | 1                     | 0        | 0        | 0    | 1             | 1               | 0        | 0   | 0     |  |

| 1                       | 1         | 0       | 1                       | 0      | 1       | 1                     | 0   | 1      | 0                   | 1     | 1                     | 0        | 1        | 0    | 1             | 1               | 0        | 1   | 0     |  |

| 1                       | 1         | 1       | 0                       | 0      | 1       | 1                     | 1   | 0      | 0                   | 1     | 1                     | 1        | 0        | 0    | 1             | 1               | 1        | 0   | 0     |  |

| 1                       | 1         | 1       | 1                       | 0      | 1       | 1                     | 1   | 1      | 0                   | 1     | 1                     | 1        | 1        | 0    | 1             | 1               | 1        | 1   | 0     |  |

| Standard gates All to 0 |           | Standar | Standard gates All to 0 |        | Standar | Standard gates All to |     | I to O | to 0 Standard gates |       |                       | All to 0 |          |      |               |                 |          |     |       |  |

| AND                     |           | -       | A                       | I to 1 | AND     |                       | -   | A      | All to 1            |       |                       | -        | All to 1 |      | OR 👻          |                 | All to 1 |     |       |  |

| Reg                     | gular sha | ape     | I                       | nvert  | Re      | gular sha             | ape | l li   | nvert               | Re    | gular sha             | ape      | I        | wert | Regular shape |                 |          |     | nvert |  |

Figure 7: LUTs Configurations

## 5.5 **DFFs Configurations**

| 3-b                                                                      | oit LUT(                    | 0/DFF/LATCH                                 | 43    | 3-b                                                                           | 3-bit LUT1/DFF/LATCH4                  |               |                                                                                                                                                           |                              |        | 3-bit LUT2/DFF/LATCH5 |       |  |  |  |

|--------------------------------------------------------------------------|-----------------------------|---------------------------------------------|-------|-------------------------------------------------------------------------------|----------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------|-----------------------|-------|--|--|--|

| Туре:                                                                    |                             | DFF / LATCH                                 | •     | Туре:                                                                         |                                        | DFF / LATCH   | *                                                                                                                                                         | Туре:                        | (      | DFF / LATCH           | •     |  |  |  |

| Mode:                                                                    |                             | DFF                                         | -     | Mode:                                                                         |                                        | DFF -         |                                                                                                                                                           | Mode:                        |        | DFF                   |       |  |  |  |

| Second Q s                                                               | elect:                      | Q of first DF                               | F Ŧ   | Second Q se                                                                   | elect:                                 | None          | -                                                                                                                                                         | Second Q se                  | elect: | None                  | -     |  |  |  |

| nSET/nRESI<br>option:                                                    | ET                          | nRESET 💌                                    |       | nSET/nRESET<br>option:                                                        |                                        | nRESET 🔻      |                                                                                                                                                           | nSET/nRESET<br>option:       |        | nSET -                |       |  |  |  |

| Initial polar                                                            | ity:                        | High                                        | •     | Initial polari                                                                | ty:                                    | Low           |                                                                                                                                                           | Initial polari               | ity:   | High                  |       |  |  |  |

| Q output<br>polarity:                                                    |                             | Inverted (nQ)                               |       | Q output<br>polarity:                                                         |                                        | Inverted (nQ) |                                                                                                                                                           | Q output<br>polarity:        |        | Inverted (nQ)         |       |  |  |  |

| Active level<br>RST/SET:                                                 | for                         | Low level 💌                                 |       | Active level for<br>RST/SET:                                                  |                                        | Low level 🔻   |                                                                                                                                                           | Active level for<br>RST/SET: |        | Low level 🔻           |       |  |  |  |

|                                                                          | Info                        | rmation                                     |       |                                                                               | Info                                   | rmation       |                                                                                                                                                           | Information                  |        |                       |       |  |  |  |

| Normal oper                                                              | ation                       |                                             |       | Normal opera                                                                  | ation                                  |               |                                                                                                                                                           | Normal operation             |        |                       |       |  |  |  |

| D                                                                        | CLK                         | Q(t)                                        | nQ(t) | D                                                                             | CLK                                    | Q(t)          | nQ(t)                                                                                                                                                     | D                            | CLK    | Q(t)                  | nQ(t) |  |  |  |

| 0                                                                        | t                           | 0                                           | 1     | 0                                                                             | t                                      | 0             | 1                                                                                                                                                         | 0                            | t      | 0                     | 1     |  |  |  |

| 0                                                                        | Ļ                           | t - 1                                       | t - 1 | 0                                                                             | 1.                                     | t - 1         | t - 1                                                                                                                                                     | 0                            | Ļ      | t - 1                 | t - 1 |  |  |  |

| 1                                                                        | t                           | 1                                           | 0     | 1                                                                             | t                                      | 1             | 0                                                                                                                                                         | 1                            | t      | 1                     | 0     |  |  |  |

| 1                                                                        | Ļ                           | t - 1                                       | t - 1 | 1                                                                             | Ļ                                      | t - 1         | t-1                                                                                                                                                       | 1                            | Ļ      | t - 1                 | t - 1 |  |  |  |

| t - 1 - previo<br>nRESET = 0<br>nRESET = 1<br>nSET = 0 =><br>nSET = 1 => | => Q =<br>=> norr<br>Q = 1; | ,<br>0; nQ = 1;<br>mal operatior<br>nQ = 0; | n;    | t - 1 - previou<br>nRESET = 0 =<br>nRESET = 1 =<br>nSET = 0 =><br>nSET = 1 => | 0; nQ = 1;<br>nal operatior<br>nQ = 0; | ı;            | t - 1 - previous state;<br>nRESET = 0 => Q = 0; nQ = 1;<br>nRESET = 1 => normal operation;<br>nSET = 0 => Q = 1; nQ = 0;<br>nSET = 1 => normal operation; |                              |        |                       |       |  |  |  |

|                                                                          |                             |                                             |       | Figure 8:                                                                     | DFF                                    | s Config      | uration                                                                                                                                                   | 5                            |        |                       |       |  |  |  |

#### **Application Note**

#### **Revision 1.0**

#### 03-Nov-2020

# 5.6 Filter/Edge Detector Configuration

| FILTER/EDGE DET  |                     |  |  |  |  |  |  |  |

|------------------|---------------------|--|--|--|--|--|--|--|

| Туре:            | EDGE DET 💌          |  |  |  |  |  |  |  |

| Mode:            | Rising edge detec 🔻 |  |  |  |  |  |  |  |

| Output polarity: | Non-inverted (OU    |  |  |  |  |  |  |  |

Figure 9: Filter/Edge Detector Configuration

## 5.7 Vref0 Configuration

To configure the Vref0 macrocell, the ACMP0L should also be configured.

| A                          | CMPOL      | VREFO                 |                         |                     |  |  |  |

|----------------------------|------------|-----------------------|-------------------------|---------------------|--|--|--|

| Hysteresis:                | 0 mV       | Power down<br>source: | From matrix 💌           |                     |  |  |  |

| IN+ gain:                  | Disable    | •                     | Power down<br>register: | Disable 🔻           |  |  |  |

| Input LPF:                 | Disable    | •                     | Force bandgap<br>on:    | Enable 💌            |  |  |  |

| Vref LPF: (7)              | Disable    | •                     |                         |                     |  |  |  |

| Low power start<br>up:     | Disable    | •                     | Source selector:        | A CMP0L reference 🔻 |  |  |  |

| αр.                        |            | 5                     | Cor                     | nections            |  |  |  |

| Sampling mode:             | Disable    | •                     |                         |                     |  |  |  |

| Vrefs source<br>selection: | 2.048 V    | •                     | Output:                 | PIN 12 (GPIO0)      |  |  |  |

| Cor                        | nections   |                       |                         |                     |  |  |  |

| IN+ source:                | OpAmp0 Out | •                     |                         |                     |  |  |  |

| IN- Low to High<br>source: | 2048 mV    | -                     |                         |                     |  |  |  |

| IN- High to Low<br>source: | 2048 mV    | •                     |                         |                     |  |  |  |

| Inf                        | ormation   |                       |                         |                     |  |  |  |

| Typical ACMP thres         | holds      |                       |                         |                     |  |  |  |

| V_IH (mV)                  | V_IL (mV)  |                       |                         |                     |  |  |  |

| 2048                       | 2048       |                       |                         |                     |  |  |  |

#### Figure 10: ACMP0L and Vref0 Configurations

# 5.8 IO Pins Configurations

| PIN 12 (GPIO0)                                  |                                      | PIN 16 (GPIO2)                                  |                      | PIN 19 (GPIO5)                                  |                                     | PIN 20 (GPIO6)                                  |                                            |

|-------------------------------------------------|--------------------------------------|-------------------------------------------------|----------------------|-------------------------------------------------|-------------------------------------|-------------------------------------------------|--------------------------------------------|

| I/O selection:                                  | Analog input/out; 🔻                  | I/O selection:                                  | Digital input 👻      | I/O selection:                                  | Digital output 🔹                    | I/O selection:                                  | Digital input 🔹                            |

| Input mode:<br>OE = 0<br>Output mode:<br>OE = 1 | Analog input/out;  Analog input/out; | Input mode:<br>OE = 0<br>Output mode:<br>OE = 1 | Digital in without 💌 | Input mode:<br>OE = 0<br>Output mode:<br>OE = 1 | None        None       1x push pull | Input mode:<br>OE = 0<br>Output mode:<br>OE = 1 | Digital in without 💌                       |

| Resistor:<br>Resistor value:                    | Floating     •       Floating     •  | Resistor:<br>Resistor value:                    | Floating             | Resistor:<br>Resistor value:                    | Floating                            | Resistor:<br>Resistor value:                    | Pull Up         •           100K         • |

#### Figure 11: IO Pins Configurations

# Application Note Revision 1.0

RENESAS

## 5.9 I<sup>2</sup>C Macrocell Configuration

I<sup>2</sup>C Macrocell uses default settings.

## 6 Design Verification Using Software Simulation and Hardware Prototype

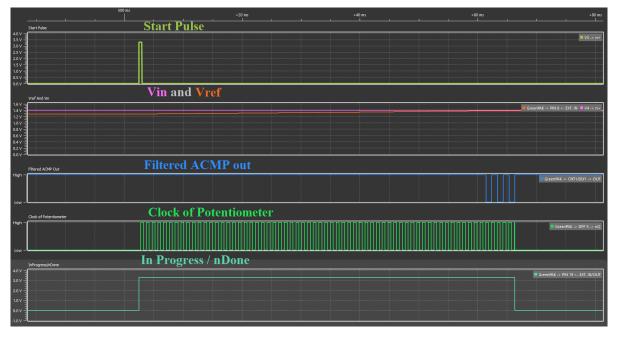

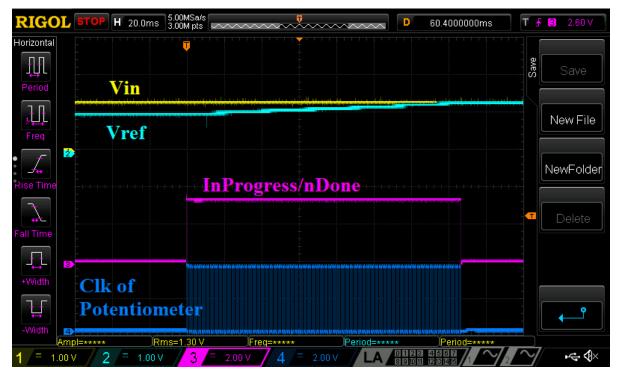

Figure 12 shows the results of software simulation of the tracking ADC with disabled auto-reload feature. It can be seen that after a start pulse, the clock signals come to the digital potentiometer. At each clock the potentiometer changes the wiper position (the 3<sup>rd</sup> common terminal) and the reference voltage approaches the input voltage. When the reference voltage at wiper terminal becomes equal to the input voltage, the ACMP changes its level. After the 3<sup>rd</sup> rising edge of the ACMP signal the process ends. The same process is demonstrated in Figure 13.

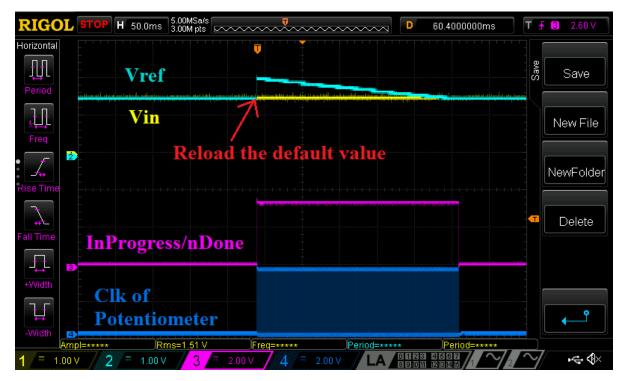

If auto-reload feature is disabled, the process begins from the current potentiometer state. But if auto-reload feature is enabled, the digital potentiometer starts counting from the default value defined by the User. The operation of the tracking ADC with enabled auto-reload feature is shown in Figure 14.

Figure 12: Software Simulation of ADC Operation with Disabled Auto-Reload Feature

# AN-CM-309

## **Tracking ADC**

Figure 13: Waveforms of ADC Operation with Disabled Auto-Reload Feature

Figure 14: Waveforms of ADC Operation with Enabled Auto-Reload Feature

| Application Note Revision 1.0 | 03-Nov-2020 |

|-------------------------------|-------------|

|-------------------------------|-------------|

# 7 Accuracy and Timing Characteristics

The most essential error sources of ADC are non-linearity (DNL and INL), gain error, and offset error. The output voltage considering errors caused by the rheostats DNL and INL can be estimated using formula (1). The digital rheostats of the SLG47004 have DNL and INL =  $\pm 1$  LSB (max).

$$Vout = \frac{Vref}{\frac{1LSB_{INL}}{1024}R \pm \frac{2LSB_{DNL}}{1024}R} \cdot \frac{R_{RH}}{1024} \cdot \left(N \pm 1LSB_{DNL} \pm \frac{1LSB_{INL}}{1024-N}\right),$$

(1)

where Vout – output voltage; Vref – reference voltage of divider;  $R_{RH}$  – maximum rheostat resistance; N – number of bits that corresponds to sampled voltage.

According to formula (1), the maximum error caused by the rheostats DNL and INL is ~2LSB. The next DC error source is the input offset voltage of the comparator. In the case of 2.048 V voltage reference of divider:

$$V_{offsetLSB} = V_{offsetACMP} \frac{1024}{2.048}$$

where  $V_{offsetLSB}$  and  $V_{offsetACMP}$  – comparator offset in LSB and in volts.

In the case of Chopper ACMP  $V_{offsetLSB} = 0.15$  LSB (0.3 mV maximal offset).

The absolute value of Vref is another additional error source. The Vref with accuracy of  $\pm 1$  % causes a gain error of 10 LSB. Eventually, full-scale error is **12.15 LSB max**.

Note that both gain and offset errors can be easily compensated by software, unlike DNL and INL errors.

Temperature drift of the system depends mainly on the temperature drift of internal Vref. It is equal to  $40 \mu$ V/°C. It should be noted that the temperature change doesn't affect the potentiometer ratio.

Maximum time of the conversion depends on the maximum allowed switching frequency of rheostats. The switching frequency of the rheostats is 1 kHz max in regular mode. Maximum time of the conversion:  $T_{Conv} = \frac{1}{f_{max}}(512 + 5) = 0.517$ s or ~2Hz

# 8 Conclusions

This application note describes the design of a simple tracking ADC based on the unique analog blocks within the SLG47004. Another popular type of ADC for the devices that don't have dedicated embedded ADC is the capacitor based or the Wilkinson ADC. The main principle of that ADC is the measurement of the time of an external capacitor charging (discharging). The comparison of these two ADC types can be found in Table 1.

| Table 1: The Comparison of Trackin | g ADC and Capacitor Based (Wilkinson) ADC |

|------------------------------------|-------------------------------------------|

|                                    |                                           |

| Parameter                                                 | Tracking ADC | Capacitor Based ADC                                                                                                  |  |

|-----------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------|--|

| External components                                       | -            | One capacitor                                                                                                        |  |

| The full-scale error without calibration, % of full range | 1.2 % (max)  | <ul> <li>&gt;10 % for mainstream<br/>capacitors</li> <li>&gt;1 % for best in class<br/>ceramic capacitors</li> </ul> |  |

| Temperature drift, ppm                                    | 20 ppm/°C    | From 30 ppm/°C to<br>2500 ppm/°C for ceramic<br>capacitors                                                           |  |

| Sample time, ms                                           | 517 (max)    | >7 (limited by the ACMP propagation error)                                                                           |  |

The data from Table 1 shows that the tracking ADC has much better accuracy performance while the Wilkinson is much faster.

# **Revision History**

| Revision | Date        | Description     |

|----------|-------------|-----------------|

| 1.0      | 03-Nov-2020 | Initial Version |

**Application Note**

**Revision 1.0**

03-Nov-2020

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.