# Application Note

## Design and Implementation of a Single-Phase Inverter

**AN-CM-270**

### Abstract

*This application note explores the use of a GreenPAK IC in Power Electronics Applications. This app note will demonstrate the implementation of a single-phase inverter using different control methodologies. In this app note Square and Quasi Square techniques will be implemented using a SLG46621V GreenPAK IC. One switching pattern is applied to SW1 and SW4 simultaneously, whereas the other switching pattern is applied to SW2 and SW3. Complex switching patterns are generated using the GreenPAK IC in order to realize the Quasi-square wave inverter implementation.*

*This application note comes complete with design files which can be found in the References section.*

## Design and Implementation of a Single-Phase Inverter

### Contents

|                                                                               |    |

|-------------------------------------------------------------------------------|----|

| <b>Abstract</b> .....                                                         | 1  |

| <b>Contents</b> .....                                                         | 2  |

| <b>Figures</b> .....                                                          | 2  |

| <b>Tables</b> .....                                                           | 3  |

| <b>1 Terms and Definitions</b> .....                                          | 4  |

| <b>2 References</b> .....                                                     | 4  |

| <b>3 Introduction</b> .....                                                   | 5  |

| 3.1 Single-Phase Inverter.....                                                | 5  |

| 3.2 Topologies of Single-Phase Inverter.....                                  | 5  |

| 3.2.1 Full-Bridge Topology.....                                               | 5  |

| 3.3 Insulated Gate Bipolar Transistor .....                                   | 6  |

| 3.4 Pulse Width Modulation Block in GreenPAK .....                            | 7  |

| <b>4 GreenPAK Design for PWM-Based Square Wave Implementation</b> .....       | 8  |

| 4.1 Disadvantage of Square Wave Control Strategy .....                        | 10 |

| <b>5 GreenPAK Design for PWM-Based Quasi-Square Wave Implementation</b> ..... | 10 |

| <b>6 Results</b> .....                                                        | 15 |

| <b>7 Conclusion</b> .....                                                     | 18 |

| <b>Revision History</b> .....                                                 | 19 |

### Figures

|                                                                                   |    |

|-----------------------------------------------------------------------------------|----|

| Figure 1: Full-Bridge Single-Phase Inverter Topology .....                        | 6  |

| Figure 2: Insulated Gate Bipolar Transistor.....                                  | 7  |

| Figure 3: Switching Pattern for S1 and S4 .....                                   | 8  |

| Figure 4: Output Voltage Waveform.....                                            | 8  |

| Figure 5: GreenPAK Design for Square Wave Control Strategy.....                   | 9  |

| Figure 6: Configuration Setting for PWM Block.....                                | 9  |

| Figure 7: Configuration Settings for FSM0 and FSM1 .....                          | 10 |

| Figure 8: Quasi Square Wave .....                                                 | 11 |

| Figure 9: GreenPAK Design for Square Wave Control Strategy.....                   | 11 |

| Figure 10: Configuration Settings for PWM Block.....                              | 12 |

| Figure 11: Configuration Settings for FSM0 and FSM1 .....                         | 13 |

| Figure 12: Configuration Settings for PDLY1 and CNT3.....                         | 14 |

| Figure 13: Configuration Settings for CNT7 and CNT8.....                          | 14 |

| Figure 14: Configuration Settings for CNT1 .....                                  | 15 |

| Figure 15: Switching Pattern for S1 and S4 .....                                  | 15 |

| Figure 16: Switching Pattern for S2 and S3 .....                                  | 15 |

| Figure 17: Output Waveform of Single-Phase Inverter .....                         | 16 |

| Figure 18: 12V Supply and Hardware Configuration for a Single-Phase Inverter..... | 16 |

| Figure 19: Single-Phase Inverter Using GreenPAK IC .....                          | 17 |

| Figure 20: Complete Hardware of Single-Phase Inverter .....                       | 17 |

**Design and Implementation of a Single-Phase Inverter****Tables**

|                                                   |   |

|---------------------------------------------------|---|

| Table 1: Switching States and Output Voltage..... | 5 |

|---------------------------------------------------|---|

---

## Design and Implementation of a Single-Phase Inverter

---

### 1 Terms and Definitions

|     |                           |

|-----|---------------------------|

| AC  | Alternating current       |

| DC  | Direct current            |

| THD | Total harmonic distortion |

| PWM | Pulse width modulation    |

### 2 References

For related documents and software, please visit:

[GreenPAK™ Programmable Mixed-Signal Products | Renesas](#)

Download our free [GreenPAK™ Designer software](#) [1] to open the .gp files [2] and view the proposed circuit design. Use the [GreenPAK](#) development tools [3] to freeze the design into your own customized IC in a matter of minutes. Find out more in complete library of application notes [4] featuring design examples as well as explanations of features and blocks within the GreenPAK IC.

- [1] [GreenPAK Designer Software](#), Software Download and User Guide

- [2] [AN-CM-270 Design and Implementation of Single-phase Inverter.gp](#), [GreenPAK Design File](#)

- [3] [GreenPAK Development Tools](#), [GreenPAK Development Tools Webpage](#)

- [4] [GreenPAK Application Notes](#), [GreenPAK Application Notes Webpage](#)

## Design and Implementation of a Single-Phase Inverter

### 3 Introduction

This application note explores the use of GreenPAK ICs in power electronics applications and will demonstrate the implementation of a single-phase inverter using various control methodologies. Different parameters are used to determine the quality of the single-phase inverter. An important parameter is Total Harmonic Distortion (THD). THD is a measurement of the harmonic distortion in a signal and is defined as the ratio of the sum of the powers of all harmonic components to the power of the fundamental frequency.

#### 3.1 Single-Phase Inverter

A power inverter, or inverter, is an electronic device or circuitry that changes direct current (DC) into alternating current (AC). Depending upon the number of phases of the AC output, there are several types of inverters.

- Single-phase inverters

- Three-phase inverters

DC is the unidirectional flow of electric charge. If a constant voltage is applied across a purely resistive circuit, it results in a constant current. Comparatively, with AC, the flow of electric current periodically reverses polarity. The most typical AC waveform is a sine wave, but it can also be a triangular or square wave. In order to transfer electrical power with different current profiles, special devices are required. Devices that convert AC into DC are known as rectifiers and devices that convert DC into AC are known as inverters.

#### 3.2 Topologies of Single-Phase Inverter

There are two main topologies of single-phase inverters; half-bridge and full-bridge topologies. This application note focusses on the full-bridge topology, since it provides double the output voltage compared to the half-bridge topology.

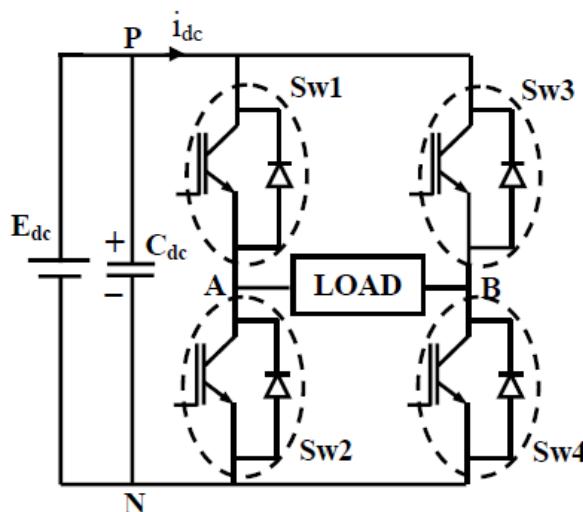

##### 3.2.1 Full-Bridge Topology

In a full-bridge topology 4 switches are needed, since the alternating output voltage is obtained by the difference between two branches of switching cells. The output voltage is obtained by intelligently switching the transistors on and off at particular time instants. There are four different states depending upon which switches are closed. The table below summarizes the states and output voltage based on which switches are closed.

**Table 1: Switching States and Output Voltage**

| State | Switches Closed | Vout |

|-------|-----------------|------|

| 1     | S1 & S2         | +Vdc |

| 2     | S3 & S4         | -Vdc |

| 3     | S1 & S3         | 0    |

| 4     | S2 & S4         | 0    |

To maximize the output voltage, the fundamental component of the input voltage on each branch must be 180° out of phase. The semiconductors of each branch are complementary in performance, which is to say when one is conducting the other is cut-off and vice versa. This topology is the most widely used for inverters. The diagram in Fig. 1 shows the circuit of a full-bridge topology for a single-phase inverter.

## Design and Implementation of a Single-Phase Inverter

Figure 1: Full-Bridge Single-Phase Inverter Topology

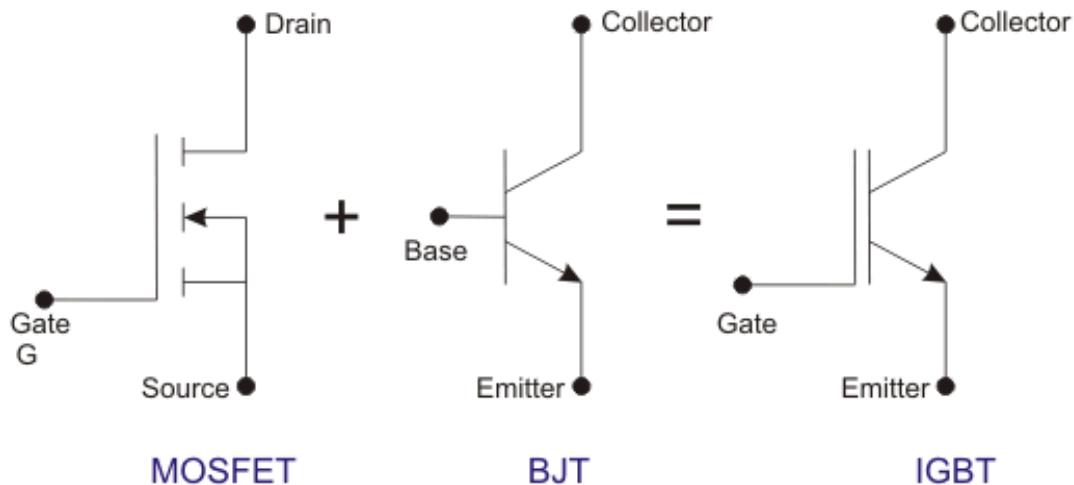

### 3.3 Insulated Gate Bipolar Transistor

The Insulated Gate Bipolar Transistor (IGBT) is like a MOSFET with the addition of a third PN-junction. This allows voltage-based control, like a MOSFET, but with output characteristics like a BJT regarding high loads and low saturation voltage.

Four main regions can be observed on its static behavior.

- Avalanche Region

- Saturation Region

- Cut Area

- Active Region

The avalanche region is the area when a voltage below breakdown voltage is applied, resulting in the destruction of the IGBT. The cut area includes values from breakdown voltage up to threshold voltage, wherein the IGBT doesn't conduct. In the saturation region, the IGBT behaves as a dependent voltage source and a series resistance. With low variations of voltage, high amplification of current can be achieved. This area is the most desirable for operation. If the voltage is augmented, the IGBT enters the active region, and current remains constant. There is a maximum voltage applied for the IGBT to ensure it won't enter the avalanche region. This is one of the most used semiconductors in power electronics, since it can support a wide range of voltages from a few volts to kV and powers between kW and MW.

## Design and Implementation of a Single-Phase Inverter

Figure 2: Insulated Gate Bipolar Transistor

These Insulated Gate Bipolar Transistors act as switching devices for the full-bridge single-phase inverter topology.

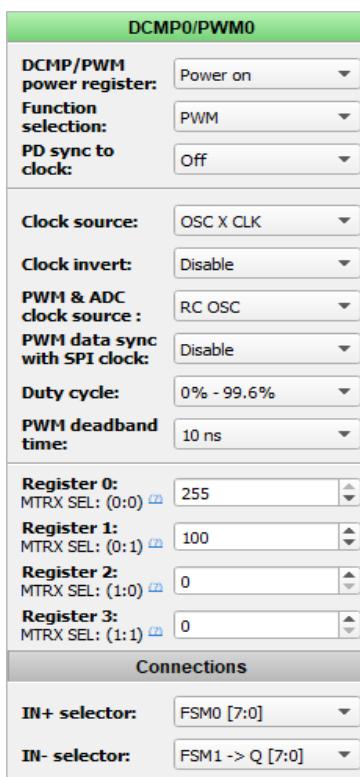

### 3.4 Pulse Width Modulation Block in GreenPAK

The Pulse Width Modulation (PWM) Block is a useful block that can be used for a wide range of applications. The DCMP/PWM Block can be configured as a PWM Block. The PWM block can be sourced through FSM0 and FSM1. PWM IN+ pin is connected to FSM0 whereas IN- pin is connected to FSM1. Both FSM0 and FSM1 provides 8-bit data to PWM Block. PWM time period is defined by the time period of FSM1. The duty cycle for the PWM block is controlled by the FSM0.

$$\text{Output Duty Cycle} = \frac{IN_+}{256}$$

There are two options for the duty cycle configuration:

- 0-99.6%: DC ranges from 0% to 99.6% and is determined as  $IN_+/256$ .

- 0.39-100%: DC ranges from 0.39% to 100% and is determined as  $(IN_+ + 1)/256$ .

## Design and Implementation of a Single-Phase Inverter

### 4 GreenPAK Design for PWM-Based Square Wave Implementation

There are different control methodologies that can be used to implement a single-phase inverter. One such control strategy includes a PWM-based square wave for the single-phase inverter.

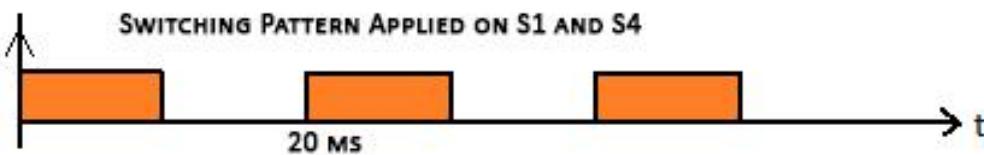

A **GreenPAK** IC is used to generate periodic switching patterns in order to conveniently convert DC into AC. The DC voltages are fed from the battery and the output obtained from the inverter can be used to supply the AC load. For the purpose of this application note the AC frequency has been set to 50Hz, a common household power frequency in many parts of the world. Correspondingly, the period is 20ms.

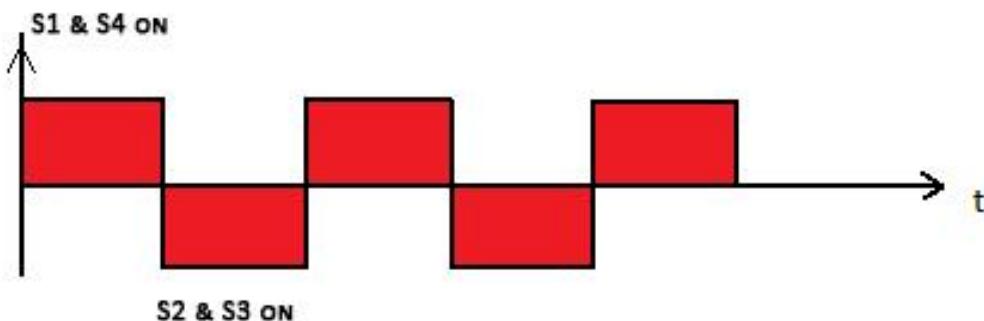

The switching pattern that must be generated by **GreenPAK** for SW1 and SW4 is shown in Fig. 3.

Figure 3: Switching Pattern for S1 and S4

The switching pattern for SW2 and SW3 is shown in Fig. 4

Figure 4: Output Voltage Waveform

The above switching patterns can be conveniently produced using a PWM block. The PWM time period is set by the time period of FSM1. The time period for FSM1 must be set to 20ms corresponding to 50Hz frequency. The duty cycle for the PWM block is controlled by the data sourced from FSM0. In order to generate the 50% duty cycle, the FSM0 counter value is set to be 128.

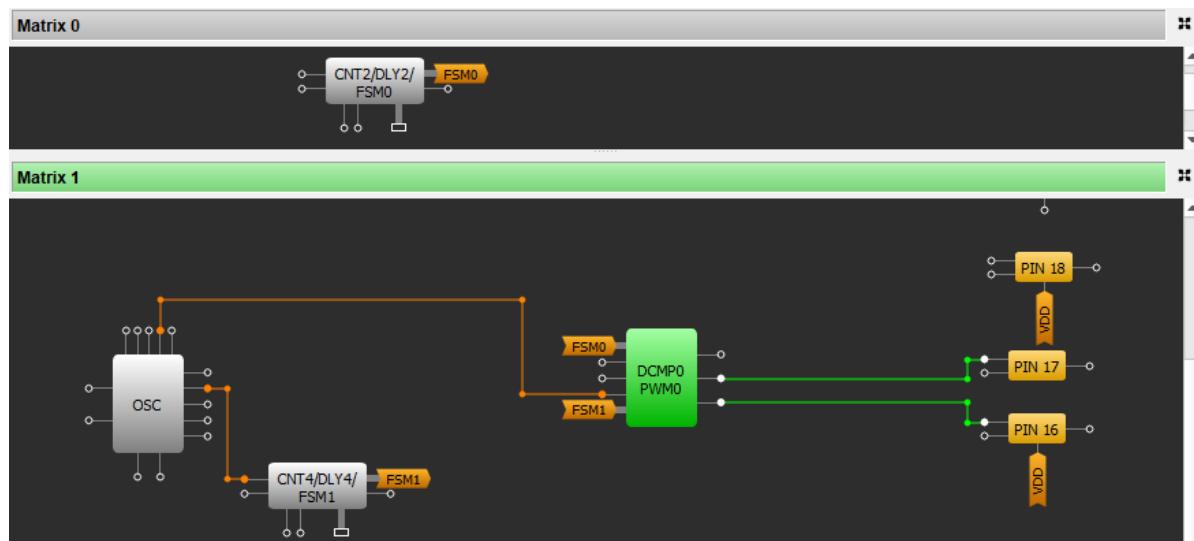

The corresponding **GreenPAK** Design is shown in Fig. 5.

## Design and Implementation of a Single-Phase Inverter

Figure 5: GreenPAK Design for Square Wave Control Strategy

Figure 6: Configuration Setting for PWM Block

## Design and Implementation of a Single-Phase Inverter

|                                      |                                 |                                      |                               |

|--------------------------------------|---------------------------------|--------------------------------------|-------------------------------|

| <b>14-bit CNT2/DLY2/FSM0</b>         |                                 | <b>8-bit CNT4/DLY4/FSM1</b>          |                               |

| <b>Mode:</b>                         | Counter/FSM                     | <b>Mode:</b>                         | Counter/FSM                   |

| <b>Counter data:</b>                 | 128<br>(Range: 1 - 16383)       | <b>Counter data:</b>                 | 124<br>(Range: 1 - 255)       |

| <b>Output period (typical):</b>      | 5.16 ms <a href="#">Formula</a> | <b>Output period (typical):</b>      | 20 ms <a href="#">Formula</a> |

| <b>Edge select:</b>                  | Both                            | <b>Edge select:</b>                  | Both                          |

| <b>Counter value control:</b>        | Reset (counter value)           | <b>Counter value control:</b>        | Reset (counter value)         |

| <b>DFF bypass enable:</b>            | None                            | <b>DFF bypass enable:</b>            | None                          |

| <b>FSM data sync with SPI clock:</b> | Disable                         | <b>FSM data sync with SPI clock:</b> | Disable                       |

| <b>Connections</b>                   |                                 |                                      |                               |

| <b>FSM data:</b>                     | Counter data                    | <b>FSM data:</b>                     | Counter data                  |

| <b>Clock:</b>                        | CLK                             | <b>Clock:</b>                        | CLK /4                        |

| <b>Clock source:</b>                 | RC OSC Freq.                    | <b>Clock source:</b>                 | RC OSC Freq. /4               |

| <b>Clock frequency:</b>              | 25 kHz                          | <b>Clock frequency:</b>              | 6.25 kHz                      |

Figure 7: Configuration Settings for FSM0 and FSM1

### 4.1 Disadvantage of Square Wave Control Strategy

Using the square wave control strategy causes the inverter to produce a large amount of harmonics. Apart from the fundamental frequency, square wave inverters have odd frequency components. These harmonics cause machine flux to be saturated, thus leading to poor performance of the machine, sometimes even damaging the hardware. Hence, the THD produced by these types of inverters is very large. In order to overcome this problem another control strategy known as Quasi-Square Wave can be employed to significantly reduce the amount of harmonics produced by the inverter.

## 5 GreenPAK Design for PWM-Based Quasi-Square Wave Implementation

In Quasi-square wave control strategy, a zero output voltage is introduced which can significantly reduce the harmonics present in the conventional square waveform. Major advantages of using a Quasi-square wave inverter include:

- Amplitude of the fundamental component can be controlled (by controlling  $\alpha$ )

- Certain harmonic contents can be eliminated (also by controlling  $\alpha$ )

## Design and Implementation of a Single-Phase Inverter

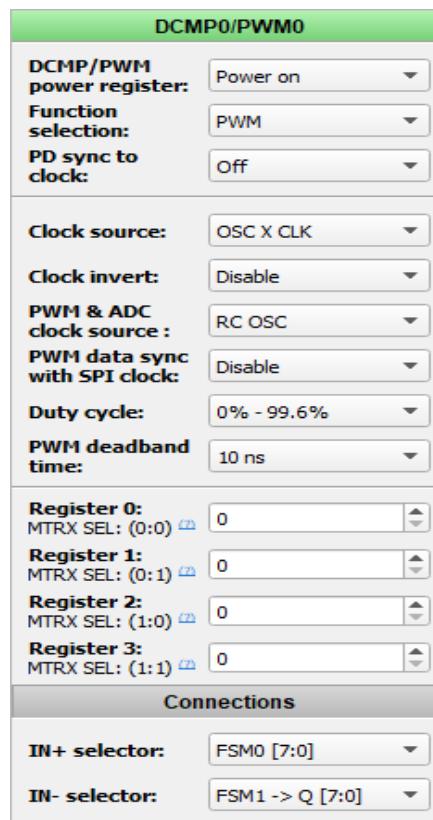

Figure 8: Quasi Square Wave

The amplitude of the fundamental component can be controlled by controlling the value of  $\alpha$

$$V_1 = \frac{4V_{dc}}{\pi} \cos \alpha$$

The nth harmonic can be eliminated if its amplitude is made zero. For example, the amplitude of the third harmonic ( $n=3$ ) is zero when  $\alpha = 30^\circ$

$$V_1 = \frac{4V_{dc}}{\pi} \cos(3 * 30) = 0$$

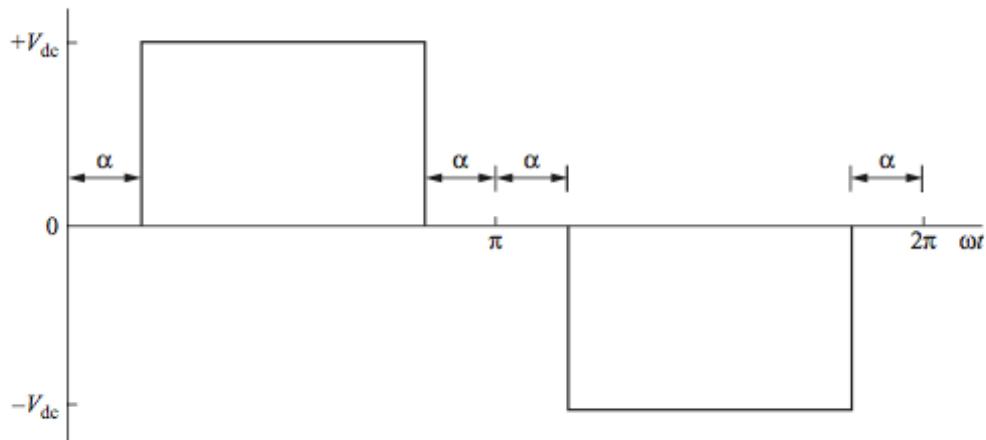

The [GreenPAK](#) Design for Implementing the Quasi- Square Wave control strategy is shown in Fig. 9.

Figure 9: GreenPAK Design for Square Wave Control Strategy

The PWM block is used to generate a square waveform with 50 % duty cycle. The zero output voltage is introduced by delaying the voltage appearing across output Pin-15. The P-DLY1 block is configured to detect the rising edge of the waveform. P-DLY1 will periodically detect the rising edge after each period and trigger the DLY-3 block, which produces a delay of 2ms before clocking the VDD across a D-flip flop to enable the Pin-15 output.

## Design and Implementation of a Single-Phase Inverter

Pin-15 can cause both SW1 and SW4 to turn on. When this occurs, a positive voltage will appear across the load.

The P-DLY1 rising edge detection mechanism also activates the DLY-7 block, which after 8ms resets the D-flip flop and 0 V appears across the output.

DLY-8 and DLY-9 are also triggered from the same rising edge. DLY-8 produces a delay of 10ms and triggers DLY-3 again, which after 2ms will clock the DFF causing a logical high across the two AND gates.

At this point Out+ from the PWM block becomes 0, since the duty cycle of the block was configured to be 50 %. Out- will appear across Pin-16 causing the SW2 and SW3 to turn on, producing an alternating voltage across the load. After 18ms DLY-9 will reset the DFF and 0V will appear across the Pin-16 and the periodic cycle continues to output an AC signal.

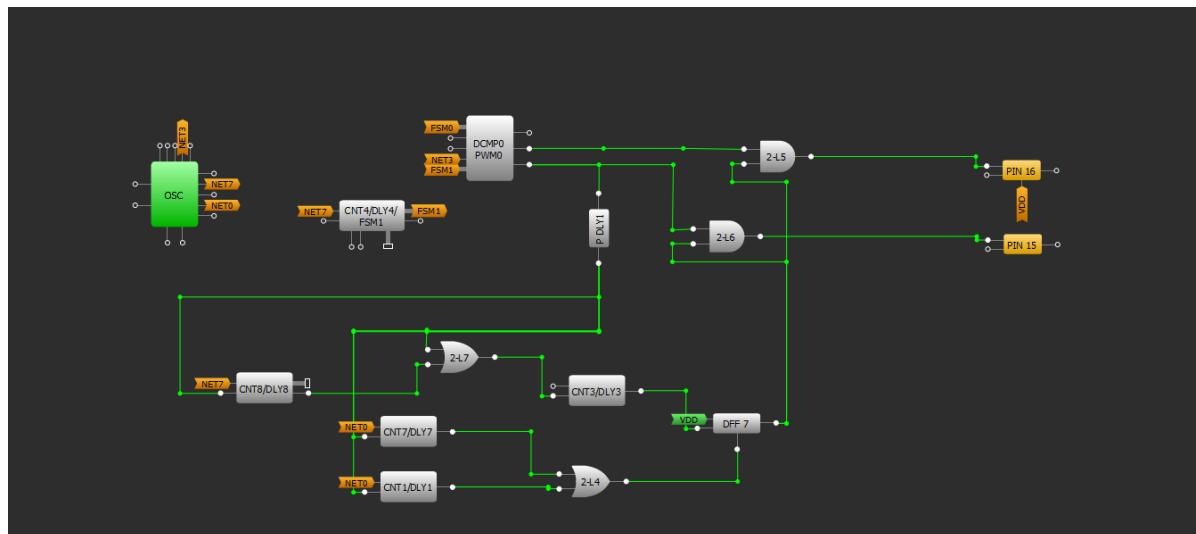

The configuration for different **GreenPAK** blocks are shown in Figs 10-14.

Figure 10: Configuration Settings for PWM Block

## Design and Implementation of a Single-Phase Inverter

| 14-bit CNT2/DLY2/FSM0                |                     | 8-bit CNT4/DLY4/FSM1                 |                     |

|--------------------------------------|---------------------|--------------------------------------|---------------------|

| <b>Mode:</b>                         | Counter/FSM         | <b>Mode:</b>                         | Counter/FSM         |

| <b>Counter data:</b>                 | 128                 | <b>Counter data:</b>                 | 124                 |

| (Range: 1 - 16383)                   |                     | (Range: 1 - 255)                     |                     |

| <b>Output period (typical):</b>      | 5.16 ms             | <b>Output period (typical):</b>      | 20 ms               |

| <a href="#">Formula</a>              |                     | <a href="#">Formula</a>              |                     |

| <b>Edge select:</b>                  | Both                | <b>Edge select:</b>                  | Both                |

| <b>Counter value control:</b>        | Reset (counter valu | <b>Counter value control:</b>        | Reset (counter valu |

| <a href="#">▼</a>                    | <a href="#">▼</a>   | <a href="#">▼</a>                    | <a href="#">▼</a>   |

| <b>DFF bypass enable:</b>            | None                | <b>DFF bypass enable:</b>            | None                |

| <b>FSM data sync with SPI clock:</b> | Disable             | <b>FSM data sync with SPI clock:</b> | Disable             |

| <b>Connections</b>                   |                     |                                      |                     |

| <b>FSM data:</b>                     | Counter data        | <b>FSM data:</b>                     | Counter data        |

| <b>Clock:</b>                        | CLK                 | <b>Clock:</b>                        | CLK /4              |

| <b>Clock source:</b>                 | RC OSC Freq.        | <b>Clock source:</b>                 | RC OSC Freq. /4     |

| <b>Clock frequency:</b>              | 25 kHz              | <b>Clock frequency:</b>              | 6.25 kHz            |

Figure 11: Configuration Settings for FSM0 and FSM1

## Design and Implementation of a Single-Phase Inverter

| <div style="border: 1px solid #ccc; padding: 10px; border-bottom: none;"> <p style="background-color: #90EE90; color: white; padding: 2px 0; margin: 0;"><b>P DLY1</b></p> <p><b>Mode:</b> Rising edge detect</p> <p><b>Delay:</b> 1 Cell</p> <p><b>Output mode:</b> Non-delayed</p> </div> <div style="border: 1px solid #ccc; padding: 10px; border-top: none;"> <p><b>Information</b></p> <p><b>Delay and pulse width</b></p> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th>VDD (V)</th> <th>Delay (ns)</th> <th>Pulse width (ns)</th> </tr> </thead> <tbody> <tr> <td>1.8</td> <td>30.12</td> <td>340.2</td> </tr> <tr> <td>3.3</td> <td>12.27</td> <td>153.7</td> </tr> <tr> <td>5.0</td> <td>8.48</td> <td>112.66</td> </tr> </tbody> </table> </div> | VDD (V)    | Delay (ns)       | Pulse width (ns) | 1.8 | 30.12 | 340.2 | 3.3 | 12.27 | 153.7 | 5.0 | 8.48 | 112.66 | <div style="border: 1px solid #ccc; padding: 10px; border-bottom: none;"> <p style="background-color: #90EE90; color: white; padding: 2px 0; margin: 0;"><b>14-bit CNT3/DLY3</b></p> <p><b>Mode:</b> Delay</p> <p><b>Counter data:</b> 48<br/>(Range: 1 - 16383)</p> <p><b>Delay time (typical):</b> 2.02 ms <a href="#">Formula</a></p> <p><b>Edge select:</b> Both</p> <p><b>Counter value control:</b> None</p> <p><b>DFF bypass enable:</b> None</p> </div> <div style="border: 1px solid #ccc; padding: 10px; border-top: none;"> <p><b>Connections</b></p> <p><b>FSM data:</b> None</p> <p><b>Clock:</b> CLK</p> <p><b>Clock source:</b> RC OSC Freq.</p> <p><b>Clock frequency:</b> 25 kHz</p> </div> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|------------------|-----|-------|-------|-----|-------|-------|-----|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD (V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Delay (ns) | Pulse width (ns) |                  |     |       |       |     |       |       |     |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30.12      | 340.2            |                  |     |       |       |     |       |       |     |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12.27      | 153.7            |                  |     |       |       |     |       |       |     |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8.48       | 112.66           |                  |     |       |       |     |       |       |     |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Figure 12: Configuration Settings for PDLY1 and CNT3

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <div style="border: 1px solid #ccc; padding: 10px; border-bottom: none;"> <p style="background-color: #90EE90; color: white; padding: 2px 0; margin: 0;"><b>8-bit CNT7/DLY7</b></p> <p><b>Mode:</b> Counter</p> <p><b>Counter data:</b> 49<br/>(Range: 1 - 255)</p> <p><b>Output period (typical):</b> 8 ms <a href="#">Formula</a></p> <p><b>Edge select:</b> Both</p> <p><b>Counter value control:</b> None</p> <p><b>DFF bypass enable:</b> None</p> </div> <div style="border: 1px solid #ccc; padding: 10px; border-top: none;"> <p><b>Connections</b></p> <p><b>FSM data:</b> None</p> <p><b>Clock:</b> CLK /4</p> <p><b>Clock source:</b> RC OSC Freq. /4</p> <p><b>Clock frequency:</b> 6.25 kHz</p> </div> | <div style="border: 1px solid #ccc; padding: 10px; border-bottom: none;"> <p style="background-color: #90EE90; color: white; padding: 2px 0; margin: 0;"><b>8-bit CNT8/DLY8</b></p> <p><b>Mode:</b> Counter/PWM ramp</p> <p><b>Counter data:</b> 62<br/>(Range: 1 - 255)</p> <p><b>Output period (typical):</b> 10.08 ms <a href="#">Formula</a></p> <p><b>Edge select:</b> Both</p> <p><b>Counter value control:</b> None</p> <p><b>DFF bypass enable:</b> None</p> </div> <div style="border: 1px solid #ccc; padding: 10px; border-top: none;"> <p><b>Connections</b></p> <p><b>FSM data:</b> None</p> <p><b>Clock:</b> CLK /4</p> <p><b>Clock source:</b> RC OSC Freq. /4</p> <p><b>Clock frequency:</b> 6.25 kHz</p> </div> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Figure 13: Configuration Settings for CNT7 and CNT8

## Design and Implementation of a Single-Phase Inverter

**14-bit CNT1/DLY1**

|                                 |                                  |

|---------------------------------|----------------------------------|

| <b>Mode:</b>                    | Counter                          |

| <b>Counter data:</b>            | 112<br>(Range: 1 - 16383)        |

| <b>Output period (typical):</b> | 18.08 ms <a href="#">Formula</a> |

| <b>Edge select:</b>             | Both                             |

| <b>Counter value control:</b>   | None                             |

| <b>DFF bypass enable:</b>       | None                             |

| <b>Connections</b>              |                                  |

| <b>FSM data:</b>                | None                             |

| <b>Clock:</b>                   | CLK /4                           |

| <b>Clock source:</b>            | RC OSC Freq. /4                  |

| <b>Clock frequency:</b>         | 6.25 kHz                         |

Figure 14: Configuration Settings for CNT1

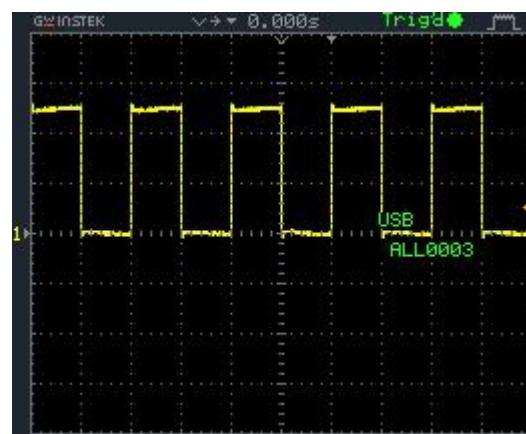

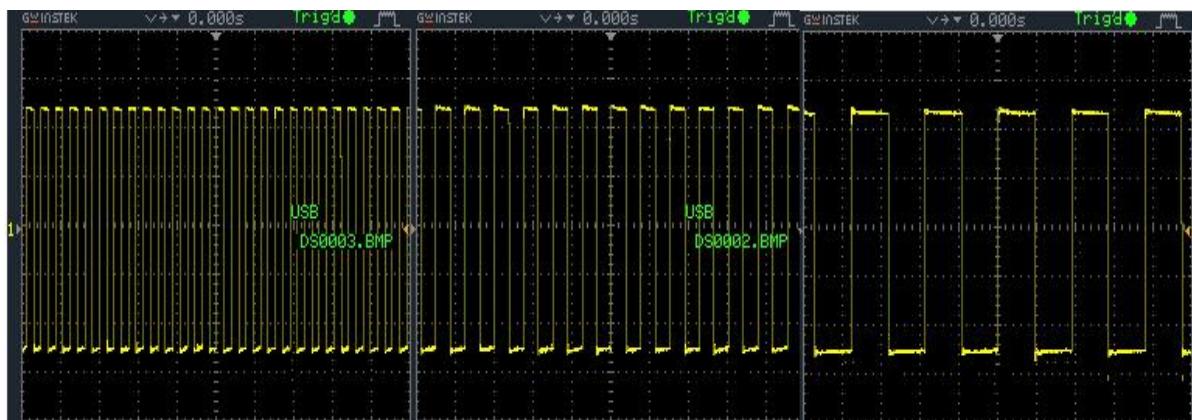

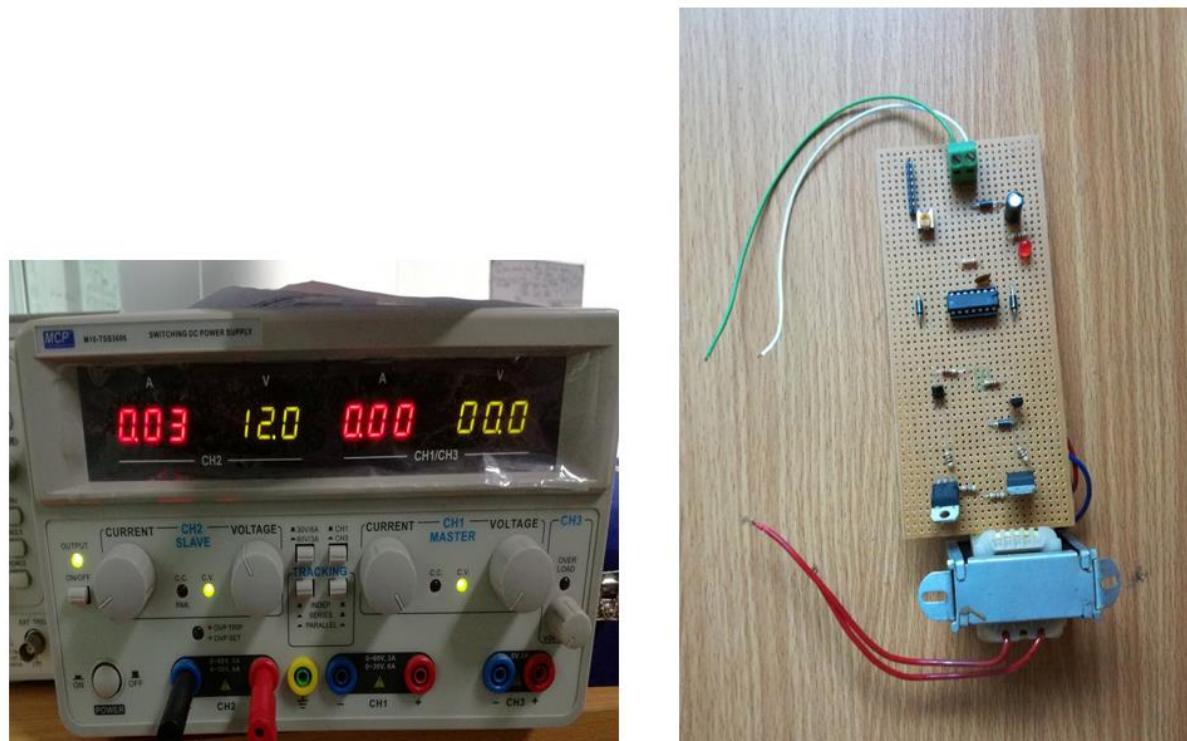

## 6 Results

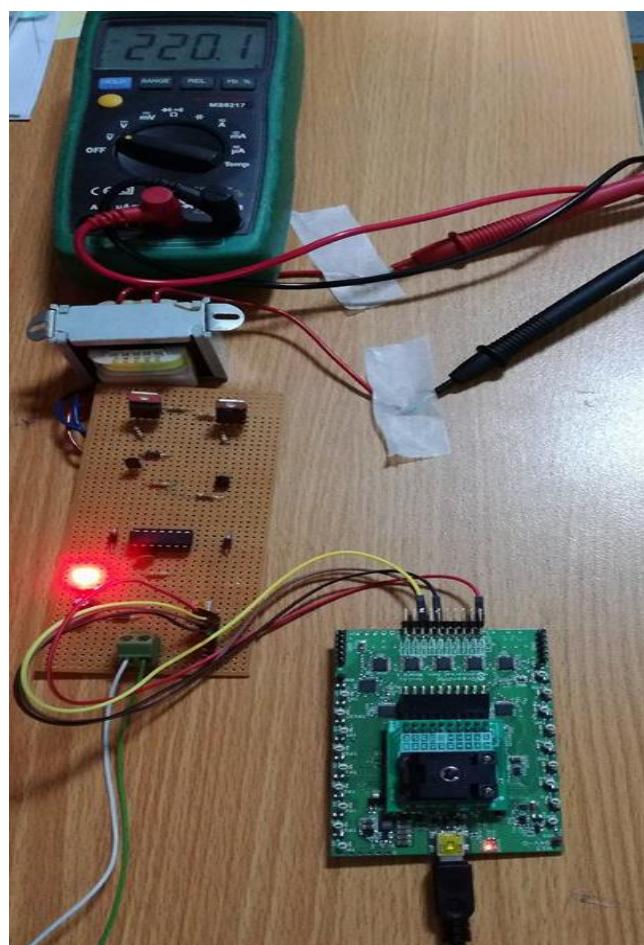

12 V DC voltage is supplied from the battery to the inverter. The inverter converts this voltage into an AC waveform. The output from the inverter is fed to a step-up transformer which converts 12 V AC Voltage into 220 V which can be used to drive the AC loads.

Figure 15: Switching Pattern for S1 and S4

Figure 16: Switching Pattern for S2 and S3

## Design and Implementation of a Single-Phase Inverter

Figure 17: Output Waveform of Single-Phase Inverter

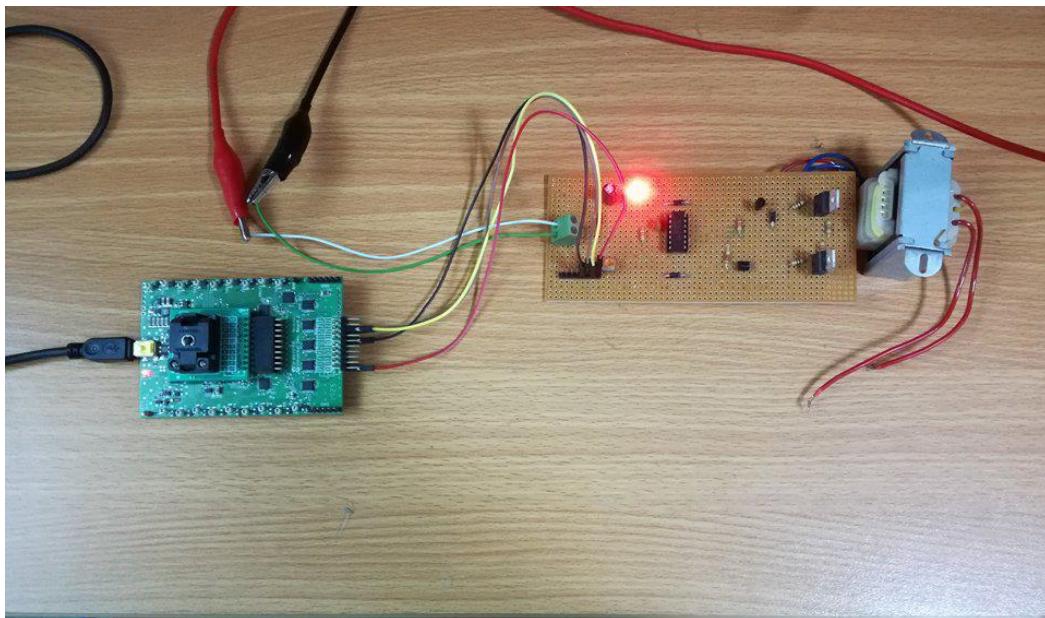

Figure 18: 12V Supply and Hardware Configuration for a Single-Phase Inverter

## Design and Implementation of a Single-Phase Inverter

Figure 19: Single-Phase Inverter Using GreenPAK IC

Figure 20: Complete Hardware of Single-Phase Inverter

---

## Design and Implementation of a Single-Phase Inverter

---

### 7 Conclusion

In this application note, we have implemented a Single-Phase Inverter using Square Wave and Quasi Square Wave control strategies using a [GreenPAK](#) IC. [GreenPAK](#) ICs act as a convenient substitute of Micro Controllers and analog circuitry that is conventionally used to implement a Single-phase inverter. Furthermore, [GreenPAK](#) ICs have potential in the design of Three Phase Inverters.

---

**Design and Implementation of a Single-Phase Inverter**

---

**Revision History**

| Revision | Date        | Description     |

|----------|-------------|-----------------|

| 1.0      | 18-Feb-2019 | Initial Version |

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).