## **Capacitive Sensor Microcontrollers**

## CTSU Capacitive Touch Electrode Design Guide

## Introduction

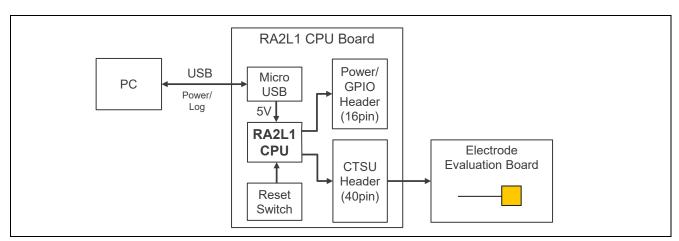

This application note describes how to design electrode patterns, with sample patterns for reference, for MCUs embedding the Capacitive Touch Sensing Unit (CTSU).

For information on the power supply design and layout of microcontrollers, refer to the following application notes.

Capacitive Sensor MCU Capacitive Touch Ripple Noise Prevention Guide

## **Target Device**

RX Family, RA Family, and RL78 Family MCUs and Renesas Synergy™ embedding the CTSU

(CTSU indicates CTSU2, CTSU2L, CTSU2SL, etc.)

In addition, refer to CTSU2 for CTSU2L/CTSU2La/CTSU2SL/CTSU2SLa after the next page."

## Contents

| 1.    | Outline                                                    | 4   |

|-------|------------------------------------------------------------|-----|

| 2.    | Self-capacitance Method Buttons: Electrode Layout Patterns | 4   |

| 2.1   | Outline of Design Recommendations                          | . 4 |

| 2.2   | Self-capacitance Method Overview                           | . 6 |

| 2.3   | Principle of CTSU Self-capacitance Method Detection        | . 6 |

| 2.4   | Electrode Pattern Design                                   | . 9 |

| 2.4.1 | Electrode circuit configuration                            | . 9 |

| 2.4.2 | Electrode pads and wiring                                  | 10  |

| 2.4.3 | Wiring                                                     | 11  |

| 2.5   | Anti-Noise Layout Pattern Designs                          | 14  |

| 2.5.1 | Shield pattern                                             | 14  |

| 2.5.1 | .1 Shield design                                           | 14  |

| 2.5.1 | .2 GND shield                                              | 15  |

| 2.5.1 | .3 Active shield (CTSU2 function)                          | 16  |

| 2.6   | Effect of Panel Thickness                                  | 20  |

| 2.6.1 | Relationship of panel thickness and touch sensitivity      | 20  |

| 2.6.2 | Relationship of panel thickness and crosstalk              | 21  |

| 2.7   | Electrode Application Examples                             | 22  |

| 2.7.1 | Example of slider electrode layout pattern design          | 22  |

| 2.7.2 | Example of wheel layout pattern design                     | 22  |

| 2.7.3 | Film-type circuit boards                                   | 22  |

| 2.7.3 | .1 Flexible printed circuit boards                         | 22  |

| 2.7.3 | .2 Film device                                             | 23  |

| 2.7.3 | .3 Design example                                          | 24  |

| 2.7.4 LED wiring layout                                             | 25 |

|---------------------------------------------------------------------|----|

| 2.7.4.1 Direct lighting example                                     |    |

| 2.7.4.2 Indirect lighting (using light guide plate)                 |    |

| 2.7.5 When panel and button electrodes are separated                |    |

| 2.7.6 Self-capacitance Matrix                                       |    |

| 2.7.7 Precautions for Using RF Communication Device                 |    |

| 2.7.8 Design Example of Metal Overlay Panel                         |    |

| 3. Mutual Capacitance Method: Electrode Layout Patterns             | 27 |

| 3.1 Outline of Design Recommendations                               |    |

| 3.2 Mutual-capacitance Method Overview                              |    |

| 3.3 Principle of CTSU Mutual-capacitance Method Detection           |    |

| 3.4 Electrode Pattern Designs                                       |    |

| 3.4.1 Electrode circuit configuration                               |    |

| 3.4.2 Electrode pads                                                | 30 |

| 3.4.3 Wiring                                                        | 33 |

| 3.5 Distance from Touch Surface to Electrode                        | 35 |

| 3.6 Anti-noise Layout Pattern Designs                               | 36 |

| 3.6.1 Shield Patterns                                               | 36 |

| 3.6.1.1 Shield shapes                                               | 36 |

| 3.6.1.2 GND shield                                                  | 37 |

| 3.7 Design Application Examples                                     | 38 |

| 3.7.1 Water-resistant electrode layout pattern design               | 38 |

| 3.7.2 LED wiring layout                                             | 39 |

| 3.7.2.1 Direct lighting example                                     | 39 |

| 3.7.2.2 Indirect lighting example                                   | 40 |

| 4. Reference Materials                                              | 41 |

| 4.1 Reference Documents                                             | 41 |

| 4.2 Base Clock Frequency/Sensor Drive Pulse Frequency Settings      | 42 |

| 4.2.1 Normal Operating Mode                                         | 42 |

| 4.2.2 Low Voltage Operating Mode                                    | 44 |

| 5. Self-capacitance Method Button Patterns and Characteristics Data | 45 |

| 5.1 Self-capacitance Method Button Sensitivity (SNR)                |    |

| <ul><li>5.2 Evaluation Conditions</li></ul>                         |    |

| 5.3 Design Parameters and Sensitivity Characteristics               |    |

| 5.3.1 Electrode Size                                                |    |

| 5.3.2 Wiring Length                                                 |    |

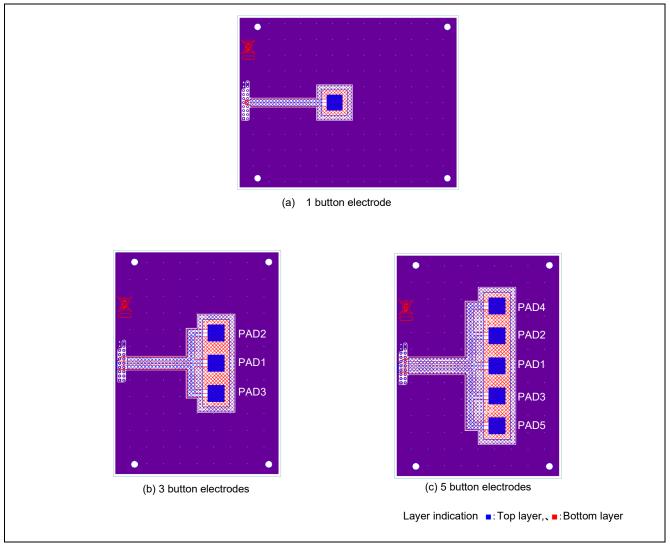

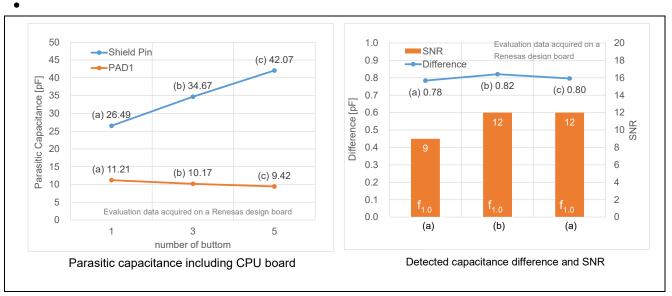

| 5.3.3 Multiple Button Design                                        |    |

| 5.3.3.1 Wiring Pitch                                                |    |

| 5.3.3.2 Distance between Button Electrodes                          |    |

| 5.3.4   | GND Pattern Design                                                 | . 57 |

|---------|--------------------------------------------------------------------|------|

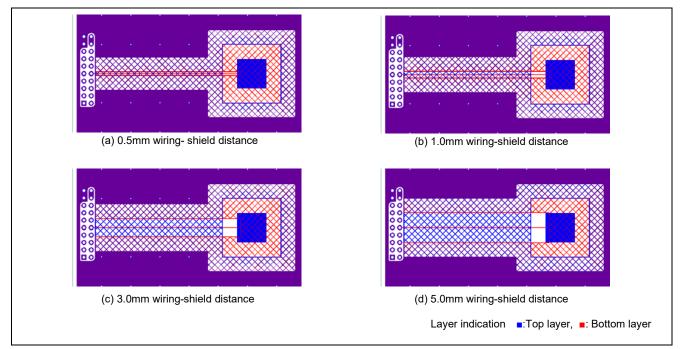

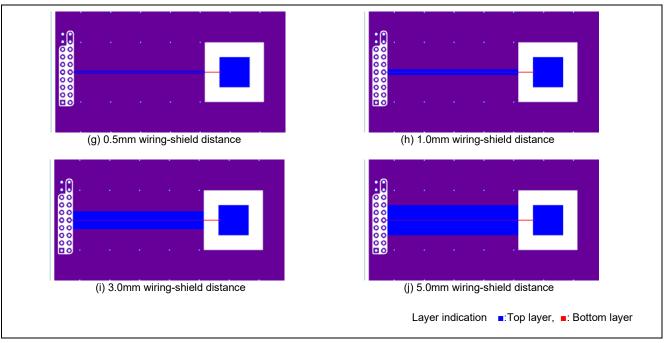

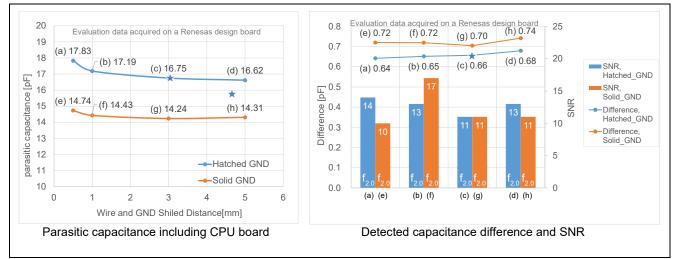

| 5.3.4.1 | Electrode and Shield Distance                                      | . 57 |

| 5.3.4.2 | Distance between Wiring and Shield                                 | . 59 |

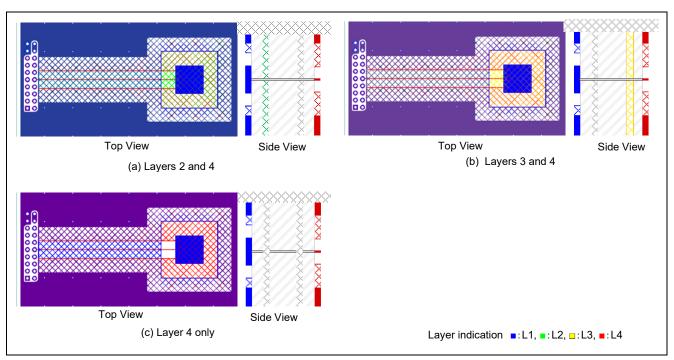

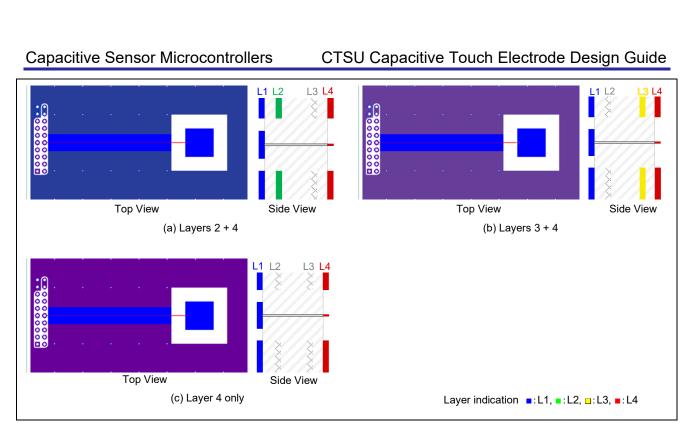

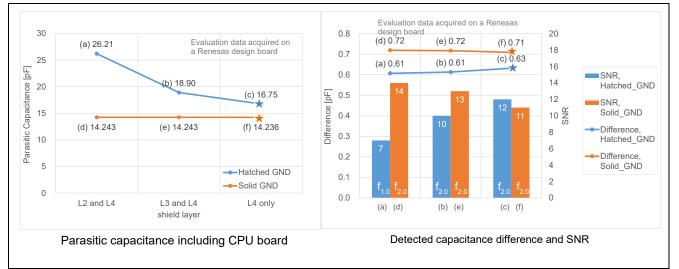

| 5.3.4.3 | Effect of Inner Layer GND                                          | . 61 |

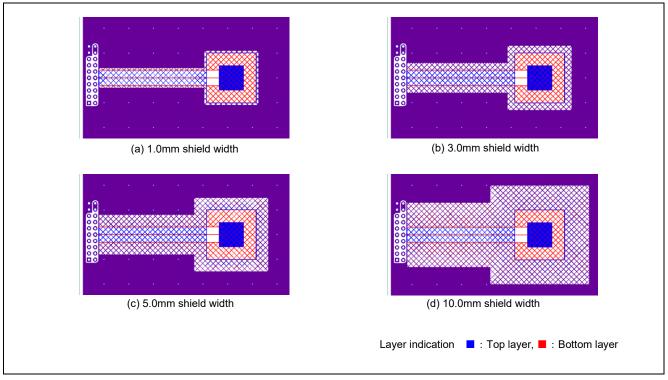

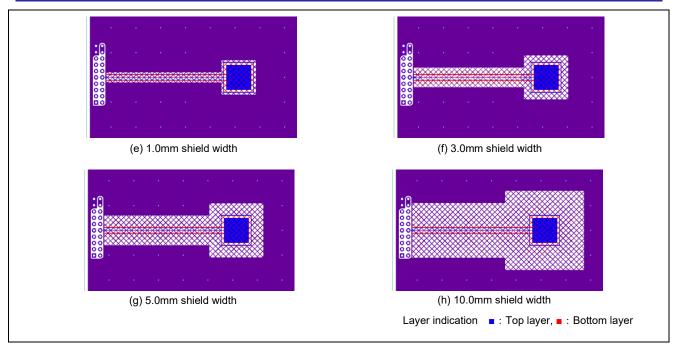

| 5.3.4.4 | Cross-hatched Shield Pattern Width                                 | . 63 |

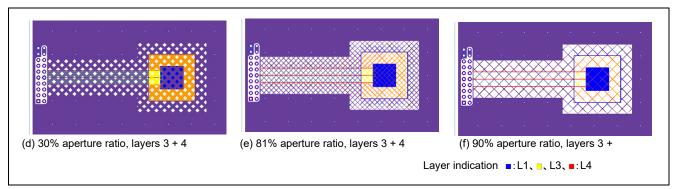

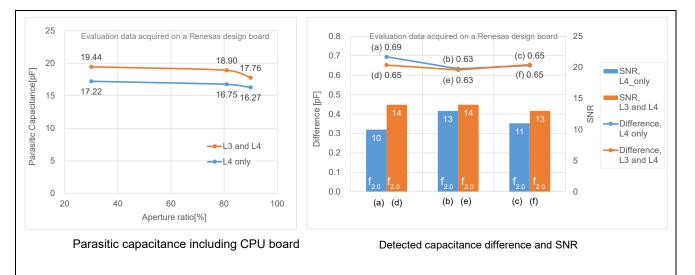

| 5.3.4.5 | Cross-hatched Shield Pattern Aperture Ratio                        | . 66 |

| 5.3.5   | Active Shield Design                                               | . 68 |

| 5.3.5.1 | Active Shield Area                                                 | . 68 |

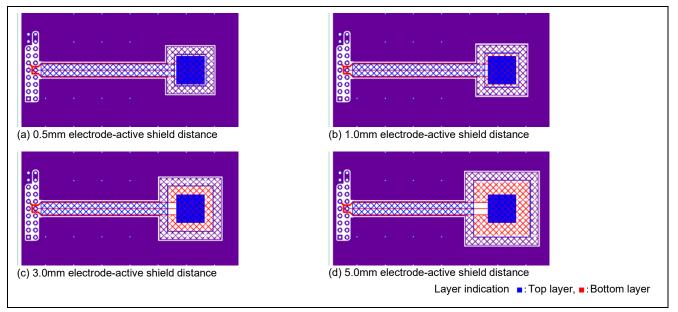

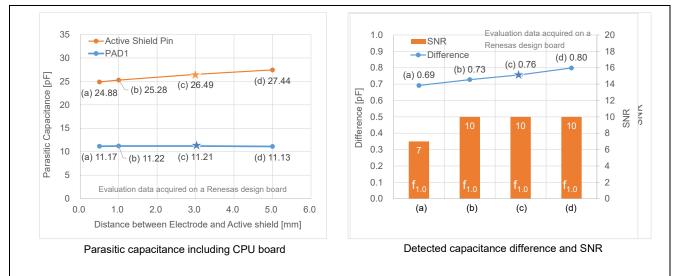

| 5.3.5.2 | Distance Between Electrode and Active Shield                       | . 70 |

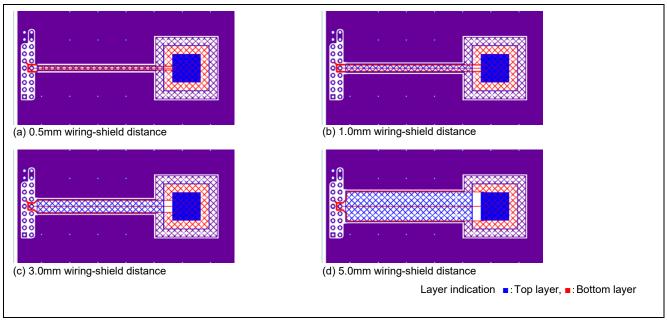

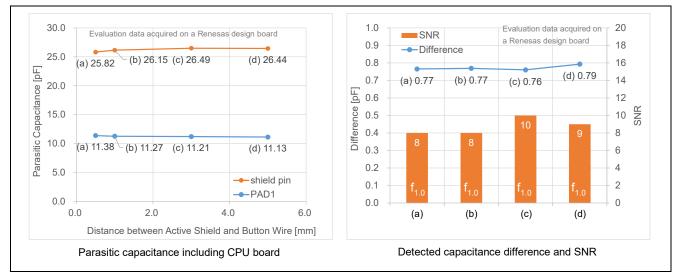

| 5.3.5.3 | Distance between Wiring and Active Shield                          | . 72 |

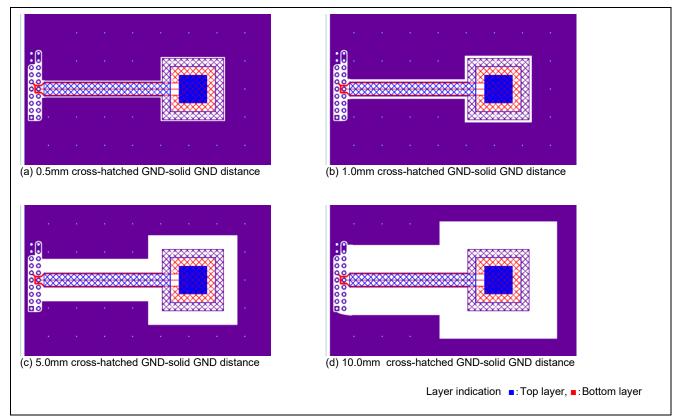

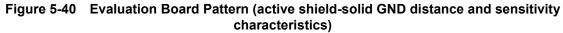

| 5.3.5.4 | Distance Between Active Shield and Solid GND                       | . 74 |

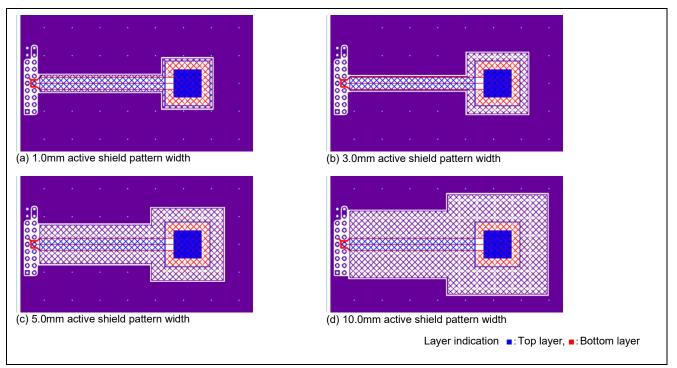

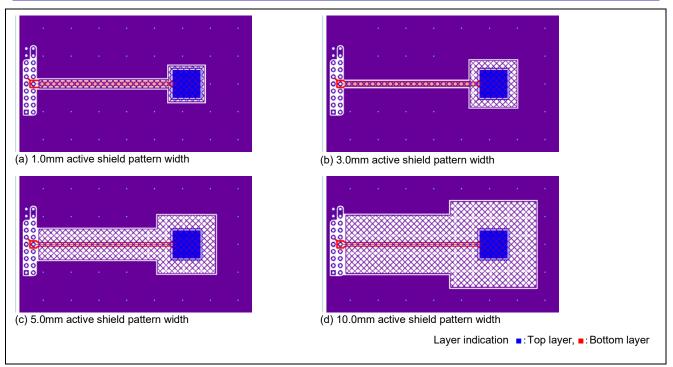

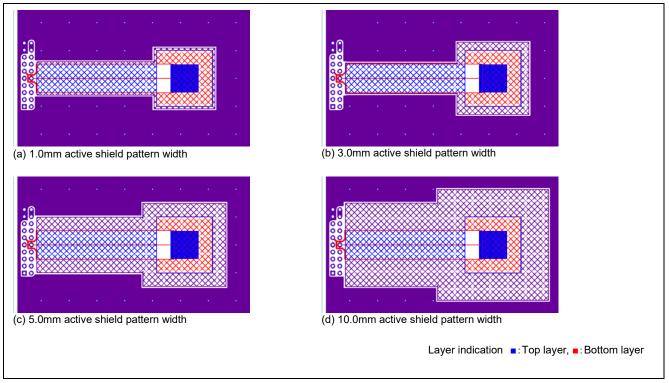

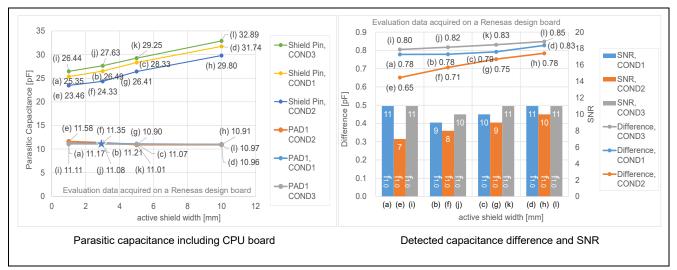

| 5.3.5.5 | Active Shield Pattern Width                                        | . 76 |

| 5.3.5.6 | Damping Resistance Value of Active Shield Pin                      | . 79 |

| 5.3.6   | Parameters Unrelated to Board Design                               | . 80 |

| 5.3.6.1 | Overlay Panel Design and Sensitivity Characteristics               | . 80 |

| 5.3.6.2 | Electrode Damping Resistance Value and Sensitivity Characteristics | . 82 |

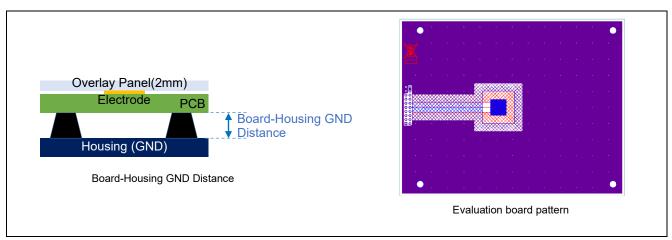

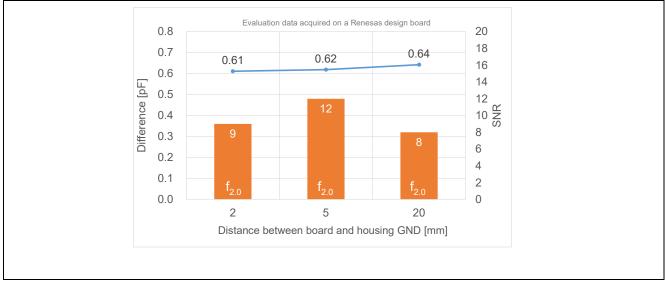

| 5.3.6.3 | Board-Housing GND Distance and Sensitivity                         | . 83 |

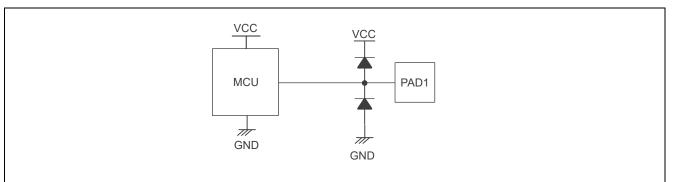

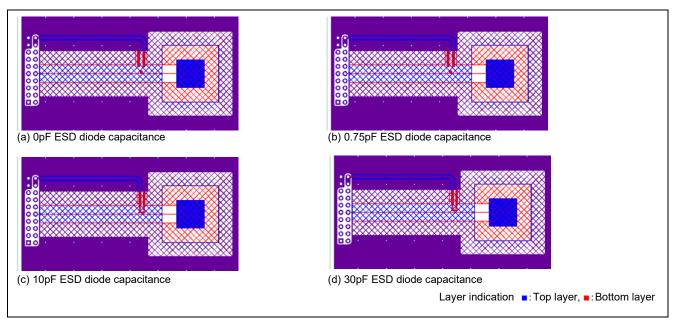

| 5.3.6.4 | Sensitivity Characteristics with ESD Protection Diode Connected    | . 84 |

| 5.3.6.5 | Supply Voltage and Sensitivity Characteristics                     | . 86 |

| 5.3.6.6 | Sensitivity at Wire Touch                                          | . 89 |

| Revisio | on History                                                         | .92  |

## 1. Outline

Capacitive touch button sensitivity and anti-noise performance are both influenced by the shape and size of the touch electrode pad (herein referred to as "electrode"), wire routing, patterns surrounding the electrode, overlay panel thickness, inclusion of air gap, internal configuration of product housing, and other factors. All of these factors need to be taken into consideration when designing the electrode as well as the surrounding area.

This application note describes how to design electrode pads and wiring as well as how to deal with related issues and potential problems when using the Renesas Touch Capacitance Sensor Unit (CTSU). It also provides recommended applications.

## 2. Self-capacitance Method Buttons: Electrode Layout Patterns

## 2.1 Outline of Design Recommendations

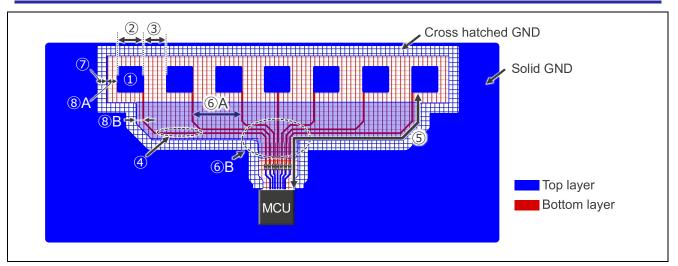

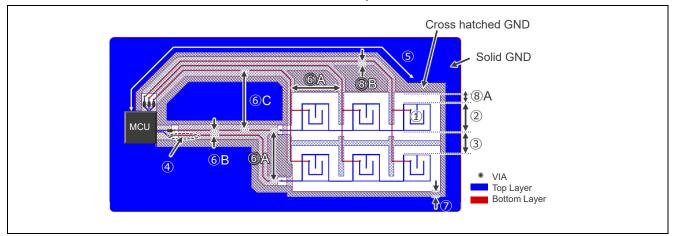

The following provides reference information for designing self-capacitance method buttons on a two-sided printed board We recommend using a 2- or more layer board and placing a shield guard of a cross-hatched GND pattern (referred to as "cross-hatched GND shield" herein) around the touch electrodes and on the area directly underneath the touch electrodes to suppress parasitic capacitance fluctuations due to the surrounding environment and noise factors as well as a measure to handle external noise. We also recommend using an ESD countermeasure by shielding the outer circumference of the board with a solid GND pattern. The numbers listed here correspond to the numbers in Figure2-1, excluding numbers (9) and (10). Each item is described in detail later.

- ① Electrode shape: square or circle

- ② Electrode size: 10mm to 15mm

- ③ Electrode proximity: Electrodes should be placed with ample distance so that they do not react simultaneously to the target human interface, (referred to as "finger" in this document); suggested interval: button size x 0.8 or more

- ④ Wire width: approx. 0.15mm to 0.20mm for printed board

- <sup>(5)</sup> Wiring length: Make the wiring as short as possible. On corners, form a 45-degree angle, not a right angle.

- 6 Wiring spacing:

- (A) Make spacing as wide as possible to prevent false detection by neighboring electrodes. (B) 1.27mm pitch

- ⑦ Cross-hatched GND pattern width: 5mm

- 8 Cross-hatched GND pattern and button/wiring spacing

- (A) area around electrodes: 5mm (B) area around wiring: 3mm or more

Cover the electrode area as well as the wiring and opposite surface with a cross-hatched pattern. Also place a cross-hatched pattern in the empty spaces, and connect the 2 surfaces of cross-hatched patterns through vias.

Refer to section "2.5 Anti-Noise Layout Pattern Designs" for cross-hatched pattern dimensions, active shield (CTSU2 only), and other anti-noise countermeasures.

- Electrode + wiring capacitance: See Table 2-1 and Table 2-2.

For other conditions, see 4.2 Base Clock Frequency/Sensor Drive Pulse Frequency Settings.

- (1) Electrode + wiring resistance:  $1k\Omega$  or less (including damping resistor with reference value of  $560\Omega$ ) Place the damping resistor as close as possible to the TS pin.

For additional noise countermeasures such as 7 Cross-hatched pattern dimensions and 8 Active shield (CTSU2 only), refer to 2.5 Anti-Noise Layout Pattern Designs.

For cautions when exceeding the recommended values of 9 and 10, refer to 2.4 Electrode Pattern Design.

Figure 2-1. Example of Anti-noise Layout Pattern for Self-capacitance Method Buttons

Table 2-1 lists the classification of products and types with capacitive Sensors. Table 2-2 lists the List of recommended values for capacitive sensor types and parasitic capacitance (unit: pF) of TS pins. Select the category from Table 2-1 from the device to be used and the CTSU operation mode, and design the pattern so that the parasitic capacitance is less than the recommended value according to the total resistance value of the TS pin from Table 2-2. The recommended parasitic capacitance includes the terminal capacitance of the overlay panel and the TS terminal. The recommended value is that the sensor drive pulse frequency is set to 1MHz or more by the automatic adjustment of QE for Capacitive Touch so that the sensitivity of the button can be obtained sufficiently. For TS pin conditions other than the recommended values that valid range and deprecated range, refer to "4.2 Base Clock Frequency/Sensor Drive Pulse Frequency Settings."

| Capacitance Sensor Type |      | CTSU1           |                     |               | CTSU2          |             |

|-------------------------|------|-----------------|---------------------|---------------|----------------|-------------|

|                         | RL78 | RL78/G16        | -                   | -             | RL78/G22, RL78 | /G23        |

| mily                    | RX   | RX113, RX130    |                     | RX671         | RX140          |             |

| Far                     |      | RX230, RX231, F | RX230, RX231, RX23W |               | RX260, RX261   |             |

| Product<br>Category/Fa  | RA   | RA2A1, RA4M1,   | RA2A1, RA4M1,       |               | RA2E1, RA2L1   |             |

| Pr                      |      | RA4W1           |                     | RA6M1, RA6M2, | RA4L1          |             |

| Cat                     |      |                 |                     | RA6M3, RA6M4, |                |             |

|                         |      |                 |                     | RA6M5         |                |             |

| CTSU Operating Mode     |      | Nomal           | Low voltage         | Nomal         | Nomal          | Low voltage |

|                         |      | Operation       |                     | Operation     | Operation      |             |

| Category (Note)         |      | A               | В                   | С             | D              | E           |

| Table 2-1 | Classification ( | of Products and  | Types with C    | apacitive Sensors  |

|-----------|------------------|------------------|-----------------|--------------------|

|           | Classification   | or i rouucis and | i i ypes with o | apacitive Selisors |

Note: The Category is specific to this application note.

# Table 2-2 List of Recommended Values for Capacitive Sensor Types and Parasitic Capacitance (Unit: pF) of TS Pins

| Category   |      | Α  | В  | С  | D  | E  |

|------------|------|----|----|----|----|----|

| Total      | 560  | 39 | 22 | 46 | 49 | 36 |

| Resistance | 620  | 38 | 21 | 44 | 46 | 35 |

| (Ω)        | 680  | 36 | 21 | 44 | 44 | 34 |

|            | 750  | 35 | 20 | 42 | 42 | 33 |

|            | 820  | 33 | 20 | 40 | 40 | 32 |

|            | 910  | 32 | 19 | 38 | 37 | 30 |

|            | 1000 | 30 | 19 | 36 | 35 | 29 |

#### 2.2 Self-capacitance Method Overview

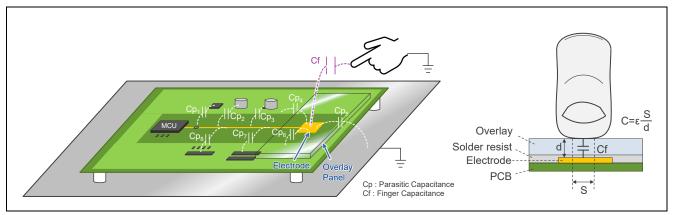

Figure2-2 shows the self-capacitance generated in the electrode. A single electrode connected to the capacitive sensor in the self-capacitance method button measures capacitance C. The value of C is a composite of parasitic capacitance Cp formed by the electrode and surrounding conductors and parasitic capacitance Cf formed by the electrode and the finger. The size of the capacitance can be considered in the capacitor equation  $C = \varepsilon \frac{s}{d}$  (see note). Cp is constant as the surrounding devices are static, but Cf increases as the finger gets closer. By setting a threshold for the amount of increase in Cf, you can determine whether the touch button is ON or OFF. Note that if the finger actually touches the electrode, it will short and no longer be able to measure capacitance. Normally, there is an overlay panel of a few mm between the electrode and the finger.

Note) C: capacitance,  $\epsilon$ : Relative permittivity, S: electrode facing area, d: inter-electrode distance

Figure2-2. Image of Self-capacitance Generated in the Electrode

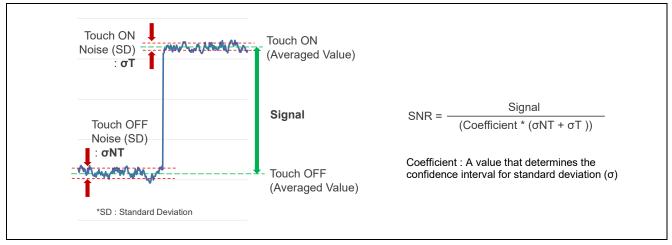

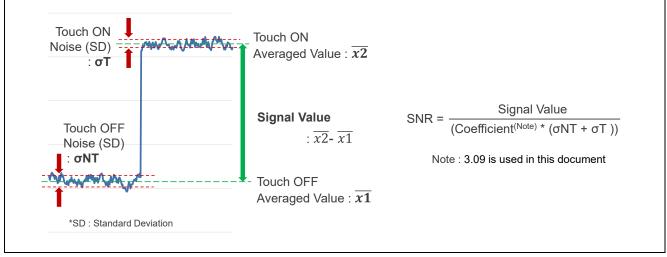

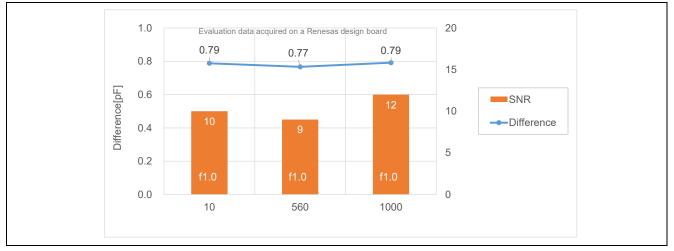

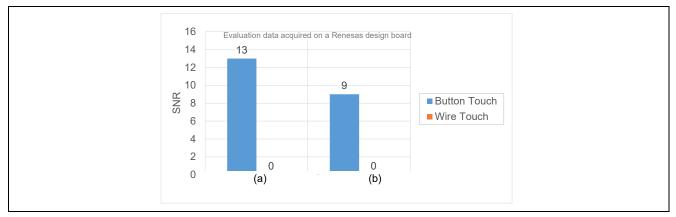

The sensitivity of the touch button is defined by SNR (Signal-to-Noise-Ratio). Figure2-3 shows Button Sensitivity (SNR) Derivation Method. SNR is calculated by taking the difference in measurement values between the touch button ON and OFF (touch/non-touch) states as the signal value, and calculating its ratio to the noise value. Noise can originate from within the MCU or it can be received externally by patterns on the board. A higher SNR results in higher touch button sensitivity. This formula shows a Coefficient as part of the calculation. Recommend referencing Figure 5-1 for the for the value and section 5.1 for the calculation examples.

Figure2-3. Button Sensitivity (SNR) Derivation Method

## 2.3 Principle of CTSU Self-capacitance Method Detection

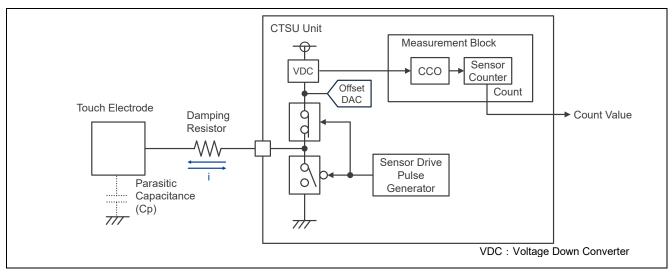

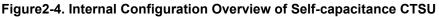

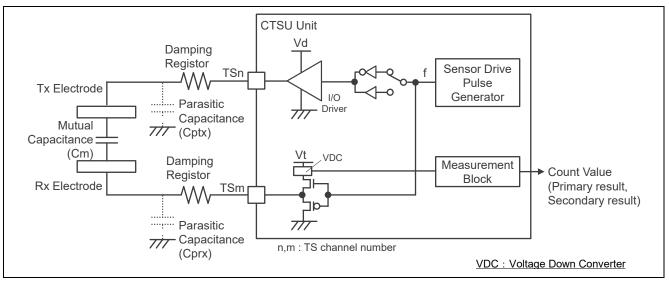

Figure2-4 shows an overview of the CTSU internal configuration for the self-capacitance method. The CTSU outputs a digital count value proportional to capacitance C of the connected electrode, and determines whether the touch button is ON or OFF by software. When the electrode is connected to the CTSU, it

performs as a switched capacitor controlled by the sensor drive pulse frequency and estimates capacitance from the charge/discharge current to C. The CTSU measurement block has a current-frequency conversion function which inputs a current equivalent to the charge/discharge current and outputs a frequency signal proportional to the amount of current. The frequency signal is measured for a fixed period according to the sensor drive pulse output. It is stored in the sensor counter register. For details on the detection principle, refer to the application note "Capacitive Sensor Microcontrollers CTSU Capacitive Touch Introduction Guide."

Figure2-5 shows an image of CTSU measurement. When one cycle of the sensor drive pulse frequency is shorter than the C charge/discharge time and the charge/discharge is insufficient, not enough current flows to C and the count value is smaller than the ideal value. In this situation, you can lengthen the charge/discharge time of 1 cycle by lowering the sensor drive pulse frequency; this will result in sufficient charge/discharge even for hardware with large parasitic capacitance. However, when lowering the sensor drive pulse frequency, the charge/discharge count (number of measurements) per unit time also decreases, resulting in a smaller measurement value.

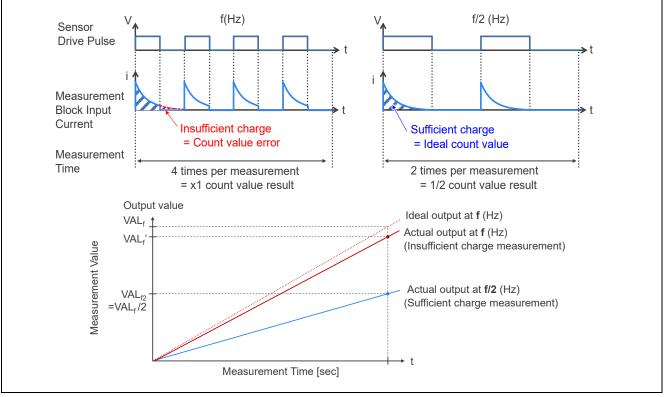

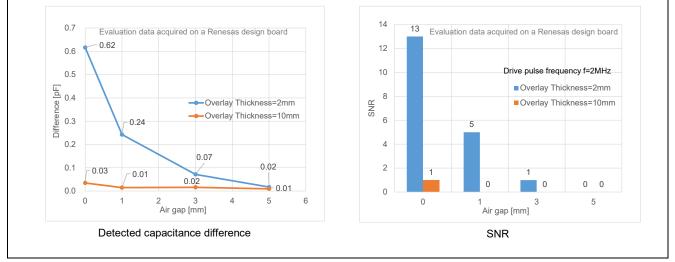

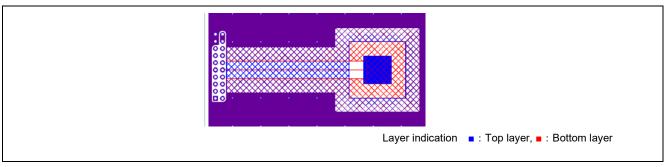

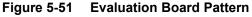

Figure2-6 shows the relationship of sensor drive pulse frequency and sensitivity. Figure2-6 (a) shows the measured difference between touch ON and OFF for each sensor drive pulse frequency, which is proportional to the sensor drive pulse frequency. In the same manner as the detected capacitance at touch (Signal Value [pF]) shown in Figure2-6 (b), when the measured value is converted to a capacitance value, it remains constant regardless of sensor drive pulse frequency. On the other hand, the SNR improves in proportion to the sensor drive pulse frequency. The lower the sensor drive pulse frequency, the higher the amount of noise per count, and the SNR tends to decrease. Accordingly, to achieve highly sensitive buttons, set the parasitic capacitance of the electrode circuit to low in the hardware design stage, allowing selection of a high sensor drive pulse frequency.

Figure2-6. Relationship of Sensor Drive Pulse Frequency and Sensitivity

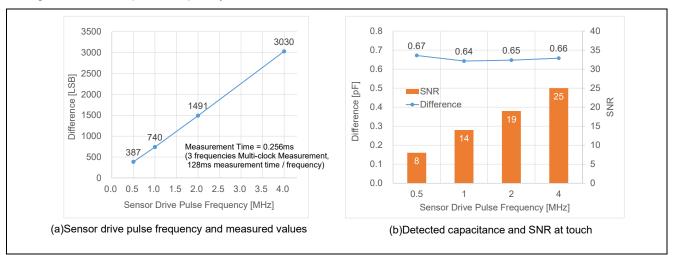

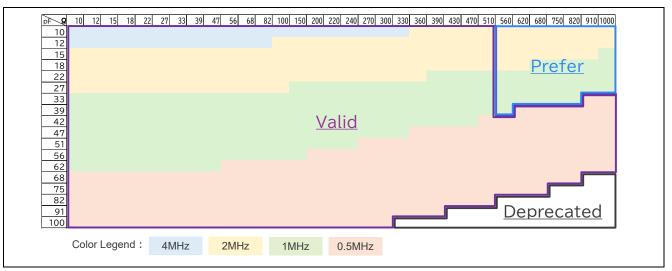

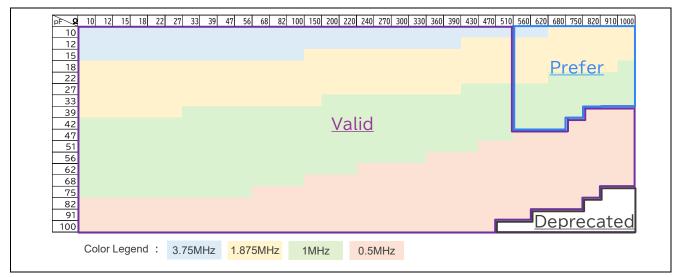

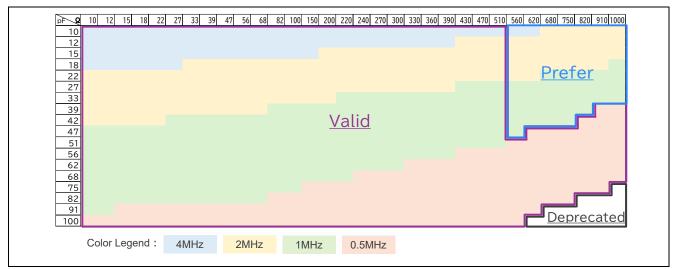

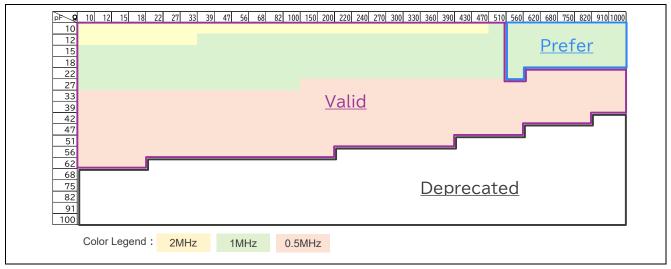

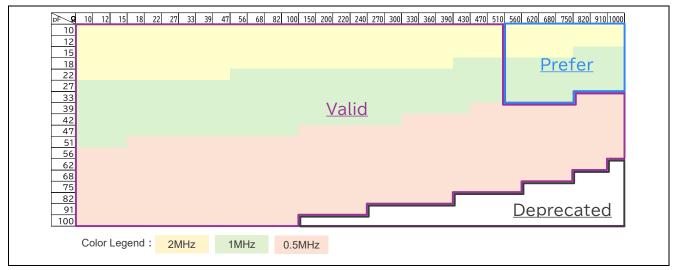

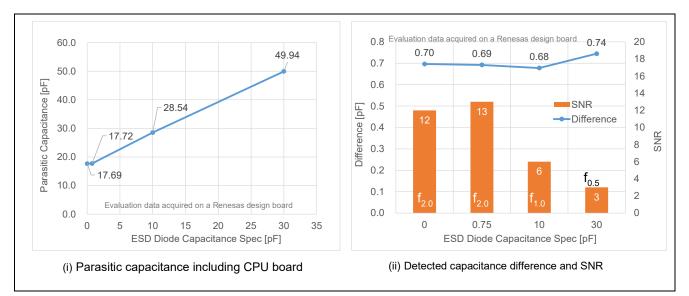

The sensor drive pulse frequency of the CTSU affects both the capacitance measurement range as well as the SNR. Figure2-7 shows a . Setting Example for Parasitic Capacitance and Sensor Drive Pulse Frequency. The conditions for this example are as follows: the MCU is RA2L1, supply voltage (VCC) is 5.0V, and damping resistance value is R=560  $\Omega$ . Damping resistance value of 560 $\Omega$  is recommended to protect the pins from external noise and limit the output current from pins. The QE for Capacitive Touch auto-tuning function selects the sensor drive pulse frequency from 4.0, 2.0, 1.0, and 0.5 MHz. The setting values differ according to the MCU and hardware design used.

For self-capacitance method button applications, when using RA2L1, the recommended range of parasitic capacitance for button electrodes, including the overlay panel and MCU pins, is up to 49pF.-The recommended range is that the sensor drive pulse frequency is set to 1MHz or more by the automatic adjustment of QE for Capacitive Touch so that the sensitivity of the button can be obtained sufficiently. For TS pin conditions other than the recommended values that valid range and deprecated range, refer to "4.2 Base Clock Frequency/Sensor Drive Pulse Frequency Settings." If the range exceeds the recommended range, the drive pulse frequency will be lower, which may result in insufficient SNR.

Figure2-7. Setting Example for Parasitic Capacitance and Sensor Drive Pulse Frequency

Capacitive Sensor Microcontrollers

If the parasitic capacitance cannot be reduced due to hardware restrictions, causing the sensor drive pulse frequency to be low and the sensitivity insufficient, the sensitivity can be enhanced by increasing the measurement count/measurement time in the advanced mode settings of QE for Capacitive Touch. However, this may cause an increase in the time required to complete the measurement or an overflow of the measurement value. For details regarding how to adjust the measurement count/measurement time, see <u>Capacitive Sensor MCU QE for Capacitive Touch Advanced Mode Parameter Guide</u>.

## 2.4 Electrode Pattern Design

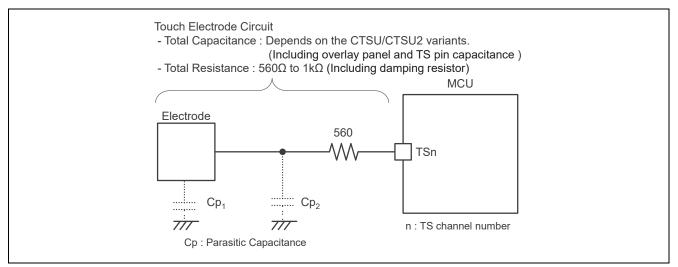

#### 2.4.1 Electrode circuit configuration

Figure2-8 shows a self-capacitance electrode circuit. The configuration of the touch electrode circuit that connects to the TS pin comprises the touch electrode, electrode wiring, and damping resistor. The touch electrodes and wiring are created using patterns on the printed circuit board. The reference value of the damping resistor is  $560\Omega$ . Place the damping resistor as close as possible to the TS pin to prevent noise mixing in from the wiring between the TS pin and the resistor.

When designing a self-capacitive touch electrode circuit, design the pattern and select the materials so that the following recommended conditions are met.

① Parasitic capacity C: See Table 2-1 and Table 2-2.

② Resistance value R: 560 $\Omega$  to 1k $\Omega$  (including damping resistor)

Keep in mind that the electrostatic capacitance C of the entire electrode circuit also includes parasitic capacitance with objects around the board, such as the board's GND pattern, the overlay panel, and the body chassis. By keeping C low in the design, the touch ON/OFF measurement value difference (signal value) will increase, and the SNR will improve when selecting a high frequency for the CTSU sensor drive pulse frequency. The total capacitance for each TS pin can be confirmed using QE for Capacitive Touch.

Figure 2-8. Self-capacitance Method Electrode Circuit

#### 2.4.2 Electrode pads and wiring

The following offers recommended shapes for button electrodes and wiring conditions.

- Shape: square or circular plane patterns

- Size: 10 x 10 to 15 x 15mm

- Electrode interval: To avoid crosstalk<sup>(Note)</sup>, use an interval wide enough to prevent simultaneous response by adjacent electrodes based on finger or other touch interface Target interval size: electrode button size x 0.8 or more

- harget interval size, electrode button size x 0.6 of more

- Interval between electrode and GND pattern: 5mm or more

- Do not place wiring or a pattern for another function, or a GND plane pattern, directly under an electrode. Noise emitted from wiring directly under the electrode can cause the electrode potential to fluctuate, which can affect the CTSU measurement value. A solid GND pattern tends to increase parasitic capacitance, which may exceed the measurement range of the CTSU. When a GND pattern is necessary as an anti-noise countermeasure, place a cross-hatched GND pattern.

Note: Crosstalk refers to capacitive coupling between adjacent electrodes or capacitive coupling between a finger and adjacent electrodes when the target electrode is touched. For more details, see section "2.6 Effect of Panel Thickness."

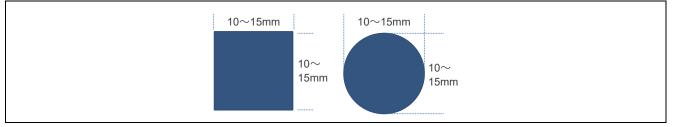

Figure2-9 shows the recommended electrode shapes and size. Shapes and sizes are fairly flexible and can be determined based on the button design of the panel on the final product. Make sure that the size is not extremely large or extremely small with respect to the part of the human body (finger, etc.) that will be operating the product. If the size is extremely large the parasitic capacitance will increase, requiring a lower CTSU sensor drive pulse frequency setting which may in turn reduce button sensitivity. If the size is extremely small, the contact area between the finger and the electrode pad will be limited, which will reduce the change in capacitance and may prevent touch detection. If the pad is square, round the corners of the electrode with a radius of 0.5 to 1.0 mm to reduce the effects of noise.

Figure 2-9. Recommended Electrode Shapes and Size

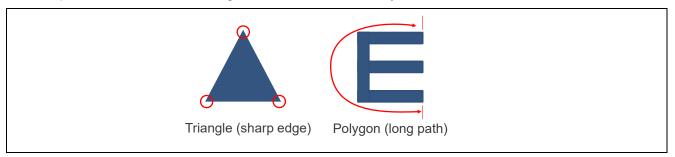

Figure2-10 shows shapes that are not recommended for electrodes—triangles with angles of 90 degrees or less and E-shapes with narrow line width and long total length. These shapes are not recommended as they tend to perform as antennas and degrade the RF noise immunity.

Figure2-10. Unsuitable Electrode Shapes

## 2.4.3 Wiring

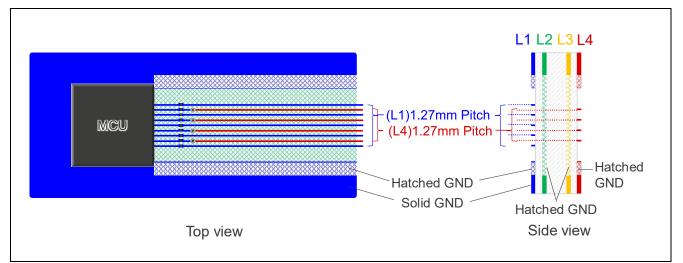

Recommended layout and dimensions of wiring are listed below.

- Wiring width: 0.15mm (the thinnest wire achievable through mass production)

- Wiring spacing: 1.27mm pitch However, leave at least 5mm, more if possible, around the electrode pad circumference (about twice the length of the electrode pad)

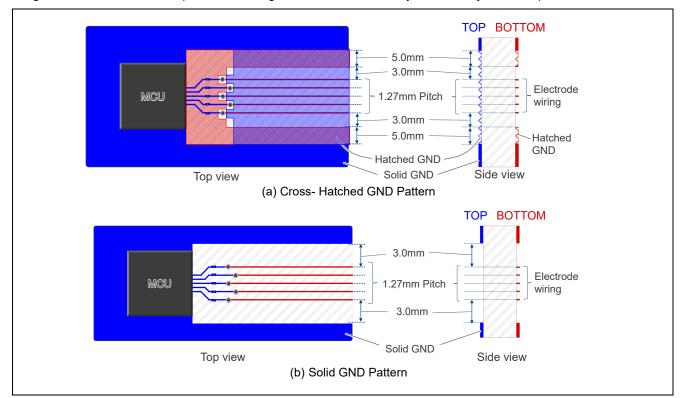

- Cross-hatched GND pattern width: 5mm

- Wiring and cross-hatched GND pattern spacing: 3.0mm

- Wiring and GND pattern spacing: 3mm or more (when not using a cross-hatched GND shield)

Make sure the design satisfies the following wiring requirements as well.

- Keep the wiring as short as possible, as parasitic capacitance increases in proportion to the wiring length. In addition, The longer the wiring length, the more susceptible it is to external noise. Keep this in mind when planning to use the device in environments with RF frequency noise.

- Try to have as few corners in the wiring as possible; make corners 45 degrees or rounded. This reduces noise radiated from the wiring.

- Drill vias at the edge of the electrode pad and layout wiring on the back side. This helps reduce malfunctions when wires are touched. However, keep the number of vias at a minimum as they tend to increase parasitic capacitance.

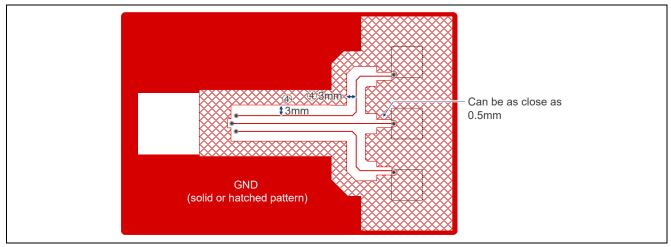

- As an anti-noise countermeasure, place a cross-hatched GND pattern directly under (the back layer of wiring) the electrode and wiring.

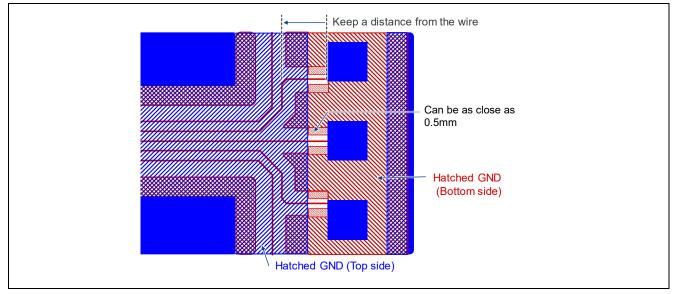

- The wire routing extending from the electrode is vulnerable to noise as there is no cross-hatched GND pattern directly under the wiring. Bring the cross-hatched GND as close as 0.5mm to this part.

- Do not place wiring other than that used for the touch function directly under the electrode wiring. If you must do so, make the wiring orthogonal and minimize the facing area. This reduces the effects of noise caused by capacitive coupling between wires.

The wiring part of the electrode has a small parasitic capacitance and is easily affected by external noise. Noise immunity can be improved by suitably arranging the GND shield. In addition, since the nonmeasurement TS pins of the CTSU are fixed to the GND level, the wiring connected to the TS pins also functions as a shield<sup>(Note)</sup>. the GND shield to the wiring and the shorter the distance between the wiring of each TS pin, the greater the parasitic capacitance of the TS pins, the greater the parasitic capacitance of the TS pins. Therefore, adjust the GND shield placement and wiring spacing so that total parasitic capacitance conditions are satisfied.

Note: Applies if you are using the CTSU or if the Active Shield function of the CTSU2 is disabled.

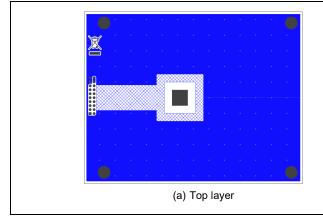

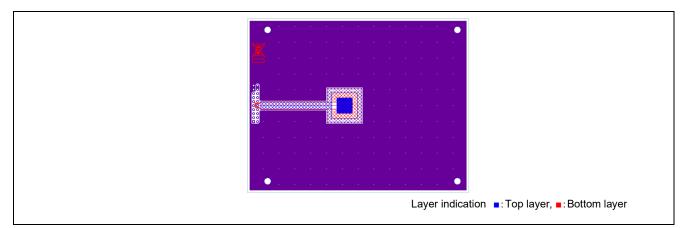

Figure 2-11 shows an example of the wiring section of a double-layer board layout example.

Figure2-11. Double-Layer Board Layout Example (wiring section)

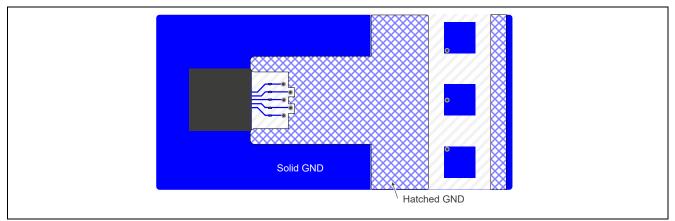

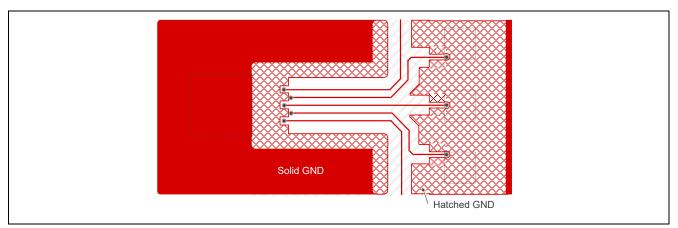

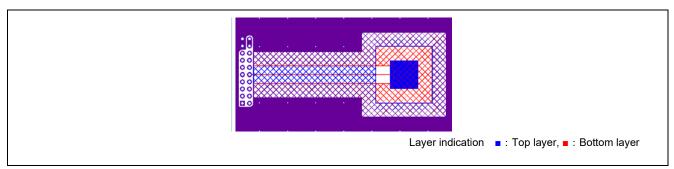

Figure 2-12 shows an example of the electrode section of a double-layer board layout.

Figure2-12. Double-Layer Board Layout Example (electrode section)

Figure 2-13 and Figure 2-14 show layout examples for each layer.

Figure 2-13. Top Layer Layout Example

Figure2-14. Bottom Layer Layout Example

Figure2-15 shows an example of high-density wiring. When you have limited board size and need to increase the wiring density, shift the wiring by a half pitch and lay out the wiring on both sides of the board. For 4-layer boards, make sure to place a cross-hatched GND on the inner layers.

Figure2-15. High-density Wiring

## 2.5 Anti-Noise Layout Pattern Designs

The electrode circuit configuration allows the circuit to act as an antenna (the MCU pin is open only for capacitive coupling) and makes it vulnerable to electromagnetic field noise. Renesas Touch MCUs employ several anti-noise countermeasures to ensure high noise immunity. However, an MCU alone cannot prevent influence from all noise. Hardware countermeasures are indispensable when using the MCU in a severe noise environment. The following are a few examples of how to protect the system from external noise.

In general, the longer the wiring length, the more susceptible it is to external noise. Make sure the wiring between button electrodes and the touch MCU is kept as short as possible.

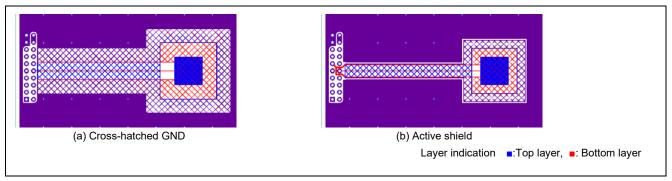

The CTSU2-embedded MCU is equipped with an active shield function that drives a shield at the same potential and in the same phase as the touch electrode circuit. In this section, the shield at the GND level is described as a "GND shield" to distinguish it from an active shield.

For details regarding anti-noise measurements for the IEC61000 series, see <u>Capacitive Sensor MCU</u> <u>Capacitive Touch Noise Immunity Guide</u>.

## 2.5.1 Shield pattern

## 2.5.1.1 Shield design

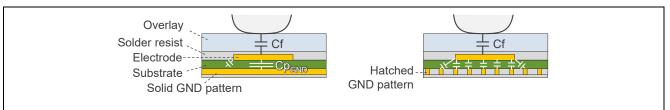

To prevent touch button malfunctions caused by external noise, place a GND level shield around the touch button and wiring. Placing a GND shield around the touch electrode circuit releases external noise to GND from the path created by the capacitive coupling, stabilizing the potential of the touch electrode circuit and reducing the effect of noise appearing in the CTSU measurement value. We recommend a hatched-pattern shield to reduce the increase in parasitic capacitance of the electrode pattern. Figure2-16 shows an image of GND patterns and parasitic capacitance. When using a printed board, place a GND plane pattern directly under the wiring pattern as a general anti-noise countermeasure. In the self-capacitance button, the parasitic capacitance Cp<sub>GND</sub> generated by the electrode and GND plane pattern is much larger than Cf and exceeds the measurement range of the CTSU. So, when designing the self-capacitance button, do not place a GND plane pattern directly under the electrode. If an anti-noise countermeasure is needed, use a cross-hatched GND pattern to reduce the increase in parasitic capacitance.

Figure2-16. Image of GND Pattern and Parasitic Capacitance

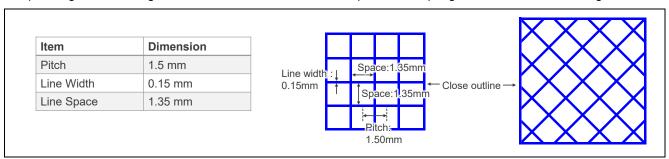

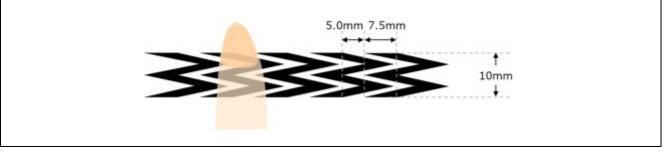

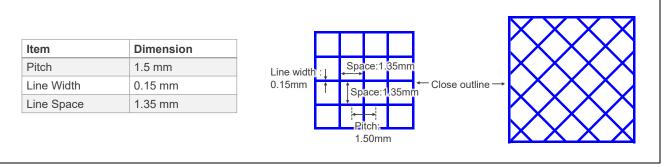

Figure 2-17 shows the cross-hatched pattern dimensions. Shielding the electrode and electrode wiring serves as an effective EMC noise countermeasure. A shield guard can be placed directly under the electrode or electrode wiring on a multi-layer board but the GND plane pattern has a large coupling capacity which will prevent the electrode from detecting capacitance fluctuation when touched. Therefore, a cross-hatched pattern shield-should be used. Reducing the pitch and wiring spacing from the recommended dimensions will improve noise immunity but keep in mind that the parasitic capacitance of the electrode circuit will increase as the GND pattern ratio per unit area increases. In addition, the cross-hatched pattern is tilted 45 degrees depending on the wiring direction in order to reduce the capacitive coupling with the electrode wiring.

Figure 2-17. Cross-hatched Pattern Dimensions

## 2.5.1.2 GND shield

The GND shield is a noise countermeasure that can be achieved with the board pattern, and the GND shield should generally be located as close as possible to the digital signal line. When designing a capacitive touch button, the closer the GND shield is to the touch electrode circuit, the higher the parasitic capacitance. In this case, it is necessary to set the sensor drive pulse frequency of the CTSU to a lower value, which reduces the sensitivity of the button. Also, in board designs with long wiring, the longer the parallel run distance between the electrode circuit wiring and the GND shield, the higher the parasitic capacitance. Careful consideration is required for placement spacing throughout the entire pattern.

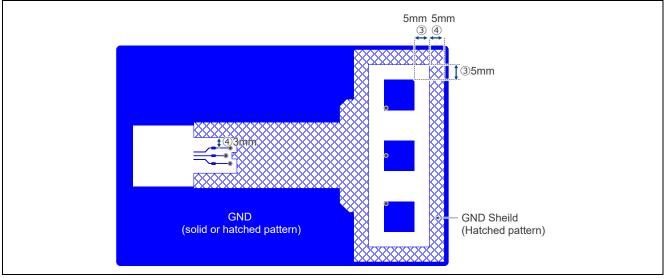

The following are recommended shape and wiring conditions for the top layer. These recommendations assume the electrode pads are placed on the top layer.

- ① Board layer configuration: 2 or more layers to block external noise

- 2 Pattern shape: cross-hatched pattern

- See 2.5.1.1 Shield design for dimensions.

- 3 Distance between touch electrode and cross-hatched GND shield: 5mm

- ④ Distance between touch electrode wiring and cross-hatched GND shield: 3mm

- 5 Width of cross-hatched GND shield: 5mm or more

- Make sure to connect the cross-hatched GND pattern and GND plane.

Cover the area directly under the electrode and wiring with the cross-hatched GND pattern.

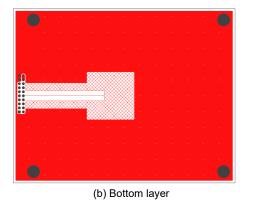

Figure 2-18 and Figure 2-19 show an example of a GND shield pattern for a multi-layer board.

Figure 2-18. GND Shield Pattern Example for Multi-layer Board (top layer)

Figure2-19. GND Shield Pattern Example for Multi-layer Board (bottom layer)

## 2.5.1.3 Active shield (CTSU2 function)

This function is provided for MCUs embedded with CTSU2.

The active shield function drives the shield with signals of the same potential and phase as the electrodes. Using the active shield will reduce capacitance coupling between the electrode and shield guard as well reduce noise interference. This is mainly used to improve the water resistance of touch buttons.

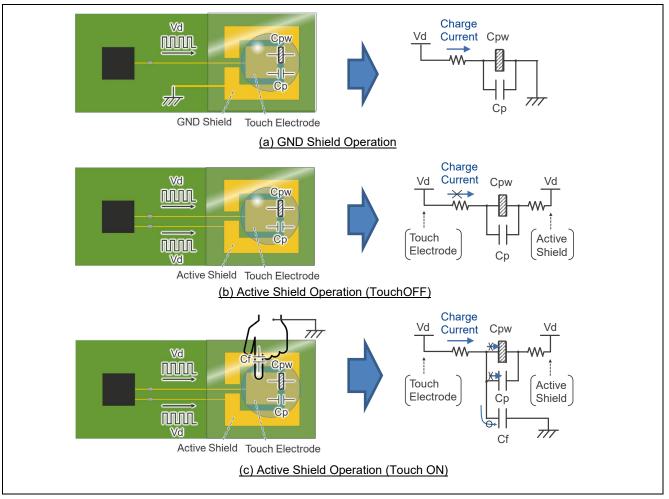

Figure2-20 shows an image of how an active shield reduces the effects of parasitic capacitance. The figure shows a water droplet adheres to the overlay panel during touch measurement, forming a conductive bridge between the touch electrode and the shield pattern. Parasitic capacitance Cp occurs between the touch electrode and the shield pattern. Parasitic capacitance Cp occurs between the touch electrode and the shield pattern adheres to it, a new parasitic capacitance indicated by Cpw occurs. The relative dielectric constant of water is 80 times that of air, so if Cp is 1pF, a simple calculation gives a parasitic capacitance of Cpw as 80pF. When the touch button is pressed with a finger, the change in capacitance is approximately 1pF, depending on the hardware conditions.

In the figure, (a) shows an example using a GND shield. During touch measurement, the potential difference between the touch electrode and the shield is the sensor drive pulse voltage Vd, and Cp and Cpw are charged. Since the charging current of Cpw is also added to the CTSU measurement value, the value may exceed the touch threshold and falsely detect touch ON.

Example (b) shows use of an active shield. Since the same voltage Vd as the touch electrode is applied to the active shield, both ends of Cp and Cpw are at the same potential and are not charged. Therefore, the CTSU measurement value does not change from the state where a drop of water is adhered to the electrode, and the touch OFF state is continually detected.

Example (c) shows the touch button pressed under the same conditions as in (b). However, since the finger is connected to GND, its parasitic capacitance Cf causes a potential difference on the touch electrode, resulting in it being charged. As Cp and Cpw are not charged, the CTSU detects only the change in Cf, enabling touch detection (touch ON) even when water is adhered to the button

Figure2-20. Image of How an Active Shield Reduces the Effects of Parasitic Capacitance

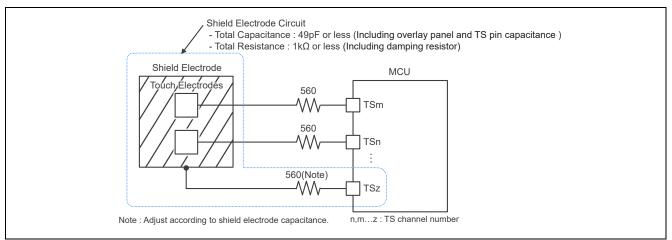

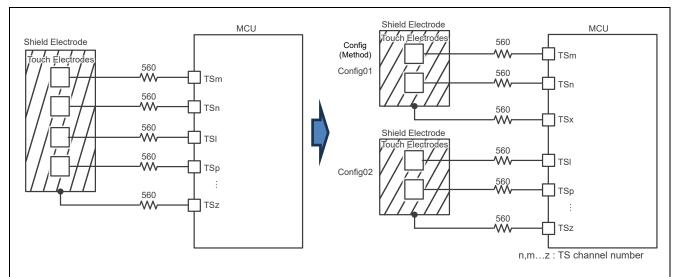

Figure2-21 shows an example of a shield electrode circuit. The active shield is connected to the TS pin, in the same manner as a touch electrode. Since one shield pin can be combined with multiple TS pins of button electrodes, design the shield pattern by grouping the button electrodes that you want to apply the active shield.

The active shield is driven by the sensor drive pulse in the same way as the touch electrode. When designing the circuit, be aware that a significant difference between the parasitic capacitance of the shield pattern and that of the touch electrode can cause a phase shift in the sensor drive pulse, reducing its effectiveness. We recommend keeping the total parasitic capacitance of the TS pin connecting the shield pattern at 49pF or less. As the number of button electrodes increases, the area of the shield pattern will increase, as will the parasitic capacitance. The shield pattern should be designed as a cross-hatched pattern to suppress parasitic capacitance. See 2.5.1.1 Shield design for recommended cross-hatched dimensions.

Figure2-21. Shield Electrode Circuit

If the circuit hosts many button electrodes and the parasitic capacitance per shield pattern is large, the parasitic capacitance can be reduced by dividing the button electrodes and active shields into groups. Note that when grouping electrodes and shields, the groups that are not being measured are fixed to low output. Therefore, if the measurement group and the non-measurement group are close to each other, parasitic capacitance charging/discharging may occur between electrode groups, which may affect the measurement value. In particular, false reactions can be caused by water adherence, so when considering water resistance and usage environments, be sure to separate electrode groups far enough apart so they will not be bridged by water.

Figure 2-22. Example of Deviding of Shielded Electrode Circuits

QE for Capacitive Touch supports up to 8 groupings (configuration (method)). For details on the configuration (method), refer to the help file of QE for Capacitive Touch. As a guideline, grouping should be 4 buttons or less per active shield pin (assuming the active shield pin damping resistance is  $560 \Omega$  and the button size is 10 mm square). For more than 4 buttons, consider dividing the grouping again to avoid exceeding 49pF. Refer to section 5.3.5.1 Active Shield Area for reference values of parasitic capacitance changes due to number of buttons and active shield area.

Table 2-3shows the recommended designs for active shield electrodes. The items listed below assume the electrode pads are placed on the TOP layer. For design items not listed in the table, refer to section 2.1 Outline of Design Recommendations.

| No         | Design Parameter                                                | Recommended Value                                                   | Cautions                                                                                                                                                                                                         |

|------------|-----------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | Board layer                                                     | 2 layers                                                            | To prevent noise, cover the area directly below electrodes and wiring with active shield electrodes                                                                                                              |

|            |                                                                 |                                                                     | Single-sided boards offer less noise immunity                                                                                                                                                                    |

|            |                                                                 |                                                                     | because shields cannot be placed directly under electrodes.                                                                                                                                                      |

|            |                                                                 |                                                                     | When using 3 or more layers: See Note 1                                                                                                                                                                          |

| -          | Space around touch electro                                      | odes                                                                |                                                                                                                                                                                                                  |

| 2          | Pattern shape                                                   | Cross-hatched pattern                                               | For dimensions, see 2.5.1.1 Shield design                                                                                                                                                                        |

|            |                                                                 |                                                                     | For solid pattern: Note 2                                                                                                                                                                                        |

| 3          | Pattern width                                                   | 3.0mm                                                               | For wider width: Note 2                                                                                                                                                                                          |

|            |                                                                 |                                                                     | For narrower width: Note 3                                                                                                                                                                                       |

| 4          | Interval between touch                                          | 3.0mm                                                               | For wider interval: Note 3                                                                                                                                                                                       |

|            | electrode pads                                                  |                                                                     | For narrower interval: Note 2                                                                                                                                                                                    |

| 5          | Spacing between shield                                          | 3.0mm                                                               | For wider spacing: Note 3                                                                                                                                                                                        |

|            | pattern and solid GND                                           |                                                                     | For narrower spacing: Note 2                                                                                                                                                                                     |

| -          | Space around wiring                                             |                                                                     |                                                                                                                                                                                                                  |

| 6          | Pattern width                                                   | 0.5mm                                                               | Use 0.5mm wiring                                                                                                                                                                                                 |

|            | (shield pattern adjacent to                                     |                                                                     | For wider width: Note 2                                                                                                                                                                                          |

|            | touch electrode wiring)                                         |                                                                     | For narrower width: Note 3                                                                                                                                                                                       |

| $\bigcirc$ | Touch electrode wiring                                          | 1.27mm                                                              | For wider interval: Note 3                                                                                                                                                                                       |

|            | spacing                                                         |                                                                     | For narrower interval: Note 2                                                                                                                                                                                    |

| 8          | Touch electrode wiring<br>spacing (near touch<br>electrode pad) | 0.3mm                                                               | Use this to improve shielding in the gap between<br>the electrode pad and the shield pattern. If the<br>distance is about the width of the shield pattern,<br>the effect on parasitic capacitance is negligible. |

|            |                                                                 |                                                                     | If the distance between narrow spacing is long:<br>Note 2                                                                                                                                                        |

| -          | Common parameters                                               |                                                                     |                                                                                                                                                                                                                  |

| 9          | Spacing between shield                                          | 3.0mm                                                               | For wider spacing: Note 3                                                                                                                                                                                        |

|            | pattern and solid GND                                           |                                                                     | For narrower spacing: Note 2                                                                                                                                                                                     |

| 10         | Total capacitance                                               | 50pF or less (including<br>overlay panel and TS pin<br>capacitance) | If parasitic capacitance or total resistance exceeds<br>recommended values, see section 4.2 Base Clock<br>Frequency/Sensor Drive Pulse Frequency                                                                 |

| 1          | Total resistance                                                | 1k $\Omega$ or less (including damping resistor)                    | Settings and consider changing the design<br>settings so that the both values satisfy the<br>measurable sensor drive pulse frequency.                                                                            |

Note 1: Place the shield pattern on the top and bottom layers and do not place other patterns on the inner layers.

Note 2: Parasitic capacitance may increase, potentially breaching the CTSU sensor drive pulse lower limit. Note 3: This may cause a decrease in noise immunity.

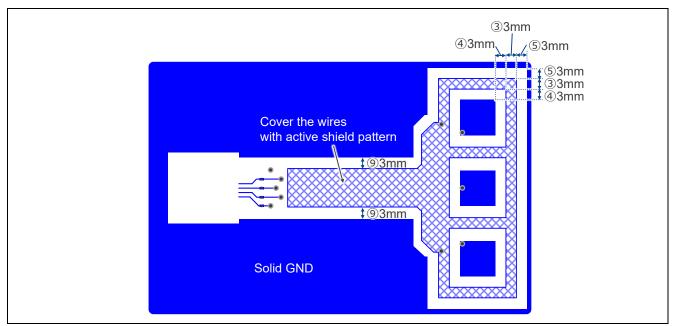

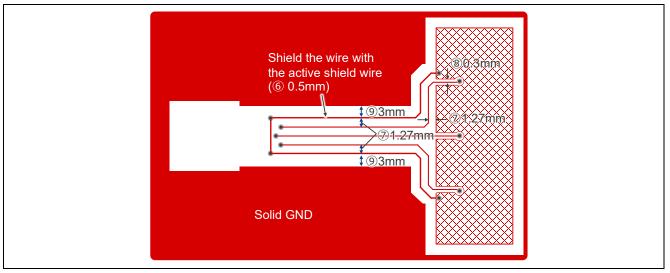

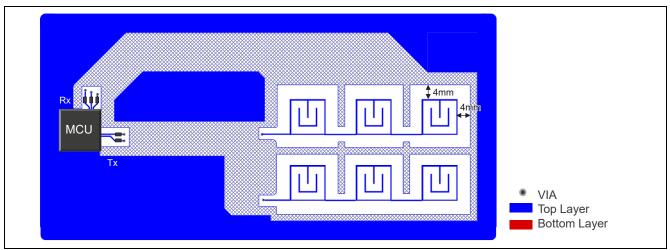

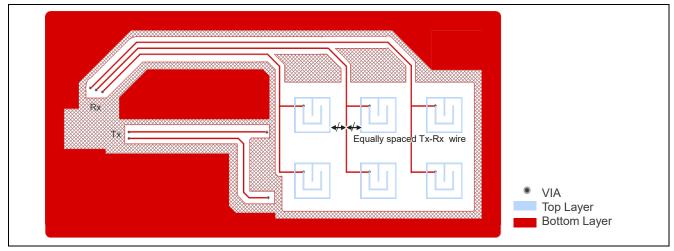

Figure2-23 and Figure2-24 show an example of the active shield pattern for multiple-layer boards. For board configurations with more than two layers, do not place other patterns on the inner layers within area 6 as the CTSU measurement values may be affected by noise.

Figure2-23. Example of Active Shield Pattern for Multiple-Layer Board (top layer)

Figure2-24. Example of Active Shield Pattern for Multiple-Layer Board (bottom layer)

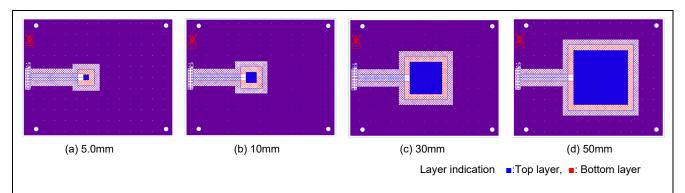

## 2.6 Effect of Panel Thickness

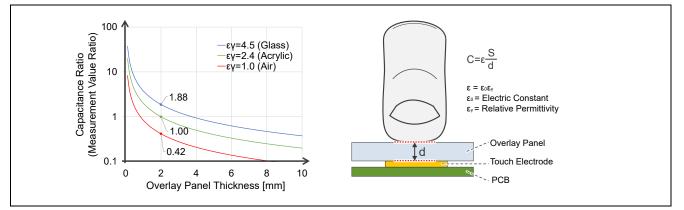

The self-capacitance method detects the capacitance generated when there is contact between the human body and a button electrode, where the relationship of capacitance is  $C = \varepsilon \frac{s}{d}$ . In touch detection using the self-capacitance method, the capacitance of the parallel plate capacitor formed between the human body and the button electrode is detected, based on the relationship of capacitance C= $\varepsilon$  S/d. Therefore, the larger the area (S) of the button electrode and part of the human body facing each other, and the smaller the distance (d) between them, the greater the capacitance when the panel is touched. This increase in capacitance enhances the sensitivity of touch ON-OFF detection.As the maximum touch surface size of the button electrode is limited (10mm to 15mm), the distance, or panel thickness, is the key factor in adjusting sensitivity.

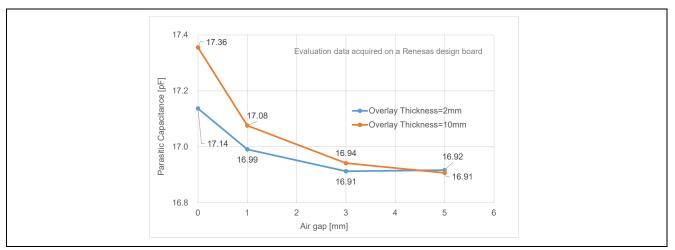

#### 2.6.1 Relationship of panel thickness and touch sensitivity

Figure 2-25 shows the relationship of the amount of capacitance change and sensitivity distance in the selfcapacitance method. This diagram uses an overlay panel with a dielectric constant of 2.4 (acrylic), and the capacitance is standardized to 1.00 when touching an overlay panel with a thickness of 2.0 mm. This shows that, if the sizes of the finger and button electrode are constant, the thinner the overlay panel, the greater the capacitance when touched. Since the CTSU has an upper limit (measurement range) for capacitance measurement, there is a limit to how thin the overlay panel can be. Renesas assumes the use of an overlay panel with a thickness of 2 to 3 mm. If a material with a relative dielectric constant of 4.5 (glass) is used as the overlay panel material, the capacitance increases by 1.88 times even at the same thickness, and if the relative dielectric constant is 1.0 (air), the capacitance decreases to 0.42 times. The capacitance at touch also increases or decreases depending on the dielectric constant of the panel material. Note that, even with the same distance (panel thickness), materials with a high dielectric constant may exceed the CTSU measurement range. To use a material with a high dielectric constant for the overlay panel, you can avoid exceeding the CTSU measurement range by reducing the material thickness or by intentionally inserting an air gap or spacer with a low dielectric constant between the overlay panel and the touch electrode pattern, which will lower the composite value of the dielectric constant. To increase the sensitivity of the touch buttons, try using a material with a higher dielectric constant, or fix the overlay panel and touch electrode pattern with double-sided tape or resin to eliminate the air gap.

In this method, the capacitance increases or decreases depending on the distance between the finger and the electrode, allowing touch detection over a broad range (distance) by adjusting the touch threshold. However, if the touch threshold is set too low compared to the capacitance change, touch detection may occur before the finger actually has contact with the panel.

Figure2-25. Relationship of Capacitance Change and Sensitivity Distance

| Dielectric Material | Dielectric constant ε |  |

|---------------------|-----------------------|--|

| Acrylic             | 2.4-4.5               |  |

| Glass               | 4.5-7.5               |  |

| Nylon Plastic       | 3.0-5.0               |  |

| Flexible Vinyl Film | 3.2                   |  |

| Air                 | 1.0                   |  |

| Water               | 80                    |  |

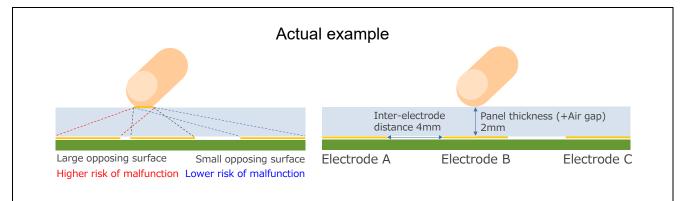

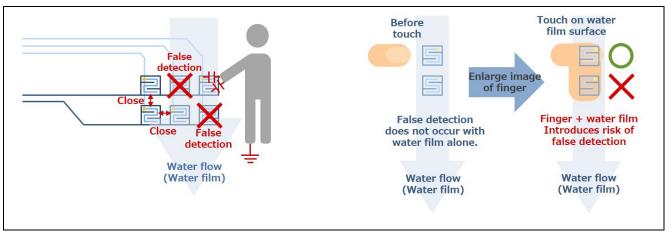

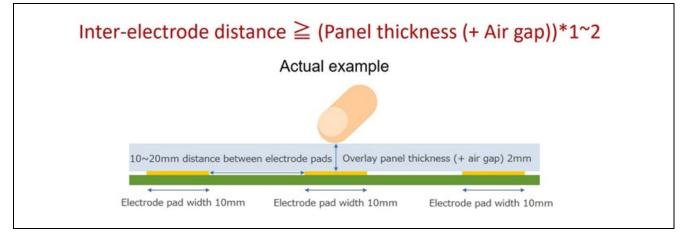

#### 2.6.2 Relationship of panel thickness and crosstalk

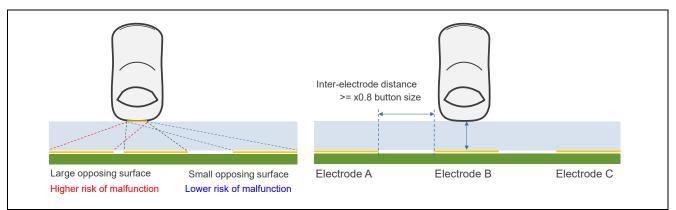

Figure2-26 shows the relationship of the inter-electrode distance and panel thickness in the self-capacitance method. If the button electrodes are placed too close together, they may cause neighboring button electrodes to turn ON erroneously (left side of figure). To prevent false detections (crosstalk), among neighboring button electrodes by changing the overlay panel thickness from 2 to 3mm, the recommended distance between button electrodes is 0.8 times wider than the button size.

# Figure2-26. Relationship of Inter-electrode Distance and Overlay Panel Thickness for Self-capacitance Method

When keeping the inter-electrode distance at 0.8 times the touch electrode size or less, you can reduce the effects of crosstalk by considering the overlay panel thickness, electrode size, and the tolerance for touch position misalignment.

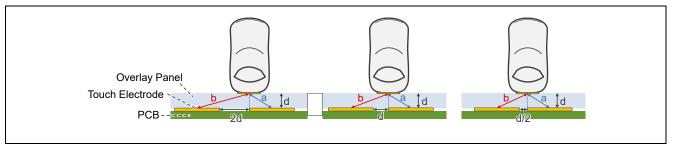

Figure 2-27 shows the relationship between inter-electrode distance and the risk of crosstalk. In the figure, (a) is the distance from the finger to the center of the touch electrode to be pressed, and (b) is the distance to the center of the adjacent touch electrode. Even if the finger's touch position is slightly offset from the target touch electrode, the target button still detects the touch ON state. If thickness (d) of the overlay panel remains constant, a shorter inter-electrode distance makes point (b) closer to point (a). This increases The capacitance of the adjacent touch electrode, making a touch ON state more likely to be detected. In addition, when the touch ON threshold value is close to the CTSU measurement value of an adjacent touch electrode, there is a higher possibility that external noise may cause fluctuations in the measurement value, resulting in false detections.

Figure 2-27. Changes in Distance between Electrodes and Finger to Touch Electrode

In addition, due to design differences such as the wiring length of the touch electrode circuit, the sensor drive pulse frequency for each electrode differs and the sensitivity varies, or if an overlay panel with a high dielectric constant is used, or if the electrode size is large and the capacitive coupling with the finger through the air is large, crosstalk is likely to occur. In all these cases, sufficient electrode spacing can be used to prevent problems.

## 2.7 Electrode Application Examples

#### 2.7.1 Example of slider electrode layout pattern design

Figure2-28 shows the recommended pattern for a slider electrode in the self-capacitance method. This pattern is designed for finger touch and ensures that 3 electrodes respond when the slider is touched anywhere other than the two ends. To change the size of the slider, adjustments must be made by adding or removing electrodes rather than expanding or shrinking the pattern.

Figure2-28. Recommended Pattern for Slider Electrode for Self-Capacitance Method

#### 2.7.2 Example of wheel layout pattern design

Figure2-29 shows the recommended wheel electrode pattern for the self-capacitance method. This pattern is designed for finger touch and ensures that 3 electrodes respond no matter where the wheel is touched. To change the size of the wheel, adjustments must be made by adding or removing electrodes rather than expanding or shrinking the pattern.

Figure2-29. Recommended Pattern for Wheel Electrode for Self-Capacitance Method

#### 2.7.3 Film-type circuit boards

Film-type circuit boards are thinner and more flexible than printed circuit boards (PCBs) and are increasingly being used for touch electrodes because they enhance the final product design. Film-type boards include flexible printed circuit boards (FPCs), on which patterns are formed with conductive metal (mainly copper foil) on a base film, and film devices for which patterns are printed on a base film with conductive paste. The basic concept of electrode circuit design for capacitive touch buttons, both for FPCs and film devices, is the same as the description in 2.1 Outline of Design Recommendations. The following sections explain precautions and the design recommendations that we suggest you avoid because they are difficult to implement when designing with film-type substrates.

#### 2.7.3.1 Flexible printed circuit boards

FPCs use copper foil for the patterns and can be designed with two or more layers, allowing for layouts similar to the PCB design recommendations. For PCB design recommendations, see 2.1 Outline of Design Recommendations. Precautions and design recommendations that are not appropriate for FPCs are as follows.

When mounting an IC device such as an MCU on an FPC, avoid placing a touch electrode directly beneath the device on the FPC surface. Doing so may lead to increased parasitic capacitance in the touch electrode circuit and make it more susceptible to noise emitted by the IC device.

When placing a shield pattern directly under the touch electrode or wiring, the parasitic capacitance increases because the board is thin and the pattern layers on both sides of the board are close to each other. When shielding the touch electrode or wiring, use a cross-hatched GND pattern. If increased parasitic capacitance is a concern, design the shield pattern for the touch electrode or wiring farther away than the recommended distance, or widen the cross-hatched pattern pitch or space to keep the parasitic capacitance below the recommended conditions for the touch electrode circuit.

CTSU can be measured even if the parasitic capacitance connected to the TS pin exceeds the recommended range, but the sensor drive pulse frequency is 0.5 MHz and the SNR of the button is reduced. If the parasitic capacitance connected to the TS pin is in the deprecated range, measurement errors, overflows, and underflows will occur in the CTSU measurements, and reduced SNR and button detection will not be possible. In that case, consider whether the pitch and space of the hatched shield pattern can be increased to reduce the parasitic capacitance to the recommended range of the touch electrode circuit. In addition, by reducing the total resistance, the upper limit of the parasitic capacitance recommendation range can be raised. If the total resistance value is greater than 560  $\Omega$ , consider whether it is possible to reduce the total resistance value from the reference value of 560  $\Omega$ .

In order to prevent deterioration of external noise immunity and excessive output current of the TS pin, select the damping resistor value so that the total resistance value of the TS pin (the total resistance value of the damping resistor and the FPC) is in the range of 560  $\Omega$  to 1 k $\Omega$ .

Parasitic capacitance increases when the touch panel is installed in the product housing, due to how it is attached to the hardware or placement space that is narrow and close to other electrodes or wiring. Always design the touch electrode circuit pattern taking this increase into consideration.

#### 2.7.3.2 Film device

Film devices, on which have patterns are printed, can be manufactured at a lower cost than FPCs. They also support transparent patterns, making it easy to place a light source directly under the touch electrode to illuminate the buttons. On the other hand, film device patterns are formed using conductive pastes that use ITO, silver, and carbon, so their resistance is higher than that of copper foil patterns found on FPCs and PCBs. Film devices are typically manufactured with single-layer patterns. While it is possible to manufacture multi-layer patterns, vias cannot be used to connect both sides, resulting in less design flexibility compared to FPC or PCB. Therefore, film devices are generally configured with only touch electrodes and wiring, and then connected with an FPC/FFC connector to the control board on which the CTSU microcontroller is mounted.

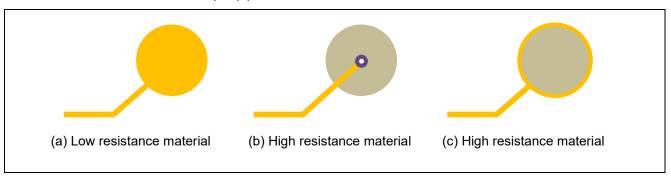

Although any conductive material can be used for the electrode, note that materials with high surface resistance—such as transparent electrodes made of ITO and AG materials, or carbon-based electrodes— can reduce the sensor drive pulse frequency of the CTSU and may reduce touch sensitivity. Also, materials with high surface resistance may not be consistently sensitive depending on where the finger is placed. If such a material must be used, lay out the wiring as shown in Figure2-30 (b) arrange wiring as close to the center of the electrode or (c) surround the entire electrode with a material that has low surface resistance so the resistance value is constant regardless of where the surface is touched. When using copper or other sufficiently low surface resistant material, the wiring can even be routed from any point on the button electrode itself, as shown in example (a).

Figure 2-30. Button Electrode Wiring Method

The basic design of a film device is the same as that of the PCB design recommendations, as described in section 2.1 Outline of Design Recommendations. Precautions and design recommendations that are not appropriate for film devices are as follows.

Whenever possible, estimate the resistance and capacitance of the touch electrode circuits on the film device and control board at the hardware design stage, and design them so that the CTSU's recommended electrode circuit conditions. Single-sided film devices tend to have longer wiring due to the routing of touch electrode wiring and the wiring from the control board, potentially causing the resistance of the touch electrode circuit to exceed the CTSU recommendation. For designs with longer wiring, consider using a conductive paste with lower resistance or increasing the pattern film thickness during the design stage to reduce overall resistance.

If the total resistance exceeds  $1k\Omega$ , and you know the parasitic capacitance when the film electrode is incorporated into the housing of the final product, refer to 4.2 Base Clock Frequency/Sensor Drive Pulse Frequency Settings and calculate a damping resistance value to make the total resistance  $1k\Omega$  or less. When using a value other than the recommended  $560\Omega$ , use a larger resistance value within the range of the settable sensor drive pulse frequency to prevent a decrease in resistance to external noise and excessive output current from the TS pin. If individual manufacturing differences in the product are expected, select a resistance value one or two levels lower so that it falls within the measurement range of the CTSU based on the worst case.

For single-sided film devices, place as much cross-hatched GND shield as possible on any vacant pattern area around the touch electrode and wiring on the film device to prevent noise. Since there is no shielding layer directly beneath the touch electrode and wiring, avoid placing potential noise-generating devices directly under the film device, and make sure the film device is kept at a distance from the control board.

When placing a shield pattern directly under the touch electrode or wiring on a film device with two or more layers, the parasitic capacitance increases because the substrate is thin and the pattern layers on both sides of the board are close to each other. When shielding the touch electrode or wiring, use a cross-hatched GND pattern. If increased parasitic capacitance is a concern, design the shield pattern for the touch electrode or wiring farther away than the recommended distance, or widen the cross-hatched pattern pitch or space to keep the parasitic capacitance below the recommended value for the touch electrode circuit.

CTSU can be measured even if the parasitic capacitance connected to the TS pin exceeds the recommended range, but the sensor drive pulse frequency is 0.5 MHz and the SNR of the button is reduced. If the parasitic capacitance connected to the TS pin is in the deprecated range, measurement errors, overflows, and underflows will occur in the CTSU measurements, and reduced SNR and button detection will not be possible. In that case, consider whether the pitch and space of the hatched shield pattern can be increased to reduce the parasitic capacitance to the recommended range of the touch electrode circuit. In addition, by reducing the total resistance, the upper limit of the parasitic capacitance recommendation range can be raised. If the total resistance value is greater than 560  $\Omega$ , consider whether it is possible to reduce the total resistance value from the reference value of 560  $\Omega$ .

Parasitic capacitance increases when the touch panel is installed in the product housing, due to how it is attached to the hardware or placement space that is narrow and close to other electrodes or wiring. Always design the touch electrode circuit pattern taking this increase into consideration.

## 2.7.3.3 Design example

Renesas has released the Touchless Button Demo Solution as a reference design for film-type circuit boards. Design-related information is available at the link below.

#### Touchless Button Reference Design

https://www.renesas.com/products/microcontrollers-microprocessors/rx-32-bit-performance-efficiencymcus/touchless-button-ref-touchless-button-reference-design

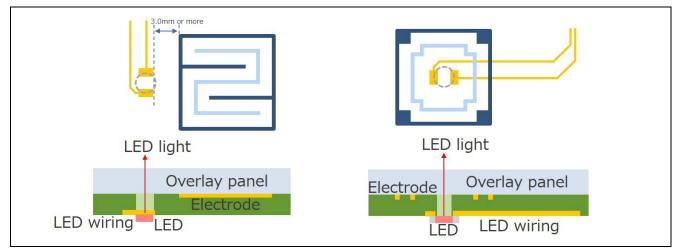

## 2.7.4 LED wiring layout

## 2.7.4.1 Direct lighting example

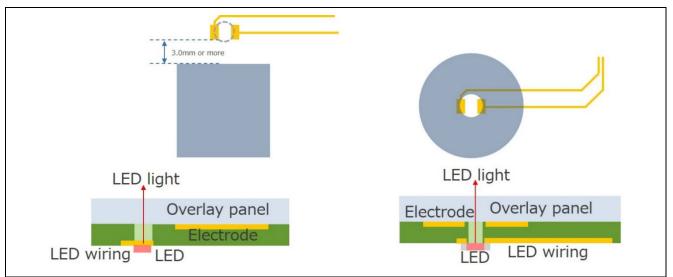

Figure2-31 shows the electrode pad and LED wiring for the self-capacitance method. We recommend routing the LED around the outer edge of the electrode pad, as shown to the right of the figure. To reduce noise radiated from the LED circuit, cover the LED wiring with a GND shield and, for multi-layer boards, cover the opposite surface with a GND shield as well.

Note that routing the LED wiring in the electrode pad requires a hole to be made in the electrode, reducing the touch-sensitive surface area and bringing the LED wiring in close proximity to the electrode. This increases the risk of weaker sensitivity due to an increased parasitic capacitance.

Figure2-31. Electrode Pad and LED Routing Example for Self-capacitance Method

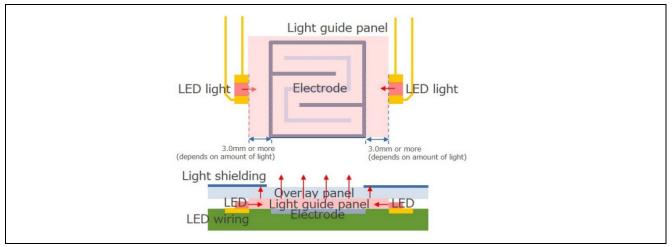

## 2.7.4.2 Indirect lighting (using light guide plate)

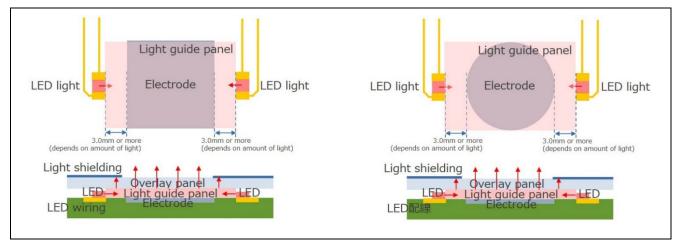

Figure2-32 shows an example of LED routing using an electrode pad and a light guide plate for the self-capacitance method. The LED (the light source) must be a set distance from light-emitting surface to ensure even lighting. Placing multiple LEDs (light sources) in opposing positions helps to eliminate uneven lighting.

Figure2-32. Example of LED Routing using Electrode Pad Light Guide Plate for Self-capacitance Method

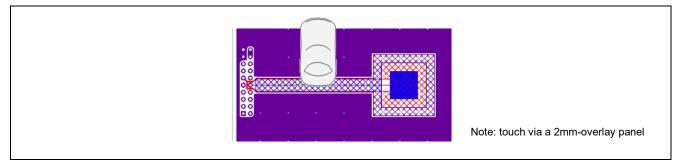

#### 2.7.5 When panel and button electrodes are separated

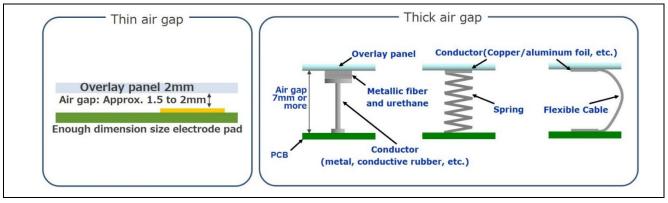

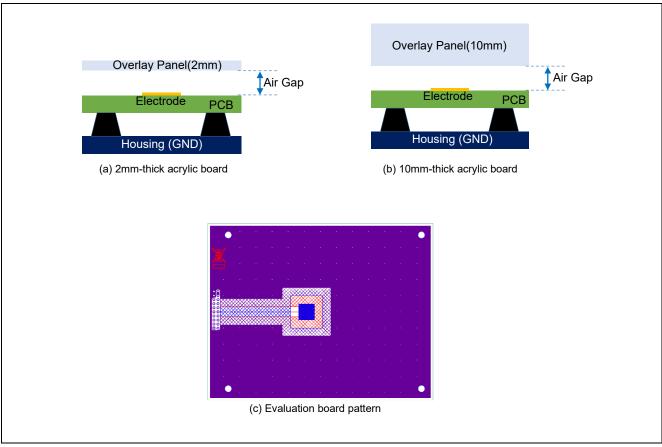

Figure2-33 shows an example configuration with space between the panel and button electrodes. Although the configuration depends on the size of the button electrode, parasitic capacitance, and other factors, if all conditions are favorable, touch can be detected even with a 2mm air gap between the panel and electrodes. However, the thicker the air gap, the smaller the capacitance change at touch, lowering the SNR of the touch button.

Note that, when dealing with strict noise immunity requirements, if the air gap is larger than 2mm and touch detection is difficult due to other conditions, you may need to extend the button electrodes to the panel, as shown on the right of the figure. For either method, design the layout so that the contact points are electrically connected to the PCB or to the conductive parts corresponding to the touch electrodes on the panel side.

Figure2-33. Example of Air Gap Measure for Auto-capacitance Method

#### 2.7.6 Self-capacitance Matrix

Self-capacitance matrix configurations in which self-capacitance electrodes are arranged in a grid pattern are not supported by the CTSU driver, middleware, or QE for Capacitive Touch. When using electrodes in a matrix configuration, make sure you use the mutual capacitance method.

#### 2.7.7 Precautions for Using RF Communication Device

Since the CTSU can detect minute changes in the capacitance of the touch electrode circuit, it may be susceptible to noise in the surrounding environment. Radio waves from RF communication devices such as Wi-Fi and Bluetooth® may also affect CTSU measurements. If the antenna of the RF communication device must be placed on the CTSU-embedded MCU board or within the housing, minimize interference by maximizing the distance between the touch MCU/touch electrode circuit and the RF antenna.

#### 2.7.8 Design Example of Metal Overlay Panel

Renesas has released an application note offering a design example using a metal panel as the overlay panel. Design-related information and other details are available at the link below.

Metal Touch Solution Reference Design

https://www.renesas.com/products/microcontrollers-microprocessors/rx-32-bit-performance-efficiencymcus/metal-touch-ref-metal-touch-solution-reference-design

## 3. Mutual Capacitance Method: Electrode Layout Patterns

## 3.1 Outline of Design Recommendations

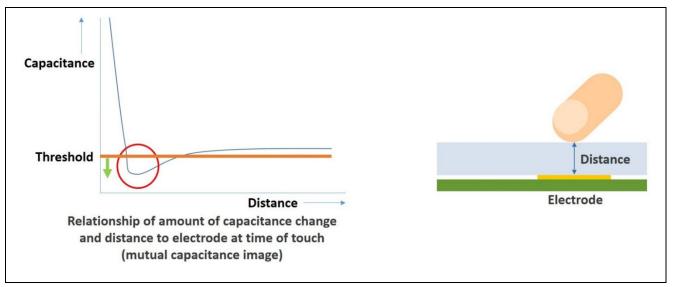

The mutual-capacitance method boasts button electrodes with superior water-resistance, support based on using matrix structure, and many other functions not available with self-capacitance. However, mutual-capacitance requires complicated button electrode configurations and wire routing, making sensitivity adjustment difficult. The merits and demerits of each method must be taken into account when designing layout patterns. Furthermore, unlike the self-capacitance method, sensitivity is lost when panel thickness falls below a specified level. The designer must carefully consider the button electrode configuration when determining panel thickness.

Always use a multi-layer board of at least two layers for the mutual-capacitance method. This chapter describes a double-layer board as an example.

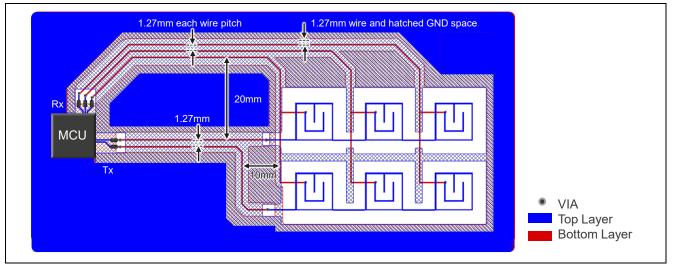

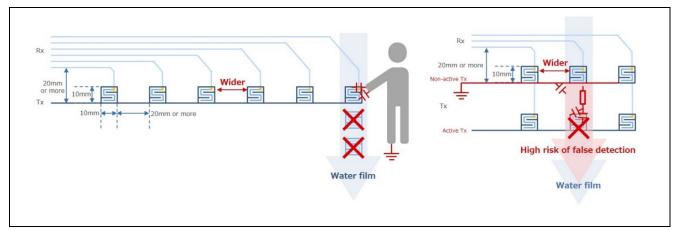

This section provides reference design information for creating mutual-capacitance method buttons on a printed board. We recommend placing a cross-hatched pattern GND shield guard around the electrodes. We also recommend using an ESD countermeasure by shielding the outer circumference of the board with a GND plane pattern. The numbers listed here correspond to the numbers in each figure, excluding numbers 8 and 9. Each item is described in detail later.

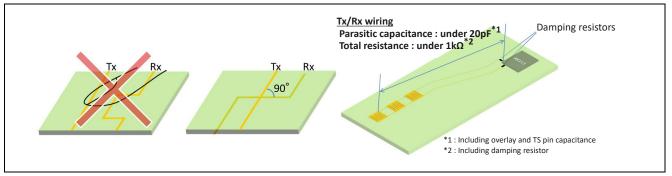

- ① Electrode shape: square (combined transmitter electrode TX and receiver electrode RX)

- ② Electrode size: 10mm or larger

- ③ Electrode proximity: Electrodes should be placed with ample distance so that they do not react simultaneously to the touch object (finger, etc.), (suggested interval: button size x 0.8 or more)

- ④ Wire width: The thinnest wire achievable through mass production; approx. 0.15mm to 0.20mm for a printed board

- <sup>(5)</sup> Wiring length: Make the wiring as short as possible. On corners, form a 45-degree angle, not a right angle.

- 6 Wiring spacing:

(A) Make spacing as wide as possible to prevent false detection by neighboring electrodes.

- (B) When electrodes are separated: 1.27mm pitch

- (C) 20mm or more to prevent coupling capacitance generation between Tx and Rx.

- ⑦ Cross-hatched GND pattern width: 2mm or more

- 8 Cross-hatched GND pattern (shield guard) proximity

- Because the pin parasitic capacitance in the recommended button pattern is comparatively small, parasitic capacitance increases the closer the pins are to GND.

- A: 4mm or more around electrodes

- We also recommend approx. 2-mm wide cross-hatched GND plane pattern between electrodes. B: 1.27mm or more around wiring

- 9 Tx, Rx parasitic capacitance: 20pF or less (including overlay panel and TS pin capacitance)

- (1) Electrode + wiring resistance: 560 $\Omega$  to 1k $\Omega$  (including damping resistor with reference value of 560 $\Omega$ )

- ① Do not place GND pattern directly under the electrodes or wiring.

The active shield function cannot be used for the mutual-capacitance method.

Figure3-1. Example of Button Pattern for Mutual-capacitance Method

## 3.2 Mutual-capacitance Method Overview

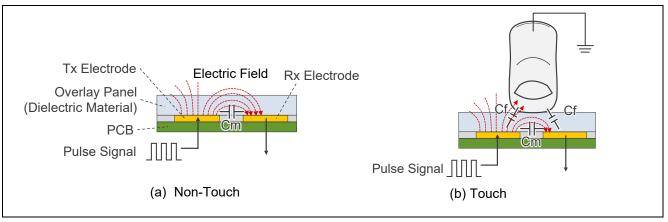

Figure3-2 shows the mutual-capacitance generated in the electrode. Mutual capacitance indicates electrostatic capacitance Cm generated by the electric field between two electrodes: transmitter electrode (Tx) and receiver electrode (Rx). When a finger or other body part comes close to the button, a capacitive coupling is created with part of the electric field, causing capacitance Cm to decrease. In the mutual-capacitance method, the CTSU determines whether the button is ON or OFF from the decrease in capacitance Cm caused by the proximity of the finger (body).

Figure 3-2. Image of Mutual-capacitance Electrodes

## 3.3 Principle of CTSU Mutual-capacitance Method Detection

Figure3-3 shows an overview of the CTSU internal configuration for the mutual-capacitance method. The CTSU outputs a digital count that is negatively proportional to the mutual capacitance of Rx and Tx connected to the electrode, and determines whether the touch button is ON or OFF by software.

In order to measure the capacitance Cm existing on the two connected electrodes, the CTSU obtains Cm by inverting the phase relationship between the pulse output and the switched capacitor, measuring the self capacitance twice, then calculating the difference of the two values by software. For more details on the mutual-capacitance detection principle, refer to the application note "<u>Capacitive Sensor Microcontrollers</u> <u>CTSU Capacitive Touch Introduction Guide (R30AN0424)</u>".

The image of CTSU measurement and the relationship between the sensor drive pulse frequency and sensitivity are based on the same concept as the self-capacitance method. For details, see 2.3 Principle of CTSU Self-capacitance Method Detection.

Figure 3-3. Internal Configuration Outline for Mutual-Capacitance Method

## 3.4 Electrode Pattern Designs

#### 3.4.1 Electrode circuit configuration

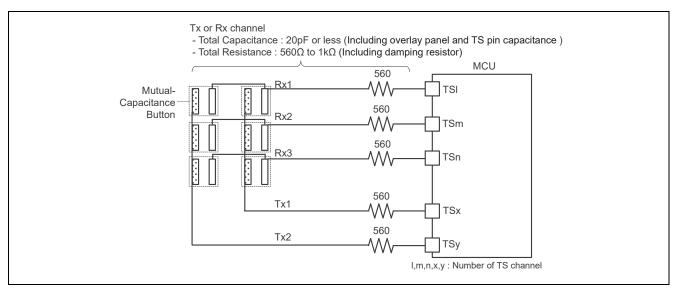

Figure3-4 shows an electrode circuit for the mutual-capacitance method. Mutual-capacitance method button electrodes are configured as receiver electrode (Rx) and transmitter electrode (Tx), and include electrode wiring and a damping resistor. The standard value for the damping resistor is  $560\Omega$ . Place the damping resistor as close as possible to the TS terminal to prevent noise from mixing in from the wiring between the TS pin and the resistor.

When designing a mutual-capacitive touch electrode circuit, design the pattern and select the materials so that the following recommended conditions are met.

Parasitic capacity C: 20pF or less (including Tx or Rx, overlay panel and TS pin capacitance) Resistance value R:  $560\Omega$  to  $1k\Omega$  or less (including damping resistor)

Keep in mind that the electrostatic capacitance C of the entire electrode circuit also includes parasitic capacitance with objects around the board, such as the board's GND pattern, the overlay panel, and the body chassis. By keeping C low in the design, the touch ON/OFF measurement value difference (signal value) will increase, and the SNR will improve when selecting a high frequency for the CTSU sensor drive pulse frequency. The total capacitance for each electrode can be confirmed using QE for Capacitive Touch.

Figure 3-4. Electrode Circuit for Mutual-capacitance Method

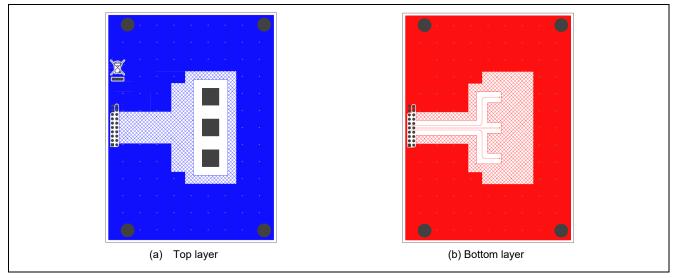

#### 3.4.2 Electrode pads

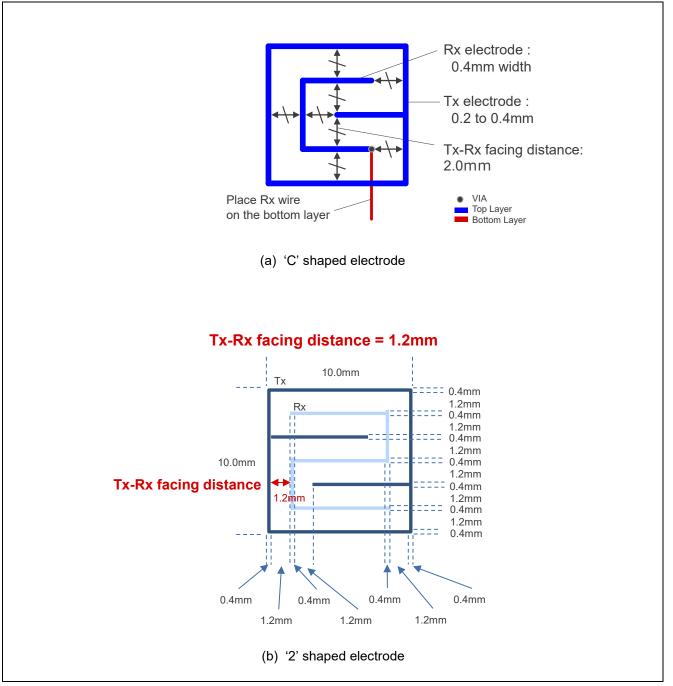

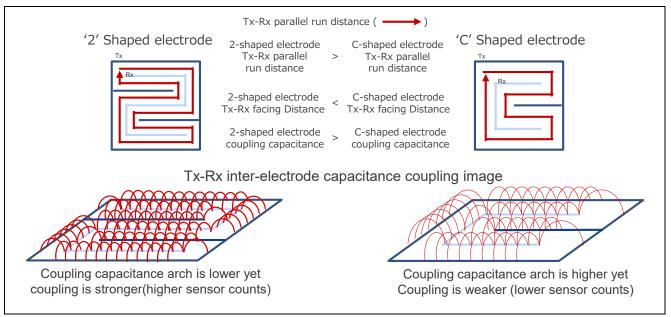

Figure3-5 shows the recommended electrode pattern for the mutual-capacitance method. Renesas has verified operation using the pattern in this example. This pattern supports an overlay panel thickness of 2mm to3mm. The Tx pattern surrounds the Rx pattern to protect the Rx electrode, which is vulnerable to noise. This configuration increases the distance between Tx and Rx opposing sides (called "facing distance" herein) as well as the surface area that comes in contact with the finger.

Figure 3-5. Mutual Capacitance Method: Pattern Example

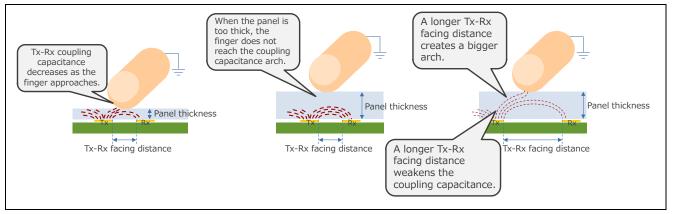

Mutual-capacitance method touch measurement measures the electromagnetic field (capacitive coupling) between Tx and Rx and captures the phenomenon of the capacitive coupling decreasing as a fingertip (i.e., part of the human body) in close proximity attracts part of the electromagnetic field. Therefore, the layout pattern must be designed to (1) maximize the capacitive coupling between Rx and Tx, and (2) make the rate of capacitance coupling reduction as large as possible when a finger is in proximity

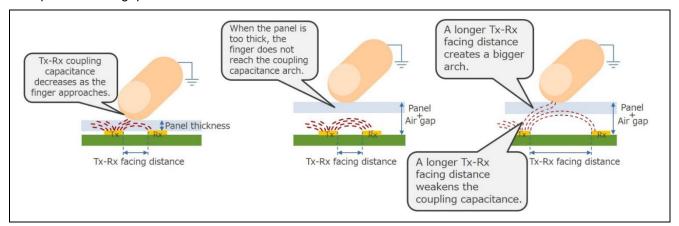

Figure3-6 shows an image of the Tx/Rx coupling capacitance electromagnetic field for mutual-capacitance method electrodes. A greater Tx/Rx facing distance is required when using a thick overlay panel. However, as most products limit the electrode size, it is often difficult to extend the Tx/Rx distance. As shown in Figure3-5, you may need to use an electrode with a shorter Tx/Rx distance like the Type C electrode, but compared to the Type 2 electrode, the shorter Tx/Rx distance of the Type C electrode means the measured value may also be smaller.

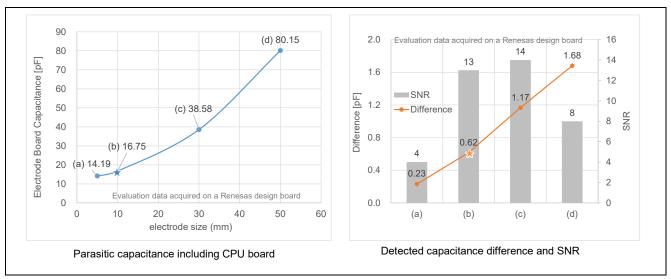

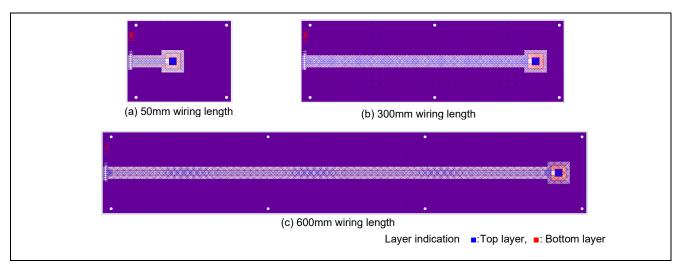

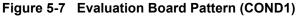

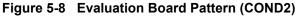

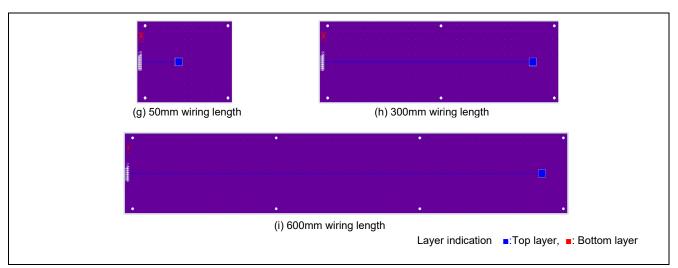

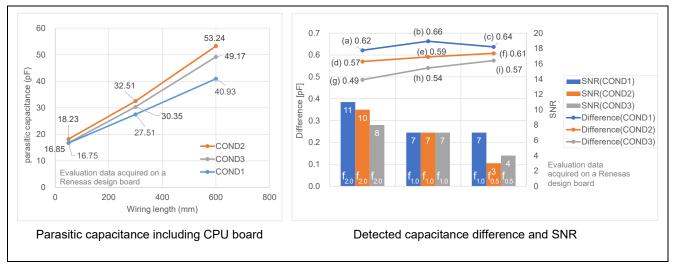

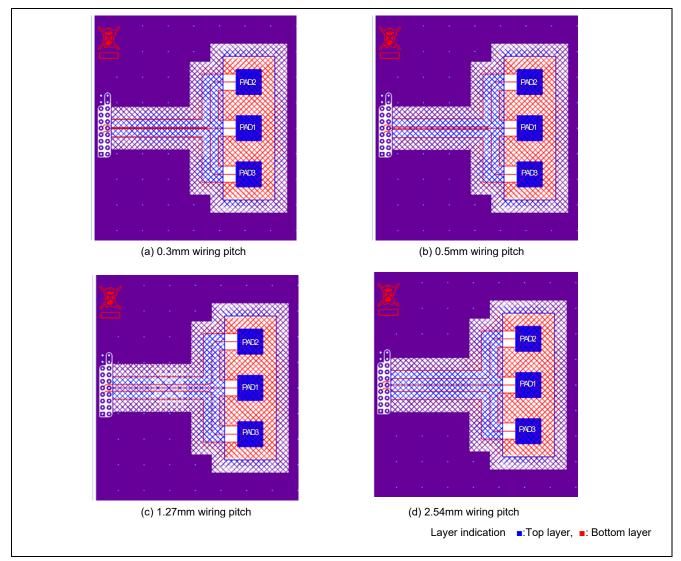

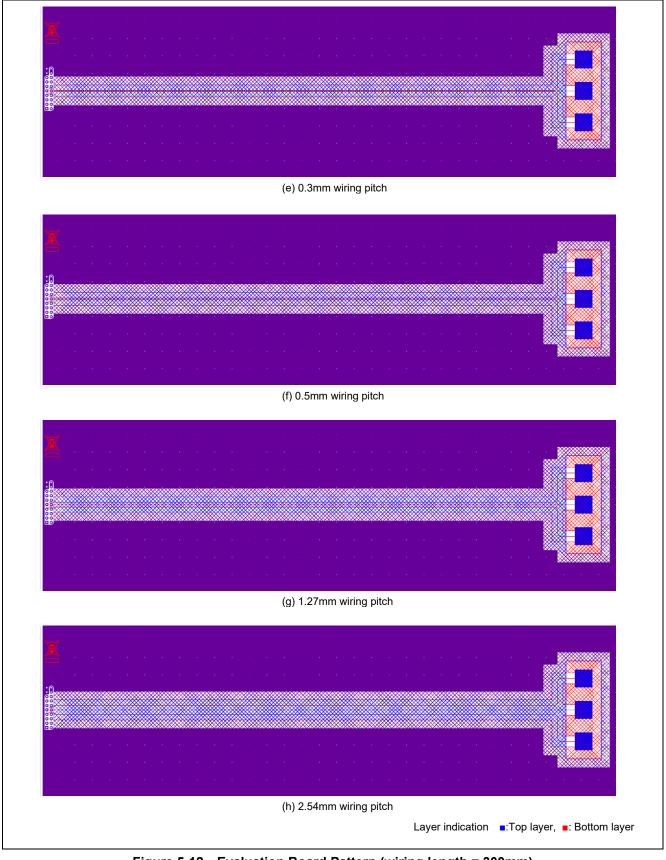

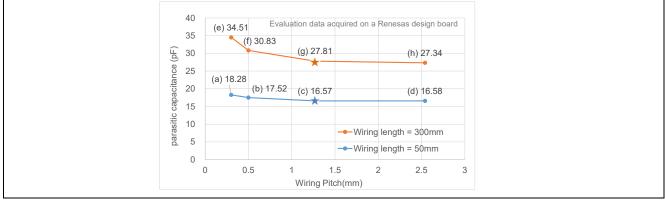

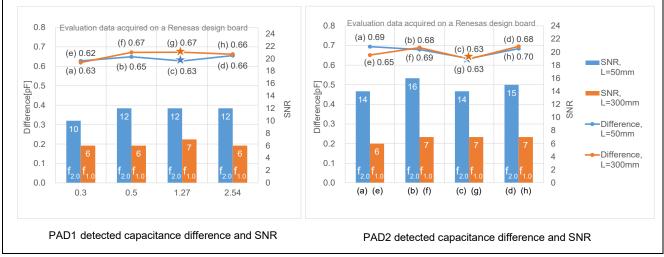

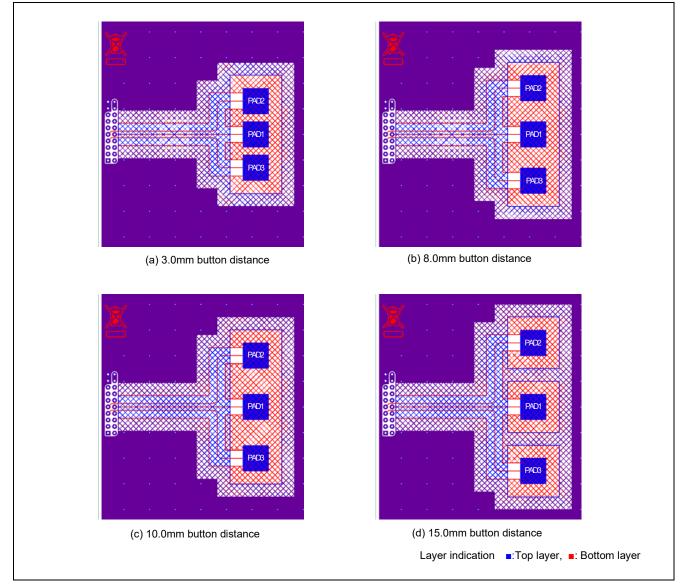

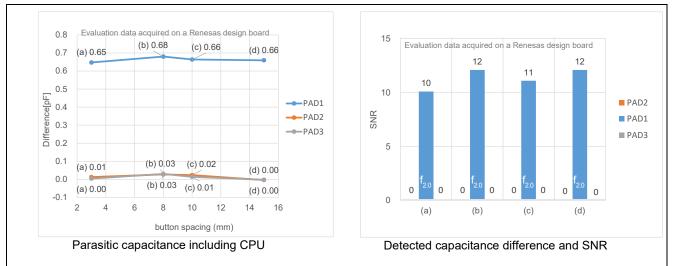

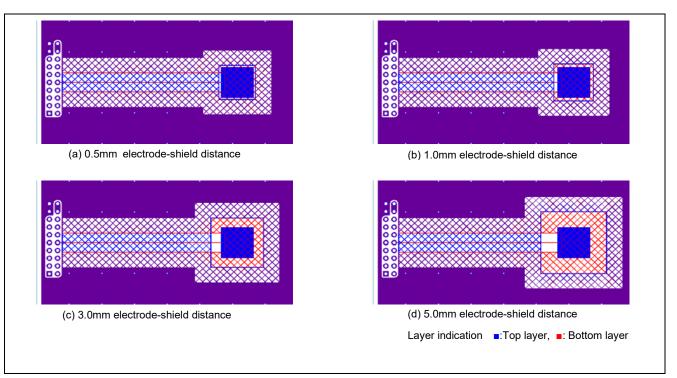

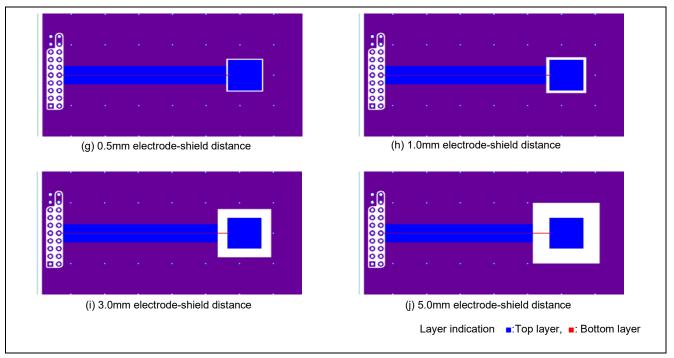

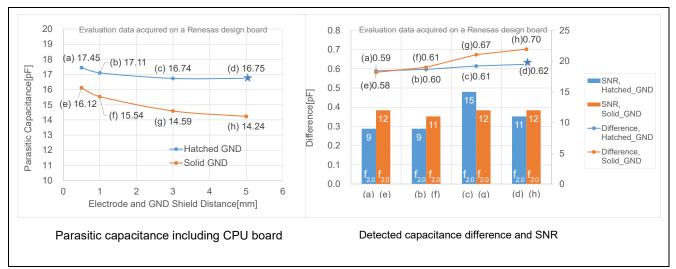

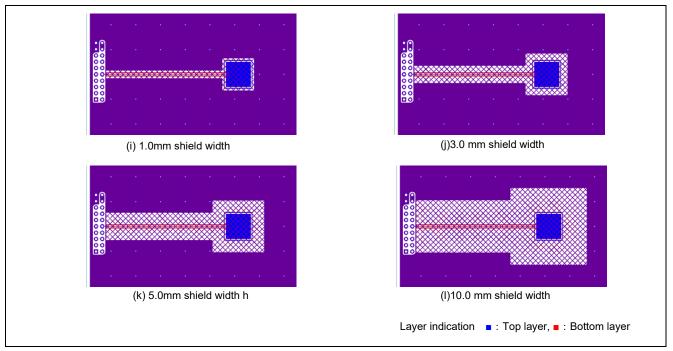

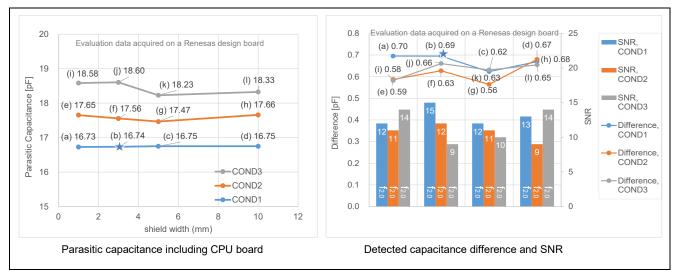

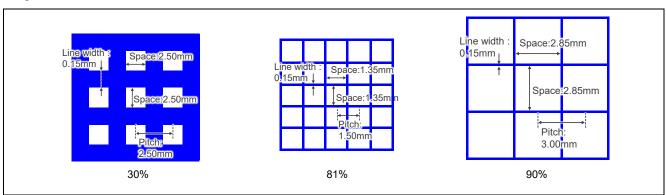

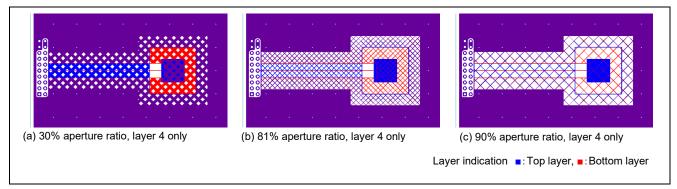

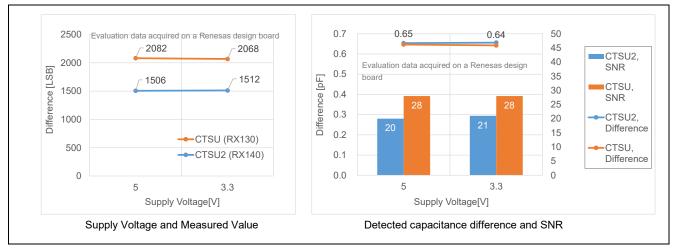

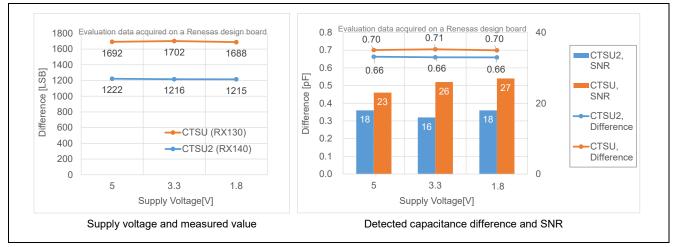

Figure3-6. Image of Electrode Tx-Rx Capacitance Coupling for Mutual Capacitance Method