# No. AN9533 October 1995

# **Application Note**

# Design Considerations When Using the HI1176 Input Clamp Circuit

Author: Juan C. Garcia

#### Introduction

The HI1176 is an 8-bit CMOS analog-to-digital converter designed for video applications and includes a sync clamp function. The device utilizes a 2-step parallel conversion method which allows for high conversion speeds and low power consumption. The datasheet for the HI1176 can be obtained by accessing AnswerFAX document number 3582.

# Clamp Operation

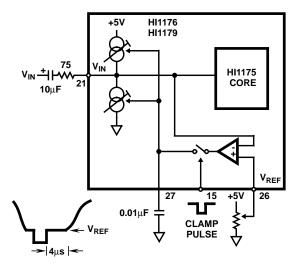

The HI1176 has the capability to clamp the input signal before it is digitized by the ADC (see Figure 1). A comparator is used to determine if the input, during the clamp pulse time, is above or below the desired clamp voltage,  $V_{\mbox{\scriptsize REF}}.$  Once the comparison has been made, the appropriate current source is then turned on to charge the input capacitor up or down depending on the comparator output. The HI1176 also has an internal monostable multivibrator that can be set to run in various modes of clamp pulse operation. For example, if performing the DC restore function for NTSC video, the HI1176 can be configured to clamp the back porch of the incoming video to the voltage on the V<sub>REF</sub> pin. If a sync detect function is required after the ADC, then V<sub>RFF</sub> can be set so the complete video signal including the sync pulse is digitized. If the sync is to be stripped before the ADC then V<sub>REF</sub> can be set so only the active video portion of the video gets digitized. This will effectively increase the resolution for this portion of the video signal.

FIGURE 1. CLAMP BLOCK DIAGRAM

There are several methods for implementing the input DC restore function when using the HI1176. One method is to directly input the clamp pulse. Another method is to use the internal monostable multivibrator, eliminating the external monostable multivibrator. To use the built in multivibrator an RC network is necessary to set the pulse width on pin 15 and the clamping pulse is connected to pin 14 (SYNC). An RC of 130k and 100pF gives a 2.75us pulse. Narrower pulse widths can be achieved by reducing the resistor and/or capacitor values. The SEL pin (pin 13) will determine which SYNC edge the pulse is generated on. In this mode of operation, the RC time constant can be set to provide very narrow pulse widths. As a general rule, the resistor value should be a minimum of 5k and capacitance should be greater than zero (the monostable will generally work without a capacitor connected due to parasitic capacitance provided by the package, bond wires and silicon itself, however this is not recommended due to lot variation in the assembly and wafer fab processes).

The minimum reset time for the monostable is equal to one period of the sampling clock (or 50ns for 20MHz operation).

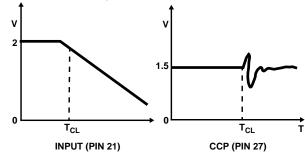

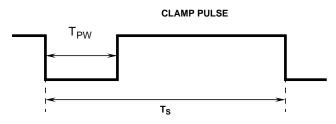

T<sub>CL</sub> = CLAMP PULSE OCCURRENCE

#### FIGURE 2. CLAMPING CHARACTERISTICS

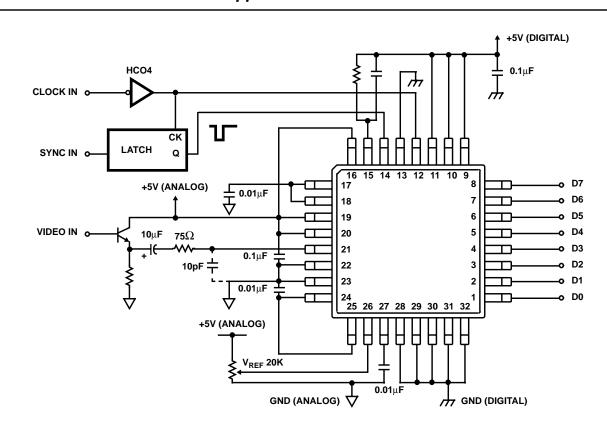

When inputting the clamp pulse directly, care should be taken to have the SYNC pulse input latched by the ADC sampling clock connected to the PW input. This is done to prevent beat frequencies, generated between the clock and clamp inputs, from showing up as vertical sag in video applications. If this is not a concern the latch is not necessary. In this mode of operation, narrow pulse widths can also be achieved. The minimum allowable pulse on the PW pin (14) in this configuration is 1.75ns. Figure 3 graphically illustrates this mode of operation.

FIGURE 3. PEDESTAL CLAMP EXECUTED BY SYNC PULSE

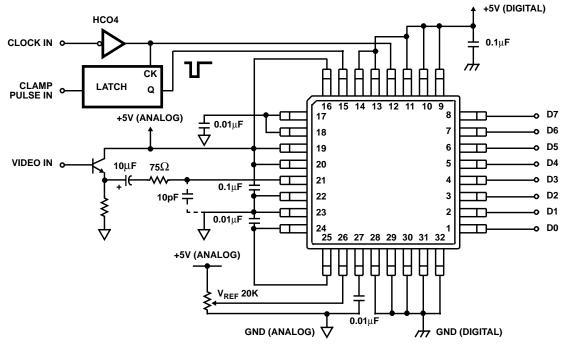

FIGURE 4. CLAMP PULSE IS DIRECTLY INPUT (SELF BIAS USED)

# **Design Equations**

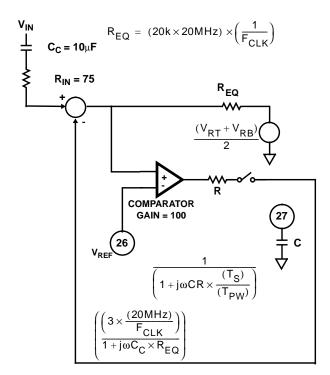

As stated in the previous section, the HI1176 clamp circuitry gives designers the ability to clamp the ADC input to a predetermined value set by the voltage on the  $V_{REF}$  pin. When enabled, the clamp circuit (as seen in Figure 5) closes the feedback loop to the input and thereby calling in a low pass filter function defined by the following equation:

$$F_{C} = \frac{1}{\left(1 + j\omega CR \times \frac{(T_{S})}{(T_{PW})}\right)}$$

Where  $T_{\text{S}}$  is the period of the clamp pulse,  $t_{\text{PW}}$  is width of the clamp pulse, R is the output resistance of the comparator (typically  $2k\Omega)$  and C is the  $C_{\text{CP}}$  capacitor on pin 27 of the HI1176 (nomenclature changed to avoid confusion during analysis).

Typical values for the variables in the equation above are as follows:

$$R=2k\Omega,\,C=0.01\mu F,\,T_S=15\mu s,\,T_{PW}=2ns.$$

Inserting these values and solving for the cutoff frequency of the low pass filter yields a cutoff frequency for the low-pass which will effectively filter out the desired signal.

$$F_C = \frac{1}{1 + 2\pi (0.01 \mu F) (100) \frac{(15 \mu s)}{(2ns)}} = 0.955 Hz$$

The overall equation for the ADC can also be solved for in a similar fashion. By using the equation defined in Figure 5 for the overall feedback loop, a cutoff frequency of 1.32Hz is obtained at a sampling frequency of 20MHz.

# Conclusion

The input clamp circuit of the HI1176 has been shown to be a useful tool for users who wish to select portions of their incoming signals which they do not wish to digitize. The flexibility of the circuit makes it ideally suited for a variety of applications, particularly those which are video related. Should your application require faster sampling speeds than the HI1176 offer, refer to the HI1179 (datasheet available via AnswerFAX document 3566). The HI1179 offers a similar input clamp circuit to the HI1176 and is capable of sampling speeds up to 35MHz.

FIGURE 5. CHARACTERISTIC EQUATIONS DEFINING CLAMP FUNCTION.

# **Application Note 9533**

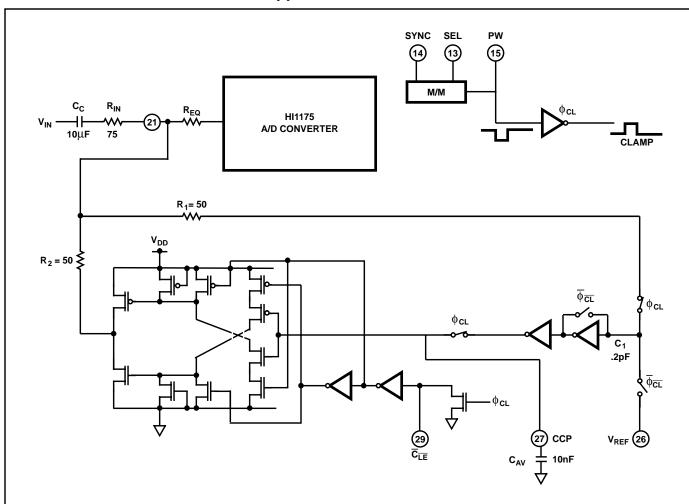

FIGURE 6. CLAMP CIRCUIT HI1176

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

## Sales Office Headquarters

#### **NORTH AMERICA**

Intersil Corporation

P. O. Box 883, Mail Stop 53-204

Melbourne, FL 32902

TEL: (321) 724-7000 FAX: (321) 724-7240

#### **EUROPE**

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

#### **ASIA**

Intersil (Taiwan) Ltd.

Taiwan Limited

7F-6, No. 101 Fu Hsing North Road

Taipei, Taiwan

Republic of China

TEL: (886) 2 2716 9310

FAX: (886) 2 2716 9310 FAX: (886) 2 2715 3029