## APPLICATION NOTE

AN017 Rev 0.00 Feb 1999

The Integrating A/D Converter (ICL7135)

## Introduction

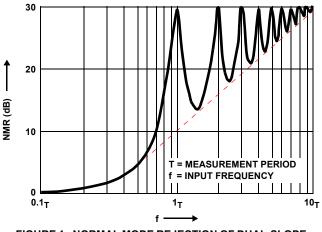

Integrating A/D converters have two characteristics in common. First, as the name implies, their output represents the integral or average of an input voltage over a fixed period of time. Compared with techniques which require that the input is "frozen" with a sample-and-hold, the integrating converter will give repeatable results in the presence of high frequency noise (relative to the measurement period). A second and equally important characteristic is that they use time to quantize the answer, resulting in extremely small nonlinearity errors and no possibility of missing output codes. Furthermore, the integrating converter has very good rejection of frequencies whose periods are an integral multiple of the measurement period. This feature can be used to advantage in reducing line frequency noise, for example in laboratory instruments (Figure 1).

FIGURE 1. NORMAL MODE REJECTION OF DUAL-SLOPE CONVERTER AS A FUNCTION OF FREQUENCY

In addition, a competitive instrument-quality product should have the following features:

- Single Reference Voltage. This is strictly a convenience to the user; but since many designs are available with single references that contribute negligible error, products requiring dual references are rapidly becoming obsolete.

- Auto-Zero. This eliminates one trim-pot and a troublesome calibration step. Furthermore, it allows the manufacturer to use op amps with up to 10mV offset while still achieving system offsets of only a few microvolts.

- High Input Impedance. Recently developed monolithic FET technology allows input impedances of 1000MΩ and leakages of a few pico amps to be achieved fairly readily.

The unique characteristics of the integrating converter have made it the natural choice for panel meters and digital

voltmeter applications. For this reason, overall usage of integrating converters exceeds the combined total of all other conversion methods. Furthermore, the availability of low cost one chip converters will encourage digitizing at the sensor in applications such as process control. This represents a radical departure from traditional data logging techniques which in the past have relied heavily on the transmission of analog signals. The availability of one chip microprocessor system (with ROM and RAM on chip) will give a further boost to the 'conversion at the sensor' concept by facilitating local data processing. The advantage of local processing is that only essential data, such as significant changes or danger signals, will be transmitted to the central processor.

# *The Dual Slope Technique - Theory and Practice*

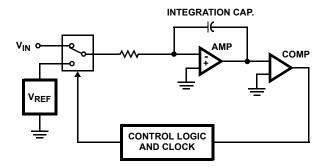

The most popular integrating converter is the "dual-slope" type, the basic operating principles of which will be described briefly. However, most of the comments relating to linearity, noise rejection, auto-zero capability, etc., apply to the whole family of integrating designs including charge balancing, triple ramps, and the 101 other techniques that have appeared in the literature. A simplified dual-slope converter is shown in Figure 2.

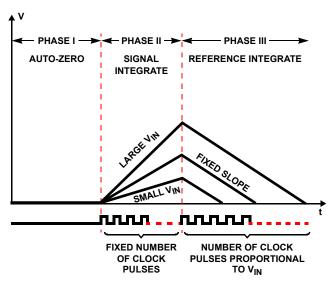

The conversion takes place in three distinct phases (Figure 3).

FIGURE 2. SIMPLIFIED DUAL-SLOPE CONVERTER

#### FIGURE 3. THE THREE PHASES OF DUAL-SLOPE CONVERSION

**Phase 1, Auto-Zero.** During auto-zero, the errors in the analog components (buffer offset voltages, etc.) will be automatically nulled out by grounding the input and closing a feedback loop such that error information is stored on an "auto-zero" capacitor.

**Phase 2, Signal Integrate.** The input signal is integrated for a fixed number of clock pulses. For a  $3^{1}/_{2}$ -digit converter, 1,000 pulses is the usual count; for a  $4^{1}/_{2}$ -digit converter, 10,000 is typical. On completion of the integration period, the voltage V in Figure 3 is directly proportional to the input signal.

**Phase 3, Reference Integrate.** At the beginning of this phase, the integrator input is switched from V<sub>IN</sub> to V<sub>REF</sub>. The polarity of the reference is determined during Phase 2 such that the integrator discharges back towards zero. The number of clock pulses counted between the beginning of this cycle and the time when the integrator output passes through zero is a digital measure of the magnitude of V<sub>IN</sub>.

The beauty of the dual slope technique is that the theoretical accuracy depends only on the absolute value of the reference and the equality of the individual clock pulses within a given conversion cycle. The latter can easily be held to 1 part in 106, so in practical terms the only critical component is the reference. Changes in the value of other components such as the integration capacitor or the comparator input offset voltage have no effect, provided they don't change during an individual conversion cycle. This is in contrast to Successive Approximation converters which rely on matching a whole string of resistor values for quantization.

In a very real sense the designer is presented with a near perfect system; his job is to avoid introducing additional error sources in turning this textbook circuit into a real piece of hardware. From the foregoing discussion, it might be assumed that designing a high performance dual-slope converter is as easy as falling off the proverbial log. This is not true, however, because in a practical circuit a host of pitfalls must be avoided. These include the non-ideal characteristics of FET switches and capacitors, and the switching delay in the zero crossing detector.

## Analyzing the Errors

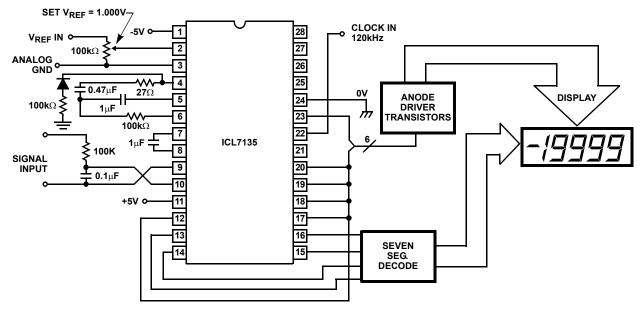

At this point it is instructive to perform a detailed error analysis of a representative dual slope circuit, Intersil's ICL7135. This is a  $4^{1}/_{2}$ -digit design, as shown in Figure 4. The error analysis which follows relates to this chip - however, the principles behind the analysis apply to most integrating converters.

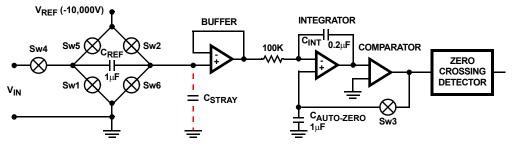

The analog section of the converter is shown in Figure 5. Typical values are shown for 120kHz clock and 3 measurements/second. Each measurement is divided into three parts. In part 1, the auto-zero FET switches 1, 2 and 3 are closed for 10,000 clock pulses. The reference capacitor is charged to  $V_{REF}$  and the auto-zero capacitor is charged to the voltage that makes dV/dt of the integrator equal to zero. In each instance the capacitors are charged for 20 or more time constants such that the voltage across them is only limited by noise.

In the second phase, signal integrate, switches 1, 2 and 3 are opened and switch 4 is closed for 10,000 clock pulses. The integrator capacitor will ramp up at a rate that is proportional to  $V_{IN}$ . In the final phase, de-integrate, switch 4 is opened and, depending on the polarity of the input signal, switch 5 or 6 is closed. In either case the integrator will ramp down at a rate that is proportional to  $V_{REF}$ . The amount of time, or number of clock pulses, required to bring the integrator back to its auto-zero value is 10,000

Of course, this is a description of the "ideal" cycle. Errors from this ideal cycle are caused by:

- 1. Capacitor droop due to leakage.

- 2. Capacitor voltage change due to charge "suck-out" (the reverse of charge injection) when the switches turn off.

- 3. Nonlinearity of buffer and integrator.

- 4. High-frequency limitations of buffer, integrator and comparator.

- 5. Integrating capacitor nonlinearity (dielectric absorption).

- 6. Charge lost by  $C_{REF}$  in charging  $C_{STRAY}$ .

Each of these errors will be analyzed for its error contribution to the converter.

FIGURE 4. THE ICL7135 FUNCTIONAL DIAGRAM

FIGURE 5. ANALOG SECTION OF A DUAL SLOPE CONVERTER

### Capacitor Droop Due to Leakage

Typical leakage (IDOFF) of the switches at normal operating voltage is 1pA each and 2pA at each input of the buffer and integrator op amps. In terms of offset voltage caused by capacitor droop, the effect of the auto-zero and reference capacitors is differential, i.e., there is no offset if they droop an equal amount. A conservative typical effect of droop on offset would be 2pA discharging  $1\mu F$  for 83ms (10,000 clock periods), which amounts to an averaged equivalent of 083µV referred to the input. The effect of the droop on rollover error (difference between equal positive and negative voltages near full scale) is slightly different. For a negative input voltage, switch 5 is closed for the de-integrate cycle. Thus the reference capacitor and auto-zero capacitor operate differentially for the entire measurement cycle. For a positive voltage, switch 6 is closed and the differential compensation of the reference capacitor is lost during de-integrate. A typical contribution to rollover error is 3pA discharging 1µF capacitor for 166ms, equivalent to 0.249µV when averaged. These numbers are certainly insignificant for room temperature

leakages but even at 100<sup>o</sup>C the contributions should be only 15 $\mu$ V and 45 $\mu$ V respectively. A rollover error of 45 $\mu$ V is less than 0.5 counts on this 20,000 count instrument.

#### Charge "Suck-Out" When the Switches Turn-Off

There is no problem in charging the capacitors to the correct value when the switches are on. The problem is getting the switches off without changing this value. As the gate is driven off, the gate-to-drain capacitance of the switch injects a charge on the reference or auto-zero capacitor, changing its value. The net charge injection of switch 3 turning off can be measured indirectly by noting the offset resulting by using a 0.01µF auto-zero capacitor instead of 1.0µF. For this condition the offset is typically  $250\mu$ V, and since the signal ramp is a straight line instead of a parabola the main error is due to charge injection rather than leakage. This given a net injected charge of 2.5pC or an equivalent  $C_{qd}$  of 0.16pF. The effect of switches 1, 2, 4, 5 and 6 are more complicated since they depend on timing and some switches are going on while others are going off. A substitution of an 0.01µF capacitor for reference capacitor gives less than 100µV offset error. Thus, a

conservative typical offset error for a  $1.0\mu$ F capacitor is  $2.5\mu$ V. There is no contribution to rollover error (independent of offset). Also this value does not change significantly with temperature.

#### Nonlinearity of Buffer and Integrator

In this converter, since the signal and reference are injected at the same point, the gain of the buffer and integrator are not of first-order importance in determining accuracy. This means that the buffer can have a very poor CMRR over the input range and still contribute zero error as long as it is constant, i.e., offset changes linearly with common mode voltage. The first error term is the nonlinear component of CMRR. Careful measurement of CMRR on 30 buffers indicated rollover errors from  $5\mu$ V to  $30\mu$ V. The contribution of integrator nonlinearity is less than  $1\mu$ V in each case.

#### High Frequency Limitations of Amplifiers

For a zero input signal, the buffer output will switch from zero to  $V_{REF}$  (1.0V) in 0.5µs with an approximately linear response. The net result is to lose 0.25µs of de-integrate period. For a 120kHz clock, this is 3% of a clock pulse or 3µV. This is not an offset error since the delay is equal for both positive and negative references. The net result is the converter would switch from 0 to 1 at 97µV instead of 100µV in the ideal case.

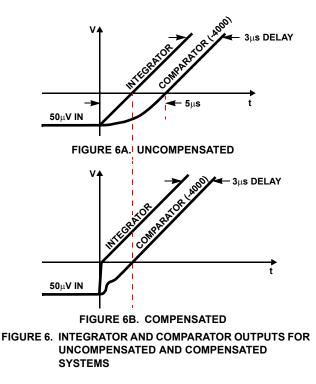

A much larger source of delay is the comparator which contributes 3µs. At first glance, this sounds absolutely ridiculous compared to the few tens of nanoseconds delay of modern IC comparators. However, they are specified with 2 to 10mV of overdrive. By the time the ICL7135 comparator gets 10mV of overdrive, the integrator will have been through zerocrossing or 20 clock pulses! Actually, the comparator has a 300MHz gain-bandwidth product which is comparable to the best ICs. The problem is that it must operate on  $30\mu$ V of overdrive instead of 10mV. Again, this delay causes no offset error but means the converter switches from 0 to 1 at 60uV. from 1 to 2 at  $160\mu$ V, etc. Most users consider this switching at approximately <sup>1</sup>/<sub>2</sub> LSB more desirable than the "so-called ideal" case of switching at  $100\mu$ V. If it is important that switching occur at  $100\mu$ V, the comparator delay may be compensated by including a small value resistor ( $\cong 20\Omega$ ) in series with the integration capacitor. (Further details of this technique are given on page 5 under the heading "Maximum Clock Frequency".) The integrator time delay is less than 200ns and contributes no measurable error.

#### Integrating Capacitor Dielectric Absorption

Any integrating A/D assumes that the voltage change across the capacitor is exactly proportional to the integral of the current into it. Actually, a very small percentage of this charge is "used up" in rearranging charges within the capacitor and does not appear as a voltage across the capacitor. This is dielectric absorption. Probably the most accurate means of measuring dielectric absorption is to use it in a dual-slope A/D converter with  $V_{IN} = V_{REF}$ . In this mode, the instrument should read 1.0000 independent of other component values. In very careful measurements where zero-crossings were observed in order to extrapolate a fifth digit and all delay errors were calculated out, polypropylene capacitors gave the best results. Their equivalent readings were 0.99998. In the same test polycarbonate capacitors typically read 0.9992, polystyrene 0.9997. Thus, polypropylene is an excellent choice since they are not expensive and their increased temperature coefficient is of no consequence in this circuit. The dielectric absorption of the reference and auto-zero capacitors are only important at power-on or when the circuit is recovering from an overload. Thus, smaller or cheaper capacitors can be used if very accurate readings are not required for the first few seconds of recovery.

#### Charge Lost by CREF in Charging CSTRAY

In addition to leakage and switching charge injection, the reference capacitor has a third method of losing charge and, therefore, voltage. It must charge  $C_{STRAY}$  as it swings from 0 to  $V_{IN}$  to  $V_{REF}$  (Figure 5). However,  $C_{STRAY}$  only causes an error for positive inputs. To see why, let's look firstly at the sequence of events which occurs for negative inputs. During auto-zero  $C_{REF}$  and  $C_{STRAY}$  are both charged through the switches. When the negative signal is applied,  $C_{REF}$  and  $C_{STRAY}$  are in series and act as a capacitance divider. For  $C_{STRAY}$  are in series and act as a capacitance divider. For  $C_{STRAY}$  = 15pF, the divider ratio is 0.999985. When the positive reference is applied through switch #5, the same divider operates. As mentioned previously, a constant gain network contributes no error and, thus, negative inputs are measured exactly.

For positive inputs, the divider operates as before when switching from auto-zero to V<sub>IN</sub>, but the negative reference is applied by closing switch #6. The reference capacitor is not used, and therefore the equivalent divider network is 1.0000 instead of 0.999985. At full scale, this 15 $\mu$ V/V error gives a 30 $\mu$ V rollover error with the negative reading being 30 $\mu$ V too low. Of course for smaller C<sub>STRAY</sub>, the error is proportionally less.

#### Summary

Error analysis of the circuit using typical values shows four types of errors. They are (1) an offset error of  $2.5\mu$ V due to charge injection, (2) a full scale rollover error of  $30\mu$ V due to C<sub>STRAY</sub>, (3) a full scale rollover error of 5 to  $30\mu$ V due to buffer nonlinearity and (4) a delay error of  $40\mu$ V for the first count. These numbers are in good agreement with actual results observed for the ICL7135. Due to peak-to-peak noise of  $20\mu$ V around zero, it is possible only to say that any offsets are less than  $10\mu$ V. Also, the observed rollover error is typically  $1/_2$  count ( $50\mu$ V) with the negative reading larger than the positive. Finally, the transition from a reading of 0000 to 0001 occurs at  $50\mu$ V.

These figures illustrate the very high performance which can be expected from a well designed dual-slope circuit performance figures which can be achieved with no tricky 'tweaking' of component values. Furthermore, the circuit

includes desirable convenience features such as auto-zero, auto-polarity and a single reference.

## Maximum Clock Frequency

Because of the  $3\mu$ s delay in the comparator, the maximum recommended clock frequency is 160kHz. In the error analysis it was shown that under these conditions half of the first reference integrate period is lost in delay. This means that the meter reading will change from 0 to 1 at  $50\mu$ V, from 1 to 2 at  $150\mu$ V, etc. As was noted earlier, most users consider this transition at midpoint to be desirable. However, if the clock frequency is increased appreciably above 160kHz, the instrument will flash 1 on noise peaks even when the input is shorted.

The clock frequency may be extended above 160kHz, however, by using a low value resistor in series with the integration capacitor. The effect of the resistor is to introduce a small pedestal voltage on to the integrator output at the beginning of the reference integrate phase (Figure 6). By careful selection of the ratio between this resistor and the integrating resistor (a few tens of ohms in the recommended circuit), the comparator delay can be compensated and the maximum clock frequency extended by approximately a factor of 3. At higher frequencies, ringing and second order breaks will cause significant nonlinearities in the first few counts of the instrument.

## Noise

The peak-to-peak noise around zero is approximately  $20\mu$ V (peak-to-peak value not exceeded 95% of the time). Near full scale, this value increases to approximately  $40\mu$ V.

Since much of the noise originates in the auto-zero loop, some improvement in noise can be achieved by putting gain in the buffer. A gain of about 5X is optimum. Too much gain will cause the auto-zero switch to misbehave, because the amplified  $V_{OS}$  of the buffer will exceed the switch operating range.

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard" Computers: office equipment: communications equipment: test and measurement equipment: audio and visual equipment: home electronic appliances; machine tools; personal electronic equipment: industrial robots: etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics oroducts outside of such specified ranges

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Plea e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### **Renesas Electronics Corporation**

http://www.renesas.com

SALES OFFICES Refer to "http://www.renesas.com/" for the latest and detailed information Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Miliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tei: +44-1628-651-700, Fax: +44-1628-651-804 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germar Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tei: +822-558-3737, Fax: +822-558-5338