## Introduction

This application note describes the procedure used within the Timing and Synchronization (TSD) division of IDT to analyze the PSNR for its devices. Power supply noise rejection (PSNR) is a measurement of how well a circuit rejects noise from various frequencies which are coupled into the power supply. In actual high speed analog and digital circuitry, the power supply pins are vulnerable to random noise. Most customer designs use linear voltage regulators or switching voltage regulators as the power supply for ICs. Linear regulators will almost always get input voltage from a switching DC/DC converter. Therefore, power supply noises in a customer board typically come from the switching noise of the power supply and coupling from other high-frequency sections of the circuit board.

Many of the problems facing PCB designers today are related to power supply noise. There are guidelines that can be used to solve simple issues. For more complex issues, a better understanding and consideration of all the parameters will be required to provide a clean solution. For this reason, it is essential to understand the PSNR of the clock devices. This can assist in designing the correct bypassing and decoupling for the system.

## Power Supply Filtering Topology

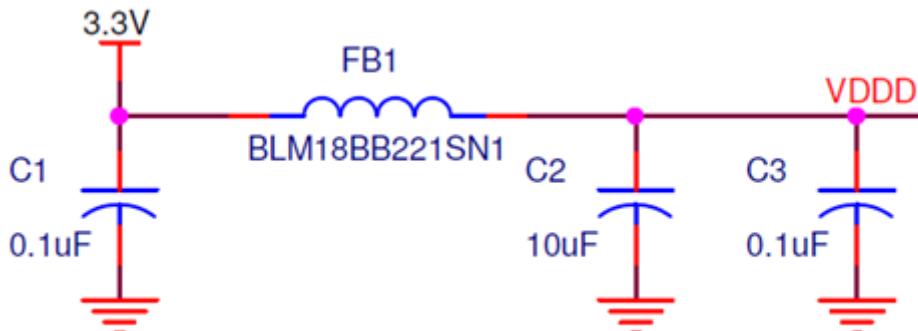

Figure 1 is a simplified 3-component power supply filtering circuit that is recommended for a power rail. It consists of a  $0.1\mu\text{F}$  capacitor (C1) a ferrite bead (FB1) and a  $10\mu\text{F}$  capacitor (C2). While C1, FB1 and C2 are for the power rail, C3 is used for each power pin supplied by this rail. If a power rail supplies multiple power pins, each power pin will have a  $0.1\mu\text{F}$  capacitor for decoupling.

**Figure 1. Power Supply Filtering Circuit Topology**

The ferrite bead above is any surface-mount bead with sufficient current rating for the circuits supplied. Please refer to AN-805 for ferrite bead recommendations.

## Effectiveness Study of the Noise Rejection Circuits

The frequency response is used to study the attenuation capability the above circuit demonstrates on different frequency elements of a signal (noise). In the following sections of this application note, frequency response of the circuit is plotted by sweeping C1, C2 and C3, respectively:

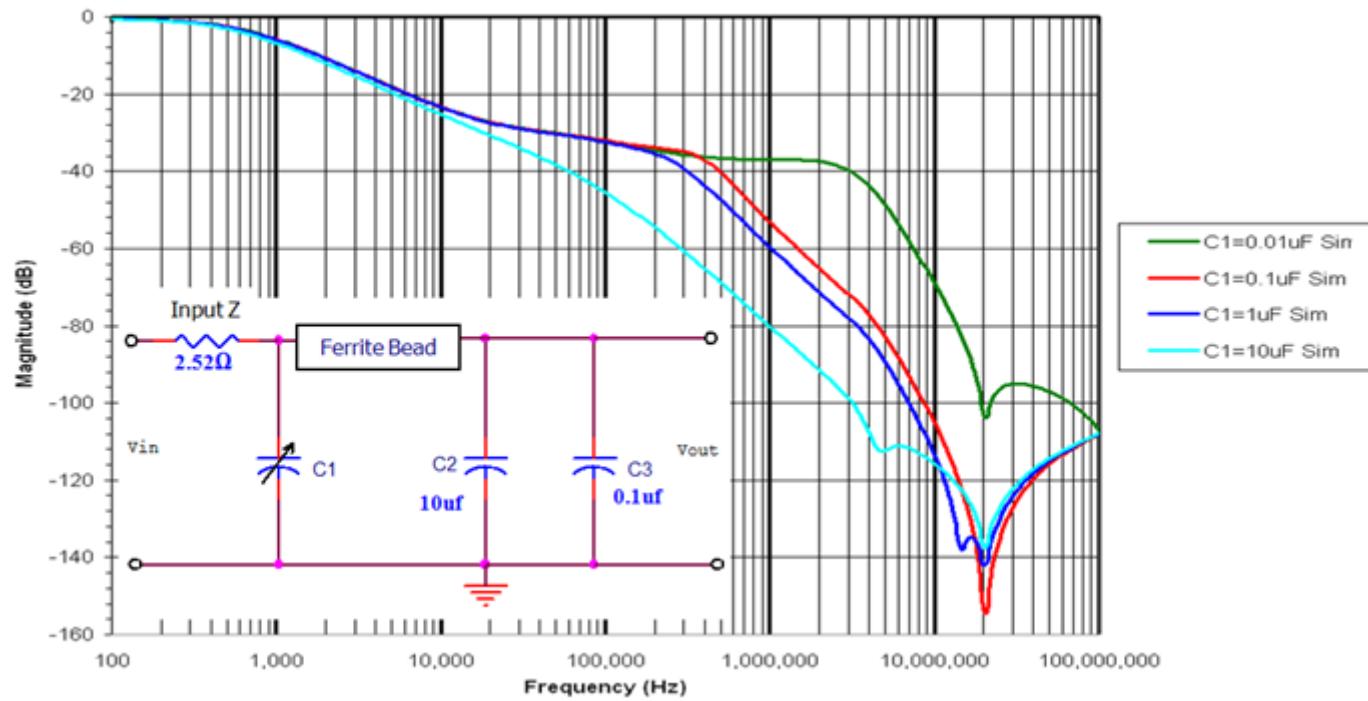

*Figure 2: Sweeping C1 while keeping C2 =  $10\mu\text{F}$ , C3 =  $0.1\mu\text{F}$  – Optimal value for C1 is  $0.1\mu\text{F}$*

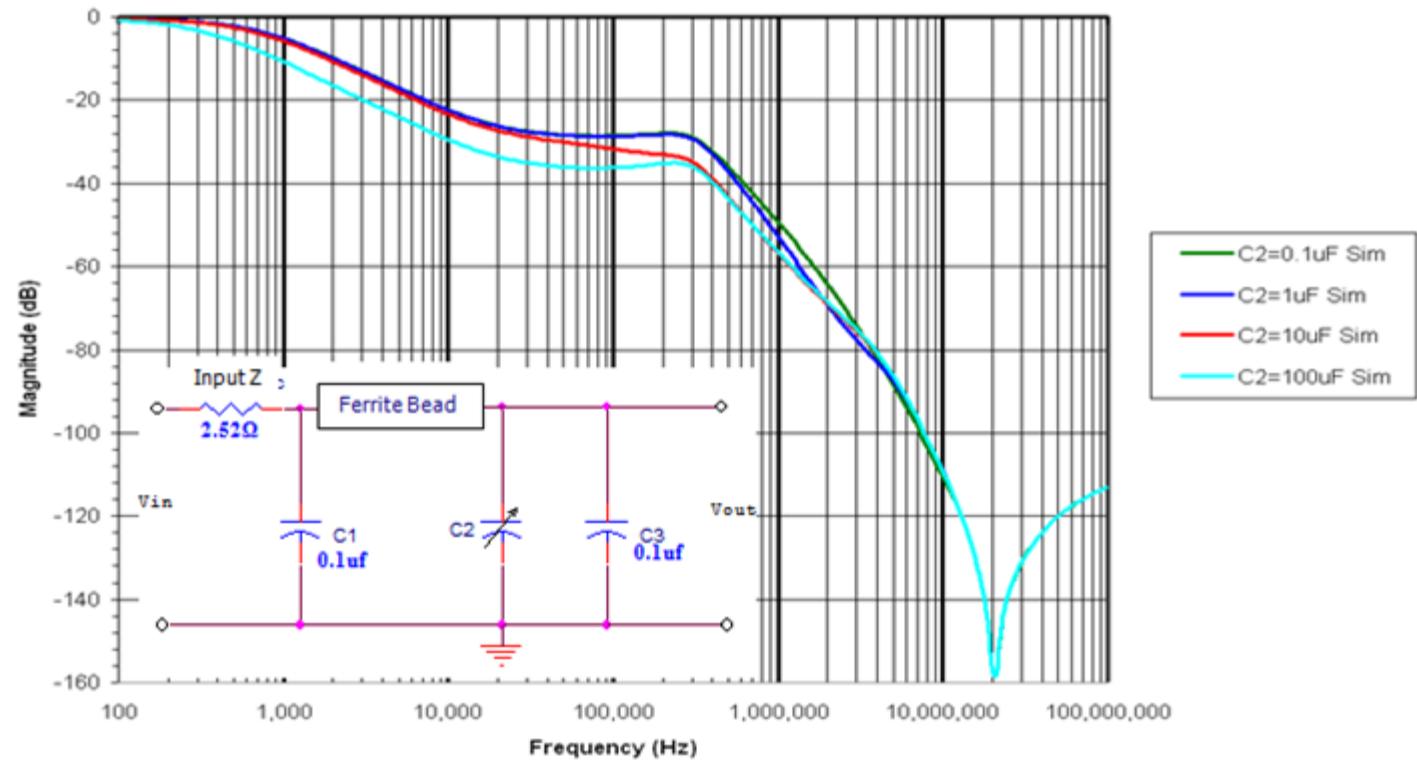

*Figure 3: Sweeping C2 while keeping C1 =  $0.1\mu\text{F}$ , C3 =  $0.1\mu\text{F}$  – Optimal value for C2 is  $10\mu\text{F}$*

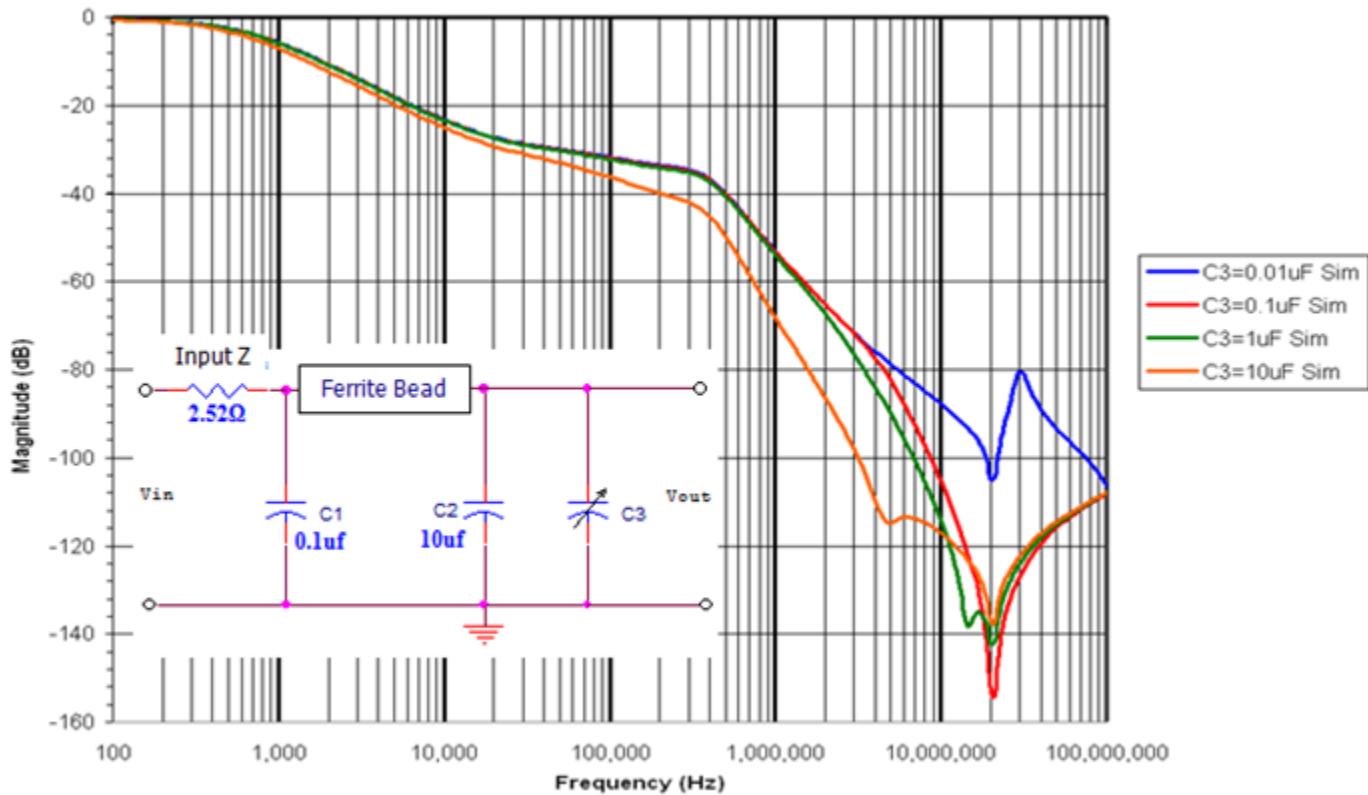

*Figure 4: Sweeping C3 while keeping C1 =  $0.1\mu\text{F}$ , C2 =  $10\mu\text{F}$  – Optimal value for C3 is  $0.1\mu\text{F}$*

**Figure 2. Sweeping C1 while keeping C2 = 10 $\mu$ F, C3 = 0.1 $\mu$ F****Figure 3. Sweeping C2 while keeping C1 = 0.1 $\mu$ F, C3 = 0.1 $\mu$ F**

**Figure 4. Sweeping C3 while keeping C1 = 0.1 $\mu$ F, C2 = 10 $\mu$ F**

## Power Supply Noise Rejection Measurements

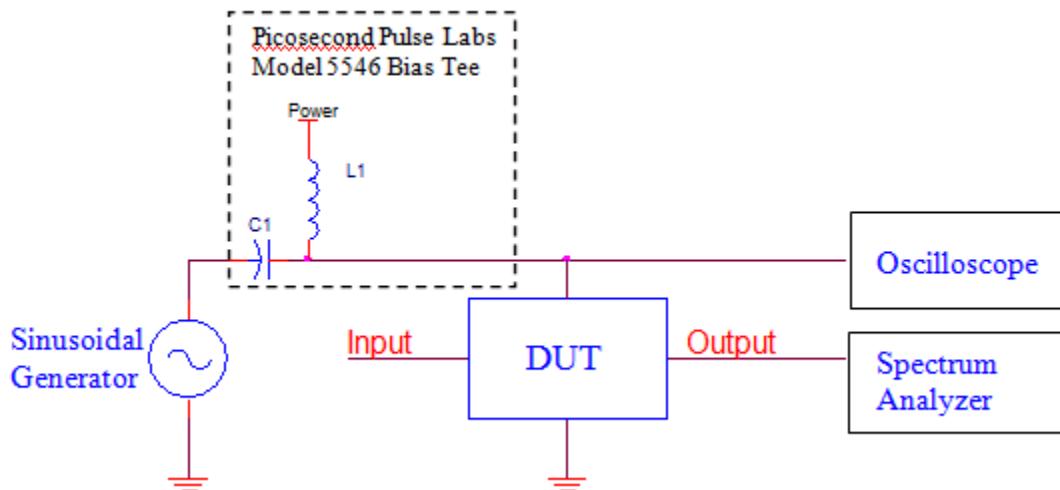

PSNR is measured by injecting a sinusoidal signal of a known amplitude and frequency onto the various power supply pins of the devices. Many of the devices in the TSD portfolio contain multiple power supply pins. The two of interest are the core power pin and the analog power pin. The core power pin primarily supplies voltage to all PLL peripherals while the analog power pin supplies the voltage to the PLL. Each power pin should be analyzed independently, and noise should be applied to one power pin at a time.

The technique used for applying the injected frequency into the device supply uses an inductor which presents a high AC impedance back to the supply. Then a signal from a generator is injected through a capacitor after the inductor at the pin of the DUT. Refer to Figure 1. Both the input and output should be monitored with an oscilloscope and Spectrum analyzer. The oscilloscope is used to ensure the signal amplitude while the spectrum analyzer is used to measure the deterministic jitter.

**Figure 5. PSNR Schematic**

In order to analyze the performance of the device, initially all external bypass and decoupling capacitors should be removed. A 50mV signal is swept from a start to a stop frequency. The 1kHz to 50MHz sweep range covers most of standard frequencies which occur in typical applications.

**Table 1. PSNR Configuration**

| Power Pin      | Temperature (°C) | Signal Amplitude (mV) | Start Frequency (kHz) | Stop Frequency (MHz) |

|----------------|------------------|-----------------------|-----------------------|----------------------|

| Core Voltage   | 25               | 50                    | 1                     | 50                   |

| Analog Voltage | 25               | 50                    | 1                     | 50                   |

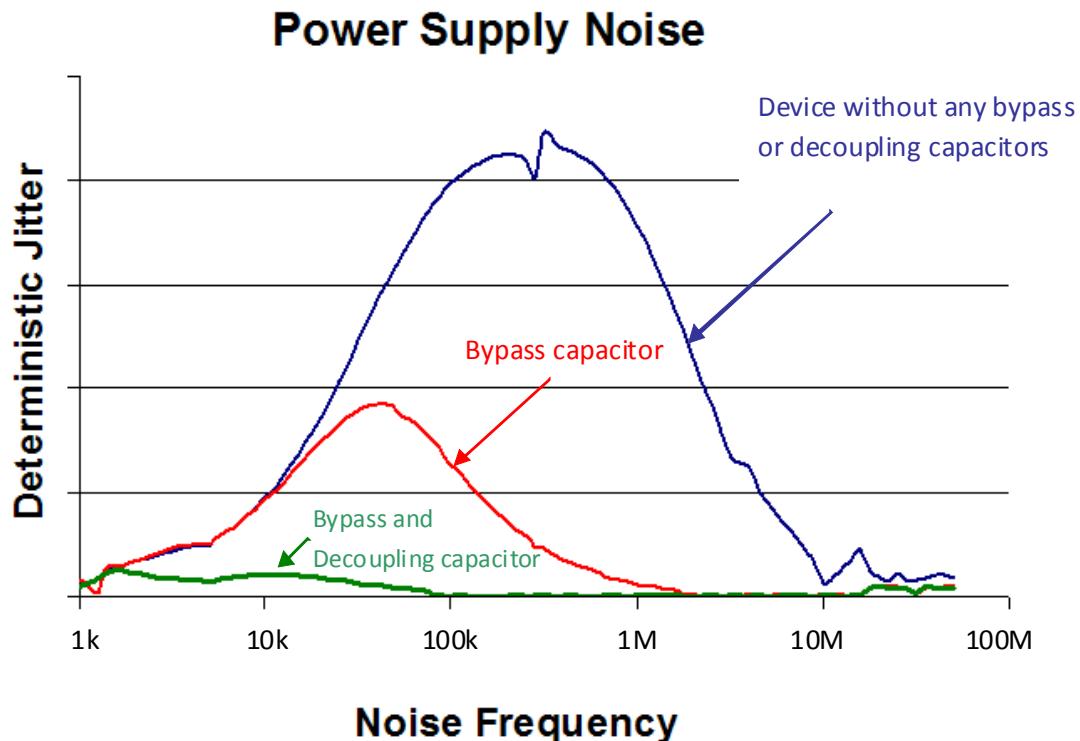

The following graph represents three tests of PSNR data. First, the device was swept without any decoupling or bypass capacitors. Notice, the deterministic jitter peaked at approximately 400kHz. Next, a 0.1 $\mu$ F bypass capacitor was added and the noise decreased significantly. Lastly, in addition to the 0.1 $\mu$ F, a 10 $\mu$ F capacitor was added and majority of the noise is filtered. Refer to Figure 2.

In conclusion, the combination of a 0.1 $\mu$ F and 10 $\mu$ F capacitor will attenuate some of the noise generated by a switching power supplies. For many of the TSD devices, a power supply filter with a ferrite bead is recommended. This will attenuate noise between 100kHz and 600kHz.

**Figure 6. Deterministic Jitter versus Noise Frequency**

## Summary

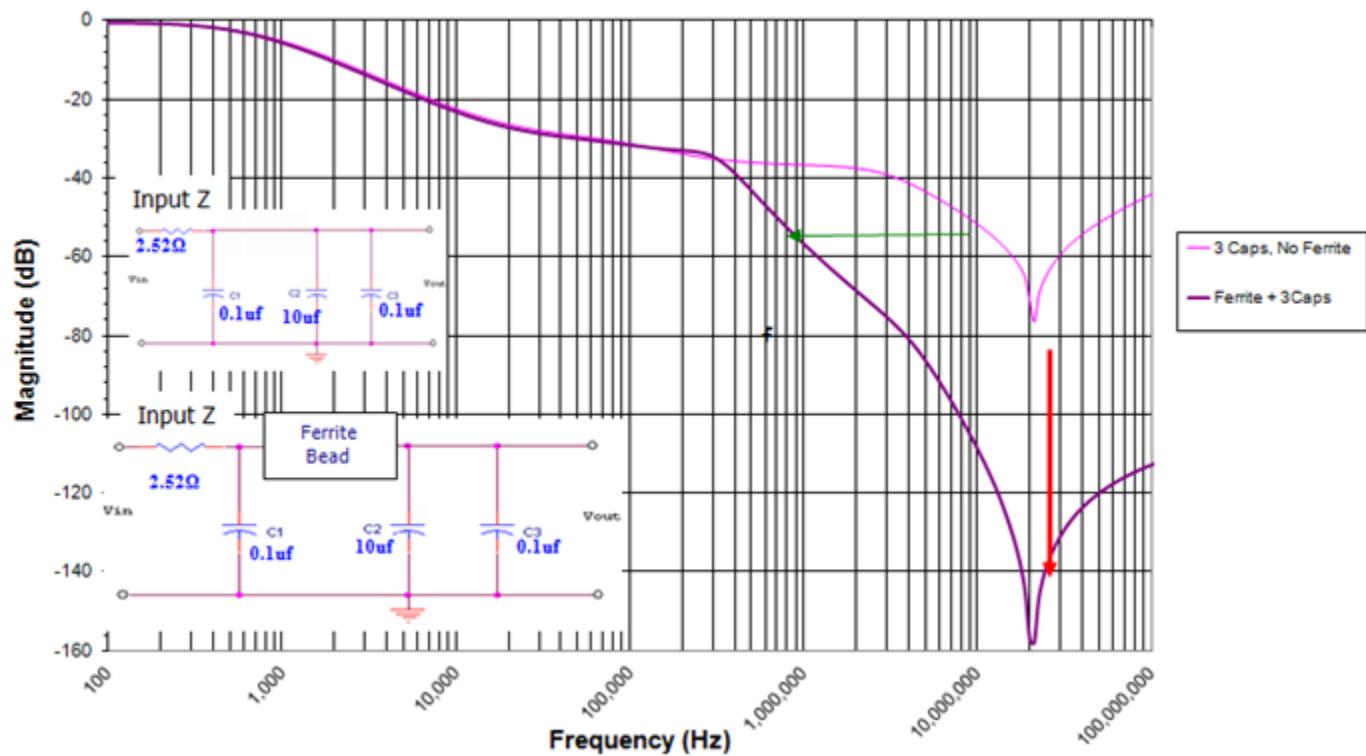

This application note proposes a simple power supply noise rejection topology consisting of two capacitors and a ferrite bead. By sweeping the values of the capacitors, a noise-filtering circuit with recommended component values is provided in Figure 1. The filter performance is designed for a wide range of noise frequencies. This low-pass filter starts to attenuate noise at approximately 10kHz. If a specific frequency noise component is known, such as switching power supply frequencies, it is recommended that component values be adjusted and if required, additional filtering be added. Additionally, good general design practices for power plane voltage stability suggests adding bulk capacitance in the local area of all devices.

Overall, this filtering circuit provides significant noise attenuation in frequency range of 10KHz to 100MHz compared with a 0.1 $\mu$ F-only filtering. Figure 7 shows the comparison between a 0.1 $\mu$ F-only filter and Figure 1 filtering circuit.

**Figure 7. Noise Rejection Comparison: 0.1 $\mu$ F Capacitor Only vs Filtering Circuit by Figure 1**

## Notice

1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

(Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

(Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Disclaimer Rev.5.0-1)

## Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

## Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

[www.renesas.com/contact/](http://www.renesas.com/contact/)

## Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.