## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## RENESAS

## APPLICATION NOTE

# 78K/IV SERIES 16-BIT SINGLE-CHIP MICROCOMPUTER

**SOFTWARE BASICS**

μPD784026 SUBSERIES μPD784915 SUBSERIES

The export of these products from Japan is regulated by the Japanese government. The export of some or all of these products may be prohibited without governmental license. To export or re-export some or all of these products from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

## The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customer must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices in "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact NEC Sales Representative in advance.

Anti-radioactive design is not implemented in this product.

## **PREFACE**

## **Target Users**

This application note is for engineers who wish to understand 78K/IV Series devices and design application programs using these devices.

#### 78K/IV Series

• μPD784026 Subseries: μPD784020, 784021, 784025, 784026, 78P4026

• μPD784915 Subseries: μPD784915 Note, 78P4916 Note

Note Under development

## Objective

The purpose of this application note is to use program examples to help users to understand the basic functions of 78K/IV Series devices.

The program and hardware structures published here are illustrative examples and are not designed for mass production.

## Organization

This application note describes the basic numeric operation programs.

## **Application Area**

The 78K/IV Series devices have a 1-MB program memory space and are capable of high-speed instruction execution and low-voltage operation, making them suitable for a wide range of applications, including the following:

Portable telephonesCD-ROMsVCRsPrinters

HDDs

Audio systems, etc.

Cameras

## Legend

The symbols and notations used in this manual have the following meanings:

Significance of the data description: The left side is high-order data and the right

side is low-order data.

Active-low description :  $\overline{xxx}$  (line above pin and signal names)

Note : Explanation of the note attached to the text

Caution : Contents that should be read carefully

Remark : Supplemental explanation of the text

Number descriptions : Binary numbers ... xxxxxxxxB

: Decimal numbers ... xxxx

: Hexadecimal numbers ... xxxxH

Easily confused characters : 0 (zero), O (oh)

: 1 (one), I (lowercase letter), I (uppercase

letter)

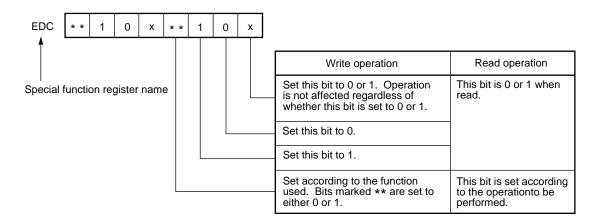

## Special Function Register (SFR) Description

Do not attempt to enter a combination of codes indicated in "Setting Prohibited" in the register charts provided throughout this document.

## Example of Special Function Register (SFR) Description

**Remark** Throughout this application note, those register bits that must be set are indicated by shading. When using a register, refer to the provided example as necessary.

**Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

## • Documents common to 78K/IV series devices

| Document name                     | Document number |          |

|-----------------------------------|-----------------|----------|

|                                   | Japanese        | English  |

| User's Manual, Instruction        | IEU-844         | IEU-1386 |

| Application Note, Software Basics | This manual     | _        |

| Instruction Table                 | IEM-5580        | _        |

| Instruction Set                   | IEM-5572        | _        |

| 78K Series Selection Guide        | IF-258          | IF-1141  |

| Development Tool Selection Guide  | EF-219          | EF-1111  |

## • Individual documents

## μ**PD784026 subseries**

| Document name                                         | Documer        | Document number |  |

|-------------------------------------------------------|----------------|-----------------|--|

| Document name                                         | Japanese       | English         |  |

| μPD784020, 784021 Data Sheet                          | IC-8776        | IP-3234         |  |

| μPD784025, 784026 Data Sheet                          | IC-8722        | IP-3230         |  |

| μPD78P4026 Data Sheet                                 | IC-8734        | IP-3231         |  |

| μPD784026 Subseries Special Function Register Table   | IEM-5579       | _               |  |

| μPD784026 Subseries User's Manual, Hardware           | IEU-850        | IEU-1379        |  |

| μPD784026 Subseries Application Note, Hardware Basics | In preparation | _               |  |

## $\mu$ PD784915 subseries

| Document name                                       | Document number |         |

|-----------------------------------------------------|-----------------|---------|

| Document name                                       | Japanese        | English |

| μPD784915 Product Information                       | IP-9130         | _       |

| μPD78P4916 Product Information                      | IP-9178         | _       |

| μPD784915 Subseries Special Function Register Table | IEM-5602        | _       |

| μPD784915 Subseries User's Manual, Hardware         | IEU-850         | _       |

Caution The related documents described above may be changed without notice. Always use the newest document when designing.

[MEMO]

Phase-out/Discontinued

## **CONTENTS**

| CHAPTER 1 | GEN              | IERAL                                                 | 1   |

|-----------|------------------|-------------------------------------------------------|-----|

|           | 1.1              | READING THIS DOCUMENT                                 | 1   |

|           | 1.2              | USING APPLICATION PROGRAMS                            | 2   |

|           | 1.3              | FEATURES OF 78K/IV SERIES DEVICES                     | 2   |

|           | 1.4              | PROGRAM                                               | 3   |

| CHAPTER 2 | BIN              | ARY OPERATIONS                                        | 5   |

|           | 2.1              | BINARY ADDITION OF SIGNED 32 BITS + 32 BITS           | 5   |

|           | 2.2              | BINARY SUBTRACTION OF SIGNED 32 BITS - 32 BITS        | 10  |

|           | 2.3              | BINARY MULTIPLICATION OF SIGNED 32 BITS x 32 BITS     | 15  |

|           | 2.4              | BINARY DIVISION OF SIGNED 32 BITS/32 BITS             | 24  |

| CHAPTER 3 | DEC              | CIMAL OPERATIONS                                      | 35  |

|           | 3.1              | DECIMAL ADDITION OF SIGNED 8 DIGITS + 8 DIGITS        | 36  |

|           | 3.2              | DECIMAL SUBTRACTION OF SIGNED 8 DIGITS - 8 DIGITS     | 45  |

|           | 3.3              | DECIMAL MULTIPLICATION OF SIGNED 8 DIGITS x 8 DIGITS  | 49  |

|           | 3.4              | DECIMAL DIVISION OF SIGNED 8 DIGITS/8 DIGITS          | 56  |

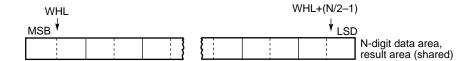

| CHAPTER 4 | SHIFT PROCESSING |                                                       | 65  |

|           | 4.1              | SHIFTING N-BYTE DATA 1 BYTE TO THE RIGHT              | 65  |

|           | 4.2              | SHIFTING N-DIGIT DATA 1 BYTE TO THE RIGHT             |     |

|           |                  | (DECIMAL 1/10 PROCESSING)                             | 68  |

| CHAPTER 5 | BLO              | OCK TRANSFER PROCESSING                               | 71  |

|           | 5.1              | BLOCK TRANSFER PROCESSING OF FIXED BYTE DATA          | 71  |

|           | 5.2              | BLOCK TRANSFER PROCESSING OF BYTE DATA                | 73  |

|           | 5.3              | BLOCK COMPARISON (COINCIDENCE DETECTION) OF BYTE DATA | 75  |

| CHAPTER 6 | DAT              | A EXCHANGE PROCESSING                                 | 77  |

|           | 6.1              | CONVERTING A HEXADECIMAL NUMBER (HEX) TO A            |     |

|           |                  | DECIMAL NUMBER (BCD)                                  | 77  |

|           | 6.2              | CONVERTING A DECIMAL NUMBER (BCD) TO A                |     |

|           |                  | HEXADECIMAL NUMBER (HEX)                              | 83  |

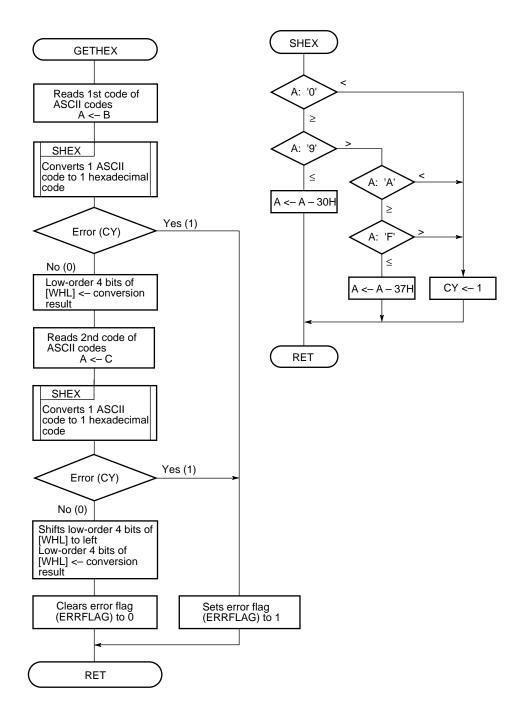

|           | 6.3              | CONVERTING AN ASCII CODE TO A HEXADECIMAL CODE        | 89  |

|           | 6.4              | CONVERTING A HEXADECIMAL CODE TO AN ASCII CODE        | 94  |

| CHAPTER 7 | DAT              | A PROCESSING                                          | 99  |

|           | 7.1              | SORTING 1-BYTE DATA                                   | 99  |

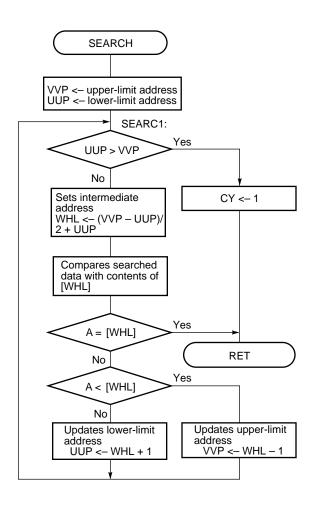

|           | 7.2              | SEARCHING FOR DATA                                    | 104 |

## **LIST OF FIGURES**

| Figure No. | Title                               | Page |

|------------|-------------------------------------|------|

| 2-1        | Expressing Binary Numbers           | £    |

| 2-2        | Algorithm for Binary Multiplication | 16   |

| 2-3        | Algorithm for Binary Division       | 27   |

| 3-1        | Expressing Decimal Numbers          | 35   |

## **CHAPTER 1 GENERAL**

#### 1.1 READING THIS DOCUMENT

This application note introduces examples of programs for basic binary and decimal arithmetic operations, such as addition, subtraction, multiplication, and division, as well as data exchange and data transfer as subroutine programs. The algorithms of these programs are described so that they can be used as user programs.

The program examples given in this document are presented in the following format:

## (1) Outline of processing

Outlines the processing performed by the program.

## (2) RAM area

Describes the RAM area used by the program.

Note that if a work area is used as the RAM area, its contents will be undefined after the program has been executed.

## (3) Registers

Describes the registers used in the program.

To protect the contents of registers that have already been used by another program, save the contents of those registers by switching the register bank before executing the described program.

## (4) Input

Describes the arguments that must be input when executing the program.

## (5) Output

Describes the arguments that are output after the program has been executed.

## (6) Program description

Describes the algorithm on which the program is based.

Also refer to the flowchart and program listing.

## (7) Flowchart

Illustrates the algorithm of the program by means of a flowchart.

## (8) Program listing

Presents a listing of the program.

All program listing are described as source programs. The address, therefore, differs depending on the link condition.

The programs shown in this application note are provided only as examples and their actual operation is not guaranteed.

## 1.2 USING APPLICATION PROGRAMS

Basically, use the application programs presented in this document as specified in the description of each application program. Some application programs call other application programs. In this case, link the programs by means of a linker (LK78K/IV) and by referring to the description. A work area may also be necessary. Reserve a RAM area according to the description and make a public declaration.

#### 1.3 FEATURES OF 78K/IV SERIES DEVICES

As the functions of microcomputer-based products have improved and their cost fallen, the demand for microcomputers that can satisfy these mutually contradicting requirements — more sophisticated functions at lower cost — has steadily increased. In addition, with the explosive growth in portable systems such as cellular telephones, the demand for microcomputers that can operate at lower voltages while dissipating less power has also grown.

NEC's 78K/IV Series of 16-bit single-chip microcomputers was developed in response to these market demands.

The features of the 78K/IV series of microcomputers are as follows:

## (1) Compatibility with existing models

The 78K/IV Series microcomputers maintain, at source level, upward compatibility with the 8-bit models (78K/0, 78K/I, and 78K/II Series) and 16-bit models (78K/III Series) of the 78K Series, thus protecting your investment in software.

## (2) Wide linear memory space

Up to 1 MB of program memory and 16 MB of data memory are supported.

## (3) Low voltage, low current dissipation

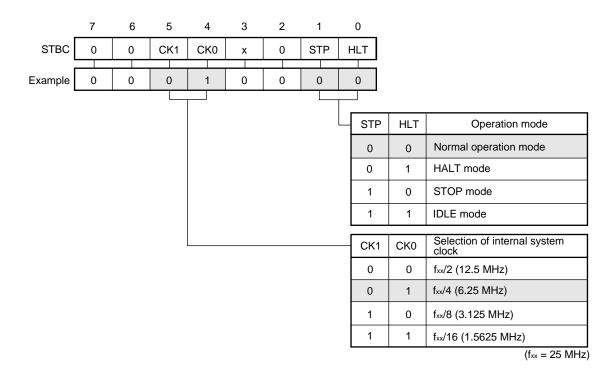

The operating voltage ranges from 2.7 to 5.5 V, so that 78K/IV Series devices can operate at very low voltages. In addition, three standby modes, STOP, IDLE, and HALT, and a function for dividing the clock to be supplied to the CPU are provided to enable power management according to the operating status.

### (4) High-speed multiplication and division instructions

High-speed multiplication and division instructions are provided to support complicated control systems and high-accuracy control algorithms.

## (5) Powerful interrupt response

For control applications, the way in which a microcomputer responds to an interrupt is particularly important. The 78K/IV Series supports the following three interrupt functions:

- · Vector interrupt

- Context switching

- Macro service

## (6) Support of high-level language (C)

An enhanced instruction set for a C compiler, an efficient C compiler, and easy-to-use source debugging environments are supported.

## (7) Easy-to-use tools

Easy-to-use tools, such as an assembler package, C compiler, in-circuit emulator, and integrated debugger are also supported.

#### 1.4 PROGRAM

Some example programs presented in this application note require that the results of operations and numeric data be written into RAM. When referring to the programs in this application note, therefore, reserve the necessary amount of RAM by using the program below.

When using programs that perform binary division, decimal addition, decimal subtraction, and decimal division, add the processing to be performed in the case of an error, as necessary.

```

PUBLIC BMLCND, BMLIER, BUFRAM, BRSLT

; binary multiply

PUBLIC DEND, DVISOR, DRMND

; binary division

PUBLIC DMLCND, DMLIER, DRSLT, CARRY

; decimal multiply

PUBLIC DIVSOR, DIVIND, RMIND

; decimal division

PUBLIC SFLAG

PUBLIC ERRFLAG

; error flag

BSEG

; sin flag

SFLAG

DBIT

; error flag

ERRFLAG

DBIT

WORKSEG

DSEG saddr

binary multiply area

BMLCND: DS

BMLIER: DS

4

BUFRAM: DS

15

BRSLT: DS

8

```

```

binary division area

DEND: DS 4

DVISOR: DS

DRMND: DS

4

decimal multiply area

DMLCND: DS 4

DMLIER: DS 4

DRSLT: DS 8

CARRY: DS 1

4

;-----

decimal division

DIVSOR: DS 4

DIVIND: DS

RMIND: DS

4

CSEG

; if(error flag=1) then

BT ERRFLAG, $ERROR

; go to ERROR

ERROR:

; error routine

; Error processing. Prepare as

; necessary.

```

## **CHAPTER 2 BINARY OPERATIONS**

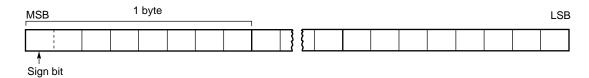

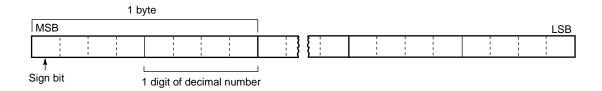

In binary operations, the most significant bit is used as a sign bit, the remaining bits expressing a numeric value. Negative numbers are expressed as a 2's complement.

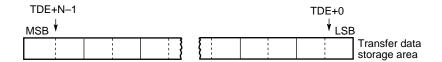

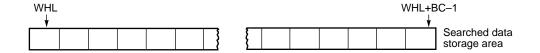

Figure 2-1. Expressing Binary Numbers

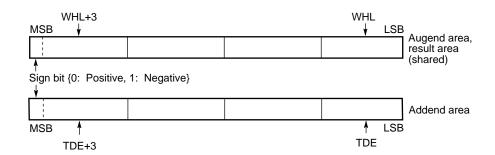

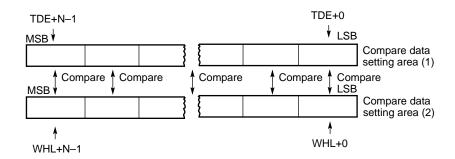

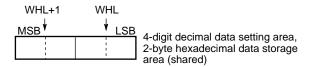

For binary operations, the data storage area used for the operation and the area storing the result of the operation are located in RAM.

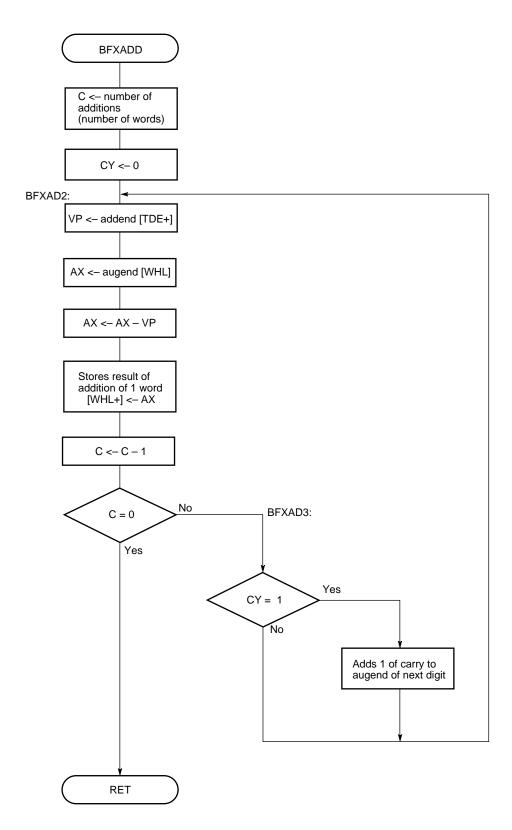

#### 2.1 BINARY ADDITION OF SIGNED 32 BITS + 32 BITS

## (1) Outline of Processing

This section presents an example program that adds a signed 32-bit augend to a 32-bit addend, then stores the result into a 32-bit result area (shared with the augend area).

## (2) RAM area

When the sign bit is (0): Positive (00000000H through 7FFFFFFH) When the sign bit is (1): Negative (FFFFFFFH through 80000000H)

## (3) Registers

AX, C, VP, TDE, and WHL registers

## (4) Input

Set the following addresses in the WHL and TDE registers.

WHL: Lowest address of the RAM area containing the 32-bit augend TDE: Lowest address of the RAM area containing the 32-bit addend

## (5) Output

The following contents are stored into the 4-byte RAM area indicated by the WHL register.

WHL to WHL+3: Stores the result of addition.

## (6) Program description

- (a) Sets the number of words to be manipulated in a counter (C register).

- (b) Clears the carry flag (CY) to 0 in advance.

- (c) Reads the 2 bytes from the addend area indicated by the addend address (TDE register) into the AX register, and increments the added register (TDE register).

- (d) Adds the 2 bytes in the augend area, indicated by the augend register (WHL register), into the AX register.

- (e) Stores the value in the AX register into the RAM area indicated by the augend address (WHL register), and increments the augend address (WHL register).

- (f) Decrements the counter (C register). When the value of the counter reaches 0, ends addition processing.

- (g) If a carry has occurred as a result of the addition, reads the data of the high-order 2 bytes in the result area indicated by the next augend address (WHL register) into the AX register, and adds the 1 of the carry.

- (h) Stores the value in the AX register into the result area indicated by the augend address (WHL register), then continues processing from step (c).

## (7) Flowchart

## (8) Program listing

## • Description of the label used for executing of application routine

AUGNE: Lowest address of the RAM area containing the 32-bit augend that stores the 32-bit result

(shared)

ADDEN: Lowest address of the RAM area containing the 32-bit addend

## • Example program listing for main routine

```

MOVG WHL, #AUGNE ;

MOVG TDE, #ADDEN ;

CALL !BFXADD ; data "A+B" subrutin

.

```

**Remark** Set the WHL and TDE registers as shown above, then call the subroutine.

## • Program listing for this application routine

```

NAME

BFXADR

; *

binary addition

32 bit <- 32 bit + 32 bit

input condition

; *

WHL-register <- augnend bottom.address

; *

TDE-register <- addend bottom.address

output condition

result <- (HL+3, HL+2, HL+1, HL)

; ******************

PUBLIC BFXADD

CSEG

BFXADD:

C, #2

MOV

BFXAD1:

CLR1

CY

BFXAD2:

AX, [TDE+]; TDE-register <- addend address

MVVOM

MOVW

VP, AX

AX, [WHL] ; WHL-register <- augnend address

MVVOM

; AX <- augnend + addend

AX, VP

ADDW

WVOM

[WHL+], AX ;

DBNZ

C, $BFXAD3 ; add end?

ADDEND

; [yes]

BR

BFXAD3:

$BFXAD2 ; [no] CY = 1 ?

BNC

AX, [WHL] ; [yes]

MVVOM

;

AX, #1

next data add 1

ADDW

MOVW

[WHL], AX ;

BFXAD2

BR

ADDEND:

RET

```

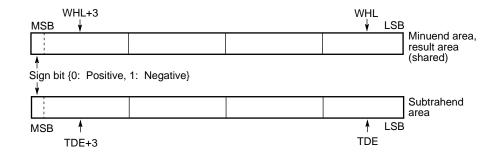

## 2.2 BINARY SUBTRACTION OF SIGNED 32 BITS - 32 BITS

## (1) Outline of processing

This section presents an example program that subtracts a 32-bit subtrahend from a signed 32-bit minuend and stores the result into a 32-bit result area (shared with the minuend area).

## (2) RAM area

When the sign bit is (0): Positive (00000000H through 7FFFFFFH) When the sign bit is (1): Negative (FFFFFFFH through 80000000H)

## (3) Registers

AX, C, VP, TDE, and WHL registers

## (4) Input

Set the following addresses in the WHL and TDE registers.

WHL: Lowest address of the RAM area containing the 32-bit minuend TDE: Lowest address of the RAM area containing the 32-bit subtrahend

## (5) Output

The following contents are stored into the 4-byte RAM area indicated by the WHL register.

WHL to WHL+3: Stores the result of the subtraction.

## (6) Program description

- (a) Sets the number of words to be manipulated in a counter (C register).

- (b) Sets the data for subtraction in the subtrahend and minuend areas.

- (c) Clears the carry flag (CY) to 0 in advance.

- (d) Reads the 2 bytes from the subtrahend area indicated by the subtrahend address (TDE register) into the AX register, and increments the subtrahend address (TDE register).

- (e) Subtracts the 2 bytes in the minuend area, indicated by the minuend address (WHL register), from the AX register.

- (f) Stores the value of the AX register into the result area indicated by the minuend address (WHL register), and increments the minuend address (WHL register).

- (g) Decrements the counter (C register). When the value of the counter reaches 0, ends subtraction processing.

- (h) If a borrow has occurred as a result of the subtraction, reads the data of the high-order 2 bytes indicated by the next minuend address (WHL register) into the AX register, and subtracts the 1 of the borrow.

- (i) Stores the value in the AX register into the result area indicated by the minuend address (WHL register), then continues processing from step (d).

# Phase-out/Discontinued

## (7) Flowchart

## (8) Program listing

## • Description of the label used for executing of application routine

MINU: Lowest address of the RAM area containing the 32-bit minuend that stores the 32-bit result (shared)

SUBT: Lowest address of the RAM area containing the 32-bit subtrahend

## • Example of program listing for main routine

```

MOVG WHL, #MINU;

MOVG TDE, #SUBT;

CALL !BFXSUB; data "A-B" subrutin

```

**Remark** Set the WHL and TDE registers as shown above, then call the subroutine.

## • Program listing for this application routine

```

NAME

BFXSBR

binary subtraction

32 bit <- 32 bit - 32 bit

input condition

WHL-register <- minus value bottom.address

TDE-register <- subtrahend bottom.address

output condition

result <- (WHL+3, WHL+2, WHL+1, WHL)

; ***************

PUBLIC BFXSUB

;

BFXSUB:

C, #2

MOV

BFXSUB1:

CLR1

CY

BFXSUB2:

AX, [TDE+]; TDE-register <- minus value address

MVVOM

MOVW

VP, AX

AX, [WHL] ; WHL-register <- subtrahend address

MOVW

AX, VP ; AX <- minus value addend - subtrahend

SUBW

[WHL+], AX ;

MVVOM

DBNZ

C, $BFXSUB3 ; sub end?

; [yes]

SUBEND

BR

BFXSUB3:

$BFXSUB2; [no] CY = 1?

BNC

AX, [WHL] ; [yes]

MOVW

AX, #1 ;

next data sub 1

SUBW

MOVW

[WHL], AX ;

BFXSUB2

SUBEND:

RET

```

## 2.3 BINARY MULTIPLICATION OF SIGNED 32 BITS x 32 BITS

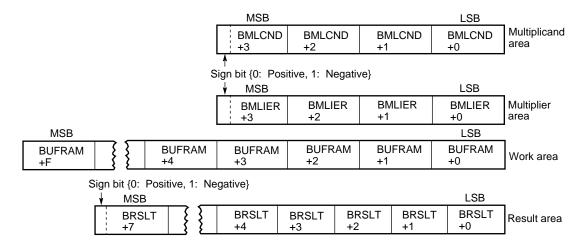

## (1) Outline of processing

This section presents an example program that multiplies a signed 32-bit multiplicand by a 32-bit multiplier, and stores the result into a 64-bit result area.

## (2) RAM area

When the sign bit is (0): Positive (00000000H through 7FFFFFFH) When the sign bit is (1): Negative (FFFFFFFH through 80000000H)

## (3) Registers

A, X, B, C, VP, TDE, WHL, RP2, and R4 registers

## (4) Input

Set the data necessary for the operation into the following 4-byte RAM areas.

BMLCND to BMLCND+3: 32-bit multiplicand data BMLIER to BMLIER+3 : 32-bit multiplier data

## (5) Output

The following contents are stored into the following 8-byte RAM area.

BRSLT to BRSLT+7: Result of multiplication

## (6) Program description

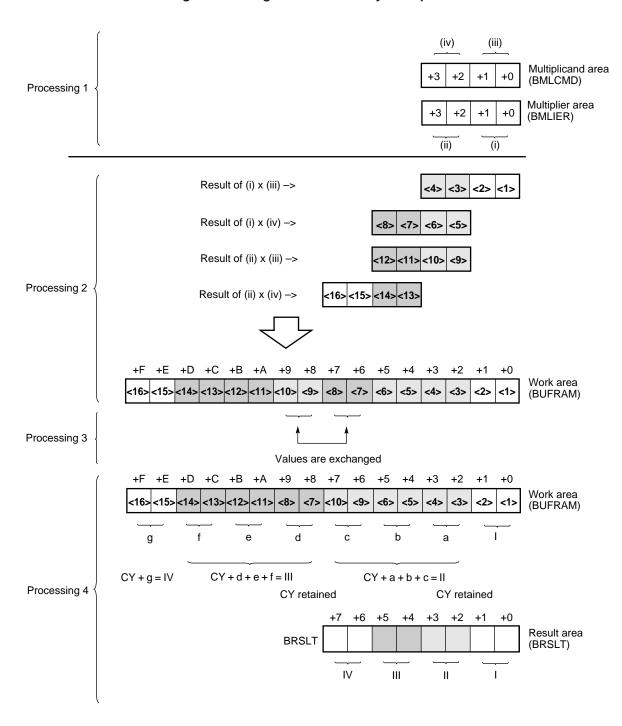

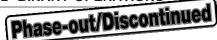

Figure 2-2 illustrates the algorithm for binary multiplication using the 16-bit multiplication instruction.

Figure 2-2. Algorithm for Binary Multiplication

## Remark CY: Carry flag

Processing 4 adds the carry flag (CY) that has been generated as a result of the operation on the lower digit.

The processing performed by this program is as follows:

- (a) Takes the absolute values of the multiplier and multiplicand. If the signs of the multiplier and multiplicand differ, sets the sign identification flag (SFLAG) to 1. If the signs are the same, clears the flag to 0.

- (b) Sets the multiplication end flag (LFLAG) to 1. (LFLAG = 1: Multiplication does not end, LFLAG = 0: Multiplication ends)

- (c) Sets 0 to indicate the lowest address by using the B register as the address pointer to the multiplicand area.

- (d) Sets the lowest address of the work area in the TDE register and the lowest address of the multiplier area in the WHL register.

- (e) Reads the 2-byte multiplier indicated by the WHL register into the VP register, and saves its contents in preparation for the operation performed on the next digit.

- (f) Reads the 2-byte multiplicand, indicated by the address pointer (B register) in the multiplicand area, into the AX register, multiplies it by the multiplier stored in the VP register, then stores the result into the work area indicated by the TDE register, 4 bytes at a time.

- (g) Adds 2 to the B register, and increments the address pointer of the multiplicand area by 2 bytes.

- (h) Compares the value of the address pointer (B register) in the multiplicand area with the number of digits (4) in the multiplicand area to determine whether the two values are the same.

- If the values are found to be different, restores the value of the multiplier saved to the VP register in step (e) to multiply the multiplicand of the next digit, and returns to step (g). Steps (g) through (i) are repeated until the values are the same.

- (i) Sets 0, to indicate the lowest address, into the address pointer (B register) of the multiplicand area.

- (j) Judges whether all multiplications have been completed, by referencing the multiplication end flag (LFLAG). If multiplication has not yet been completed, clears the multiplication end flag (LFLAG) to 0, returns to step (e), then repeats the processing up to step (j).

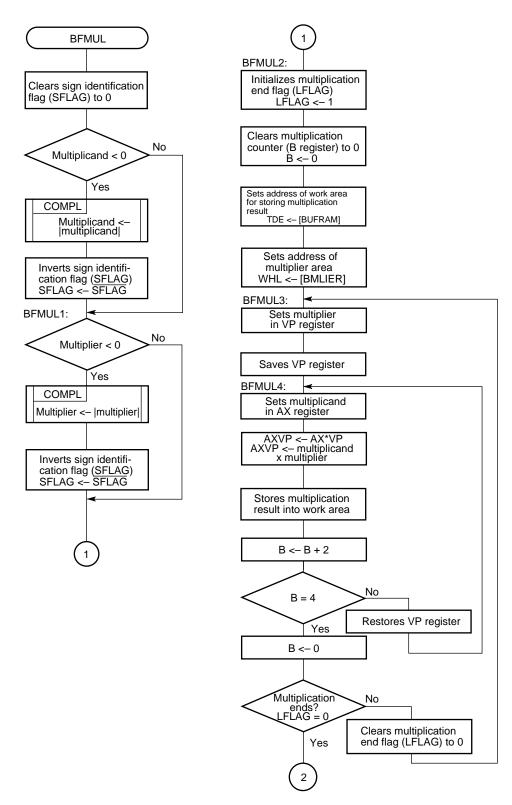

- (k) Exchanges the contents of work areas BUFRAM+6 and BUFRAM+7, and BUFRAM+8 and BUFRAM+9, in which the multiplication result is stored.

- (I) Stores the values of BUFRAM+0 and BUFRAM+1 into the first and second bytes of the result area (BRSLT).

- (m) Adds the values of BUFRAM+2 through BUFRAM+7 with the carry flag (CY), 2 bytes at a time, then stores the result into the third and fourth bytes of the result area (BRSLT).

- (n) Adds the values of BUFRAM+8 through BUFRAM+0DH with the carry flags (CY), 2 bytes at a time, then stores the result into the fifth and sixth bytes of the result area (BRSLT).

- (o) Adds the contents of BUFRAM+0EH and BUFRAM+0FH with the carry flags (CY), then stores the result into the seventh and eighth bytes of the result area (BRSLT).

- (p) If the sign identification flag (SFLAG) is 1, takes the 2's complement of the multiplication result as the result.

## Processing 1

## Processing 2

## Processing 3

Processing 4

Remark Steps 1 through 4 correspond to the numbers shown in Figure 2-2.

## (7) Flowchart

# Phase-out/Discontinued

## (8) Program listing

## Description of label used for executing the application routine

BMLCND: Lowest address of the RAM area containing the 32-bit multiplicand BMLIER: Lowest address of the RAM area containing the 32-bit multiplier

BUFRAM: Lowest address of the work area that temporarily contains the 15-byte multiplication result

BRSLT : Lowest address of the RAM area that contains the final multiplication result

SFLAG : Sign identification flag

SFLAG = 0 ... Same signs SFLAG = 1 ... Different signs

LFLAG : Multiplication end flag

LFLAG = 0 ... Multiplication has ended LFLAG = 1 ... Multiplication has not ended

## • Example program listing for main routine

```

MOVW BMLCND , #02H

MOVW BMLCND+2 , #00H

MOVW BMLIER , #08H

MOVW BMLIER+2 , #15H

CALL !BFMUL

```

**Remark** Set the multiplicand and multiplier as shown above, then call the subroutine.

## • Program listing for this application routine

```

NAME

BFMULR

; ******************

; *

binary multiplication

; *

input condition

; *

multiplicand <- (BMLCND+3, ..., BMLCND)</pre>

; *

multiplier <- (BMLIER+3, ..., BMLIER)</pre>

; *

output condition

result <- (BRSLT+7, BRSLT+6, ..., BRSLT) *

; *

PUBLIC BFMUL

;

EXTRN COMPL, COMP1

EXTRN BMLCND, BMLIER, BRSLT

EXTRN BUFRAM

EXTBIT SFLAG, LFLAG

;

BYTNUM EOU 4

; value length

CSEG

BFMUL:

*** compliment convert ***

CLR1

SFLAG

; sign-flag <- 0

BF

BMLCND+3.7, $BFMUL1

; if data<0 go to BFMUL1

MOVG

WHL, #BMLCND

; WHL-reg. <- BMLCND

; complement subroutine

!COMPL

CALL

NOT1

SFLAG

; not sign-flag

BFMUL1:

; if data<0 go to BFMUL2

BF

BMLIER+3.7, $BFMUL2

; WHL-reg. <- BMLIER

WHL, #BMLIER

MOVG

; complement subroutine

CALL

!COMPL

NOT1

SFLAG

; not sign-flag

```

```

*** word multiplication process ***

BFMUL2:

SET1

LFLAG

;

MOV

B, #0

; MULT loop number clear

MOVG

TDE, #BUFRAM

; TDE-reg. <- BUFRAM

WHL, #BMLIER

MOVG

; WHL-reg. <- BMLIER

BFMUL3:

MOVW

AX, [WHL+]

VP, AX

; VP <- BMLIER

MOVW

VP

PUSH

BFMUL4:

; AX <- BMLCND[B]

MOVW

AX, BMLCND[B]

; AXVP <- AX*VP

MULUW

VP

ï

XCHW

AX, VP

MVVOM

[TDE+], AX

XCHW

AX, VP

; WORK area <- AXVP

MOVW

[TDE+], AX

B, #2

ADD

B, #4

CMP

$BFMUL5

BZ

POP

VP

BR

BFMUL4

;

BFMUL5:

MOV

B, #0

BTCLR

LFLAG, $BFMUL3

;

*** multiplicated data add process ***

;

XCHW

BUFRAM+6, BUFRAM+8

; BUFRAM+6, BUFRAM+7

<-> BUFRAM+8, BUFRAM+9

MOVG

WHL, #BUFRAM+2

MOVG

TDE, #BMSLT+2

SET1

LFLAG

MOVW

RP2, #00H

MOVW

BRSLT, BUFRAM

; answer of lower set

BFMUL6:

VP, RP2

MOVW

RP2, #0

MOVW

MOV

B, #3

; add number set

```

```

BFMUL7:

AX, [WHL+]

MVVOM

ADDW

VP, AX

; add

ADDC

R4, #0

DBNZ

B, $BFMUL7

XCHW

AX, VP

; BMSLT+ <- data set

[TDE+], AX

MOVW

; all add end?

LFLAG, $BFMUL6

BTCLR

AX, [WHL+]

; [no] add again

MVVOM

AX, RP2

ADDW

MOVW

[TDE], AX

BF

SFLAG, $BFMUL8

; if sflag=1 complement convert

C, #8

MOV

MOVG

WHL, #BRSLT

!COMP1

CALL

BFMUL8:

RET

NAME

CMPLE

; *****************

; *

complement convert subroutine

; *

input condition

; *

WHL-register <- complement top.address

; *

output condition

; *

(WHL+3, WHL+2, ..., WHL) <- convert data *

PUBLIC

COMPL, COMP1

BYTNUM

EQU

; value length

CSEG

COMPL:

MOV

C, #BYTNUM

COMP1:

CLR1

CY

;

COMP2:

MOV

A, #0H

A, [WHL]

SUBC

[WHL+], A

MOV

C, $COMP2

DBNZ

RET

```

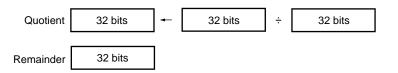

## 2.4 BINARY DIVISION OF SIGNED 32 BITS/32 BITS

## (1) Outline of processing

This section presents an example program that divides a signed 32-bit dividend by a 32-bit divisor and stores the result into a 32-bit result area.

## (2) RAM area

When the sign bit is (0): Positive (00000000H through 7FFFFFFH) When the sign bit is (1): Negative (FFFFFFFH through 80000000H)

Caution The dividend and quotient (DEND+3, ..., DEND), and remainder (DRMND+3, ..., DRMND) areas must all be 8-byte contiguous RAM areas.

## (3) Registers

A, X, B, C, TDE, and WHL registers

## (4) Input

Set the data necessary for the operation into the following 4-byte RAM areas.

DEND to DEND+3 : 32-bit dividend data DVISOR to DVISOR+3: 32-bit divisor data

## (5) Output

The status of the division processing is indicated by setting the following flag.

ERRFLAG: Error flag

$\mathsf{ERRFLAG} = 0 \dots$  No error has occurred (division has been completed normally)  $\mathsf{ERRFLAG} = 1 \dots$  An error has occurred (division cannot be executed because the

divisor is 0)

The 4-byte RAM areas are used to store the results shown.

DEND to DEND+3 : Stores the quotient resulting from the divisionNote DRMND to DRMND+3: Stores the remainder resulting from the divisionNote

Note The values before the operation are retained as these values if the error flag (ERRFLAG) = 1.

Remark The main routine checks the error flag (ERRFLAG). Add error processing as necessary.

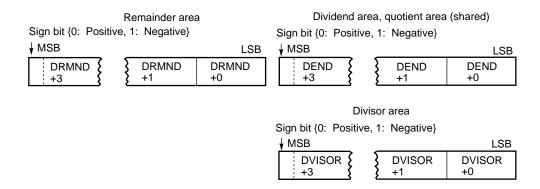

## (6) Program description

This program uses a subtract and return method as the algorithm for binary division. This algorithm is illustrated below.

• Algorithm of division by subtract and return method

<1> Q <- 0

<2> Y <- Y x  $2^{m-n}$

<3> { X <- X - Y

**<4>** if  $X \ge 0$  then Q < -Q + 1 else X < -X + Y

**<5>** Q <- Q x 2

**<6>** Y <- Y/2 }

<7> { } in <3> through <6> is repeated n times.

As a result, the quotient is stored into Q and the remainder is stored into X.

**Remark** The meanings of the above symbols are as follows.

Q: Quotient area

X: Dividend area

Y: Divisor area

m: Number of digits in dividend

n: Number of digits in divisor

• Example of binary division (4 bits/4 bits) using the subtract and return method

**Example** 14/3 = quotient: 4, remainder: 2 (The following expression is in binary.)

• Algorithm for binary division (32 bits/32 bits) performed by this program

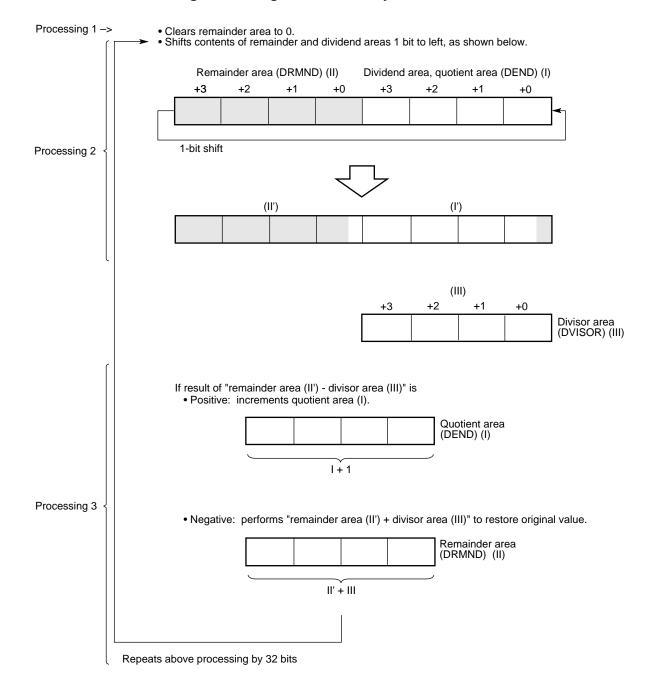

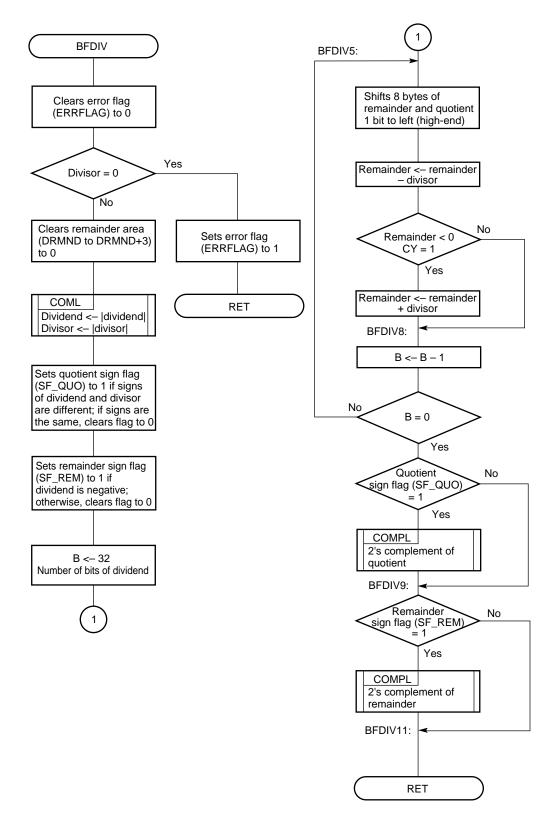

Figure 2-3. Algorithm for Binary Division

The processing performed by this programs is explained below.

- Processing 1 -> (a) Determines whether the value of the divisor area is 0. If 0, sets the error flag (ERRFLAG) to 1, then ends the operation, with only information indicating the occurrence of an error remaining.

- (ERRFLAG = 0 ... No error has occurred, ERRFLAG = 1 ... An error has occurred)

- (b) Clears the remainder area to 0.

- (c) Takes the absolute values of the dividend and divisor areas. If either of the values in the dividend and divisor areas is negative, sets the quotient sign flag (QUOFLAG) to 1.

(QUOFLAG = 0 ... Sign of quotient is positive, QUOFLAG = 1 ... Sign of quotient is negative)

Sets the remainder sign flag (REMFLAG) to 1 if the value of the dividend area is negative.

(REMFLAG = 0 ... Sign of remainder is positive, REMFLAG = 1 ... Sign of remainder is negative)

- (d) Uses the B register as a bit counter that counts the number of bits in the dividend area, then sets the number of bits (32) in the dividend area in this counter.

- Processing 2 -> (e) Shifts the remainder area and dividend area (8-byte contiguous area) 1 bit to the left.

- Processing  $3 \rightarrow (f)$  Executes "remainder area  $\leftarrow$  remainder area  $\rightarrow$  divisor area". If the result is negative, jumps to (h).

- (g) Increments the quotient area (DEND). Jumps to (i).

- (h) Because too great a value has been subtracted, executes "remainder area <- remainder area + divisor area" to restore the original value of the remainder area.

- (i) Decrements the bit counter (B register) of the dividend area, and repeats steps (e) through (h) until the counter reaches 0.

- Processing 4 <

- (j) Checks the quotient sign flag (QUOFLAG), and takes the 2's complement of the quotient if the flag is set to 1.

- Checks the remainder sign flag (REMFLAG), and takes the 2's complement of the remainder if the flag is set to 1.

- Remarks 1. For details of the COMPL subroutine, see Section 2.3.

- 2. Processing 1 through 4 corresponds to the numbers shown in Figure 2-3.

# Phase-out/Discontinued

# (7) Flowchart

# (8) Program listing

# • Description of label used for execution of application routine

DEND : Lowest address of the RAM area containing the 32-bit dividend and 32-bit quotient (shared)

DRMND : Lowest address of the RAM area containing the 32-bit remainder that results from division

DIVSOR : Lowest address of the RAM area containing the 32-bit divisor

BYTNUM: Number of bytes in the remainder area (used to clear the remainder area to 0)

QUOFLAG: Quotient sign flag

QUOFLAG = 0 ... Sign of quotient is positive QUOFLAG = 1 ... Sign of quotient is negative

REMFLAG: Remainder flag

REMFLAG = 0 ... Sign of remainder is positive REMFLAG = 1 ... Sign of remainder is negative

ERRFLAG: Error flag

ERRFLAG = 0 ... An error has not occurred ERRFLAG = 1 ... An error has occurred

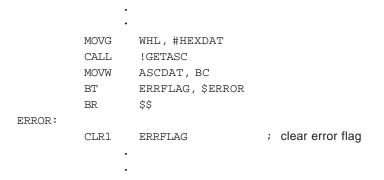

# Example of program listing for main routine

```

; data "A"

MVVOM

DEND,

#00

MVVOM

DEND+2, #32

; data "B"

MVVOM

DVISOR, #00

DVISOR+2, #08

MVVOM

CALL

!BFDIV

; data "A/B" subroutine

BT

ERRFLAG, $ERROR ;

ERROR:

CLR1

ERRFLAG

; clear error flag

```

**Remark** Set the dividend and divisor as shown above, then call the subroutine.

# • Program listing for this application routine

```

NAME

BFDIVR

;*

binary division

;*

32 bit <- 32 bit / 32 bit

input condition

;*

dividend <- (DEND+3, ..., DEND)</pre>

;*

divisor

<- (DVISOR+3, ..., DVISOR)

output condition

;*

quotient <- (DEND+3, ..., DEND)

;*

remainder <- (DRMND, ..., DRMND)</pre>

; *

z flag <- 0:output ok 1: NG

PUBLIC BFDIV

EXTRN

COMPL

DEND, DVISOR, DRMND

EXTRN

EXTBIT ERRFLAG

EXTBIT REMFLAG, QUOFLAG

BYTNUM

EQU

4

CSEG

BFDIV:

ERRFLAG ; clear error flag

CLR1

**** check / divisor = 0 ? ****

;

;

WHL, #DVISOR ; WHL <- DVISOR

MOVG

AX, [WHL+]

MVVOM

CMPW

AX, #0

BNZ

$BFDIV2

; [WHL] = 0 ?

MOVW

AX, [WHL+]

AX, #0

CMPW

; [WHL] = 0 ?

BNZ

$BFDIV2

;

**** divisor = 0 ****

SET1

ERRFLAG

; OVERFLOW

RET

**** quotient 0-clear ****

BFDIV2:

TDE, #DRMND; TDE-register <- DRMND

MOVG

MOV

C, #BYTNUM

MOV

A, #0

MOVM

[TDE+], A

```

```

**** complement convert ****

;

; clear remainder sign-flag

CLR1

REMFLAG

CLR1

; clear quotient sign-flag

OUOFLAG

BF

DEND+3.7, $BFDIV3

WHL, #DEND ; WHL-register <- DEND

MOVG

; complement subroutine

CALL

!COMPL

SET1

REMFLAG

; set remainder sign-flag

; not quotient sign-flag

NOT1

QUOFLAG

BFDIV3:

DVISOR+3.7, $BFDIV4

BF

WHL, #DVISOR ; WHL-register <- DVISOR

MOVG

CALL

!COMPL

; complement subroutine

NOT1

QUOFLAG

; not quotient sign-flag

**** byte counter set ****

;

BFDIV4:

MOV

B, #32

; B-register <- 32

**** dividend, remainder 1-byte left shift ****

;

BFDIV5:

CLR1

CY

; WHL <- DEND

MOVG

WHL, #DEND

MOV

C, #8

; loop counter

BCDLS1:

MOV

A, [WHL]

ROLC

A, 1

MOV

[WHL+], A

C, $BCDLS1

DBNZ

;

***

subtract divisor from dividend ****

BFDIV6:

; TDE <- DVISOR

MOVG

TDE, #DVISOR

MOVW

AX, [TDE+]

SUBW

DRMND, AX

A, [TDE+]

VOM

DRMND+2, A

SUBC

VOM

A, [TDE+]

SUBC

DRMND+3, A

$BFDIV7

BC

SET1

DEND.0

BFDIV8

BR

```

```

**** if borrow divisor + dividend ****

BFDIV7:

TDE, #DVISOR ; TDE <- DVISOR

MOVG

MOVW

AX, [TDE+]

;

ADDW

DRMND, AX

MOV

A, [TDE+]

DRMND+2, A

ADDC

MOV

A, [TDE+]

;

ADDC

DRMND+3, A

BFDIV8:

DBNZ

B, $BFDIV5

;

**** check / division end ? ****

REMFLAG, &BFDIV9

BF

WHL, #DRMND

MOVG

CALL

!COMPL

BFDIV9:

BF

QUOFLAG, $BFDIV10

MOVG

WHL, #DEND

!COMPL

CALL

BFDIV10:

; clear z flag

CLR1

PSWL.6

BFDIV11:

RET

```

[MEMO]

Phase-out/Discontinued

# **CHAPTER 3 DECIMAL OPERATIONS**

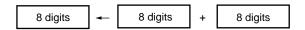

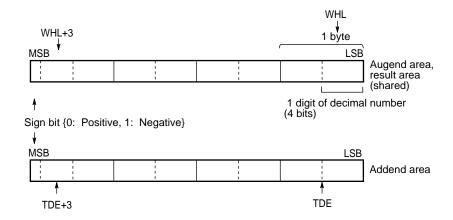

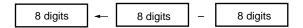

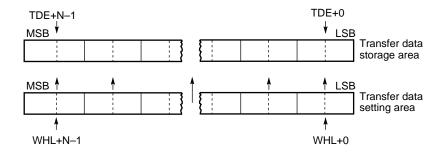

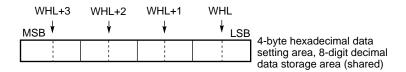

In decimal operations, the most significant bit is used as a sign bit, the remaining bits expressing a numeric value, as shown in Figure 3-1. Decimal numbers are expressed as BCD codes.

Figure 3-1. Expressing Decimal Numbers

For decimal operations, the data storage area used for the operation and the area storing the result of the operation are located in RAM.

#### 3.1 DECIMAL ADDITION OF SIGNED 8 DIGITS + 8 DIGITS

# (1) Outline of Processing

This section presents an example program that adds a signed 8-digit augend to an 8-digit addend, then stores the result into an 8-digit result area (shared with the augend area).

# (2) RAM area

When the sign bit is (0): Positive (0 through 79999999)

When the sign bit is (1): Negative (-1 through -79999999)

#### (3) Registers

A, C, B, TDE, and WHL registers

#### (4) Input

Set the following addresses in the WHL and TDE registers.

WHL: Lowest address of the RAM area containing the 8-digit (4-byte) augend TDE: Lowest address of the RAM area containing the 8-digit (4-byte) addend

# (5) Output

The status of the division processing is indicated by the following flag.

ERRFLAG: Error flag

ERRFLAG = 0 ... An error has not occurred (addition was completed normally)

ERRFLAG = 1 ... An error has occurred (addition cannot be executed because an

overflow or underflow occurred)

The following contents are stored into the 4-byte RAM area indicated by the WHL register.

WHL to WHL+3: Stores the result of the addition Note

**Note** When the error flag (ERRFLAG) = 1, the 4-byte value in the WHL register will be undefined.

- **Remarks 1.** The operation range is -79999999 to 79999999.

- 2. The error flag (ERRFLAG) is identified by the main routine. Add error processing as necessary.

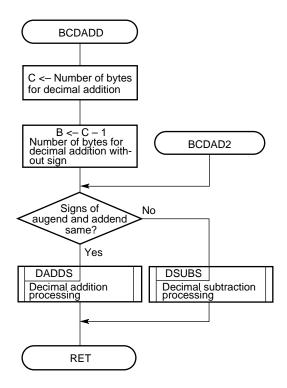

# (6) Program description

This program performs addition if the signs of the addend and augend are the same; if not, it performs subtraction.

- (a) Sets the number of bytes for decimal addition in the C counter (C register).

- (b) If the signs of the addend and augend are different, jumps to step (o).

- (c) Clears the carry flag (CY) and sign identification flag (SFLAG) to 0.

- (d) Reads 1 byte of the augend area indicated by the augend address (WHL register) into the A register.

- (e) Adds the 1 byte of the addend area, indicated by the addend address (TDE register), to the A register with the carry flag (CY), and increments the addend address (TDE register).Converts the result of the operation to a decimal number, stores it into the result area indicated by the augend address (WHL register), then increments the augend address (WHL register).

- (f) Decrements the counter (B register), then repeats steps (d) through (e) until the value of the counter reaches 0.

- (g) Reads 1 byte from the augend area indicated by the augend address (WHL register) into the A register.

- (h) Adds 1 byte of the addend area, indicated by the addend address (TDE register) into the A register with the carry flag (CY).

- (i) Jumps to step (k) if the carry flag (CY) is "0".

- (j) Sets the sign identification flag (SFLAG) to 1, then clears the carry flag (CY) to 0.

- (k) Converts the value of the A register to a decimal number.

- (I) If the carry flag (CY) is "1", or if the seventh bit of the A register is "1", an overflow occurs. In this case, sets the error flag (ERRFLAG) to 1 and terminates the operation.

- (m) Sets the seventh bit of the A register into 1 if the sign identification flag (SFLAG) is "1".

- (n) Stores the contents of the A register into the result area indicated by the augend address (WHL register), then terminates the operation.

- (o) Makes the subtrahend positive, then clears the sign identification flag (SFLAG) to 0.

- (p) If the minuend is negative, makes the minuend positive, then sets the sign identification flag to 1.

- (q) Clears the carry flag (CY) to 0.

- (r) Reads 1 byte in the minuend area, indicated by the minuend address (WHL register), into the A register.

- (s) Subtracts 1 byte in the subtrahend area, indicated by the subtrahend address (TDE register), from the A register with the carry flag (CY), and increments the subtrahend address (TDE register). Converts the result of the operation to a decimal number, stores it into the result area indicated by the minuend address (WHL register), then increments the minuend address (WHL register).

- (t) Decrements the counter (C register), then repeats steps (r) and (s) until the value of the counter reaches 0.

- (u) Jumps to step (w) if the carry flag (CY) is 0.

- (v) Takes the 10's complement of the result and inverts the sign identification flag (SFLAG).

- (w) Terminates the operation if the result is 0.

- (x) Jumps to step (y) if the sign identification flag (SFLAG) is 1; if the flag is 0, terminates the operation.

- (y) Sets the sign bit of the result to 1, then terminates the operation.

**Remark** For the decimal subtraction routine (steps (o) through (y)), the augend area is replaced by the minuend area, while the addend area is replaced by the subtrahend area.

# (7) Flowchart

# Phase-out/Discontinued

# (8) Program listing

. Description of label used for executing the application routine

BCDAUG: Lowest address of the RAM area containing the 8-digit (4-byte) augend and 8-digit result

(shared)

BCDADE: Lowest address of the RAM area containing the 8-digit (4-byte) addend

SFLAG : Sign identification flag

SFLAG = 0 ... Same signs

SFLAG = 1 ... Different signs

ERRFLAG: Error flag

ERRFLAG = 0 ... No error has occurred ERRFLAG = 1 ... An error occurred

• Example of program listing for main routine

```

MOVG WHL, #BCDAUG ;

MOVG TDE, #BCDADE ;

CALL !BCDADD ;

BT ERRFLAG, $ERROR ;

BR $$ ;

ERROR:

CLR1 ERRFLAG ; clear error flag

```

**Remark** Set the WHL and TDE registers as shown above, then call the subroutine. Prepare and add error processing as necessary.

# · Program listing for this application routine

```

NAME

BCDADR

;*

decimal addition

8 digit <- 8 digit + 8 digit

input condition

;*

WHL-register <- augend area top.address

;*

TDE-register <- addend area top.address

output condition

result <- (WHL, WHL+1, WHL+2, WHL+3)

; ***************

PUBLIC BCDADD, BCDAD1, BCDAD2

PUBLIC

DADDS

PUBLIC DSUBS

; work flag for sign flag

EXTBIT SFLAG

EXTBIT ERRFLAG ; error sign flag

BYTNUM EQU

CSEG

BCDADD:

C, #BYTNUM

; C-register <- 4

MOV

BCDAD1:

; B-register <- C-register - 1

MOV

В, С

DEC

В

BCDAD2:

MOV

A, [WHL+BYTNUM-1]

A, [TDE+BYTNUM-1]

XOR

; clear error flag

CLR1

ERRFLAG

A.7, $BCDAD3

BT

! DADDS

CALL

EBCDAD

BR

BCDAD3:

CALL!DSUBS

EBCDAD:

RET

```

\*\*\*\* decimal addition subroutine \*\*\*\* DADDS: CY CLR1 CLR1 SFLAG ; clear sign-flag DADDS1: MOV A, [WHL] A, [TDE+] ADDC ; decimal adjust ADJBA MOV [WHL+], A B, \$DADDS1 DBNZ MOV A, [WHL] ADDC A, [TDE] DADDS2: BNC \$DADDS3 ; set sign-flag SET1 SFLAG CLR1 CY DADDS3: ADJBA ; decimal adjust BNC \$DADDS4 DADDS7 DADDS4: A.7, \$DADDS5 BFDADDS7 DADDS5: BFSFLAG, \$DADDS6 SET1 A.7 DADDS6: MOV [WHL], A BR EDADDS DADDS7: ; set error flag SET1 ERRFLAG EDADDS: RET

```

**** decimal subtraction subroutine ****

DSUBS:

PUSH

WHL

; save WHL-register

SFLAG

; clear sign-flag

CLR1

VOM

A, [TDE+BYTNUM-1]

CLR1

A.7

MOV

[TDE+BYTNUM-1], A

MOV

A, [WHL+BYTNUM-1]

BF

A.7, $DSUBS1

CLR1

A.7

[WHL+BYTNUM-1], A

MOV

SET1

; set sign-flag

DSUBS1:

MOV

В, С

; save C-register

CLR1

CY

DSUBS2:

MOV

A, [WHL]

A, [TDE+]

SUBC

; decimal adjust

ADJBS

MOV

[WHL+], A

C, $DSUBS2

DBNZ

BNC

$DSUBS5

WHL

; load WHL-register

POP

PUSH

WHL

; save WHL-register

C, B

; load C-register

MOV

DSUBS3:

; (WHL) <- 9 - (WHL)

A, #99H

MOV

increment WHL-register

SUB

A, [WHL]

ADJBS

; decimal adjust

MOV

[WHL+], A

C, $DSUBS3

DBNZ

; load WHL-register

POP

WHL

PUSH

WHL

; save WHL-register

SET1

CY

С, В

; load C-register

MOV

DSUBS4:

MOV

A, #0

; Acc <- 0

A, [WHL]

ADDC

; decimal adjust

ADJBA

[WHL+], A

MOV

DBNZ

C, $DSUBS4

NOT1

SFLAG

```

Phase-out/Discontinued

```

**** check / result = 0 ****

DSUBS5:

; load C-register

MOV

С, В

WHL

; load WHL-register

POP

MOVG

TDE, WHL

A, #0

MOV

CMPME [TDE+], A

$EDSUBS

BZ

BF

SFLAG, $EDSUBS

A, [WHL+BYTNUM-1]

MOV

SET1

A.7 ; set sign

MOV

[WHL+BYTNUM-1], A

EDSUBS:

RET

```

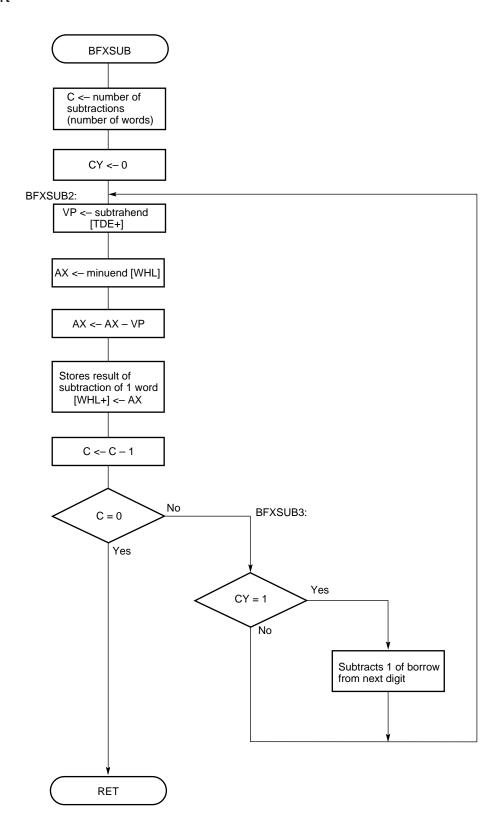

# 3.2 DECIMAL SUBTRACTION OF SIGNED 8 DIGITS - 8 DIGITS

# (1) Outline of Processing

This section presents an example program that subtracts an 8-digit subtrahend from a signed 8-digit minuend then stores the result into an 8-digit result area (shared with the minuend area).

# (2) RAM area

When the sign bit is (0): Positive (0 through 79999999)

When the sign bit is (1): Negative (-1 through -79999999)

# (3) Registers

A, B, C, TDE, and WHL registers

# (4) Input

Set the following addresses in the WHL and TDE registers.

WHL: Lowest address of the RAM area containing the 8-digit (4-byte) minuend TDE: Lowest address of the RAM area containing the 8-digit (4-byte) subtrahend

# (5) Output

The status of the subtraction processing is indicated by the following flag.

ERRFLAG: Error flag

ERRFLAG = 0 ... No error has occurred (subtraction was completed normally)

ERRFLAG = 1 ... An error occurred (subtraction cannot be executed because overflow

or underflow occurs)

The following contents are stored into the 4-byte RAM area indicated by the WHL register.

WHL to WHL+3: Stores the result of subtraction Note

**Note** When the error flag (ERRFLAG) = 1, the 4-byte value indicated by the WHL register will be undefined.

**Remarks 1.** The operation range is -79999999 to 79999999.

2. The error flag (ERRFLAG) is identified by the main routine. Add error processing as necessary.

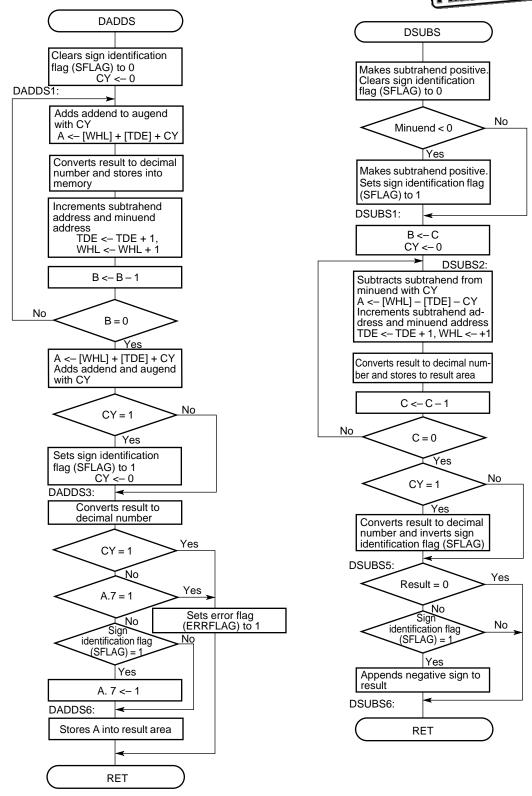

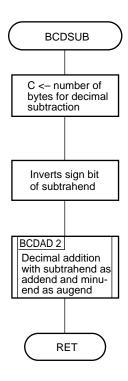

# (6) Program description

This program performs the processing of "minuend – subtrahend" by converting it into "minuend + (–subtrahend)".

- (a) Sets the number of bytes for decimal subtraction into the C counter (C register).

- (b) Inverts the sign bit of the subtrahend area.

- (c) Performs decimal addition by using the minuend and subtrahend areas as the augend and addend areas.

**Remark** For details of the BCDAD2 subroutine (including the processing for setting the error flag (ERRFLAG) to 1), see **Section 3.1**.

The operation error processing is included in the main routine. Prepare and add error processing as necessary.

# (7) Flowchart

# (8) Program listing

. Description of label used for executing the application routine

BCDMIN: Lowest address of the RAM area containing the 8-digit (4-byte) minuend and 8-digit result (shared)

BCDSUT: Lowest address of the RAM area containing the 8-digit (4-byte) subtrahend

· Example program listing of main routine

```

MOVG WHL, #BCDMIN

MOVG TDE, #BCDSUT

CALL !BCDSUB

BT ERRFLAG, $ERROR;

BR $$;

ERROR:

CLR1 ERRFLAG; clear error flag

```

**Remark** Set the WHL and TDE registers as shown above, then call the subroutine. Prepare and add error processing as necessary.

# · Program listing for this application routine

```

NAME

BCDSUR

;* decimal subtraction

8 digit <- 8 digit - 8 digit

input condition

WHL-register <- minus value area top.address

TDE-register <- subtrahend area top.address

output condition

result <- (WHL, WHL+1, WHL+2, WHL+3)

; ****************

PUBLIC BCDSUB

EXTRN BCDAD2

BYTNUM EQU

CSEG

BCDSUB:

C, #BYTNUM ; C-register <- 4

MOV

BCDSU1:

В, С

; B-register <- C-register - 1

MOV

DEC

MOV

A, [TDE+BYTNUM-1]

NOT1

A.7

[TDE+BYTNUM-1],A

MOV

CALL

!BCDAD2

RET

```

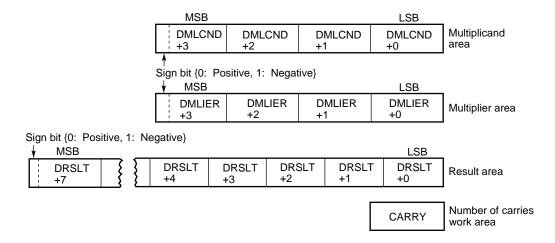

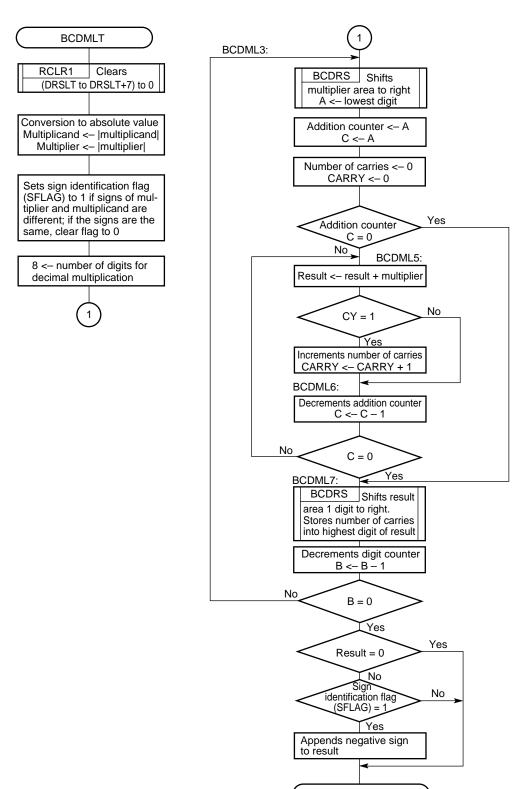

# 3.3 DECIMAL MULTIPLICATION OF SIGNED 8 DIGITS x 8 DIGITS

#### (1) Outline of Processing

This section presents an example program that multiplies a signed 8-digit multiplicand by an 8-digit multiplier, then stores the result into a 16-digit result area.

# (2) RAM area

When the sign bit is (0): Positive (0 through 79999999)

When the sign bit is (1): Negative (-1 through -79999999)

#### (3) Registers

A, X, B, C, TDE, and WHL registers

#### (4) Input

Set the data necessary for the operation into the following 4-byte RAM areas.

DMLCND to DMLCND+3: 8-digit multiplicand data DMLIER to DMLIER+3 : 8-digit multiplier data

# (5) Output

The following 8-byte RAM area is used to store the contents shown.

DRSLT to DRSLT+7: Result of multiplication

**Remark** Both the multiplier and multiplicand can be between –79999999 and 79999999. The operation result can be between –6399999840000001 and 6399999840000001.

# (6) Program description

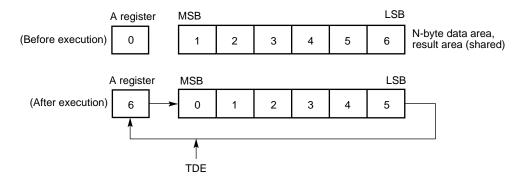

This program shifts the multiplier 1 digit (4 bits) to the right then loads the multiplicand into the addition counter, starting from the lowest digit, 1 digit at a time. Using the addition counter, the "result <- result + multiplicand" operation is repeated.

When addition using the addition counter has ended, addition is performed using the multiplier 1 digit higher; therefore, the result area is shifted 1 digit (4 bits) to the right.

The processing is explained below:

- (a) Clears the result area to 0.

- (b) Takes the absolute values of the multiplier area and multiplicand area. If the signs of the multiplier and multiplicand areas are different, sets the sign identification flag (SFLAG) to 1; if the signs are the same, clears the flag to 0.

- (c) Sets the number of digits (8) for multiplication, using the B register as a digit counter.

- (d) Sets the value of the lowest digit (4 bits) of the multiplier area into the addition counter (C register) by shifting the multiplier area 1 digit (4 bits) to the right.

- (e) Clears the number of carries work area (CARRY), reserved in advance and which is used to save the number of carries, to 0.

- (f) Jumps to step (i) if the value of the addition counter (C register) is 0.

- (g) Executes "result area (higher 8 digits) <- result area (higher 8 digits) + multiplicand area" decimal addition processing. If an overflow occurs, increments the value in the number of carries work area (CARRY).

- (h) Decrements the addition counter (C register), then repeats step (g) until the value of the counter reaches 0.

- (i) Shifts the result area, including the number of carries work area (CARRY), 1 digit (4 bits) to the right. Stores the number of carries into the highest digit of the result area.

- (j) Decrements the digit counter (B register), then repeats steps (d) through (i) until the value of the counter reaches 0.

- (k) Terminates the operation if the contents of the digit counter (B register) are 0.

- (I) Sets the sign bit of the result area to 1 if the sign identification flag (SFLAG) is 1.

# (7) Flowchart

**RET**

# (8) Program listing

# . Description of label used for execution of application routine

DMLCND: Lowest address of the RAM area containing the 8-digit (4-byte) multiplicand DMLIER: Lowest address of the RAM area containing the 8-digit (4-byte) multiplier

CARRY: Number of carries work area

DRSLT : Lowest address of the RAM area used to contain the 16-digit (8-byte) result

SFLAG : Sign identification flag

SFLAG = 0 ... Same signs SFLAG = 1 ... Different signs

# · Example program listing for main routine

```

MOVW DMLCND , #12H

MOVW DMLCND+2 , #00

MOVW DMLIER , #54H

MOVW DMLIER+2 , #12H

CALL !BCDMLT

.

```

**Remark** Set the multiplicand and multiplier as shown above, then call the subroutine.

# · Program listing for this application routine

```

NAME

BCDMLR

;*

decimal multiplication

16 digit <- 8 digit * 8 digit

input condition

;*

multiplicand <- (DMLCND+3, ..., DMLCND)</pre>

;*

multiplier <- (DMLIER+3, ..., DMLIER)</pre>

output condition

result <- (DRSLT+7, ..., DRSLT)

; *****************

PUBLIC BCDMLT

DMLCND, DMLIER, DRSLT

EXTRN

EXTRN

CARRY

; carry data set ram

EXTBIT SFLAG

CSEG

BCDMLT:

;

**** result area 0-clear ****

C, #8

; C-register <- 8

MOV

; TDE <- DRSLT

MOVG

TDE, #DRSLT

A, #0

; Acc <- 0

MOV

MOVM

[TDE+], A

;

**** check / sign ****

;

; clear sign-flag

CLR1

SFLAG

BF

DMLCND+3.7, $BCDML1

DMLCND+3.7

CLR1

; not sign-flag

NOT1

SFLAG

BCDML1:

A, [WHL]

BF

DMLIER+3.7, $BCDML2

CLR1

DMLIER+3.7

NOT1

SFLAG

; not sign-flag

;

**** digit counter set ****

;

BCDML2:

MOV B, #8

; B-register <- 8

;

**** multiplier right shift ****

```

```

BCDML3:

WHL, #DMLIER+3

MOVG

MOV

C, #4

; C-register <- 4

; Acc <- 0

MOV

A, #0

BCDRS:

ROR4

[WHL]

DECG

\mathtt{WHL}

; decrement (WHL)

DBNZ

C, $BCDRS

MOV

C, A

; C-register <- Acc

MOV

CARRY, #0

; carry <- 0

;

**** check / multiplier = 0 ? ****

;

;

ADD

A, #0

$BCDML7

; if Acc = 0 then go to BCDML6

BZ

;

**** result <- DMLCND + result ****

BCDML4:

; TDE <- DMLCND

MOVG

TDE, #DMLCND

MOVG

WHL, #DRSLT+4

; WHL <- DRSLT+4

CY

; clear carry

CLR1

PUSH

AX

; save AX-register

; save BC-register

PUSH

BC

C, #4

; C-register <- 4

MOV

BCDML5:

A, [WHL]

MOV

A, [TDE+]

ADDC

ADJBA

; decimal adjust

MOV

[WHL+], A

DBNZ

C, $BCDML5

; load BC-register

POP

BC

POP

AX

; load AX-register

$BCDML6

BNC

INC

CARRY

BCDML6:

DBNZ

C, $BCDML4

**** result right shift with carry ****

BCDML7:

MOV

A, CARRY

; WHL <- DRSLT+7

WHL, #DRSLT+7

MOVG

C, #8

VOM

BCDRS1:

ROR4

[WHL]

DECG

WHL

; decrement (WHL)

DBNZ

C, $BCDRS1

**** check / multiply end ? ****

```

# Phase-out/Discontinued

```

DBNZ

B, $BCDML3

;

**** check / multiply = 0 ****

;

MOVG

TDE, #DRSLT

MOV

C, #8

A, #0

MOV

BCDML8:

CMPME

[TDE+], A

BZ

$BCDML9

**** check / sign-flag ****

;

SFLAG, $BCDML9

BF

MOVG

WHL, #DRSLT+7

A, [WHL]

MOV

SET1

A.7

[WHL], A

MOV

BCDML9:

RET

```

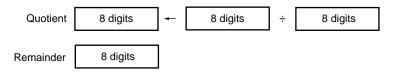

#### 3.4 DECIMAL DIVISION OF SIGNED 8 DIGITS/8 DIGITS

#### (1) Outline of Processing

This section presents an example of a program that divides a signed 8-digit dividend by an 8-digit divisor, then stores the result into an 8-digit result area, and the remainder into an 8-digit remainder area.

#### (2) RAM area

Caution The dividend and quotient areas (DIVIND, ..., DIVIND+3) and remainder area (RMIND, ..., RMIND+3) must all be contiguous 8-byte RAM areas.

When the sign bit is (0): Positive (0 through 79999999)

When the sign bit is (1): Negative (-1 through -79999999)

#### (3) Registers

A, X, B, C, TDE, and WHL registers

**Remark** When the X register takes the absolute value of the dividend or divisor, the following bits of the register are used as flags.

QUOFLAG: Bit 0 of X register is used as quotient sign flag

REMFLAG: Bit 1 of X register is used as remainder sign flag

# (4) Input

Set the data necessary for the operation into the following 4-byte RAM areas.

DIVIND to DIVIND+3 : 8-digit dividend data DIVSOR to DIVSOR+3: 8-digit divisor data

# (5) Output

The status of the division processing is indicated by the following flag.

ERRFLAG: Error flag

ERRFLAG = 0 ... No error has occurred (division was completed normally)

ERRFLAG = 1 ... An error occurred (division cannot be executed because the divisor

is 0)

The following contents are stored into the following 4-byte RAM areas.

DIVIND to DIVIND+3: Quotient resulting from division operation<sup>Note</sup> RMIND to RMIND+3: Remainder resulting from division operation<sup>Note</sup>

**Note** These values will be the same as those before the operation if the error flag (ERRFLAG) is set to 1.

**Remark** The value of the error flag (ERRFLAG) is determined by the main routine. Add error processing as necessary.

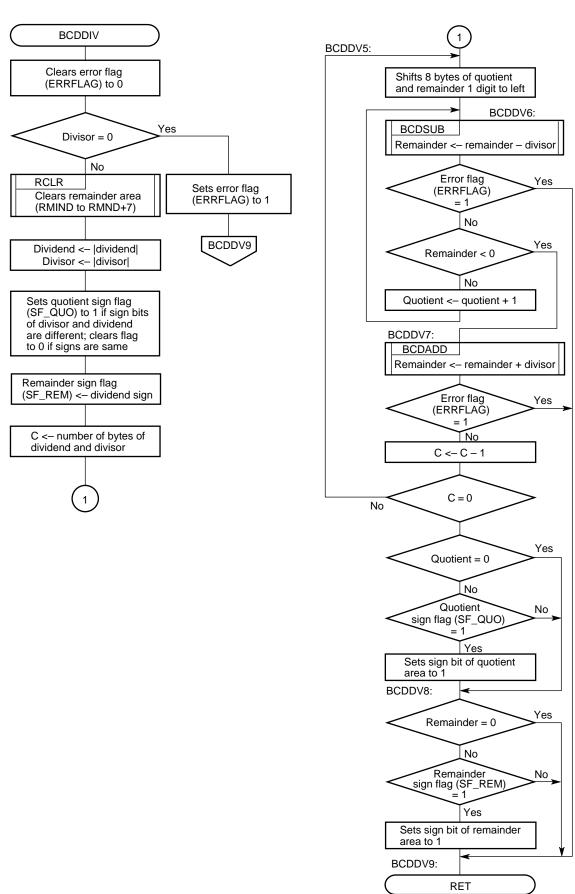

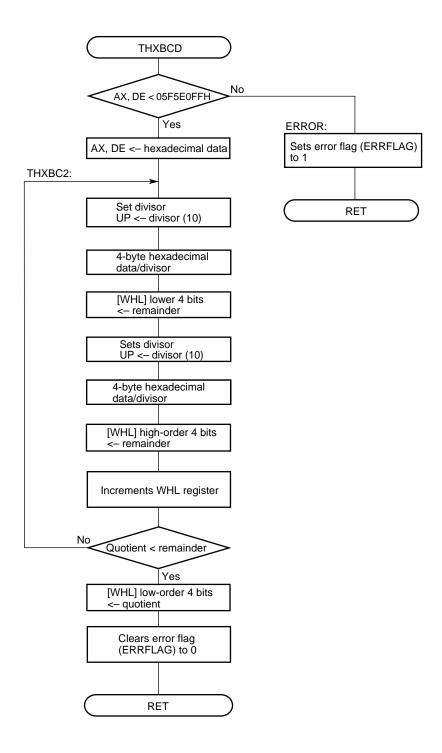

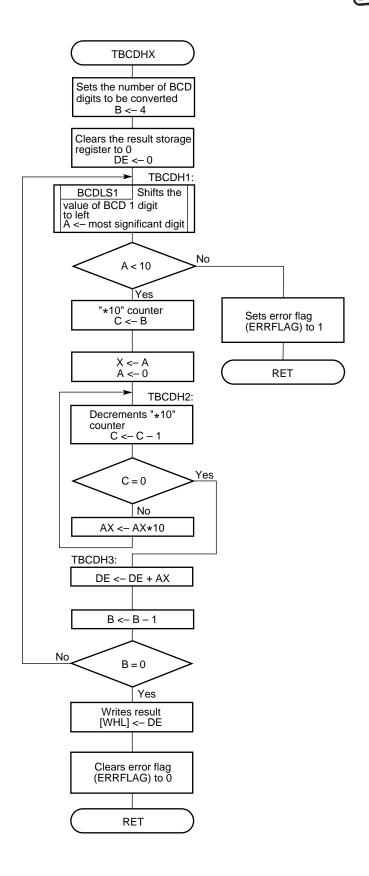

# (6) Program description

This program uses contiguous 8-byte areas as the dividend and quotient (DIVIND, ..., DIVIND+3), and remainder (RMIND, ..., RMIND+3) areas.

The highest digit of the dividend is transferred to the lowest area of the remainder by shifting the dividend and remainder 1 digit to the left, while the quotient is stored into the lowest area of the dividend, 1 digit at a time.

Each digit of the quotient indicates the number of times the operation must be repeated until the result of "remainder – divisor" becomes negative.

- (a) Identifies whether the value of the divisor area is 0. If it is 0, sets the error flag (ERRFLAG) to 1, and terminates the operation with only information indicating the occurrence of an error remaining. (ERRFLAG = 0 ... No error has occurred, ERRFLAG = 1 ... An error occurred)

- (b) Clears the remainder area to 0.

- (c) Obtains the absolute values of the dividend and divisor areas.

If either the dividend or divisor areas is negative, sets the quotient sign flag (QUOFLAG) to 1.

(QUOFLAG = 0 ... Sign of quotient is positive, QUOFLAG = 1 ... Sign of quotient is negative)

If the dividend is negative, sets the remainder sign flag (REMFLAG) to 1.

- (REMFLAG = 0 ... Sign of remainder is positive, REMFLAG = 1 ... Sign of remainder is negative)

- (d) Sets the number of bits (8) in the dividend area by using the C register as a bit counter that counts the number of bits in the dividend area.

- (e) Shifts the remainder and quotient areas (contiguous 8-byte areas) 4 bits to the left.

- (f) Executes the "remainder area <- remainder area divisor area" operation. If the result is negative, jumps to (h).

- (g) Increments the quotient area (DIVIND). Jumps to (i).

- (h) Because too great a value has been subtracted from the remainder area, executes the "remainder area <- remainder area + divisor area" operation to restore the original value of the remainder area.

- (i) Decrements the bit counter (C register) of the dividend area, then repeats steps (e) through (h) until the value of the counter reaches 0.

- (j) Jumps to step (l) if the quotient is 0.

- (k) Sets the sign bit of the quotient area to 1 if the quotient sign flag (QUOFLAG) is 1.

- (I) Terminates the operation if the remainder is 0.

- (m) Sets the sign bit of the remainder area to 1 if the remainder sign flag (REMFLAG) is 1.

**Remark** For details of the BCDAD2 subroutine, see **Section 3.1**. For details of the BCDSUB subroutine, see **Section 3.2**.

For details of the processing to set the error flag (ERRFLAG) to 1, and of the error processing, see **Section 3.1**.

# Phase-out/Discontinued

# (7) Flowchart

# (8) Program listing

# · Description of label used for executing application routine

DIVSOR : Lowest address of the RAM area containing the 8-digit (4-byte) dividend and 8-digit

quotient

DIVIND : Lowest address of the area containing the 8-digit (4-byte) remainder resulting from division

RMIND : Lowest address of the area containing 8-digit (4-byte) divisor

QUOFLAG: Quotient sign flag

QUOFLAG = 0 ... Sign of quotient is positive QUOFLAG = 1 ... Sign of quotient is negative

REMFLAG: Remainder sign flag

REMFLAG = 0 ... Sign of remainder is positive REMFLAG = 1 ... Sign of remainder is negative

SFLAG : Sign identification flag

SFLAG = 0 ... Same signs SFLAG = 1 ... Different signs

ERRFLAG: Error flag

ERRFLAG = 0 ... No error has occurred ERRFLAG = 1 ... An error occurred

# . Example of program listing for main routine

```

MVVOM

DIVSOR , #42H

DIVSOR+2 , #65H

MVVOM

MVVOM

DIVIND , #12H

MVVOM

DIVIND+2 , #34H

CALL

!BCDDIV

ВT

ERRFLAG, $ERROR

ERROR:

CLR1

ERRFLAG

; clear error flag

```

**Remark** Set the dividend and divisor as shown, then call the subroutine.

# · Program listing for this application routine

```

NAME

BCDIVR

; *

decimal division

8 digit <- 8 digit / 8 digit

input condition

; *

dividend <- (DIVIND+3, ..., DIVIND)</pre>

; *

<- (DIVSOR+3, ..., DIVSOR)

divisor

output condition

; *

quotient <- (DIVIND+3, ..., DIVIND)

remainder <- (RMIND+3, ..., RMIND)</pre>

; *

PUBLIC

BCDDIV

BCDSUB

EXTRN

EXTRN

BCDADD, BCDAD2

EXTRN

DIVSOR, DIVIND, RMIND

EXTBIT ERRFLAG

EXTBIT

SFLAG

EXTBIT

REMFLAG, QUOFLAG

BYTNUM

EQU

CSEG

BCDDIV:

; clear error flag

CLR1

ERRFLAG

;

**** check / divisor = 0 ? ****

;

C, #4

; C-register <- 4

MOV

; Acc <- 0

MOV