## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

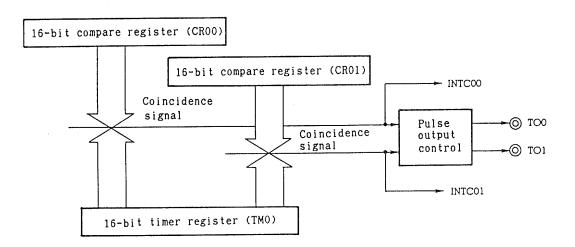

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

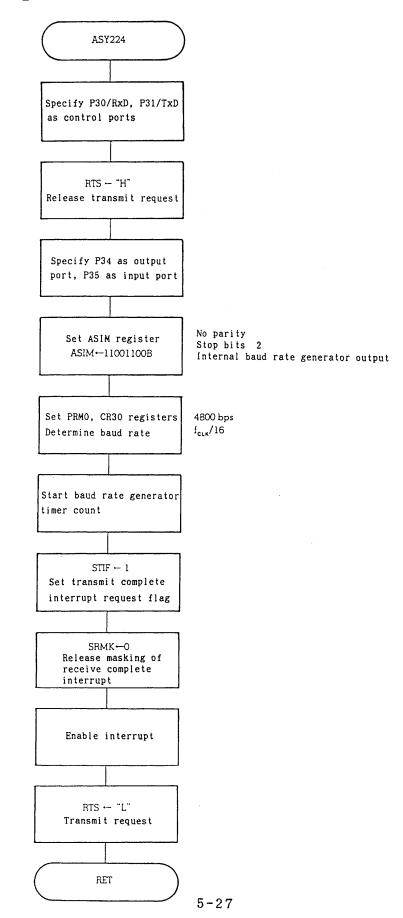

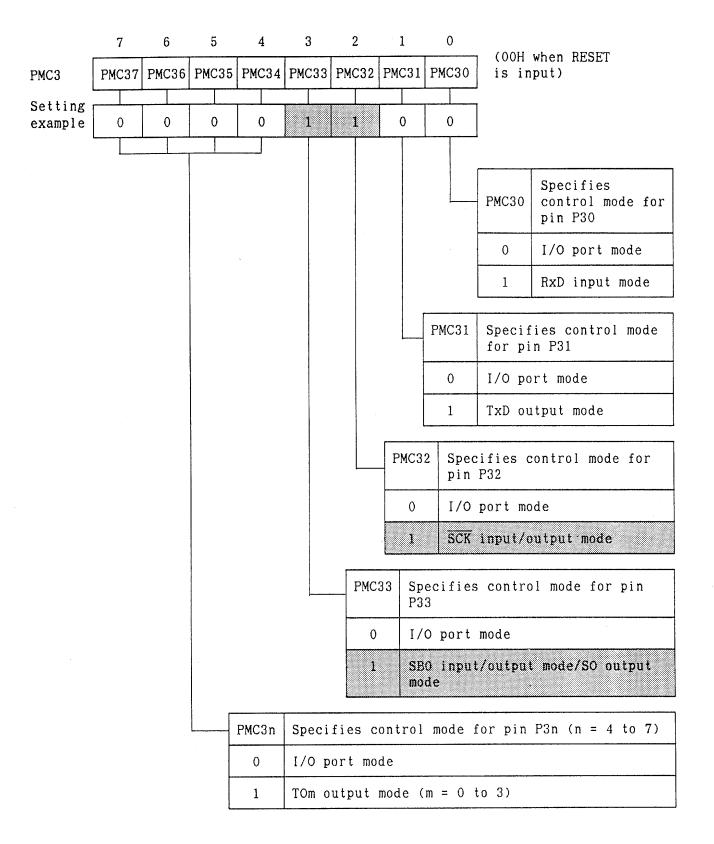

Send any inquiries to http://www.renesas.com/inquiry.

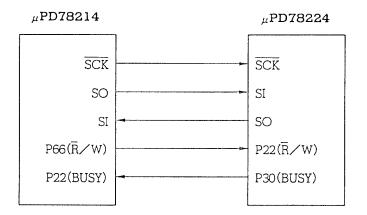

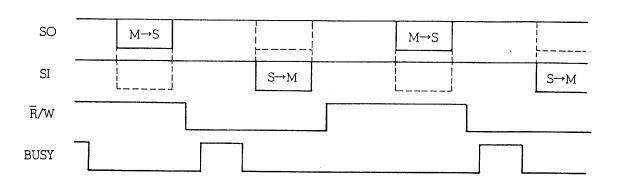

## Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# APPLICATION NOTE

# RENESAS

# 78K/I SERIES

## 8-BIT SINGLE-CHIP MICROCOMPUTER

## **BASIC GUIDE**

μPD78214 SERIES μPD78218A SERIES μPD78224 SERIES μPD78234 SERIES μPD78244 SERIES

> Document No. IEA-1220E (0. D. No. IEA-607E) Date Published December 1993 P Printed in Japan

# APPLICATION NOTE

# 78K/I SERIES

## 8-BIT SINGLE-CHIP MICROCOMPUTER

**BASIC GUIDE**

μPD78214 SERIES μPD78218A SERIES μPD78224 SERIES μPD78234 SERIES μPD78244 SERIES

The application circuits and their parameters are for references only and are not intended for use in actual design-in's.

### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

The devices listed in this document are not suitable for use in aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. If customers intend to use NEC devices for above applications or they intend to use "Standard" quality grade NEC devices for applications not intended by NEC, please contact our sales people in advance.

Application examples recommended by NEC Corporation

Standard: Computer, Office equipment, Communication equipment, Test and Measurement equipment, Machine tools, Industrial robots, Audio and Visual equipment, Other consumer products, etc.

Special: Automotive and Transportation equipment, Traffic control systems, Antidisaster systems, Anticrime systems, etc.

Contents Modified or Added in This Edition

| Page       | Contents                                              |

|------------|-------------------------------------------------------|

| Throughout | Description regarding the uPD78P224 has been deleted. |

### INTRODUCTION

#### Target reader:

This application note is designed to provide information regarding the functions of the 78K/II series to the user engineers who design application programs for a system using the 78K/II series products.

| 78K/II | series products  |   |                                         |

|--------|------------------|---|-----------------------------------------|

| -      | uPD78214 series  | : | uPD78212, uPD78213, uPD78214,           |

|        |                  |   | uPD78P214, uPD78212(A), uPD78213(A),    |

|        |                  |   | uPD78214(A), uPD78P214(A)               |

|        | uPD78218A series | : | uPD78217A, uPD78218A, uPD78P218A,       |

|        |                  |   | uPD78218A(A)                            |

| -      | uPD78224 series  | : | uPD78220, uPD78224, uPD78P224           |

| -      | uPD78234 series  | : | uPD78233, uPD78234, uPD78237, uPD78238, |

|        |                  |   | uPD78P238, uPD78234(A), uPD78238(A)     |

| -      | uPD78244 series  | : | uPD78243, uPD78244                      |

Objective:

This application note is designed to provide information regarding the basic functions of the 78K/II series to the users. Application program examples are provided to enhance the user's understanding. However, it must be noted that the programs and hardware configurations shown in this application note are just examples and not intended to be used for commercial productions.

Configuration:

This application note is configured as follows:

- Outline

- Software Part

- Hardware Program examples

The following application notes are also provided separately:

- Application Part (IEA-700)

- Floating Point Operatin Program Part (IEA-686)

How to read:

Unless otherwise specifically noted, the contents of this application note are targeted for all of the 78K/II series products. The index is used to indicate whether or not there is any difference.

o How to read the index:

Can be used as is.

Some portion can be used, and some other portion cannot be used.

None : Cannot be used as is.

Refer to the text for details.

- For examples:

$\rightarrow$  Read according to the table of contents.

- To find out how to use instructions:  $\rightarrow$  Read according to the table of contents.

- For examples of how to use internal hardware:

→ Read cover to cover for all examples, or refer to the table of contents or Appendix B to see a certain product.

- For the application examples for a certain product:  $\rightarrow$  Refer to Appendix B

- For an example for a certain application example:

→ Refer to both the table of contents and Appendix B.

#### Quality grade:

The uPD78212(A), uPD78213(A), uPD78214(A) and uPD78P214(A) are "special" quality grade versions of the uPD78212, uPD78213, uPD78214 and uPD78P214 respectively. The uPD78218A(A) is "Special" quality grade versions of the uPD78218A. The uPD78234(A) and uPD78238(A) are also "special" quality grade versions of the uPD78234 and uPD78238, respectively.

The examples shown in this application note are designed for "standard" quality versions for general electronics equipment. When using an example shown in this application note for an application requiring "special" quality grade, the actually used components and circuits must be evaluated for the quality grade.

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) publoished by NEC Corporation to know the quality grade specification on the devices and its recommended applicatins.

Applications:

o Standard grade

o Special grade

- Printers

- Cameras

- Fuel control, etc.

- Automotive electronics

- Typewriters

- PPCs

- Electronic musical instruments

- Air conditioners, etc.

### Examples:

Significance in data expression

: The left-most side is the most significant digit, and the right-most side is the least significant digit.

Active low indication :  $\overline{xxx}$  (a line is placed on the signal name)

Note: Explanation of contents noted in the text.

Notes: Contents which require attention.

Remarks: Complementary description of the contents.

Numeric expression: Binary ..... xxxx or xxxxB Decimal ..... xxxx Hexadecimal ..... xxxxH

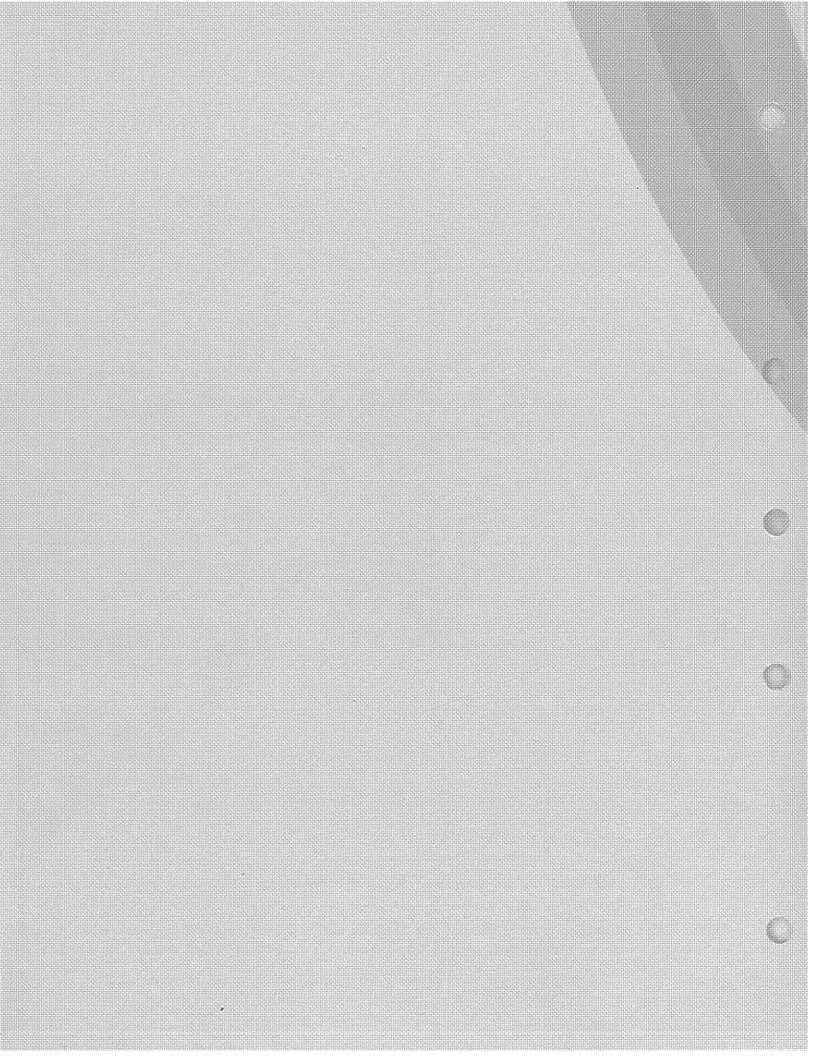

Register expression

never write any combination of code noted as "Not allowed" in register expression in the text.

```

Confusing characters: 0 (zero), 0 (oh)

: 1 (one), 1 (el), I (ai)

```

Related documents:

o List of common documents

| Document name                    |                                       | Document number       |

|----------------------------------|---------------------------------------|-----------------------|

| Users Manual Instruction Part    |                                       | I EU-754              |

| SBI User's Manual                |                                       | IEM-5040              |

|                                  | Fundamentals                          | This Application Note |

| Application Note                 | Application Part                      | IEA-700               |

|                                  | Floating Point Operation Program Part | IEA-686               |

| Selection Guide                  |                                       | IF-304                |

| Development Tool Selection Guide |                                       | EF-231                |

| Instruction Reference Table      |                                       | IEM-5101              |

| Instruction Set                  |                                       | IEM-5102              |

## o Individual documents

## uPD78214 series

| Product name<br>Document name | uPD <b>782</b> 12 | uPD78213 | uPD78214 | uPD78P214 |

|-------------------------------|-------------------|----------|----------|-----------|

| Brochure                      |                   | IB-      | 5036     |           |

| Data Sheet                    | IC-8149           | IC-      | 7649     | IC-7732   |

| User's Manual Hardware Part   |                   | I EM-    | 5119     |           |

| Mode Register Reference Table |                   | I EM-    | 5100     |           |

| Product name<br>Document name | uPD78212(A) | uPD78213(A) | uPD78214(A) | uPD78P214(A) |

|-------------------------------|-------------|-------------|-------------|--------------|

| Data Sheet                    | IC-8147     | IC-8        | 234         | IC-8589      |

| User's Manual Hardware Part   |             | I EM-       | 5119        |              |

| Mode Register Reference Table |             | I EM-       | 5100        |              |

uPD78218A series

| Product name<br>Document name                | uPD78217A | uPD78218A | uPD78P218A | uPD78218A(A) |

|----------------------------------------------|-----------|-----------|------------|--------------|

| Brochure                                     |           | Ι         | F-288      |              |

| Data Sheet                                   | IC-8132   | IC-8131   | IC-8133    | [C-8685      |

| User's Manual Hardware Part                  |           | ΙE        | U-755      |              |

| Special function Register<br>Reference Table | I EM-5532 |           |            |              |

## uPD78224 series

| Product name<br>Document name                | uPD <b>7822</b> 0 | uPD78224 | uPD78P224 |

|----------------------------------------------|-------------------|----------|-----------|

| Brochure                                     |                   | IB-5011  |           |

| Data Sheet                                   | IC-5              | 457      | IC-7757   |

| User's Manual Hardware Part                  |                   | IEM-5019 |           |

| Special function Register<br>Reference Table |                   | IEM-999  |           |

## uPD78234 series

| Product name<br>Document name                | uPD <b>78233</b> | uPD78234 | uPD78237 | uPD78238 | uPD78P238 |

|----------------------------------------------|------------------|----------|----------|----------|-----------|

| Brochure                                     |                  |          | IF-207   |          |           |

| Data Sheet                                   | IC-              | 7902     | IC-8348  | IC-8028  | IC-8030   |

| User's Manual Hardware Part                  |                  |          | IEU-718  |          |           |

| Special function Register<br>Reference Table |                  |          | IEM-5515 |          |           |

| Product name<br>Document name                | uPD78234(A) | uPD78238(A) |

|----------------------------------------------|-------------|-------------|

| Brochure                                     | -           |             |

| Data Sheet                                   | IC-8146     | IC-8727     |

| User's Manual Hardware Part                  | I EU-       | 718         |

| Special function Register<br>Reference Table | _           |             |

## uPD78244 series

| Product name<br>Document name                | uPD78243 | uPD78244 |

|----------------------------------------------|----------|----------|

| Brochure                                     | I F-2    | 14       |

| Data Sheet                                   | IC-8355  | IC-8070  |

| User's Manual Hardware Part                  | I EU-    | 747      |

| Special function Register<br>Reference Table | I EM-    | 5528     |

## Table of Contents

| CHAPTER 1 OVERVIEW                                                                                                                                                                         |                                                   | 1        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------|

| 1.1 Organization of This Applicatio                                                                                                                                                        | n Note 1-                                         | 1        |

| 1.1.1 Legend for discussion on sof<br>1.1.2 Legend for discussion on har                                                                                                                   |                                                   |          |

| 1.2 Use of Application Programs                                                                                                                                                            |                                                   | 5        |

| 1.3 Features of 78K/II Series Produ                                                                                                                                                        | cts 1-                                            | 6        |

| CHAPTER 2 SOFTWARE PART                                                                                                                                                                    |                                                   | 1        |

| 2.1 Binary Operations                                                                                                                                                                      |                                                   | 2        |

| <ul> <li>2.1.1 Binary addition</li> <li>2.1.2 Binary subtraction</li> <li>2.1.3 Binary multiplication</li> <li>2.1.4 Binary division</li> </ul>                                            | · · · · · · · · · · · · · · · · · · 2 - · · 2 - · | 7<br>11  |

| 2.2 Decimal Operations                                                                                                                                                                     |                                                   | 26       |

| 2.2.1Decimal addition2.2.2Decimal subtraction2.2.3Decimal multiplication2.2.4Decimal division                                                                                              | 2-3<br>2-3<br>2-3                                 | 34<br>37 |

| 2.3 Shift Processing                                                                                                                                                                       |                                                   | 50       |

| <ul> <li>2.3.1 Shifting N-byte data to righ</li> <li>2.3.2 Shifting N-byte data to left</li> <li>2.3.3 Shifting N-digit data 1 digi</li> <li>2.3.4 Shifting N-digit data 1 digi</li> </ul> | t to right 2-1                                    | 52<br>54 |

| 2.4 Data Conversion Processing                                                                                                                                                             |                                                   | 58       |

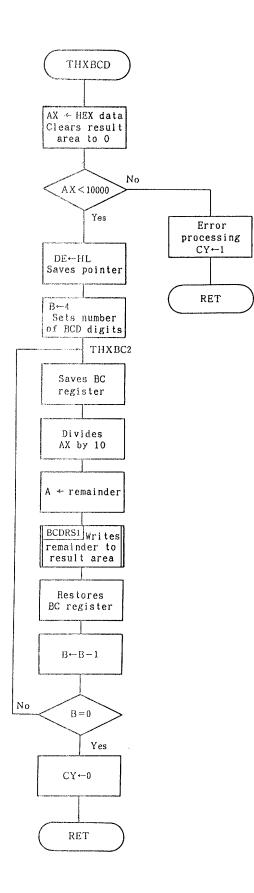

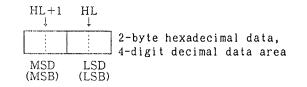

| <ul> <li>2.4.1 Conversion from hexadecimal decimal (BCD)</li> <li>2.4.2 Conversion from decimal (BCD)</li> </ul>                                                                           |                                                   | 58       |

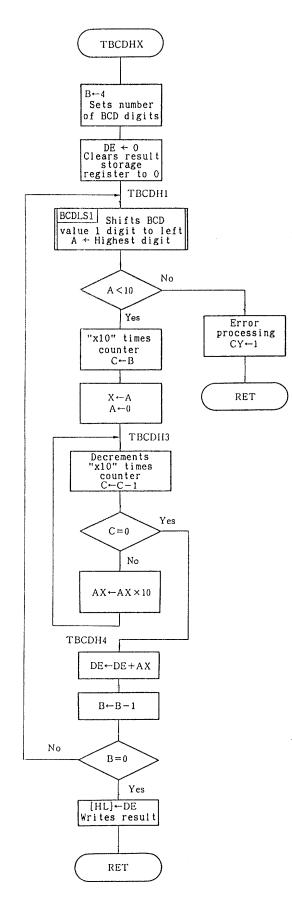

| hexadecimal (HEX)<br>2.4.3 Converting ASCII into hexade<br>2.4.4 Converting hexadecimal (HEX)                                                                                              |                                                   | 66       |

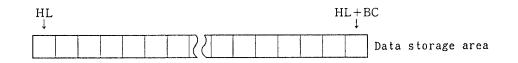

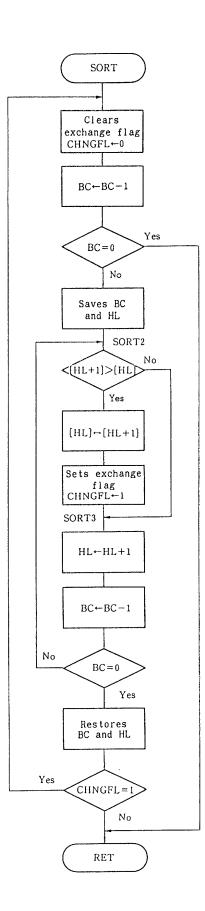

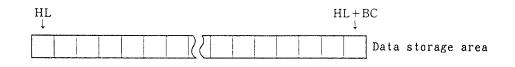

| 2.5 Data Processing                                                                                                                                                                        |                                                   | 72       |

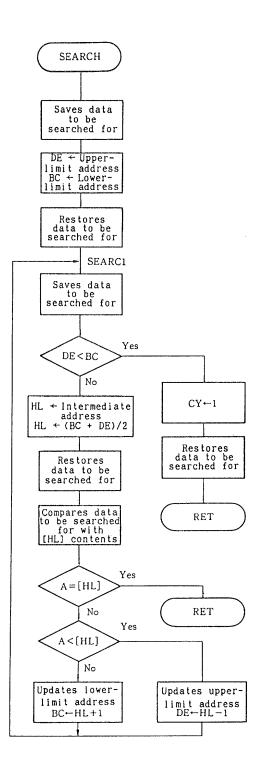

| 2.5.1Sorting dataSorting data2.5.2Searching dataSearching data                                                                                                                             |                                                   |          |

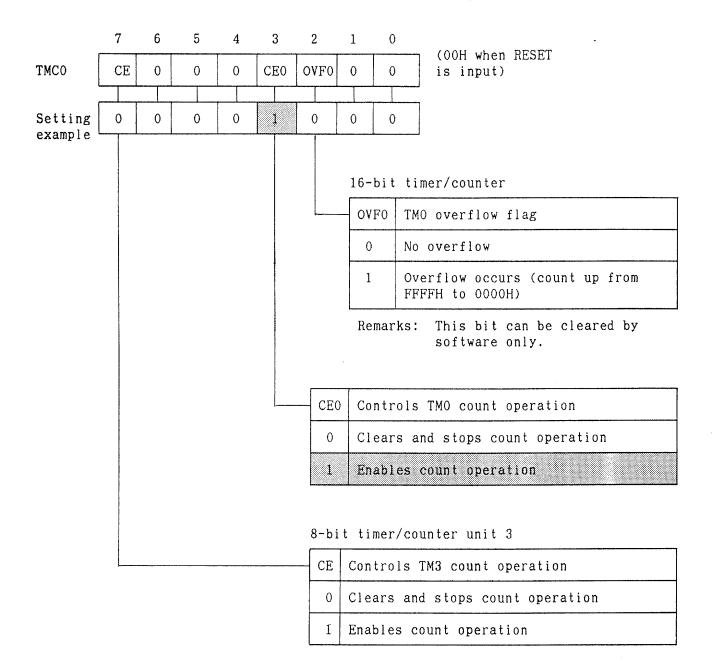

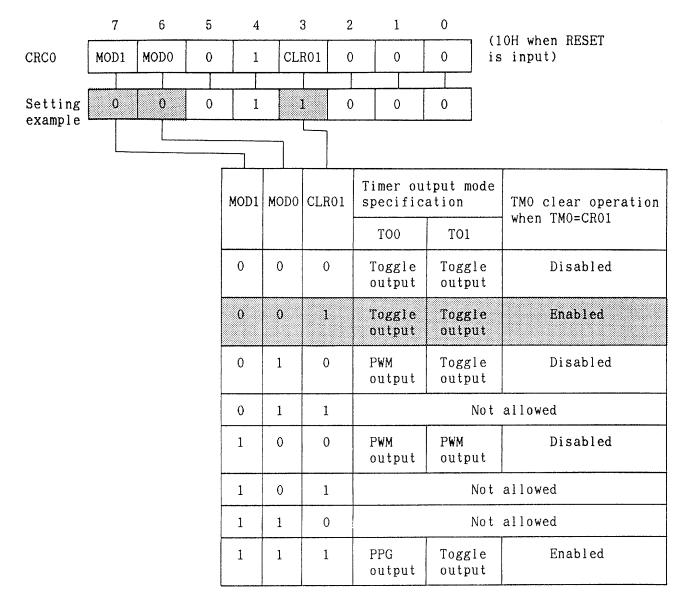

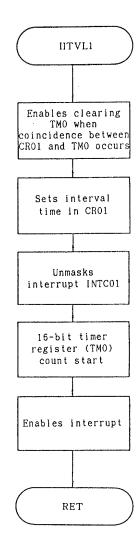

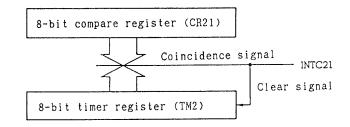

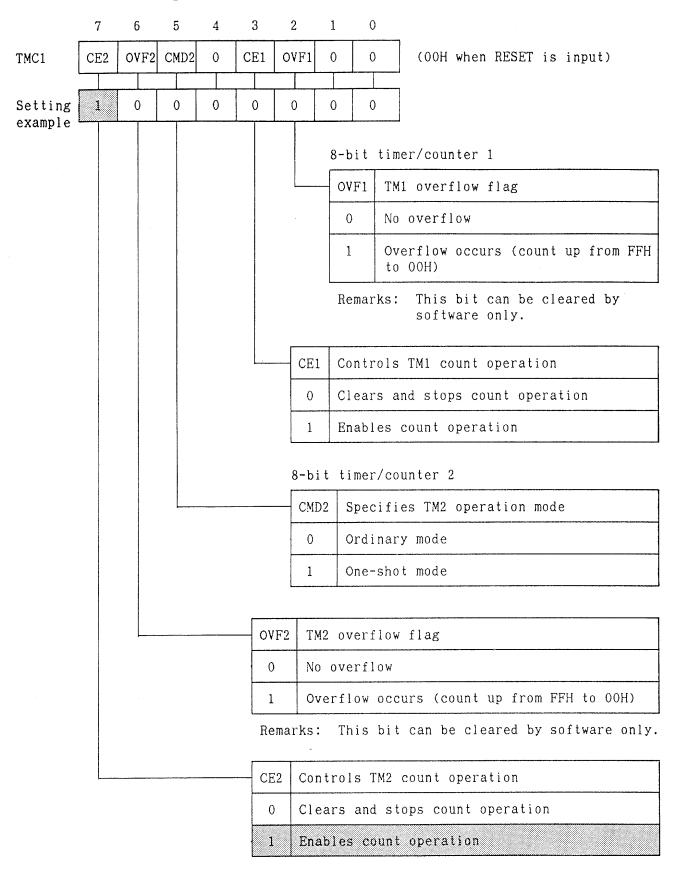

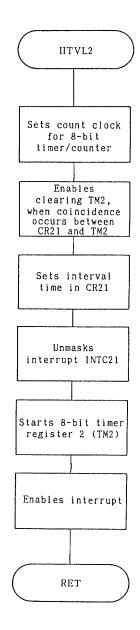

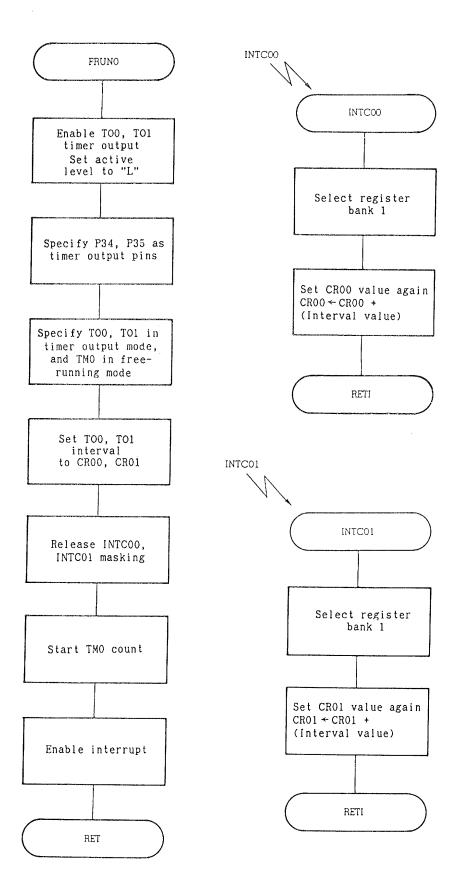

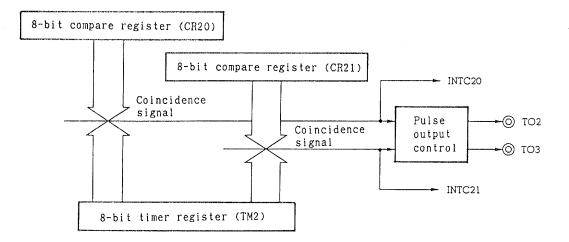

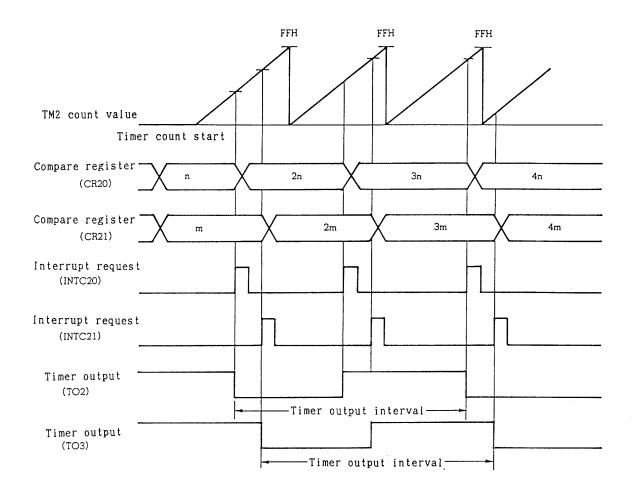

| CHAPTER 3         | TIMER/COUNTER PROGRAM EXAMPLES                                                                                                                   | 3-1                         |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 3.13.23.33.43.5   | Internal Interval Timer<br>Programmable Rectangular Pulse Output<br>Free-running Interval Timer<br>PWM/PPG Output<br>Software Triggered One-shot | 3-4<br>3-22<br>3-33<br>3-61 |

| 3.6               | Pulse Output<br>Pulse Cycle Measurement                                                                                                          |                             |

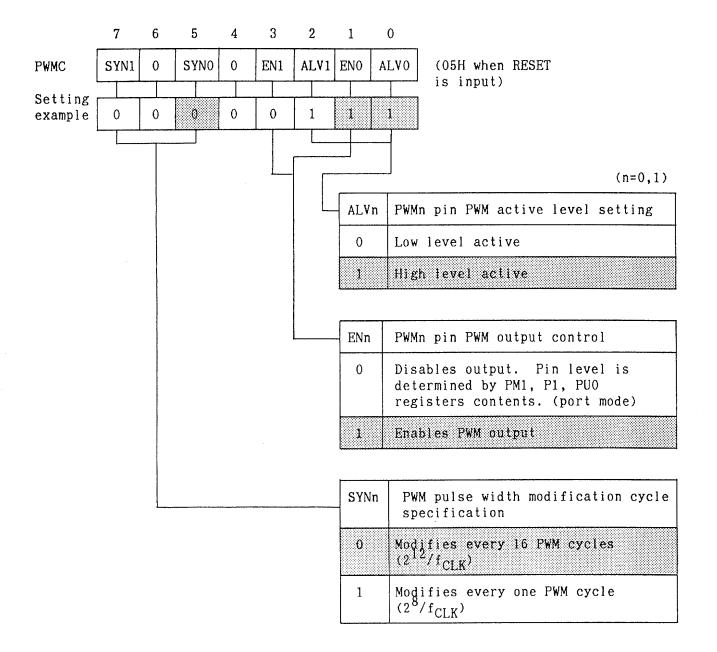

| CHAPTER 4         | PWM OUTPUT UNIT PROGRAM EXAMPLE (uPD78234)                                                                                                       | 4-1                         |

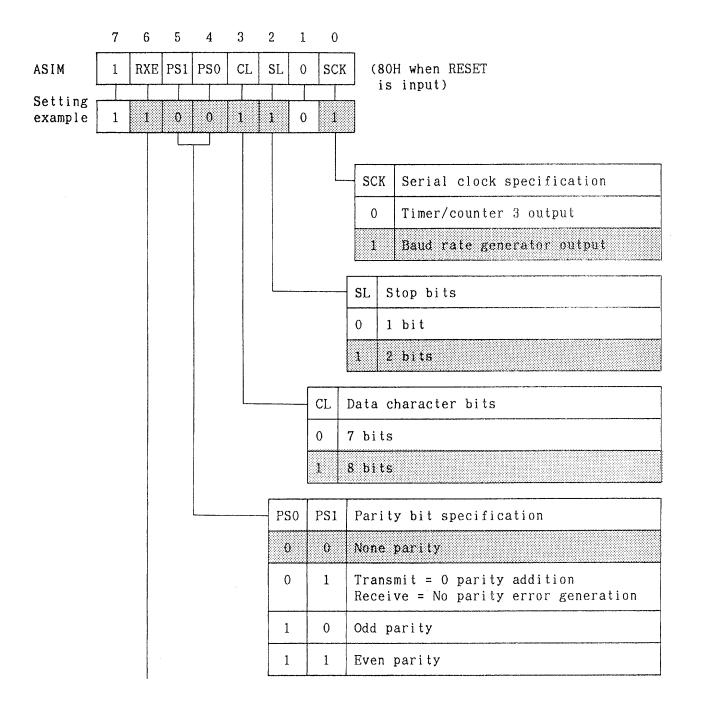

| CHAPTER 5         | ASYNCHRONOUS SERIAL INERFACE PROGRAM<br>EXAMPLES                                                                                                 | 5-1                         |

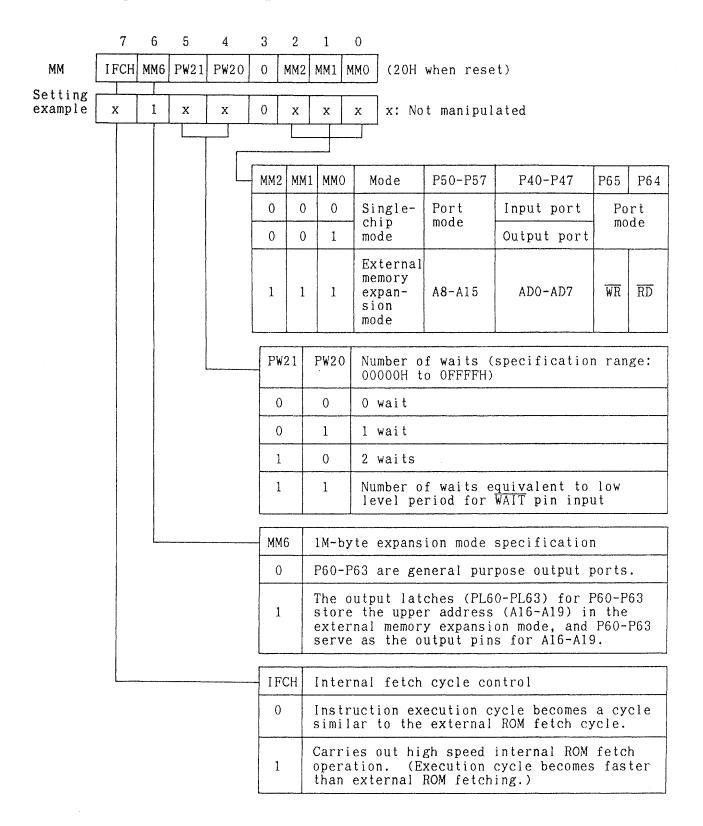

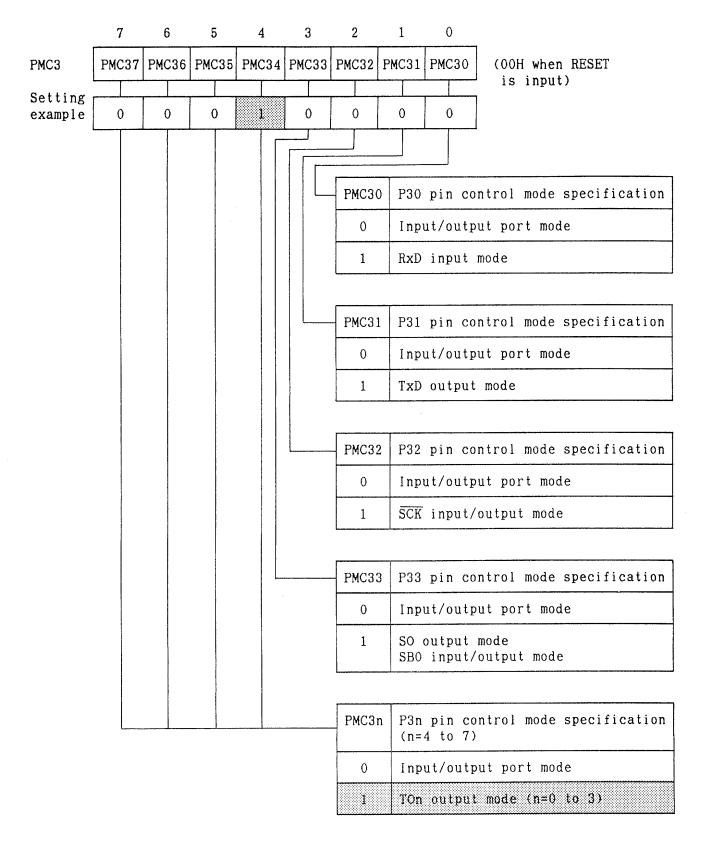

| 5.1<br>5.2<br>5.3 | Operation Outline<br>Program Description<br>Mode Register Setting Example                                                                        | 5-2<br>5-4<br>5-6           |

| CHAPTER 6         | THREE-LINE SERIAL INTERFACE                                                                                                                      | 6-1                         |

| CHAPTER 7         | INTERRUPT PROCESSING PROGRAM EXAMPLES                                                                                                            | 7-1                         |

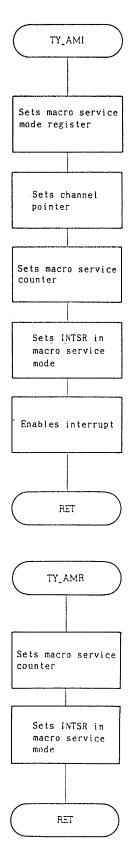

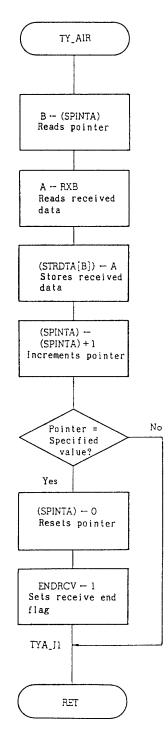

| 7.1<br>7.2        | UART Reception Processing<br>Parallel Data Input in Synchronization                                                                              | 7-1                         |

| 7.3               | with External Interrupt Request<br>Open Loop Control for Stepping                                                                                | 7-13                        |

| 7.4               | Motor (1)<br>Open Loop Control for Stepping<br>Motor (2)                                                                                         | 7-28<br>7-43                |

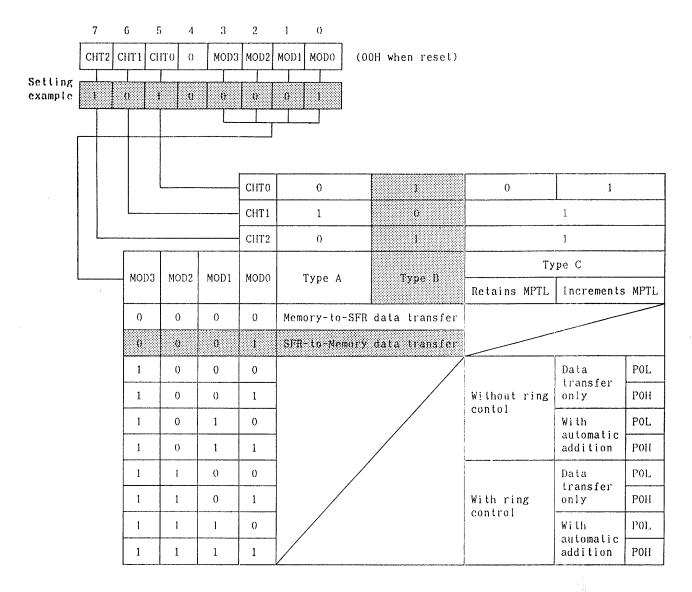

| CHAPTER 8         | A/D CONVERTER PROGRAM EXAMPLES (uPD78214)                                                                                                        | 8-1                         |

| CHAPTER 9         | COMPARATER PROGRAM EXAMPLE (uPD78224)                                                                                                            | 9-1                         |

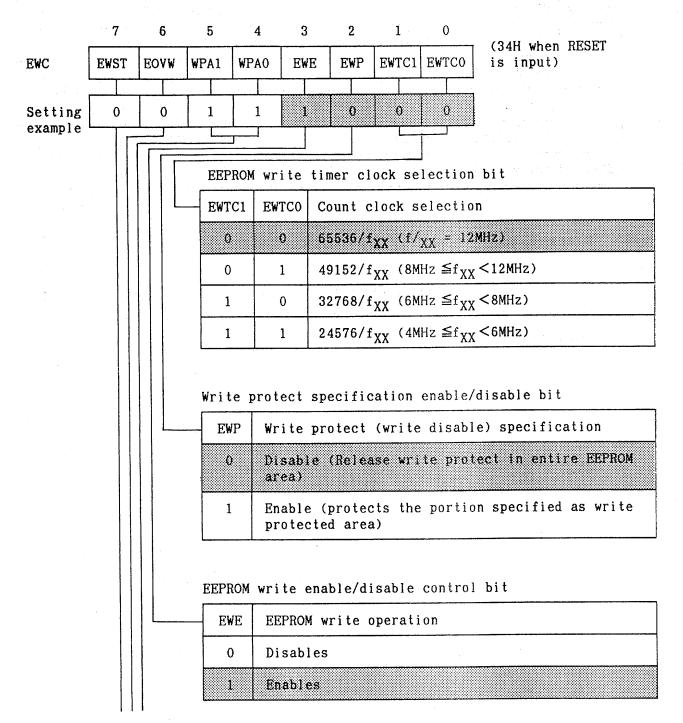

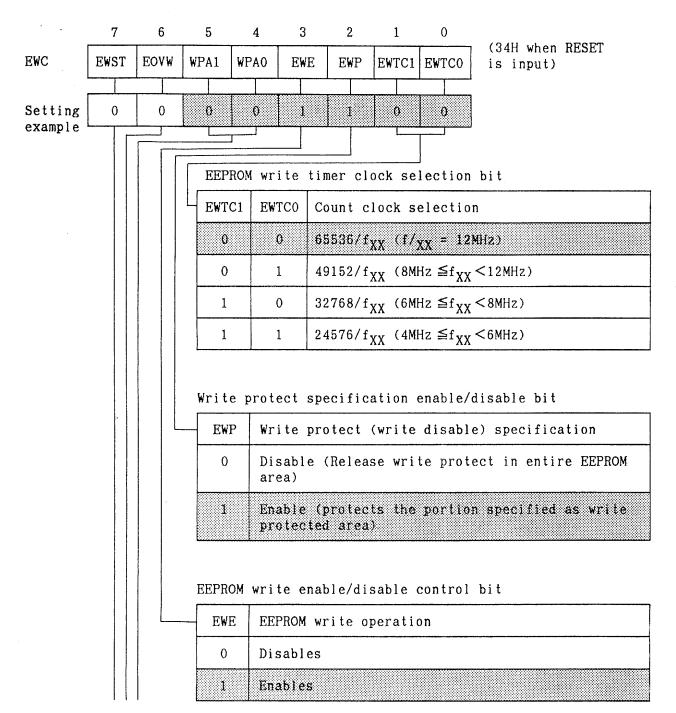

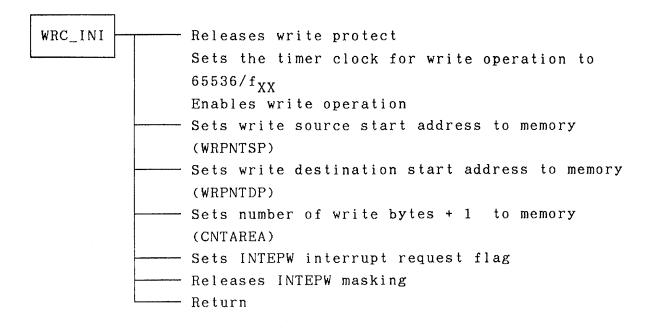

| CHAPTER 10        | EEPROM PROGRAM EXAMPLE (uPD78244)                                                                                                                | 10-1                        |

| 10.1<br>10.2      | Operation Outline<br>Program Example                                                                                                             | 10-1<br>10-4                |

| APPENDIX A        | NOTES ON 78K/II SERIES PROGRAMMING                                                                                                               | A-1                         |

| A.1               | Notes on Vector Interrupt Processing                                                                                                             | A-1                         |

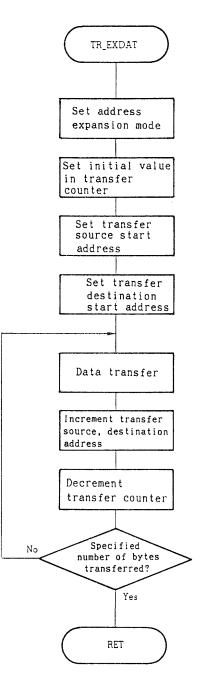

| A.2               | Notes on Accessing External Expansion Data<br>Memory for uPD7821x and uPD7822x                                                                   | A-5                         |

| A.3               | Notes on Accessing Port O and Real-Time<br>Output Port                                                                                           | A-6                         |

| APPENDIX B RA78K/II                                                                 | B <b>-</b> 1 |

|-------------------------------------------------------------------------------------|--------------|

| B.1 File Provided with RA78K/II                                                     | B-1          |

| B.1.1SFRBIT.DEFB.1.2INTMS.DEF                                                       | B-3<br>B-3   |

| B.2 Register Bank Area Assuring Method                                              | B <b>-</b> 4 |

| B.2.1PreparationB.2.2How to use                                                     | B-4<br>B-8   |

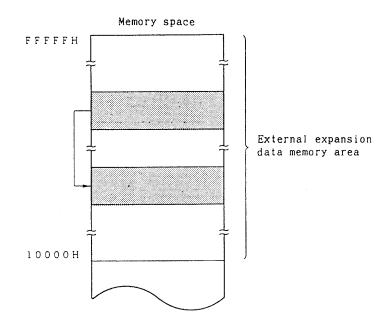

| B.3 How to Use 1M-byte Extension Data<br>Memory Space                               | B-10         |

| APPENDIX C LIST OF 78K/II SERIES PRODUCTS                                           | C-1          |

| APPENDIX D CORRESPONDENCE FOR PROGRAMS, DEVICES AND<br>INTERNAL PERIPHERAL HARDWARE | D-1          |

## List of Figures

| Fig. No. | Title                                      | Page  |

|----------|--------------------------------------------|-------|

| 1 - 1    | Clock Oscillation Circuit                  | 1-5   |

| 1-2      | Peripheral Hardware Correlation Diagram    | 1-7   |

| 2 - 1    | Binary Representation                      | 2-2   |

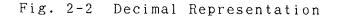

| 2 - 2    | Decimal Representation                     | 2-26  |

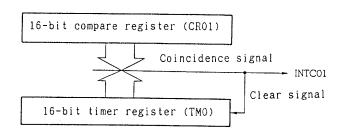

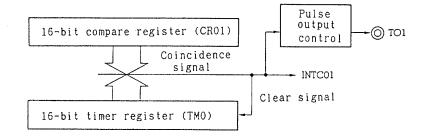

| 3-1      | Interval Timer Generating INTCO1 Interrupt |       |

|          | Request                                    | 3-4   |

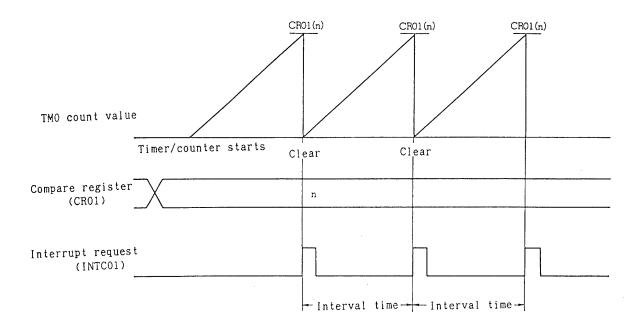

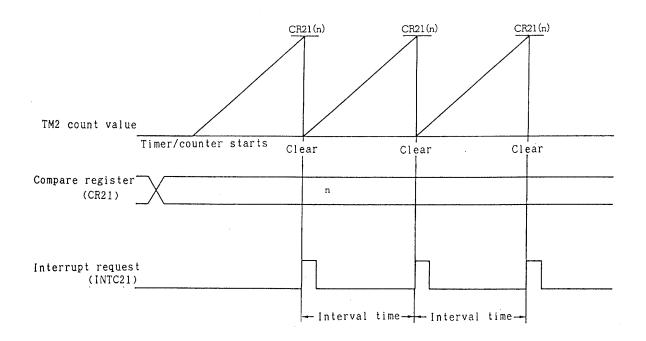

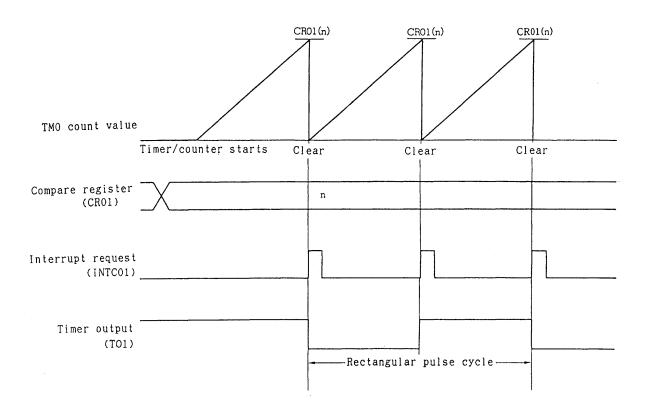

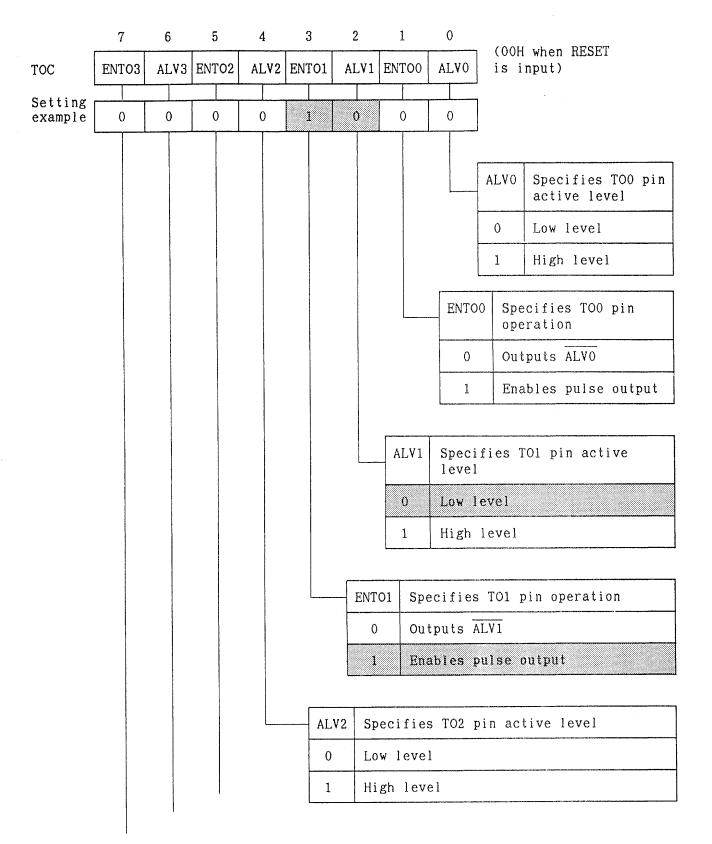

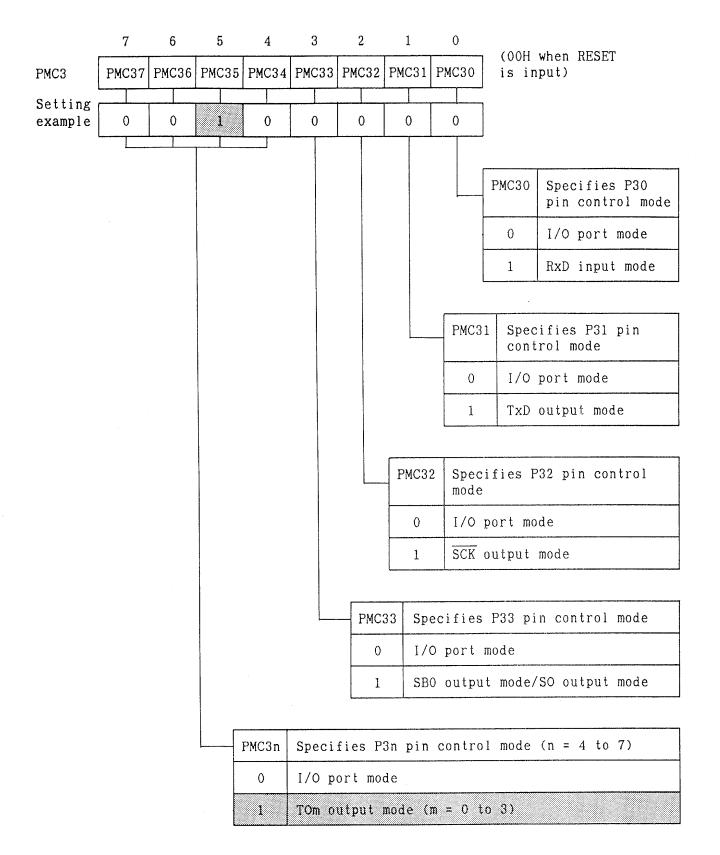

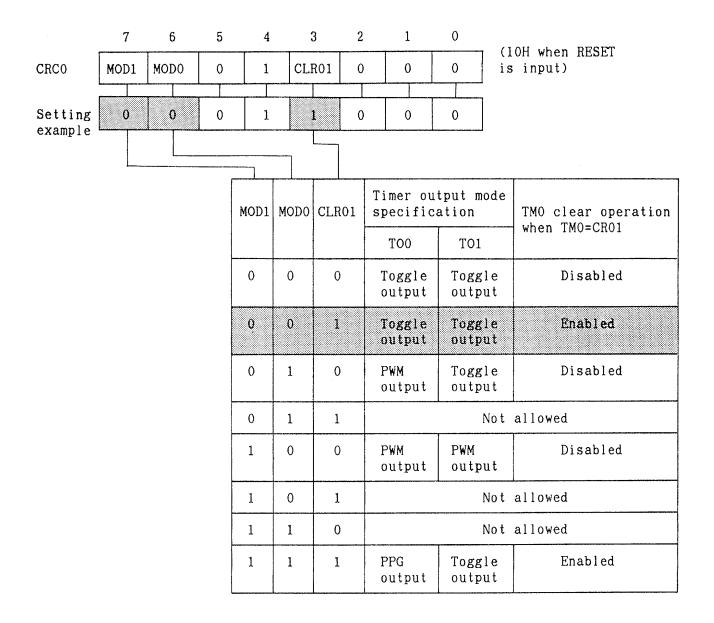

| 3-2      | Timing Chart                               | 3 - 5 |

| 3-3      | Interval Timer Generating Interrupt        |       |

|          | Request INTC21                             | 3-12  |

| 3-4      | Timing Chart                               | 3-12  |

| 3-5      | Rectangular Pulse Output from TO1 Pin      | 3-22  |

| 3-6      | Timing Chart                               | 3-23  |

| 3-7      | Timer Outputs from TOO/TO1 Pins            | 3-33  |

| 3-8      | Timing Chart for Outputting Timer from     |       |

|          | T00/T01 Pins                               | 3-34  |

| 3-9      | Timer Outputs from TO2/TO3 Pins            | 3-46  |

| 3-10     | Timing Charts for Outputting Timer from    |       |

|          | TO2/TO3 Pins                               | 3-47  |

| 3-11     | PWM Output from TOO Pin                    | 3-61  |

| 3-12     | Timing Chart for Outputting PWM from       |       |

|          | TOO Pin                                    | 3-62  |

| 3-13     | PWM Output from TO2 Pin                    | 3-74  |

| 3-14     | Timing Chart for Outputting PWM from       |       |

|          | PO2 Pin                                    | 3-75  |

| 3-15     | PPG Output from TOO Pin                    | 3-89  |

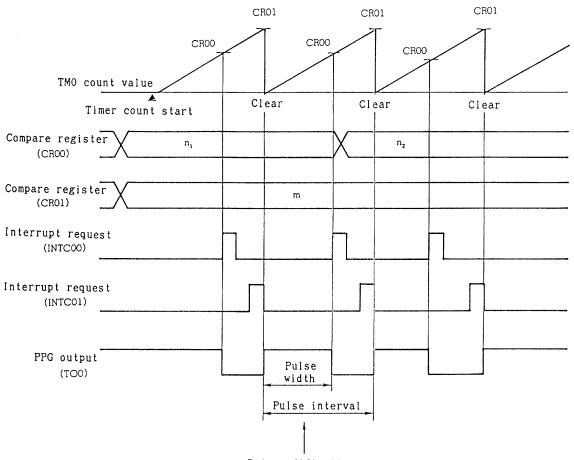

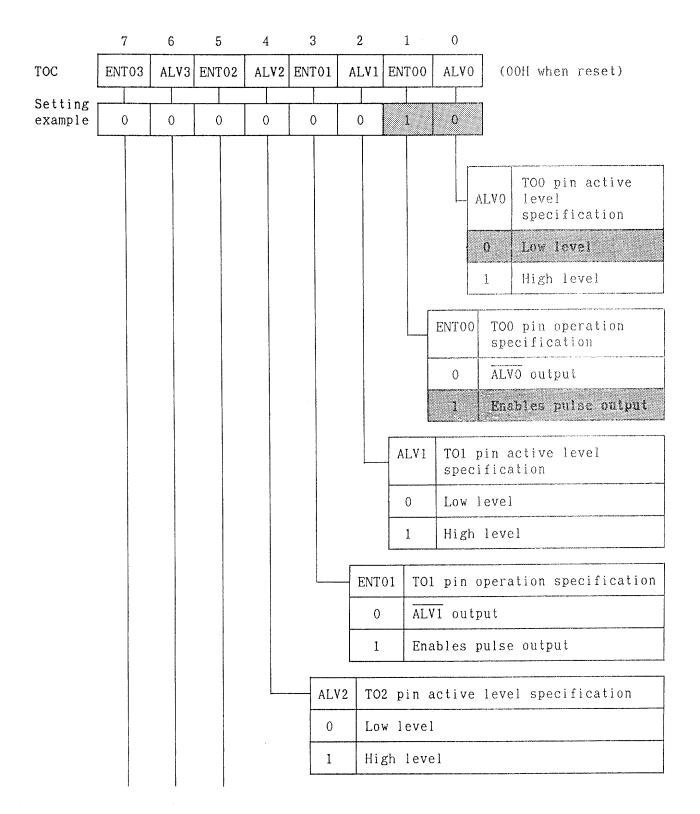

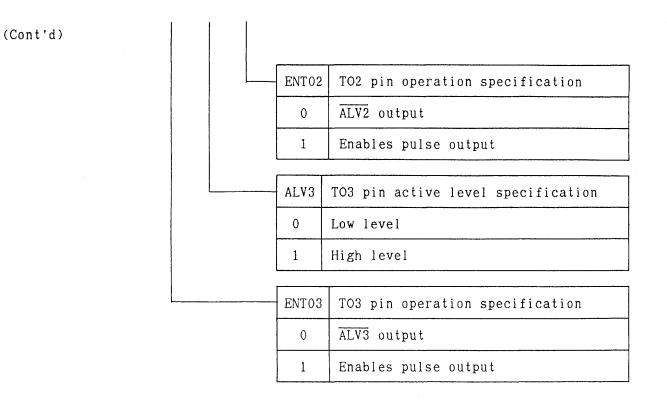

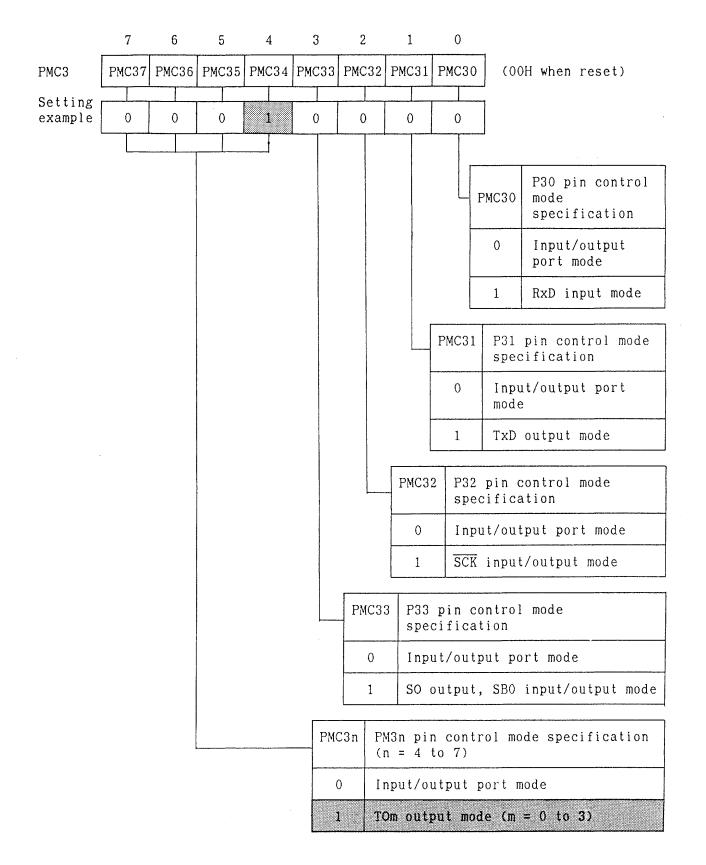

| 3-16     | Timing Chart for Outputting PPG from       |       |

|          | TOO Pin                                    | 3-90  |

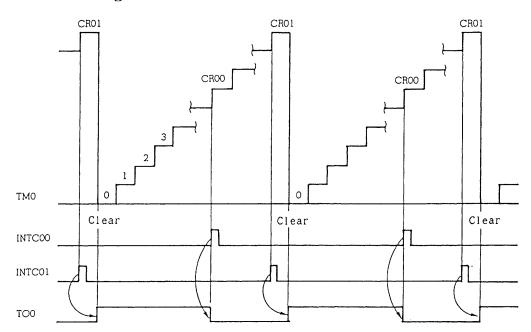

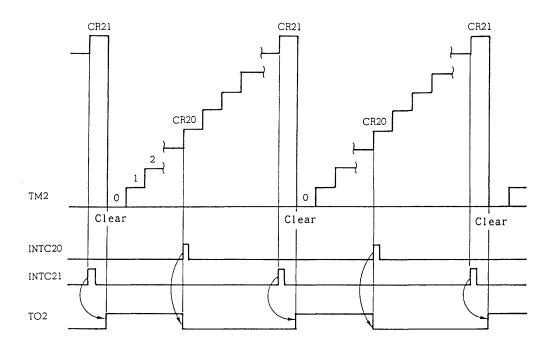

| 3-17     | PPG Output Timing (TMO)                    | 3-100 |

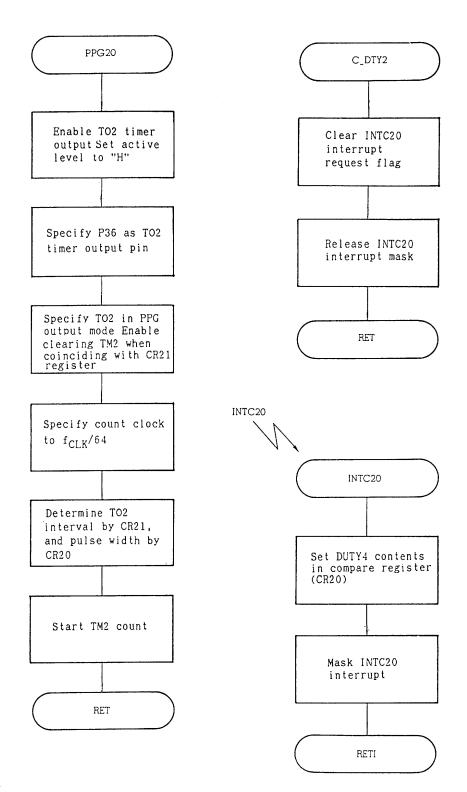

| 3-18     | PPG Output from TO2 Pin                    | 3-104 |

| 3-19     | Timing Chart for Outputting PPG from       |       |

|          | TO2 Pin                                    | 3-105 |

## Fig. No.

## Title

| 3-20  | PPG Output Timing (TM2)                      | 3-117 |

|-------|----------------------------------------------|-------|

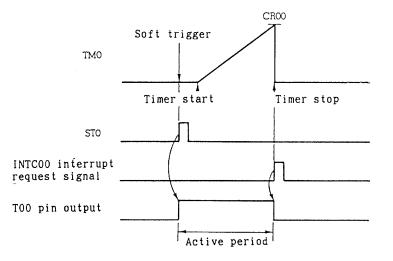

| 3-21  | Typical Example of Outputting One-Shot Pulse |       |

|       | from TOO Pin                                 | 3-121 |

| 3-22  | Pulse Cycle Measurement                      | 3-134 |

| 3-23  | Timing Chart                                 | 3-134 |

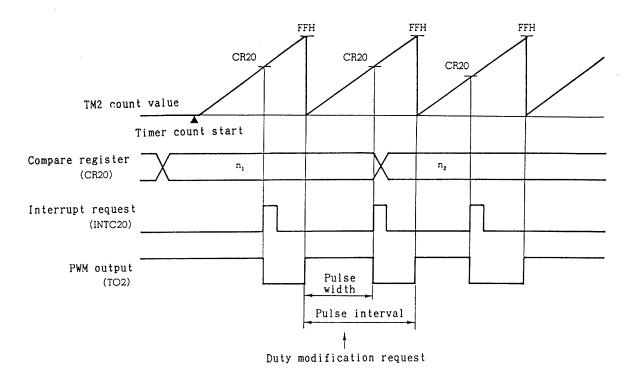

| 4-1   | Timing Chart for Outputting PWM from         |       |

|       | PWMO Pin                                     | 4-1   |

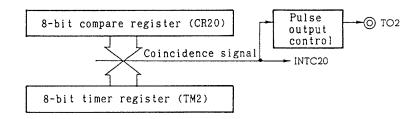

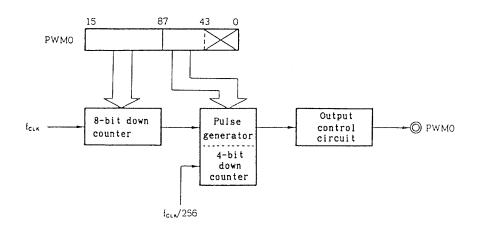

| 4-2   | PWM Output Function Block Diagram            | 4-2   |

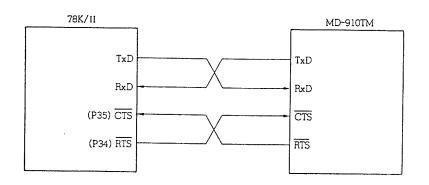

| 5-1   | Connection of $78K/II$ Series and MD-910TM   | 5-2   |

| 6-1   | Connection uPD78214 to uPD78224              | 6-1   |

| 6 - 2 | Timing Chart (Viewed from master)            | 6 - 2 |

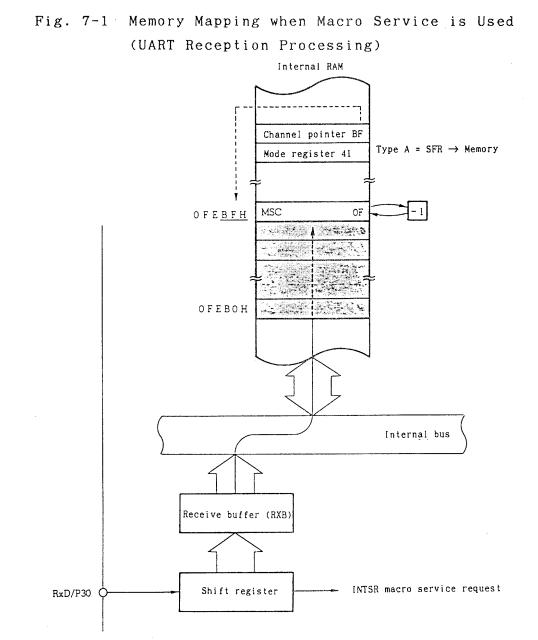

| 7-1   | Memory Mapping when Macro Service is Used    |       |

|       | (UART Reception Processing)                  | 7-3   |

| 7-2   | Memory Mapping when Macro Service is Used    |       |

|       | (Parallel Data Input)                        | 7-14  |

| 7-3   | Memory Mapping for Open Loop Control of      |       |

|       | Stepping Motor                               | 7-29  |

| 7-4   | Memory Map for Macro Service                 |       |

|       | (when MSC = 16 bits)                         | 7-44  |

| 7-5   | Automatic Addition Mode Timing Chart         |       |

|       | (Single Phase Energization)                  | 7-46  |

| 8-1   | Memory Mapping for A/D Converter Program     |       |

|       | Example                                      | 8-2   |

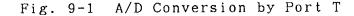

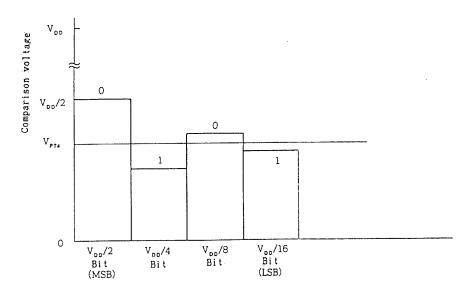

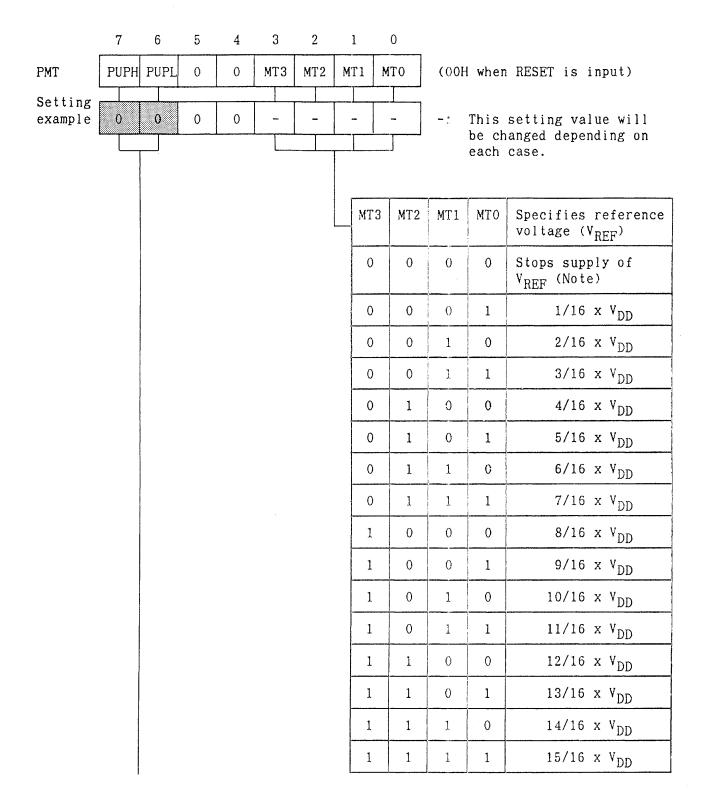

| 9-1   | A/D Conversion by Port T                     | 9-2   |

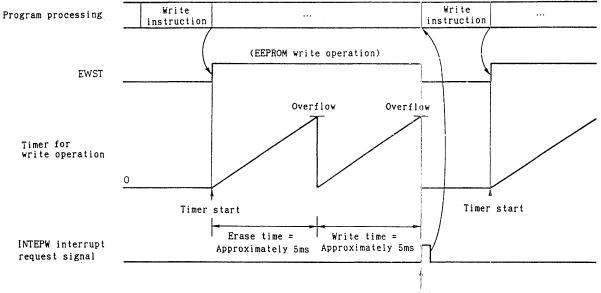

| 10-1  | Timing Chart for Writing to EEPROM           | 10-2  |

|       |                                              |       |

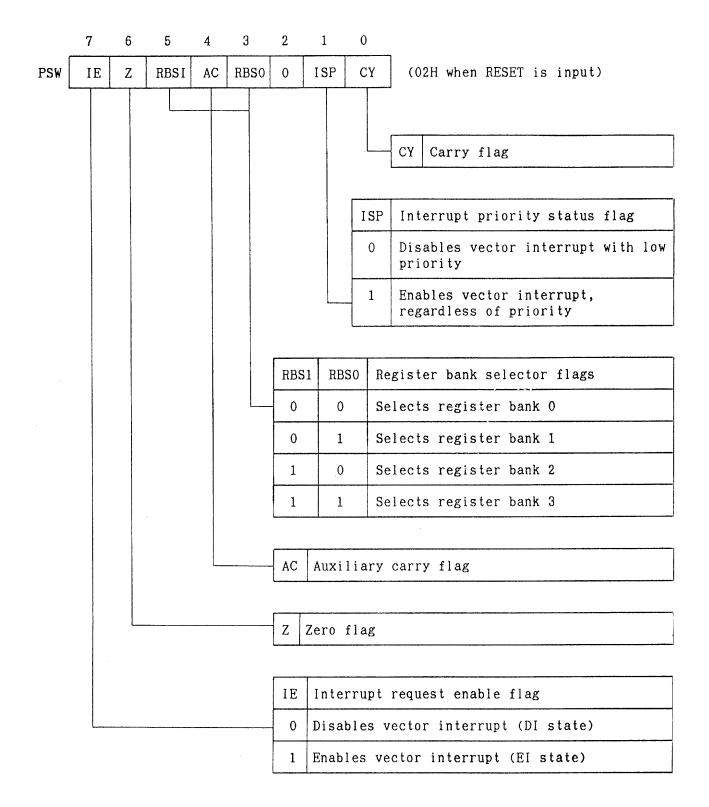

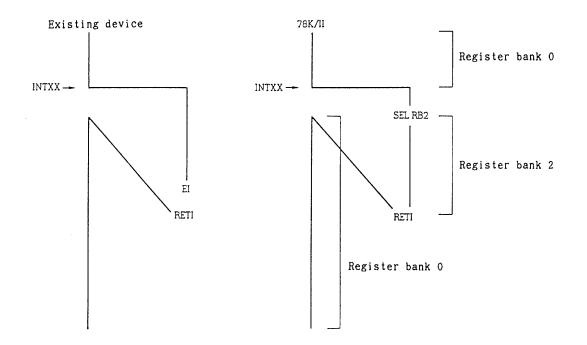

| A-1   | Program Status Word                          | A-2   |

| A-2   | Relation between Vector Interrupt and PSW    | A-3   |

|       |                                              |       |

| B-1   | Memory Space Use Example                     | B-10  |

## List of Tables

| Table No. |  |

|-----------|--|

|-----------|--|

Title

## Page

| 3-1   | uPD78214 Series Timer/Counter Functions    |       |

|-------|--------------------------------------------|-------|

|       | and Types                                  | 3-1   |

| 3-2   | Timer/Counter Functions and Types          |       |

|       | in uPD78218A Series, uPD78234 Series,      |       |

|       | uPD78244 Series                            | 3-2   |

| 3-3   | uPD78224 Series Timer/Counter Functions    |       |

|       | and Types                                  | 3-3   |

| 3-4   | Work Area Used by PWM Output Program       |       |

|       | by TMO                                     | 3-63  |

| 3-5   | Work Area Used for PWM Output Program      |       |

|       | by TM2                                     | 3-76  |

| 3-6   | Work Area Used by PPG Output Program       |       |

|       | by TMO                                     | 3-91  |

| 3-7   | Work Area Used by PPG Output Program       |       |

|       | by TM2                                     | 3-106 |

| 5-1   | 78K/II UART Baud Rate Setting Method       | 5-1   |

| 5 - 2 | UART Program Example Specifications        | 5-2   |

| 5-3   | Work Area Used by UART Program Example     | 5-3   |

| 5-4   | Flags Used by UART Program Example         | 5-4   |

| 6 - 1 | Work Areas for Three-Line Serial Interface |       |

|       | Program (Master)                           | 6-2   |

| 6 - 2 | Flags for Three-Line Serial Interface      |       |

|       | Program (Master)                           | 6-2   |

| 6-3   | Work Areas for Three-Line Serial Interface |       |

|       | Program (Slave)                            | 6-3   |

| 6 - 4 | Flags for Three-Line Serial Interface      |       |

|       | Program (Slave)                            | 6-3   |

| 7-1   | Interrupt Processing for 78K/II Series     | 7-1   |

| 7-2   | RAM Areas Used for Macro Service           |       |

|       | (MSC=16 bits)                              | 7-49  |

| 10-1  | RAM Areas used for EEPROM Program Example  | 10-6  |

| 10-2  | Input Parameters for EEPROM                |       |

|       | Program Example                            | 10-6  |

|       |                                            |       |

,

| 10-3       | Register Used for EEPROM Program                               | 10-7 |

|------------|----------------------------------------------------------------|------|

| B-1<br>B-2 | Segment Name and Allocation Location<br>Memory Area Definition |      |

| B-3        | Sement Allocation                                              |      |

| C-1        | List of 78K/II Series Products                                 | C-2  |

#### CHAPTER 1 OVERVIEW

#### 1.1 Organization of This Application Note

This Application Note contains the following items of information:

(1) Software

Chapter 2 of this Application Note presents software examples. The registers and memory areas to be used, input and output conditions, processing sequence, the number of steps required, flowchart, and program list for each application example are also presented.

#### (2) Hardware program examples

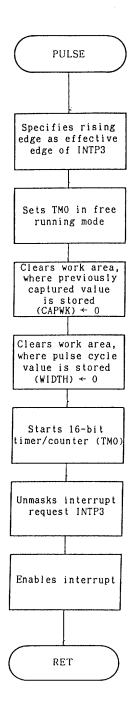

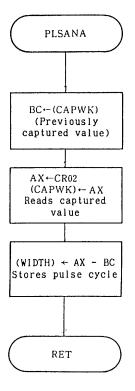

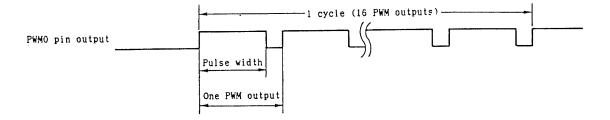

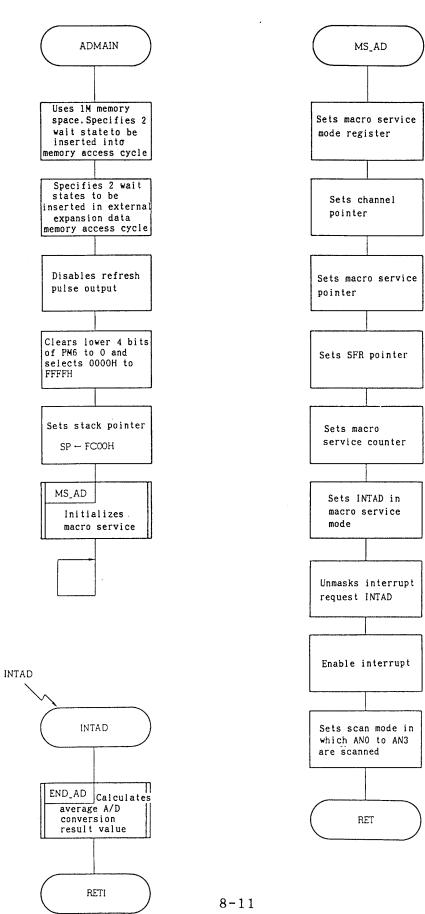

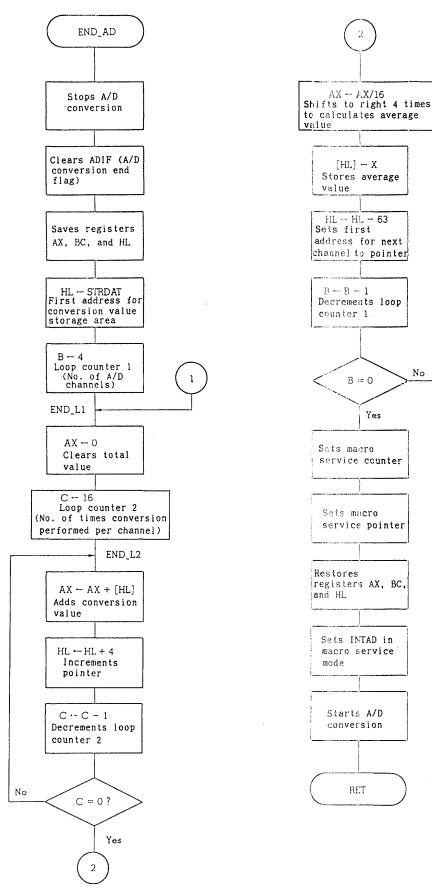

Chapters 3 through 10 discuss hardware examples. This chapter presents discussions on the operation, program, mode registers, input/output parameters, and registers to be used for each application example, along with the program example, flowchart, and program list necessary for the example.

1.1.1 Legend for discussion on software part

In Chapter 2, many software application examples are presented. Each example in this chapter includes these items of information:

(1) Registers

Under the heading "Registers", the registers used for the example program are presented. If the contents of the registers already used should not be destroyed, save the register contents to stack by executing the PUSH instruction, etc., before calling the example program.

(2) Memory

How the memory is to be used is indicated under this heading. Note that, when the example program has been executed, the memory work area contents become undefined.

(3) Input conditions

The input conditions necessary for using the example program are shown under this heading.

(4) Output conditions

The data or information, output as a result of executing the example program, are shown under this heading.

(5) Processing sequence

Under this heading, how the example program is executed is discussed in detail. A flowchart and a program list are also presented, along with an example program. Read the discussion under this heading while referring to the flowchart and program list.

(6) Number of steps

Since the example programs are presented as subroutines, they are linked with the main routine by using the LK78K2 linker for the RA78K/2 relocatable assembler. Therefore, each example program ends with the RET instruction. The number of steps presented under this heading includes this RET instruction.

(7) Program list

All the example programs presented under this heading are source programs. The addresses at which each example program is to be located differ, depending on the conditions under which the program has been linked.

1.1.2 Legend for discussion on hardware program examples

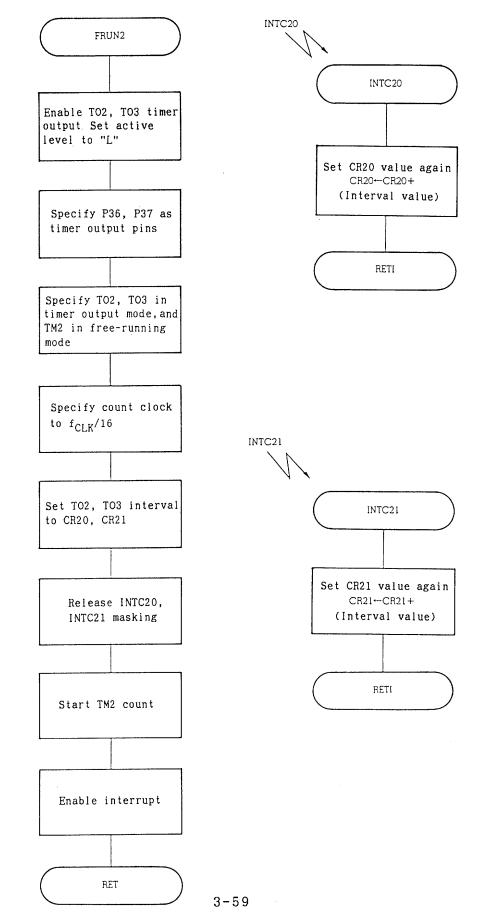

Chapter 3 presents application examples for hardware devices. Each example consists of the following items of information:

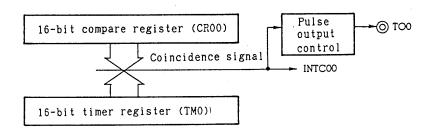

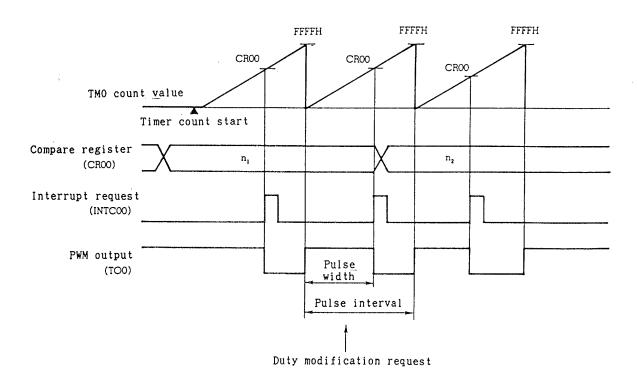

(1) Operation

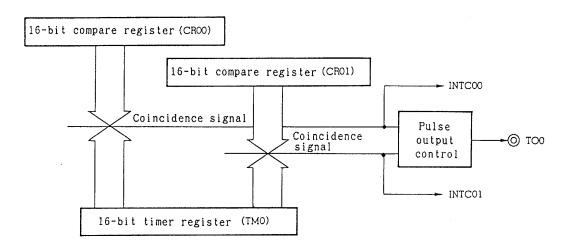

Under the heading "Operation", the operation to be executed by the hardware device in question is presented. Occasionally, a blockdiagram of the hardware device is also shown.

(2) Program

Under this heading, the program processing sequence, the setting of the necessary mode registers and memory are indicated.

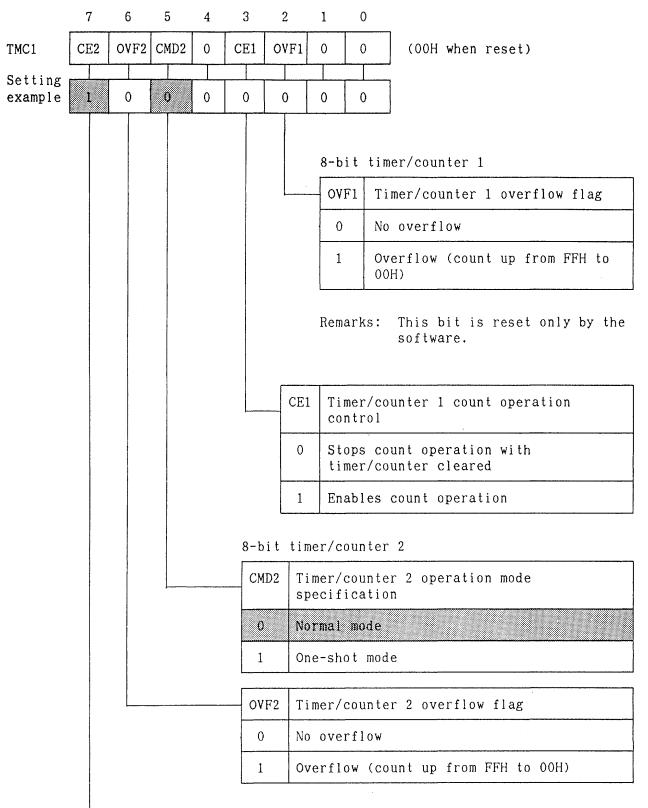

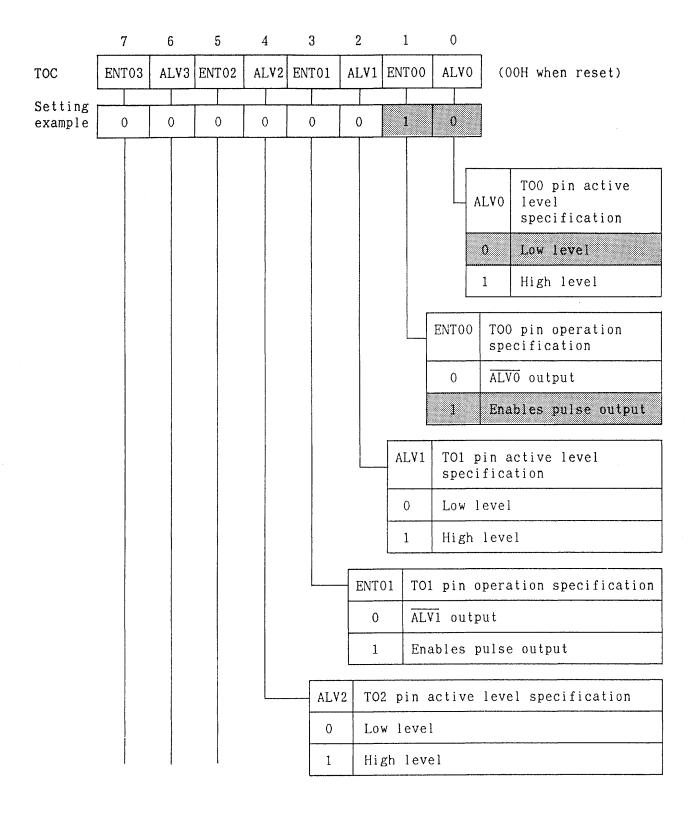

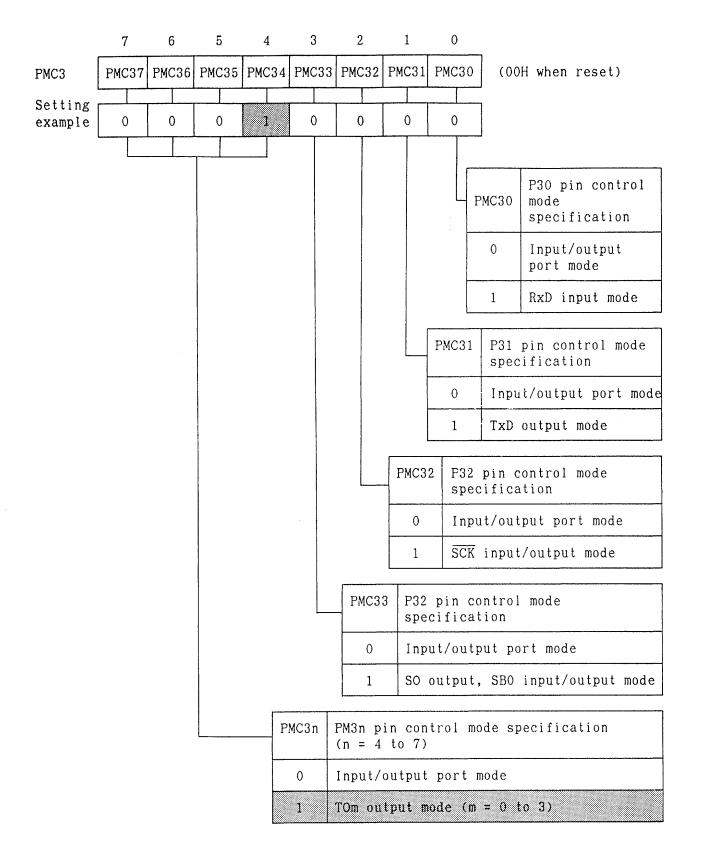

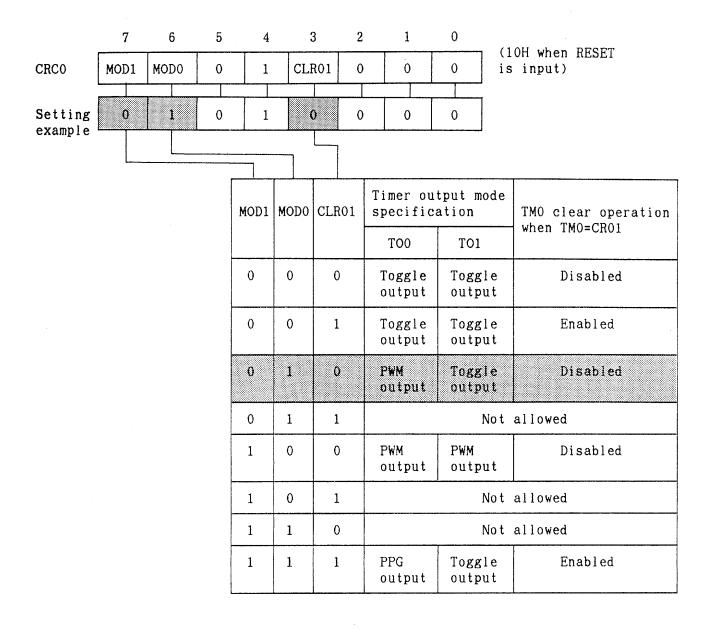

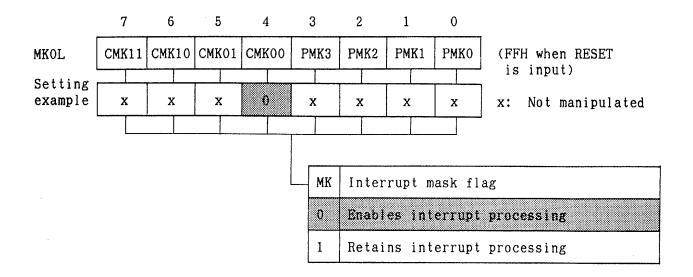

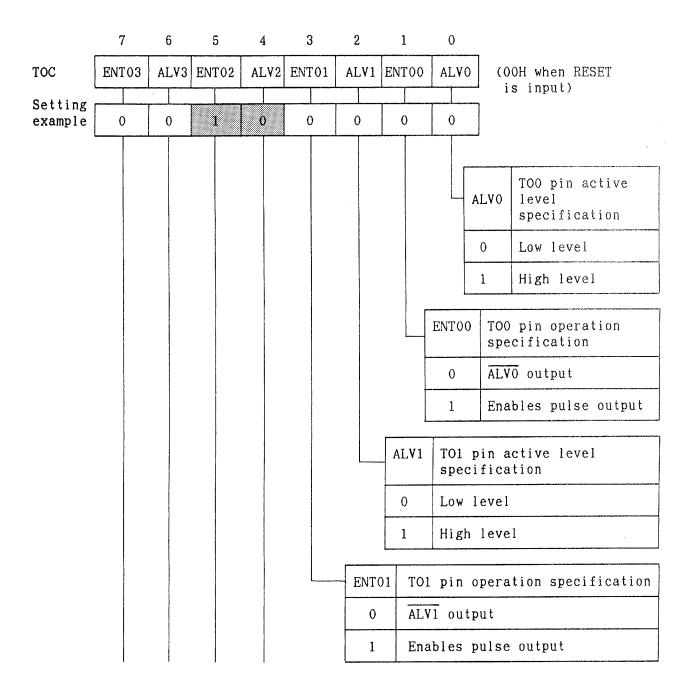

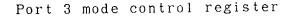

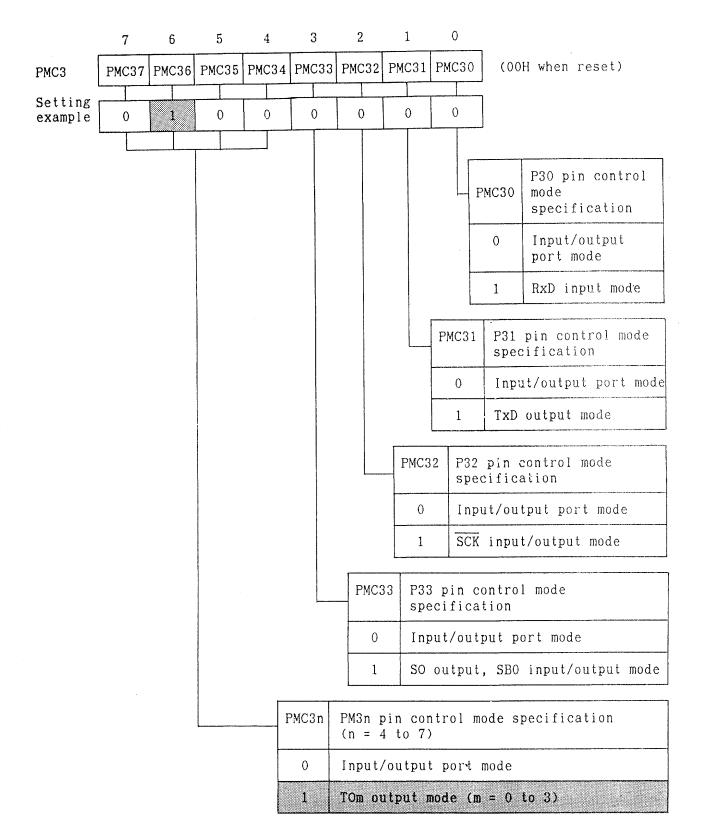

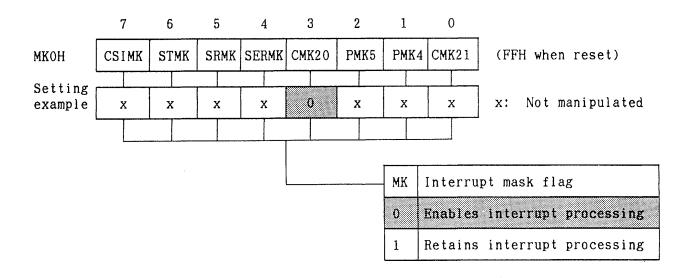

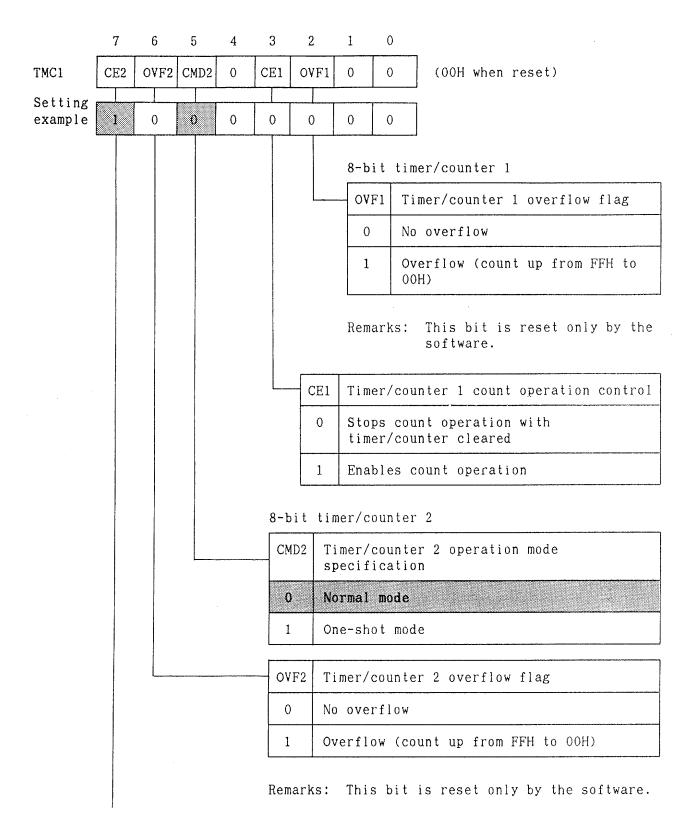

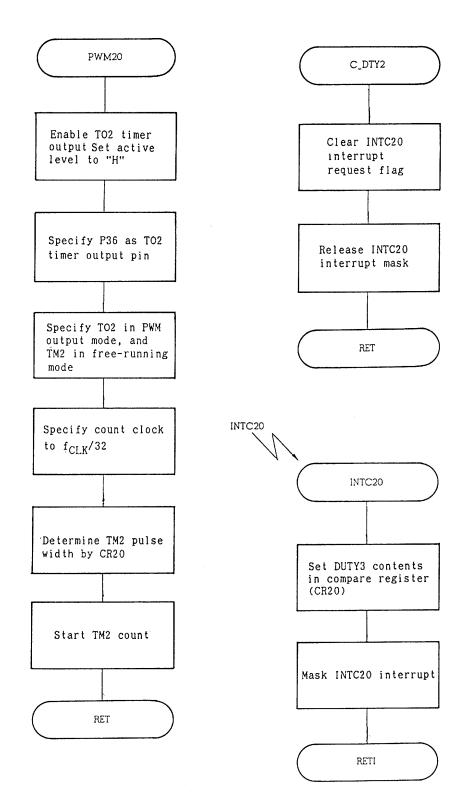

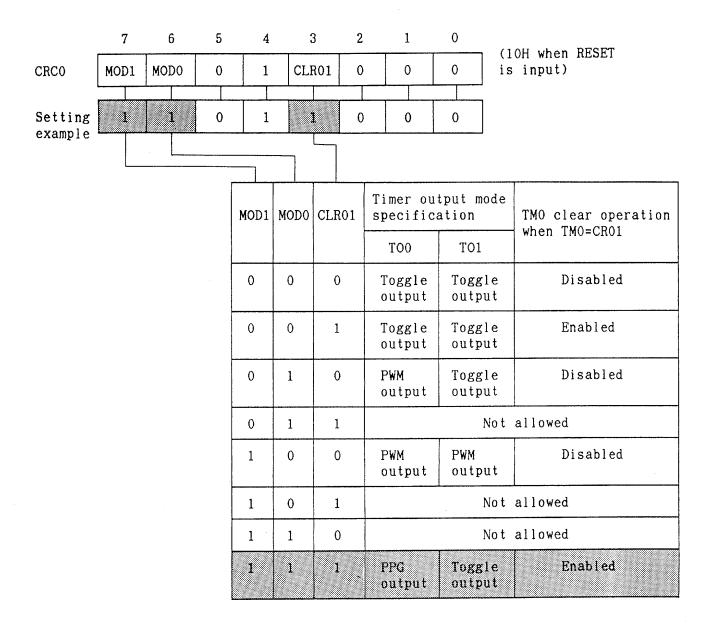

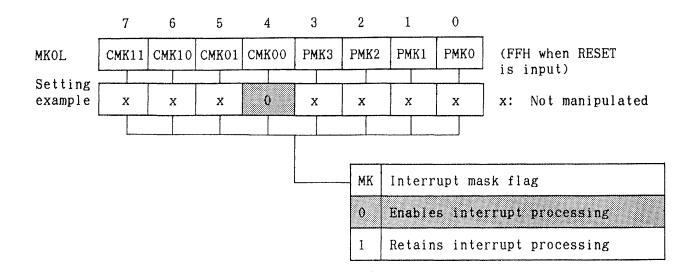

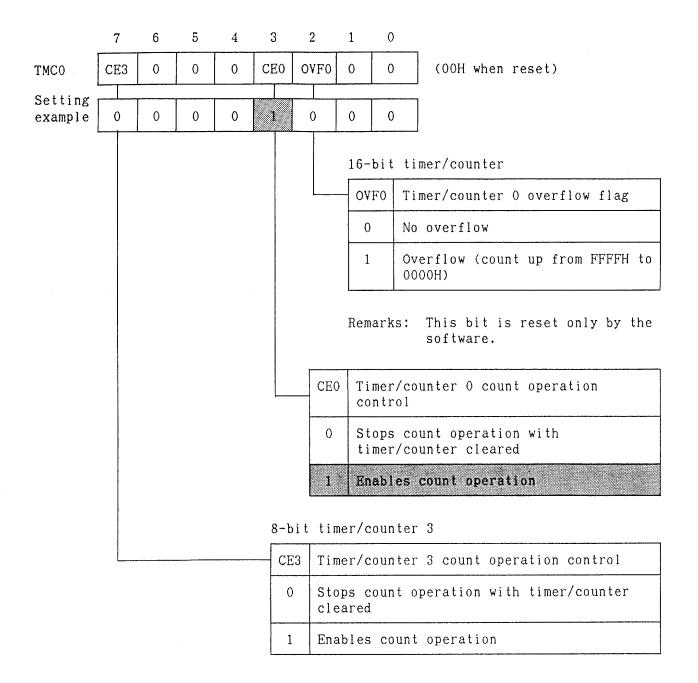

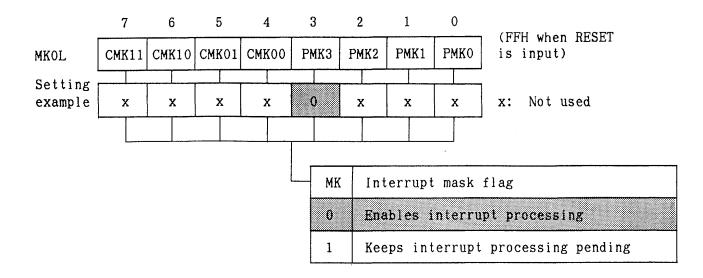

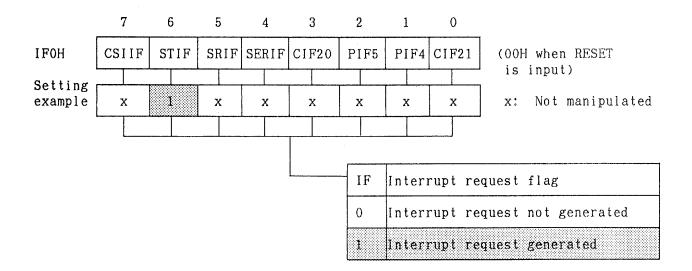

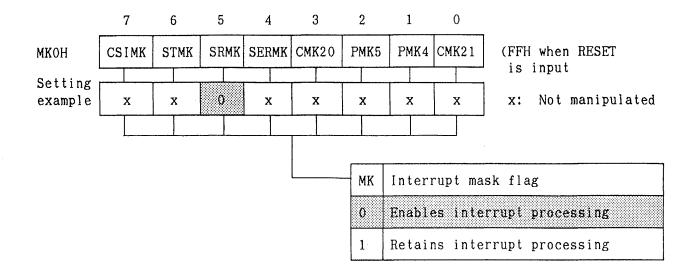

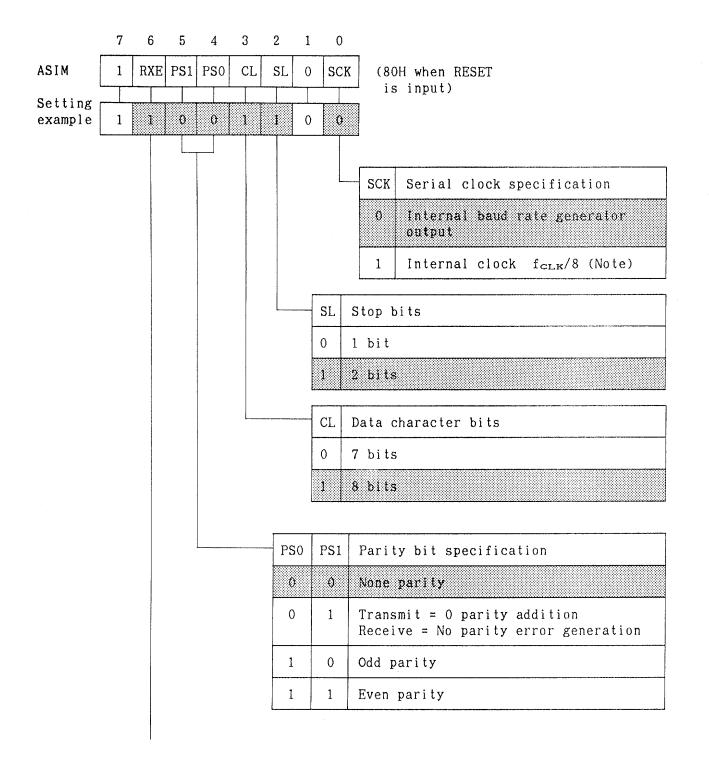

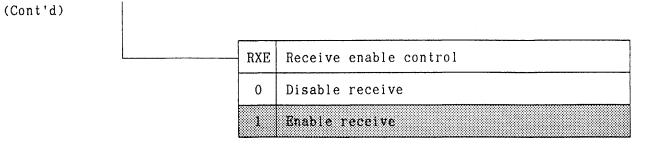

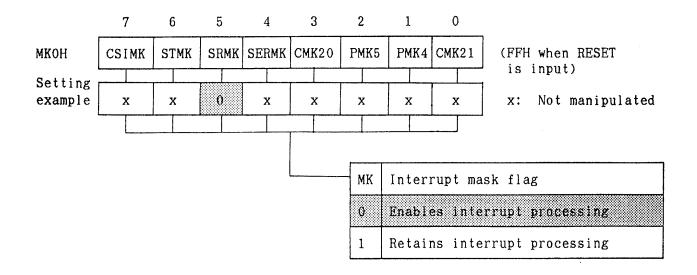

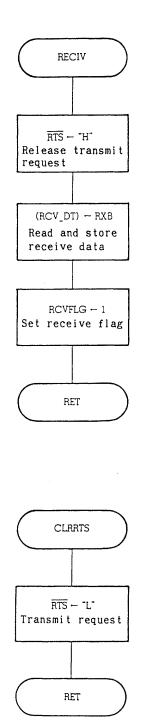

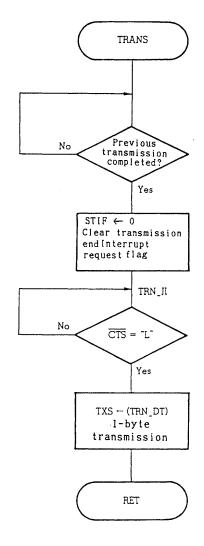

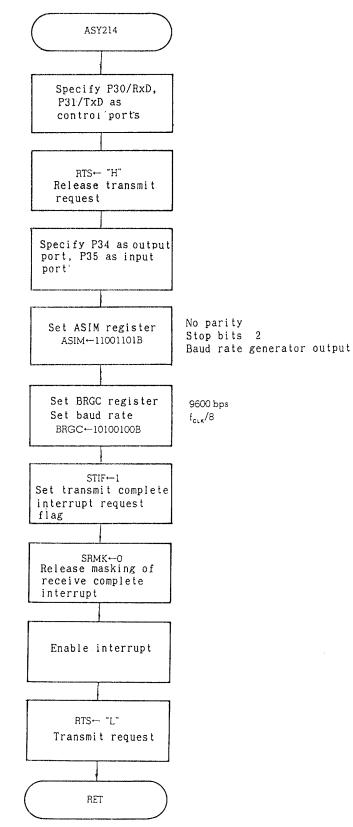

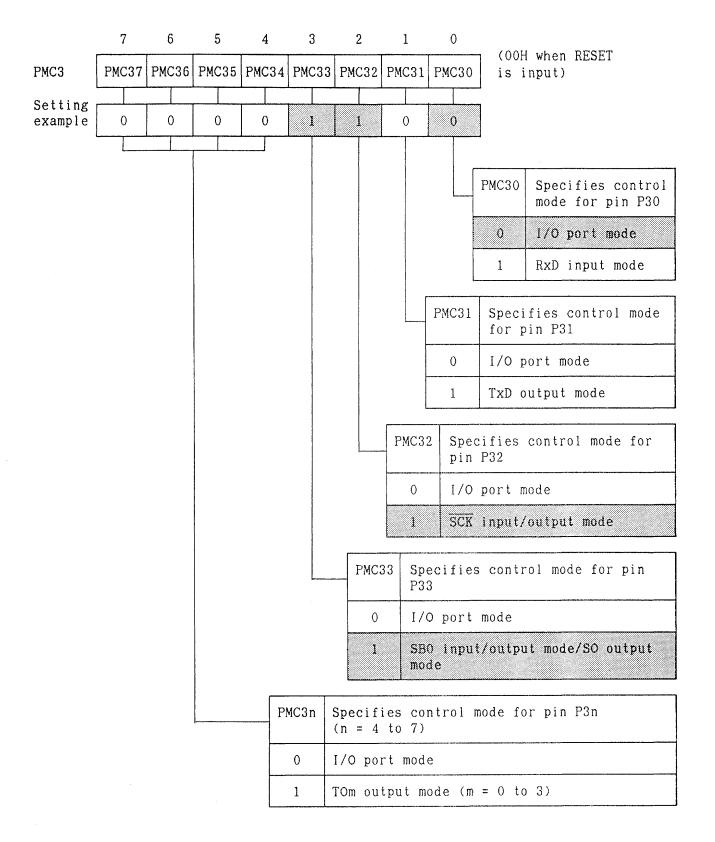

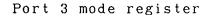

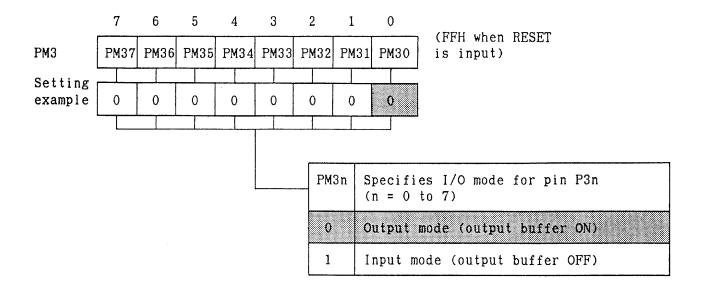

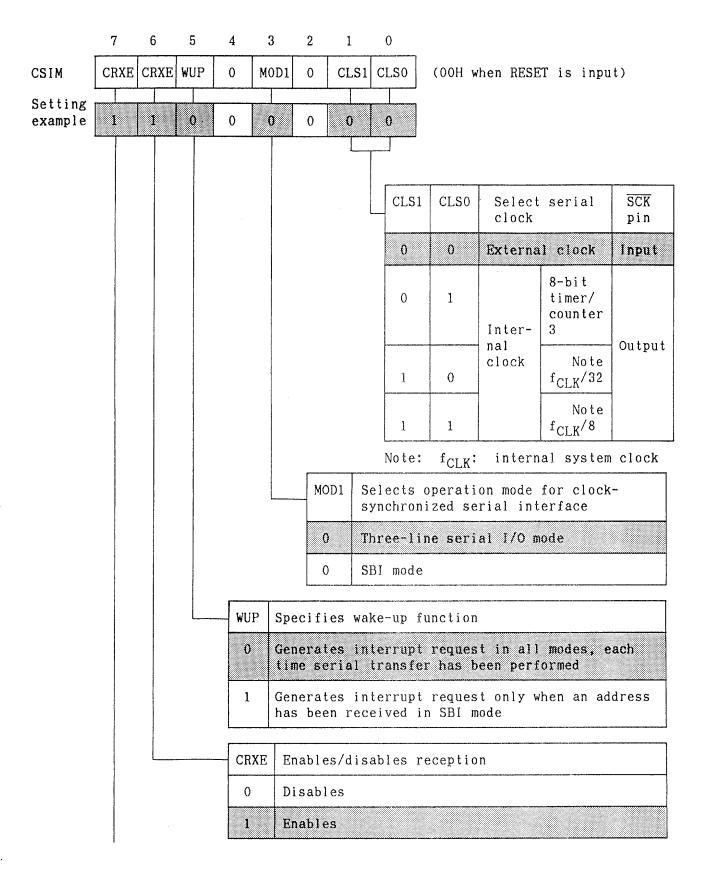

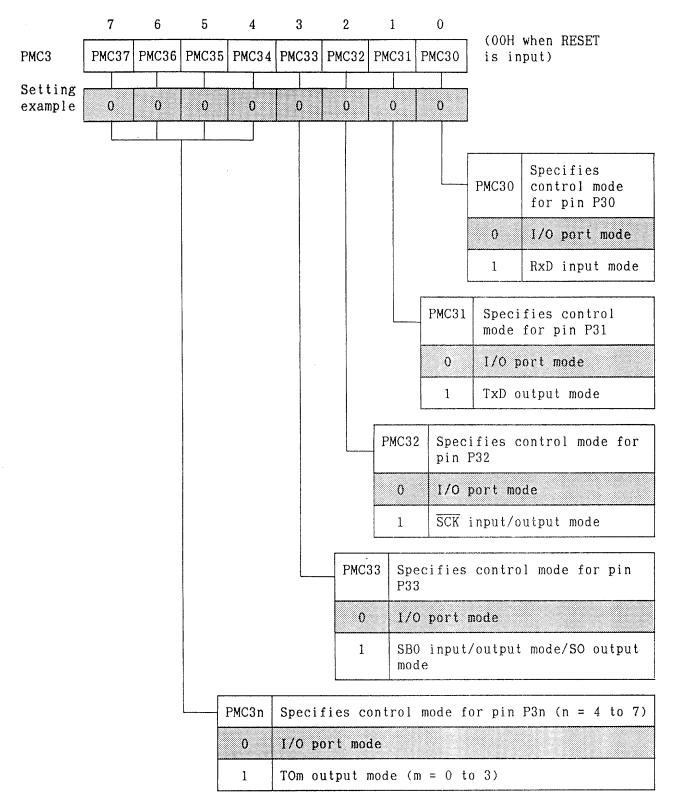

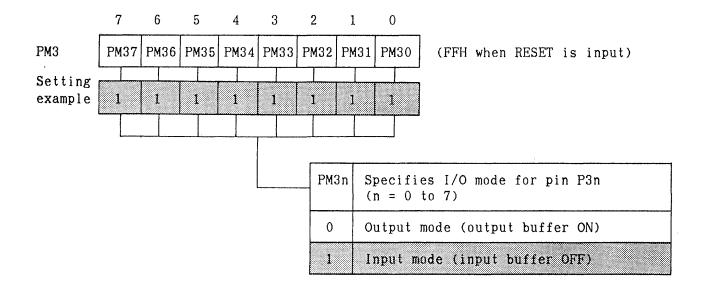

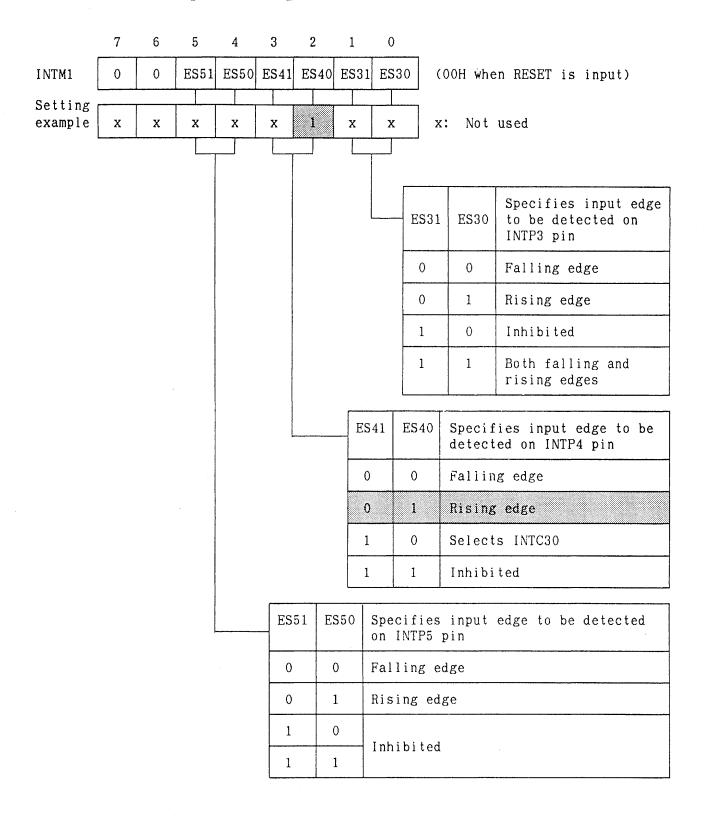

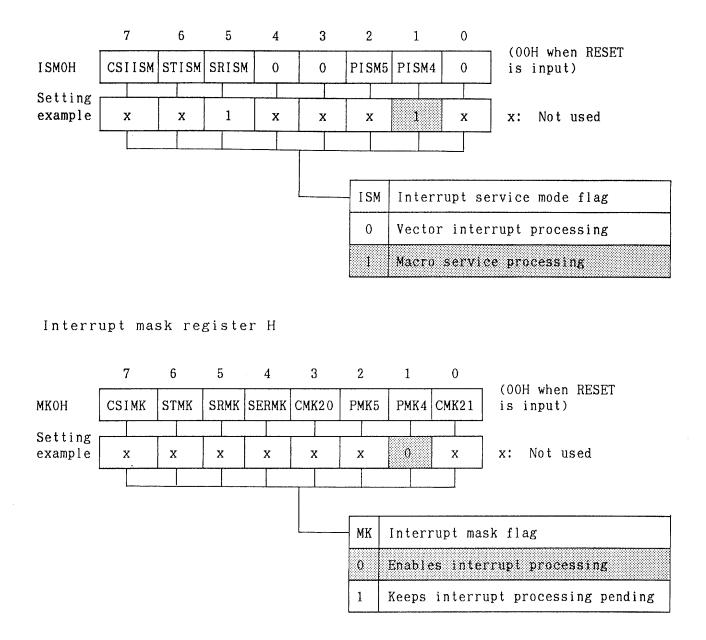

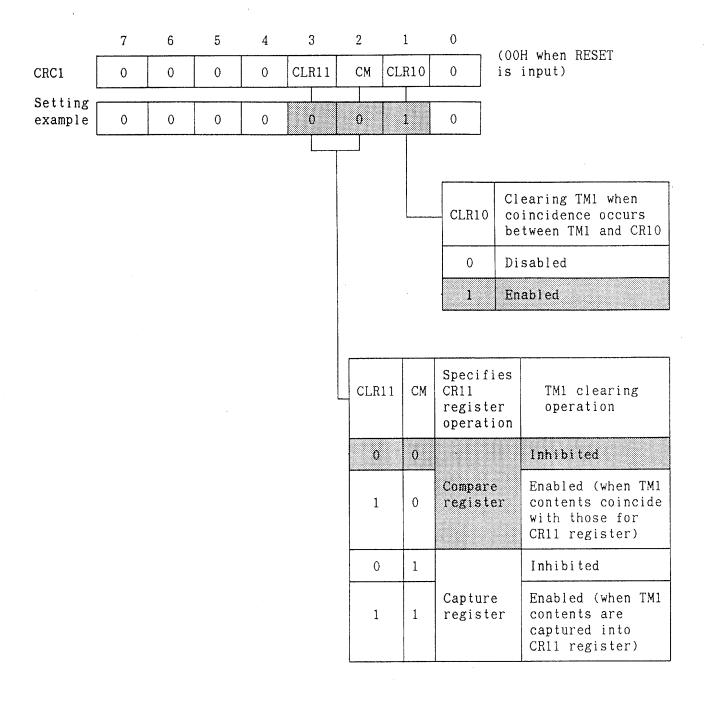

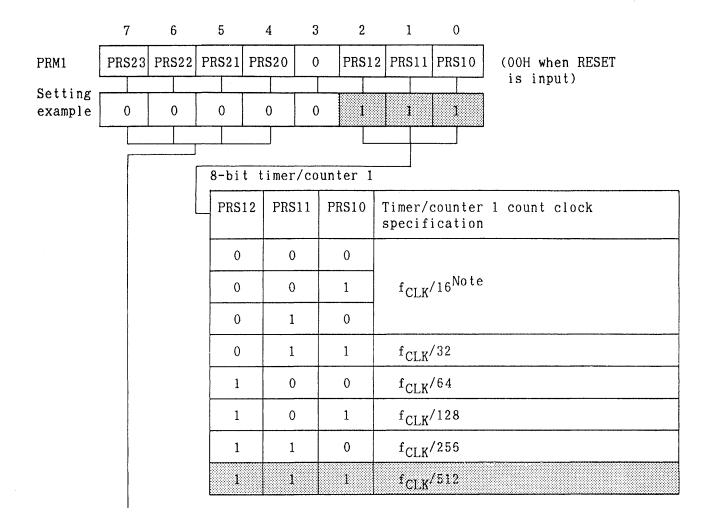

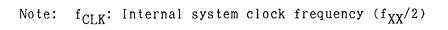

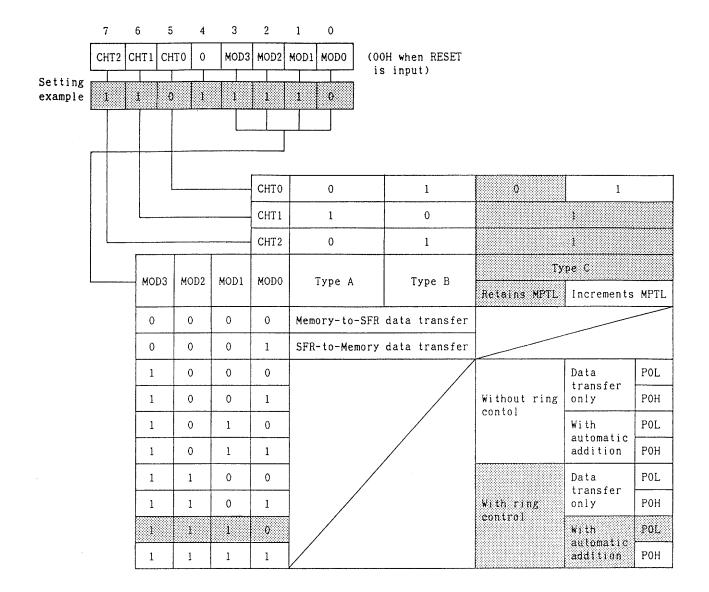

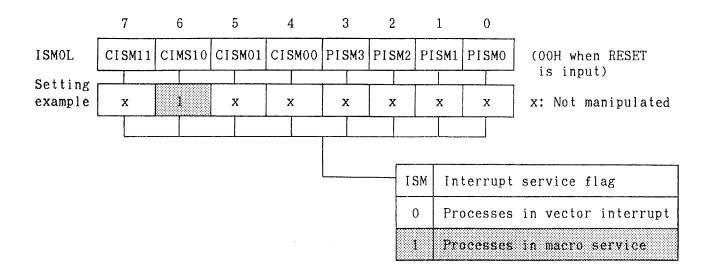

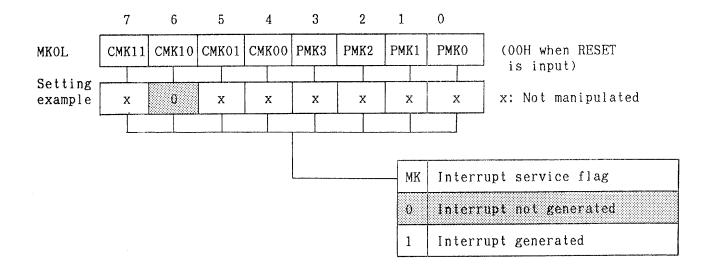

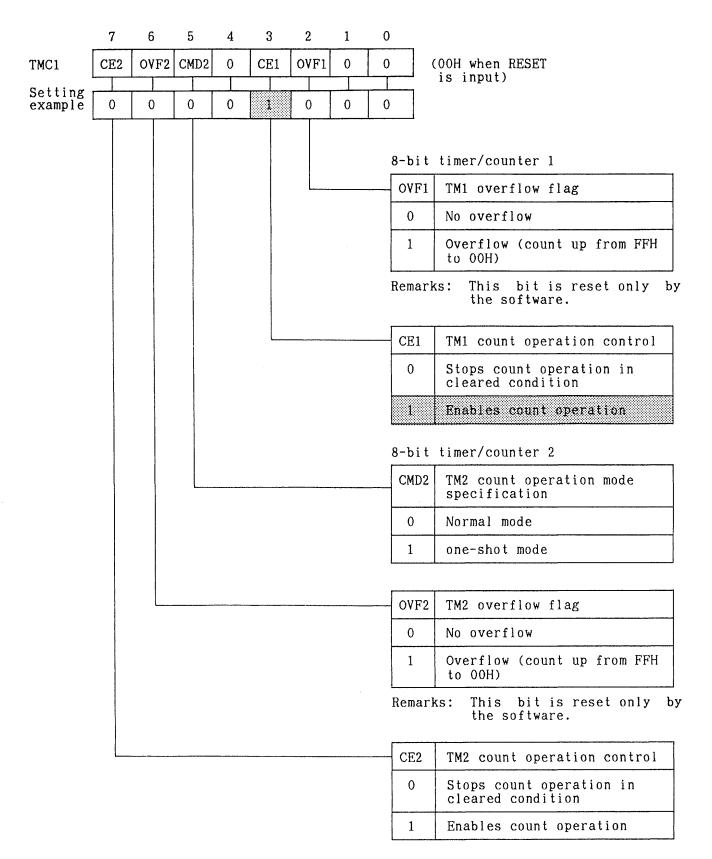

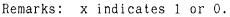

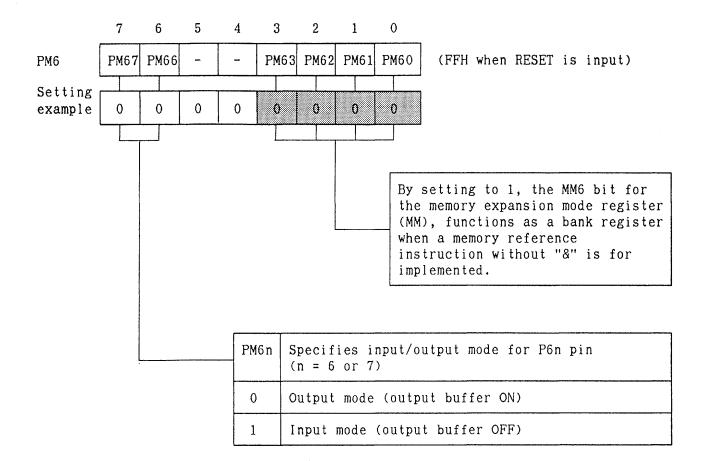

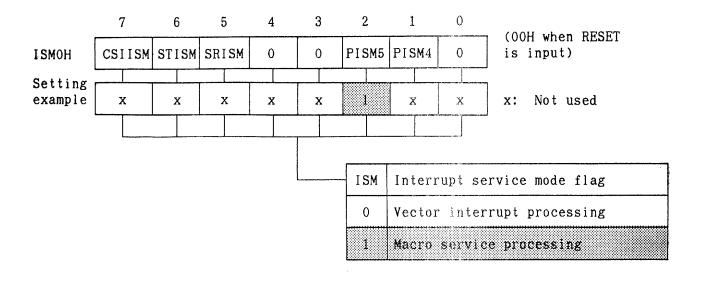

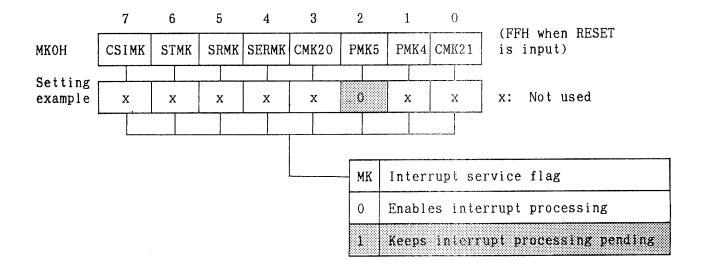

(3) Mode register setting example

Mode register setting examples are shown under this heading.

#### (4) Input/Output parameters

These parameters are given or output when the hardware device is to be operated. Many programs are shown as relocatable programs. Therefore, those programs must be defined by the EQU directive in the user program and then declared to be public.

(5) Registers

Under the heading "Registers", the registers used for the example program are presented. If the contents of registers already used should not be destroyed, save the register contents to stack by executing the PUSH instruction, etc., before calling the example program.

## (6) Program example

An example program for operating the hardware device is given.

(7) Program list

All the example programs presented under this heading are source programs. The addresses at which each example program is to be located differ, depending on the conditions under which the program has been linked.

#### 1.2 Use of Application Programs

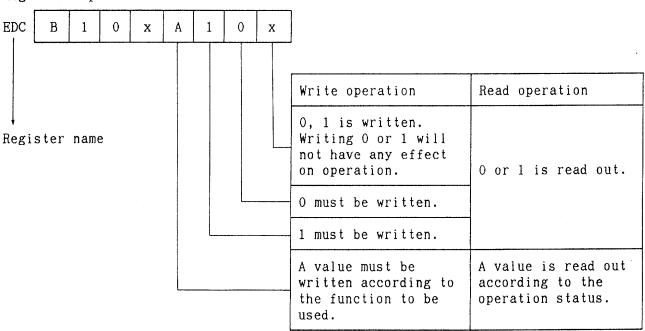

Basically, execute the application programs as described. Some application programs are used to call other application programs. These programs must be linked by using a linker. Some programs may require a work area. To use these programs, reserve a memory area described and accomplish public declaration. Internal hardware devices for the microcomputers covered in this Application Note are dependent on the internal system clock for their operations. The 78K/II series products divide the frequency of the externally supplied clock ( $f_{XX}$  or  $f_X$ ) by two to produce the internal system clock  $(f_{CLK})$ , as illustrated i n Fig. 1-1.

### Fig. 1-1 Clock Oscillation Circuit

Remarks:

$f_{XX}$ : Crystal/ceramic oscillation frequency  $f_X$ : External clock frequency  $f_{CLK}$ : Internal system clock frequency (=  $1/2f_{XX}$  or  $1/2f_X$ )

Note that the system clock is represented as  $\mathbf{f}_{\text{CLK}}$  throughout this Application Note.

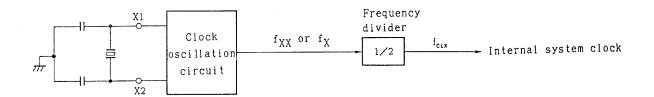

#### 1.3 Features of 78K/II Series Products

The 78K/II series microcomputers are 78K series 8-bit single-chip microcomputers. Each of the 78K/II series microcomputers contains a high-performance 8-bit CPU, ROM, RAM, and abundant peripheral hardware in the chip.

The instruction set for the 78K/II series microcomputers includes abundant instruction, such as 16-bit operation instruction, multiplication/division instruction, and bit manipulation instructions. The data address space can be extended up to 1M bytes so that a large amount of data can be accommodated.

In addition, for OA application, the 78K/II series microcomputers are provided with peripheral hardware data transfer processing function. The real-time output port, which is effective for stepping motor control, is also provided.

The 78K/II series microcomputers are further divided into five sub-series (uPD78214 series, uPD78218A series, uPD78224 series, uPD78234 series, and uPD78244 series). Therefore, a suitable series can be selected for a desired application. The same CPU used in these series. Only the hardware is different. is Therefore, the instruction set is common to all of these series, that programs which control individual peripheral hardware S O units can mostly be commonly used (refer to Fig. 1-2). Within the sub series, only the internal memory sizes are different.

\*\*\*\*\*\*\*

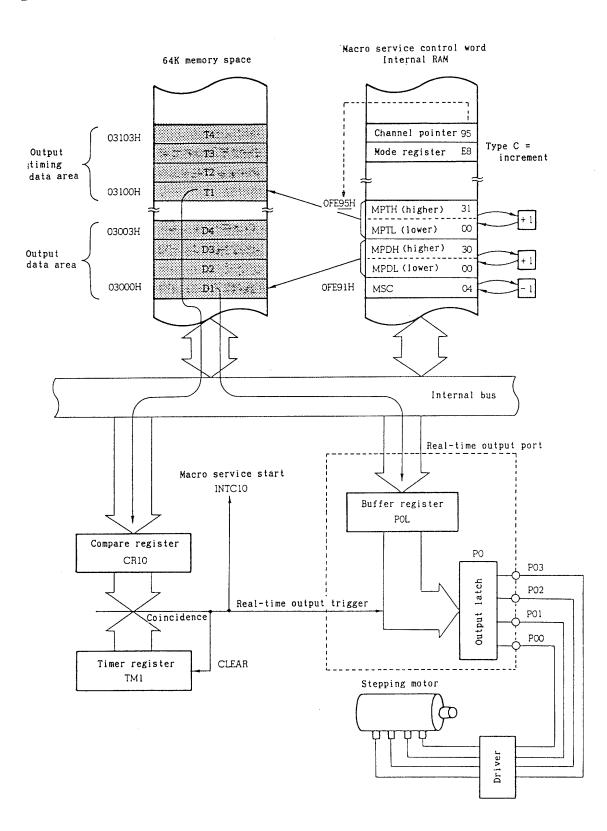

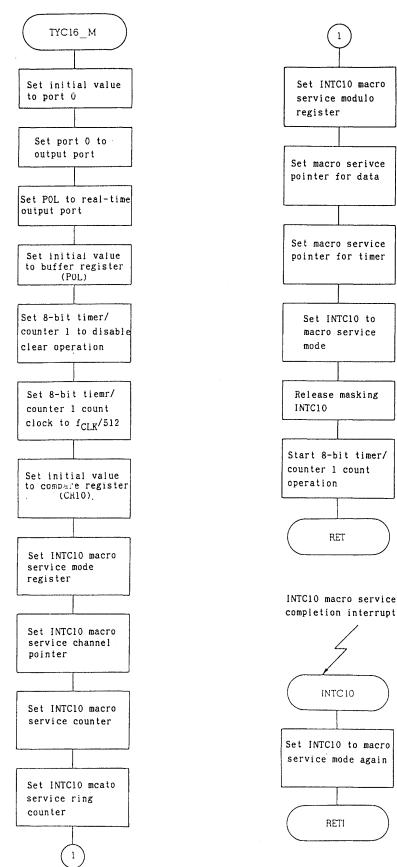

Macro service

A/D

Real-time

output pori

Edge detection

Comparator

CSI

UART

## Fig. 1-2 Peripheral Hardware Correlation Diagram

## CHAPTER 2 SOFTWARE PART

In the Software Part, operation results and numeric data are allocated on the RAM by the program. The program example shown below presents an example of how to assure the area availability.

|                              | PUBLIC<br>PUBLIC                      | BMLCND, BMLIER, B<br>DVISOR, DEND, DRM<br>DMLCND, DMLIER, D<br>DIVSOR, DIVIND, R<br>ERROR | IND<br>RS | LT    | ,<br>,<br>,<br>,<br>, | Binary multiplication<br>Binary division<br>Decimal multiplication<br>Decimal division<br>Error processing |

|------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------|-----------|-------|-----------------------|------------------------------------------------------------------------------------------------------------|

|                              | PUBLIC<br>PUBLIC                      |                                                                                           |           |       | •<br>•<br>•           | Sign flag<br>Carry data                                                                                    |

| SFLAG                        | BSEG<br>DBIT                          |                                                                                           | ;         | Sign  | fl                    | ag                                                                                                         |

| SOFT_D1<br>CARRY:            |                                       | SADDR<br>1<br>•                                                                           | .,        | Carry | ′ d                   | ata                                                                                                        |

| •                            | Data a<br>*******<br>DSEG<br>DS<br>DS | ******************<br>rea<br>****************                                             | **:       | ***** | ***                   |                                                                                                            |

| DVISOR:<br>DEND:<br>DRMND:   | DS                                    | 4<br>4<br>4                                                                               | ;         | Binar | ·у                    | division area                                                                                              |

| DMLCND:<br>DMLIER:<br>DRSLT: | DS                                    | 4<br>4<br>8                                                                               | ;         | Decim | al                    | multiplication area                                                                                        |

| DIVSOR:<br>DIVIND:<br>RMIND: |                                       | 4<br>4<br>4                                                                               | ;         | Decim | al                    | division area                                                                                              |

|                              | CSEG                                  |                                                                                           |           |       |                       |                                                                                                            |

| ERROR:                       |                                       |                                                                                           | ;         | Write | e                     | error processing                                                                                           |

### 2.1 Binary Operations

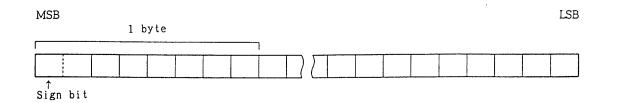

The most significant bit is a sign bit with a numeric value represented by the other bits. Negative numbers are represented in the 2s complement system.

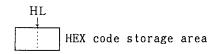

## Fig. 2-1 Binary Representation

In binary operations, numeric values are located in the memory, both before and after the operations.

2.1.1 Binary addition

$$32 \text{ bits} \leftarrow 32 \text{ bits} + 32 \text{ bits}$$

(1) Memory

(2) Registers

A, C, DE, HL

(3) Input conditions

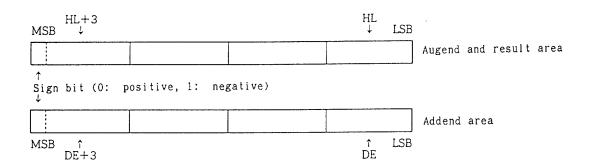

As indicated in (1), the contents of HL, DE registers are set as follows.

- . The lowest address in the memory area, where the 32-bit augend is stored, should be loaded to register HL.

- . The lowest address in the area, where the 32-bit addend is stored, should be loaded to register DE.

- Remarks: Addition of data of other than 4 bytes (32 bits) can also be executed by changing the BYTNUM value in the program.

- (4) Output conditions

The result of the operation is stored in the memory areas (HL, HL + 1, HL + 2, and HL + 3) indicated in (1).

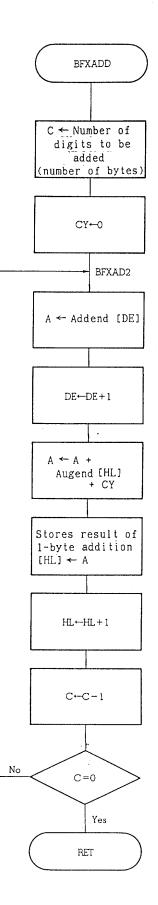

- (5) Processing sequence

- (a) 4 is set in the byte counter (register C).

- (b) The carry flag is cleared to 0 in advance.

- (c) One byte of data, indicated by the addend register (register DE), is read into register A, and the contents of the addend register are then incremented.

- (d) One byte of data indicated by the augend register (register HL) is added with carry to the register A contents.

- (e) The register A value is stored in a memory location indicated by the addend register. The addend register contents are then incremented.

- (f) The byte counter contents are decremented. Steps (a)

to (e) above are repeated until the byte counter

contents are decremented to zero.

- (6) Number of steps

7

```

NAME BFXADR

```

| ;* | binary addition                    | * |

|----|------------------------------------|---|

| ;* | 32 bit <- 32 bit + 32 bit          | * |

| ;* | input condition                    | * |

| ;* | HL-register <- augnend top.address | * |

| ;* | DE-register <- addend top.address  | * |

| *  | output condition                   | * |

| *  | result <- (HL,HL+1,HL+2,HL+3)      | * |

PUBLIC BFXADD

|              | 100010                     | DI ARDD                                    |

|--------------|----------------------------|--------------------------------------------|

| BYTNUM       | EQU                        | 4                                          |

| ,<br>BFXADD: | CSEG                       |                                            |

| BFXAD1:      | MOV                        | C,#BYTNUM                                  |

|              | CLR1                       | СҮ                                         |

| BFXAD2:      | MOV<br>ADDC<br>MOV<br>DBNZ | A,[DE+]<br>A,[HL]<br>[HL+],A<br>C,\$BFXAD2 |

| •            | RET                        |                                            |

| ,            |                            |                                            |

END

32 bits

$$\leftarrow$$

32 bits  $-$  32 bits

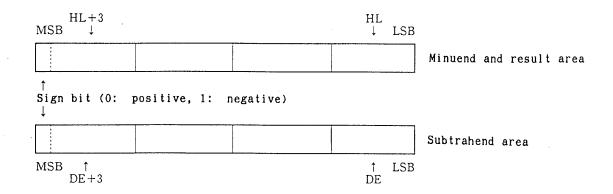

#### (1) Memory

(2) Registers

A, C, DE, HL

(3) Input conditions

As indicated in (1), the contents of registers HL and DE are set as follows.

- . The lowest address in the memory area, where the 32-bit minuend is stored, should be loaded to register HL.

- . The lowest address in the area, where the 32-bit subtrahend is stored, should be loaded to register DE.

- Remarks: Subtraction of data of other than 4 bytes (32 bits) can also be executed by changing the BYTNUM value in the program.

- (4) Output conditions

The operation result is stored in the memory areas (HL, HL + 1, HL + 2, and HL + 3) indicated in (1).

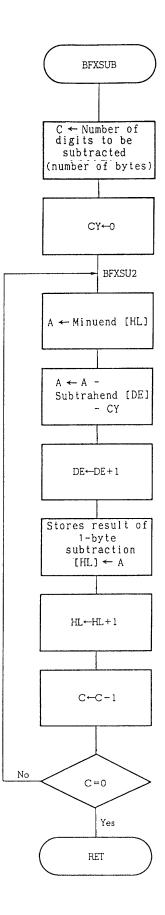

#### (5) Processing sequence

- (a) 4 is set in the byte counter (register C).

- (b) The carry flag is cleared to 0 in advance.

- (c) One byte of data, indicated by the minuend register (register DE), is read into register A.

- (d) One byte of data, indicated by the subtrahend register (register HL), is subtracted with carry from the register A contents. After that, the subtrahend register (register DE) contents are incremented.

- (e) The register A value is stored in a memory location indicated by the minuend register. The subtrahend register contents are then incremented.

- (f) The byte counter contents are decremented. Steps (a)

to (e) above are repeated until the byte counter

contents are decremented to zero.

(6) Number of steps

7

# (7) Flowchart

NAME BFXSBR

| , , , , , , , , , , , , , , , , , , , | binary<br>32<br>input<br>output | <pre>************************************</pre> | * * * * * * |

|---------------------------------------|---------------------------------|-------------------------------------------------|-------------|

|                                       | PUBLIC                          | BFXSUB                                          |             |

| ,<br>BYTNUM                           | EQU                             | 4                                               |             |

| 3                                     | CSEG                            |                                                 |             |

| BFXSUB:                               | ИОИ                             | 0 <b>4</b> 0.07000                              |             |

| BFXSU1:                               | MOV                             | C,#BYTNUM                                       |             |

| BFXSU2:                               | CLR1                            | СҮ                                              |             |

| DI X302 (                             | MOV<br>SUBC<br>MOV<br>DBNZ      | A,[HL]<br>A,[DE+]<br>[HL+],A<br>C,\$BFXSU2      |             |

|                                       | RET <sup>.</sup>                |                                                 |             |

| ,                                     | END                             |                                                 |             |

|                                       |                                 |                                                 |             |

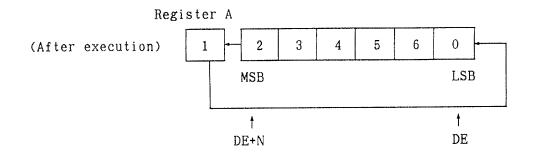

# 2.1.3 Binary multiplication

64 bits

$$\leftarrow$$

32 bits x 32 bits

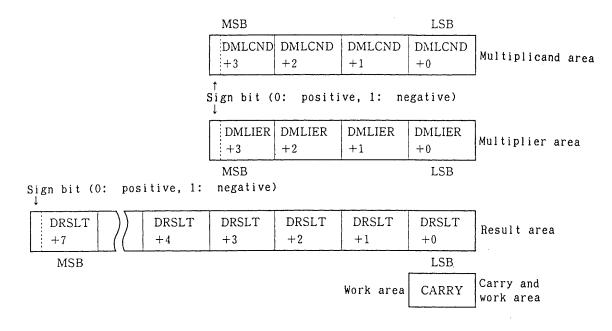

(1) Memory

|                       |             | MSB              |              |              | LSB          |                   |

|-----------------------|-------------|------------------|--------------|--------------|--------------|-------------------|

|                       |             | BMLCND<br>+3     | BMLCND<br>+2 | BMLCND<br>+1 | BMLCND<br>+0 | Multiplicand area |

|                       | S           | †<br>Sign bit (C | ): positi    | ve, 1: ne    | gative)      |                   |

|                       |             | BMLIER<br>+3     | BMLIER<br>+2 | BMLIER<br>+1 | BMLIER<br>+0 | Multiplier area   |

|                       |             | MSB              |              |              | LSB          | •                 |

| Sign bit (0: po.<br>↓ | sitive, 1:  | negative)        |              |              |              |                   |

| BRSLT +7              | BRSLT<br>+4 | BRSLT<br>+3      | BRSLT<br>+2  | BRSLT<br>+1  | BRSLT<br>+0  | Result area       |

| MSB                   |             |                  |              |              | LSB          |                   |

(2) Registers

X, A, C, B, DE, HL

# (3) Input conditions

As indicated in (1), the 32-bit multiplicand and multiplier are stored in the following areas:

Multiplicand: BMLCND, BMLCND + 1, BMLCND + 2, BMLCND + 3

Multiplier : BMLIER, BMLIER + 1, BMLIER + 2, BMLIER + 3

(4) Output conditions

The operation result is stored in the result areas indicated in (1) (BRSLT, BRSLT + 1, ..., BRSLT + 7).

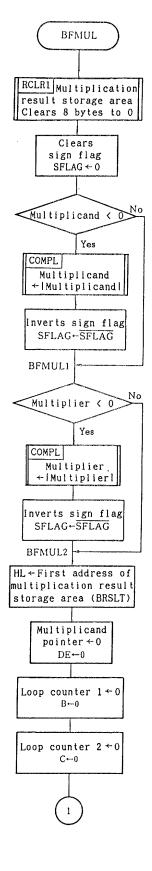

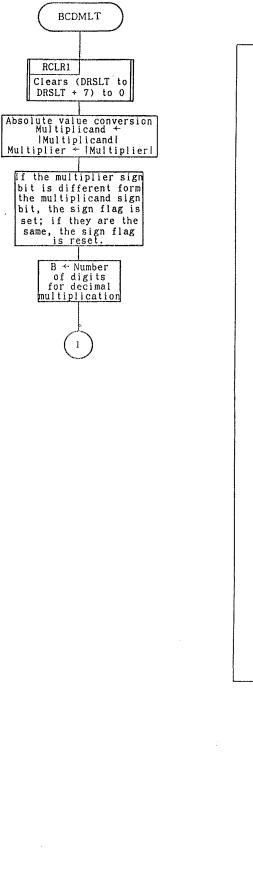

#### (5) Processing sequence

Since the multiplication instruction for 78K/II is used, the processing is analogous to hand calculation.

- (a) The result area is cleared to 0.

- (b) The absolute values of the multiplier and multiplicand are taken. If the sign of the multiplier is different from that of the multiplicand, the sign flag (user flag) is set to 1; if the signs are the same, the sign flag is cleared to 0.

- (c) The first address for the result area is set in register HL.

- (d) 0 is set as an initial value in the multiplier digit pointer (register DE) and loop counter (register B and C).

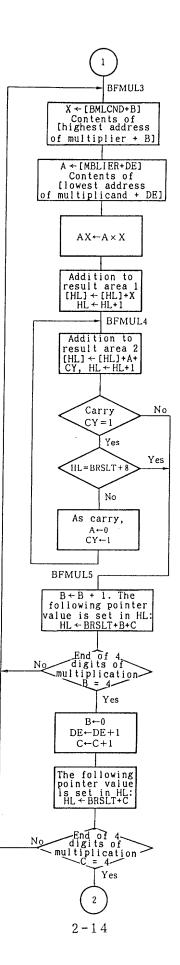

- (e) One byte of multiplicand, indicated by (BMLCND + register B), is read into register X.

- (f) One byte of multiplier, indicated by (BMLIER + register DE), is read into register A. The register A contents are then multiplied by the register X contents, and the result is added to the result area (register HL) contents.

- (g) If a carry has been generated as a result of (f), the carry is processed. However, overflow from area BRSLT + 7 is ignored.

- (h) The loop counter (register B) contents are incremented.

- (i) The BRSLT + B + C value is loaded to the multiplication result pointer (register HL).

- (j) The register B value is tested to see whether or not multiplication of four digits of data has been completed. If the register B value is less than 4, steps (e) to (i) above are repeated.

- (k) 0 is set in the loop counter (register B) again, and the contents of the multiplicand pointer (register DE) and loop counter (register C) are incremented.

- (1) The BRSLT + C value is loaded to the multiplication result pointer.

- (m) The register C value is tested to see whether or not multiplication of four digits of data has been completed. If the register C value is less than 4, steps (e) to (m) above are repeated.

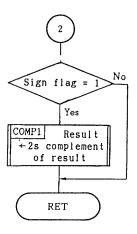

- (n) If the sign flag is 1, the 2s complement for the above multiplication result is taken, which is regarded as the real result of the multiplication.

- (6) Number of steps

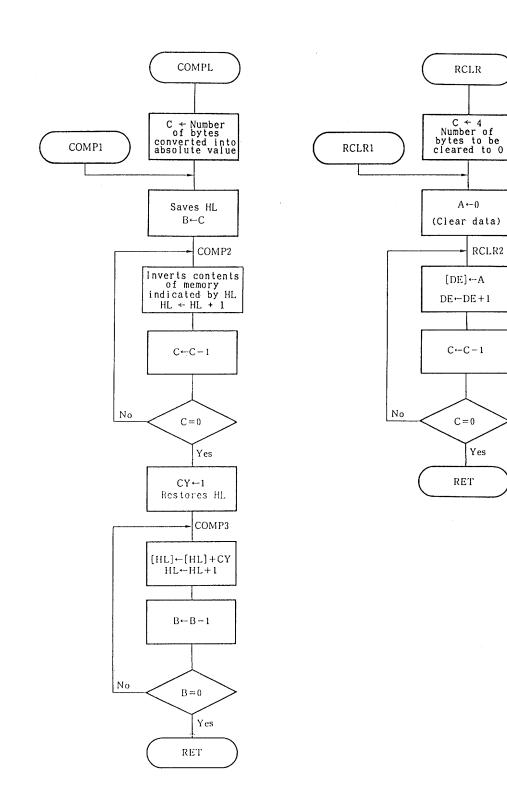

BFMUL: 59 RCLR : 5 COMPL: 14

#### (7) Flowchart

(8) Program list NAME BFMULR

binary multiplication \* ;\* \* ;\* input condition multiplicand <- (BMLCND+3,..., BMLCND) \* ;\* \* ;\* multiplier <- (BMLIER+3,...,BMLIER) \* ;\* output condition \* result <- (BRSLT+7, BRSLT+6..., BRSLT) ;\* PUBLIC BFMUL BMLCND, BMLIER, BRSLT EXTRN RCLR, RCLR1, COMPL, COMP1 EXTRN EXTBIT SFLAG ; sign-flag BYTNUM EQU 4 ; value length ; CSEG BFMUL: \*\*\* result area O-clear \*\*\* ; ; C, #8 ; set area length MOY ; HL-reg. <- BRSLT MOV₩ DE, #BRSLT ! RCLR1 ; clear subroutine CALL • , • , • , \*\*\* compliment convert \*\*\* ; sign-flag <- 0 SFLAG CLR1 ; HL-reg. <- BMLCND HL, #BMLCND MOV₩ MOV A, [HL+3] check sign BF A.7, \$BFMUL1 ; if data<O goto BFMUL1 !COMPL ; complement subroutine CALL NOT 1 SFLAG ; not sign-flag BFMUL1: ; HL-reg. <- BMLIER MOVW HL, #BMLIER MOV A.[HL+3] BF A.7,\$BFMUL2 ; complement subroutine CALL !COMPL NOT 1 SFLAG ; not sign-flag · , , , \*\*\* set multiplication counter \*\*\* BFMUL2: MOVW HL, #BRSLT ; result top address MOVW DE.#0 ; sub pointer\_l MOVW BC,#0 ; loop counter\_1,2 \*\*\* binary multiplication process \*\*\* BFMUL3: MOV ; read base value A.BMLCNDFB7 MOV X.A ; read multiplier MOV A, BMLIER[DE] MULU Х A,X XCH A,[HL] ; write result ADD MOV [HL+], A 2 - 16

```

MOV A,X

```

| BFMUL4: | ADDC<br>MOV<br>BNC<br>MOVW<br>CMPW<br>BZ<br>MOV<br>SET 1<br>BR | A,[HL]<br>[HL+],A<br>\$BFMUL5<br>AX,HL<br>AX,#BRSLT+8<br>\$BFMUL5<br>A,#O<br>CY<br>BFMUL4 |        | check end of value<br>multiplication carry                                                       |

|---------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------|

| BFMUL5: | INC<br>MOV<br>ADD<br>MOV<br>ADDW<br>MOVW<br>MOV<br>CMP<br>BNZ  | B<br>X, B<br>X, C<br>A, #O<br>AX, #BRSLT<br>HL, AX<br>A, #BYTNUM<br>B, A<br>\$BFMUL3      | • •    | increment loop counter_1<br>next result pointer<br>check loop counter 1                          |

|         | MOV<br>INCW<br>MOV<br>MOV<br>ADDW<br>MOVW<br>MOV<br>CMP<br>BNZ | B,#0<br>DE<br>C<br>X,C<br>A,#0<br>AX,#BRSLT<br>HL,AX<br>A,#BYTNUM<br>C,A<br>\$BFMUL3      | ,<br>, | increment sub pointer<br>increment loop counter_2<br>next result pointer<br>check loop counter_2 |

| BFMUL6: | BT<br>RET                                                      | SFLAG,\$BFMUL6                                                                            | ;      | if sflag=1 complement convert                                                                    |

|         | MOV<br>MOVW<br>CALL<br>RET                                     | C,#8<br>HL,#BRSLT<br>!COMP1                                                               |        |                                                                                                  |

|         | END                                                            |                                                                                           |        |                                                                                                  |

NAME CLR

;\* 0-clear process \* ;\* input condition \* ;\* DE-register <- O-clear start address \* ;\* \* PUBLIC RCLR, RCLR1, RCLR2 PUBLIC COMPL, COMP1 BYTNUM EQU 4 ; CSEG RCLR: MOV C, #BYTNUM ; C-register <- 4 RCLR1: MOV A,#O ; Acc <- 0 RCLR2: MOV [DE+],A DBNZ C, \$RCLR2 RET ; ;\* complement convert subroutine \* ;\* input condition \* ;\* HL-register <- complement top.address \* ;\* output condition \* ;\* (HL+3,HL+2,...,HL) <- convert data \* ;\* ж CSEG COMPL: MOV C, #BYTNUM COMP1: PUSH HL ; save HL-register MOV B,C COMP2: MOV A,#OFFH XOR A,[HL] MOV [HL+],A DBNZ C, \$COMP2 SET 1 СҮ POP ΗL COMP3: MOV A,#O ADDC A,[HL] MOV [HL+],A DBNZ B, \$COMP3 RET ; END

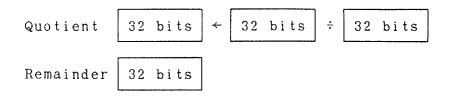

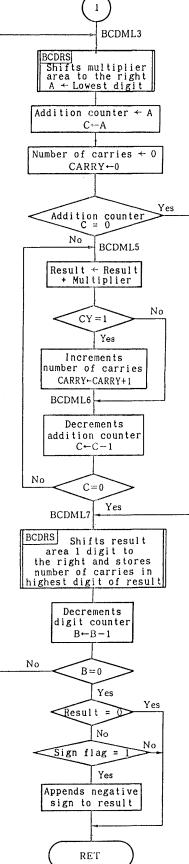

#### 2.1.4 Binary division

(1) Memory

(2) Registers

X, A, C, B, DE, HL

#### (3) Input conditions

As indicated in (1), the 32-bit dividend and divisor are respectively stored in the following areas:

. Dividend: DEND, DEND + 1, DEND + 2, DEND + 3 . Divisor : DVISOR, DVISOR + 1, DVISOR + 2, DVISOR + 3

(4) Output conditions

The quotient and remainder are stored in the following areas:

2-19

The quotient is stored in the quotient areas indicated in (1):

DEND, DEND + 1, DEND + 2, DEND + 3

. The remainder is stored in the remainder areas indicated in (1):

DRMND, DRMND + 1, DRMND + 2, DRMND + 3

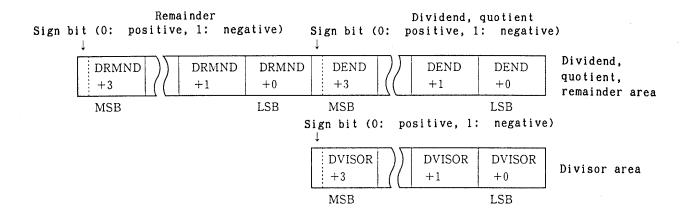

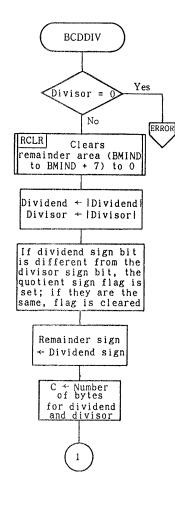

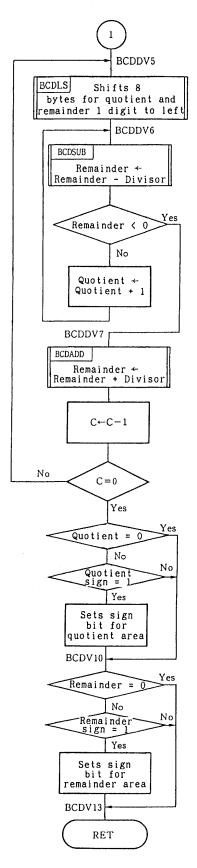

# (5) Processing sequence

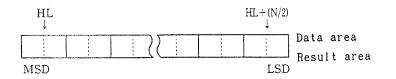

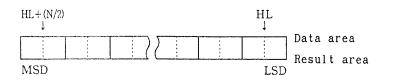

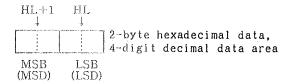

In the division program shown in this section, the dividend (DEND to DEND + 3) and remainder (DRMND to DRMND + 3)are stored in an area consisting of contiguous 8 bytes. One digit (4 bits) of the dividend and remainder is shifted to the left to transfer the highest digit of the dividend to the lowest area of the remainder. Consequently, the quotient, starting from the highest digit, is stored to the lowest area of the dividend on a digit-by-digit basis. The number of digits of the quotient is the same as the number of times the divisor is subtracted from the remainder until the subtraction result becomes negative. The processing is indicated in the following sequence:

- (a) The divisor is checked to see whether it is 0; if the divisor is 0, execution branches to an error processing routine.

- (b) The remainder area is cleared to 0.

- (c) The absolute values for the dividend and divisor are computed. Bit 0 of register X serves as a quotient sign flag, while bit 1 of register X is used as a remainder sign flag. If either of the dividend and divisor is negative, the quotient sign flag is set to 1.

If the dividend is negative, the remainder sign flag is set to 1.

(d) As the number of bytes for the dividend, 8 is set in register B.

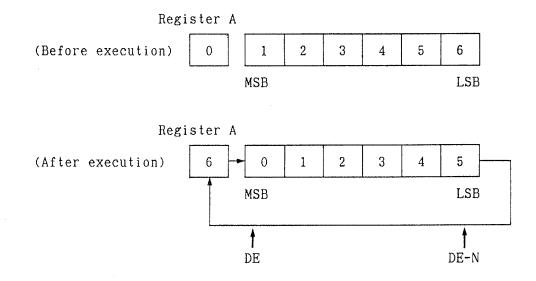

- (e) The quotient and remainder area, which consists of contiguous 8 bytes, is shifted 4 bits to the left.

- (f) The divisor is subtracted from the remainder and the result is regarded as the real remainder. If the result is negative, however, execution jumps to (h).

- (g) The quotient (DEND) contents are incremented, and execution jumps to (e).

- (h) Because the divisor has been subtracted from the remainder too many times, the divisor is added back to the remainder to obtain the real remainder.

- (i) The register B contents are decremented. Steps (e) to(h) above are repeated until the register contents are decremented to 0.

- (j) The quotient sign flag is checked. If it is found to be set to 1, the 2s complement for the quotient is calculated.

The remainder sign flag is checked, and if it is found to be set to 1, the 2s complement of the remainder is calculated.

(6) Number of steps

48

2-21

2-22

(8) Program list NAME BFDIVR

| ;*****                |                |                                                                     | **                              | *****                     |  |  |  |  |

|-----------------------|----------------|---------------------------------------------------------------------|---------------------------------|---------------------------|--|--|--|--|

| ;*                    | binar          | y division                                                          | 10                              | *<br>2. hit. *            |  |  |  |  |

| ;*                    |                |                                                                     |                                 |                           |  |  |  |  |

| ;*<br>;*              | Inba           | t condition *<br>dividend <- (DEND+3,,DEND) *                       |                                 |                           |  |  |  |  |

| ,^<br>;*              |                |                                                                     | divisor <- (DVISOR+3,,DVISOR) * |                           |  |  |  |  |

| ;*                    | outp           | ut condition                                                        |                                 | *                         |  |  |  |  |

| ;*                    | 0401           | quotient <- (DE                                                     | END                             | +3,,DEND) *               |  |  |  |  |

| ;*                    |                | remainder <- (DF                                                    | RWN                             | D+3,,DRMND) *             |  |  |  |  |

| ;*****                |                |                                                                     | (**                             | *****                     |  |  |  |  |

|                       | EXTRN<br>EXTRN | C BFDIV<br>BFXADD, BFXSUB<br>RCLR, COMPL, BCDL<br>DEND, DVISOR, DRM | .S,<br>IND                      | ERROR                     |  |  |  |  |

| ;<br>SF_REM<br>SF_QUO | EQU            | X.0                                                                 |                                 |                           |  |  |  |  |

| BYTNUM                | EQU<br>EQU     | X.1<br>4                                                            |                                 |                           |  |  |  |  |

| 3                     | CSEG           |                                                                     |                                 |                           |  |  |  |  |

| BFDIV:                |                |                                                                     |                                 |                           |  |  |  |  |

| ;<br>;<br>;           | ****           | check / divisor =                                                   | : 0                             | ? ****                    |  |  |  |  |

| 3                     | MOV            | C,#BYTNUM                                                           | ;                               | C-register <- 4           |  |  |  |  |

|                       | MOV            | A,#O                                                                | ;                               | Acc <- O<br>HL <- DVISOR  |  |  |  |  |

|                       | MOVW           | HL,#DVISOR                                                          | ;                               | HL <- DVISOR              |  |  |  |  |

| BFDIV1:               | CMP            | A,[HL+]                                                             |                                 |                           |  |  |  |  |

|                       |                |                                                                     | :                               | [HL] = 0 ?                |  |  |  |  |

|                       |                | C,\$BFDIV1                                                          | ,                               | 2                         |  |  |  |  |

| •                     |                |                                                                     |                                 |                           |  |  |  |  |

| •                     | ****           | divisor = 0 ****                                                    | ć                               |                           |  |  |  |  |

| ,                     | BR             | ERROR                                                               | ;                               | OVER FLOW                 |  |  |  |  |

| ,<br>,<br>,           | ****           | quotient O-clear                                                    | *:                              | ***                       |  |  |  |  |

| ,<br>,<br>,           |                |                                                                     |                                 |                           |  |  |  |  |

| BFD[V2:               | MOVW           | DE,#DRMND                                                           |                                 | DE-register <- DRMND      |  |  |  |  |

|                       | CALL           | ! RCLR                                                              | ,                               | DE TEGISCEI · DIMMD       |  |  |  |  |

| •                     | 011111         |                                                                     |                                 |                           |  |  |  |  |

| •<br>•                | ****           | complement conver                                                   | t                               | ****                      |  |  |  |  |

| ,                     | CLR1           | SF_REM                                                              | ;                               | clear remainder sign-flag |  |  |  |  |

|                       | CLR1           | SF_QUO                                                              |                                 | clear quotient sign-flag  |  |  |  |  |

|                       | MOVW           | HL, #DEND                                                           | ;                               | HL-register <- DEND       |  |  |  |  |

|                       | MOV<br>BF      | A,[HL+3]<br>A.7,\$BFDIV3                                            |                                 |                           |  |  |  |  |

|                       | CALL           | A. 7, SDFDTVS<br>!COMPL                                             | :                               | complement subroutine     |  |  |  |  |

|                       | SET 1          | SF_REM                                                              | ,<br>,                          | set remainder sign-flag   |  |  |  |  |

|                       | NOT 1          | SF_QUO                                                              | ;                               | not quotient sign-flag    |  |  |  |  |

|                       |                |                                                                     |                                 |                           |  |  |  |  |

BFD1V3: MOVW HL, #DVISOR ; HL-register <- DVISOR MOV A,[HL+3] BF A.7, \$BFDIV4 ; complement subroutine CALL !COMPL SF\_QUO ; not quotient sign-flag NOT 1 , , , \*\*\*\* byte counter set \*\*\*\* BFDIV4: MOV B,#8 ; B-register <- 8 \*\*\*\* dividend, remainder 1-byte left shift \*\*\*\* BFDIV5: MOVW HL, #DEND ; HL <- DEND MOV C,#8 ; C-register <- 8 **!BCDLS** CALL , , \*\*\*\* subtract divisor from dividend \*\*\*\* BFDIV6: ; DE <- DVISOR MOVW DE, #DVISOR MOVW HL, #DRMND ; HL <- DRMND CALL **!BFXSUB** DECW HL ; decrement HL MOV A,[HL] BT A.7, \$BFDIV7 ; if borrow MOV A,#1 ; Acc <- 1 HL,#DEND MOVW ADD A, [HL]; increment DEND MOV [HL],A BR BFDIV6 \*\*\*\* if borrow divisor + dividend \*\*\*\* BFDIV7: MOVW DE, #DVISOR ; DE <- DVISOR ; HL <- DRMND MOVW HL, #DRMND **!BFXADD** CALL

| •<br>5<br>•<br>7 | ****               | check / division end ?                 | **** |

|------------------|--------------------|----------------------------------------|------|

| ,                | DBNZ               | B,\$BFDIV5                             |      |

| BFDIV8:          | BF<br>Mov₩<br>Call | SF_REM,\$BFDIV8<br>HL,#DRMND<br>!COMPL |      |

|                  | BF<br>MOVW<br>CALL | SF_QUO,\$BFDIV9<br>HL,#DEND<br>!COMPL  |      |

| BFD1V9:          | RET                |                                        |      |

| ,                | END                |                                        |      |

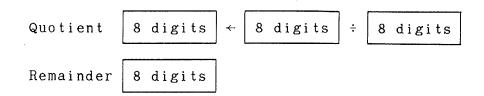

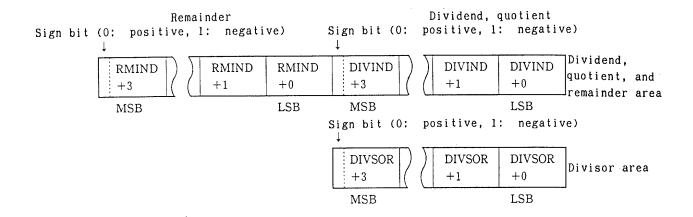

The most significant bit is a sign bit with a numeric value represented by the other bits. Decimal numbers are represented as BCD codes.

In decimal operations, numeric values are located in the memory, both before and after the operations.

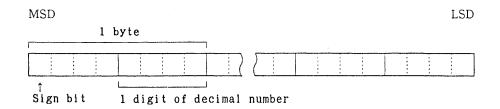

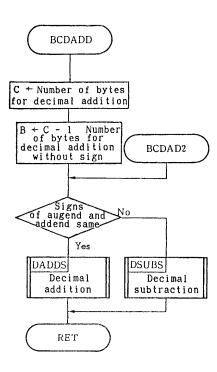

2.2.1 Decimal addition

(1) Memory

(2) Registers

A, C, B, DE, HL

#### (3) Input conditions

As indicated in (1), the contents of registers HL and DE are set as follows.

- . The lowest address in the memory area, where the 8-digit (4-byte) augend is stored, should be loaded to register HL.

- . The lowest address in the area, where 8-digit (4-byte) addend is stored, should be loaded to register DE.

- (4) Output conditions

The operation result is stored in the result area indicated in (1). However, the contents of HL register is damaged. If an overflow or underflow occurs, execution branches to an error processing routine.

- Note: The numeric values that can be operated must be in a -79999999 to 79999999 range.

- (5) Processing sequence

This addition program executes addition, if both the augend and addend have the same sign. If the augend sign differs from the addend sign, the program executes subtraction. The processing is indicated in the following sequence:

- (a) The number of bytes for decimal addition is set in register C.

The contents of this register minus 1 (C 1) are set in register B, as the number of bytes for decimal addition without sign.

- (b) If the signs of the augend and addend differ from each other, execution jumps to (o).

- (c) The carry flag and sign flag are cleared to 0.

- (d) A 1 byte of augend, indicated by the augend address, is read into register A.

- (e) A 1 byte of addend, indicated by the addend address, is added with carry to the register A contents, and the addend address is incremented. The addition result is adjusted for decimal and is stored in a memory location indicated by the augend address. After that, the augend address is incremented.

- (f) The register B contents are decremented. Steps (d) to(e) above are repeated until the register contents are decremented to 0.

- (g) A 1 byte of augend, indicated by the augend address, is read into register A.

- (h) A 1 byte of addend, indicated by the addend address, is added with carry to the register A contents.

- (i) If the carry flag is 0, execution jumps to (k).

- (j) The sign flag is set to 1 and the carry flag is cleared to 0.

- (k) The register A contents are adjusted for decimal.

- (1) If an overflow has occurred, the carry flag or bit 7 for register A is set to 1. If either of these bits is

1, execution jumps to an error processing routine.

- (m) If the sign flag is 1, bit 7 of register A is set to 1.

- (n) The register A contents are stored in a memory location indicated by the augend address. This completes the operation.

- (o) The subtrahend is made positive and the sign flag is cleared to 0.

- (p) If the minuend is negative, it is made positive and the sign flag is set to 1.

- (q) The carry flag is cleared to 0.

- (r) A 1 byte of minuend, indicated by the minuend address, is read to register A.

- (s) A 1 byte of subtrahend, indicated by the subtrahend address, is subtracted with carry from the register A contents and the subtrahend address is subsequently incremented. The subtraction result is adjusted for decimal, and is stored in a memory location indicated by the minuend address. After that, the minuend address is incremented.

- (t) The register C contents are decremented. Steps (r) to

(s) above are repeated until the register contents are decremented to 0.

- (u) If the carry flag is 0, execution proceeds to (w).

- (v) The 10s complement of the result is computed and the sign flag is inverted.

- (w) If the result is 0, the operation ends.

- (x) If the sign flag is 1, processing (y) is started. If the flag is 0, the operation ends.

- (y) The result sign bit is set to 1, and the operation ends.

(6) Number of steps

83

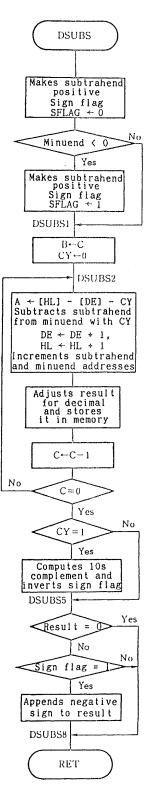

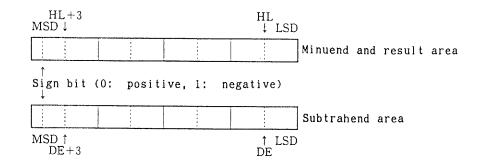

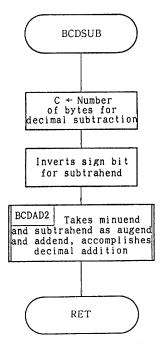

### (7) Flowchart

÷

(8) Program list NAME BCDADR

| * * * * * * * | decima<br>8<br>input<br>output                | l addition<br>digit <- 8 digi<br>condition<br>HL-register <- =<br>DE-register <- =<br>c condition<br>result <- (HL,H | *<br>augend area top.address *<br>addend area top.address *<br>* |

|---------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

|               | PUBLIC<br>PUBLIC<br>PUBLIC<br>EXTRN<br>EXTBIT | BCDADD, BCDAD1, I<br>DADDS<br>DSUBS<br>ERROR<br>SFLAG                                                                | BCDAD2<br>; work flag for sign flag                              |

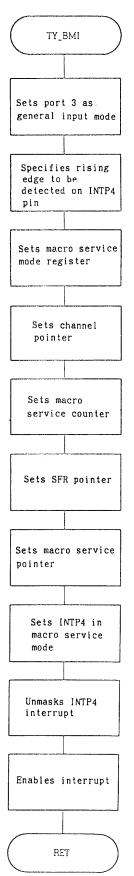

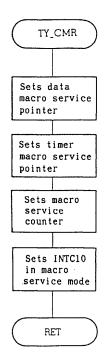

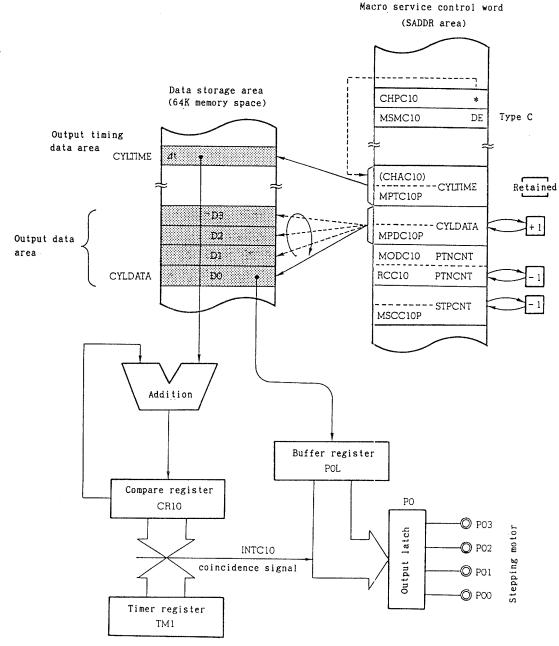

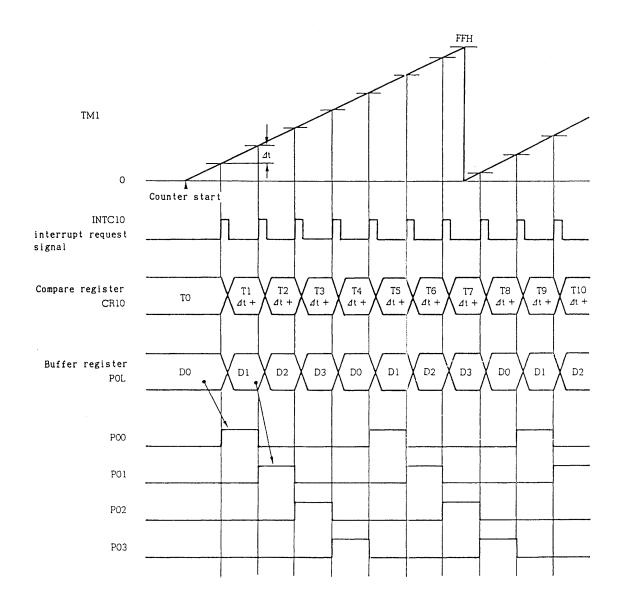

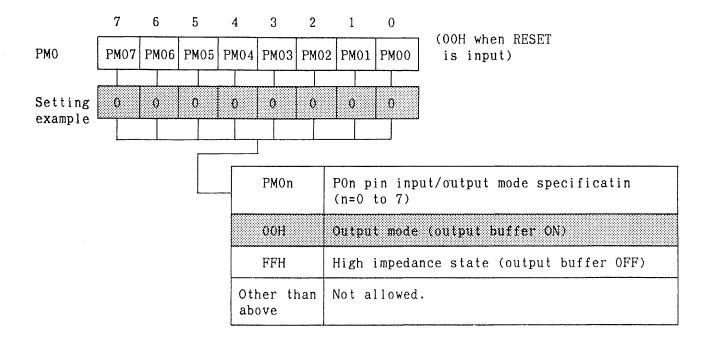

| BYTNUM        | EQU                                           | 4                                                                                                                    |                                                                  |