# NEC

**Application Note**

# **V850**

# **32-Bit Single-Chip Microcontrollers**

**Clock Monitor**

**V850E Series**

**V850ES Series**

Document No. U18898EE1V0AN00 Date Published 15 <sup>th</sup> August 2007 © NEC Electronics Corporation 2007 Printed in Germany [MEMO]

- The information in this document is current as of April, 2007. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual

property rights of third parties by or arising from the use of NEC Electronics products listed in this

document or any other liability arising from the use of such products. No license, express, implied or

otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics

or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics

products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated

entirely. To minimize risks of damage to property or injury (including death) to persons arising from

defects in NEC Electronics products, customers must incorporate sufficient safety measures in their

design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

#### (Note)

(1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

(2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02. 11-1

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### NEC Electronics America Inc.

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### NEC Electronics (Europe) GmbH

Duesseldorf, Germany Tel: 0211-65 030 Fax: 0211-65 03 1327

#### Sucursal en España

Madrid, Spain Tel: 091-504 27 87 Fax: 091-504 28 60

#### Succursale Française

Vélizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99 Filiale Italiana Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

Branch The Netherlands Eindhoven, The Netherlands Tel: 040-244 58 45 Fax: 040-244 45 80

#### Branch Sweden

Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

# United Kingdom Branch

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290 NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

#### NEC Electronics Hong Kong Ltd.

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd. Singapore Tel: 65-6253-8311 Fax: 65-6250-3583

# NEC Electronics Taiwan Ltd.

Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

# Introduction

| Target Readers      | This application note is intended for users who understand the functions of the V850 and will use this product to design application systems.                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose             | The purpose of this application note is to help users to understand the functionality, benefits and how to use the clock monitor implemented in several microcontrollers of theV850E and V850ES subseries. The clock monitor peripheral an its features differ from device to device. So, the handling and usage shown in this document is for reference only. Correct operation is not guaranteed if these samples are implemented as they are described here. The user has to adapt the usage and handling of the clock monitor to his application specific needs. |

| Organization        | <ul> <li>This manual consists of the following main sections.</li> <li>Reason for implementation of a clock monitor</li> <li>Functionality of a clock monitor</li> <li>Remarks for usage of a clock monitor in an application</li> <li>Hints for handling during stand – by modes</li> <li>Handling example when clock monitor has generated a reset</li> </ul>                                                                                                                                                                                                      |

| How to Read This Ma |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                     | It is assumed that the reader of this manual has general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | <ul> <li>To gain a general understanding of functions:</li> <li>→ Read this manual in the order of the CONTENTS. The mark "<r>" shows major revised points. The revised points can be easily searched by copying an "<r>" in the PDF file and specifying it in the "Find what:" field.</r></r></li> </ul>                                                                                                                                                                                                                                                            |

|                     | • To learn more about the 78K0/Kx2's hardware functions: $\rightarrow$ See the user's manual of each 78K0 product.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Conventions         | Data significance:Higher digits on the left and lower digits on the rightActive low representation:xxx (overscore over pin or signal name)Note:Footnote for item marked with Note in the textCaution:Information requiring particular attentionRemark:Supplementary informationNumeral representation:Binaryxxxx or xxxxBDecimalxxxxHexadecimalxxxH                                                                                                                                                                                                                  |

# **Table of Contents**

| CHAF | PTER  | 1 BENEFITS OF A CLOCK MONITOR                                 | 8  |

|------|-------|---------------------------------------------------------------|----|

| 1.1  | Rea   | ison and benefit of a clock monitor                           | 8  |

| CHAF | PTER  | 2 FUNCTIONALITY OF A CLOCK MONITOR                            | 9  |

| 2.1  | Prir  | ncipal description of a clock monitor                         | 9  |

| 2.2  | 2 Cor | ntrolling the clock monitor                                   | 10 |

|      | 2.2.1 | Enabling clock monitor peripheral                             | 10 |

|      | 2.2.2 | Stopping clock monitoring during STOP – mode                  | 11 |

|      | 2.2.3 | Stopping the clock monitor when the internal oscillator stops | 12 |

| CHAF | PTER  | 3 BEHAVIOUR AFTER RESET RELEASE                               | 13 |

| 3.1  | Det   | ection of the indication for a Reset                          | 13 |

| 3.2  | 2 Han | ndling when a clock monitor reset has occured                 | 13 |

# List of Figures

| Figure 2-1. Principal block diagram of a clock monitor                           | 9  |

|----------------------------------------------------------------------------------|----|

| Figure 2-2. Timing diagram when the mainclock fails                              | 9  |

| Figure 2-3. Principal of a clock monitor with controlling function               | 10 |

| Figure 2-4. Clock monitor operation during STOP mode and after STOP mode release | 11 |

| Figure 2-5. Stopping the supervision when internal oscillator stops              | 12 |

| Figure 3-1. Example for a reset control flag register (RESF)                     | 13 |

# CHAPTER 1 BENEFITS OF A CLOCK MONITOR

# 1.1 Reason and benefit of a clock monitor

At the pins X1/X2, a resonator or quartz is connected to a microcontroller. The frequency which is generated by this oscillator is called mainclock. The mainclock is responsible for all functionality in the microcontroller. It is used to run the software, it clocks the on – board peripherals and is responsible to realise the timing, necessary for the specific application. If the mainclock stops unexpectedly, the microcontroller hangs up and the functionality of the application fails. It is imaginable that in some applications a microcontroller hang up will be a big disaster because this might destroy external environment or jeopardize humans.

The clock monitor is a peripheral, which supervises the mainclock. When the mainclock is much slower than expected or even stops, the clock monitor detects this and reacts on it.

The kind of reaction differs among the microcontrollers. Usually the clock monitor generates an internal reset when the mainclock fails. In some controllers the user has the possibility to select if an internal reset will be generated or a vectored interrupt (NMI) is generated by software. In most controllers, a marker bit is set during clock monitors reset generation. During reset initialisation the user can check if this marker bit is set and run a special software which handles the malfunction.

With the clock monitor peripheral, the microcontroller can react very fast on a mainclock failure and system break down can be prevented. Even some restricted functionality of the application can be realised or information of malfunction can be send to an host.

# CHAPTER 2 FUNCTIONALITY OF A CLOCK MONITOR

# 2.1 Principal description of a clock monitor

For the functionality of a clock monitor, a second active frequency is necessary to supervise the mainclock. To be sure that the clock, used for supervision is working in each case, an internal oscillator is used for supervision. This internal oscillator has no connection to external. There is no pin which can influence or even stop the internal oscillator from outside. It is a very reliable kind of oscillator, active just when power supply is connected.

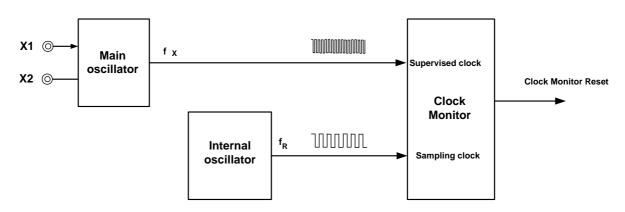

The principal block diagram of a clock monitor is shown in Figure 2-1.

# Figure 2-1. Principal block diagram of a clock monitor

The clock monitor samples the mainclock by using the internal oscillator. It generates a reset request signal when the oscillation of the mainclock has stopped or is too slow.

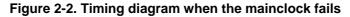

Figure 2-2 shows the internal behaviour when the mainclock fails. In this example, the mainclock supervision time takes four clocks of the internal oscillator. When there is no mainclock during this time frame, an internal reset request is generated.

# 2.2 Controlling the clock monitor

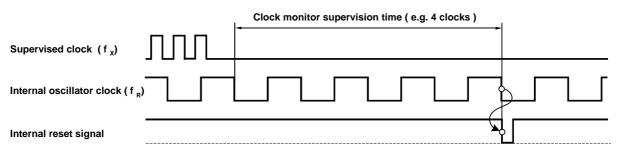

## 2.2.1 Enabling clock monitor peripheral

In some applications, the clock monitor is not necessary or even not practicable. For this reason, the clock monitor can be switched on by software (CLME = 1) when it will be used in an application. Due to security reasons, if it is switched on once, it can not be switched off by software any more. Only a reset, even that one generated from the clock monitor itself, will reset the clock monitor enable bit (CLME = 0).

After reset release the microcontroller starts with CLME = 0 and the clock monitor is disabled.

### Figure 2-3. Principal of a clock monitor with controlling function

## 2.2.2 Stopping clock monitoring during STOP – mode

To be able to use the standby modes even when the clock monitor is active, there is a control unit included which takes care that the clock monitor is disabled when the mainclock is stopped in a controlled manner. Remember: once enabled, the clock monitor cannot be stopped by software any more.

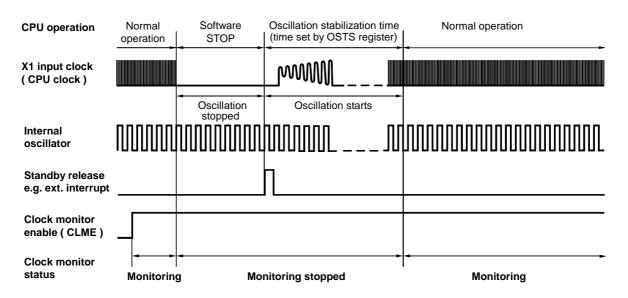

When the STOP – mode is entered, the mainclock is stopped. A control logic detects this and stops the supervision during STOP – mode and after reset release during oscillation stabilisation time.

Figure 2-4. Clock monitor operation during STOP mode and after STOP mode release

Within the standby modes HALT, IDLE1 and IDLE2, the mainclock keeps oscillating. When the clock monitor is enabled (CLME = 1) and the internal oscillator remains active, the clock monitor status is "monitoring".

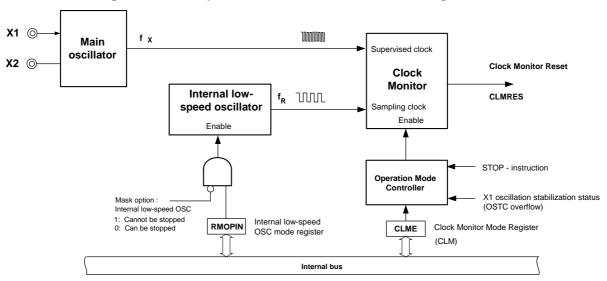

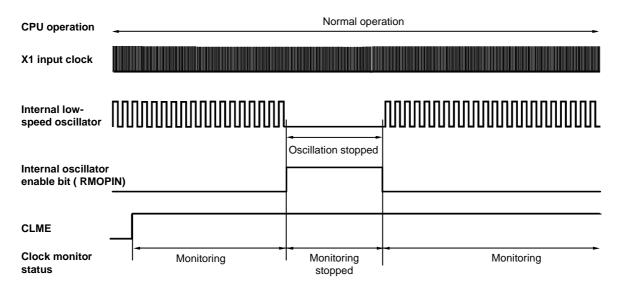

## 2.2.3 Stopping the clock monitor when the internal oscillator stops

Usually the user can decide if the internal oscillator can be switched on and off via software. This decision is fixed either by a mask option in a mask device or within an option byte in a flash device. So, this decision is fixed for all time due to the fact that the software can not change the option byte or a mask option by accident. So, the user can select either "internal oscillator can be stopped by software".

For supervision of the mainclock it is necessary that the internal oscillator is active. When the option "internal oscillator can be stopped by software" is selected and the internal oscillator is stopped by software, the clock monitor is also stopped. This gives the user the possibility to halt the supervision of the mainclock for a certain time. On one hand this is flexible, on the other hand, this is a security risk. If the mainclock fails while the internal oscillator is stopped, this failure of the mainclock is not detected.

When the internal oscillator is switched on by software again, the supervision function of the clock monitor is available as well again (see: Figure 2-5).

# Figure 2-5. Stopping the supervision when internal oscillator stops

# CHAPTER 3 BEHAVIOUR AFTER RESET RELEASE

# 3.1 Detection of the indication for a Reset

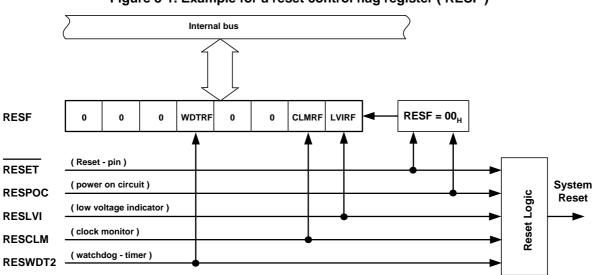

Several reasons for a reset are possible. The usual source of a reset is when a reset signal is applied at the external reset – pin or that the internal power – on detection unit (POC) generates a reset. These resets are harmless ones, no functional abnormality has to be assumed.

When a reset is generated from a watchdog – timer (WDT), a low voltage indicator (LVI) or the clock monitor (CLM), an abnormal situation has been detected. In the controller, usually a reset control flag register (RESF) is implemented which stores the source of the reset. When this register is read during the reset software routine, the reason for the previously occurred abnormal operation can be detected.

Figure 3-1 shows an example how such a register is configured. Due to the microcontrollers of the V850 family differs in their peripherals, the specific configuration of the reset control flag register has to be examined in the relevant users manual.

## 3.2 Handling when a clock monitor reset has occured

After reset release, the software can read this reset control flag register. If the clock monitor reset flag is set, the mainclock has failed before. Now, the software is able to react on such failure. It depends on the application which kind of reaction is useful and possible.

After reset, the controller starts execution of the instructions based on its internal oscillator. So, in case of a clock monitor reset previously, it is not necessary to switch to the faulty mainclock. With its internal CPU clock, reduced functionality of the application should be available. An error message might be send to a host or an error indicator might show the malfunction for servicing.