# CLOCK AND SIGNAL DISTRIBUTION USING FCT CLOCK BUFFERS

# APPLICATION NOTE AN-150

# INTRODUCTION

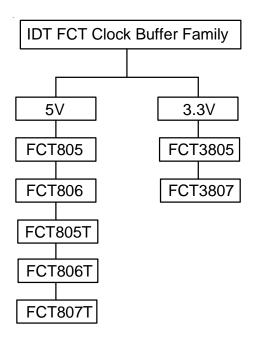

In synchronous systems where timing and performance of the system are dependent on the clock, integrity of the clock signal is important. Thus information on the characteristics of IDT clock buffers are provided in this application note. IDT has a family of low skew clock distribution chips. This application note discusses both IDT clock buffer characteristics and general clock distribution issues. Information on IDT's phase-lock loop-based clock distribution chips can be found in specific datasheets and a separate application note (AN-155).

## **TABLE OF CONTENTS**

| CLOCK BUFFER CHARACTERISTICS  | 1 |

|-------------------------------|---|

| AC CHARACTERISTICS            | 3 |

| SIGNALINTEGRITY               | 4 |

| Switching noise               | 4 |

| Transmission Line Reflections | 5 |

| Decoupling                    | 5 |

| EMI                           | 6 |

| SUMMARY                       | 6 |

# **CLOCK BUFFER CHARACTERISTICS**

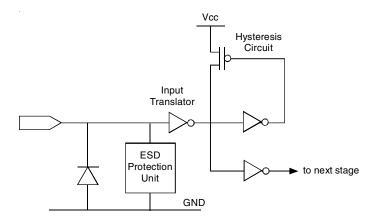

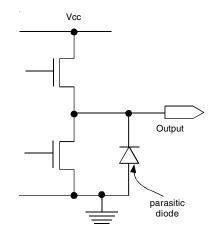

AllIDT clock buffers have 150 to 200mV of hysteresis. Their input structure is similar to other FCT/FCT-T devices and is shown in figure 1 (next page). 5V FCT-T (TTL outputs) clock buffers have a totem pole output structure consisting of an nchannel pullup transistor and an n-channel pulldown transistor. 5V FCT (CMOS outputs) clock buffers and 3.3V clock buffers, however, have a p-channel pullup instead. Figure 2 (next page) shows the two types of clock buffer output structures.

Figure 1: IDT Clock Buffer Input Structure

The devices with p-channel pullups have rail-to-rail output voltage swings, while devices with n-channel pullups have TTL output voltage swings. This difference is highlighted in a datasheet by typical Voh specifications as shown in the tables below.

Vcc parasitic diode

Output

parasitic diode

CMOS Output: FCT805/806, FCT3805, FCT3807

Another difference between the two types of output structures is the parasitic diode clamp to Vcc. 5V FCT-T buffers have no diode clamp to Vcc, while 3.3V devices and 5V FCT buffers have the diode.

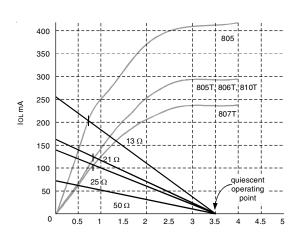

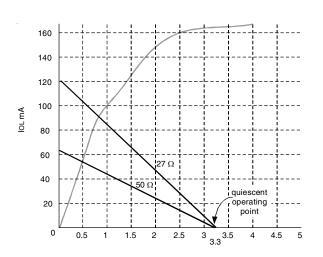

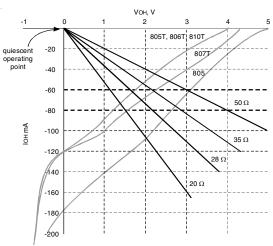

Static drive specifications in datasheets are often standard values maintained for compatibility reasons. The output drive characteristics of a device are usually more accurately represented by typical V/I curves. The output V/I graphs for the pullup(logic high) and pulldown(logic low) stages of IDT clock drivers are shown in figures 3, 4, 5 and 6 (next page). The equivalent output impedance of the driver can be obtained from the straightline portion of the output V/I curves. The FCT LOGIC HIGH, FCT-T LOGIC HIGH, and CLOCK BUFFER OUTPUT DRIVE tables present output driver information on various IDT clock buffers. Clock lines are often required to drive long traces and need sufficient drive capability for this. IDT Clock drivers typically have strong output drivers. Transmission line impedances have been superimposed on the output V/I curves in figures 3,4,5 and 6 to give an idea of the impedance the driver is capable of switching. In addition to the  $50\Omega$  load the graphs also show the minimum impedance each driver is capable of switching on first incidence. As more aggressive technologies are introduced speeds and edge

TTL Output: FCT805T/806T, FCT807T

Figure 2: IDT Clock Buffer Output Structures

# **FCTLOGICHIGH**

| Symbol | Parameter           | Test Conditions                                                | Min. | Тур. | Max. | Unit |

|--------|---------------------|----------------------------------------------------------------|------|------|------|------|

| Vон    | Output HIGH Voltage | Vcc = Min., $Vin = Vih or Vil (Vhc = Vcc - 0.2V), Ioh = -15mA$ | Vнс  | Vcc  | 1    | V    |

# **FCT-TLOGIC HIGH**

| Symbol | Parameter           | Test Conditions                           | Min. | Тур. | Max. | Unit |

|--------|---------------------|-------------------------------------------|------|------|------|------|

| Vон    | Output HIGH Voltage | Vcc = Min., Vin = Vih or Vil, Ioh = -15mA | 2.4  | 3.3  | -    | V    |

Figure 3: FCT805, FCT805T/806T, FCT807T Output LOW

Figure 5: FCT3805/3807 Output LOW

Figure 4: FCT805, FCT805T/806T, FCT807T Output HIGH

Figure 6: FCT3805/3807 Output HIGH

# **CLOCK BUFFER OUTPUT DRIVE AND IMPEDANCE**

| Device        | Output Voltage<br>Swing | Ron (HIGH) | Ron (LOW) | Dymanic Drive (typ.)<br>IODH/ IOLD | Static Drive Specs<br>Іон/ Іоц |

|---------------|-------------------------|------------|-----------|------------------------------------|--------------------------------|

| FCT805/806    | CMOS                    | 25Ω        | $4\Omega$ | -120/320mA                         | -24/64mA                       |

| FCT3805T/806T | ∏L                      | 25Ω        | Ω8        | -70/210mA                          | -15/48mA                       |

| FCT807T       | ΠL                      | 33Ω        | Ω8        | -80/175mA                          | -15/48mA                       |

| FCT3805       | CMOS                    | 12Ω        | 19Ω       | -50/115mA                          | -8/ 24mA                       |

| FCT3807       | CMOS                    | 12Ω        | 29Ω       | -50/135mA                          | -8/ 24mA                       |

rates get faster. The CLOCK BUFFER OUTPUT DRIVE table summarizes typical edge rates encountered with IDT clock buffers. These edge rates are measured between 10% and 90% levels into a standard 50pF, 500 $\Omega$  load. In addition to this rise and fall times between 0.8V and 2.0V are also specified in the datasheet.

# **ACCHARACTERISTICS**

IDT clock buffers are available in a number of different speed grades and key parameters are shown in the 5V CLOCK BUFFER and 3.3V CLOCK

BUFFER tables. AC parameters for logic devices are specified with a standard test load of 50pF in parallel with 500  $\Omega$ . In the case of clock buffers, some devices like the 807 and 3807 are specified with several different load configurations that include pure capacitive loads and transmission line loads. This provides users with a closer approximation to the real life load. AC performance tends to degrade at higher capacitive loads and this performance penalty can be estimated using derating factors. Typical derating factors for IDT clock buffers are :

Propagation delay load derating Output skew load derating 2ns/100pF 75ps/10pF

## **5V CLOCK BUFFER PERFORMANCE**

| Parameter | 805,806 | 805A, 806A | 805BT, 806BT | 805CT, 806CT | 807BT | 807CT |

|-----------|---------|------------|--------------|--------------|-------|-------|

| tpD       | 6.5     | 5.8        | 5            | 4.5          | 3.8   | 3.5   |

| tsk(o)    | 0.7     | 0.7        | 0.7          | 0.5          | 0.5   | 0.25  |

| tsk(p)    | 1       | 1          | 0.7          | 0.6          | 0.5   | 0.35  |

| tsk(t)    | 1.5     | 1.5        | 1.2          | 1            | 1     | 0.75  |

# 3.3V CLOCK BUFFER PERFORMANCE

| Parameter | 3805 | 3805A | 3807 | 3807A |

|-----------|------|-------|------|-------|

| tpD       | 5.8  | 5     | 4.8  | 4.3   |

| tsk(o)    | 0.7  | 0.7   | 0.5  | 0.35  |

| tsk(p)    | 1    | 0.7   | 0.5  | 0.35  |

| tsk(t)    | 1.5  | 1.2   | 1    | 0.75  |

# **SIGNAL INTEGRITY**

Noise on a clock line is harmful because it can result in false switching and data corruption in downstream devices. Taking appropriate steps to reduce noise on the clock line is critical since it can have wide ranging effects on systems ranging from EMI and system malfunction to degradation of performance and reliability. This section provides some guidelines on improving clock signal integrity.

# Switching noise

As in the case of all high performance logic, a key contributor to noise on a clock line is simultaneous switching noise or "ground/Vcc bounce". Every device has certain inherent switching noise characteristics which can be compared by means of a ground bounce test. This test requires that the effect of simultaneously switching outputs be measured on a "quiet" or low output. This is not always possible, especially in the case of clock buffers - there may be no "quiet" output available. In such cases, overshoot and undershoot on a switching output can be used as the next best measure of switching noise. Vcc or ground noise is given by,

$V_G = L_G di/dt = L_G (C_L d^2 V/dt^2)$

where

Lg = Vcc or ground lead inductance

C<sub>L</sub> = Load capacitance

dV = Output voltage swing

dt=rise/fall time

The equation shows that switching noise is dependent on package inductance, edge rates, output voltage swings and the output load.

## a. Package inductance

Packages with reduced lead inductances are to be preferred. Usually smaller packages tend to have lower associated package inductances.

## b. Edge rates

Faster edge rates are usually responsible for generating greater ground bounce because Vg is inversely proportional to the square of dt. Edge rates

# **CLOCK BUFFER OUTPUT EDGE RATES(1)**

| Device       | Rise Time | Fall Time |

|--------------|-----------|-----------|

| FCT805/806   | 3ns       | 1.7ns     |

| FCT805T/806T | 3.5ns     | 2.6ns     |

| FCT807T      | 3ns       | 1.7ns     |

| FCT3805      | 2.5ns     | 1.6ns     |

| FCT3807      | 3.7ns     | 2.3ns     |

|              |           |           |

#### NOTE:

1. Typical output edge rates between 10% and 90% levels.

# CLOCK BUFFER PACKAGE PARASITICS(1)

| Package | Inductance L, nH     | Capacitance Сім/ Соит, pF |

|---------|----------------------|---------------------------|

| PDIP-20 | 8nH                  | 6pF/8pF                   |

| PDIP-24 | 12nH                 | 6pF/8pF                   |

| SOIC-20 | 5nH                  | 6pF/8pF                   |

| SOIC-24 | 6nH                  | 6pF/8pF                   |

| SSOP-20 | 4nH                  | 6pF/8pF                   |

| SSOP-24 | 4nH                  | 6pF/8pF                   |

| QSOP-20 | 3.5nH <sup>(1)</sup> | 6pF/8pF                   |

| QSOP-24 | 3.5nH <sup>(1)</sup> | 6pF/8pF                   |

|         |                      |                           |

#### NOTE:

1. Modeled approximation.

on IDT buffers are given in the CLOCK BUFFER OUTPUT EDGE RATES table.

## c. Output voltage swings

Wider output voltage swings generate more switching noise(larger dV). Thus TTL outputs (FCT-T devices) are preferred over CMOS outputs (FCT devices) for 5V designs.

## d. Output load

The output load effects two factors in the above equation -  $C_L$  and dt.  $V_G$  is directly proportional to  $C_L$  and inversely proportional to  $dt^2$ . Increasing the output load causes both  $C_L$  and dt to go up. Usually the effect of the increase indt dominates and the switching noise decreases with increasing load, but this is not a linear variation and the decrease in switching noise tends to flatten out at large loads. The effect of other parasitics in the equation can also cause unpredictable effects with increasing capacitive load.

## **Transmission Line Reflections**

Traces longer than four or five inches appear as transmission lines to an FCT/FCT-T driver. This is because an output edge rate faster than two or three times the transmission line delay requires special consideration over a simpler lumped capacitive load model. Typical microstrip traces have a line impedance of  $70\Omega$  which corresponds to a line capacitance of 2pF per inch or a delay of 0.15ns per inch. Typical FCT edge rates lie in the 2ns range. Once it has been determined that the load is infact a transmission line, the line should be properly terminated in order to reduce line reflections. There are two main questions that arise:

1) Does the driver have sufficient drive capability to achieve first incidence switching at the receiver or the sending end of the line?

This can be verified by drawing a line with slope corresponding to the line impedance from the quiescent point (0V, 0mA for logic low and 3.5V, 0mA for a logic high TTL output) and intersecting the driver's output V/I curve. This is illustrated for the various IDT clock buffers in figures 3,4,5 and 6. In cases where the line has loads distributed along its length, the impedance of the line is driven down further. The loaded line impedance is given by:

$Z_L = Z_O [C_O/(C_O + C_L)]^{1/2}$

where

Zo - the unloaded line impedance

Z<sub>L</sub> - loaded line impedance

Co - the inherent line capacitance per unit length

CL - the load capacitance per unit length.

For example, a 10inch long  $70\Omega$  line loaded with two distributed loads of 8pF each presents a lowered effective line impedance of ~52 $\Omega$ . A lower impedance now requires a stronger driver to drive to the same logic voltage threshold.

2) Is the line properly terminated to prevent line reflections and ringing?

The line can be terminated either at the near end or the far end. Series termination is used at the near end and parallel termination, Thevenin termination or ac termination is used at the far end. Near end termination seeks to match the source end impedance (output driver + series resistor) and absorbs relections at the near end. Far end termination seeks to match the termination value to the line impedance preventing any reflections at the far end. The advantages and disadvantages of the different termination schemes are discussed in greater detail in a separate IDT application note.

## a. Type of termination

In general, the preferred termination techniques are series or ac termination. For tight timing budgets series termination sometimes poses a problem by adding to the output skew.

## b. Termination values

Series termination - Sum total of driver output impedance and series resistor should equal the line impedance. Assuming a loaded line impedance of  $50\Omega$ , a termination value of  $25\Omega$  to  $33\Omega$  usually works.

Parallel termination - Termination value should match the line impedance.

The venin termination - Equivalent The venin impedance should match the line impedance. Also the voltage at the line termination point should be above the threshold voltage of the receiver. Terminating with  $100\Omega$  to Vcc &  $100\Omega$  to ground matches a  $50\Omega$  line impedance and also maintains a voltage at the line termination point of Vcc/2 which is above the receiver input threshold of 2.4V.

AC Termination - Here the value of the termination resistor should match the line impedance and the terminating capacitor value should be such that RC time constant > 3 times the line delay. Commonly used ac termination values for a  $50\Omega$  line are  $50\Omega$  and 220pF.

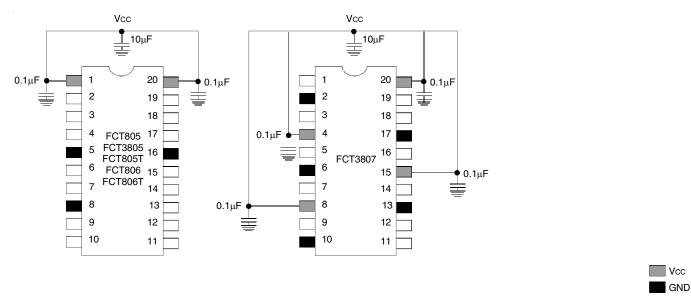

## Decoupling

Adequate and proper decoupling is very important. Bypass capacitors provide the required current surge for transient switching. Some guidelines for decoupling high speed clock buffers are given below.

- Use ceramic capacitors for each Vcc pin. 0.1mF is a good value to use here. One large MLC (multilayer ceramic chip capacitor) should be used per chip for power supply bypassing. These work best for power supply decoupling on account of their low inductance characteristics. A 10mF to 50mF capacitor value is usually suitable here.

- The bypass capacitor should be placed right at the device Vcc pin where possible and connected to the ground plane on the other side. Capacitor, device and trace inductance which together make up the Vcc-ground loop length must be minimized.

- Pick the capacitor value based on the device loading. The bypass cap should be able to supply the required amount of switching current at frequency.

As an example consider a case of a clock driver with 10 outputs each driving  $70\Omega$  transmission lines.

Total current required =  $10 \times 5V / 70\Omega = 714 \text{mA}$

So, I = CdV/dt = 714mA

Assuming an allowable Vcc droop of 30mV and an output edge rate of 2ns, minimum required bypass capacitor value

- $= 0.714 \times 2ns / 30mV$

- = 0.047 mF

Figure 6: Recommended Decoupling

For lower values of line impedance, I increases and therefore a higher capacitor value may be required. Figure 7 shows decoupling schemes for IDT clock buffers.

# **EMI**

There is a strong correlation between noise and EMI, so all precautions discussed in previous sections should be reviewed carefully when seeking to reduce EMI. In addition, some simple rules pertaining to board layout can help in reducing EMI.

Arule of thumb for reducing EMI is to ensure that the clock driver is located towards the center of the PCB rather than at the periphery. The magnetic dipole moments tend to be higher when the clock traces are located at the periphery of the board or card worsening the risk of EMI. Burying the clock traces in inner signal layers sandwiched between ground and Vcc planes is also a good precaution. For clock signals that are routed on a surface layer, additional EMI protection can be achieved by routing ground traces parallel to and on either side of the clock trace. Refer to REFERENCES for recommendations on spacing the vias connecting these ground traces to the ground plane.

Narrow signal traces tend to increase high frequency damping and reduce capacitive coupling between traces. Thus 4 to 8 mil traces should be used for clock signals. Right angles should be avoided as they increase the trace capacitance and also introduce an impedance discontinuity that could effect signal integrity. Crosstalk can contribute to EMI, so ensure that there are no clock lines running on long traces parallel to each other. Spacing between traces should at least equal the trace width.

Designs today call for the use of high speed logic families whose faster edge rates tend to radiate more high frequency energy. It is important therefore that the board enclosure contain the radiated energy. Shielding plays an important role in reducing EMI and adequate shielding should be provided around openings in the board enclosure such as cable or wiring outlets, disk drives, etc.

Ferrites are commonly used to suppress high frequency common mode radiation. The impedance of a ferrite varies with frequency, so that at high frequencies it behaves more like a resistor than an inductor. Thus by choosing a ferrite with appropriate impedance characteristics over frequency the ferrite's resistive losses can be used to eliminate specific offending frequency radiation.

# **SUMMARY**

This application note seeks to provide designers with information on the characteristics of IDT clock buffers and guidelines to reduce noise on the clock signals. The designer is advised to refer to current IDT datasheets for specifications on all IDT clock products.

## REFERENCES

<u>Printed Circuit Design Techniques for the control of EMI</u>, Michael Conn. 1993 HP High Speed Digital Symposium.

## **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

## **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

## **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.