# AN-1167 Utility Transformer Protection using GreenPAK

Author: Muhammad Waseem Date: December 17, 2016

# Introduction

The GreenPAK device can be used for the protection of utility power equipment. In this application note, we will explain how to design and implement the differential protection of a single-phase transformer using the GreenPAK3. This design will help to protect the transformer from internal faults, i.e. inter-turn faults, bushing faults, single phase to ground faults, double line to ground fault, etc. Two analog inputs from the current transformer are monitored and those are used to detect faults in a power system.

## **Problem Statement**

Faults are inevitable in power system generation, transmission and distribution. Protection devices are designed to overcome these unavoidable conditions and increase the reliability of the system. The transformer is the most important and costly equipment in a power system. Therefore, proper protection of the transformer is required.

## **Transformer Background**

A Power System deals with the generation, transmission and distribution of electrical energy from the source to load end, and devices that are connected to such systems include generators, transformers, and motors.

The transformer is the major component of the power system that is used to step up or down the voltage levels so that transmission line losses might be reduced.

It has two windings: one is known as a primary winding and the second one is known as secondary winding. The winding with high voltage is called HV (High Voltage) winding and other with low voltage is called LV (Low Voltage) winding. Transformers have been used at power generating stations to step up the voltage levels for the transmission purposes over long distances. At substations, transformers step down the voltage somewhat so that transmission lines can pass through populated areas without the induction phenomenon. Then finally distribution transformers are used to step-down the voltage levels for the load end use. There is an appropriate requirement to protect the transformer from faults that occur in the power system so that further damage can be avoided.

A Protective Relay is a device designed to trip a circuit breaker when a fault is detected. Relays may be categorized as Differential Relay, Distance Relay, Over-Current Relay, Under-Voltage Relay, etc. Of these, Differential Relay is primarily used for the protection of a transformer that has the boundaries HV CT (High Voltage Current Transformer) and LV CT (Low Voltage Current Transformer).

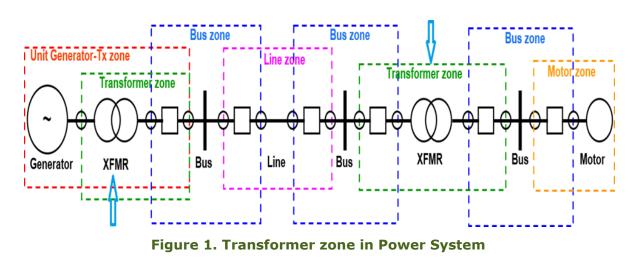

Since the transformer is an integral part of the bulk power system, it will probably require more sophisticated relays in terms of design and redundancy. The transformer zones in a power system are shown in Fig. 1

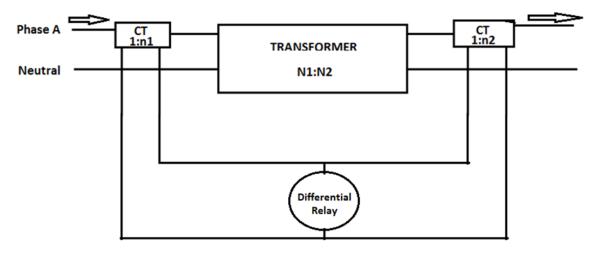

The HV and LV side currents are first stepped down to 5A or 1A using CT and then the difference of magnitude is taken between the two currents. In normal conditions, the difference is zero. But when a fault occurs then the difference is not equal to zero and transformer needs protection from faults to avoid the detrimental effects. Based on the difference value, a trip signal is generated and it is sent to the circuit breaker. The circuit breaker opens the circuit on both sides of the transformer and in this way the transformer can be protected from the faults. Block diagram for single phase protection of transformer is in Fig. 2.

There are two CTs that are connected at the HV and LV sides of the transformer. HV CT has a turn ratio of 1:n1 and LV CT has a turn ratio of 1:n2. CT is basically used to step down the current so that it can be measured accurately and easily. Thus, small and accurate instruments can be used to measure the current and then actual current flowing in the power system can be found by multiplying the measured current value with the turn ratio.

Mathematically, turn ratio can be written as:

Np = Number of turns in the primary winding;

Ns = Number of turns in the secondary winding;

Ip = Current in the primary winding;

Is = Current in the secondary winding;

To find Is, we have:

#### Is=Ip (Np/Ns)

Different ratings of CT are available in the market. It may be either 100/1, 200/1, 300/1, 400/1, 100/5, 200/5, 400/5, 800/5, 1200/5, etc. The numerator shows the primary current in amperes and denominator shows the secondary current of CT.

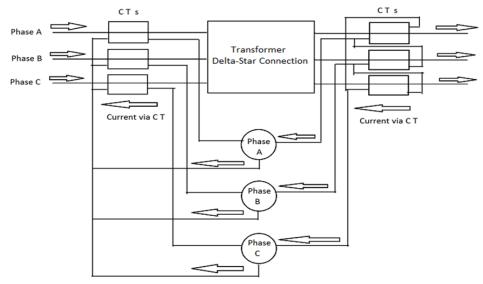

In three-phase protection of a transformer, three single phase differential relays are used to protect the transformer. It has total of six CTs, three on HV side and three on LV side.

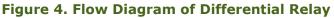

Figure 2. Single Phase Transformer Protection

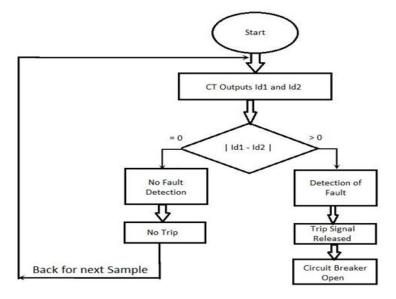

If the transformer has delta winding configuration on HV side, then CT connected on HV side will be in star winding connection and vice versa configuration is applied on LV side. It is used to cancel the effect of 30-degree phase shift that occurs due to Delta-Star connection of transformer windings. The Block diagram for the three-phase protection of transformer is shown in Fig. 3. The complete flow process for single phase transformer protection that starts from two outputs of CTs: take the difference between them and based on the difference value, the circuit compares and trips if needed. This is repeated to monitor whether there is normal current or fault current flowing through the power system. A flow diagram for the differential protection of transformer is depicted in Fig. 4. The top-level schematic for the designed differential protection of transformer is shown in Fig. 5.

**Figure 3. Three Phase Transformer Protection**

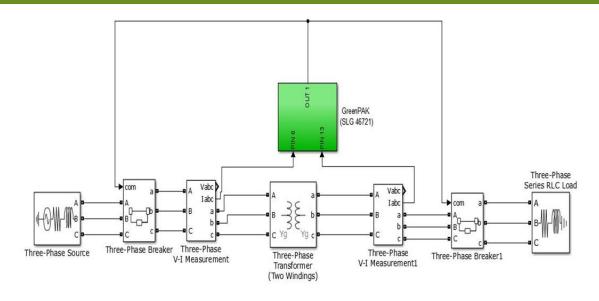

Figure 5. Connection Diagram

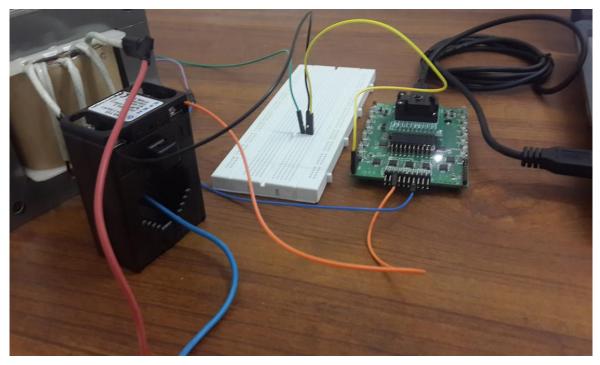

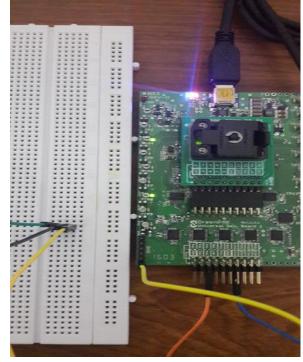

Figure 6. Connection to GreenPAK

## **GreenPAK Design**

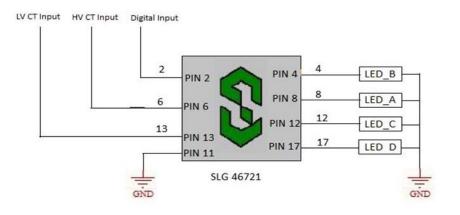

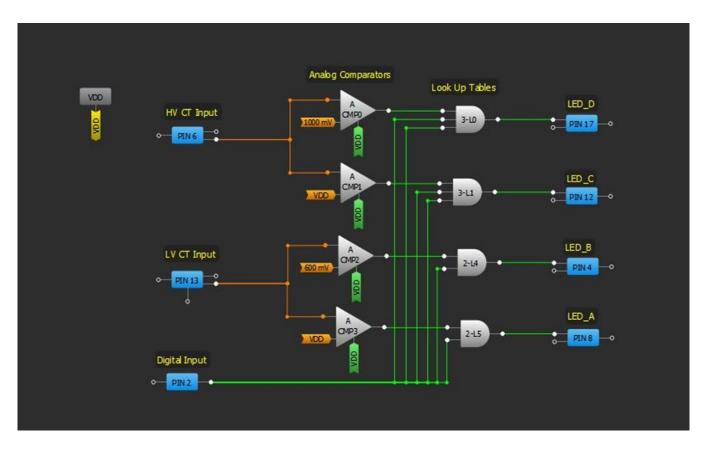

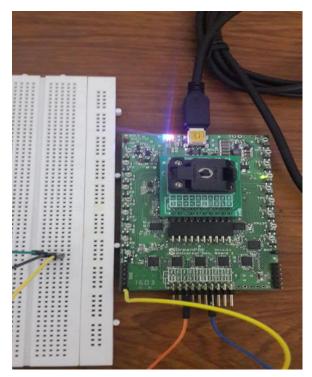

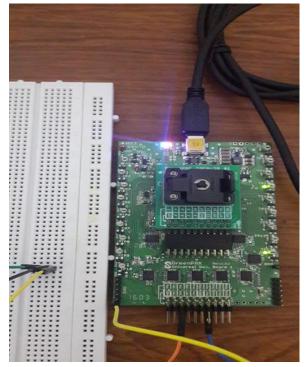

To implement differential protection of a transformer in GreenPAK, we are using the SLG 46721V. Required components are analog input pins, comparators, look up tables, VDD, ground, etc. Green PAK configuration for the Differential protection of a transformer is shown in Fig. 7.

## **GreenPAK Configuration Description**

In this configuration, we have used CT of 1A secondary current that supplies current at the analog input terminals. Therefore, during normal conditions 1A current flows through CT secondary but when a fault occurs then it increases, depending upon the fault intensity. During normal flow of current that is 1A, all the LEDs are turned off.

The LEDs turn on only due to the fault in the power system. If LED\_D is turned on, then it shows a minor fault on HV side and if LED\_C is turned on then it shows a severe fault on HV side.

Similarly, on LV side, LED\_B shows a minor fault, and LED\_A shows a severe fault.

## **High Voltage Current Transformer**

Analog input from HV CT has been taken and then it is fed to a comparator, A CMP0 compares the analog input at positive terminal with the fixed value applied to the negative terminal. The fixed value is the fault value that has been assigned. Its magnitude is VDD/4 (1.275). Normally 1A current flows through the CT but when a fault occurs then this current increases and voltage decreases. Therefore, a comparison is made between the positive terminal input and negative terminal input. During normal conditions, the positive input terminal of A CMPO is low so the output of the comparator is also low. But when a fault occurs then the positive input terminal value increases to higher than the negative terminal, and so the comparator output is high and then LED\_D is turned on due to all high inputs at the AND gate terminals.

A CMP1 has fault value of magnitude VDD/3 (1.7). In A CMP1, the fault current is compared with 1.7 and when the fault current is greater than this value, then LED\_C connected to the PIN 12 turns on and this shows the severe condition of fault current.

Figure 7. GreenPAK Configuration for Differential Protection of Transformer

## Low Voltage Current Transformer

On LV CT side, the analog output from LV CT is fed to the A CMP2 at the positive terminal and the negative terminal is supplied by the constant magnitude of VDD/4. During normal flow of 1A current, the comparison between input terminals of A CMP2 is not satisfied and so output of A CMP2 is low. But when a fault occurs and positive terminal input becomes greater than VDD/4 then the output of A CMP2 becomes high and LED B turns on due to the high output of the AND gate. A CMP3 also uses the analog output current of LV CT and compares it with VDD/3 magnitude. When a fault occurs, then A CMP3 compares the fault current with 1.7 and if fault current is greater than this value then LED A connected to PIN 8 turns on.

When PIN 8 LED turns on, it shows the severe nature of fault current and there is a need to generate the trip signal to the circuit breaker so that it can open both HV and LV terminals of the transformer from the power system.

## **Circuit Breaker Tripping**

Here we have used LEDs to display fault detection. Practically, when a fault occurs and depending upon the severity of the fault, a trip signal is sent to the circuit breaker and then it opens its terminals. One circuit breaker is connected before HV CT and the other is connected after LV CT. In this way, the transformer is taken out of the system so that high fault current might not damage it. This is an appropriate requirement for protection of transformer to save it from highly dangerous faults.

In order to operate the circuit breaker from GreenPAK designer, we have to connect output pins (previously connected to LEDs) to a 220V Arduino Relay Board or similar. It is shown in Fig. 8.

Figure 8. 220V Arduino Relay Board

This board is connected to the 220V supply from the main circuit. When the digital high value of 5 volts from GreenPAK is provided at the input of this board, then at the output it supplies 220V AC. Since circuit breakers operate at 110 DC voltages, so there is a need to convert AC to DC.

For that, we can use a rectifier. And then rectified DC voltage can be used to operate the circuit breaker.

## Conclusion

By using A CMP and LUT blocks of GPAK, we designed a differential relay that can be primarily used for the protection of a transformer. By using the GreenPAK to design this differential relay circuit, a single-phase transformer can be protected from internal faults. Three phase transformer protection can also be accomplished after making some modifications to this design.

# Appendix (detail of configuration settings in GreenPAK Designer)

There are two analog inputs that have been taken from HV CT and LV CT and are connected to the analog input/output pins 6 and 13 respectively. The configurations of both analog pins are shown in Figs. 9,10.

PIN 2 has been used as a digital input pin and its configuration is shown in Fig. 11.

The output pin of each analog input supplies current to two comparators at the positive input terminals. The negative input terminals of comparators are connected to constant magnitude. Here the comparison is made between the positive and negative terminal inputs.

If the positive terminal has higher magnitude, then the output of the comparator is high, otherwise it is low.

Pro

| PIN 13           |                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Analog in        | out/outpu <sup>r</sup>                                                                                                              |

| Analog in        | out/outpu                                                                                                                           |

| Analog in        | out/outpu                                                                                                                           |

| Pull down        |                                                                                                                                     |

| 1M               |                                                                                                                                     |

| ormation         |                                                                                                                                     |

| ons              |                                                                                                                                     |

| 3.3 V<br>min/max | 5.0 V<br>min/max                                                                                                                    |

| -/-              | -/-                                                                                                                                 |

| -/-              | -/-                                                                                                                                 |

| -/-              | -/-                                                                                                                                 |

| -/-              | -/-                                                                                                                                 |

| -/-              | -/-                                                                                                                                 |

|                  |                                                                                                                                     |

|                  | Analog in;<br>Analog in;<br>Analog in;<br>Pull down<br>1M<br>ormation<br>ons<br>3.3 V<br>min/max<br>-/-<br>-/-<br>-/-<br>-/-<br>-/- |

#### Figure 10. PIN 13 Configuration

| roperties              |                    | (                |  |

|------------------------|--------------------|------------------|--|

|                        | PIN 6              |                  |  |

| I/O selection:         | Analog input/outpu |                  |  |

| Input mode:<br>OE = 0  | Analog in          | out/outpu 👻      |  |

| Output mode:<br>OE = 1 | Analog in          | out/outpu 👻      |  |

| Resistor:              | Pull down          | Ŧ                |  |

| Resistor value:        | 1M                 | Ŧ                |  |

| Int                    | formation          |                  |  |

| lectrical Specificati  | ions               |                  |  |

| 1.8 V<br>min/max       | 3.3 V<br>min/max   | 5.0 V<br>min/max |  |

| -/-                    | -/-                | -/-              |  |

| -/-                    | -/-                | -/-              |  |

| -/-                    | -/-                | -/-              |  |

| -/-                    | -/-                | -/-              |  |

| -/-                    | -/-                | -/-              |  |

| -/-                    | -/-                | -/-              |  |

Figure 9. PIN 6 Configuration

|                        |                  | PIN 2            |                  |  |

|------------------------|------------------|------------------|------------------|--|

| I/O sele               | ction:           | Digital input    | t 🔻              |  |

| Input m<br>OE = 0      | ode:             | Digital in wi    | thout Sc 🔻       |  |

| Output mode:<br>OE = 1 |                  | None             | Ť                |  |

| Resistor               | :                | Pull down        |                  |  |

| Resistor value:        |                  | 1M •             |                  |  |

|                        | Info             | ormation         |                  |  |

| Electrical S           | pecificatio      | ns               |                  |  |

|                        | 1.8 V<br>min/max | 3.3 V<br>min/max | 5.0 V<br>min/max |  |

| V_IH (V)               | 1.100/-          | 1.780/-          | 2.640/-          |  |

| V_IL (V)               | -/0.690          | -/1.210          | -/1.840          |  |

| -                      | -/-              | -/-              | -/-              |  |

| -                      | -/-              | -/-              | -/-              |  |

| -                      | -/-              | -/-              | -/-              |  |

| -                      | -/-              | -/-              | -/-              |  |

|                        |                  | B                | Apply            |  |

#### Figure 11. PIN 2 Configuration

The configuration of each comparator is shown in Figs. 12-15.

| roperties                     |                | 5 |  |

|-------------------------------|----------------|---|--|

| A                             | CMP0           |   |  |

| 100uA pullup on<br>input:     | None           | Ŧ |  |

| Hysteresis:                   | 25 mV          | • |  |

| Low bandwi <mark>d</mark> th: | Disable        | • |  |

| IN+ gain:                     | Disable        | • |  |

| Con                           | nections       |   |  |

| IN+ source:                   | PIN 6          | • |  |

| IN- source:                   | VDD / 4        | • |  |

| Info                          | ormation       |   |  |

| Typical ACMP thresh           | olds           |   |  |

| V_IH (mV)<br>-                | V_IL (mV<br>-  | ) |  |

| Power                         | ctrl. settings |   |  |

| 0 5                           | Apply          |   |  |

#### Figure 12. A CMP0 Configuration

| roperties                 |                  |   |

|---------------------------|------------------|---|

| A                         | CMP1             |   |

| 100uA pullup on<br>input: | None             | ¥ |

| Hysteresis:               | 25 mV            | ٠ |

| Low bandwidth:            | Disable          | * |

| IN+ gain:                 | Disable          | * |

| Con                       | nections         |   |

| IN+ source:               | ACMP0 IN+ source | ٠ |

| IN- source:               | VDD / 3          | ٠ |

| Info                      | ormation         |   |

| ypical ACMP thresh        | olds             |   |

| V_IH (mV)                 | V_IL (mV)        |   |

|                           | -                | _ |

| Power                     | ctrl. settings   |   |

| <b>n</b> -                | Apply            | _ |

Figure 13. A CMP1 Configuration

| Properties                |                | 6   |

|---------------------------|----------------|-----|

| A                         | CMP2           |     |

| 100uA pullup on<br>input: | None           | v   |

| Hysteresis:               | 25 mV          | •   |

| Low bandwidth:            | Disable        | •   |

| IN+ gain:                 | Disable        | *   |

| Cor                       | nections       |     |

| IN+ source:               | PIN 13         | •   |

| IN- source:               | VDD / 4        | •   |

| Infe                      | ormation       |     |

| Typical ACMP thresh       | olds           |     |

| V_IH (mV)                 | V_IL (         | mV) |

|                           | -              |     |

| Power                     | ctrl. settings |     |

| 0 5                       | App:           | bly |

## Figure 14. A CMP2 Configuration

| Properties                |                  |   |

|---------------------------|------------------|---|

| А                         | CMP3             |   |

| 100uA pullup on<br>input: | None             | Ŧ |

| Hysteresis:               | 25 mV            | Ŧ |

| Low bandwidth:            | Disable          | * |

| IN+ gain:                 | Disable          | Ŧ |

| Con                       | inections        |   |

| IN+ source:               | ACMP2 IN+ source | ¥ |

| IN- source:               | VDD / 3          | ¥ |

| Info                      | ormation         |   |

| Typical ACMP thresh       | olds             |   |

| V_IH (mV)<br>-            | V_IL (mV)<br>-   |   |

| Power                     | ctrl. settings   |   |

| 0                         | Apply            |   |

#### Figure 15. A CMP3 Configuration

Then the output of each comparator is fed to an individual look-up table. Two 2-bit and two 3-bit look-up tables have been used. After connecting one input terminal to a comparator output, all other input terminals of look-up tables are connected to digital input pin 2 that is always at a high value.

is high then the output of look up table is also high since in look-up table we are using a standard AND gate. The configuration of each look-up table is shown in Figs. 16-19.

At the output of LUTs, four different LEDs are connected that are turned on if the input is high, otherwise it is turned off.

Figure 17. 3-bit LUT1 Configuration

|        | 2         | -bit LUT | 4   |        |

|--------|-----------|----------|-----|--------|

| IN3    | IN2       | IN1      | INO | OUT    |

| 0      | 0         | 0        | 0   | 0      |

| 0      | 0         | 0        | 1   | 0      |

| 0      | 0         | 1        | 0   | 0      |

| 0      | 0         | 1        | 1   | 1      |

| 0      | 1         | 0        | 0   | 0      |

| 0      | 1         | 0        | 1   | 0      |

| 0      | 1         | 1        | 0   | 0      |

| 0      | 1         | 1        | 1   | 0      |

| 1      | 0         | 0        | 0   | 0      |

| 1      | 0         | 0        | 1   | 0      |

| 1      | 0         | 1        | 0   | 0      |

| 1      | 0         | 1        | 1   | 0      |

| 1      | 1         | 0        | 0   | 0      |

| 1      | 1         | 0        | 1   | 0      |

| 1      | 1         | 1        | 0   | 0      |

| 1      | 1         | 1        | 1   | 0      |

| andard | gates     |          | A   | l to 0 |

| AND    |           | •        | A   | l to 1 |

| Reg    | ular shap | be       | Ir  | nvert  |

#### Figure 18. 2-bit LUT4 Configuration

Figure 19. 2-bit LUT5 Configuration

The configurations of LED pins are shown in Figs. 20-23.

|                        |                | PI       | 18               |                  |

|------------------------|----------------|----------|------------------|------------------|

| I/O select             | ion:           | D        | igital output    |                  |

| Input mod<br>OE = 0    | le:            | N        | one              | ÷                |

| Output mode:<br>OE = 1 |                | 1        | x push pull      | •                |

| Resistor:              |                | F        | oating           | ~                |

| Resistor value:        |                | Floating |                  |                  |

|                        | Inf            | orn      | nation           |                  |

| lectrical Spe          | cificatio      | ons      |                  |                  |

|                        | 1.8 \<br>min/m | 10       | 3.3 V<br>min/max | 5.0 V<br>min/max |

| V_OH (V)               | 1.690          | 1-       | 2.735/-          | 4.190/-          |

| V_OL (V)               | -/0.03         | 0        | -/0.228          | -/0.270          |

| OH (mA)                | 1.066          | /-       | 6.045/-          | 22.080/-         |

| I_OL (mA)              | 0.917          | /-       | 4.875/-          | 7.215/-          |

| -                      | -/-            |          | -/-              | -/-              |

|                        | -/-            |          | -/-              | -/-              |

#### Figure 20. PIN 8 Configuration

|                        |                | PIN      | 14               |                  |

|------------------------|----------------|----------|------------------|------------------|

| I/O select             | ion:           | D        | igital output    | • •              |

| Input mod<br>OE = 0    | ie:            | N        | one 💧            | ~                |

| Output mode:<br>OE = 1 |                | 1        | x push pull      | •                |

| Resistor:              |                | F        | oating           | Ŧ                |

| Resistor value:        |                | Floating |                  |                  |

|                        | Inf            | огп      | nation           |                  |

| lectrical Spe          | cificatio      | ons      |                  |                  |

|                        | 1.8 \<br>min/m | 10000    | 3.3 V<br>min/max | 5.0 V<br>min/max |

| V_OH (V)               | 1.690          | /-       | 2.735/-          | 4.190/-          |

| V_OL (V)               | -/0.03         | 0        | -/0.228          | -/0.270          |

| I_OH (mA)              | 1.066          | /-       | 6.045/-          | 22.080/-         |

| _OL (mA)               | 0.917          | /-       | 4.875/-          | 7.215/-          |

|                        | -/-            |          | -/-              | -/-              |

|                        | -/-            |          | -/-              | -/-              |

Figure 21. PIN 4 Configuration

|                        |                | PIN                | 12               |                  |

|------------------------|----------------|--------------------|------------------|------------------|

| I/O select             | ion:           | Di                 | gital output     | •                |

| Input mod<br>OE = 0    | je:            | N                  | one              | ÷                |

| Output mode:<br>OE = 1 |                | 1)                 | k push pull      | •                |

| Resistor:              |                | F                  | oating           | v                |

| Resistor value:        |                | Floating           |                  |                  |

|                        | Inf            | orm                | ation            |                  |

| Electrical Spe         | cificatio      | ons                |                  |                  |

|                        | 1.8 \<br>min/m | 100 million (1990) | 3.3 V<br>min/max | 5.0 V<br>min/max |

| V_OH (V)               | 1.690          | /-                 | 2.735/-          | 4.190/-          |

| V_OL (V)               | -/0.03         | 0                  | -/0.228          | -/0.270          |

| I_OH (mA)              | 1.066          | /-                 | 6.045/-          | 22.080/-         |

| I_OL (mA)              | 0.917          | /-                 | 4.875/-          | 7.215/-          |

| -                      | -/-            |                    | -/-              | -/-              |

|                        | -/-            |                    | -/-              | -/-              |

Figure 22. PIN 12 Configuration

| roperties           | 3              | PIN            | 17               |                  |  |

|---------------------|----------------|----------------|------------------|------------------|--|

| I/O select          | ion:           | Di             | gital output     | t - <del>-</del> |  |

| Input mod           | le:            | N              | one              | ~                |  |

| Output mo<br>OE = 1 | ode:           | 1x push pull 💌 |                  |                  |  |

| Resistor:           |                | F              | oating           | ~                |  |

| Resistor value:     |                | Floating       |                  |                  |  |

|                     | Infe           | огп            | ation            |                  |  |

| Electrical Spe      | cificatio      | ns             |                  |                  |  |

|                     | 1.8 \<br>min/m |                | 3.3 V<br>min/max | 5.0 V<br>min/max |  |

| V_OH (V)            | 1.690          | /-             | 2.735/-          | 4.190/-          |  |

| V_OL (V)            | -/0.03         | 0              | -/0.228          | -/0.270          |  |

| I_OH (mA)           | 1.066          | 1-             | 6.045/-          | 22.080/-         |  |

| I_OL (mA)           | 0.917          | /-             | 4.875/-          | 7.215/-          |  |

| -33                 | -/-            |                | -/-              | -/-              |  |

| -                   | -/-            |                | -/-              | -/-              |  |

|                     |                | E              | Ar               | ply              |  |

Figure 23. PIN 17 Configuration

# PIN 2 and VDD emulation settings are shown in Fig. 24.

💓 Signal Wizard Х Options General 1000.00 100.00 150.00 200.00 250.00 300.00 350.00 400.00 450.00 500.00 550.00 600.00 650.00 700.00 750.00 800.008 850.00 900.009 950.00 50.00 00'0 Generator: TP2 (PIN2) - Logic S 🔻 5.50 5.50 Shown period: Auto \* 4.4 Start point: 0.00 ms A T 1000.00 ms Stop point: 4.00 Global linkage: Linked ٠ 3.50 (INIA) DO . Cyclic Repeat: Repeat count: 2 2.00 Pre-start state: Low -4 1.50 Pre-start delay: 0.00 ms End state: Pre-start state \* 0.50 Output type: Push-Pull ۳ 0.00 0.00 \* Last state Pause type: Logic Generator Settings Mode: Normal -Т Level 1 500.00 ms \$ High ٣ 2 500.00 ms \$ High \* (2NI9) 241 00.00 200.00 300.00 350.00 400.00 \$50.00 500.00 550.00 600.009 650.00 700.00 750.00 800.008 850.00 900.006 950.00 \* 1 Insert (ms) ĉ Remove Logic levels 1 . Al Start Pause Stop Auto Min: 0.00 ms Max: 1000.00 ms 4 -) Auto Apply Ð Apply

Figure 24. VDD and PIN 2 Configuration

# Hardware Implementation

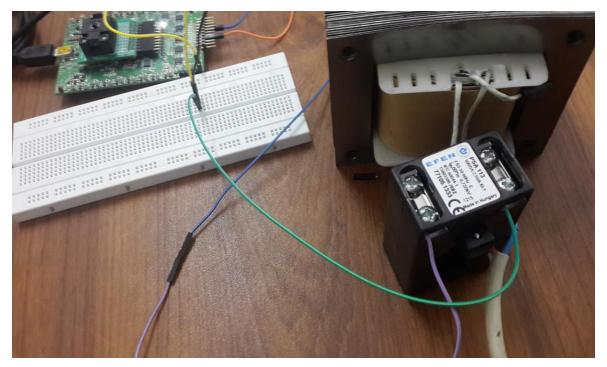

On LV side of transformer, ring type current transformer is connected and positive terminal of LV side is passed through it (Fig.25).

On HV side, the positive terminal of HV side is also passed through another CT as shown on Fig.26.

Figure 25. LV side Connection

Figure 26. HV side Connection

# **Transformer Inter-Turn Fault Results**

Figure 27. LED PIN 17 High

Figure 28. LED PIN 12 and 17 both High

Figure 29. LED PIN 4 High

Figure 30. LED PIN 4 and 8 High

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.