HI5731

12-Bit, 100MSPS, High Speed D/A Converter

FN4070 Rev 10.00 October 2, 2015

The HI5731 is a 12-bit, 100MSPS, D/A converter which is implemented in the Intersil BiCMOS 10V (HBC-10) process. Operating from +5V and -5.2V, the converter provides -20.48mA of full scale output current and includes an input data register and bandgap voltage reference. Low glitch energy and excellent frequency domain performance are achieved using a segmented architecture. The digital inputs are TTL/CMOS compatible and translated internally to ECL. All internal logic is implemented in ECL to achieve high switching speed with low noise. The addition of laser trimming assures 12-bit linearity is maintained along the entire transfer curve.

## Ordering Information

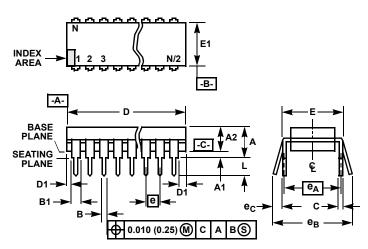

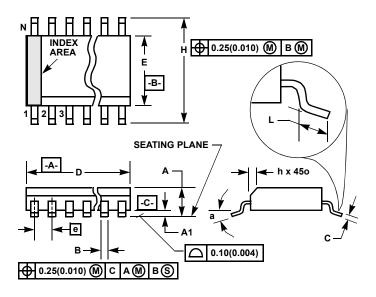

| PART NUMBER                                                                                     | TEMP.<br>RANGE (°C) | PACKAGE                 | PKG. DWG.<br># |

|-------------------------------------------------------------------------------------------------|---------------------|-------------------------|----------------|

| HI5731BIPZ (No<br>longer available,<br>recommended<br>replacement:<br>HI5731BIBZ)<br>(See Note) | -40 to 85           | 28 Ld PDIP<br>(Pb-free) | E28.6          |

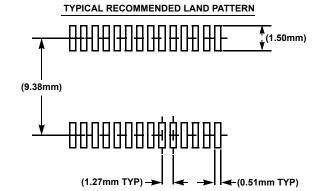

| HI5731BIBZ<br>(See Note)                                                                        | -40 to 85           | 28 Ld SOIC<br>(Pb-free) | M28.3          |

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which is compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020C.

#### **Features**

| 1 b-liee Available as all Option |  |

|----------------------------------|--|

| Throughput Bate                  |  |

Phyfree Available as an Ontion

| • Throughput Rate100MSPS          |

|-----------------------------------|

| • Low Power                       |

| Integral Linearity Error 0.75 LSB |

| • Low Glitch Energy               |

|                                   |

• TTL/CMOS Compatible Inputs

• Improved Hold Time................. 0.25ns

· Excellent Spurious Free Dynamic Range

## **Applications**

- Cellular Base Stations

- · GSM Base Stations

- · Wireless Communications

- · Direct Digital Frequency Synthesis

- Signal Reconstruction

- Test Equipment

- · High Resolution Imaging Systems

- · Arbitrary Waveform Generators

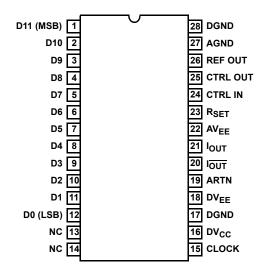

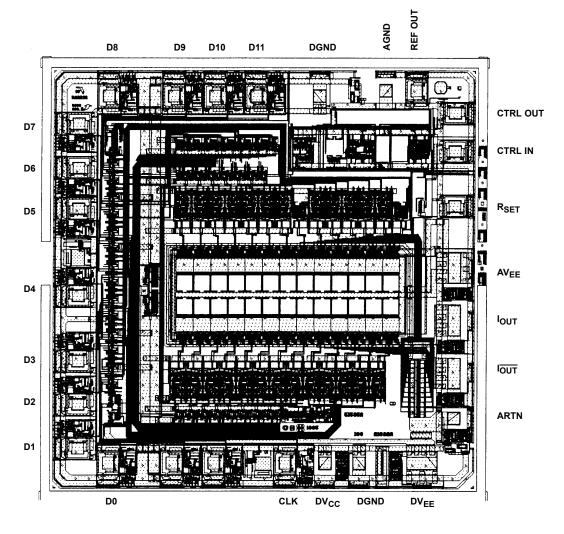

#### Pinout

HI5731 (PDIP, SOIC) TOP VIEW

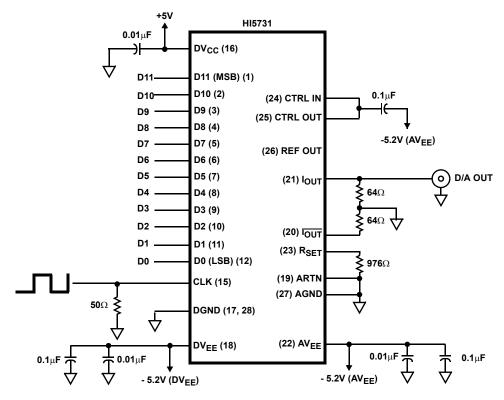

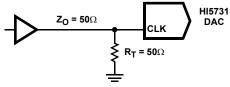

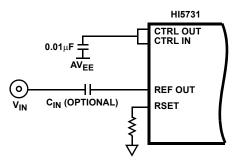

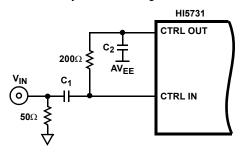

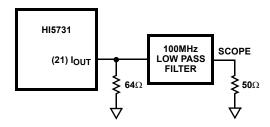

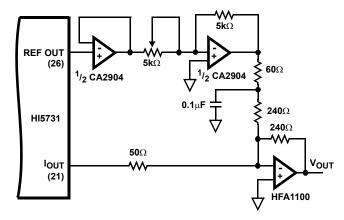

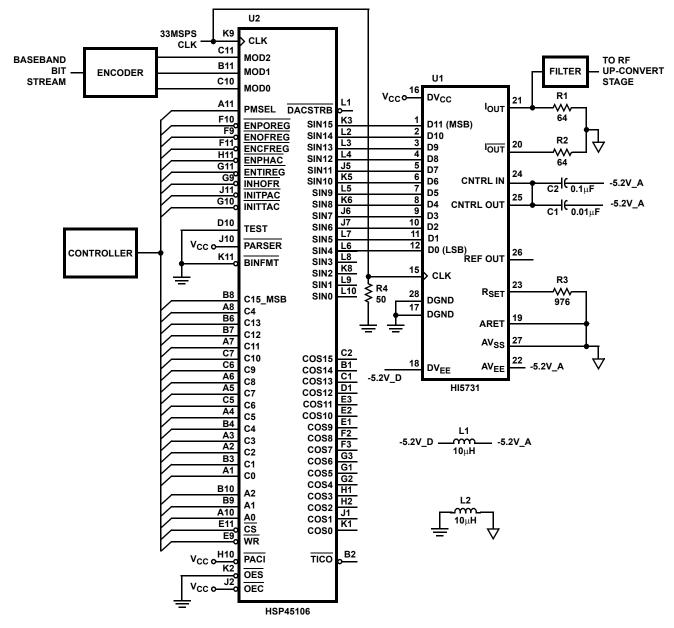

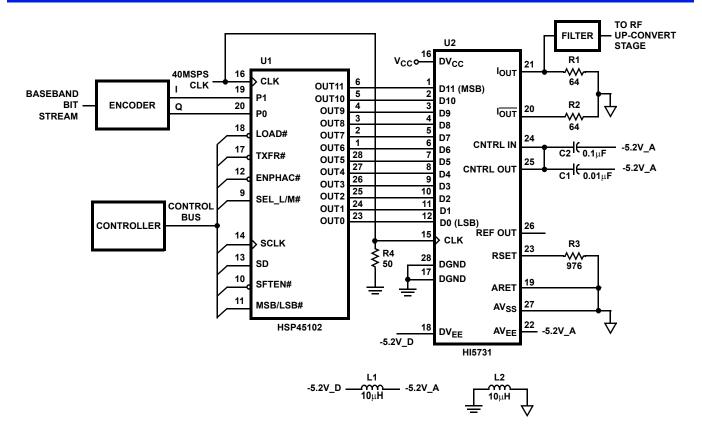

# **Typical Application Circuit**

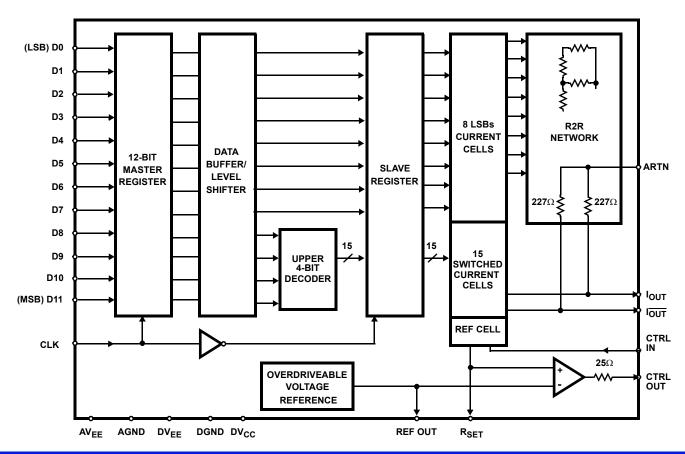

# Functional Block Diagram

## **Absolute Maximum Ratings**

| Digital Supply Voltage V <sub>CC</sub> to DGND +5.5V                   |

|------------------------------------------------------------------------|

| Negative Digital Supply Voltage DVEE to DGND5.5V                       |

| Negative Analog Supply Voltage AVEE to AGND, ARTN5.5V                  |

| Digital Input Voltages (D11-D0, CLK) to DGND DV <sub>CC</sub> to -0.5V |

| Internal Reference Output Current                                      |

| Voltage from CTRL IN to AVEE 2.5V to 0V                                |

| Control Amplifier Output Current                                       |

| Reference Input Voltage Range3.7V to AVEE                              |

| Analog Output Current (IOUT)                                           |

### **Thermal Information**

| Thermal Resistance (Typical, Note 1)                             | $\theta_{JA}$ (°C/W)                 |

|------------------------------------------------------------------|--------------------------------------|

| PDIP Package                                                     | 50                                   |

| SOIC Package                                                     |                                      |

| Maximum Junction Temperature                                     |                                      |

| HI5731Blx                                                        | 150°C                                |

| Maximum Storage Temperature Range65                              | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10s) (SOIC - Lead Tips Only) | 300°C                                |

### **Operating Conditions**

Temperature Range.....-40°C to 85°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### NOTE:

1. θ<sub>JA</sub> is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

##

|                                                                                 |                                                                   |       | HI5731BI<br>T <sub>A</sub> = -40°C TO 85°C |      |                             |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------|-------|--------------------------------------------|------|-----------------------------|

| PARAMETER                                                                       | TEST CONDITIONS                                                   | MIN   | TYP                                        | MAX  | UNITS                       |

| SYSTEM PERFORMANCE                                                              |                                                                   |       |                                            | 1    | '                           |

| Resolution                                                                      |                                                                   | 12    | -                                          | -    | Bits                        |

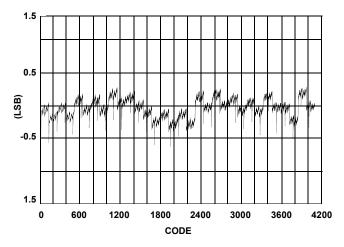

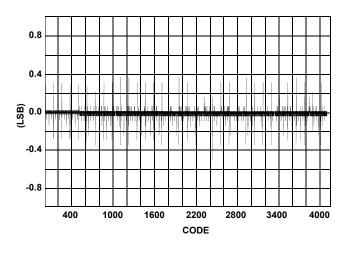

| Integral Linearity Error, INL                                                   | (Note 4) ("Best Fit" Straight Line)                               | -     | 0.75                                       | 1.5  | LSB                         |

| Differential Linearity Error, DNL                                               | (Note 4)                                                          | -     | 0.5                                        | 1.0  | LSB                         |

| Offset Error, I <sub>OS</sub>                                                   | (Note 4)                                                          | -     | 20                                         | 75   | μА                          |

| Full Scale Gain Error, FSE                                                      | (Notes 2, 4)                                                      | -     | 1                                          | 10   | %                           |

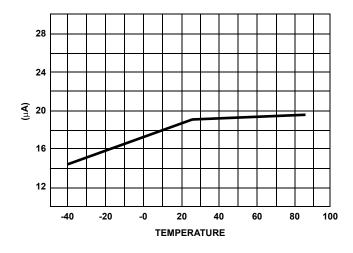

| Full Scale Gain Drift                                                           | With Internal Reference                                           | -     | ±150                                       | -    | ppm<br>FSR/ <sup>o</sup> C  |

| Offset Drift Coefficient                                                        | (Note 3)                                                          | -     | -                                          | 0.05 | μ <b>Α</b> / <sup>o</sup> C |

| Full Scale Output Current, IFS                                                  |                                                                   | -     | 20.48                                      | -    | mA                          |

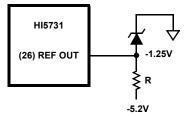

| Output Voltage Compliance Range                                                 | (Note 3)                                                          | -1.25 | -                                          | 0    | V                           |

| DYNAMIC CHARACTERISTICS                                                         |                                                                   | 1     |                                            |      | 1                           |

| Throughput Rate                                                                 | (Note 3)                                                          | 100   | -                                          | -    | MSPS                        |

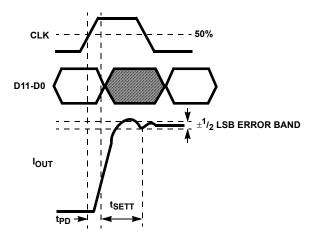

| Output Voltage Full Scale Step<br>Settling Time, t <sub>SETT</sub> , Full Scale | To $\pm 0.5$ LSB Error Band R <sub>L</sub> = $50\Omega$ (Note 3)  | -     | 20                                         | -    | ns                          |

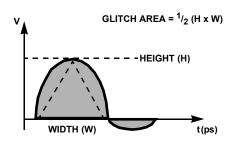

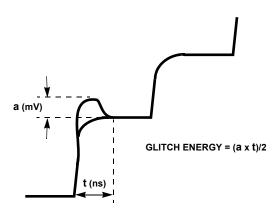

| Singlet Glitch Area, GE (Peak)                                                  | R <sub>L</sub> = 50Ω (Note 3)                                     | -     | 5                                          | -    | pV-s                        |

| Doublet Glitch Area, (Net)                                                      |                                                                   | -     | 3                                          | -    | pV-s                        |

| Output Slew Rate                                                                | $R_L = 50\Omega$ , DAC Operating in Latched Mode (Note 3)         | -     | 1,000                                      | -    | V/μs                        |

| Output Rise Time                                                                | $R_L = 50\Omega$ , DAC Operating in Latched Mode (Note 3)         | -     | 675                                        | -    | ps                          |

| Output Fall Time                                                                | $R_L = 50\Omega$ , DAC Operating in Latched Mode (Note 3)         | -     | 470                                        | -    | ps                          |

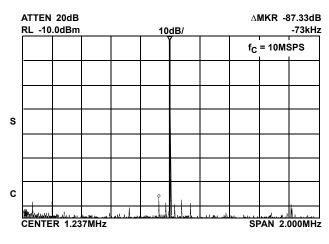

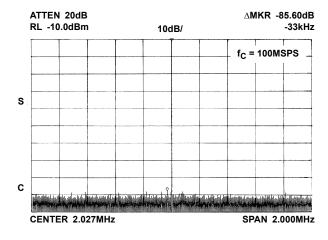

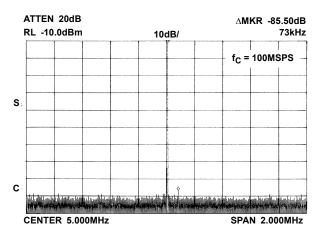

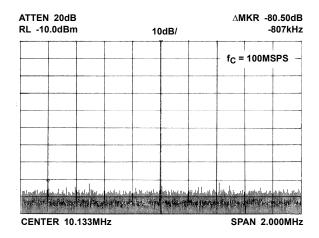

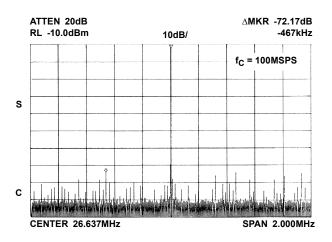

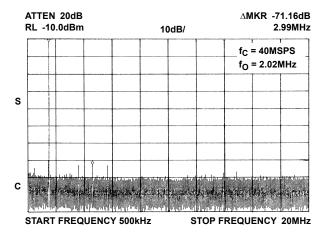

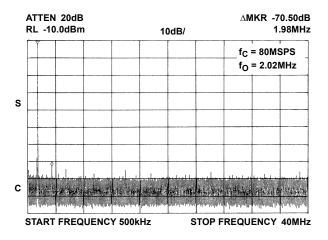

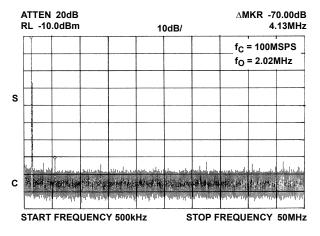

| Spurious Free Dynamic Range within a Window                                     | f <sub>CLK</sub> = 10MSPS, f <sub>OUT</sub> = 1.23MHz, 2MHz Span  | -     | 85                                         | -    | dBc                         |

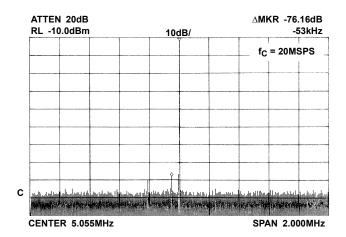

| (Note 3)                                                                        | f <sub>CLK</sub> = 20MSPS, f <sub>OUT</sub> = 5.055MHz, 2MHz Span | -     | 77                                         | -    | dBc                         |

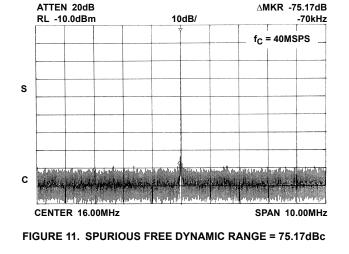

|                                                                                 | f <sub>CLK</sub> = 40MSPS, f <sub>OUT</sub> = 16MHz, 10MHz Span   | -     | 75                                         | -    | dBc                         |

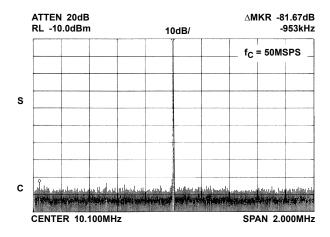

|                                                                                 | f <sub>CLK</sub> = 50MSPS, f <sub>OUT</sub> = 10.1MHz, 2MHz Span  | -     | 80                                         | -    | dBc                         |

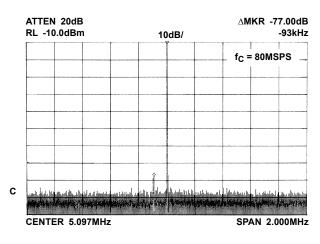

|                                                                                 | f <sub>CLK</sub> = 80MSPS, f <sub>OUT</sub> = 5.1MHz, 2MHz Span   | -     | 78                                         | -    | dBc                         |

|                                                                                 | f <sub>CLK</sub> = 100MSPS, f <sub>OUT</sub> = 10.1MHz, 2MHz Span | -     | 79                                         | -    | dBc                         |

##

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TYP   | MAX   |                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|--------------------|

| $ \begin{array}{c} \text{(Note 3)} \\ \hline \\ \text{f}_{\text{CLK}} = 80\text{MSPS, f}_{\text{OUT}} = 2.02\text{MHz, 40MHz Span} \\ \hline \\ \text{f}_{\text{CLK}} = 100\text{MSPS, f}_{\text{OUT}} = 2.02\text{MHz, 50MHz Span} \\ \hline \\ \text{REFERENCE/CONTROL AMPLIFIER} \\ \hline \\ \text{Internal Reference Voltage, V}_{\text{REF}} \\ \hline \\ \text{(Note 4)} \\ \hline \\ \text{Internal Reference Voltage Drift} \\ \hline \\ \text{(Note 3)} \\ \hline \\ \text{Internal Reference Output Current Sink/Source Capability} \\ \hline \\ \text{Internal Reference Load Regulation} \\ \hline \\ \text{Internal Reference Load Regulation} \\ \hline \\ \text{Internal Impedance at REF OUT pin} \\ \hline \\ \text{(Note 3)} \\ \hline \\ \text{Amplifier Large Signal Bandwidth (0.6V_{P-P})} \\ \hline \\ \text{Sine Wave Input, to Slew Rate Limited (Note 3)} \\ \hline \\ \text{Amplifier Small Signal Bandwidth (0.1V_{P-P})} \\ \hline \\ \text{Sine Wave Input, to -3dB Loss (Note 3)} \\ \hline \\ \text{Reference Input Impedance} \\ \hline \\ \text{(Note 3)} \\ \hline \\ \hline \\ \text{Reference Input Multiplying Bandwidth (CTL IN)} \\ \hline \\ \hline \\ \text{R}_{L} = 50\Omega_{L}, 100\text{mV Sine Wave, to -3dB Loss at I}_{\text{OUT}} \\ \hline \\ \text{(Note 3)} \\ \hline \\ \hline \\ \text{DIGITAL INPUTS (D9-D0, CLK, INVERT)} \\ \hline \\ \hline \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | IVIAA | UNITS              |

| $\frac{\text{f}_{\text{CLK}} = 80\text{MSPS},  f_{\text{OUT}} = 2.02\text{MHz},  40\text{MHz Span}}{f_{\text{CLK}} = 100\text{MSPS},  f_{\text{OUT}} = 2.02\text{MHz},  50\text{MHz Span}} - \frac{1}{100\text{MSPS}}$ $\frac{\text{REFERENCE/CONTROL AMPLIFIER}}{\text{Internal Reference Voltage, V}_{\text{REF}}} \qquad (\text{Note 4}) \qquad -1.27$ $\frac{1}{\text{Internal Reference Voltage Drift}} \qquad (\text{Note 3}) \qquad -\frac{1}{100\text{MSPS}} = -\frac$ | 70    | -     | dBc                |

| REFERENCE/CONTROL AMPLIFIER         Internal Reference Voltage, VREF       (Note 4)       -1.27         Internal Reference Voltage Drift       (Note 3)       -         Internal Reference Output Current Sink/Source Capability       (Note 3)       -125         Internal Reference Load Regulation       IREF = 0 to IREF = -125μA       -         Input Impedance at REF OUT pin       (Note 3)       -         Amplifier Large Signal Bandwidth (0.6VP-P)       Sine Wave Input, to Slew Rate Limited (Note 3)       -         Amplifier Small Signal Bandwidth (0.1VP-P)       Sine Wave Input, to -3dB Loss (Note 3)       -         Reference Input Impedance       (Note 3)       -         Reference Input Multiplying Bandwidth (CTL IN)       R <sub>L</sub> = 50Ω, 100mV Sine Wave, to -3dB Loss at IOUT (Note 3)       -         DIGITAL INPUTS (D9-D0, CLK, INVERT)       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70    | -     | dBc                |

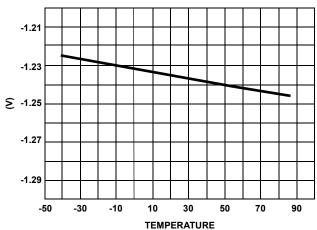

| Internal Reference Voltage, V <sub>REF</sub> (Note 4) -1.27  Internal Reference Voltage Drift (Note 3) -  Internal Reference Output Current Sink/Source Capability (Note 3) -125  Internal Reference Load Regulation I <sub>REF</sub> = 0 to I <sub>REF</sub> = -125μA -  Input Impedance at REF OUT pin (Note 3) -  Amplifier Large Signal Bandwidth (0.6V <sub>P-P</sub> ) Sine Wave Input, to Slew Rate Limited (Note 3) -  Amplifier Small Signal Bandwidth (0.1V <sub>P-P</sub> ) Sine Wave Input, to -3dB Loss (Note 3) -  Reference Input Impedance (Note 3) -  Reference Input Multiplying Bandwidth (CTL IN) R <sub>L</sub> = 50Ω, 100mV Sine Wave, to -3dB Loss at I <sub>OUT</sub> (Note 3)  DIGITAL INPUTS (D9-D0, CLK, INVERT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69    | -     | dBc                |

| Internal Reference Voltage Drift (Note 3) -  Internal Reference Output Current Sink/Source Capability (Note 3) -125  Internal Reference Load Regulation IREF = 0 to IREF = -125μA -  Input Impedance at REF OUT pin (Note 3) -  Amplifier Large Signal Bandwidth (0.6V <sub>P-P</sub> ) Sine Wave Input, to Slew Rate Limited (Note 3) -  Amplifier Small Signal Bandwidth (0.1V <sub>P-P</sub> ) Sine Wave Input, to -3dB Loss (Note 3) -  Reference Input Impedance (Note 3) -  Reference Input Multiplying Bandwidth (CTL IN) R <sub>L</sub> = 50Ω, 100mV Sine Wave, to -3dB Loss at I <sub>OUT</sub> (Note 3)  DIGITAL INPUTS (D9-D0, CLK, INVERT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |       | 1                  |

| Internal Reference Output Current Sink/Source Capability       (Note 3)       -125         Internal Reference Load Regulation $I_{REF} = 0$ to $I_{REF} = -125\mu A$ -         Input Impedance at REF OUT pin       (Note 3)       -         Amplifier Large Signal Bandwidth $(0.6V_{P-P})$ Sine Wave Input, to Slew Rate Limited (Note 3)       -         Amplifier Small Signal Bandwidth $(0.1V_{P-P})$ Sine Wave Input, to -3dB Loss (Note 3)       -         Reference Input Impedance       (Note 3)       -         Reference Input Multiplying Bandwidth (CTL IN) $R_L = 50\Omega$ , 100mV Sine Wave, to -3dB Loss at $I_{OUT}$ (Note 3)       -         DIGITAL INPUTS (D9-D0, CLK, INVERT)       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -1.23 | -1.17 | ٧                  |

| Capability  Internal Reference Load Regulation $I_{REF} = 0 \text{ to } I_{REF} = -125 \mu A$ Input Impedance at REF OUT pin  (Note 3)  Amplifier Large Signal Bandwidth $(0.6V_{P-P})$ Sine Wave Input, to Slew Rate Limited (Note 3)  Amplifier Small Signal Bandwidth $(0.1V_{P-P})$ Sine Wave Input, to -3dB Loss (Note 3)  Reference Input Impedance  (Note 3)  Reference Input Multiplying Bandwidth (CTL IN) $R_L = 50\Omega$ , 100mV Sine Wave, to -3dB Loss at $I_{OUT}$ (Note 3)  DIGITAL INPUTS (D9-D0, CLK, INVERT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 175   | -     | μV/ <sup>o</sup> C |

| Input Impedance at REF OUT pin (Note 3) -  Amplifier Large Signal Bandwidth (0.6V <sub>P-P</sub> ) Sine Wave Input, to Slew Rate Limited (Note 3) -  Amplifier Small Signal Bandwidth (0.1V <sub>P-P</sub> ) Sine Wave Input, to -3dB Loss (Note 3) -  Reference Input Impedance (Note 3) -  Reference Input Multiplying Bandwidth (CTL IN) R <sub>L</sub> = 50Ω, 100mV Sine Wave, to -3dB Loss at I <sub>OUT</sub> (Note 3)  DIGITAL INPUTS (D9-D0, CLK, INVERT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -     | +50   | μΑ                 |

| Amplifier Large Signal Bandwidth $(0.6V_{P-P})$ Sine Wave Input, to Slew Rate Limited (Note 3) - Amplifier Small Signal Bandwidth $(0.1V_{P-P})$ Sine Wave Input, to -3dB Loss (Note 3) - Reference Input Impedance (Note 3) - Reference Input Multiplying Bandwidth (CTL IN) $R_L = 50\Omega$ , 100mV Sine Wave, to -3dB Loss at $I_{OUT}$ (Note 3) - DIGITAL INPUTS (D9-D0, CLK, INVERT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50    | -     | μV                 |

| Amplifier Small Signal Bandwidth $(0.1V_{P-P})$ Sine Wave Input, to -3dB Loss (Note 3) - Reference Input Impedance (Note 3) - Reference Input Multiplying Bandwidth (CTL IN) $R_L = 50\Omega$ , 100mV Sine Wave, to -3dB Loss at $I_{OUT}$ - (Note 3) - DIGITAL INPUTS (D9-D0, CLK, INVERT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.4   | -     | kΩ                 |

| Reference Input Impedance (Note 3) -  Reference Input Multiplying Bandwidth (CTL IN) R <sub>L</sub> = 50Ω, 100mV Sine Wave, to -3dB Loss at I <sub>OUT</sub> (Note 3)  DIGITAL INPUTS (D9-D0, CLK, INVERT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3     | -     | MHz                |

| Reference Input Multiplying Bandwidth (CTL IN) $R_L = 50\Omega$ , 100mV Sine Wave, to -3dB Loss at $I_{OUT}$ - (Note 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10    | -     | MHz                |

| (Note 3)  DIGITAL INPUTS (D9-D0, CLK, INVERT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12    | -     | kΩ                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 200   | -     | MHz                |

| Input Logic High Voltage VIII. (Note 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |       |                    |

| input Logic Fright voltage, vIH (Note 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -     | -     | ٧                  |

| Input Logic Low Voltage, V <sub>IL</sub> (Note 4) -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -     | 0.8   | V                  |

| Input Logic Current, I <sub>IH</sub> (Note 4) -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -     | 400   | μΑ                 |

| Input Logic Current, I <sub>IL</sub> (Note 4) -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -     | 700   | μА                 |

| Digital Input Capacitance, C <sub>IN</sub> (Note 3) -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.0   | -     | pF                 |

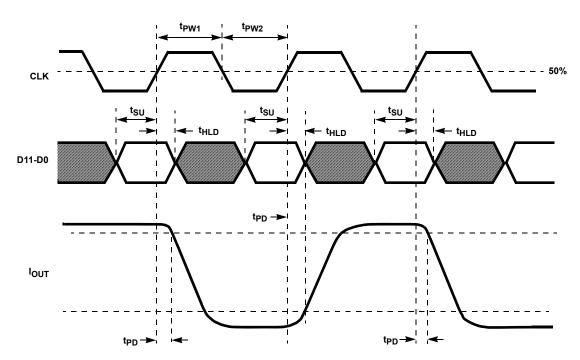

| TIMING CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |       |                    |

| Data Setup Time, t <sub>SU</sub> See Figure 1 (Note 3) 3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.0   | -     | ns                 |