# Using ECC Memory Configuration and Error Injection and Detection with the Tsi107™

80C2000\_AN005\_03

November 3, 2009

6024 Silver Creek Valley Road San Jose, California 95138

Telephone: (408) 284-8200 • FAX: (408) 284-3572

Printed in U.S.A.

©2009 Integrated Device Technology, Inc.

**GENERAL DISCLAIMER**

Integrated Device Technology, Inc. ("IDT") reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance. IDT does not assume responsibility for use of any circuitry described herein other than the circuitry embodied in an IDT product. Disclosure of the information herein does not convey a license or any other right, by implication or otherwise, in any patent, trademark, or other intellectual property right of IDT. IDT products may contain errata which can affect product performance to a minor or immaterial degree. Current characterized errata will be made available upon request. Items identified herein as "reserved" or "undefined" are reserved for future definition. IDT does not assume responsibility for conflicts or incompatibilities arising from the future definition of such items. IDT products have not been designed, tested, or manufactured for use in, and thus are not warranted for, applications where the failure, malfunction, or any inaccuracy in the application carries a risk of death, serious bodily injury, or damage to tangible property. Code examples provided herein by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of such code examples shall be at the user's sole risk.

Copyright © 2009 Integrated Device Technology, Inc.

All Rights Reserved.

The IDT logo is registered to Integrated Device Technology, Inc. IDT is a trademark of Integrated Device Technology, Inc.

## About this Document

One of the most important aspects of system memory is ensuring the integrity of the data contained within. Configuring the memory array to contain check bits is the most common method. Two common implementations that take advantage of the extra bits are parity and Error Detection and Correction (also called ECC for Error Correcting Code). The Tsi107 PowerPC™ provides hardware support for both implementations.

For basic integrity checking and notification of corrupt data, the parity checking feature of the bridge is sufficient. However, in applications where the presence of a corrupt bit in memory can cause a serious situation, and the delay in recovering from this situation is unacceptable, the use of ECC is desired. The ECC controller in the Tsi107 has the capability of detecting and repairing one corrupt bit in a word at the memory interface speed, and detecting and generating a notification of the presence of multiple corrupt bits.

This application note is intended to provide the user the necessary understanding and processes required to initialize the Tsi107 memory controller, configure the error detection registers for error notification and intentionally generate errors in the memory array in order to validate the detection and correction circuitry.

Most of the information contained herein, has been extracted from the Tsi107 User Manual. The content flow has been changed in order to aid the user in gaining a better understanding of the registers and operation of the SDRAM memory interface.

This document discusses the following topics:

- “Tsi107 Memory Controller Architecture”

- “SDRAM In-Line ECC”

- “Debug Registers”

- “Watchpoint Control Register (WP\_CONTROL)”

- “How the error injection logic is put to use”

- “Sample Code”

## Revision History

### ***80C2000\_AN005\_03, Formal, November 2009***

This version of the document was rebranded as IDT. It does not include any technical changes.

### ***80C2000\_AN005\_02, Formal, March 2007***

This version fixed a typographical error.

**80C2000\_AN005\_01, Formal, March 2004**

This is the first release of the application note.

---

## 1. Tsi107 Memory Controller Architecture

The Tsi107 integrates a high-performance memory controller that controls processor and PCI interactions to local memory. The Tsi107 supports various types of DRAM and ROM/Flash configurations as local memory.

- SDRAM

- SDRAMs must comply with the JEDEC specification for SDRAM

- High-bandwidth bus (32- or 64-bit data bus) to SDRAM

- One-Mbyte to 1-GB SDRAM memory—1 to 8 chip selects for SDRAM bank sizes ranging from 1 MB to 512 MB per bank

- Supports page mode SDRAMs—four open pages simultaneously

- Programmable timing for SDRAMs

- DRAM—fast page mode (FPM) and extended data out (EDO)

- High-bandwidth bus (32- or 64-bit data bus) to DRAM

- One-Mbyte to 1-GB DRAM memory space

- One to eight chip selects of 4-, 16-, 64- or 128-Mbit memory devices

- Programmable timing for FPM and EDO

- ROM/Flash

- 144 Mbytes of ROM/Flash space can be divided between the PCI bus and the memory bus (8 Mbytes each)

- Supports 8-bit asynchronous ROM or 64-bit burst-mode ROM

- Configurable data path—8-, 32-, or 64-bit

- Supports bus-width writes to Flash

- Port X—The ROM/Flash controller can interface any device that can be controlled with an address and data field (communication devices, DSPs, general purpose I/O devices, or registers). Some devices may require a small amount of external logic to properly generate address strobes and chip selects.

- 8-bit Port X

- 32-bit Port X

- 64-bit Port X—the floating-point (FPU) unit in the CPU must be present for 64-bit writes

- Data path buffering—72 bits (64-bit data and 8-bit parity)

- Reduces loading on the internal processor core bus

- Reduces loading of the drivers of the memory system

- Reduces signal trace delay known as time-of-flight (TOF)

- Parity—Supports normal parity and read-modify-write (RMW)

- Error checking and correction (ECC)—64-bit only

- DRAM ECC—Located in the central control unit (CCU)

- SDRAM ECC—Located in-line with the data path buffers

The Tsi107 is designed to control a 32- or 64-bit data path to main memory (SDRAM or DRAM). The Tsi107 can also be configured to check parity or ECC on memory reads. Parity checking and generation can be enabled with 4 parity bits for a 32-bit data path or 8 parity bits for 64-bit data path. Concurrent ECC is only generated for a 64-bit data path with 8 syndrome bits. The Tsi107 supports SDRAM or DRAM bank sizes from 1 to 512 Mbytes and provides bank start address and end address configuration registers. However the Tsi107 does not support mixed SDRAM or DRAM configurations. The Tsi107 can be configured so that the appropriate row and column address multiplexing occurs for each physical bank. Addresses (DRAM or SDRAM) and bank selects (SDRAM only) are provided through a 15-bit interface for SDRAM and 13-bit interface for DRAM.

ROM/Flash systems are supported by up to 24 address bits, 4 bank selects, 1 write enable and 1 output enable.

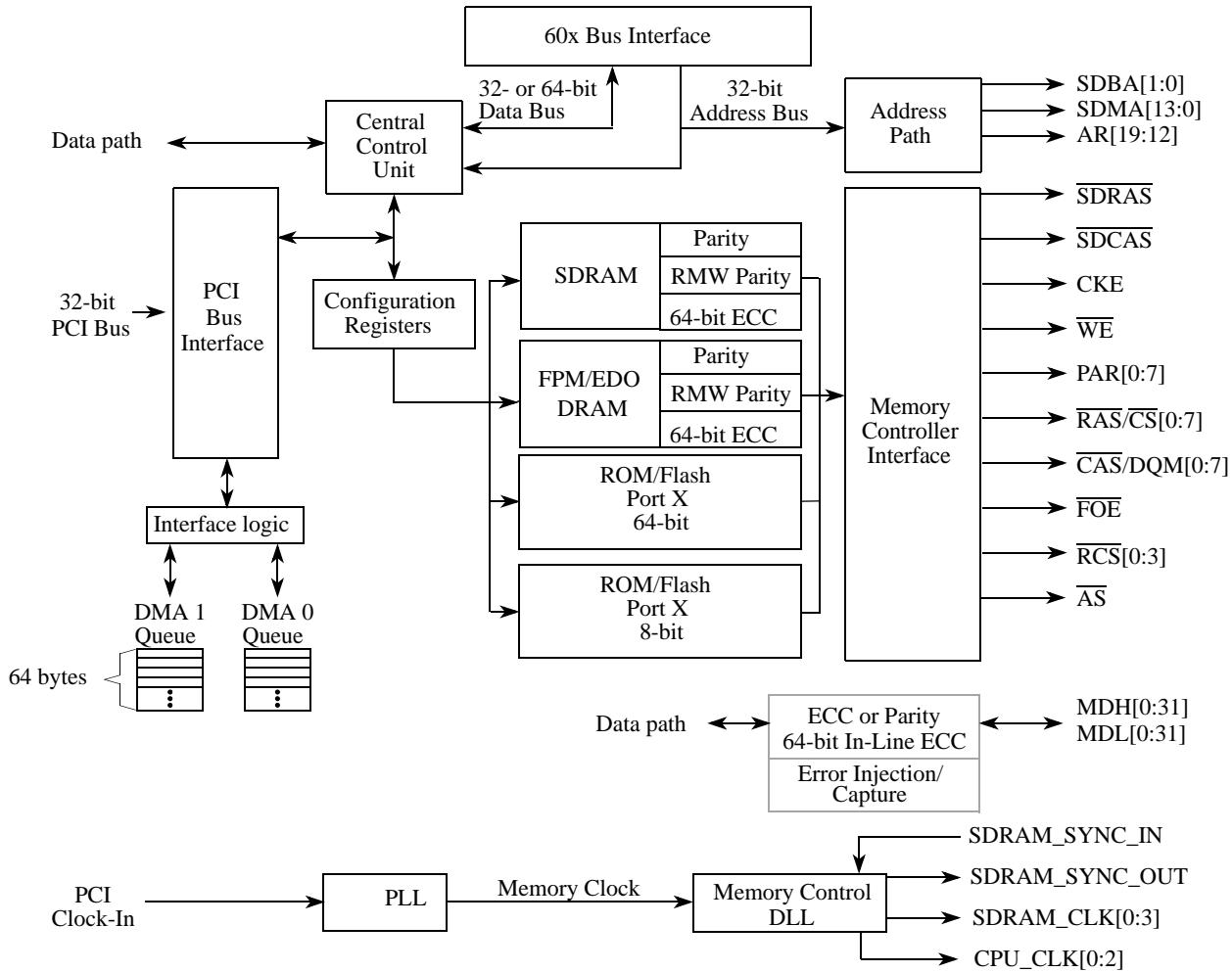

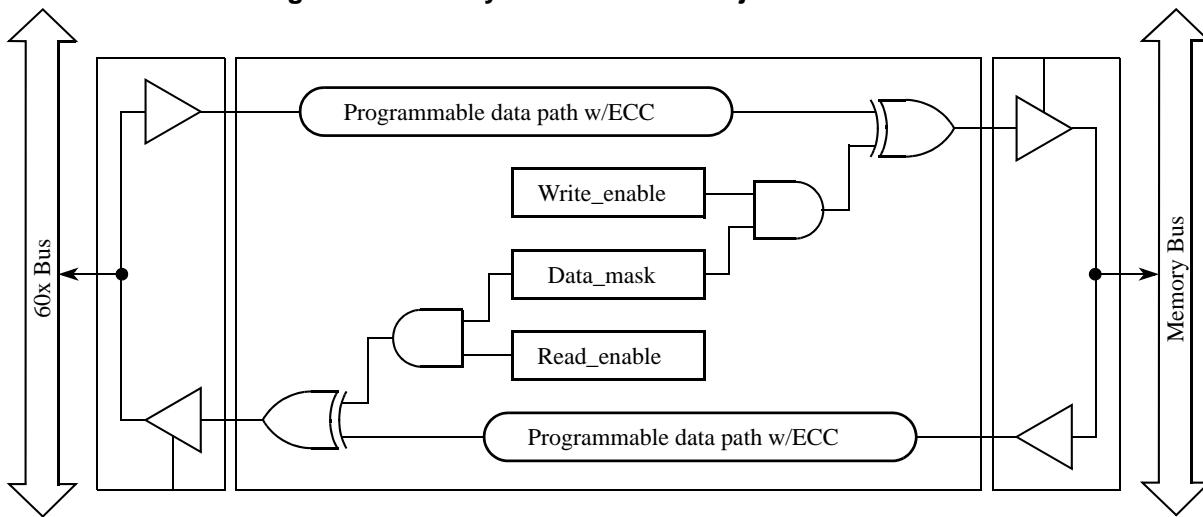

**Figure 1** is a block diagram of the memory interface.

SDRAM is the most commonly available type of memory used with the Tsi107. For this reason, this application note will focus on the use of SDRAM in an ECC application.

**Figure 1: Block Diagram for Memory Interface**

## 1.1 SDRAM Interface Operation

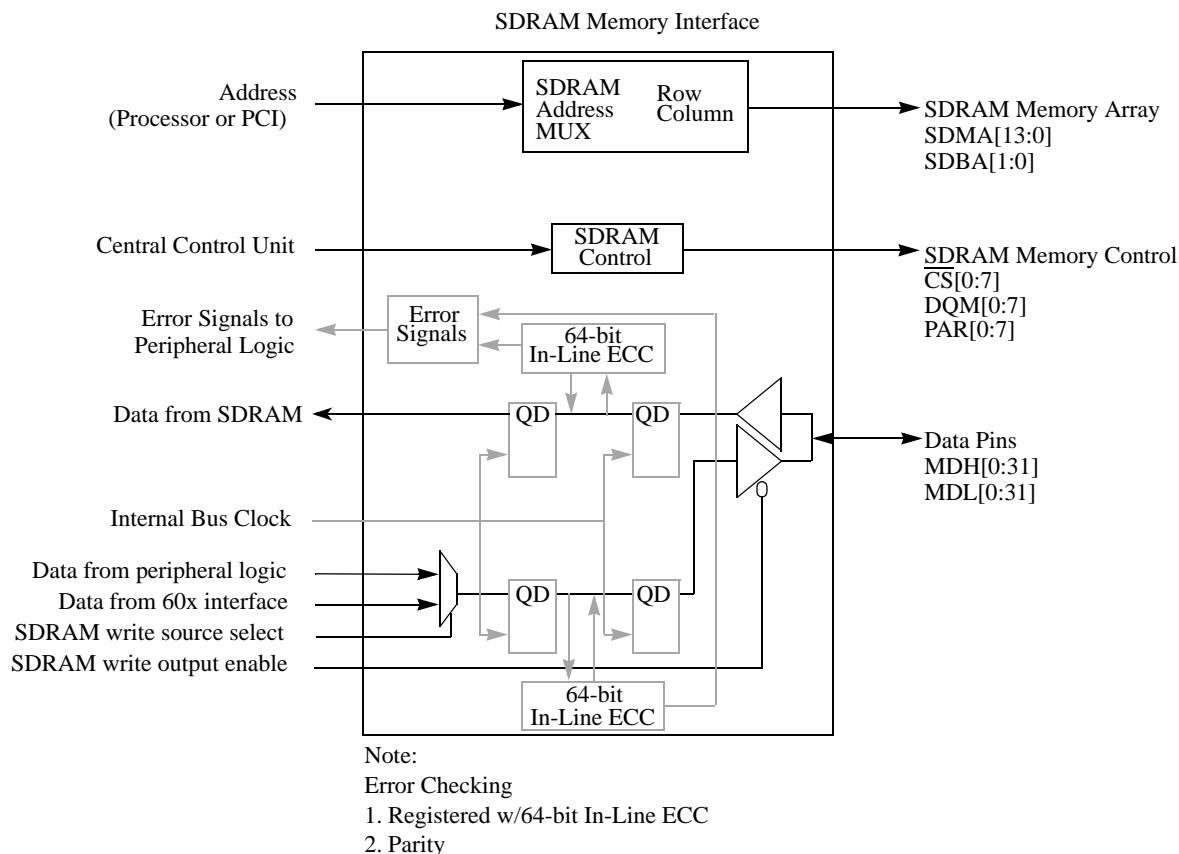

Figure 2 shows an internal block diagram of the SDRAM interface of the Tsi107.

The Tsi107 provides control functions and signals for JEDEC-compliant SDRAM. The Tsi107 supplies the **SDRAM\_CLK[0:3]** to be distributed to the SDRAM. These clocks are the same frequency and are in phase with the memory bus clock. The other control signals provided for the interface are a write enable signal (WE), a row address strobe signal (SDRAS), a column address strobe signal (SDCAS), a memory clock enable signal (CKE),

The SDRAM memory bus can be configured to be 64 bits (72 bits with parity) requiring a four-beat SDRAM data burst, or configured to be 32 bits (36 bits with parity) requiring an eight-beat SDRAM data burst.

The data width of the device determines its density and the physical bank size. Eight chip select signals (CS[0:7]) support up to eight banks of memory. The row, column and bank multiplexing is flexible enough to allow the banks to be built of x1, x4, x8, x16, or x32 SDRAMs as they become available. Collectively, these interface signals allow a total of 1 GB of addressable memory.

The thirteen row/column multiplexed address signals (SDMA[12:0]) in conjunction with two bank select signals (SDBA[1:0]) provide SDRAM addressing for up to 64 M. SDMA[13] is only used on the ROM/FLASH port in addressing as AR[23].

**Figure 2: SDRAM Interface**

Programmable CAS latency is supported for data read operations and is set through the SDMODE parameter (MCCR4 bits 14-12). For write operations, the first beat of write data is supplied concurrent with the write command. The memory design must be byte-selectable for writes using the Tsi107's DQM outputs.

The Tsi107 allows for four simultaneous open pages for page mode operation. The number of clocks for which the pages are maintained open is programmable by the BSTOPRE and PGMAX parameters. Page register allocation uses a “least recently used” (LRU) algorithm.

**Table 1** below shows how the SDRAS, SDCAS and bank select bits are multiplexed into the physical addresses of the SDRAM interface to convert from the linear addressing mode of the 60x architecture to the SDRAM architecture.

**Table 1: SDRAM Address Multiplexing SDMA[12:0] and SDBA[1:0] —64-Bit Mode**

| Row x Col x Bank |       | msb |   |   |   |   |   |             |             |             | Physical Address |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | lsb |    |

|------------------|-------|-----|---|---|---|---|---|-------------|-------------|-------------|------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|

|                  |       | 0-2 | 3 | 4 | 5 | 6 | 7 | 8           | 9           | 10          | 11               | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29  | 30 |

| 11x10x2          | SDRAS |     |   |   |   |   |   |             |             | B<br>A<br>0 | 1                | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |    |    |    |    |    |    |    |     |    |

|                  | SDCAS |     |   |   |   |   |   | 9           | 8           | B<br>A<br>0 |                  |    |    |    |    |    |    |    |    |    |    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0   |    |

| 11x9x2           | SDRAS |     |   |   |   |   |   |             |             | B<br>A<br>0 | 1                | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |    |    |    |    |    |    |    |     |    |

|                  | SDCAS |     |   |   |   |   |   |             | 8           | B<br>A<br>0 |                  |    |    |    |    |    |    |    |    |    |    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0   |    |

| 11x8x2           | SDRAS |     |   |   |   |   |   |             |             | B<br>A<br>0 | 1                | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |    |    |    |    |    |    |    |     |    |

|                  | SDCAS |     |   |   |   |   |   |             | B<br>A<br>0 |             |                  |    |    |    |    |    |    |    |    |    |    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0   |    |

| 13x10x2          | SDRAS |     |   |   |   |   | 1 | 12          | B<br>A<br>0 | 1           | 9                | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |    |    |    |    |    |    |    |    |     |    |

|                  | SDCAS |     |   |   |   | 9 | 8 |             | B<br>A<br>0 |             |                  |    |    |    |    |    |    |    |    |    |    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0   |    |

| 13x9x2           | SDRAS |     |   |   |   |   | 1 | 12          | B<br>A<br>0 | 1           | 9                | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |    |    |    |    |    |    |    |    |     |    |

|                  | SDCAS |     |   |   |   |   | 8 |             | B<br>A<br>0 |             |                  |    |    |    |    |    |    |    |    |    |    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0   |    |

| 13x8x2           | SDRAS |     |   |   |   |   | 1 | 12          | B<br>A<br>0 | 1           | 9                | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |    |    |    |    |    |    |    |    |     |    |

|                  | SDCAS |     |   |   |   |   |   | B<br>A<br>0 |             |             |                  |    |    |    |    |    |    |    |    |    |    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0   |    |

**Table 1: SDRAM Address Multiplexing SDMA[12:0] and SDBA[1:0] —64-Bit Mode (Continued)**

| Row x Col x Bank       |       | Physical Address |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | lsb |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|------------------------|-------|------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|                        |       | 0-2              | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 1 | 0 | 1 | 1 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 1 | 8 | 9 | 2 | 0 | 2 | 1   | 2 | 3 | 2 | 4 | 2 | 5 | 2 | 6 | 2 | 7 | 2 | 8 | 2 | 9 | 3 |

| 12x11x4 <sup>a</sup>   | SDRAS |                  |   |   |   |   |   |   | 1 | B | B | 1 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                        | SDCAS |                  |   |   | 1 | 9 | 8 |   | B | B | B | 1 | 0 |   |   |   |   |   |   |   |   |   |   |   |   |   | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |   |   |   |   |

| 12x10x4                | SDRAS |                  |   |   |   |   |   | 1 | B | B | 1 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                        | SDCAS |                  |   |   |   | 9 | 8 |   | B | B | B | 1 | 0 |   |   |   |   |   |   |   |   |   |   |   |   |   | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |   |   |   |   |

| 12x9x4                 | SDRAS |                  |   |   |   |   |   | 1 | B | B | 1 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                        | SDCAS |                  |   |   |   |   | 8 |   | B | B | B | 1 | 0 |   |   |   |   |   |   |   |   |   |   |   |   |   | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |   |   |   |   |

| 11x8x4<br>or<br>12x8x4 | SDRAS |                  |   |   |   |   |   | 1 | B | B | 1 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                        | SDCAS |                  |   |   |   |   |   |   | B | B | B | 1 | 0 |   |   |   |   |   |   |   |   |   |   |   |   |   | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |   |   |   |   |

| 13x11x4 <sup>a</sup>   | SDRAS |                  |   |   |   |   | 1 | 1 | B | B | 1 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                        | SDCAS |                  |   |   | 1 | 9 | 8 |   | B | B | B | 1 | 0 |   |   |   |   |   |   |   |   |   |   |   |   | 7 | 6   | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |   |   |   |   |   |

| 13x10x4                | SDRAS |                  |   |   |   |   | 1 | 1 | B | B | 1 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                        | SDCAS |                  |   |   |   | 9 | 8 |   | B | B | B | 1 | 0 |   |   |   |   |   |   |   |   |   |   |   |   | 7 | 6   | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |   |   |   |   |   |

| 13x9x4                 | SDRAS |                  |   |   |   |   | 1 | 1 | B | B | 1 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                        | SDCAS |                  |   |   |   |   | 8 |   | B | B | B | 1 | 0 |   |   |   |   |   |   |   |   |   |   |   |   | 7 | 6   | 5 | 4 | 3 | 2 | 1 | 0 |   |   |   |   |   |   |   |   |   |

**Table 1: SDRAM Address Multiplexing SDMA[12:0] and SDBA[1:0] —64-Bit Mode (Continued)**

- a. For SDRAMs with 11 column bits, SDMA10 is driven low during the SDCAS phase to indicate a read or write without autoprecharge and SDMA11 is used as the 11th column bit.

## 1.2 SDRAM Memory Data Interface

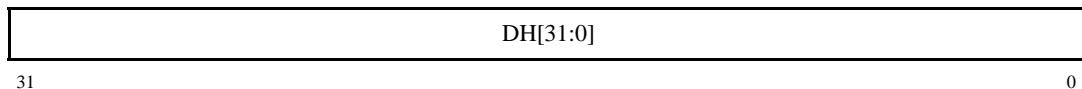

To reduce loading on the data bus, the Tsi107 features on-chip buffers between the 60x data bus and the memory data bus. There are sixty four bidirectional data signals (MDH[0:31] and MDL[0:31]), and eight bidirectional data parity signals (PAR[0:7]). The PAR[0:7] signals also perform as ECC syndrome bits when the controller is running in ECC mode.

Eight SDRAM data in/out mask signals (DQM[0:7]) are provided to control the byte lane selection for 32- and 64-bit accesses. The architecture is constructed with the premise that an 8-bit SDRAM device has one DQM signal and eight data signals (DQ[0:7]), and a 16-bit SDRAM device has two DQM signals associated to specific halves of the sixteen data signals (DQ[0:7] and DQ[8:15]).

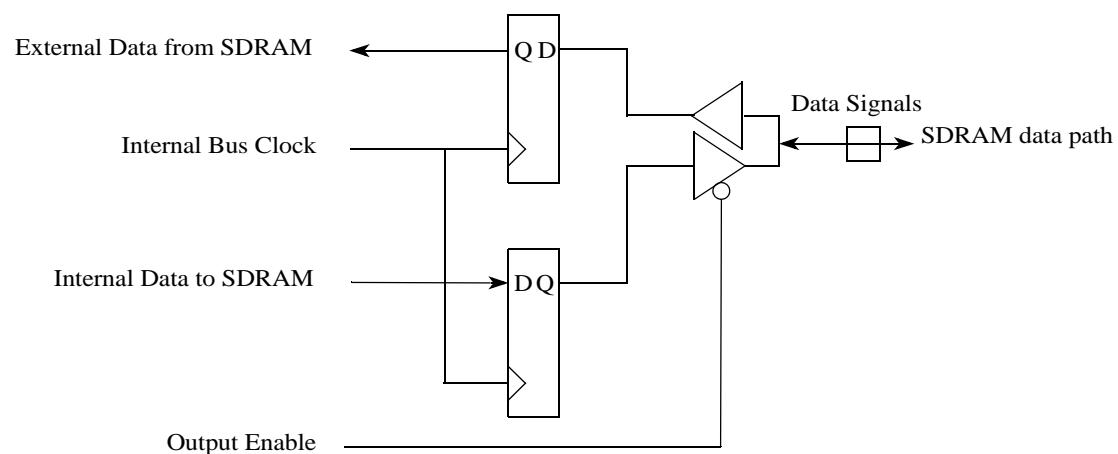

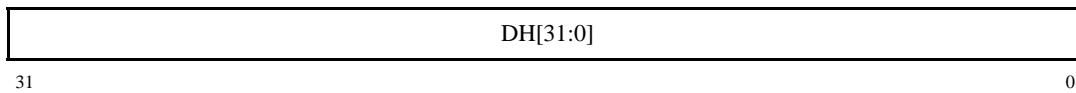

The Tsi107 supports two types of internal data path buffering for the SDRAM data interface, registered and in-line. Registered buffer mode is the default mode for the Tsi107 and has a latency of one clock cycle. [Figure 3](#) shows the basic structure of the registered interface. This structure is used to correct the setup and hold times associated with the interface.

**Figure 3: SDRAM Registered Memory Interface**

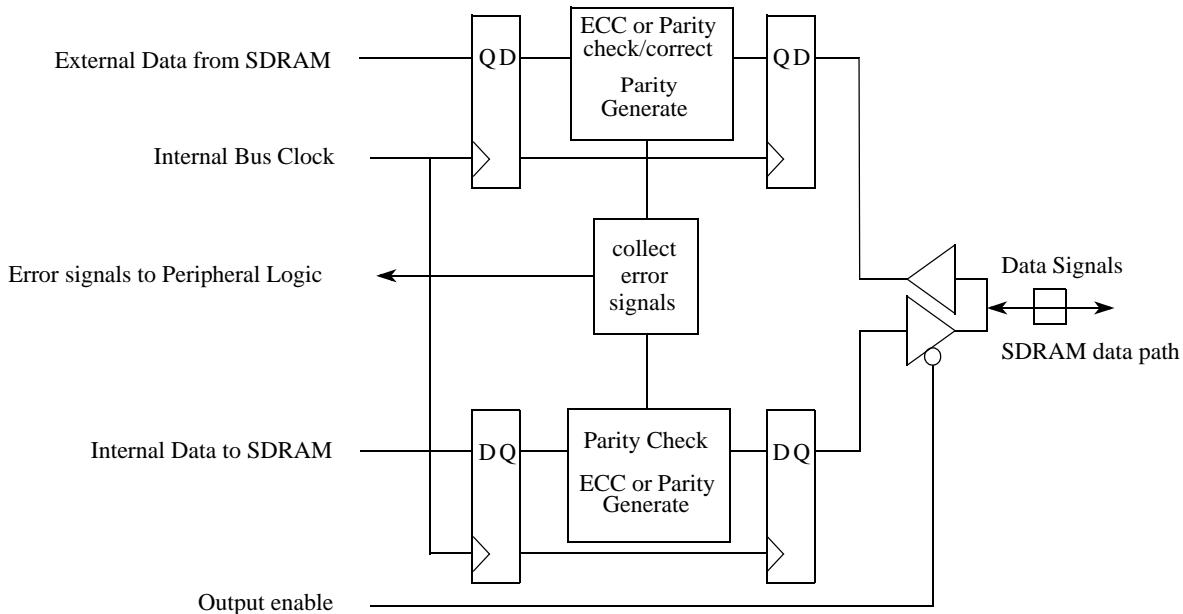

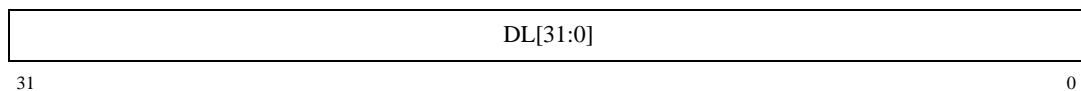

The use of ECC or parity for data error management requires that the data be held for one clock cycle while the respective syndrome code or parity bit generation and checking logic perform their function. This required the introduction of an additional set of latches as shown in [Figure 4](#). The detailed operation of the In-line ECC function is described in [Section 2](#).

**Figure 4: SDRAM In-Line ECC/Parity Memory Interface**

### 1.3

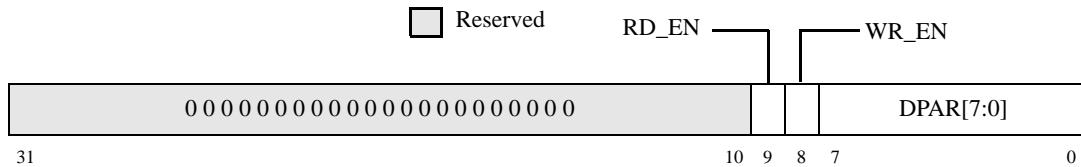

## Memory Datapath Configuration and Control Registers

The Memory Configuration and Control Registers (MCCR 1 to 4) are used to set up the operating parameters of the memory interface. The configuration information can be split into two categories, memory data path parameters and memory device operating parameters.

[Table 2](#) lists the names and locations of the parameters that determine the data path buffer mode and the parity or ECC operation of the Tsi107. Following the table are descriptions of the individual bits. The memory device operating parameters are device specific. The bit fields and detailed descriptions are contained in [Section 1.4 on page 16](#).

[Table 3](#) describes the parameter settings for the available SDRAM data path buffer options. Note that combinations of configuration register bit settings that are not specified in [Table 3](#) have undefined behavior.

This application note concerns itself with the last entry of [Table 3](#), titled “In-line, ECC enabled”. For information on the remaining configurations, refer to the *Tsi107 User Manual*.

**Table 2: Memory Data Path Parameters**

| Bit Name           | Register and Offset | Bit Number in Register |

|--------------------|---------------------|------------------------|

| RAM_TYPE           | MCCR1 @F0           | 17                     |

| EDO                | MCCR2 @F4           | 16                     |

| PCKEN              | MCCR1 @F0           | 16                     |

| INLINE_WR_EN       | MCCR2 @F4           | 19                     |

| INLINE_RD_EN       | MCCR2 @F4           | 18                     |

| INLINE_PAR_NOT_ECC | MCCR2 @F4           | 20                     |

| BUF_TYPE[0]        | MCCR4 @FC           | 22                     |

| BUF_TYPE[1]        | MCCR4 @FC           | 20                     |

| RMW_PAR            | MCCR2 @F4           | 0                      |

| ECC_EN             | MCCR2 @F4           | 17                     |

| MEM_PARITY_ECC_EN  | ErrEnR1 @C0         | 2                      |

| MB_ECC_ERR_EN      | ErrEnR2 @C4         | 3                      |

**1.3.1****RAM TYPE MCCR1 bit 17**

The RAM TYPE bit controls the operation of the memory controller. This determination is necessary as the controller is required to communicate some initialization information to SDRAM type devices, but not to FPM or EDO type devices.

- 0) Indicates synchronous DRAM (SDRAM).

- 1) Indicates FPM DRAM or EDO DRAM (depending on the setting for MCCR2[EDO])

**For the purpose of this app note, this bit must be cleared.**

Note that this bit must be cleared (selecting DRAM or SDRAM) before the in-line or registered buffer mode bits in MCCR4 are set.

**1.3.2****EDO MCCR2 bit 16**

The EDO enable allows the memory controller to differentiate between FPM and EDO type devices. See the *Ts1107 User Manual*, Section 6.3, “FPM or EDO DRAM Interface Operation” for more information.

- 0) Indicates standard DRAMs

- 1) Indicates EDO DRAMs

**For the purpose of this app note, this bit must be cleared.**

**1.3.3****PCKEN MCCR1 bit 16**

This bit enables parity checking/generation in the memory interface.

- 0) Disables parity checking and parity generation for transactions to DRAM/EDO/SDRAM memory. Note that this bit must be cleared for SDRAM memory when operating in in-line buffer mode (MCCR4[BUF\_TYPE[0-1]] = 0b10) and in-line parity/ECC is enabled with MCCR2[INLINE\_RD\_EN] = 1.

- 1) Enables parity checking and generation for all registered mode memory transactions to DRAM/EDO/SDRAM memory when using the registered mode of operation.

**For the purpose of this app note, this bit must be cleared.**

**1.3.4****INLINE\_WR\_EN MCCR2 bit 19**

This bit is called In-line parity error reporting enable and is used for SDRAM only. This bit controls whether the Tsi107 uses the in-line parity hardware to report 60x bus parity errors on writes to memory. Note that the buffer type selector in MCCR4 must be set to in-line buffer mode (MCCR4[BUF\_TYPE[0-1]] = 0b10) to enable the in-line ECC/parity logic.

- 0) In-line 60x bus parity error reporting disabled.

- 1) In-line 60x bus parity error reporting enabled.

**For the purpose of this app note, this bit must be cleared.**

**1.3.5****INLINE\_RD\_EN MCCR2 bit 18**

This is a multi-function bit and is called “In-line read parity or ECC check/correction enable”. This bit controls whether the Tsi107 uses the ECC/parity checking and/or correction hardware in the in-line data path to report ECC or parity errors on memory system read operations. This bit activates different parity/ECC checking/correction hardware than that controlled by ECC\_EN and PCKEN. Read parity/ECC checking can be enabled for SDRAM systems running in in-line buffer mode (MCCR4[BUF\_TYPE[0-1]] = 0b10) only. Also, note that when the INLINE\_RD\_EN bit is used in conjunction with the INLINE\_PAR\_NOT\_ECC bit, the INLINE\_PAR\_NOT\_ECC bit selects between parity or ECC on the memory data bus.

- 0) In-line memory bus read parity/ECC error reporting disabled

- 1) In-line memory bus read parity/ECC error reporting enabled. Note that MCCR1[PCKEN] must be cleared when this bit is set.

**For the purpose of this app note, this bit must be set.**

### 1.3.6 **INLINE\_PAR\_NOT\_ECC**

This bit selects between the ECC and parity checking/correction mechanisms of the in-line data path when performing memory reads. This bit is applicable for SDRAM systems running in in-line buffer mode only (MCCR4[BUF\_TYPE[0–1]] = 0b10), and when INLINE\_RD\_EN = 1.

- 0) Tsi107 uses ECC on the memory data bus.

- 1) Tsi107 uses parity on the memory data bus.

**For the purpose of this app note, this bit must be cleared.**

### 1.3.7 **BUF\_TYPE[0] MCCR4 bit 22 and BUF\_TYPE[1] MCCR4 bit 20**

The most significant bit of the memory data bus buffer-type field. BUF\_TYPE[0] is used with bit 20 (BUF\_TYPE[1]) to configure the internal memory data path buffering scheme as follows:

BUF\_TYPE[0–1]:

- 00) Reserved

- 01) Registered buffer mode (default)

- 10) In-line buffer mode; SDRAM only

- 11) Reserved

The Tsi107 must be configured for in-line buffer mode in order to use the in-line ECC/parity logic for SDRAM. The in-line ECC and parity hardware allow the Tsi107 to check and generate parity on the 60x bus and check, correct and generate ECC or parity on the external SDRAM memory bus. See [Section 1.2, “SDRAM Memory Data Interface”](#) for more information.

**For the purpose of this app note, BUF\_TYPE[0] must be set, and BUF\_TYPE[1] must be cleared.**

### 1.3.8 **RMW\_PAR MCCR2 bit 0**

Read-modify-write (RMW) parity enable. This bit controls how the Tsi107 writes parity bits to DRAM/EDO/SDRAM. Note that this bit does not enable parity checking and generation. PCKEN must be set to enable parity checking. Also note that this bit and ECC\_EN cannot both be set to 1. See Table 3 for valid combinations.

- 0) RMW parity disabled

- 1) RMW parity enabled. Note that this bit must be set for SDRAM systems that use in-line ECC in combination with (MCCR2[ECC\_EN] = 0, MCCR4[BUF\_TYPE[0–1]] = 0b10, and MCCR2[INLINE\_PAR\_NOT\_ECC]) = 0).

**For the purpose of this app note, this bit must be set.**

**1.3.9    ECC\_EN MCCR2 bit 17**

This bit controls whether the Tsi107 uses ECC for transactions to system memory that is constructed of FPM or EDO devices. ECC\_EN can be set only for systems using FPM/EDO memory. Note that the ECC\_EN parameter overrides the PCKEN parameter. Also note that this bit and RMW\_PAR cannot both be set, and it is illegal to set this bit with the combination of EDO = 1 and REGISTERED = 1. Systems using SDRAM use a different (in-line) ECC hardware and therefore, must have ECC\_EN = 0.

- 0) ECC disabled

- 1) ECC enabled

**For the purpose of this app note, this bit must be cleared.**

**1.3.10    Mem\_parity\_ECC\_en ErrEnR1 bit 2**

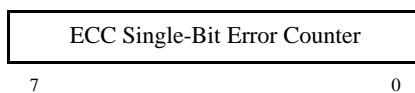

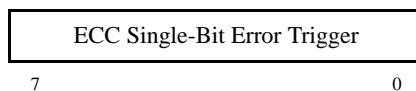

This bit is called Memory Parity and ECC Error Enable. It enables the detection of system memory read parity errors that occur on accesses to system memory or those that occur that exceed the ECC single-bit error threshold. The threshold is set in the ECC Single-bit Error Trigger Register, and the error occurrence is counted in the ECC Single-bit Error Counter Register. The fact that the threshold was exceeded is indicated in Error Detection Register 1, bit 2.

- 0) Memory read parity/ECC single-bit threshold disabled

- 1) Memory read parity/ECC single-bit threshold enabled

**For the purpose of this app note, this bit must be set.**

**1.3.11    MB\_ECC\_ERR\_EN ErrEnR2 bit 3**

This bit is called the Multi-bit ECC Error Enable. This bit enables the detection of ECC multibit errors. The occurrence is reported in Error Detection Register 2, bit 3.

- 0) ECC multi-bit error detection disabled

- 1) ECC multi-bit error detection enabled

**For the purpose of this app note, this bit must be set.**

**Table 3: SDRAM System Configurations**

| RAM_TYPE | EDO | PCKEN | INLINE_WR_EN | INLINE_RD_EN | INLINE_PAR_NOT_ECC | BUF_TYPE[0] | BUF_TYPE[1] | RMW_PAR | ECC_EN | MEM_PARITY_ECC_EN | MB_ECC_ERR_EN | Description                                           |                                                        |     |

|----------|-----|-------|--------------|--------------|--------------------|-------------|-------------|---------|--------|-------------------|---------------|-------------------------------------------------------|--------------------------------------------------------|-----|

|          |     |       |              |              |                    |             |             |         |        |                   |               | Supports 60x Bus Parity on Processor Reads from SDRAM | Supports 60x Bus Parity on Processor Writes from SDRAM |     |

| 0        | 0   | 0     | 0            | 0            | 0                  | 0           | 1           | 0       | 0      | 0                 | 0             | Registered, no ECC or parity                          | No                                                     | No  |

| 0        | 0   | 1     | 0            | 0            | 0                  | 0           | 1           | 0       | 0      | 1                 | 0             | Registered buffer parity                              | Yes                                                    | No  |

| 0        | 0   | 1     | 0            | 0            | 0                  | 0           | 1           | 1       | 0      | 1                 | 0             | Registered buffer RMW parity                          | Yes                                                    | No  |

| 0        | 0   | 0     | 0            | 0            | 0                  | 1           | 0           | 0       | 0      | 0                 | 0             | In-line, no parity                                    | No                                                     | No  |

| 0        | 0   | 0     | 1            | 1            | 1                  | 1           | 0           | 0       | 0      | 1                 | 0             | In-line, parity enabled                               | Yes                                                    | No  |

| 0        | 0   | 0     | 0            | 1            | 1                  | 1           | 0           | 1       | 0      | 1                 | 0             | In-line, RMW parity enabled                           | Yes                                                    | Yes |

| 0        | 0   | 0     | 0            | 1            | 0                  | 1           | 0           | 1       | 0      | 1                 | 1             | In-line, ECC enabled                                  | No                                                     | No  |

## 1.4 Bit settings for SDRAM System Configurations

In order to configure a fully operational memory system, a number of memory device specific parameters are required to be programmed into the MCCR registers. These parameters tell the controller when to make write data valid on the memory bus and when to expect read data from the memory devices on the bus.

The registers will be examined sequentially from MCCR1 to MCCR4, however, when the user actually writes to the Tsi107, MCCR1 will need to be written a second time with the “MEMGO” bit set to command the controller to begin initializing the SDRAM memory devices with the correct control patterns.

The intent of this app note is to explain to the reader what parameters are required in the related bit fields. The compilation of the data word to be written into the register is left up to the reader. The bit field descriptions have been focused on SDRAM devices and so are different from those found in the *Tsi107 User Manual*.

### 1.4.1 Memory Page Mode Register

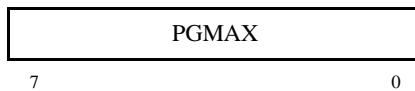

The 1-byte memory page mode register, shown in Figure 5 and Table 4, contains the PGMAX parameter which controls how long the Tsi107 retains the currently accessed page (row) in memory.

**Figure 5: Memory Page Mode Register—0xA3****Table 4: Bit Settings for Memory Page Mode Register—0xA3**

| Bits | Name  | Reset Value | Description                                                                                                                                                                                                                          |

|------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0  | PGMAX | All 0s      | For SDRAM configurations, the value of PGMAX multiplied by 64 determines the activate to precharge interval (sometimes called row active time or $t_{RAS}$ ) for retained page mode. When programmed to 0x00, page mode is disabled. |

The 1-byte memory page mode register (MPMR) contains the PGMAX parameter that controls how long the Tsi107 retains the currently accessed page (row) in memory. The PGMAX parameter specifies the activate-to-precharge interval (sometimes called row active time or  $t_{RAS}$ ). The PGMAX value is multiplied by 64 to generate the actual number of clock cycles for the interval. When PGMAX is programmed to 0x00, page mode is disabled. The value for PGMAX depends on the specific SDRAM devices used, the ROM system, and the operating frequency of the Tsi107. When the interval specified by PGMAX expires, the Tsi107 must close the active page by issuing a precharge bank command. PGMAX must be sufficiently less than the maximum row active time for the SDRAM device to ensure that the issuing of a precharge command is not stalled by a memory access. When PGMAX expires during a memory access, the Tsi107 must wait for the access to complete before issuing the precharge command to the SDRAM. In the worst case, the Tsi107 initiates a memory access one clock cycle before PGMAX expires. If ROM is located on the memory bus, the longest access that could potentially stall a precharge is a burst read from ROM. If ROM is located on the PCI bus, the longest memory access is a burst read from the SDRAM.

The Tsi107 also requires two clock cycles to issue a precharge bank command to the SDRAM device so the PGMAX interval must be further reduced by two clock cycles. Therefore, PGMAX should be programmed according to the following equation:

$$\text{PGMAX} < [t_{RAS}(\text{MAX}) - (\text{worst case memory access}) - 2] / 64$$

For example, consider a system with a memory bus clock frequency of 66 MHz using SDRAMs with a maximum row active time ( $t_{RAS}(\text{MAX})$ ) of 100 us. The maximum number of clock cycles between activate bank and precharge bank commands is  $66 \text{ MHz} \times 100 \text{ us} = 6600$  clock cycles.

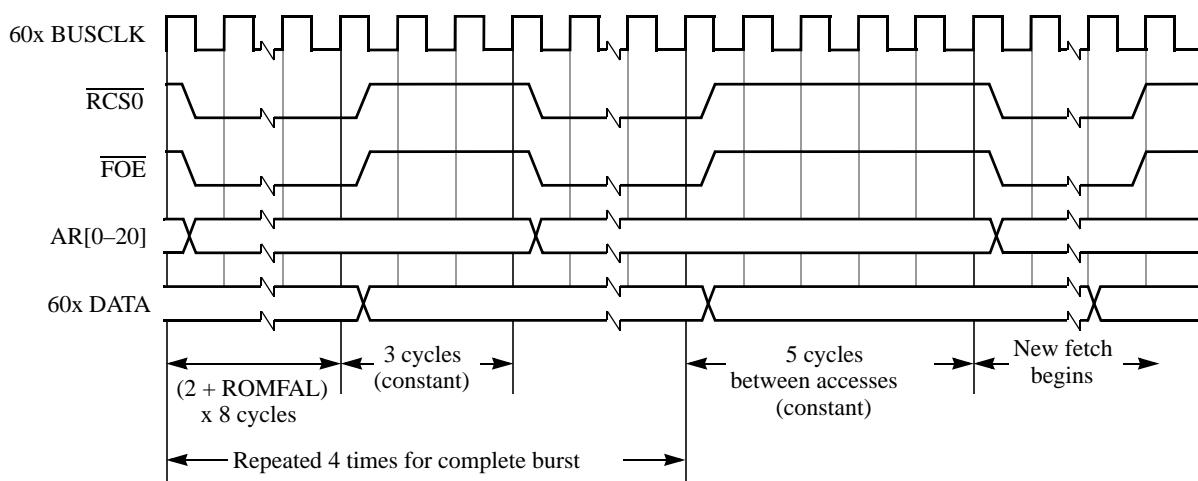

If the system uses 8-bit ROMs on the memory bus, a processor burst read (a 32-byte cache line read) from ROM (a non-bursting ROM device) follows the timing shown in Figure 6-60. Also affecting the ROM access time is MCCR2[TS\_WAIT\_TIMER]. The minimum time allowed for ROM devices to enter high impedance is two clock cycles. TS\_WAIT\_TIMER adds clocks (n-1) to the minimum disable time. This delay is enforced after all ROM accesses preventing any other memory access from starting. Therefore a burst read from an 8-bit ROM (worst case access time) takes:

$$\{[(ROMFAL + 2) \times 8 + 3] \times 4\} + [2 + (TS\_WAIT\_TIMER - 1)] \text{ clock cycles}$$

So, if MCCR1[ROMFAL] = 4 and MCCR2[TS\_WAIT\_TIMER] = 3, the interval for a local processor burst read from an 8-bit ROM takes

$$\{[(4 + 2) \times 8 + 3] \times 4\} + [2 + (3 - 1)] = 204 + 4 = 208 \text{ clock cycles.}$$

Plugging the values into the PGMAX equation above,

$$PGMAX < (6600 - 208 - 2) \div 64 = 99.8 \text{ clock cycles.}$$

The value stored in PGMAX would be 0b0110\_0011 (or 99 clock cycles).

#### 1.4.2 Memory Control Configuration Register 1

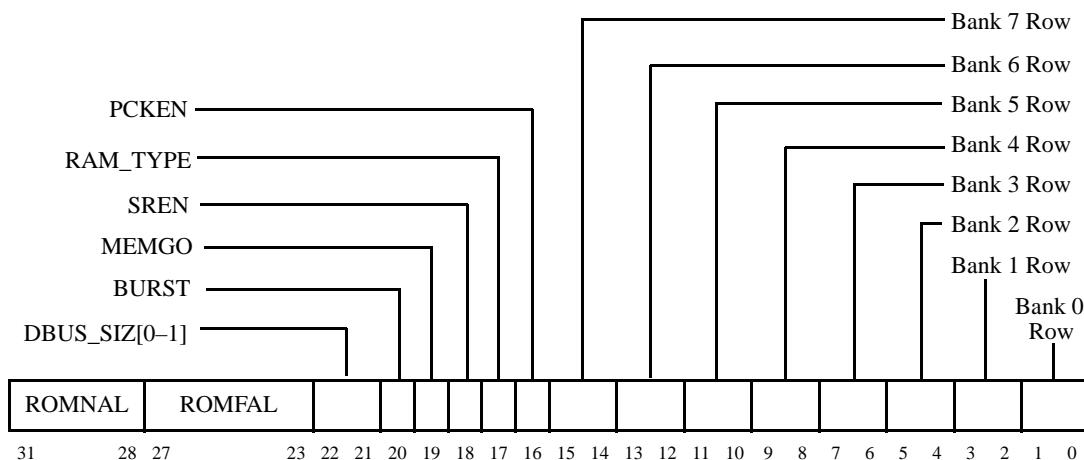

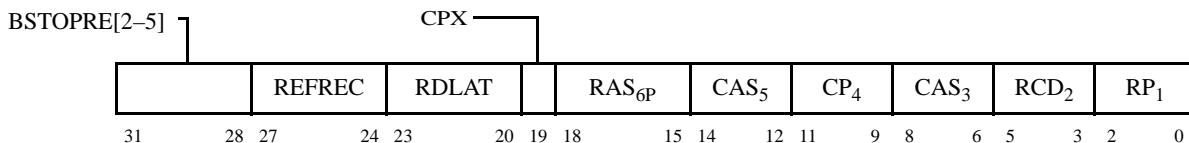

Figure 6 and Table 5 show the memory control configuration register 1 (MCCR1) format and bit settings.

**Figure 6: Memory Control Configuration Register 1 (MCCR1)—0xF0**

***SDRAM related bit fields in MCCR1 that require attention:***

**bit 18 SREN** - If the system will support power down modes, this bit selects who becomes responsible for refreshing the SDRAM during sleep.

**bit 17 RAMTYPE** - this bit needs to be cleared during initialization to select SDRAM.

**bit 16 PCKEN** - this bit needs to be cleared for ECC operation.

**bits 15 to 0 Bank n row** - these need to be configured for the row/column/bank architectures of the SDRAM devices being used in the system.

**Table 5: Bit Settings for MCCR1—0xF0**

| Bits  | Name   | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–28 | ROMNAL | All 1s      | For burst-mode ROM and Flash reads, ROMNAL controls the next access time. The maximum value is 0b1111 (15). The actual cycle count is three cycles more than the binary value of ROMNAL.<br>For Flash writes, ROMNAL measures the write pulse recovery (high) time. The maximum value is 0b1111 (15). The actual cycle count is four cycles more than the binary value of ROMNAL.                                                                                                                                                                                             |

| 27–23 | ROMFAL | All 1s      | For nonburst ROM and Flash reads, ROMFAL controls the access time. For burst-mode ROMs, ROMFAL controls the first access time. The maximum value is 0b11111 (31). For the 64-bit and 32-bit configurations, the actual cycle count is three cycles more than the binary value of ROMFAL. For the 8-bit configuration, the actual cycle count is two cycles more than the binary value of ROMFAL.<br>For Flash writes, ROMFAL measures the write pulse low time. The maximum value is 0b11111 (31). The actual cycle count is two cycles more than the binary value of ROMFAL. |

**Table 5: Bit Settings for MCCR1—0xF0 (Continued)**

| Bits  | Name          | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22–21 | DBUS_SIZ[0–1] | xx          | <p>Read-only. This field indicates the state of the memory data path width. The value of this field is determined by the reset configuration signals [DL[0], FOE]. Used with DBUS_SIZ2 (stored in MCCR4[17]) as shown below.</p> <p>DBUS_SIZ[0–2]:</p> <p>For ROM/Flash chip select #0 (<math>\overline{\text{RCS0}}</math>):</p> <ul style="list-style-type: none"> <li>00n 32-bit data bus</li> <li>n1n 8-bit data bus</li> <li>10n 64-bit data bus</li> </ul> <p>For ROM/Flash chip select #1 (<math>\overline{\text{RCS1}}</math>):</p> <ul style="list-style-type: none"> <li>0n0 32-bit data bus</li> <li>nn1 8-bit data bus</li> <li>1n0 64-bit data bus</li> </ul> <p>For ROM/Flash chip select #2 (<math>\overline{\text{RCS2}}</math>), ROM/Flash chip select #3 (<math>\overline{\text{RCS3}}</math>), and (S)DRAM:</p> <ul style="list-style-type: none"> <li>0nn 32-bit data bus</li> <li>1nn 64-bit data bus</li> </ul> |

| 20    | BURST         | 0           | <p>Burst mode ROM timing enable</p> <p>0 Indicates standard (nonburst) ROM access timing</p> <p>1 Indicates burst-mode ROM access timing</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 19    | MEMGO         | 0           | <p>RAM interface logic enable. Note that this bit must not be set until all other memory configuration parameters have been appropriately configured by boot code.</p> <p>0 Tsi107 RAM interface logic disabled</p> <p>1 Tsi107 RAM interface logic enabled</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18    | SREN          | 0           | <p>Self-refresh enable. Note that if self refresh is disabled, the system is responsible for preserving the integrity of DRAM/EDO/SDRAM during sleep mode.</p> <p>0 Disables the DRAM/EDO/SDRAM self refresh during sleep mode</p> <p>1 Enables the DRAM/EDO/SDRAM self refresh during sleep mode</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17    | RAM_TYPE      | 1           | <p>RAM type</p> <p>0 Indicates synchronous DRAM (SDRAM)</p> <p>1 Indicates DRAM or EDO DRAM (depending on the setting for MCCR2[EDO])</p> <p>Note that this bit must be cleared (selecting DRAM or SDRAM) before the in-line or registered buffer mode bits in MCCR4 are set.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

**Table 5: Bit Settings for MCCR1—0xF0 (Continued)**

| Bits  | Name       | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16    | PCKEN      | 0           | Memory interface parity checking/generation enable<br>0 Disables parity checking and parity generation for transactions to DRAM/EDO/SDRAM memory. Note that this bit must be cleared for SDRAM memory when operating in in-line buffer mode (MCCR4[BUF_TYPE[0-1]] = 0b10) and in-line parity/ECC is enabled with MCCR2[INLINE_RD_EN] = 1.<br>1 Enables parity checking and generation for all registered mode memory transactions to DRAM/EDO/SDRAM memory.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15–14 | Bank 7 row | 00          | RAM bank 7 row address bit count. These bits indicate the number of row address bits that are required by the RAM devices in bank 7.<br>For FPM/EDO DRAM configurations (RAM_TYPE = 1), the encoding is as follows:<br>00 9 row bits<br>01 10 row bits<br>10 11 row bits<br>11 12 or 13 row bits<br><br>For SDRAM configurations (RAM_TYPE = 0), the encoding is as follows:<br>00 12 row bits by n column bits by 4 logical banks ( $12 \times n \times 4$ ) or<br>11 row bits by n column bits by 4 logical banks ( $11 \times n \times 4$ )<br>01 13 row bits by n column bits by 2 logical banks ( $13 \times n \times 2$ ) or<br>12 row bits by n column bits by 2 logical banks ( $12 \times n \times 2$ )<br>10 13 row bits by n column bits by 4 logical banks ( $13 \times n \times 4$ )<br>11 11 row bits by n column bits by 2 logical banks ( $11 \times n \times 2$ ) |

| 13–12 | Bank 6 row | 00          | RAM bank 6 row address bit count. See the description for Bank 7 row (bits 15–14).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11–10 | Bank 5 row | 00          | RAM bank 5 row address bit count. See the description for Bank 7 row (bits 15–14).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9–8   | Bank 4 row | 00          | RAM bank 4 row address bit count. See the description for Bank 7 row (bits 15–14).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7–6   | Bank 3 row | 00          | RAM bank 3 row address bit count. See the description for Bank 7 row (bits 15–14).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5–4   | Bank 2 row | 00          | RAM bank 2 row address bit count. See the description for Bank 7 row (bits 15–14).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3–2   | Bank 1 row | 00          | RAM bank 1 row address bit count. See the description for Bank 7 row (bits 15–14).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1–0   | Bank 0 row | 00          | RAM bank 0 row address bit count. See the description for Bank 7 row (bits 15–14).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### 1.4.3 Memory Control Configuration Register 2—0xF4

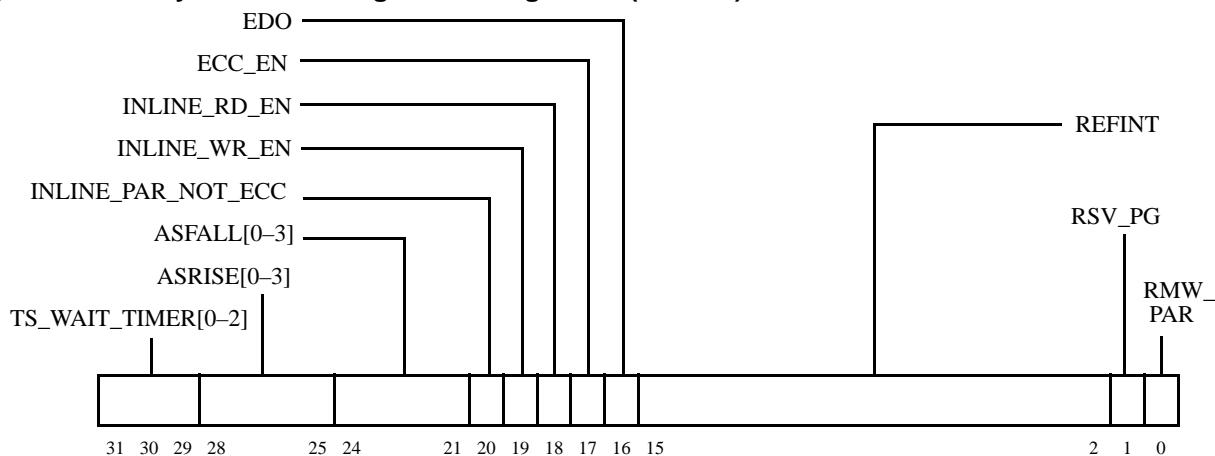

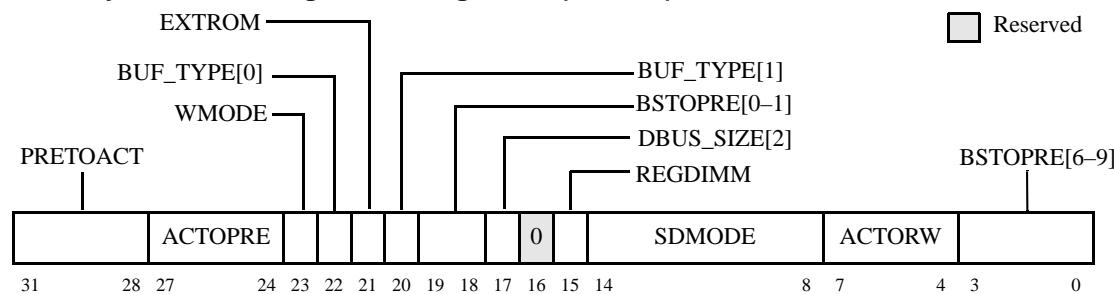

Figure 7 and Table 6 show the memory control configuration register 2 (MCCR2) format and bit settings.

**Figure 7: Memory Control Configuration Register 2 (MCCR2)—0xF4*****SDRAM related bit fields in MCCR2 that require attention:***

**bit 20 Inline\_par\_not\_ECC** - This bit needs to be cleared for ECC operation.

**bit 19 Inline\_WR\_EN** - This bit needs to be cleared for ECC operation.

**bit 18 Inline\_RD\_EN** - This bit needs to be set for ECC operation.

**bit 17 ECC\_EN** - This bit needs to be cleared for ECC operation with SDRAM.

**bit 16 EDO** - This bit needs to be cleared for ECC operation.

**bit 15-2 REFINT** - The memory interface supplies CAS before RAS (CBR) refreshes to SDRAM at the refresh interval specified by MCCR2[REFINT]. When REFINT expires, the Tsi107 issues a precharge and then a refresh command to the SDRAM devices. The value stored in REFINT should allow for a potential collision between memory accesses and refresh cycles. In the worst case, the refresh must wait the number of clock cycles required by the longest access. For example, if ROM is located on the 60x/memory bus and a ROM access is in progress at the time a refresh operation needs to be performed, the refresh must wait until the ROM access has completed. If ROM is located on the 60x/memory bus, the longest access that could potentially stall a refresh is a burst read from ROM. If ROM is located on the PCI bus, the longest memory access is a burst read from the SDRAM. The Tsi107 also has to wait for a precharge command (to close any open pages) before it can issue the refresh command. The Tsi107 requires two clock cycles to issue a precharge to an internal bank; with two pages open simultaneously, this equates to four extra clock cycles that must be taken off the refresh interval. Finally, the Tsi107 must wait for the PRETOACT interval to pass before issuing the refresh command.

Therefore, REFINT should be programmed according to the following equation:

$$\text{REFINT} < (\text{per row refresh interval}) - (\text{worst case memory access}) - (\text{PRETOACT}) - 4$$

Consider a typical SDRAM device with a refresh period of 32 ms for a 2K cycle. This means that it takes 32 ms to refresh each internal bank and each internal bank has 2K rows. To refresh the whole SDRAM (two internal banks, 4K rows) it takes 64 ms. The refresh time per row is  $32\text{ ms} \div 2048\text{ rows}$  (or  $64\text{ ms} \div 4096\text{ rows}$ ) =  $15.6\text{ }\mu\text{s}$ . If the 60x bus clock is running at 66 MHz, the number of clock cycles per row refresh is  $15.6\text{ }\mu\text{s} \times 66\text{ MHz} = 1030$  clock cycles.

If the system uses 8-bit ROMs on the 60x/memory bus, a burst read from ROM will follow the timing shown in [Figure 8](#) below. Also affecting the ROM access time is MCCR2[TS\_WAIT\_TIMER]. The minimum time allowed for ROM devices to enter high impedance is two clock cycles. TS\_WAIT\_TIMER adds clocks (n-1) to the minimum disable time. This delay is enforced after all ROM accesses preventing any other memory access from starting. Therefore, a burst read from an 8-bit ROM will take:

$$\{[(\text{ROMFAL} + 2) \times 8 + 3] \times 4 + 5\} + [2 + (\text{TS_WAIT_TIMER} - 1)] \text{ clock cycles}$$

So, if MCCR1[ROMFAL] = 4 and MCCR2[TS\_WAIT\_TIMER] = 3, the interval for a 60x burst read from an 8-bit ROM will take:

$$\{[(4 + 2) \times 8 + 3] \times 4 + 5\} + [2 + (3 - 1)] = 209 + 4 = 213 \text{ clock cycles}$$

Plugging the values into the REFINT equation above:

$$\text{REFINT} < 1030 - 213 - 2 - 4 = 811 \text{ clock cycles}$$

The value stored in REFINT should be 0b00 0011 0010 1010 (or 810 clock cycles).

**bit 0 RMW\_PAR** - This bit needs to be set for ECC operation

**Figure 8: 8-Bit ROM/Flash Interface—Burst Read Timing.**

**Table 6: Bit Settings for MCCR2—0xF4**

| Bits  | Name                                     | Reset Value                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                                    |  |  |                                          |                                                                                       |                                                                                                   |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |           |

|-------|------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------|--|--|------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|----------|----------|----------|-----|----------|----------|----------|-----|----------|----------|----------|-----|----------|----------|----------|-----|----------|----------|----------|-----|----------|----------|----------|-----|----------|----------|----------|-----|----------|----------|-----------|

| 31–29 | TS_WAIT_TIMER[0–2]                       | 000                                                                                   | <p>Transaction start wait states timer. The minimum time allowed for ROM/Flash/Port X devices to enter high impedance is 2 memory system clocks. TS_WAIT_TIMER[0–2] adds wait states before the subsequent transaction starts in order to account for longer disable times of a ROM/Flash/Port X device. This delay is enforced after all ROM and Flash accesses, delaying the next memory access from starting (for example, DRAM after ROM access, SDRAM after Flash access, ROM after Flash access).</p> <p>Note that this parameter is supported for SDRAM systems only. For EDO/FPM DRAM systems, TS_WAIT_TIMER[0–2] must = 000.</p> <table border="1" data-bbox="571 665 1395 1203"> <thead> <tr> <th rowspan="2">Bits</th><th colspan="3">Wait States for ROM High Impedance</th></tr> <tr> <th>Reads with wide data path (32 or 64-bit)</th><th>Reads with gather data path in flow-through or registered buffer mode (8, 16, 32-bit)</th><th>All writes<sup>1, 2</sup> and reads with gather data path in in-line buffer mode (8, 16, 32-bit)</th></tr> </thead> <tbody> <tr> <td>000</td><td>2 clocks</td><td>5 clocks</td><td>6 clocks</td></tr> <tr> <td>001</td><td>2 clocks</td><td>5 clocks</td><td>6 clocks</td></tr> <tr> <td>010</td><td>3 clocks</td><td>5 clocks</td><td>6 clocks</td></tr> <tr> <td>011</td><td>4 clocks</td><td>5 clocks</td><td>6 clocks</td></tr> <tr> <td>100</td><td>5 clocks</td><td>6 clocks</td><td>7 clocks</td></tr> <tr> <td>101</td><td>6 clocks</td><td>7 clocks</td><td>8 clocks</td></tr> <tr> <td>110</td><td>7 clocks</td><td>7 clocks</td><td>7 clocks</td></tr> <tr> <td>111</td><td>8 clocks</td><td>9 clocks</td><td>10 clocks</td></tr> </tbody> </table> <p>Note 1. In this context, Flash writes are defined as any write to <math>\overline{\text{RCS}}[0–3]</math>.</p> <p>Note 2: For Flash writes, add the write recovery time, ROMNAL, to the given wait states for ROM high-impedance time.</p> | Bits | Wait States for ROM High Impedance |  |  | Reads with wide data path (32 or 64-bit) | Reads with gather data path in flow-through or registered buffer mode (8, 16, 32-bit) | All writes <sup>1, 2</sup> and reads with gather data path in in-line buffer mode (8, 16, 32-bit) | 000 | 2 clocks | 5 clocks | 6 clocks | 001 | 2 clocks | 5 clocks | 6 clocks | 010 | 3 clocks | 5 clocks | 6 clocks | 011 | 4 clocks | 5 clocks | 6 clocks | 100 | 5 clocks | 6 clocks | 7 clocks | 101 | 6 clocks | 7 clocks | 8 clocks | 110 | 7 clocks | 7 clocks | 7 clocks | 111 | 8 clocks | 9 clocks | 10 clocks |

| Bits  | Wait States for ROM High Impedance       |                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                                    |  |  |                                          |                                                                                       |                                                                                                   |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |           |

|       | Reads with wide data path (32 or 64-bit) | Reads with gather data path in flow-through or registered buffer mode (8, 16, 32-bit) | All writes <sup>1, 2</sup> and reads with gather data path in in-line buffer mode (8, 16, 32-bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                                    |  |  |                                          |                                                                                       |                                                                                                   |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |           |

| 000   | 2 clocks                                 | 5 clocks                                                                              | 6 clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                    |  |  |                                          |                                                                                       |                                                                                                   |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |           |

| 001   | 2 clocks                                 | 5 clocks                                                                              | 6 clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                    |  |  |                                          |                                                                                       |                                                                                                   |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |          |     |          |          |           |