Date: Dec. 4, 2013

## F9B9G5G'H97<B=75@I D85H9

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product category      | MPU/MCU                                            | Document<br>No.      | TN-RX*-A083A/E         |                                                                      | Rev. | 1.00 |

|-----------------------|----------------------------------------------------|----------------------|------------------------|----------------------------------------------------------------------|------|------|

| Title                 | Usage Notes on Group-A Priority Contr<br>Converter | Information category | Technical Notification |                                                                      |      |      |

| Applicable<br>Product | RX63T Group                                        | Lot No.              |                        | RX63T Group User's Manual:<br>Hardware Rev.2.10<br>(R01UH0238JJ0210) |      |      |

|                       |                                                    | All lots             | Reference<br>Document  |                                                                      |      | al:  |

Thank you for your valued patronage and best wished for your continued success in business.

It turned out that there are some restrictions on Group-A priority control of the 12-bit A/D converter (144/120/112/100pin packages). We would like to inform you of the restrictions and countermeasures.

## ■Usage Notes

- (1) When operating under group-A priority control in the group-scan mode, specify the frequency ratio between the peripheral module clock (PCLKB) and A/D conversion clock, ADCLK (=PCLKD) as indicated below.

- a) PCLKB = PCLKD (Set the same value to the SCKCR. PCKB [3:0] and SCKCR. PCKD[3:0])

- b) PCLKB/2 = PCLKD (Set a value which +1 is added to the one set to the SCKCR. PCKB [3:0] to the SCKCR. PCKD[3:0])

- (2) When operating under the setting other than those mentioned in (1), write 1 to the PGSC bit of the newly-released ADGSPMR register before use.

Specifications of the ADGSPMR register are shown in the next page.

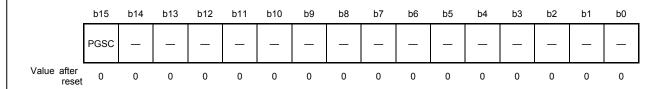

## A/D Group Scan Priority Control Register (ADGSPMR)

Address S12AD: ADGSPMR 0008 90FCh

| Bit    | Symbol | Bit name                                                                  | Description                                                                                                                                                                                                       | R/W |

|--------|--------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b14-b0 | _      | Reserved                                                                  | These bits are read as 0. The write value should be 0.                                                                                                                                                            | R/W |

| b15    | PGSC   | Clock frequency setting bit when operating under group-A priority control | O: When operating under group-A priority control, frequency ratio between PCLK and ADCLK is 2:1 or 1:1.  1: When operating under group-A priority control, frequency ratio between PCLK and ADCLK is 4:1 or over. | R/W |

ADGSPMR should always be accessed in 16-bits.

Adhere to the above-mentioned restriction; otherwise the following errors may occur.

- (1) Under group-A priority control, if a group-A trigger is input during A/D conversion for group B, A/D conversion for group B is discontinued and A/D conversion for group A proceeds. In this case, on the completion of the A/D conversion, S12GBADI interrupt request may be generated instead of generating S12ADI interrupt request.

- (2) While double-trigger mode is selected in group-scan mode, if a group-A trigger is input during A/D conversion for group B under group-A priority control, A/D conversion for group B is discontinued and A/D conversion for group A proceeds. In this case, on the completion of the A/D conversion, S12GBADI interrupt request may be generated and a wrong data register as a storage destination may be selected, instead of generating S12ADI interrupt request.