# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

発行日: 2005年 07月 21日

# RENESAS TECHNICAL UPDATE

〒100-0004 東京都千代田区大手町 2-6-2 日本ビル 株式会社 ルネサス テクノロジ

問合せ窓口 E-mail: csc@renesas.com

| 製    | 品分類                                                                                                                                                              | MPU&MCU                                        | 発行番号   | TN-7        | /40-A109A/J     | Rev. | 第1版 |  |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------|-------------|-----------------|------|-----|--|--|--|

| 題名   | 7542 グループデータシートのシリアル I/O 2 仕様訂正<br>について                                                                                                                          |                                                |        | 情報分類        | 技術情報            |      |     |  |  |  |

| 適用製品 | M37542<br>M37542                                                                                                                                                 | PRSS<br>PM2-XXXFP/GP/SP/HP, M37542M2T-XXXFP/GP | 対象ロット等 | 関           |                 |      |     |  |  |  |

|      | M37542M2V-XXXFP/GP<br>M37542M4-XXXFP/GP/SP/HP, M37542M4T-XXXFP/GP<br>M37542M4V-XXXFP/GP<br>M37542F8FP/GP/SP/*HP(*ES のみ。量産予定なし)<br>M37542F8TFP/GP, M37542F8VFP/GP |                                                |        | 連<br>資<br>料 | 7542 グループデータシート |      |     |  |  |  |

7542 グループのデータシートにおきまして、下記に示す内容にてシリアル I/O 2 の仕様を 訂正致しますのでご確認ください。

## <訂正内容>

7542 グループのシリアル I/O 2 において、TxD2 端子の出力形式については CMOS 出力のみの対応であり、Nch オープンドレイン出力には対応しておりません。

上記より、データシート上のシリアル I/O 2 TxD2 端子の Nch オープンドレイン出力に関する表記につきまして、これを削除し訂正致します。

7542 グループデータシート Rev.2.06 の該当箇所を訂正し、Rev.3.00 として発行致します。

# <訂正箇所>

訂正箇所について、添付資料「7542グループデータシート訂正箇所」に示します。

以上

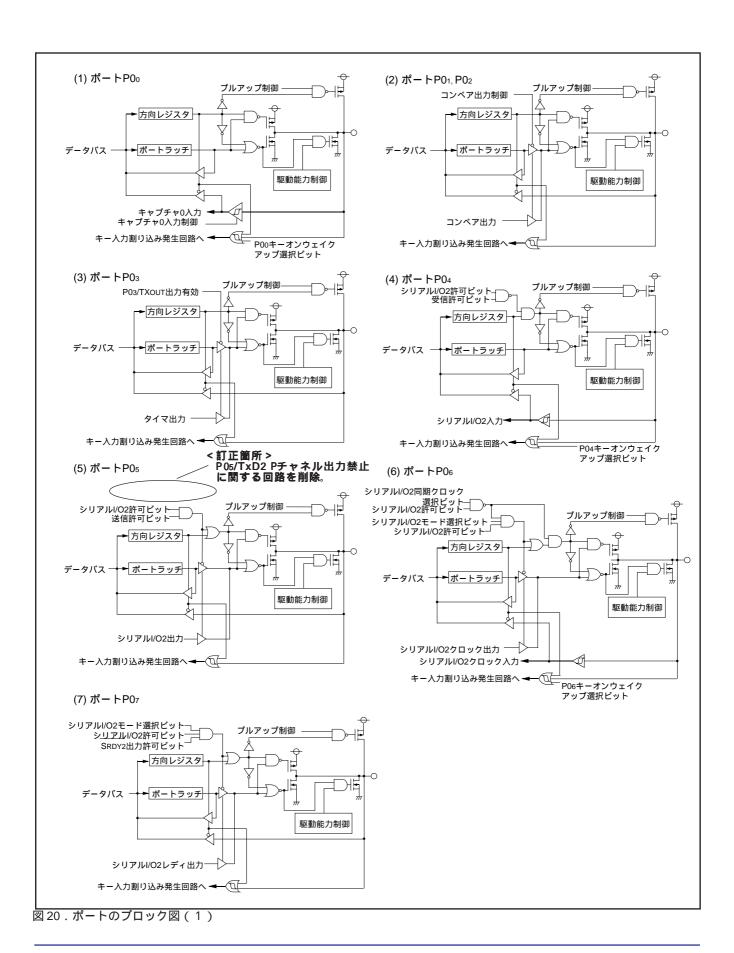

# 7542グループデータシート "Rev.2.06" page 20 of 124

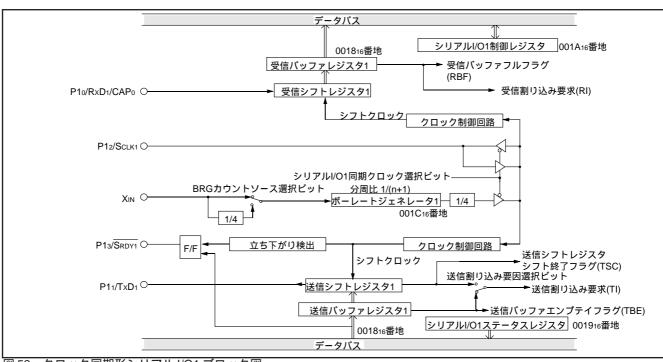

# 7542 グループデータシート "Rev.2.06" page 46 of 124

# < 訂正箇所 > / シリアルI/O2 "TxD2 "出力形式の違い についての記述を追加。

シリアル1/0

7542グループは、シリアルI/O1とシリアルI/O2を持っています。 シリアルI/O1とシリアルI/O2は、シリアルI/O1にバス衝突 検出回路があること及び、シリアルI/O2のTxD2出力形式が GMOS出力のみであることを除き、同じ仕様です。

シリアル 1/01

シリアルI/O1はクロック同期形、非同期形(UART)のどちらでも動作可能です。また、シリアルI/O1動作時のボーレート発生専用タイマ(ボーレートジェネレータ)を備えています。

(1)クロック同期形シリアルI/O1モード

シリアルI/O1制御レジスタのシリアルI/O1モード選択ビット(b6)を"1"にすることによってクロック同期形シリアルI/O1が選択されます。

クロック同期形シリアルI/O1では、シリアルI/O1の動作クロックに、送信側マイコン、受信側マイコンとも同一のクロックを用います。動作クロックとして内部クロックを用いた場合、送受信の開始は送信/受信バッファレジスタへの書き込み信号により行われます。

図 52.クロック同期形シリアル I/O1 ブロック図

図 53. クロック同期形シリアル I/O1 動作図

# 7542 グループデータシート "Rev.2.06" page 53 of 124

【送信バッファレジスタ2/受信バッファレジスタ2]TB2/RB2 送信バッファレジスタと受信バッファレジスタは同じアドレスに配置されており、送信バッファレジスタは書き込み専用、受信バッファレジスタは読み出し専用です。また、キャラクタビット長が7ビットの場合、受信バッファレジスタに格納される受信データのMSBは"0"となります。

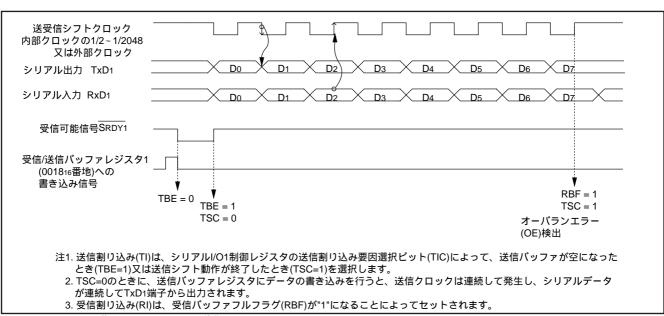

#### 【シリアルI/O2ステータスレジスタ】SIO2STS

シリアルI/O2の動作状態を示すフラグ及び各種エラーフラグで構成された7ビットの読み出し専用レジスタです。ビット4~6の3ビットはUARTモード選択時のみ有効です。

受信バッファフルフラグは受信バッファレジスタの内容を 読み出すど 0 "にクリアされます。

エラー検出は、データが受信シフトレジスタから受信バッファレジスタに転送され、受信バッファフルフラグがセットされると同時に行われます。シリアルI/O2ステータスレジスタへの書き込みですべてのエラーフラグ(OE, PE, FE, SE)がクリアされます。また、シリアルI/O2許可ビット(SIOE)に"0"を書き込むとエラーフラグを含むすべてのステータスフラグが"0"にクリアされます。

このレジスタのビット0~6はリセット時 0 に初期化されますが、シリアルI/O2制御レジスタの送信許可ビットを 1 "にしたときビット2とビット0は 1 "になります。

#### 【シリアルI/O2制御レジスタ】SIO2CON

シリアルI/O2制御レジスタはシリアルI/O2の各種制御を行う8ビットの選択ビットで構成されています。

## 【UART2制御レジスタ JUART2CON

UART選択時有効な4ビットの制御ビットで構成されたし ジスタです。このレジスタの内容でシリアルデータ送受信時のデータフォーマットを設定します。

### 【ボーレートジェネレータ2】BRG2

シリアル転送のビットレートを決定します。

リロードレジスタを持った 8 ビットのカウンタで 値nを 設定することにより、カウントソースを1/(n+1)の分周比で分 周します。

#### シリアル I/O2 に関する注意事項

#### ・シリアルI/O2割り込み

シリアルI/O2の送信許可ビットを"1"にしたとき、シリアルI/O2送信割り込み要求ビットが"1"になります。送信許可に同期した割り込み発生が不要な場合は、以下の手順で設定してください。

シリアルI/O2送信割り込み許可ビットを"0 (禁止)にする。 送信許可ビットを"1"にする。

一命令以上おいてから、シリアルI/O2送信割り込み要求 ビットを"0"にする。

シリアルI/O2送信割り込み許可ビットを"1 (許可)にする。

・シリアルI/O2許可時の入出力端子機能

シリアルI/O2モード選択ビットおよびシリアルI/O2同期クロック選択ビットの設定値により、P06、P07の機能が下記のように変化します。

# (1)シリアルI/O2モード選択ビット "1":

クロック同期形シリアルI/O選択時

- ・シリアルI/O2同期クロック選択ビットの設定

- " 0 ": P06端子は同期クロックの出力端子になります。

- "1": P06端子は同期クロックの入力端子になります。

- ・SRDY2出力許可ビット(SRDY)の設定

- " 0 ": P07端子は通常の入出力端子として使用できます。

- " 1 ": P07端子はSRDY2出力端子になります。

# (2)シリアルI/O2モード選択ビット " 0 ":

クロック非同期(UART)形シリアルI/O選択時

- ・シリアルI/O2同期クロック選択ビットの設定

- " 0 ": P06端子は通常の入出力端子として使用できます。

- " 1 ": P06端子は外部クロックの入力端子になります。

- ・クロック非同期(UART)形シリアルI/O選択時は、P07端子は通常の入出力端子として使用できます。

< 訂正箇所 > P05/TxD2 Pチャネル出力禁止ビット に関する説明を削除。

# 7542 グループデータシート "Rev.2.06" page 54 of 124

図 64.シリアル I/O2 関係レジスタの構成

# 7542 グループデータシート "Rev.2.06" page 98 of 124

## (3) 電気的特性(一般品)

表 16. 電気的特性(1)(一般品)

| 記号        | 項目                                                                               | 測定条件                                                                        |       | 規   | . 格  | 值   |          | 単位  |

|-----------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|-----|------|-----|----------|-----|

| 마 与       |                                                                                  | <b>测定示</b> 什                                                                | 最     | 小   | 標    | 準量  | <b>大</b> |     |

| Vон       | "H"出力電圧<br>P00 ~ P07, P10 ~ P14,<br>P20 ~ P27, P30 ~ P37 (注1)                    | IOH = - 5mA<br>Vcc = 4.0 ~ 5.5V                                             | Vcc - | 1.5 |      |     |          | V   |

|           |                                                                                  | IOH = - 1.0mA<br>マスク ROM 版:Vcc = 2.2 ~ 5.5V<br>FLASH ROM 版:Vcc = 2.7 ~ 5.5V | Vcc - | 1.0 |      |     |          | V   |

| Vol       | " L " 出力電圧<br>P00 ~ P07, P30 ~ P37<br>(駆動能力 = " L " 選択時)<br>P10 ~ P14, P20 ~ P27 | IOL = 5mA<br>VCC = 4.0 ~ 5.5V                                               |       |     |      |     | 1.5      | V   |

|           |                                                                                  | IOL = 1.5mA<br>VCC = 4.0 ~ 5.5V                                             |       |     |      |     | 0.3      | V   |

|           |                                                                                  | IOL = 1.0mA<br>マスク ROM 版:Vcc = 2.2 ~ 5.5V<br>FLASH ROM 版:Vcc = 2.7 ~ 5.5V   |       |     |      |     | 1.0      | V   |

| Vol       | "L"出力電圧<br>P00~P07, P30~P37<br>(駆動能力="H"選択時)                                     | IOL = 15mA<br>VCC = 4.0 ~ 5.5V                                              |       |     |      |     | 2.0      | V   |

|           |                                                                                  | IOL = 1.5mA<br>VCC = 4.0 ~ 5.5V                                             |       |     |      |     | 0.3      | V   |

|           |                                                                                  | IOL = 1.0mA<br>マスク ROM 版: Vcc = 2.2 ~ 5.5V<br>FLASH ROM 版: Vcc = 2.7 ~ 5.5V |       |     |      |     | 1.0      | V   |

| VT+ - VT- | ヒステリシス<br>CNTR0, INT0, INT1, CAP0, CAP1 (注2)<br>P00 ~ P07 (注3)                   |                                                                             |       |     | 0.4  |     |          | V   |

| VT+ - VT- | ヒステリシス<br>RxDo, Sclko, RxD1, Sclk1                                               |                                                                             |       |     | 0.5  |     |          | V   |

| VT+ - VT- | ヒステリシス RESET                                                                     |                                                                             |       |     | 0.5  |     |          | V   |

| liн       | " H " 入力電流<br>P00 ~ P07, P10 ~ P14, P20 ~ P27, P30 ~ P37                         | VI = VCC<br>(端子はフローティング。プルアッ<br>プトランジスタは切り離し状態)                             |       |     |      |     | 5.0      | μА  |

| Iн        | " H " 入力電流 RESET                                                                 | VI = VCC                                                                    |       |     |      |     | 5.0      | μА  |

| Iн        | " H " 入力電流 XIN                                                                   | VI = VCC                                                                    |       |     | 4.0  |     |          | μА  |

| lıL       | " L " 入力電流<br>P00 ~ P07, P10 ~ P14, P20 ~ P27, P30 ~ P37                         | VI = VSS<br>(端子はフローティング。プルアップトランジスタは切り離し状態)                                 |       |     |      |     | - 5.0    | μА  |

| lıL       | " L " 入力電流 RESET                                                                 | VI = VSS                                                                    |       |     |      |     | - 5.0    | μА  |

| lıL       | " L " 入力電流 XIN                                                                   | VI = VSS                                                                    |       |     | - 4  | .0  |          | μА  |

| lıL       | "L"入力電流 P00 ~ P07, P30 ~ P37                                                     | Vı = Vss<br>(プルアップトランジスタ接続時)                                                |       |     | - 0. | 2   | - 0.5    | mA  |

| VRAM      | RAM 保持電圧                                                                         | クロック停止時                                                                     | 2.0   | 0   |      |     | 5.5      | V   |

| Rosc      | オンチップオシレータ発振周波数                                                                  | VCC = 5.0V, Ta = 25                                                         | 100   | 00  | 200  | 0 ; | 3000     | kHz |

| Dosc      |                                                                                  | Vcc = 5.0V、Ta = 25                                                          | 62.   | .5  | 125  | 5 / | 87.5     | kHz |

注1.P11 に関しては , UART1 制御レジスタの P11/TxD1 P チャネル出力禁止ビット(001B16 番地のビット4)が " 0 " の場合です。

< 訂正箇所 > 注1のP05に関する記述を削除。

<sup>2 .</sup> RxD1 , SCLK1 , INT0 , INT1 ( P36 選択時 ) については , ポート P1P3 制御 レジスタのビット 0 , 1 , 2 が " 0 " ( CMOS レベル ) の時のみ ヒステリシスを持ちます。

<sup>3.</sup>キーオンウェイクアップ動作時のみです。

# 7542 グループデータシート "Rev.2.06" page 108 of 124

## (3) 電気的特性(広動作温度範囲版)

表 28. 電気的特性 (1) (広動作温度範囲版)

| 記号        | 項目                                                                               | 測定条件                                                                        |       | 規   | 格    | 值   |      | 単位  |

|-----------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|-----|------|-----|------|-----|

| nu 与      |                                                                                  | <b>测定示</b> 什                                                                | 最     | 小   | 標    | 準量  | 大    |     |

| Vон       | " H " 出力電圧<br>P00 ~ P07, P10 ~ P14,<br>P20 ~ P27, P30 ~ P37 (注1)                 | IOH = - 5mA<br>Vcc = 4.0 ~ 5.5V                                             | Vcc - | 1.5 |      |     |      | V   |

|           |                                                                                  | IOH = - 1.0mA<br>マスク ROM 版:Vcc = 2.4 ~ 5.5V<br>FLASH ROM 版:Vcc = 2.7 ~ 5.5V | Vcc - | 1.0 |      |     |      | V   |

| Vol       | " L " 出力電圧<br>P00 ~ P07, P30 ~ P37<br>(駆動能力 = " L " 選択時)<br>P10 ~ P14, P20 ~ P27 | IOL = 5mA<br>VCC = 4.0 ~ 5.5V                                               |       |     |      |     | 1.5  | V   |

|           |                                                                                  | IOL = 1.5mA<br>VCC = 4.0 ~ 5.5V                                             |       |     |      |     | 0.3  | V   |

|           |                                                                                  | IOL = 1.0mA<br>マスク ROM 版: Vcc = 2.4 ~ 5.5V<br>FLASH ROM 版: Vcc = 2.7 ~ 5.5V |       |     |      |     | 1.0  | V   |

| Vol       | " L " 出力電圧<br>P00 ~ P07, P30 ~ P37<br>(駆動能力 = " H " 選択時)                         | IOL = 15mA<br>VCC = 4.0 ~ 5.5V                                              |       |     |      |     | 2.0  | V   |

|           |                                                                                  | IOL = 1.5mA<br>VCC = 4.0 ~ 5.5V                                             |       |     |      |     | 0.3  | V   |

|           |                                                                                  | IOL = 1.0mA<br>マスク ROM 版: Vcc = 2.4 ~ 5.5V<br>FLASH ROM 版: Vcc = 2.7 ~ 5.5V |       |     |      |     | 1.0  | V   |

| VT+ - VT- | ヒステリシス<br>CNTR0, INT0, INT1, CAP0, CAP1 (注2)<br>P00 ~ P07 (注3)                   |                                                                             |       |     | 0.4  |     |      | V   |

| VT+ - VT- | ヒステリシス<br>RxDo, Sclko, RxD1, Sclk1                                               |                                                                             |       |     | 0.5  |     |      | V   |

| VT+ - VT- | ヒステリシス RESET                                                                     |                                                                             |       |     | 0.5  |     |      | V   |

| liн       | " H " 入力電流<br>P00 ~ P07, P10 ~ P14, P20 ~ P27, P30 ~ P37                         | VI = VCC<br>(端子はフローティング。プルアッ<br>プトランジスタは切り離し状態)                             |       |     |      |     | 5.0  | μА  |

| liн       | " H " 入力電流 RESET                                                                 | VI = VCC                                                                    |       |     |      |     | 5.0  | μА  |

| Iн        | " H " 入力電流 XIN                                                                   | VI = VCC                                                                    |       |     | 4.0  |     |      | μА  |

| lıL       | " L " 入力電流<br>P00 ~ P07, P10 ~ P14, P20 ~ P27, P30 ~ P37                         | VI = VSS<br>(端子はフローティング。プルアップトランジスタは切り離し状態)                                 |       |     |      | -   | 5.0  | μА  |

| lıL       | " L " 入力電流 RESET                                                                 | VI = VSS                                                                    |       |     |      | -   | 5.0  | μА  |

| lıL       | " L " 入力電流 XIN                                                                   | VI = VSS                                                                    |       |     | - 4. | 0   |      | μА  |

| lıL       | "L"入力電流 P00 ~ P07, P30 ~ P37                                                     | VI = Vss<br>(プルアップトランジスタ接続時)                                                |       |     | - 0. | 2 - | 0.5  | mA  |

| VRAM      | RAM 保持電圧                                                                         | クロック停止時                                                                     | 2.0   | 0   |      |     | 5.5  | V   |

| Rosc      | オンチップオシレータ発振周波数                                                                  | VCC = 5.0V, Ta = 25                                                         | 100   | 00  | 200  | 0 3 | 000  | kHz |

| Dosc      | 発振停止検出回路検出周波数                                                                    | Vcc = 5.0V, Ta = 25                                                         | 62.   | .5  | 125  | 5 1 | 87.5 | kHz |

注1.P11に関しては, UART1制御レジスタのP11/TxD1 Pチャネル出力禁止ビット(001B16番地のビット4)が"0"の場合です。

< 訂正箇所 > 注1のP05に関する記述を削除。

<sup>2 .</sup> RxD1 , Sclk1 , INT0 , INT1 ( P36選択時 ) については , ポート P1P3 制御レジスタのビット 0 , 1 , 2 が " 0 " ( CMOS レベル ) の時のみ ヒステリシスを持ちます。

<sup>3.</sup>キーオンウェイクアップ動作時のみです。