Date: Apr. 26, 2011

# RENESAS TECHNICAL UPDATE

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                  |          | Document<br>No.         | TN-RX*-A006A/E                                        | Rev. | 1.00 |

|-----------------------|----------------------------------------------------------|----------|-------------------------|-------------------------------------------------------|------|------|

| Title                 | Points for Caution Regarding the General PWM Timer (GPT) |          | Information<br>Category | Technical Notification                                |      |      |

| Applicable<br>Product | RX62T Group                                              | Lot No.  |                         | RX62T Group User's Manual: Hardware (R01UH0034EJ0100) |      |      |

|                       |                                                          | All lots | Reference<br>Document   |                                                       |      |      |

Thank you for your valued patronage and best wishes for your continued success in business.

We have identified a fault in the general PWM timer (GPT) of RX62T group products. Accordingly, details of the fault, points for caution in usage, and countermeasures are given in this document.

#### ■ Details of the Fault

The common fault details described below have been detected in the general PWM timer status register (GTST), LOCO count status register (LCST), general PWM timer external trigger input interrupt register (GTETINT), and general PWM timer software start register (GTSTR).

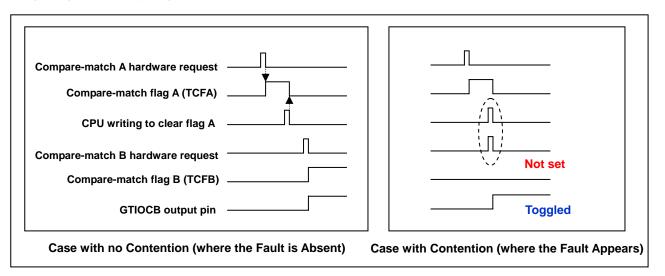

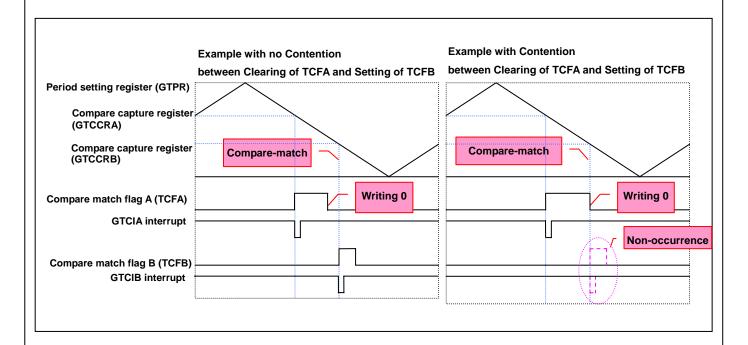

- 1. In cases of contention between the timing of a single write operation by software and setting of the hardware request-source flag, setting of the hardware request-source flag does not proceed.

- 2. In cases of contention between the timing of software clearing of a given flag and setting of a different flag by its hardware source, setting of the hardware request-source flag does not proceed.

The figure below shows an example of operation where there is contention between the timing with which flag A is cleared and flag B is set, resulting in flag B not actually being set.

## Date: April 26, 2011

## Points for Caution in Usage

Working within the following limitations on the specification provides measures against the fault.

- 1. Limit at the time of writing to GTST

- a. Do not write FFh, i.e. all ones, to the lower-order byte (bits 0 to 7) in GTST.

- b. Do not use a byte-writing instruction to write to the higher-order byte (bits 8 to 15) in GTST.

- 2. Point for caution when using compare-match with GTST

When writing to clear other flags in GTST while the compare-match flag and associated interrupt are in use, setting of the flag and generation of the interrupt will not proceed in some cases. When a compare-match flag and associated interrupt are in use, use the compare match (interrupts) as a single type and do not clear other flags in GTST.

3. Point for caution when using the GTST GTCIV interrupt

The following limitations apply to updating of the compare match registers (GTCCRA/GTCCRB) and buffer registers (GTCCRC/GTCCRD/GTCCRE/GTCCRF) while the overflow/underflow interrupt (GTCIV) is in use.

## • Limitations

While the overflow/underflow interrupt (GTCIV) is in use

- a. clear the overflow flag (TCFPO) or underflow flag (TCFPU) soon after generation of the GTCIV interrupt,

- b. when writing to clear the compare-match flags (TCFA/TCFB/TCFC/TCFD/TCFE/TCFF), clear the overflow flag (TCFPO) and underflow flag (TCFPU) at the same time, and

- c. do not clear the other flags in GTST.

Date: April 26, 2011

4. Point for caution in use of the input capture flags in GTST

The following limitations apply when input capture and an associated interrupt are in use.

- Limitations

- a. Do not simultaneously use the input capture flags and associated interrupts (GTCIA/GTCIB) for both the GTIOCA and GTIOCB inputs on a single channel.

- b. Do not clear other flags in GTST while the input capture flags and associated interrupts are in use.

- 5. Points for caution when using the LOCO count status register (LCST)

- a. If the LISC and LISD interrupts are in use at the same time, clear the corresponding interrupt flag within 4 µs following generation of either interrupt.

- b. The source conditions for the LISC and LISD interrupts will not be generated when the source condition for the LISO interrupt is generated, so using the LISC and LISD interrupts at the same time as the LISO interrupt does not create any problems.

- 6. Points for caution when using the general PWM timer external trigger input interrupt register (GTETINT)

The following limitations apply when external trigger input interrupts are in use.

- Limitations

- a. Do not use both rising and falling edges of the external trigger signal as the sense of input interrupts.

- b. Accordingly, do not write ones (03h) to both bits 8 and 9 of the higher-order byte in GTETINT.

- 7. Points for caution when using the general PWM timer software start register (GTSTR)

While settings are in place for starting and stopping due to requests from hardware sources, set hardware sources for all channels and ensure that software does not write to the software start register.

■ Permanent countermeasure

Corrections to eliminate the above limitations are under discussion.