## カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

発行日: 2005年09月21日

# RENESAS TECHNICAL UPDATE

〒100-0004 東京都千代田区大手町 2-6-2 日本ビル 株式会社 ルネサス テクノロジ

問合せ窓口 E-mail: csc@renesas.com

| 製品分類 |                                                    | MPU&MCU | 発行番号   | TN-SH7-A567A/J |                                                                                                     | Rev. | 第1版 |

|------|----------------------------------------------------|---------|--------|----------------|-----------------------------------------------------------------------------------------------------|------|-----|

| 題名   | DMAC 外部アクセスで DACK が分割された場合の<br>DREQ サンプリングについてのご注意 |         |        | 情報分類           | 技術情報                                                                                                |      |     |

| 適用製品 |                                                    |         | 対象ロット等 | 関連資料           | SH7720 ハードウェアマニュアル<br>(RJJ09B0027-0200 Rev2.00)<br>SH7705 ハードウェアマニュアル<br>(RJJ09B0075-0200H Rev2.00) |      |     |

|      | HD6417720<br>HD6417705                             | 全ロット    |        |                |                                                                                                     |      |     |

SH7720、SH7705 の DMAC の外部アクセスにおいて DACK が分割された場合の DREQ サンプリングについて、 ご使用上の注意事項がございます。ご理解、ご了承いただきたくお願いいたします。

#### 1. 不具合現象

DMAC の外部アクセスにおいて、DACK が分割して出力される場合、DREQ のサンプリングが当該外部アクセス中に、1回多く受け付けられる場合があります。

#### 2. 不具合発生条件および現象

条件:外部アクセスにおいて DACK が分割して出力される場合

- (a) 16 バイトアクセス

- (b) 8bit 空間に 32bit アクセス

- (c) 8bit 空間に 16bit アクセス

- (d) 16bit 空間に 32bit アクセス

において、当該空間を DACK で以下のいずれかのアクセス間アイドルサイクル指定を行った場合。

- (i) ライト ライトサイクル間アイドル指定 (IWW = 001 以上)

- (ii) 同一空間リード リードサイクル間アイドル (IWRRS=001 以上)

- (iii) 外部ウェイトマスク指定 (WM = 0)

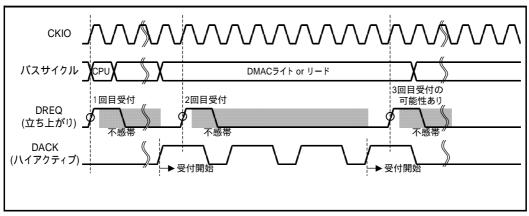

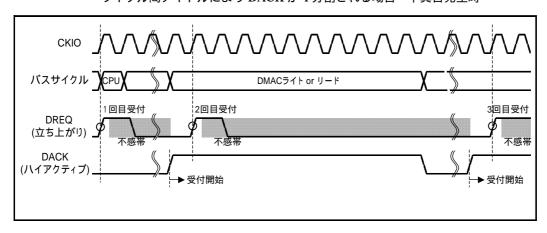

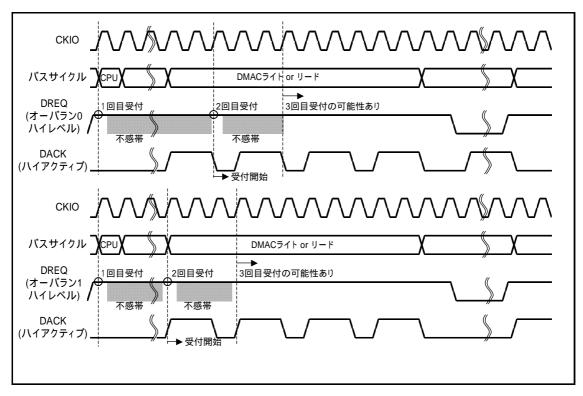

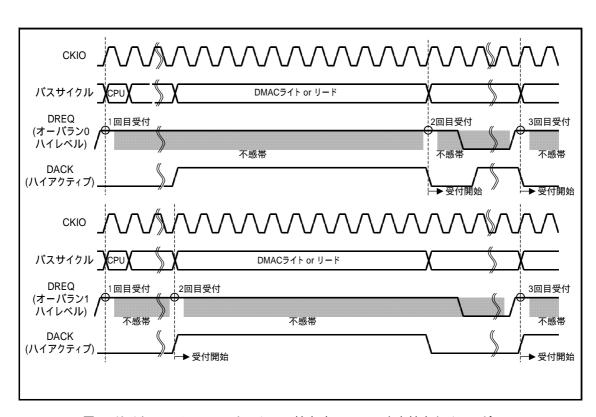

現象:上記のアクセスについて DREQ 端子の検出タイミングは次頁以降の図 1、図 3 のようになります。 上記以外のアクセスの場合は、図 2、図 4 に示すように、正常に DREQ が検出されます。

## 3 . 回避方法

上記 2.に示した条件の外部アクセスにおいては、下記の方法で不具合を回避できます。

- 1) DREQ エッジ検出時: 当該バスサイクル中、最大1回のみ DREQ エッジ入力して使用してください。

- 2)DREQ レベル検出オーバラン 0 時: 当該バスサイクル中、最初の DACK 出力のネゲート検出後、次の DACK 出力のネゲート前までに、 DREQ 入力をネゲートしてください。

- 3)DREQ レベル検出オーバラン 1 時: 当該バスサイクル中、最初の DACK 出力のアサート検出後、次の DACK 出力のアサート前までに、 DREQ 入力をネゲートしてください。

### 4. DREQ 端子の検出タイミング図

図 1. サイクルスチールモード・エッジ検出時の DREQ 入力検出タイミング サイクル間アイドルにより DACK が 4 分割される場合 不具合発生時

図 2. サイクルスチールモード・エッジ検出時の DREQ 入力検出タイミング サイクル間アイドルにより DACK が分割されないる場合 正常時

図 3. サイクルスチールモード・レベル検出時の DREQ 入力検出タイミング サイクル間アイドルにより DACK が 4 分割される場合 不具合発生時

発行日: 2005年09月21日

図 4. サイクルスチールモード・レベル検出時の DREQ 入力検出タイミング サイクル間アイドルにより DACK が分割されないる場合 正常時

以上