Date: Feb. 14, 2012

## RENESAS TECHNICAL UPDATE

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                        | Document<br>No.         | TN-R8C-A021A/E         | Rev. | 1.00 |  |

|-----------------------|--------------------------------|-------------------------|------------------------|------|------|--|

| Title                 | Notes on the R8C/Mx Series (2) | Information<br>Category | Technical Notification |      |      |  |

| Applicable<br>Product | R8C/Mx Series                  | Lot No.                 | Reference<br>Document  |      |      |  |

Note the following for the R8C/Mx Series.

- 1. Notes on flash memory stop and operation transition

- (1) Do not enter stop mode while the FMSTP bit is 1 (the flash memory is stopped).

- (2) Do not enter wait mode while the FMSTP bit is 1 (the flash memory is stopped) and the WTFMSTP bit is 1 (the flash memory is stopped in wait mode).

- (3) Do not enter flash memory stop state for 42 μs after entering from flash memory stop state to flash memory operation state. And do not rewrite the LOCODIS bit in the OCOCR register for 42 μs.

Conditions when entering flash memory operation state from flash memory stop state.

- Set the FMSTP bit to 0 (the flash memory operates).

- Return from wait mode while the WTFMSTP bit is 1 (the flash memory is stopped in wait mode).

- Return from stop mode.

Conditions when entering flash memory stop state from flash memory operation state.

- Set the FMSTP bit to 1 (the flash memory is stopped).

- Enter wait mode while the WTFMSTP bit is 1 (the flash memory is stopped in wait mode).

- Enter stop mode.

- 2. SUBCR register (only for the R8C/M13B Group)

The specification for the XCIN clock control register (SUBCR) in address 00028h has been deleted. When connecting an oscillator to the XCIN clock oscillation circuit or inputting an externally generated clock to the XCIN pin, the pins can be controlled only using bits CKPT2 and CKPT3 in the ESCKCR register (address 00020h).

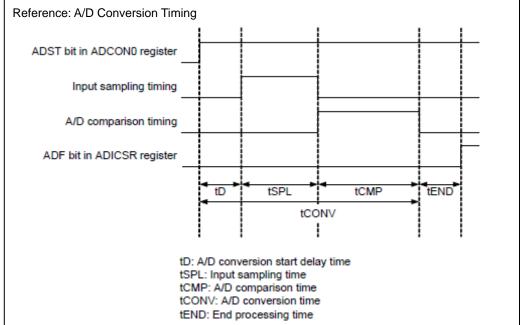

3. A/D conversion time corrections

A/D conversion time in the User's Manual (Hardware) has been revised.

(1) A/D Converter chapter

Conversion time (A/D conversion clock = at 20 MHz)

**2.2**

## Table A/D Conversion Time

|                          | Symbol | A/D Conversion Clock |                        |                       |                |                |  |  |

|--------------------------|--------|----------------------|------------------------|-----------------------|----------------|----------------|--|--|

|                          |        | f1                   | f2                     | f4                    | f8             | fAD            |  |  |

| Item                     |        | CKS0 = 1             | CKS0 = 0               | CKS0 = 1              | CKS0 = 0       | CKS0 = 0       |  |  |

|                          |        | CKS1 = 1             |                        | CKS1 = 0              |                | CKS1 = 0       |  |  |

|                          |        |                      | CKS2 = 1 (2)           |                       |                |                |  |  |

| A/D conversion start     | tD     | 3                    | 3 to 4                 | 3 to 6                | 3 to 10        | 3              |  |  |

| delay time (3)           |        | <b>→16</b>           | →31                    | <b>→61</b>            | <b>→ 121</b>   | <b>→16</b>     |  |  |

| Input sampling time      | tSPL   | <del>15</del>        | <del>30</del>          | 60                    | <del>120</del> | <del>15</del>  |  |  |

| A/D comparison time      | tCMP   | 25                   | 50                     | 100 200               |                | 25             |  |  |

| A/D conversion time      | tCONV  | <del>43</del>        | <del>-83 to 84 -</del> | <del>163 to 166</del> |                | <del>=43</del> |  |  |

| End processing time tEND |        |                      | 2                      | to 3 cycles of fA     | D              |                |  |  |

|                          |        |                      |                        |                       |                |                |  |  |

CKS0, CKS1, CKS2: Bits in ADMOD register

Notes:

- The numerical values indicate the number of states of the system clock (f).

- The numerical values indicate the number of fAD states.

In repeat mode, single sweep mode, and repeat sweep mode, there is no delay time during the A/D conversion time (tCONV) for the second and subsequent rounds.

44 84 to 85 164 to 167 324 to 331 44

## (2) Electrical Characteristics chapter

## Table A/D Converter Characteristics 2.2 tconv Conversion time AVcc = 5.0 V, φAD = 20 MHz 2±5 — — μs tsamp Sampling time φAD = 20 MHz 0.75 — — μs 0.8